Jesper Larsson Träff Sascha Hunold Francesco Versaci (Eds.)

# Euro-Par 2015: Parallel Processing

21st International Conference on Parallel and Distributed Computing Vienna, Austria, August 24–28, 2015, Proceedings

#### **Lecture Notes in Computer Science**

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison, UK Josef Kittler, UK John C. Mitchell, USA Bernhard Steffen, Germany Demetri Terzopoulos, USA Gerhard Weikum, Germany Takeo Kanade, USA Jon M. Kleinberg, USA Friedemann Mattern, Switzerland Moni Naor, Israel C. Pandu Rangan, India Doug Tygar, USA

#### Advanced Research in Computing and Software Science

Subline of Lecture Notes in Computer Science

#### Subline Series Editors

Giorgio Ausiello, *University of Rome 'La Sapienza', Italy* Vladimiro Sassone, *University of Southampton, UK*

#### Subline Advisory Board

Susanne Albers, *TU Munich, Germany* Benjamin C. Pierce, *University of Pennsylvania, USA* Bernhard Steffen, *University of Dortmund, Germany* Deng Xiaotie, *City University of Hong Kong* Jeannette M.Wing, *Microsoft Research, Redmond, WA, USA*  More information about this series at http://www.springer.com/series/7407

Jesper Larsson Träff · Sascha Hunold Francesco Versaci (Eds.)

## Euro-Par 2015: Parallel Processing

21st International Conference on Parallel and Distributed Computing Vienna, Austria, August 24–28, 2015 Proceedings

*Editors* Jesper Larsson Träff Vienna University of Technology Vienna Austria

Sascha Hunold Vienna University of Technology Vienna Austria Francesco Versaci Vienna University of Technology Vienna Austria

ISSN 0302-9743

ISSN 1611-3349

(electronic)

Lecture Notes in Computer Science

ISBN 978-3-662-48095-3

ISBN 978-3-662-48096-0

(eBook)

DOI 10.1007/978-3-662-48096-0

ISBN 978-3-662-48096-0

ISBN 978-3-662-48096-0

ISBN 978-3-662-48096-0

Library of Congress Control Number: 2015945134

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

Springer Heidelberg New York Dordrecht London

© Springer-Verlag Berlin Heidelberg 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer-Verlag GmbH Berlin Heidelberg is part of Springer Science+Business Media (www.springer.com)

#### Preface

Euro-Par is an annual, international conference on European ground, covering all aspects of parallel and distributed processing, ranging from theory to practice, from small to the largest parallel and distributed systems and infrastructures, from fundamental computational problems to full-fledged applications, from architecture, compiler, language and interface design and implementation to tools, support infrastructures, and application performance aspects. Euro-Par has a unique organization into topics capturing all these different aspects and has proven an excellent forum for focused technical discussions within a large, broad, and diverse audience. The Euro-Par conference itself is complemented by a workshop program, where workshops dedicated to more specialized themes, to cross-cutting issues, and to upcoming trends and paradigms can be easily and conveniently organized with little administrative overhead. The Euro-Par topics are relatively stable but have evolved over the years to adequately reflect the state of the field, often in reaction to thematic developments initiated by previous workshops.

Euro-Par's ambition is to be the first choice for presenting solid (European) research in all areas of parallel and distributed computing as covered by the Euro-Par topics. The target audience includes researchers, scientists and students from universities, academic research institutions, research laboratories, development centers, and also companies and industrial organizations with an often vital interest in parallel and distributed computing. With its wide spectrum, Euro-Par fosters interaction between different people and personalities and between different areas and approaches in parallel and distributed computing.

Euro-Par 2015 was the 21th conference in the Euro-Par series, and was organized in Vienna, Austria, by the Vienna University of Technology (TU Wien), Faculty of Informatics, Research Group for Parallel Computing. Previous Euro-Par conferences took place in Stockholm (1995), Lyon (1996), Passau (1997), Southampton (1998), Toulouse (1999), Munich (2000), Manchester (2001), Paderborn (2002), Klagenfurt (2003), Pisa (2004), Lisbon (2005), Dresden (2006), Rennes (2007), Las Palmas (2008), Delft (2009), Ischia (2010), Bordeaux (2011), Rhodes (2012), Aachen (2013), and Porto (2014). In 2016, the conference will be held in Grenoble. General information on the Euro-Par conference series and organization is available at http://www.europar.org.

Euro-Par 2015 was organized into 13 topics, each with its own topic Program Committee consisting of a global chair, a local chair, and at least two additional members. Topics that received a larger number of submissions had additional members, such that each topic member had the responsibility to solicit reviews for about five papers. With this organization, the aim of Euro-Par is that each submitted paper receives at least four reviews, that each paper is actually reviewed by at least one topic committee member, and that papers receive reviews from different communities and groups. For Euro-Par 2015, topic committee members hailed from 17 different countries.

The Euro-Par 2015 Call-for-Papers attracted 190 full-paper submissions, representing 37 countries. The topic committees made sure that all papers were reviewed according to the Euro-Par standards. A total of 772 paper reviews were collected over an eight-week review period, giving an average of 4.1 review reports per paper. Based on the reviews and discussions among the reviewers and topic committee members, 51 papers were selected for presentation at the conference. Of the 51 accepted papers, two were accepted with distinction. Topic 11 attracted few papers and unfortunately none could be accepted. The accepted papers represent contributions from 21 countries from all continents, resulting in an acceptance rate of 27 %. The final decisions on acceptance or rejection of the submitted papers were made at a general Program Committee meeting with physical presence of the conference co-chairs, the local (in some cases global) chairs of the topics, and additional representatives from the Euro-Par Steering Committee. An effort was made to handle potential conflicts of interest at this large meeting in a proper way.

The conference program was organized into parallel sessions roughly following the topics. The two distinguished papers that were presented at separate sessions were:

- Shahar Timnat, Maurice Herlihy and Erez Petrank: "A Practical Transactional Memory Interface".

- Leyuan Wang, Sean Baxter and John Owens: "Fast Parallel Suffix Array on the GPU".

In addition to the paper presentations, Euro-Par 2015 was very pleased to present three renowned invited speakers who gave keynote presentations on new developments and perspectives in their respective areas. These were:

- Michel Raynal (IRISA, University of Rennes, France),

- Mateo Valero (UPC Barcelona, Spain), and

- Christian Scheideler (University of Paderborn, Germany).

The program also included a panel discussion on "The Future of Parallel, Distributed and High-Performance Computing, in Europe", which was moderated by Raffaele Tripiccione, University of Ferrara, Italy, and took place before the conference dinner.

The workshop program of Euro-Par 2015 on the Monday and Tuesday before the main conference included the following workshops:

- 1. Big Data management in Clouds (BigDataCloud)

- 2. Parallel and Distributed Computing Education for Undergraduate Students (Euro-EDUPAR)

- 3. Algorithms, Models, and Tools for Parallel Computing on Heterogeneous Platforms (HeteroPar)

- 4. Large-Scale Distributed Virtual Environments (LSDVE)

- 5. On-chip Memory Hierarchies and Interconnects: Organization, management and implementation (OMHI)

- 6. Parallel and Distributed Agent-Based Simulations (PADABS)

- 7. Performance Engineering for Large-scale Graph Analytics (PELGA)

- 8. Reproducibility in Parallel computing (REPPAR)

- 9. Resiliency in high-performance computing with clouds, grids, and clusters (Resilience)

- 10. Runtime and Operating Systems for the Many-core Era (ROME)

- 11. UnConventional High-Performance Computing (UCHPC)

- 12. Virtualization in High-Performance Cloud Computing (VHPC)

Workshop papers will be published in a separate, post-conference proceedings volume.

The success and relevance of Euro-Par are first and foremost due to the researchers, who submit their contributions to the conference. We hereby warmly thank all contributors of submitted papers, and hope that also those whose contributions were not accepted for presentation this time will feel encouraged by the feedback to continue their work and consider Euro-Par in the future as a relevant venue. Reviewing papers, preparing feedback, and partaking in the discussions is a serious and considerable effort. We expressly thank all topic committee members and all reviewers for their work, especially all topic chairs for always being available and overseeing the reviewing process.

Euro-Par is largely financed by the participants' fees. A small number of institutional and industrial sponsors contributed to the conference, and we deeply thank them all. These contributions are essential for maintaining the modest conference fees, which are a significant factor in making it possible for students to attend the conference. Their names and logos appear on the Euro-Par 2015 website at http://www.europar2015.org. We point out that sponsors have no influence on the conference program or any other aspects of the Euro-Par organization.

This year, 15 special student scholarships consisting in free registrations for the conference and workshops were available and financed by the Euro-Par fund. There was a lot of interest in these scholarships, and we thank the Euro-Par Steering Committee for facilitating this support.

Euro-Par is a large conference and its organization depends on the work of many individuals and organizations. We thank all members of the local organization team, especially Christine Kamper and Margret Steinbuch. Vienna University of Technology (TU Wien) provided lecture halls and seminar rooms at reasonable costs, and supported us with the logistics. We are grateful for that. The Euro-Par Steering Committee, especially the chair Christian Lengauer and the vice-chair Luc Bougé, provided reliable guidance and support throughout the whole organizational phase going back to 2013. We acknowledge the trust put in us to organize the 2015 edition of Euro-Par.

Lastly, we thank all participants who attended the conference and the workshops and contributed to a productive meeting. It was a pleasure to organize and host Euro-Par 2015 in Vienna. We hope that everybody enjoyed the technical program, the social events, and the city of Vienna.

August 2015

Jesper Larsson Träff Sascha Hunold Francesco Versaci

#### Organization

#### **Euro-Par Steering Committee**

#### Chair Christian Lengauer University of Passau, Germany Vice-Chair

Luc Bougé

ENS Rennes, France

#### **European Representatives**

| Marco Danelutto      | University of Pisa, Italy                       |

|----------------------|-------------------------------------------------|

| Emmanuel Jeannot     | LaBRI-Inria, Bordeaux, France                   |

| Christos Kaklamanis  | Computer Technology Institute, Greece           |

| Paul Kelly           | Imperial College, UK                            |

| Thomas Ludwig        | University of Hamburg, Germany                  |

| Emilio Luque         | Autonomous University of Barcelona, Spain       |

| Tomàs Margalef       | Autonomous University of Barcelona, Spain       |

| Wolfgang Nagel       | Dresden University of Technology, Germany       |

| Rizos Sakellariou    | University of Manchester, UK                    |

| Fernando Silva       | University of Porto, Portugal                   |

| Henk Sips            | Delft University of Technology, The Netherlands |

| Domenico Talia       | University of Calabria, Italy                   |

| Felix Wolf           | Technische Universität Darmstadt, Germany       |

| Honorary Members     |                                                 |

| ·                    |                                                 |

| Ron Perrott          | Oxford e-Research Centre, UK                    |

| Karl Dieter Reinartz | University of Erlangen-Nuremberg, Germany       |

#### Observers

| Jesper Larsson Träff | Vienna University of Technology, Austria |

|----------------------|------------------------------------------|

| Denis Trystram       | Grenoble Institute of Technology, France |

#### **Euro-Par 2015 Organization**

# ChairJesper Larsson TräffVienna University of Technology, AustriaProceedingsFrancesco VersaciVienna University of Technology, Austria

#### Workshops

| Sascha Hunold                         | Vienna University of Technology, Austria                                             |

|---------------------------------------|--------------------------------------------------------------------------------------|

| Local Organization                    |                                                                                      |

| Christine Kamper<br>Margret Steinbuch | Vienna University of Technology, Austria<br>Vienna University of Technology, Austria |

#### **Program Committee**

#### **Topic 1: Support Tools and Environments**

| Barcelona Supercomputing Center, Spain        |

|-----------------------------------------------|

|                                               |

| LMU Munich, Germany                           |

|                                               |

| Lawrence Livermore National Laboratory, USA   |

| Pacific Northwest National Laboratory, USA    |

| University of Cyprus, Cyprus                  |

| Forschungszentrum Jülich, Germany             |

| Vrije Universiteit Amsterdam, The Netherlands |

| RWTH Aachen, Germany                          |

|                                               |

#### **Topic 2: Performance Modeling, Prediction, and Evaluation**

| Chair            |                                           |

|------------------|-------------------------------------------|

| Felix Wolf       | Technische Universität Darmstadt, Germany |

| Local Chair      |                                           |

| Marian Vajteršic | University of Salzburg, Austria           |

| Members          |                                           |

| Laura Carrington | San Diego Supercomputer Center, USA       |

| Frédéric Suter   | IN2P3 Computing Center, France            |

| Miquel Pericàs   | Chalmers University of Technology, Sweden |

#### **Topic 3: Scheduling and Load Balancing**

#### Chair

| Denis Trystram      | Grenoble Institute of Technology, France |

|---------------------|------------------------------------------|

| Local Chair         |                                          |

| Hans Kellerer       | Graz University of Technology, Austria   |

| Members             |                                          |

| Henri Casanova      | University of Hawai'i, USA               |

| Vitus Leung         | Sandia National Laboratories, USA        |

| Giorgio Lucarelli   | LIG Grenoble, France                     |

| Ariel Oleksiak      | Poznan Supercomputing Center, Poland     |

| Natasha Shakhlevich | University of Leeds, UK                  |

| Leonel Sousa        | University of Lisbon, Portugal           |

#### **Topic 4: Architecture and Compilers**

#### Chair

| Franz Franchetti          | Carnegie Mellon University, USA          |

|---------------------------|------------------------------------------|

| Local Chair<br>Jens Knoop | Vienna University of Technology, Austria |

| Members                   |                                          |

|                           | T T T T T T T T T T T T T T T T T T T    |

| Markus Schordan    | Lawrence Livermore National Laboratory, USA |

|--------------------|---------------------------------------------|

| Louis-Noël Pouchet | University of California, Los Angeles, USA  |

| Sid Touati         | Inria, France                               |

#### **Topic 5: Parallel and Distributed Data Management**

| Chair                              |                                                    |

|------------------------------------|----------------------------------------------------|

| André Brinkmann                    | University of Mainz, Germany                       |

| Local Chair<br>Harald Kosch        | University of Passau, Germany                      |

| Members                            |                                                    |

| Gabriel Antoniu<br>Veronika Sonigo | Inria Rennes, France<br>FEMTO-ST, Besançon, France |

#### Topic 6: Grid, Cluster and Cloud Computing

#### Chair

| Inria, France                                 |

|-----------------------------------------------|

|                                               |

| University of Innsbruck, Austria              |

|                                               |

| Inria, France                                 |

| CERN, Switzerland                             |

| University of Manchester, UK                  |

| TU Dortmund University, Germany               |

| University of Calabria, Italy                 |

| Georg-August University of Göttingen, Germany |

|                                               |

#### **Topic 7: Distributed Systems and Algorithms**

#### Chair

| André Schiper | EPFL, Switzerland |

|---------------|-------------------|

| Local Chair   |                   |

Josef Widder

Vienna University of Technology, Austria

#### Members

| Antonio Casimiro      | University of Lisbon, Portugal            |

|-----------------------|-------------------------------------------|

| Christof Fetzer       | Dresden University of Technology, Germany |

| Marta Patino-Martinez | Technical University of Madrid, Spain     |

| Pierre Sens           | LIP6/Inria Paris Rocquencourt, France     |

## **Topic 8: Parallel and Distributed Programming, Interfaces and Languages**

| Chair          |                                                 |

|----------------|-------------------------------------------------|

| Bill Gropp     | University of Illinois at Urbana-Champaign, USA |

| Local Chair    |                                                 |

| Erwin Laure    | KTH Royal Institute of Technology, Sweden       |

| Members        |                                                 |

| Keshav Pingali | The University of Texas at Austin, USA          |

| Rajeev Thakur  | Argonne National Laboratory, USA                |

| Michael Gerndt | Technische Universität München (TUM), Germany   |

#### **Topic 9: Multi- and Many-core Programming**

#### Chair

| Marco Aldinucci       | University of Turin, Italy              |

|-----------------------|-----------------------------------------|

| Local Chair           |                                         |

| Siegfried Benkner     | University of Vienna, Austria           |

| Members               |                                         |

| Hans Vandierendonck   | Queen's University Belfast, UK          |

| Franscisco De Sande   | Universidad de La Laguna, Spain         |

| Antoniu Pop           | University of Manchester, UK            |

| Massimo Torquati      | University of Pisa, Italy               |

| Samuel Thibault       | Inria Bordeaux, France                  |

| Massimiliano Meneghin | Autodesk Research, Toronto, Canada      |

| José Daniel García    | Charles III University of Madrid, Spain |

#### **Topic 10: Theory and Algorithms for Parallel Computation**

# ChairPeter SandersKarlsruhe Institute of Technology, GermanyLocal ChairRobert ElsässerUniversity of Salzburg, AustriaMembers

| Leah Epstein      | University of Haifa, Israel                |

|-------------------|--------------------------------------------|

| Pierre Fraigniaud | Paris Diderot University - Paris 7, France |

| Geppino Pucci     | University of Padua, Italy                 |

#### **Topic 11: Communication, Routing and Networks**

| Chair                         |                                         |

|-------------------------------|-----------------------------------------|

| Torsten Hoefler               | ETH Zurich, Switzerland                 |

| Local Chair<br>Holger Fröning | Heidelberg University, Germany          |

| Members                       |                                         |

| Mondrian Nüssle               | Extoll GmbH, Germany                    |

| Federico Silla                | Technical University of Valencia, Spain |

| Mitch Gusat                   | IBM Zurich, Switzerland                 |

| Tor Skeie                     | University of Oslo, Norway              |

#### **Topic 12: Numerical Methods and Applications**

| Chair                                    |                                                         |

|------------------------------------------|---------------------------------------------------------|

| Paolo Bientinesi                         | RWTH Aachen, Germany                                    |

| <b>Local Chair</b><br>Wilfried Gansterer | University of Vienna, Austria                           |

| Members                                  |                                                         |

| Daniel Ruprecht                          | Università della Svizzera italiana, Lugano, Switzerland |

| Xavier Vasseur                           | CERFACS, France                                         |

|                                          | ~ .                                                     |

#### **Topic 13: Accelerator Computing**

| Chair |  |

|-------|--|

|       |  |

Benedict Gaster

| Jörg Keller        | University of Hagen, Germany             |

|--------------------|------------------------------------------|

| Local Chair        |                                          |

| Andreas Steininger | Vienna University of Technology, Austria |

| Members            |                                          |

| Lee Howes          | Qualcomm, USA                            |

| Michael Klemm      | Intel, Germany                           |

| Naoya Maruyama     | RIKEN, Japan                             |

| Norbert Eicker     | Jülich Supercomputing Centre, Germany    |

| Erik Saule         | UNC Charlotte, USA                       |

#### **Euro-Par 2015 Reviewers**

Euro-Par is grateful to all reviewers for their willingness and their effort in providing good feedback to authors and topic committees. All external reviewers are listed and hereby thanked.

University of the West of England, UK

| Ashwin Aji            | Enes Bajrovic     |

|-----------------------|-------------------|

| Goetz Alefeld         | Tomáš Balyo       |

| Pedro Alonso          | Gergö Barany      |

| Andreea Simona Anghel | Denis Barthou     |

| Peter Arbenz          | Ezio Bartocci     |

| Rohit Atre            | Andreas Beckmann  |

| Guillaume Aupy        | Shajulin Benedict |

| Eduard Ayguadé        | Nadia Bennani     |

| Michael Bader         | Fatih Berber      |

Maciej Besta Andreas Bilke Lihan Bin Timo Bingmann Sergey Blagodurov Raphaël Bleuse Francois Bodin Matthias Bollhöfer Matthias Bolten Luc Bougé Pascal Bouvry Francois Broquedis Romain Brossier Kevin Brown Joe Buck Hans-Joachim Bungartz Martin Burtscher Alexandru Calotoiu Louis-Claude Canon Luca Capriotti Alexandra Carpen-Amarie Marc Casas Matteo Ceccarello Eduardo Cesar Eugenio Cesario Vincent Chau Daniel Chavarría Lizhong Chen Peter Chronz Michael Chu Claudiu Cobarzan Carmela Comito Isaías A. Comprés Ureña Daniel Cordeiro Alexandru Costan Georges Da Costa Tatiana Davidovic Fernando B. De Lima Neto Vincenzo De Maio Tiziano De Matteis Daniele De Sensi Diego F. De Souza Angel De Vicente Edvin Deadman Maarten Decat Joachim Deguara

Mrinal Deo Simone Deparis Youssef Diouane Jirí Dokulil Matthieu Dorier Antonio Dorta Andi Drebes Maurizio Drocco Maciej Drozdowski Alex Duran Christoph Dürr Hans Eberle Patrick Eitschberger Wael Elwasif Vanessa End Mattan Erez Gordon Erlebacher M. Anton Ertl Hassan Eslami Toni Espinosa Joël Falcou Rafael Ferreira Da Silva Jiří Filipovič Michael Firbach Markus Flatz Samantha S. Foley Athanasios Foudoulis Basilio B. Fraguela Karl Fuerlinger Matthias Függer João Gante Javier Garcia Blas María Garzarán Rong Ge Thiago Genez Giorgis Georgakoudis Paul Gibbon Mike Giles Giorgis Giorgakoudis David Glesser Bhavishya Goel José Luis Gonzàlez García Georgios Goumas Stef Graillat Matthias Grawinkel Dalvan Griebler

Tobias Grosser Armin Größlinger João F.D. Guerreiro Carla Guillen Jens Gustedt Stefan Guthe Mary Hall Jeff Hammond Frank Hannig Stuart Hawkins Thomas Herault Marc-André Hermanns Fabien Hermenier Ruben Hoeksma Matthias Hofmann Andreas Hollmann Dan Holmes Tetsuya Hoshino Derek Hower Zia Ul Huda Andra-Ecaterina Hugo Maxime Hugues Udo Hönig Shadi Ibrahim Kamran Idrees Hisham Ihshaish Aleksandar Ilic Guillaume Iooss Christian Iwainsky Jeremie Jakubowicz Andreas Janecek Matthias Janetschek Mateusz Jarus Ernesto Jiménez Pavel Jiranek Mark Joshi Dominik Kaaser Imed Kacem Rashid Kaleem Boda Kang Lars Karlsson Kostas Katrinis Kamer Kaya Jörg Keller Martin Keller-Ressel Christoph Kessler

Michael Knobloch Joanna Kolodziej Martin Kong Xi Kong Anthony Kougkas Alessandro Kraemer Andreas Krall Lidia Kuan Jean-Yves L'Excellent Stefan Lankes Johan Larsson Laurent Lefèvre **Dimitrios** Letsios Xiaoming Li Chunhua Liao Mulugeta Libsie Calvin Lin Pei-Hung Lin Torsten Linss Jack Liu Drazen Lucanin Matthias Maiterth Saeed Maleki Andrew Mallinson Valerio Mariani Artur Mariano Stefano Markidis Fabrizio Marozzo Paulo Martins Carlo Mastrojanni Roland Mathà Eduard Mehofer Dirk Meister Gabriele Mencagli Christopher Menke Ludovic Métivier Ulrich Meyer Henning Meyerhenke Samuel Midiff Antoine Miné Claudia Misale Svetislav Momcilovic Hans Moritsch Karen Murphy Claudio Márquez Lars Nagel

Raymond Namyst Alberto Nannarelli Lorenzo Naranio Wahid Nasri **Emanuele** Natale Barry L. Nelson Ulrich Neumerkel Nuno Neves Jean-Marc Nicod Bovana Norris Lucas Nussbaum Yury Olevnik Stephane Operto Anne-Cécile Orgerie Vitaly Osipov Simon Ostermann David Ozog Dario Pacciarelli Sreepathi Pai Ardavan Pedram Hung Pei-Lin Anh Huy Phan Jean-Marc Pierson Ilia Pietri **Rene-Edouard Plessix** Sabri Pllana Antoniu Pop Andreas Prell Ronald Rahaman Abtin Rahimian Cristian Ramon-Cortés Lawrence Rauchwerger Veronika Rehn-Sonigo Paul Renaud-Goud Ruvmán Reves Admilson Ribeiro David Richards Ángel Rodríguez-Rozas Sascha Roloff Thomas Ropars Barry Rountree Alban Rousset Jonathan Rouzaud-Cornabas Karl Rupp Krzysztof Rzadca Jean-Charles Régin

P. Sadayappan **Rizos Sakellariou** Debasmita Samaddar Abdoulave Samake Luis Miguel Sánchez Peter Sanders Martin Sandrieser Ahmet Erdem Sarıyüce Mitsuhisa Sato Erik Saule Christian Scheideler **Olaf Schenk** Wolfram Schiffmann Stephan Schlagkamp Dirk Schmidl **Oliver Schmitt** Stefan Schuh Christian Schulz Martin Schulz R. Oguz Selvitopi Sangmin Seo Marc Sergent Aamer Shah Jun Shirako Min Si Albert Sidelnik Mikhail Smelyanskiy Steven Smith Chrystalla Sofokleous Rafael Sotomayor Jochen Speck Paul Springer Luka Stanisic Josef Strnadel Michelle Strout Jiawen Sun Petter Svärd Tim Süß Andrei Tchernykh Marc Tchiboukdjian Thomas Toifl Fabio Tordini Ennio Torre Guy Tremblay Demetris Trihinas Horst Trinker

Paolo Trunfio Radu Tudoran Nikolaos Tziritas Nico Vervliet Stephane Vialle Frederic Wagner Mohamed Wahib Ke Wang Christian Weiß Andreas Wilhelm Sam Wilson Thomas Worsch Edwin Yaqub Kazutomo Yoshii Qian Yu Muhammad Aurang Zaib Fei Zhang Xin Zhao Wei Zheng Qiuling Zhu Georgios Zois Judicael A. Zounmevo

#### **Euro-Par 2015 Invited Talks**

#### **Concurrent Systems: Hybrid Object Implementations and Abortable Objects**

#### Michel Raynal, IRISA, University of Rennes, France

As they allow processes to communicate and synchronize, concurrent objects are, de facto, the most important objects of concurrent programming. The talk will present and illustrate two important notions associated with such objects. The first one, which is related to their implementation, is the notion of a hybrid implementation. The second one, which is related to their definition, is the notion of an abortable object.

Roughly speaking, a hybrid implementation of a concurrent object is such that the algorithms implementing its operations do not use locks in "good circumstances", those being defined statically or dynamically. In particular the use of locks must be prevented in concurrency-free execution patterns.

The notion of an abortable object is related to the object definition itself. It addresses the case where, in practice, conflicts are rare. So the idea is here to allow a process that invokes an object operation, to return a predefined default value (abort) in specific circumstances, namely in the presence of concurrency. To illustrate this, the talk will present a non-blocking implementation of an abortable stack (non-blocking means here that, in the presence of concurrency, at least one stack operation does not return abort).

#### **Runtime Aware Architectures**

#### Mateo Valero, UPC Barcelona, Spain

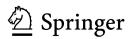

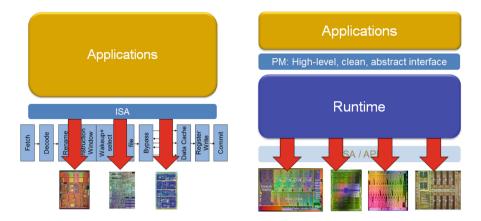

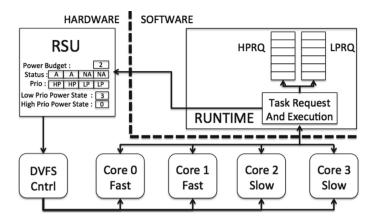

In the last few years, the traditional ways to keep the increase of hardware performance to the rate predicted by the Moore's Law have vanished. When unicores were the norm, hardware design was decoupled from the software stack thanks to a well defined Instruction Set Architecture (ISA). This simple interface allowed developing applications without worrying too much about the underlying hardware, while hardware designers were able to aggressively exploit instruction-level parallelism (ILP) in superscalar processors. With the irruption of multi-cores and parallel applications, this simple interface started to leak. As a consequence, the role of decoupling again applications from the hardware was moved to the runtime system. Efficiently using the underlying hardware from this runtime without exposing its complexities to the application has been the target of very active and prolific research in the last years.

Current multi-cores are designed as simple symmetric multiprocessors (SMP) on a chip. However, we believe that this is not enough to overcome all the problems that

multi-cores already have to face. It is our position that the runtime has to drive the design of future multi-cores to overcome the restrictions in terms of power, memory, programmability and resilience that multi-cores have. In this talk, we introduce a first approach towards a Runtime-Aware Architecture (RAA), a massively parallel architecture designed from the runtime's perspective.

#### Self-stabilizing Distributed Data Structures

#### Christian Scheideler, University of Paderborn, Germany

Once a distributed system becomes large enough, faults are not the exception but the rule. Proactive strategies that aim at protecting a distributed system from becoming corrupted can only protect a system up to a certain point, which is nicely demonstrated by the CAP-Theorem and other impossibility results. So also reactive strategies, which aim at recovering from corruptions, should be considered. A standard approach to obtain systems that are able to recover from any kind of faults is self-stabilization. However, previous research has mostly focused on the case that there are no more faults or other changes to the system (due to pending requests) during self-stabilization. So it is not clear for many of the proposed solutions how well the system would be able to serve requests while it is self-stabilizing. In my presentation I will address this issue for the specific case of self-stabilizing distributed data structures that are managed by a large distributed system that does not just allow changes to the data but also to the set of its members, and I will present our newest results in this area.

#### **Euro-Par 2015 Topics Overview**

#### **Topic 1: Support Tools and Environments**

#### Rosa Badia, Karl Fürlinger, Todd Gamblin, Nathan R. Tallent, Marios D. Dikaiakos, Brian Wylie, Thilo Kielmann, Matthias S. Mueller

Despite an impressive body of research, parallel and distributed programming remains a complex task prone to subtle software issues that can affect both the correctness and the performance of applications. The topic on support tools and environments focuses on tools and techniques to help tackling that complexity. Contributions were sought to address any of the many challenges of parallel and distributed programming related to programmability, portability, correctness, reliability, scalability, efficiency, performance and energy consumption. The aim was to bring together tool designers, developers, and users to share their concerns, ideas, solutions, and products for a wide range of parallel platforms. Contributions with solid theoretical foundations and with strong experimental validations on production-level parallel and distributed systems were especially valued, as were submissions that detailed novel program development tools and environments addressing the expected complexity of exascale systems.

Concrete topics of interest included debugging and correctness tools, hybrid shared memory and message passing tools, instrumentation and monitoring tools and techniques, program development tools, programming environments, interoperable tool environments, integration of tools, compilers and operating systems, performance and reliability analysis (manual and automatic), energy efficiency and savings tools, performance and code structure visualization, testing and analysis tools, computational steering, tool infrastructure and scalability, tool evaluations and comparisons in production environments, tools for extremescale systems, tools for code modernization, tools for homogeneous and heterogeneous multi/many-core processors, and tools and environments for clusters, clouds, and grids.

Two papers were selected for presentation.

#### **Topic 2: Performance Modeling, Prediction, and Evaluation**

#### Felix Wolf, Marian Vajteršic, Laura Carrington, Frédéric Suter, Miquel Pericàs

In recent years, a range of novel methods and tools have been developed for the evaluation, design, and modeling of parallel and distributed systems and applications. At the same time, the term "performance" has broadened to include scalability and energy efficiency, as well as to touch on reliability and robustness in addition to the classic resource-oriented notions.

The aim of the topic was to reach researchers working on different aspects of performance modeling, evaluation, and prediction, be it for systems or for applications running on the whole range of parallel and distributed systems (multi-core and heterogeneous architectures, HPC systems, grid and cloud contexts etc.), and to help bring together current theory and practice. Submissions were sought on novel research in all areas of performance modeling, prediction and evaluation, more concretely on advanced simulation techniques and tools, measurement, benchmarking, and tracing, workload modeling, verification and validation of performance models, performance visualization, power consumption modeling and prediction, performance-driven code optimization, and performance modeling and simulation of emerging exascale systems.

Three papers were selected for presentation.

#### **Topic 3: Scheduling and Load Balancing**

Denis Trystram, Hans Kellerer, Henri Casanova, Vitus Leung, Giorgio Lucarelli, Ariel Oleksiak, Natasha Shakhlevich, Leonel Sousa

Parallel and distributed systems are becoming more complex and powerful, but are still not fully exploited. Scheduling and load balancing issues remain crucial for more efficient and transparent use. At the application level, the mapping of applications onto the underlying computing platforms, and the development of dynamic algorithms able to adapt to the particular characteristics and actual utilization of the systems are of particular relevance. At the system level, areas of interest include the support for modern multi-core and many-core architectures, huge data centers, and virtual systems like cloud infrastructures.

The topic covered aspects related to scheduling and load balancing, ranging from theoretical foundations for modeling and designing efficient and robust strategies to experimental studies, applications and practical tools. This applies to multi-core processors, servers, heterogeneous systems, HPC systems, as well as to distributed systems, such as computational grids, clouds and global computing platforms. Concrete areas of interest included theoretical foundations of scheduling algorithms, robustness of scheduling algorithms, multi-objective scheduling, decentralized or hierarchical scheduling, scheduling at extreme scale, on-line scheduling, scheduling algorithms for homogeneous or heterogeneous platforms, resource management and awareness, energy-efficient scheduling, power-aware and thermal-aware methods in scheduling and load balancing, performance models for scheduling and load balancing, evaluation and analysis of load balancing and scheduling techniques, implementation issues for scheduling, workload characterization and modeling, workflow and job scheduling, and concurrent workflow scheduling.

Eleven papers were selected for presentation.

#### **Topic 4: Architecture and Compilers**

#### Franz Franchetti, Jens Knoop, Markus Schordan, Louis-Noël Pouchet, Sid Touati

The topic dealt with architecture design, languages, and compilation for parallel high performance systems. The areas of interest ranged from microprocessors to large-scale parallel machines (including multi-/many-core, possibly heterogeneous, architectures); from general-purpose to specialized hardware platforms (e.g., graphic coprocessors, low-power embedded systems); and from architecture design to compiler technology and language design.

On the compilation side, topics of interest included programmer productivity issues, concurrent and/or sequential language aspects, program analysis, program transformation, automatic discovery and/or management of parallelism at all levels, auto-tuning and feedback directed compilation, and the interaction between the compiler and the system at large. On the architecture side, the scope spanned system architectures, processor micro-architecture, memory hierarchy, and multi-threading, architectural support for parallelism, and the impact of emerging hardware technologies. Concretely, submissions were sought to deal with compiling for multi-threaded and multi-core and heterogeneous processors and architectures, compiling for emerging architectures (lowpower embedded systems, reconfigurable hardware, processors in memory, graphics processors), iterative, just-in-time, feedback-oriented, dynamic, and machinelearning-based compilation, static analysis and interaction between static and dynamic analysis, compiler, run-time, and architectural support for dynamic adaptation, programmer productivity tools and analysis, program transformation systems, highlevel programming models and tools for multi- and many-core and for heterogeneous architectures, interaction between compiler, runtime system, hardware, and operating system, parallel computer architecture design (ILP, DLP, multi-threaded, and multi-core processors), power-performance efficient designs, software and hardware fault-tolerance techniques, memory hierarchy, emerging memory technologies, and stacked memories, and application-specific, reconfigurable and embedded parallel systems.

Three papers were selected for presentation.

#### **Topic 5: Parallel and Distributed Data Management**

#### André Brinkmann, Harald Kosch, Gabriel Antoniu, Veronika Sonigo

The proliferation of extremely large and heterogeneous data sets poses complex requirements for both cloud and high-performance computing environments, ranging from the integration and management of data to complex data analytics. In addition, managing diverse data requires solutions that integrate different data management paradigms. Thus, data-intensive applications require new approaches and efficient techniques to perform such tasks on locally stored or geographically dispersed data to cope with this data explosion and heterogeneity.

An important issue is the design of highly scalable distributed data platforms offering consistency levels and programming models that can simplify the development of complex, big-data applications, with the ultimate goal of shielding programmers from sources of complexity like concurrency, distribution, and failures. The understanding of applications and storage systems, leading to these scalable data platforms, must be based on empirical evidence.

It is still necessary to improve the provisioning, staging, manipulation, continuous maintenance, and monitoring of data hosted in distributed and heterogeneous systems. This includes the interaction between object storage systems, key-value stores, and parallel file systems with batch-systems and middleware environments. The issue of self-tuning is also of paramount importance for distributed data platforms, which aim to minimize the infrastructure's operational costs or to provide quality-of-service levels by elastically adapting their scale to match dynamic shifts of the workload. Interestingly, these problems can be approached using inter-disciplinary methodologies, such as machine learning, analytical modelling, and control theory. The parallel and concurrent execution at all levels remains key to enable the development of scalable and effective data-intensive applications.

The topic sought papers on all aspects of distributed and parallel data management and data-intensive applications, with a focus on concurrency, parallelism, and distributed processing aspects. Concretely, submissions were encouraged on parallel, replicated, and highly-available distributed databases, distributed and parallel transaction and query processing over homogeneous and heterogeneous management paradigms, parallel and distributed information retrieval, middleware for processing large-scale data, management of parallel and distributed data sources, data-intensive clouds, grids and peer-to-peer systems, empirical evaluation of storage systems, integration of large datasets on parallel systems, internet-scale data-intensive applications, sensor-network data management, mobile data management, cloud- and HPC-based storage architectures and file systems, parallel data streaming and data stream mining, NoSQL data management and analysis (key value, graph management, etc.), parallel and distributed knowledge discovery and data mining, algorithms for security and privacy in data management, and new storage hierarchies in distributed data systems, e.g., based on Flash- and NVRAM-technologies.

Two papers were selected for presentation.

#### **Topic 6: Grid, Cluster and Cloud Computing**

#### Frédéric Desprez, Radu Prodan, Adrien Lebre, Helge Meinhard, Rizos Sakellariou, Uwe Schwiegelshohn, Domenico Talia, Ramin Yahyapour

Heterogeneous Distributed Computing (HDC) systems (e.g., grids, clouds) have changed the IT landscape with respect to the ways in which we access and manage IT infrastructures. The use of computing resources accessible remotely in a seamless way has become essential for many applications in various areas. These technologies provide easy-to-use and on-demand access to large-scale infrastructures and have stimulated much research involving both academia and industry.

Although significant progress has been made in the design, deployment, operation and use of such infrastructures, many research challenges remain to achieve the goal of user-friendly, efficient, and reliable HDC systems. Research issues cover many areas of computer science to address the fundamental capabilities and services that are required in a heterogeneous environment, such as adaptability, scalability, reliability and security, and to support applications as diverse as ubiquitous local services, enterprise-scale virtual organizations, and internet-scale distributed supercomputing. Research on these specific systems greatly benefits from interactions with the many related areas of computer science also represented at Euro-Par. Submissions were sought on HDC systems middleware, HDC systems-enabled applications and platforms, interoperability and portability, resource/service/information discovery, power management in cluster systems, aggregation and federation of clouds, resource management and scheduling, efficient energy usage of resources, programming models, tools, and algorithms for HDC systems, dependability, adaptability, and scalability, security and privacy for HDC systems, workflow management, automated or autonomic management of resources and applications, Quality-of-Service and Service-Level-Agreement in HDC systems, use of grid and cloud computing for HPC applications, scalability and elasticity of applications and algorithms, and faults and failure management in clusters, grids and clouds.

Two papers were selected for presentation.

#### **Topic 7: Distributed Systems and Algorithms**

#### André Schiper, Josef Widder, Antonio Casimiro, Christof Fetzer, Marta Patino-Martinez, Pierre Sens

Parallel computing is heavily dependent on and interacting with the developments and challenges for distributed systems, such as asynchrony, failures, malicious and selfish behavior, load balancing, long latencies, network partitions, disconnected operations, distributed computing models and concurrent data structures, and heterogeneity. The topic on distributed systems and algorithms provided a forum for both theoretical and practical research, of interest to both academia and industry, on distributed systems, distributed systems. Concretely, contributions were sought on design and practice of distributed algorithms and data structures, analysis of the behavior of distributed algorithms and systems, distributed systems, distributed systems, self-organized and self-adjusting distributed systems, distributed systems, collaborative computing, modeling of distributed environments, scalability, concurrency and performance of distributed systems, transactional memory, distributed operating systems, and system support for parallelism.

Two papers were selected for presentation.

#### **Topic 8: Parallel and Distributed Programming, Interfaces and Languages**

#### Bill Gropp, Erwin Laure, Keshav Pingali, Rajeev Thakur, Michael Gerndt

Developing parallel or distributed applications is a difficult task, which requires adequate programming abstractions and models, efficient design tools, parallelization techniques and practices, efficient and effective parallel languages, interfaces, libraries and frameworks, backed up by solid practical and experimental validation. The topic provided a forum for presentation of new results and practical experience in this domain. It emphasized research that facilitates the design and development of high-performance, correct, portable, and scalable parallel programs via adequate parallel and distributed programming model, interface and language support. Contributions were especially sought on assessing programming abstractions, models and methods for usability, performance prediction, scalability, self-adaptation, rapid prototyping and faulttolerance, as needed, for instance, in dynamic heterogeneous parallel and distributed infrastructures. Therefore, authors were urged to include quantitative evaluations to substantiate their claims. Concrete themes included: programming models, languages and libraries for parallel and distributed applications, programming paradigms and techniques for novel infrastructures like accelerators, exascale systems and clouds, design, implementation, performance analysis and performance portability of programming models across parallel and distributed platforms, programming models and techniques for heterogeneity, self-adaptation and fault tolerance, programming tools for application design, implementation, and performance-tuning, application case-studies for benchmarking and comparative studies of parallel programming models, domain-specific libraries and languages, and parallel and distributed programming productivity, usability, and component-based parallel programming.

Two papers were selected for presentation.

#### **Topic 9: Multi- and Many-core Programming**

Marco Aldinucci, Siegfried Benkner, Hans Vandierendonck, Franscisco De Sande, Antoniu Pop, Massimo Torquati, Samuel Thibault, Massimiliano Meneghin, José Daniel García

Modern homogeneous and heterogeneous multi-core and many-core architectures are now part of the high-end and mainstream computing scene and can offer impressive performance for many applications. This architecture trend has been driven by the need to reduce power consumption, increase processor utilization, and deal with the memory-processor speed gap. However, the complexity of these new architectures has created several programming challenges, and achieving performance on these systems is often a difficult task. The topic on multi- and many-core programming explores productive programming of multi- and manycore systems, as well as stand-alone systems with large numbers of cores like GPUs and various types of accelerators; this can also include hybrid and heterogeneous systems with different types of multi-core processors. It focuses on novel research and solutions in the form of programming models, algorithms, languages, compilers, libraries, runtime and analysis tools to increase the programmability of multi-core, many-core, and heterogeneous systems in the context of general-purpose parallel computing, including HPC.

Concretely, submissions were sought to deal with programming techniques, models, frameworks and languages, advances in algorithms and data structures, lock-free algorithms, transactional memories, compiler optimizations and techniques, libraries and runtime systems, tools for discovering and understanding parallelism, performance and scalability, innovative applications and case studies, and hardware support for programming models and runtime systems.

Six papers were selected for presentation, one as distinguished paper.

#### **Topic 10: Theory and Algorithms for Parallel Computation**

#### Peter Sanders, Robert Elsässer, Leah Epstein, Pierre Fraigniaud, Geppino Pucci

Parallelism permeates all levels of current computing systems. Hence, most performance critical applications now need efficient and scalable parallel algorithms at their heart. This is currently causing a renaissance in the study of parallel algorithms and their underlying machine models and theoretical foundations. High quality, original papers were solicited, which contribute new results on parallel algorithms, computational models, and their theoretical foundations. Concrete themes included parallel algorithms for graphs, geometrical data, strings etc., parallel data structures, parallel streaming algorithms, communication algorithms for networks, parallel memory hierarchies, communication-efficient algorithms, algorithms for GPUs and accelerators, exascale algorithms, energy-efficient parallel algorithms, fault-tolerant parallel algorithms, algorithmic challenges arising from concrete applications, algorithms and models for big-data parallel processing, foundations, models, and emerging paradigms for parallel, distributed, multiprocessor and network computation, parallel complexity theory, and lower bounds for parallel computation.

Three papers were selected for presentation.

#### **Topic 11: Communication, Routing and Networks**

#### Torsten Hoefler, Holger Fröning, Mondrian Nüssle, Federico Silla, Mitch Gusat, Tor Skeie

The topic on communication, routing and networks is dedicated to communication issues in scalable compute and storage systems, such as tightly-coupled parallel computers, clusters, and networks of workstations, including hierarchical and hybrid designs featuring several levels of possibly different interconnects. All aspects of communication in modern compute and storage systems were of interest, including advances in the design, implementation, and evaluation of interconnection networks, network interfaces, system and storage area networks, on-chip interconnects, communication protocols and interfaces, routing and communication algorithms, communication interfaces, and communication aspects of parallel and distributed algorithms. Papers were sought to present significant, original work in theory or practice on aspects of performance, reliability and availability, power consumption and heat dissipation, cost, scalability, and management. Industrial case studies were also welcome. Concrete themes included communication modeling of parallel and distributed algorithms, communication interfaces, collective communication and synchronization support, multi-level heterogeneous communication systems, lightweight and user-level communication protocols, on-chip and power-efficient interconnects, routing algorithms and implementations, network performance evaluation and analysis, I/O architectures and storage area networks, interconnection networks, switch architectures, network adapters, and software-defined networking.

The topic received few submissions, and no papers were selected for presentation.

#### **Topic 12: Numerical Methods and Applications**

#### Paolo Bientinesi, Wilfried Gansterer, Daniel Ruprecht, Xavier Vasseur

The solution of large-scale problems in Computational Science and Engineering requires accurate, robust, and efficient numerical algorithms and software that can exploit the potential of modern computer architectures. Such algorithms provide the means to further the development of existing applications, and the building blocks to prototype new methodologies. Ultimately, the objective is to relieve users from issues related to numerical methods and from implementation aspects strongly influenced by the computing environment.

The topic provided a forum for discussing recent developments in the design and implementation of parallel and distributed numerical algorithms and software. The focus was on fundamental algorithmic concepts, efficient implementations on modern parallel architectures (e.g., multi-core and hybrid platforms, multi-GPU systems), design and prototyping of scientific simulation software, performance analysis of numerical methods, and application studies. Concretely, submissions were sought on dense and sparse linear algebra, discrete algorithms in scientific computing, combinatorial scientific computing, solvers (PDE, ODE, DAE), tensor decompositions and contractions, low-rank approximations, methods for uncertainty quantification, differential, integral, and differential algebraic equations, non-linear systems, optimization, transforms (wavelets, FFTs, etc.), and large-scale parallel applications and workflows.

Five papers were selected for presentation.

#### **Topic 13: Accelerator Computing**

#### Jörg Keller, Andreas Steininger, Lee Howes, Michael Klemm, Naoya Maruyama, Norbert Eicker, Erik Saule, Benedict Gaster

Hardware accelerators of many different kinds offer a potential for achieving massive performance in applications that can leverage their high degree of parallelism and customization. Examples include graphics processors (GPUs), many-core devices, as well as more custom devices and customizable FPGA-based systems and streaming dataflow architectures. The research challenge for the topic on accelerators was to explore new avenues for actually realizing this potential. Submissions were encouraged in all areas related to accelerators: architectures, algorithms, languages, compilers, libraries, runtime systems, coordination of accelerators and CPUs, and debugging and profiling tools. Application-related submissions that contribute new insights into fundamental problems or solution approaches in this domain were also welcomed.

Concrete themes included new accelerator architectures, languages, compilers, and runtime environments for accelerator programming, programming techniques for clusters of accelerators, tools for debugging, profiling, and optimizing programs on accelerators, hybrid and heterogeneous computing with several, possibly different types of accelerators, parallel algorithms for accelerators, applications benefitting from acceleration, models and benchmarks for accelerators, manual optimization and auto-tuning, and library support for accelerators.

Ten papers were selected for presentation, one as distinguished paper.

#### Contents

#### **Invited Papers**

| Concurrent Systems: Hybrid Object Implementations                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| and Abortable Objects                                                                                                                                                                   | 3  |

| Runtime-Aware Architectures                                                                                                                                                             | 16 |

| Support Tools and Environments                                                                                                                                                          |    |

| MPI Thread-Level Checking for MPI+OpenMP Applications<br>Emmanuelle Saillard, Patrick Carribault, and Denis Barthou                                                                     | 31 |

| Event-Action Mappings for Parallel Tools Infrastructures                                                                                                                                | 43 |

| Performance Modeling, Prediction and Evaluation                                                                                                                                         |    |

| Low-Overhead Detection of Memory Access Patterns and Their<br>Time Evolution                                                                                                            | 57 |

| Automatic On-Line Detection of MPI Application Structure with Event<br>Flow Graphs                                                                                                      | 70 |

| Online Automated Reliability Classification of Queueing Models<br>for Streaming Processing Using Support Vector Machines<br>Jonathan C. Beard, Cooper Epstein, and Roger D. Chamberlain | 82 |

| Scheduling and Load Balancing                                                                                                                                                           |    |

| A Duplicate-Free State-Space Model for Optimal Task Scheduling |  |

|----------------------------------------------------------------|--|

| Michael Orr and Oliver Sinnen                                  |  |

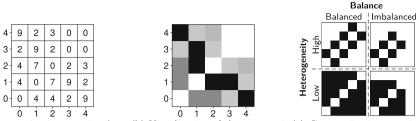

| On the Heterogeneity Bias of Cost Matrices When Assessing<br>Scheduling Algorithms.                                                                                             | 109 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Louis-Claude Canon and Laurent Philippe                                                                                                                                         |     |

| Hardware Round-Robin Scheduler for Single-ISA Asymmetric Multi-core<br>Nikola Markovic, Daniel Nemirovsky, Veljko Milutinovic, Osman Unsal,<br>Mateo Valero, and Adrian Cristal | 122 |

| Moody Scheduling for Speculative Parallelization Alvaro Estebanez, Diego R. Llanos, David Orden, and Belen Palop                                                                | 135 |

| Allocating Jobs with Periodic Demand Variations<br>Olivier Beaumont, Ikbel Belaid, Lionel Eyraud-Dubois,<br>and Juan-Angel Lorenzo-del-Castillo                                 | 147 |

| A Multi–level Hypergraph Partitioning Algorithm Using Rough<br>Set Clustering<br>Foad Lotfifar and Matthew Johnson                                                              | 159 |

| Non-preemptive Throughput Maximization for Speed-Scaling<br>with Power-Down<br>Eric Angel, Evripidis Bampis, Vincent Chau, and Nguyen Kim Thang                                 | 171 |

| Scheduling Tasks from Selfish Multi-tasks Agents                                                                                                                                | 183 |

| Locality and Balance for Communication-Aware Thread Mapping<br>in Multicore Systems                                                                                             | 196 |

| Priority Queues Are Not Good Concurrent Priority Schedulers<br>Andrew Lenharth, Donald Nguyen, and Keshav Pingali                                                               | 209 |

| Load Balancing Prioritized Tasks via Work-Stealing                                                                                                                              | 222 |

| Architecture and Compilers                                                                                                                                                      |     |

| Optimizing Task Parallelism with Library-Semantics-Aware Compilation<br>Peter Thoman, Stefan Moosbrugger, and Thomas Fahringer                                                  | 237 |

| Data Layout Optimization for Portable Performance                                                                                                                               | 250 |

| Automatic Data Layout Optimizations for GPUs                                                                                                                                    | 263 |

#### Parallel and Distributed Data Management

| Performance Impacts with Reliable Parallel File Systems at Exascale Level <i>Ramon Nou, Alberto Miranda, and Toni Cortes</i>                                                                                    | 277 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Rapid Tomographic Image Reconstruction via Large-Scale Parallelization<br>Tekin Bicer, Doga Gursoy, Rajkumar Kettimuthu, Francesco De Carlo,<br>Gagan Agrawal, and Ian T. Foster                                | 289 |

| Grid, Cluster and Cloud Computing                                                                                                                                                                               |     |

| Software Consolidation as an Efficient Energy and Cost Saving Solution<br>for a SaaS/PaaS Cloud Model<br>Alain Tchana, Noel De Palma, Ibrahim Safieddine, Daniel Hagimont,<br>Bruno Diot, and Nicolas Vuillerme | 305 |

| VMPlaceS: A Generic Tool to Investigate and Compare VM Placement<br>Algorithms<br>Adrien Lebre, Jonathan Pastor, and Mario Südholt                                                                              | 317 |

| Distributed Systems and Algorithms                                                                                                                                                                              |     |

| A Connectivity Model for Agreement in Dynamic Systems<br>Carlos Gómez-Calzado, Arnaud Casteigts, Alberto Lafuente,<br>and Mikel Larrea                                                                          | 333 |

| DFEP: Distributed Funding-Based Edge Partitioning<br>Alessio Guerrieri and Alberto Montresor                                                                                                                    | 346 |

| Parallel and Distributed Programming, Interfaces and Languages                                                                                                                                                  |     |

| PR-STM: Priority Rule Based Software Transactions for the GPU<br>Qi Shen, Craig Sharp, William Blewitt, Gary Ushaw,<br>and Graham Morgan                                                                        | 361 |

| Leveraging MPI-3 Shared-Memory Extensions for Efficient PGAS<br>Runtime Systems                                                                                                                                 | 373 |

| Multi- and Many-core Programming                                                                                                                                                                                |     |

| A Practical Transactional Memory Interface<br>Shahar Timnat, Maurice Herlihy, and Erez Petrank                                                                                                                  | 387 |

| A Multicore Parallelization of Continuous Skyline Queries on Data Streams<br><i>Tiziano De Matteis, Salvatore Di Girolamo, and Gabriele Mencagli</i>                                                            | 402 |

| A Fast and Scalable Graph Coloring Algorithm for Multi-core<br>and Many-core Architectures                                                                                                                             | 414 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Composable Deadlock-Free Approach to Object-Based Isolation                                                                                                                                                          | 426 |

| Scalable Data-Driven PageRank: Algorithms, System Issues,<br>and Lessons Learned                                                                                                                                       | 438 |

| How Many Threads will be too Many? On the Scalability<br>of OpenMP Implementations<br>Christian Iwainsky, Sergei Shudler, Alexandru Calotoiu,<br>Alexandre Strube, Michael Knobloch, Christian Bischof, and Felix Wolf | 451 |

| Theory and Algorithms for Parallel Computation                                                                                                                                                                         |     |

| Efficient Nested Dissection for Multicore Architectures<br>Dominique LaSalle and George Karypis                                                                                                                        | 467 |

| Scheduling Trees of Malleable Tasks for Sparse Linear Algebra<br>Abdou Guermouche, Loris Marchal, Bertrand Simon,<br>and Frédéric Vivien                                                                               | 479 |

| Elastic Tasks: Unifying Task Parallelism and SPMD Parallelism<br>with an Adaptive Runtime                                                                                                                              | 491 |

| Numerical Methods and Applications                                                                                                                                                                                     |     |

| Semi-discrete Matrix-Free Formulation of 3D Elastic Full Waveform<br>Inversion Modeling                                                                                                                                | 507 |

| 10,000 Performance Models per Minute – Scalability of the UG4<br>Simulation Framework                                                                                                                                  | 519 |

| Exploiting Task-Based Parallelism in Bayesian Uncertainty Quantification<br>Panagiotis E. Hadjidoukas, Panagiotis Angelikopoulos, Lina Kulakova,<br>Costas Papadimitriou, and Petros Koumoutsakos                      | 532 |

| XXXV |

|------|

|      |

|      |

| Parallelization of an Advection-Diffusion Problem Arising in Edge Plasma<br>Physics Using Hybrid MPI/OpenMP Programming<br>Matthieu Kuhn, Guillaume Latu, Nicolas Crouseilles,<br>and Stéphane Genaud | 545 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Behavioral Non-portability in Scientific Numeric Computing<br>Yijia Gu, Thomas Wahl, Mahsa Bayati, and Miriam Leeser                                                                                  | 558 |

| Accelerator Computing                                                                                                                                                                                 |     |

| Fast Parallel Suffix Array on the GPU<br>Leyuan Wang, Sean Baxter, and John D. Owens                                                                                                                  | 573 |

| Effective Barrier Synchronization on Intel Xeon Phi Coprocessor                                                                                                                                       | 588 |

| High Performance Multi-GPU SpMV for Multi-component<br>PDE-Based Applications                                                                                                                         | 601 |

| Accelerating Lattice Boltzmann Applications with OpenACC<br>Enrico Calore, Jiri Kraus, Sebastiano Fabio Schifano,<br>and Raffaele Tripiccione                                                         | 613 |

| High-Performance and Scalable Design of MPI-3 RMA on Xeon<br>Phi Clusters                                                                                                                             | 625 |

| Improving Performance of Convolutional Neural Networks         by Separable Filters on GPU         Hao-Ping Kang and Che-Rung Lee                                                                     | 638 |

| Iterative Sparse Triangular Solves for Preconditioning                                                                                                                                                | 650 |

| Targeting the ParallellaSpiros N. Agathos, Alexandros Papadogiannakis,and Vassilios V. Dimakopoulos                                                                                                   | 662 |

| Systematic Fusion of CUDA Kernels for Iterative Sparse Linear                                                                                                                                         |     |

| System Solvers                                                                                                                                                                                        | 675 |

| Efficient Execution of Multiple CUDA Applications<br>Using Transparent Suspend, Resume and Migration                                                                                                  | 687 |

| Author Index                                                                                                                                                                                          | 701 |

### **Invited Papers**

#### Concurrent Systems: Hybrid Object Implementations and Abortable Objects

Michel Raynal<sup>1,2,3</sup>  $(\boxtimes)$

<sup>1</sup> Institut Universitaire de France, Paris, France

<sup>2</sup> IRISA, Université de Rennes, Rennes, France

<sup>3</sup> Department of Computing, Polytechnic University, Hong Kong, China raynal@irisa.fr

**Abstract.** As they allow processes to communicate and synchronize, concurrent objects are, de facto, the most important objects of concurrent programming. This paper presents and illustrates two important notions associated with concurrent objects. The first one, which is related to their implementation, is the notion of a hybrid implementation. The second one, which is related to their definition, is the notion of an abortable object.

#### 1 Introduction

**Concurrent Objects: On the Classical Side.** An *object* is a (passive) computing entity providing processes with operations. Only these operations are visible from outside the object. Said differently, the internal representation, of an object remains invisible to the processes. Hence, an object is an abstraction. An object is defined by a specification, which states the properties defining all its correct behaviors. Those are usually captured by the set of the allowed sequences on operation invocations. It appears that the object notion was introduced a long time ago (it seems that its very first appearance dates back in 1967, in the language SIMULA 67 [21]).

The first object, specific to the domain of concurrent programming, seems to be the *semaphore* [3,9]. It is a counting object whose value has to never become negative. Hence, processes can decrease and increase it as long they maintain invariant the fact that it remains non-negative. Then, more sophisticated object constructs have been introduced to cope with concurrent objects, such the concept of a *monitor* [4,20]. In nearly all cases, these language constructs reduce concurrency to sequential computing (they basically ensure that the object operations are executed in mutual exclusion).

**Concurrent Objects: The World is Changing.** Concurrency in multiprocessors (e.g., multicore) is *real* concurrency. It follows that the concurrency concepts and techniques used to cope with multiplexing or interrupt handling are no longer appropriate, and must be revisited to address the new computing world. As expressed in [15]: "Changes in technology can have far-reaching effects on theory. [...] After decades of being respected but not taken seriously, research

© Springer-Verlag Berlin Heidelberg 2015

J.L. Träff et al. (Eds.): Euro-Par 2015, LNCS 9233, pp. 3–15, 2015. DOI: 10.1007/978-3-662-48096-0\_1

on multiprocessor algorithms and data structures is going mainstream" (see also [18,29,34]).

Among the most important concepts that have been introduced there is the notion of progress conditions suited to systems where processes are asynchronous and can fail by crashing. These notions are obstruction-freedom [16], non-blocking [19], and wait-freedom [14]. This has motivated researchers to re-think the implementation of concurrent data structures to exploit the benefit of new architectures (e.g. [2,7,8,26,27,35,36] to cite a few).

**Concurrent Objects: The Topics Addressed in the Paper.** This paper first defines (Sect. 2) basic computing models, which allow us to reason on concurrent objects. Their main characteristics lies in the hardware operations the processes can use, the asynchrony of the processes, and the fact that failures can occur or not.

Then the paper presents the notion of a hybrid implementation of a concurrent object (Sect. 3). Roughly speaking, a hybrid implementation is such that the algorithms implementing the object operations do not use locks in "good circumstances", those being defined statically or dynamically. It follows that in concurrency-free patterns, locks are not used.

Finally (Sect. 4), the paper considers the notion of an abortable object, and illustrates it with a non-blocking abortable stack. An abortable object allows operations to return a default value  $\perp$  when operation invocations are concurrent.