Lejla Batina Matthew Robshaw (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2014

16th International Workshop Busan, South Korea, September 23–26, 2014 Proceedings

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Lejla Batina Matthew Robshaw (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2014

16th International Workshop Busan, South Korea, September 23-26, 2014 Proceedings

Volume Editors

Lejla Batina Radboud University Nijmegen FNWI-iCIS/DS P.O. Box 9010, 6500 GL Nijmegen, The Netherlands E-mail: lejla@cs.ru.nl

Matthew Robshaw Impinj, Inc. 701 N. 34th Street, Suite 300, Seattle, WA 98103, USA E-mail: matt.robshaw@impinj.com

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-662-44708-6 e-ISBN 978-3-662-44709-3 DOI 10.1007/978-3-662-44709-3 Springer Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014947647

LNCS Sublibrary: SL 4 - Security and Cryptology

© International Association for Cryptologic Research 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in ist current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

The 16th International Workshop on Cryptographic Hardware and Embedded Systems was held in Busan, South Korea, during September 23–26, 2014. The workshop was sponsored by the International Association for Cryptologic Research.

CHES 2014 received 127 submissions from all parts of the globe. Each paper was reviewed by at least four independent reviewers, with papers from Program Committee members receiving five reviews in the first round of reviewing. The 43 members of the Program Committee were aided in this complex and time-consuming task by a further 203 external reviewers, providing striking testament to the size and robust health of the CHES community.

Out of the 127 submissions, 33 were chosen for presentation at the workshop. They represented all areas of research that are considered to sit under the CHES umbrella, and they reflected the particular blend of the theoretical and practical that makes CHES such an appealing (and successful) workshop.

We would like to thank the Program Committee and external reviewers for their expert views and spirited contributions to the review process. It was a tremendously difficult task to choose the program for CHES 2014; the standard of submissions was very high. It was even harder to identify a single best paper, but our congratulations go to Naofumi Homma, Yu-ichi Hayashi, Noriyuki Miura, Daisuke Fujimoto, Daichi Tanaka, Makoto Nagata, and Takafumi Aoki from Kobe and Tohoku Universities for the CHES 2014 Best Paper "EM Attack Is Non-Invasive? - Design Methodology and Validity Verification of EM Attack Sensor."

We were delighted that André Weimerskirch was able to accept our invitation to be the invited speaker at CHES 2014. His presentation "V2V Communication Security: A Privacy-Preserving Design for 300 Million Vehicles" cast a fascinating light on a new and far-reaching area of deployment. In addition, expert tutorials by Guido Bertoni and Viktor Fischer and a poster session chaired by Nele Mentens made CHES 2014 the complete workshop. Thank you all for your contributions.

We are, of course, indebted to the general chair, Prof. Kwangjo Kim, and the local Organizing Committee who together proved the ideal liaison for establishing the layout of the program and for supporting the speakers. Our job as program co-chairs was made much easier by the excellent tools developed by Shai Halevi and we offer our thanks to Thomas Eisenbarth, who maintained the CHES 2014 website; both Shai and Thomas were always available at short notice to answer our queries. On behalf of the CHES community we would like to thank the CHES 2014 sponsors. The interest of companies in supporting CHES is an excellent indication of the continued relevance and importance of the workshop.

### VI Preface

Finally, we would like to thank all the authors who contributed their work to CHES 2014. Without you, the workshop would not exist.

July 2014

Lejla Batina Matt Robshaw

# CHES 2014

# Workshop on Cryptographic Hardware and Embedded Systems

Busan, South Korea September 23–26, 2014

Sponsored by the International Association for Cryptologic Research

## **General Chair**

Kwangjo Kim

KAIST, South Korea

## **Program Chairs**

Lejla Batina

Matt Robshaw

Radboud University Nijmegen, The Netherlands Impinj, USA

## **Program Committee**

| Onur Aciiçmez        | Samsung Research America, USA                         |  |

|----------------------|-------------------------------------------------------|--|

| Dan Bernstein        | University of Illinois at Chicago, USA, and           |  |

|                      | Technische Universiteit Eindhoven,                    |  |

|                      | The Netherlands                                       |  |

| Guido Bertoni        | STMicroelectronics, Italy                             |  |

| Christophe Clavier   | University of Limoges, France                         |  |

| Jean-Sebastien Coron | University of Luxembourg, Luxembourg                  |  |

| Thomas Eisenbarth    | Worcester Polytechnic Institute, USA                  |  |

| Junfeng Fan          | Nationz Technologies, China                           |  |

| Wieland Fischer      | Infineon Technologies, Germany                        |  |

| Pierre-Alain Fouque  | Université Rennes 1 and Institut Universitaire        |  |

|                      | de France, France                                     |  |

| Kris Gaj             | George Mason University, USA                          |  |

| Benedikt Gierlichs   | KU Leuven, Belgium                                    |  |

| Louis Goubin         | University of Versailles, France                      |  |

| Tim Güneysu          | Ruhr-Universität Bochum, Germany                      |  |

| Dong-Guk Han         | Kookmin University, South Korea                       |  |

| Helena Handschuh     | Cryptography Research, USA, and KU Leuven,<br>Belgium |  |

| Michael Hutter       | Graz University of Technology, Austria                |  |

Marc Jove Technicolor, USA Howon Kim Pusan National University, South Korea Ilva Kizhvatov Riscure. The Netherlands François Koeune Université Catholique de Louvain, Belgium Farinaz Koushanfar ECE, Rice University, USA Gregor Leander Ruhr-Universität Bochum, Germany Kerstin Lemke-Rust Bonn-Rhein-Sieg University of Applied Sciences, Germany Roel Maes Intrinsic-ID, The Netherlands Graz University of Technology, Austria Stefan Mangard Marcel Medwed NXP Semiconductors, Austria Elke De Mulder Cryptography Research, USA/France Christof Paar Ruhr-Universität Bochum, Germany Dan Page University of Bristol, UK Eric Peeters Texas Instruments, USA Axel Poschmann NXP Semiconductors, Germany **Emmanuel Prouff** ANSSI, France Francesco Regazzoni ALaRI, Lugano, Switzerland Matthieu Rivain CryptoExperts, France Ahmad-Reza Sadeghi Technische Universität Darmstadt/CASED, Germany Kazuo Sakiyama University of Electro-Communications, Japan Akashi Satoh University of Electro-Communications, Japan Patrick Schaumont Virginia Tech. USA Peter Schwabe Radboud University Nijmegen, The Netherlands Daisuke Suzuki Mitsubishi Electric, Japan Mehdi Tibouchi NTT Secure Platform Laboratories, Japan KU Leuven, Belgium Ingrid Verbauwhede **Bo-Yin Yang** Academia Sinica, Taiwan

## **External Reviewers**

Toru Akishita Frederik Armknecht Gilles Van Assche Aydin Aysu Yoo-Jin Baek Thomas Baignères Josep Balasch Guy Barwell Georg Becker Sonia Belaid Alexandre Berzati Shivam Bhasin

Begül Bilgin Olivier Billet Peter Birkner Christina Boura Nicolas Bruneau Samuel Burri Eleonora Cagli Anne Canteaut Claude Carlet Ricardo Chaves Chien-Ning Chen Cong Chen Ming-Shing Chen Tung Chou Chitchanok Chuengsatiansup Mafalda Cortez Bita Darvish-Rohani Joan Daemen Jeroen Delvaux Odile Derouet Jean-François Dhem Christoph Dobraunig Benedikt Driessen

Francois Durvaux Barıs Ege Maria Eichlseder Benoit Feix Martin Feldhofer Matthieu Finiasz Robert FitzPatrick Jean-Pierre Flori Hamza Fraz Steven Galbraith Bayrak Ali Galip Jean-Francois Gallais Berndt Gammel Lubos Gaspar Laurie Genelle Benoit Gerard Nahid Farhady Ghalaty Chris Gori Hannes Gross Vincent Grosso Jorge Guajardo Sylvain Guillev Frank Gurkavnak Benoit Gérard Bilal Habib Mike Hamburg Neil Hanley Christian Hanser Nadia Heninger Anthony Van Herrewege Johann Hevszl Markus Hinkelmann Gesine Hinterwälder Naofumi Homma Ekawat Homsirikamol Seokhie Hong Philippe Hoogvorst Siam Umar Hussain Jong-Hvuk Im Jong-Yeon Park Pascal Junod Stefan Katzenbeisser Stéphanie Kerckhof HeeSeok Kim Hyunmin Kim

Tae Hyun Kim Taewon Kim Thomas Korak Po-Chun Kuo Sebastian Kutzner Mario Lamberger Tanja Lange Martin Lauridsen Moon Kvu Lee Vincent van der Leest Andrew Leiserson Tancrède Lepoint Liran Lerman Yang Li Zhe Liu Patrick Longa Robert Lorentz Abhranil Maiti Avradip Mandal Stefan Mangard Federica Maria Marino Damien Marion Mark Marson Daniel Martin Silvia Mella Filippo Melzani Florian Mendel Bernd Mever Azalia Mirhoseini Oliver Mischke Norivuki Miura Amir Moradi Nadia El Mrabet Michael Muehlberghuber Arslan Munir Yumiko Murakami Ruben Niederhagen Eva Van Niekerk Velickovic Nikola Ivica Nikolić Ventzislav Nikov Svetla Nikova Martin Novotny Colin O'Flynn Katsuyuki Okeya

David Oswald Jing Pan **Roel Peeters** Pedro Peris-Lopez John Pham Thomas Plos Joop van de Pol Thomas Pöppelmann Frank Quedenfeld Michael Quisquater Yamini Ravishankar Christian Rechberger Oscar Reparaz Thomas Roche Pankaj Rohatgi Sondre Røniom Masoud Rostami Sujov Sinha Rov Vladimir Rozic Minoru Saeki Gokay Saldamli Ahmad Salman Peter Samarin Jacek Samotvia Fabrizio De Santis Pascal Sasdrich Falk Schellenberg Werner Schindler Alexander Schloesser Martin Schläffer **Tobias Schneider** Rabia Shahid Aria Shahverdi Malik Umar Sharif Koichi Shimizu Jeong Eun Song Raphael Spreitzer Albert Spruyt Francois-Xavier Standaert Marc Stoettinger Daehvun Strobel Takeshi Sugawara Berk Sunar Ruggero Susella

Pawel Swierczynski Mostafa Taha Yannick Teglia Russ Tessier Adrain Thillard Mike Tunstall Pim Tuyls Kerem Varici Rajesh Velegalati Alexandre Venelli Fre Vercauteren Dennis Vermoen Vincent Verneuil Ivan Visconti Marcin Wójcik Megan Wachs Christian Wachsmann Erich Wenger Carolyn Whitnall Alexander Wild Theodore Winograd Christopher Wolf Jasper van Woudenberg Antoine Wurcker Tolga Yalcin Panasayya Yalla Dai Yamamoto Bohan Yang Shang-Yi Yang Gavin Xiaoxu Yao Xin Ye Meng-Day Yu Christian Zenger Ralf Zimmermann

## Local Organizers

Kwangjo Kim Kyung Hyune Rhee Howon Kim Daehyun Ryu Sanguk Shin Dongkuk Han Dooho Choi Byoungcheon Lee KAIST, South Korea Pukyong National University, South Korea Pusan National University, South Korea Hansei University, South Korea Pukyong National University, South Korea Kookmin University, South Korea ETRI, South Korea Joongbu University, South Korea

# **Table of Contents**

# Side-Channel Attacks

| EM Attack Is Non-invasive? - Design Methodology and Validity<br>Verification of EM Attack Sensor<br>Naofumi Homma, Yu-ichi Hayashi, Noriyuki Miura,<br>Daisuke Fujimoto, Daichi Tanaka, Makoto Nagata, and<br>Takafumi Aoki | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A New Framework for Constraint-Based Probabilistic Template Side<br>Channel Attacks                                                                                                                                         | 17 |

| How to Estimate the Success Rate of Higher-Order Side-Channel<br>Attacks<br>Victor Lomné, Emmanuel Prouff, Matthieu Rivain,<br>Thomas Roche, and Adrian Thillard                                                            | 35 |

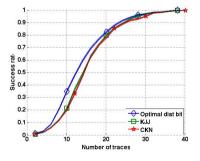

| Good Is Not Good Enough: Deriving Optimal Distinguishers from<br>Communication Theory<br>Annelie Heuser, Olivier Rioul, and Sylvain Guilley                                                                                 | 55 |

## New Attacks and Constructions

| "Ooh Aah Just a Little Bit" : A Small Amount of Side Channel Can<br>Go a Long Way                                                                                | 75  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Destroying Fault Invariant with Randomization: A Countermeasure for<br>AES against Differential Fault Attacks                                                    | 93  |

| Reversing Stealthy Dopant-Level Circuits<br>Takeshi Sugawara, Daisuke Suzuki, Ryoichi Fujii, Shigeaki Tawa,<br>Ryohei Hori, Mitsuru Shiozaki, and Takeshi Fujino | 112 |

| Constructing S-boxes for Lightweight Cryptography with Feistel<br>Structure                                                                                      | 127 |

# Countermeasures

| A Statistical Model for Higher Order DPA on Masked Devices | 147 |

|------------------------------------------------------------|-----|

| A. Adam Ding, Liwei Zhang, Yunsi Fei, and Pei Luo          |     |

| Fast Evaluation of Polynomials over Binary Finite Fields and                                                         |     |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Application to Side-Channel Countermeasures                                                                          | 170 |

| Jean-Sébastien Coron, Arnab Roy, and Srinivas Vivek                                                                  |     |

| Secure Conversion between Boolean and Arithmetic Masking of Any                                                      |     |

| Order<br>Jean-Sébastien Coron, Johann Großschädl, and                                                                | 188 |

| Praveen Kumar Vadnala                                                                                                |     |

| Making RSA–PSS Provably Secure against Non-random Faults<br>Gilles Barthe, François Dupressoir, Pierre-Alain Fouque, | 206 |

| Benjamin Grégoire, Mehdi Tibouchi, and                                                                               |     |

| Jean-Christophe Zapalowicz                                                                                           |     |

|                                                                                                                      |     |

# Algorithm Specific SCA

| Side-Channel Attack against RSA Key Generation Algorithms<br>Aurélie Bauer, Éliane Jaulmes, Victor Lomné,<br>Emmanuel Prouff, and Thomas Roche | 223 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Get Your Hands Off My Laptop: Physical Side-Channel Key-Extraction<br>Attacks on PCs<br>Daniel Genkin, Itamar Pipman, and Eran Tromer          | 242 |

| RSA Meets DPA: Recovering RSA Secret Keys from Noisy Analog<br>Data                                                                            | 261 |

| Simple Power Analysis on AES Key Expansion Revisited<br>Christophe Clavier, Damien Marion, and Antoine Wurcker                                 | 279 |

# **ECC** Implementations

| Efficient Pairings and ECC for Embedded Systems                                                     | 298  |

|-----------------------------------------------------------------------------------------------------|------|

| Thomas Unterluggauer and Erich Wenger                                                               |      |

| Curve41417: Karatsuba Revisited<br>Daniel J. Bernstein, Chitchanok Chuengsatiansup, and Tanja Lange | 316  |

| Implementations                                                                                     |      |

|                                                                                                     | 0.05 |

| Cofactorization on Graphics Processing Units        | 335 |

|-----------------------------------------------------|-----|

| Andrea Miele, Joppe W. Bos, Thorsten Kleinjung, and |     |

| Arjen K. Lenstra                                    |     |

|                                                     |     |

Enhanced Lattice-Based Signatures on Reconfigurable Hardware ...... 353 Thomas Pöppelmann, Léo Ducas, and Tim Güneysu

| Compact Ring-LWE Cryptoprocessor<br>Sujoy Sinha Roy, Frederik Vercauteren, Nele Mentens,<br>Donald Donglong Chen, and Ingrid Verbauwhede                                                             | 371 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Hardware Implementations of Symmetric<br>Cryptosystems                                                                                                                                               |     |

| ICEPOLE: High-Speed, Hardware-Oriented Authenticated<br>Encryption                                                                                                                                   | 392 |

| FPGA Implementations of SPRING: And Their Countermeasures<br>against Side-Channel Attacks<br>Hai Brenner, Lubos Gaspar, Gaëtan Leurent, Alon Rosen, and<br>François-Xavier Standaert                 | 414 |

| FOAM: Searching for Hardware-Optimal SPN Structures and<br>Components with a Fair Comparison<br>Khoongming Khoo, Thomas Peyrin, Axel Y. Poschmann, and<br>Huihui Yap                                 | 433 |

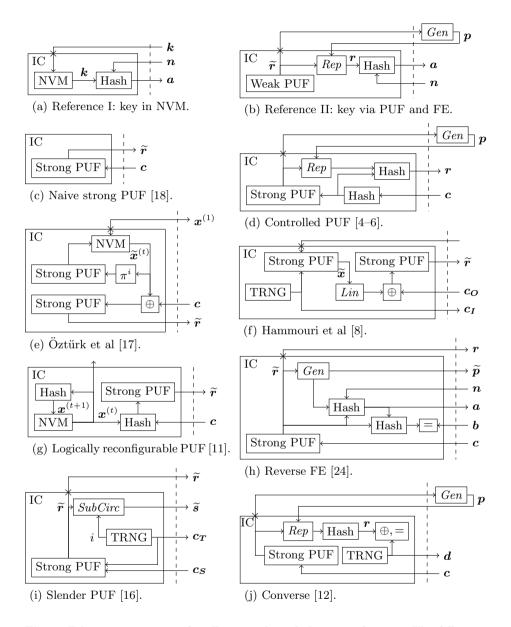

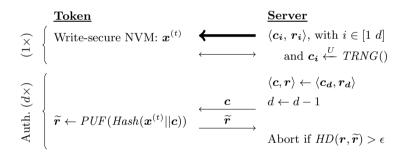

| PUFs                                                                                                                                                                                                 |     |

| Secure Lightweight Entity Authentication with Strong PUFs:<br>Mission Impossible?<br>Jeroen Delvaux, Dawu Gu, Dries Schellekens, and<br>Ingrid Verbauwhede                                           | 451 |

| Efficient Power and Timing Side Channels for Physical Unclonable<br>Functions<br>Ulrich Rührmair, Xiaolin Xu, Jan Sölter, Ahmed Mahmoud,<br>Mehrdad Majzoobi, Farinaz Koushanfar, and Wayne Burleson | 476 |

| Physical Characterization of Arbiter PUFs<br>Shahin Tajik, Enrico Dietz, Sven Frohmann, Jean-Pierre Seifert,<br>Dmitry Nedospasov, Clemens Helfmeier, Christian Boit, and<br>Helmar Dittrich         | 493 |

| Bitline PUF: Building Native Challenge-Response PUF Capability into<br>Any SRAM<br>Daniel E. Holcomb and Kevin Fu                                                                                    | 510 |

# **RNGs and SCA Issues in Hardware**

| Embedded Evaluation of Randomness in Oscillator Based Elementary<br>TRNG<br>Viktor Fischer and David Lubicz     | 527 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Entropy Evaluation for Oscillator-Based True Random Number<br>Generators                                        | 544 |

| Side-Channel Leakage through Static Power: Should We Care about in<br>Practice?                                 | 562 |

| Gate-Level Masking under a Path-Based Leakage Metric<br>Andrew J. Leiserson, Mark E. Marson, and Megan A. Wachs | 580 |

| Early Propagation and Imbalanced Routing, How to Diminish in<br>FPGAs                                           | 598 |

| Author Index                                                                                                    | 617 |

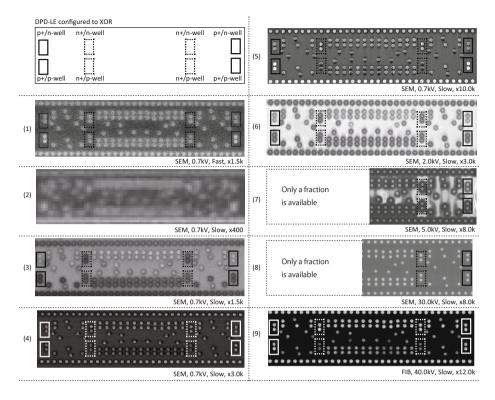

# EM Attack Is Non-invasive? - Design Methodology and Validity Verification of EM Attack Sensor

Naofumi Homma<sup>1</sup>, Yu-ichi Hayashi<sup>1</sup>, Noriyuki Miura<sup>2</sup>, Daisuke Fujimoto<sup>2</sup>, Daichi Tanaka<sup>2</sup>, Makoto Nagata<sup>2</sup>, and Takafumi Aoki<sup>1</sup>

<sup>1</sup> Graduate School of Information Sciences, Tohoku University, Japan homma@aoki.ecei.tohoku.ac.jp

<sup>2</sup> Graduate School of System Informatics, Kobe University, Japan miura@cs.kobe-u.ac.jp

Abstract. This paper presents a standard-cell-based semi-automatic design methodology of a new conceptual countermeasure against electromagnetic (EM) analysis and fault-injection attacks. The countermeasure namely EM attack sensor utilizes LC oscillators which detect variations in the EM field around a cryptographic LSI caused by a micro probe brought near the LSI. A dual-coil sensor architecture with an LUT-programming-based digital calibration can prevent a variety of microprobe-based EM attacks that cannot be thwarted by conventional countermeasures. All components of the sensor core are semiautomatically designed by standard EDA tools with a fully-digital standard cell library and hence minimum design cost. This sensor can be therefore scaled together with the cryptographic LSI to be protected. The sensor prototype is designed based on the proposed methodology together with a 128bit-key composite AES processor in  $0.18\mu m$  CMOS with overheads of only 2 respectively. The validity against a variety of EM attack scenarios has been verified successfully.

**Keywords:** EM analysis attack, EM fault injection attack, countermeasure, attack detection, micro EM probe.

## 1 Introduction

Side-channel attacks have become a source of major concern in the design and evaluation of cryptographic LSIs. In such attacks, side-channel information, such as power dissipation, electromagnetic (EM) radiation, and/or the timing of internal operations, are observed or manipulated. Two of the best known attacks developed thus far are simple power analysis (SPA) and differential power analysis (DPA), both of which were proposed by Kocher et al. [1][2]. A variety of related attacks and countermeasures have been reported [3]. EM analysis (EMA), which exploits EM radiation from LSIs, is also known as a potentially more versatile alternative of power analysis [4]-[6].

L. Batina and M. Robshaw (Eds.): CHES 2014, LNCS 8731, pp. 1–16, 2014.

$<sup>\</sup>textcircled{O}$  International Association for Cryptologic Research 2014

One of the main characteristics of EMA is that it can perform the precise observation of information leakage from a specific part of the target LSI. Such locally observed EM radiation underlies the effectiveness of EMA [7]. In a semiinvasive context, it enables attacks to be performed at the surface of LSIs beyond the conventional security assumptions (i.e., power/EM models or attackers' capabilities). For example, the study on EMA in [8] showed that the use of micro magnetic field probing makes it possible to obtain more detailed information about an unpacked microcontroller. The authors of [8] first showed that the charge (low-to-high transition) and discharge (high-to-low transition) are distinguishable by EMA. The feasibility and effectiveness of localized EM fault injection exploiting this feature were also demonstrated in [9]. In general, such semi-invasive attacks are feasible since a plastic mold package device can be unpacked easily at low cost. Hereafter, we refer to the above sophisticated EM attack measuring and exploiting local information by micro scale probing as "microprobe-based EM attack."

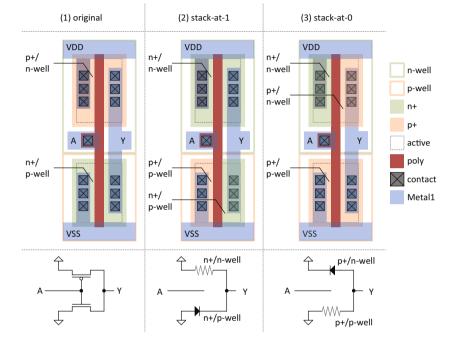

More surprisingly, the possibility of exploiting leaks inside semi-custom ASICs by such microprobe-based EMA was shown in [10]. This impressive work showed current-path and internal-gate leaks in a standard cell, and geometric leaks in a memory macro were measurable by placing a micro magnetic field probe on its surface. This suggests that most of the conventional countermeasures become ineffective if such leaks are measured by attackers. For example, measuring current-path leaks circumvents conventional gate-level countermeasures involving WDDL [11], RSL [12], and MDPL [3]. Furthermore, measuring internal-gate leaks (e.g., from XOR gates) can be used to exploit, for example, XOR gates for unmasking operations. Conventional ROM-based countermeasures using dualrail and pre-charge techniques can also be circumvented by measuring geometric leaks in a memory macro. These results still seem to be only in the realm of laboratory case studies. However, there is no doubt that microprobe-based EMA attacks on the surface of LSIs represent one of the most feasible types of attacks that operate by exploiting such critical leaks.

In order to reduce current-path and internal-gate leaks, a transistor-level countermeasure was also discussed in [10]. Such leaks can be reduced using transistorlevel balancing (hiding). However, transistor-level countermeasures usually increase the design cost and significantly decrease the circuit performance. In the worst-case scenario, designers are required to prepare many balanced cells for every critical component and to perform the place and route with the utmost care. In addition, the literature does not provide any countermeasures against geometric leaks. Thus, the problem of designing effective countermeasures is still open, and the threat of microprobe-based EM attacks using such leaks is expected to increase in the future with the advancement of measurement instruments and techniques.

A natural approach to counteracting microprobe-based EM attacks is to prevent micro probes from approaching the LSI surface. The detection of package opening might be a possible solution [13], but such detection usually employs special packaging materials, which limits its applicability due to the substantial increase in manufacturing cost. In addition, tailored packaging cannot guarantee resistance against attacks from the reverse side of the chip. Another possibility is to install an active shield on or around the LSI to be protected [14]-[16]. However, the power needed to drive signals through the shield is non-trivial. A dynamic active shield surrounding an LSI was first presented in [16]. The new concept of 3D LSI integration is designed to counteract EM attacks exploiting all aspects of the LSI. However, such shielding countermeasures inevitably increase power consumption and implementation cost.

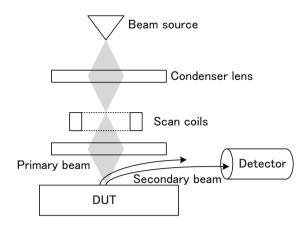

With the aim to address the above issues, this paper introduces a new countermeasure against such high-precision EM attacks using micro EM probes. The countermeasure is based on the physical law that any probe (i.e., a looped conductor) is electrically coupled with the measured object when they are placed close to each other. In other words, a probe cannot measure the original EM field without disturbing it. The proposed method detects the invasion by employing a sensor based on LC oscillators and therefore applies to any EM analysis and fault injection attack implemented with an EM probe placed near the target LSI. Such sensing is particularly resistant to attacks performed very near or on the surface of cryptographic cores, which are usually assumed for microprobe-based EM attacks, such as in [10]. In addition, the countermeasure uses a dual-coil sensor architecture and an LUT-programming-based digital sensor calibration in order to thwart a variety of microprobe-based EM attacks.

The original concept and the key sensor circuit block validation were presented in our previous report [17]. This paper proposes a standard-cell-based semi-automatic design methodology using conventional circuit design tools. A demonstrator LSI chip fully integrating a complete set of an AES processor and the sensor is brand-new designed by the proposed systematic design methodology. The sensor is composed of sensor coils and a sensor core integrated into the cryptographic LSI. It can be designed at the circuit level rather than at the transistor level since all components of the sensor, even including the coils, are semi-automatically designed by standard EDA tools with a fully-digital standard cell library, which minimizes the design cost. The validity and performance of the sensor designed based on the proposed methodology are demonstrated through experiments using a prototype integrating a 128bit-key composite AES processor in a  $0.18\mu m$  CMOS process. We confirm that the prototype sensor successfully detects a variety of microprobe-based EM attacks with overheads of only 2% in area, 9% in power, and 0.2% in performance. Thus, the major contributions of the present paper are establishing a systematic design flow for the sensor using conventional circuit design tools, showing that the sensor can be developed at the circuit level, and demonstrating the validity and performance of the prototype sensor designed by using our design flow through a set of experiments for different attack scenarios.

The remainder of this paper is organized as follows. Section 2 introduces the concept of the countermeasure with the EM attack sensor. In Section 3, the semi-automatic design flow for the sensor is proposed. Section 4 shows the experimental results obtained using the prototype integrated into an AES processor

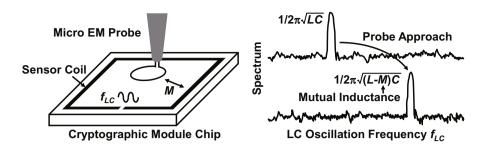

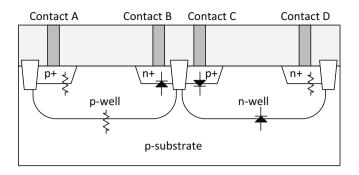

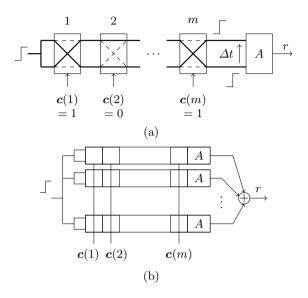

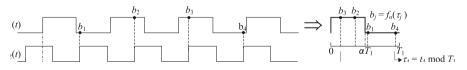

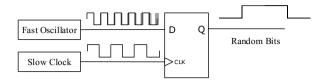

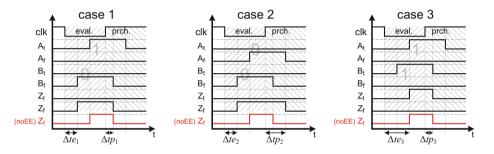

Fig. 1. Basic concept

and discusses its capabilities and limitations. Finally, Section 5 presents some concluding remarks.

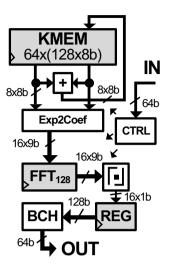

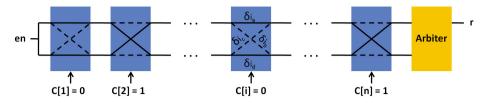

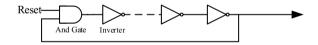

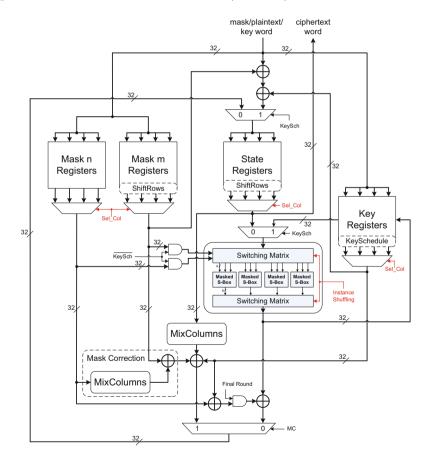

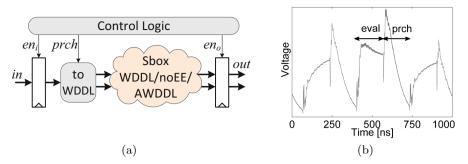

## 2 EM Attack Sensor

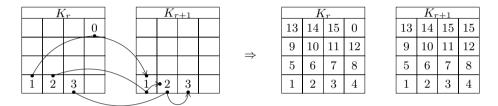

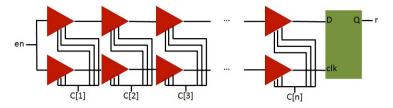

Figure 1 illustrates the basic concept of the EM attack sensor. When a probe (i.e., a looped conductor) is brought close to an LSI (i.e., another electric object), mutual inductance increases. This is a physical law that is unavoidable in magnetic field measurement. Assuming current flowing through a coil (i.e., an LC circuit), its frequency shifts due to the mutual inductance M. The original frequency  $f_{LC}$  and the shifted frequency  $\tilde{f}_{LC}$  are approximately given by

$$f_{LC} \approx \frac{1}{2\pi\sqrt{LC}},\tag{1}$$

$$\tilde{f}_{LC} \approx \frac{1}{2\pi\sqrt{(L-M)C}},\tag{2}$$

respectively. Thus, it is possible to detect the presence of a probe that has been placed inside a common LSI package by detecting the frequency shift induced in an LC circuit. Note that the corresponding variation in electric field is also detectable in the equivalent principle by capacitive coupling.

The single-coil sensing scheme in Fig. 1 is simple and straightforward, but it requires a frequency reference generated either inside or outside the LSI for detecting frequency shifts. However, any external clock signal, including a system clock, may be manipulated by the attacker, and therefore cannot be used as a reliable frequency reference. In addition, an on-chip frequency reference requires area- and power-hungry analog circuitry, such as a bandgap reference circuit. These drawbacks of the single-coil scheme are overcome by using a dual- or multi-coil scheme.

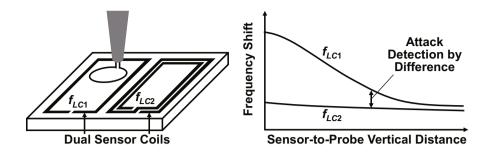

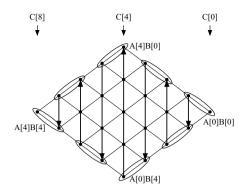

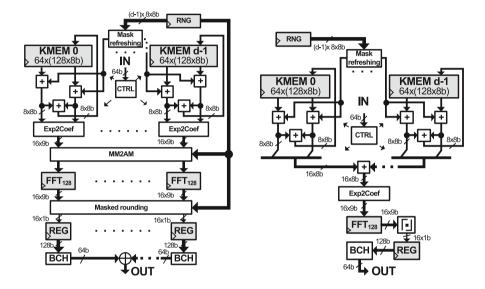

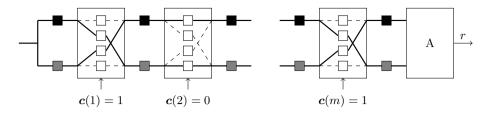

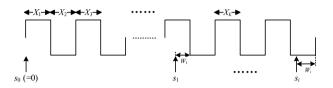

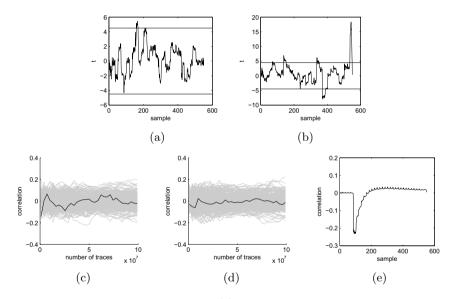

Fig. 2. Dual-coil sensor architecture

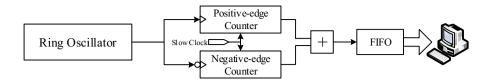

Figure 2 illustrates the concept of the dual-coil sensor architecture, where two coils are installed on the cryptographic core to be protected. Using two coils with different shape and number of turns, it is possible to detect an approaching probe by the difference of the oscillation frequencies of the two coils. This dual-coil sensor architecture avoids using any absolute frequency reference that is required in the single-coil scheme. The difference of frequencies is constant and remains detectable even if a frequency reference, such as a system clock, is tampered with. In addition, the difference of the frequencies of the two coils enables probe detection in a variety of probing scenarios (e.g., dual probing and cross-coil probing).

To enhance the attack detection accuracy, PVT (process, voltage, and temperature) variation in  $f_{LC}$  should be suppressed. A ring oscillator can be utilized as a PVT monitor for calibrating  $f_{LC}$  [17]. The abovementioned LC oscillators do not employ any varactor capacitance as they have a positive temperature coefficient ( $k_{TC} > 0$ ). Instead, small MOS capacitors with low  $k_{TC}$  are connected to the oscillator only for calibration. The  $f_{LC}$  variation in this design is inversely proportional to the transconductance of a  $g_m$  cell in the LC oscillator. As a result, the LC and the ring oscillators have a monotonic inverse dependence on PVT, and thus  $f_{LC}$  can be digitally calibrated in one step with only two counters and a small lookup table (LUT) used for converting the difference of clock counts into capacitance values (i.e., the number of capacitors).

In the calibration, first we switch on both the LC and ring oscillators, after which we check the outputs of the counters attached to the oscillators, and finally increase or decrease the number of capacitors in accordance with the difference of counts. Here, a relative frequency difference is utilized, similarly to the attack detection concept. Such digital calibration setup is implemented in a compact and low-power manner since it does not require any analog circuitry for frequency reference. In principle, this calibration only handles  $f_{LC}$  shift due to PVT variation, and the shift  $\Delta f$  due to an approaching probe always remains after the calibration. Even if the probe is placed close to the chip before the power supply is switching on, the probe can be detected immediately after wake-up.

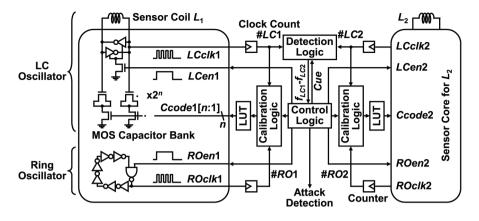

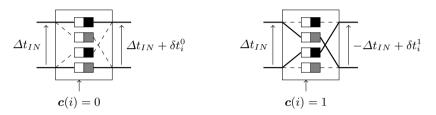

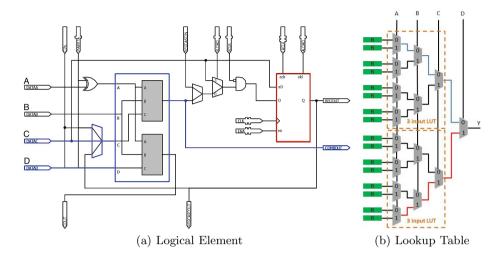

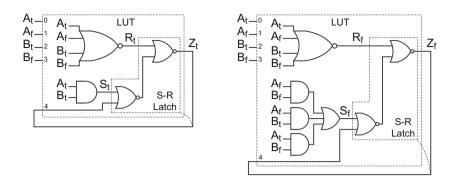

Fig. 3. Circuit diagram

## 3 Design Methodology

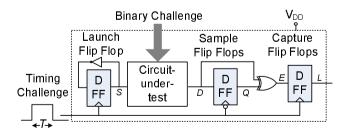

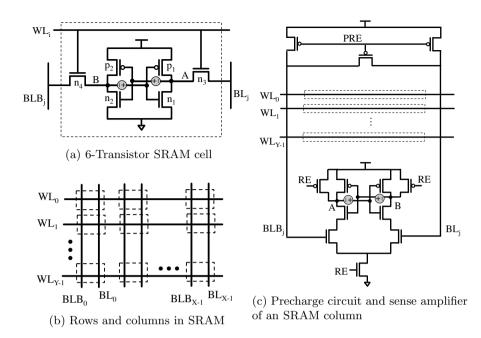

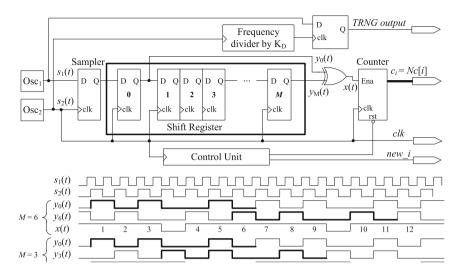

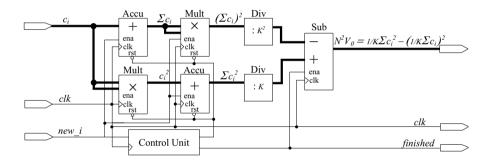

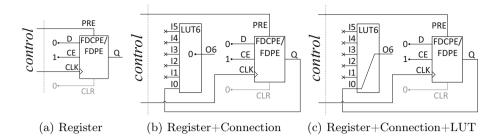

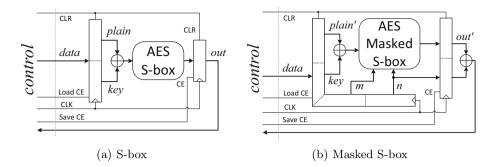

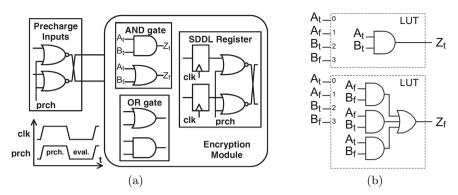

Figure 3 depicts a circuit diagram of the sensor core circuit. It consists of LC oscillators connected to sensor coils L1 and L2, ring oscillators, a detection logic circuit, two calibration logic circuits, and a control logic circuit. For the best compatibility with the standard digital design flow, standard digital cells are assigned to all the circuit components. The  $g_m$  cell of the LC oscillator can be realized by using two gated CMOS inverter and the MOS capacitor bank is composed of  $2^n$  sets of unit MOS capacitors with switch controlled by digital binary code Ccode. All other circuit components are of course realized by using the standard digital cell library. The sensor core performs detection of frequency difference, calibration of LC oscillator frequencies, and timing control of the sensor operation.

The detection logic circuit calculates the difference of LC oscillation frequencies by subtracting the clock counts of LCclk1 and LCclk2, which indicate the digitized values of the oscillation frequencies  $f_{LC1}$  and  $f_{LC2}$ , respectively.

The two calibration logic circuits calculate the difference of clock counts of LCclk1 (LCclk2) and ROclk1 (ROclk2) obtained from the LC and ring oscillators, respectively. Here, note that we know both the frequencies of LC and ring oscillators in advance under typical PVT conditions. The difference is converted into the capacitance value Ccode1 (Ccode2) based on the lookup table (LUT) connected to the calibration logic circuit. The Ccode1 (Ccode2) switches the number of capacitors connected to the LC oscillator and consequently calibrates the LC oscillator frequency.

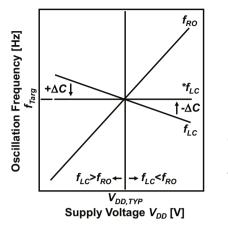

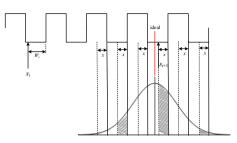

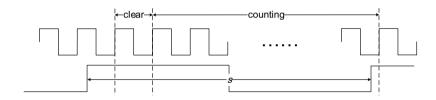

Figure 4 illustrates the process of calibration, where the LC and ring oscillators have a monotonic inverse dependence on the supply voltage and  $\Delta C$ indicates the capacitance determined by the difference of LC and ring oscillation frequencies. Although Figure 4 illustrates a case when the supply voltage varies, this calibration method is applicable to variations in process and temperature.

$$f_{LC} = \frac{1}{2\pi\sqrt{L(C \pm \Delta C)}}$$

\* $f_{LC}$ : Calibrated LC Oscillation Frequency  $f_{Targ}$ : Target Frequency after Calibration  $\Delta C$ : Capacitance Change for Calibration (Decided by  $|f_{RO} f_{LC}|$ )

Fig. 4. Calibration scheme

In order to suppress the  $f_{LC}$  variation within  $\pm 1\%$ , a 10-bit Ccode resolution is high enough. The LUT for this calibration is essentially a 10-bit subtracter whose gate count is only around 0.2k gates.

The control logic circuit provides the timings of detection and calibration operations, which are determined depending on the cryptographic operation to be protected. Calibration is performed once before the detection operation, which is performed in a timely fashion before and during cryptographic operation. If a frequency difference is detected, a signal to that effect is generated by the control logic circuit. The cryptographic operation is then changed in accordance with the detection signal.

As described above, all components of the sensor core are implemented as fully digital circuits available as standard cells (including transistor switches and capacitance cells), and therefore the sensor can be scaled together with the cryptographic LSI to be protected. The coil size is also scalable due to transistor performance improvement in device scaling. The sensor monitors for probe approach intermittently and periodically, which saves power and minimizes the performance overhead. In addition, the oscillators do not interfere with the cryptographic core since the sensor is usually activated while the cryptographic core is idle.

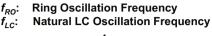

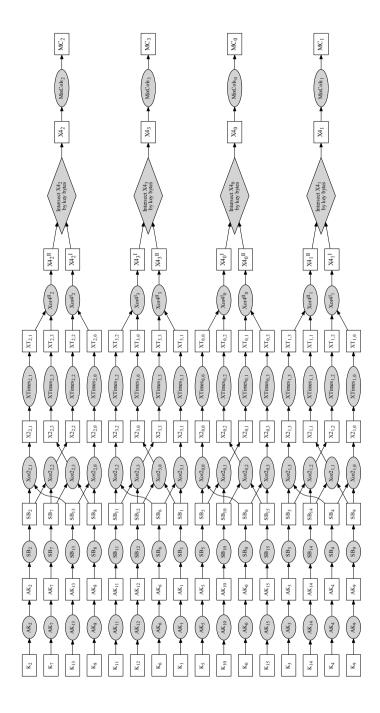

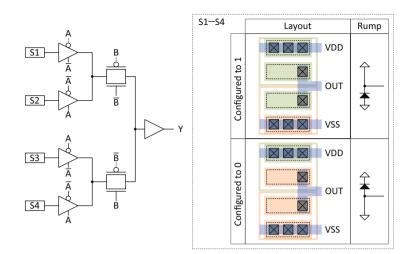

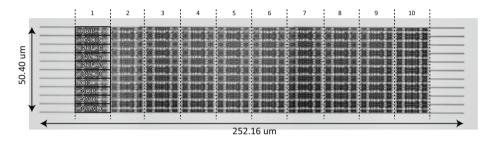

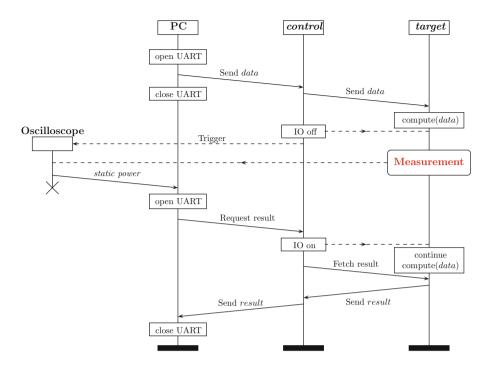

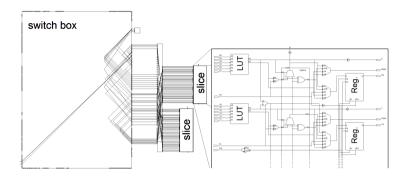

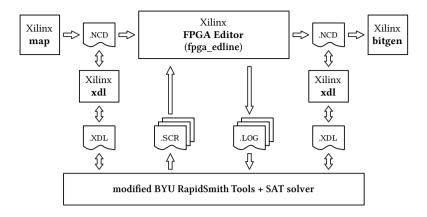

Figure 5 shows the proposed design methodology for the above sensor with conventional circuit design tools. The cryptographic and sensor cores are first described by a conventional hardware description language (e.g., Verilog-HDL) at the logic design step and synthesized by a logic synthesizer at the logic synthesis step. Logic synthesis is performed for each functional block since it is assumed that all functional blocks handling sensitive data are protected by sensor coils.

After the logic synthesis step, the sensor coils are designed in accordance with the above design. At the netlist generation step, a netlist of the sensor cores is generated for a SPICE simulation of the sensor core. In parallel, the external 8

Fig. 5. Design flow

shape of the cryptographic and sensor cores is fixed at the floor planning step, which determines the overall coil size (i.e., length and width).

With the coil length and width fixed, at the coil design step, we determine the number of turns, which determines the oscillation frequency. The gap between the wires is also adjusted to fine-tune the oscillation frequency, and the wire width is adjusted to ensure stable oscillation. A wide wire reduces loss in the coil and hence meets the oscillation requirements, at the expense of using more resources to make the wire. Then, we perform a SPICE simulation with the coil parameters for a range of possible PVT conditions and determine the required capacitor bank structure (i.e., the range and step size of capacitance values). Unit capacitors with some margin are pre-arranged at the placement step, and then the actual bank structure is constructed at the following routing step by hard-wire programming between the capacitor bank and the LUT to convert the frequency difference to capacitance value for sensor calibration.

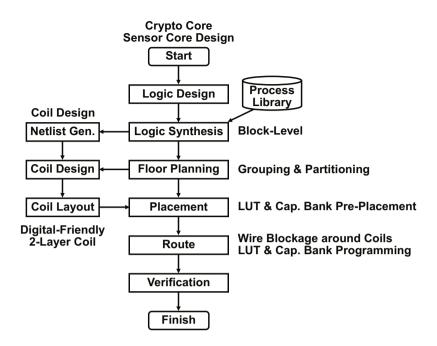

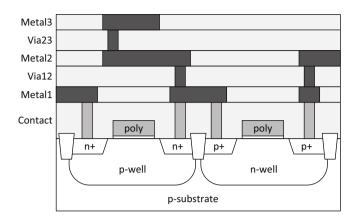

At the coil layout step, we design the coil layout according to the above parameters. Note here that we can utilize digital layout grids to provide the width and spacing of wires. A digital-friendly 2-layer coil layout style [18] is employing where coil is drawn by two different metal layers for orthogonal edges (Fig. 6). The coil can be hidden in the sea of logic interconnections as it only consumes several tens of logic interconnection tracks. Since a high Q factor is not required, it is also not necessary to have a thick upper layer of metal for the coil since phase noise (jitter) in the LC oscillator has no impact on detection

Fig. 6. Coil layout: (a) conventional one-layer coil, and (b) orthogonal two-layer coil

accuracy. Therefore, the coil can be fabricated by a standard digital process without any analog/RF options. Unlike analog LC oscillator such as for RF clock synthesizers, careful dedicated analog design is not necessary for this sensor coil and oscillator design, further lowering the design cost.

Based on the coil layout, at the placement and routing step, we place and route the components of the cryptographic and sensor cores, including the capacitor bank and LUT. The capacitor bank has n capacitors of different sizes, and therefore encodes  $2^n - 1$  capacitance values for an n-bit input. Finally, we can verify the overall functionality with a digital verification tool at the verification step since the input and output of the sensor core are digital.

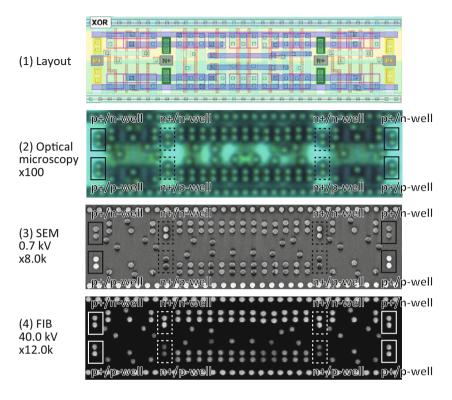

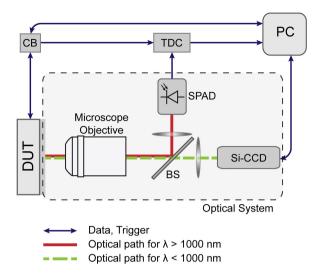

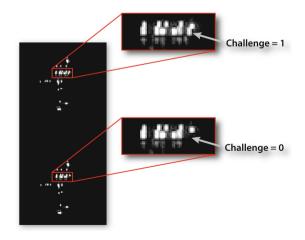

## 4 Validity Verification

The validity and performance of the proposed sensor were demonstrated through experiments with a newly fabricated chip designed on the basis of the proposed methodology. We assume here four attack scenarios with a single microprobe approaching during the sensing period, a larger micro probe approaching during the sensing period, a single micro probe approaching while the supply voltage was being changed, and a single micro probe approaching before the sensing period (i.e., during the sleep period). The first scenario assumed a conventional microprobe-based EM attack, such as that described in [8] and [10], where attackers move a microprobe close to the core surface while the sensor is working.

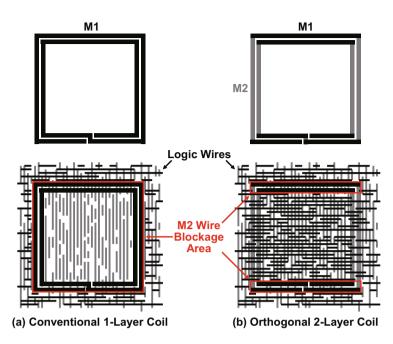

Fig. 7. Die photograph and measurement setup

The second scenario assumed an attempt to avoid detection by a larger probe crossing the two coils. This scenario is equivalent to EMA with two micro probes close to the two coils at the same time. The third scenario assumed that the attacker manipulate the PVT conditions to cheat the sensor. Finally, the fourth scenario assumed that the attacker can place a micro probe on the core surface in advance before the cryptographic and sensor cores are switched on, manipulating the PVT conditions.

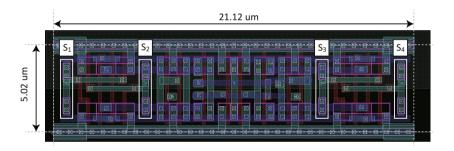

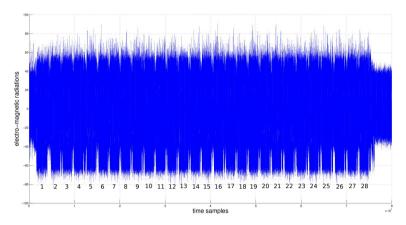

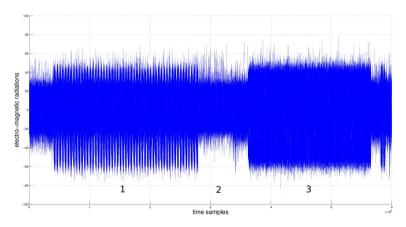

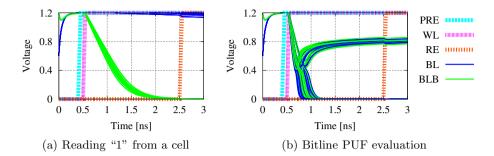

The proposed sensor was implemented in a TSMC  $0.18\mu$ m CMOS process by commercial CAD tools. More precisely, we used Design Compiler (G-2012.06-SP3), IC Compiler (vH-2013.03-SP2), and Virtuoso (6.1.4) for the logic synthesis, the P&R, and the coil design, respectively. Figure 7 shows a die photograph and the measurement setup. Two coils (a 4-turn coil (L1) and a 3-turn coil (L2)) were placed above an AES processor. The L1 (L2) coil had the resistance of 76 $\Omega$ (55 $\Omega$ ), the capacitance of 68fF (64fF), and the inductance of 13.2nH (8.5nH) according to the EM field simulation with an equivalent circuit model. The AES processor was based on a common loop architecture operating at one round per clock cycle [19]. The test chip was mounted on a side-channel attack standard evaluation board (SASEBO R-II) [20]. A micro EM probe was fixed on a manipulator, and its position was controlled manually by monitoring through a microscope. We conducted successful microprobe-based EMA using EM waveforms observed in the experimental setup, where the EM signal from the probe was amplified by a 100 W +40 dB power amplifier.

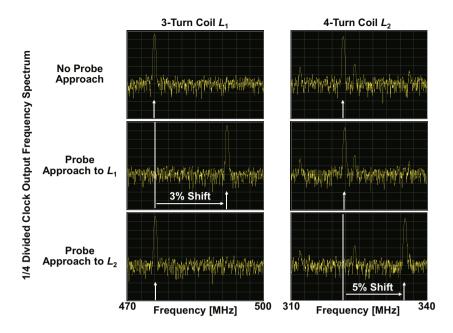

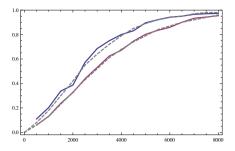

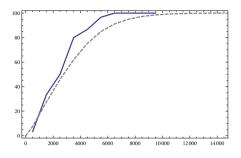

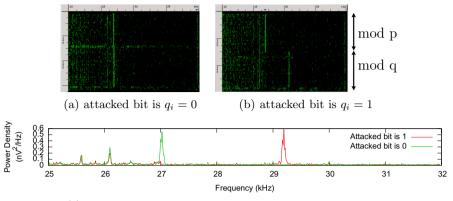

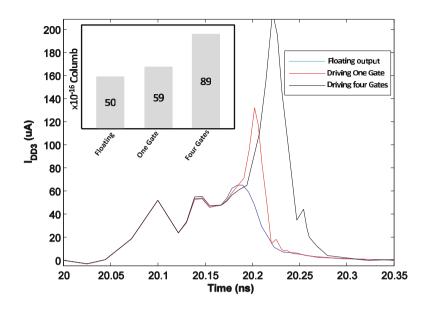

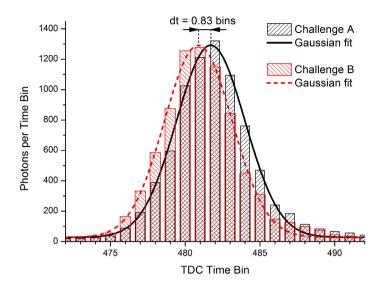

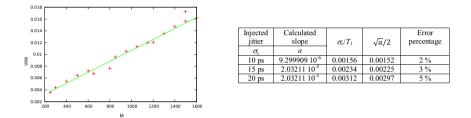

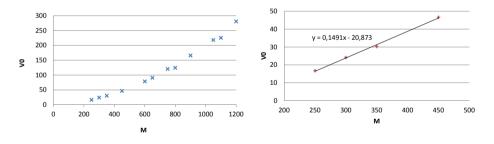

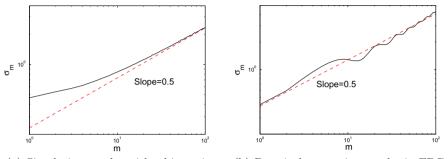

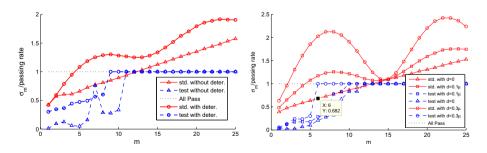

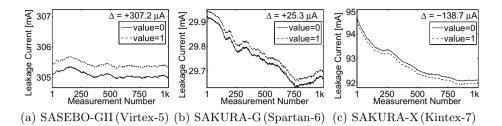

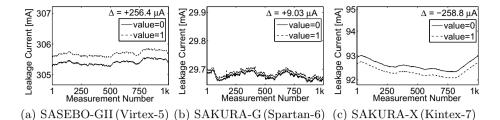

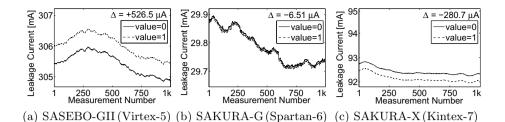

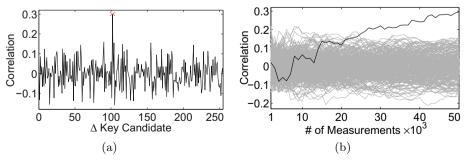

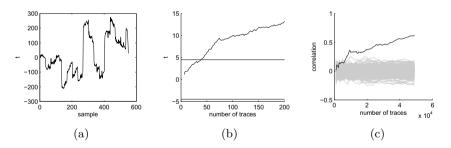

Figure 8 shows the frequency spectra of L1 and L2 in the presence and absence of a micro probe. The oscillation frequency of each coil was clearly shifted by the probe, even at a distance of about  $100\mu$ m. The result indicates that

Fig. 8. Frequency shift caused by an approaching probe

microprobe-based EM attacks such as those assumed in the first scenario can be easily detected by the sensor.

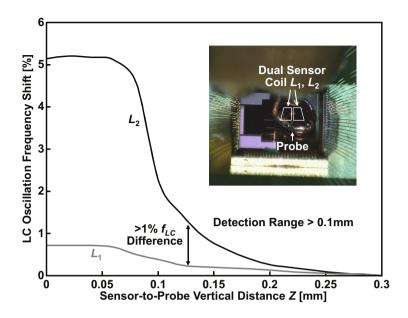

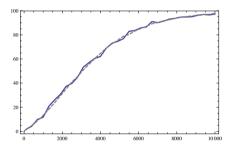

Figure 9 shows the difference of the frequency shifts of L1 and L2 for different distances between the coils and the probe. The shift ratio of L1 was clearly different from that of L2 when the same probe was used. This suggests that the second scenario is also thwarted by our dual-coil detection scheme. Even if the attacker can observe the magnitude of the frequency shifts, they would still have substantial difficulty in matching the shifts, which are determined by many coil parameters, while performing high-density EM measurements. This result indicates that EM attacks with two micro probes are also detectable.

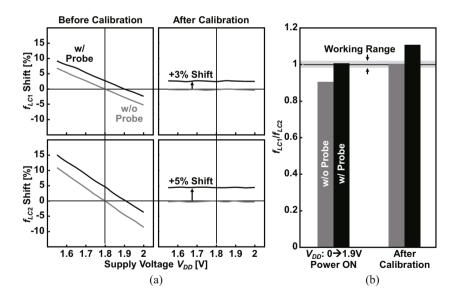

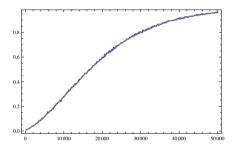

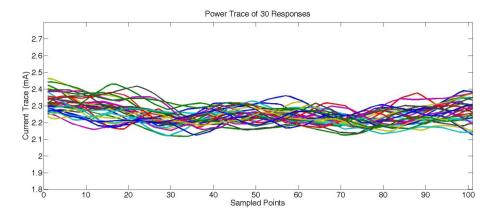

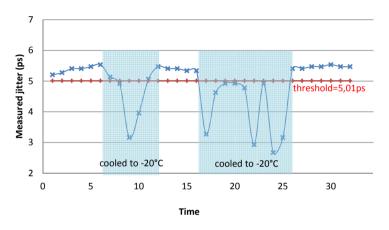

Figure 10 (a) presents the frequency shift dependence on the supply voltage VDD, where the left and right hands of the figure are the amount of frequency shifts before and after the calibration, respectively. The proposed one-step digital calibration suppresses the  $f_{LC}$  variation to within  $\pm 1\%$  over the temperature range of 0-60 °C at a VDD voltage of 1.6-2.0 V which corresponds to a variation greater than  $\pm 10\%$  from the nominal VDD voltage of 1.8 V. This result shows that the proposed sensor is robust against PVT variation since the same calibration method is applicable for a range of possible PVT conditions.

Figure 10 (a) also shows that the sensor can thwart the fourth scenario. The frequency shift due to the approaching probe remains after calibration. The result indicates that even if the probe is brought close to the cryptographic core before its power supply is switched on, the probe can be detected immediately after wake-up. Figure 10 (b) presents the result for a sophisticated fourth

Fig. 9. Difference of frequency shifts of L1 and L2 for different distances

Fig. 10. Frequency shifts before and after calibration

scenario, where the attacker can manipulate the supply voltage and suppress  $f_{LC}$  variation to within the working range (±1%) with a micro probe close to the core surface just after the power is switched on. It should be noted that such

13

|                   | AES Core             | Sensor               | Total (Sensor Overhead)       |

|-------------------|----------------------|----------------------|-------------------------------|

| 2NAND Gate Count  | 24.3k                | 0.3k                 | 24.6k (+1.2%)                 |

| Wire Resource     | 0.40 mm <sup>2</sup> | $0.05 \mathrm{mm}^2$ | $0.45 \text{mm}^2 \ (+11\%)$  |

| Layout Area       | $0.48 \mathrm{mm}^2$ | $0.01 \mathrm{mm}^2$ | $0.49 \mathrm{mm}^2 \ (+2\%)$ |

| Performance       | $125\mu s/Enc$       | $0.3 \mu s/Sense$    | $125.3\mu s (-0.2\%)$         |

| Power Consumption | $0.23 \mathrm{mW}$   | $0.02 \mathrm{mW}$   | $0.25 \mathrm{mW} \ (+9\%)$   |

Table 1. Overheads caused by sensor

cheating was also thwarted by the calibration since the  $f_{LC}$  variation is always corrected to within  $\pm 1\%$  in the absence of a probe.

Table 1 summarizes the overheads caused by the sensor hardware. The time for a single detection operation (including calibration and sense operations) can be reduced to <1% of the time for one AES encryption operation, including data I/O. Note that the application considered here is a simple device with a few IO pins, such as smartcard, which can be mainly targeted by microprobebased EMA. Such device usually equips serial IO and outputs the data at each time. This intermittent sensor operation at <1% duty cycle significantly reduces the power and performance overheads of the sensor. The power consumption was estimated from a calibration-and-sense operation before an AES encryption operation. With overheads of only 2% in area and 9% in power, the proposed sensor can be used as a countermeasure against microprobe-based EM attacks, filling a large security hole not covered by conventional countermeasures.

## 5 Discussion

The experimental results show that the proposed sensor is effective against micro-probe-based EM attacks which cannot be prevented by the conventional algorithmic- and circuit-level countermeasures. EM fault-injection attacks using a micro needle probe, such as that in [9], are also detected by the same principle. Using middle layers to draw sensor coils could also prevent attacks from the backside of the LSI since the magnetic sensing can work through interconnect, transistor and substrate layers. Thus, the proposed countermeasure can detect EM analysis and fault-injection attacks performed close to or on the LSI (front and back) surface in a robust manner.

The proposed sensor would also be invulnerable to frequency injection attacks. First, attackers must measure the original frequency very close to the coil surface but cannot measure it without disturbing the original one. Even if the frequency is known, a significant EM injection power is required to lock an oscillator since each coil is oscillating in a full swing manner. Such powerful EM injection must affect another oscillator. Note again that the oscillation frequencies are different for each other. If both oscillators are locked to the same frequency, the sensor detects it immediately. An attacker might attempt to attach a frequency-injection probe directly to an embedded coil, but it is hard to do it without affecting other wires. One possible attack on the proposed setup would be to eliminate the difference between oscillation frequencies observed by the sensor by using two probes or similar alternatives. However, performing such a sophisticated attack is extremely difficult, even if the attacker can observe the frequency shifts shown in the above experiments. In addition, it is difficult to identify and disable the sensor prior to the attack since the coils and the sensor core are embedded in the sea of logic gates and wires. Reverse engineering to removing the sensor would also be a rather challenging task when the cryptographic core operation is linked with the sensor operation.

The detectable distance between the probe and the sensor is limited to a maximum of 0.1 mm in the experimental setup. The limited maximum detection distance means that conventional EMAs on the chip package such as DEMA and CEMA are still possible, even if the proposed sensor is installed over the cryptographic core. The extension of the maximum detection distance is an open issue that will be addressed in future work. For example, we could extend the detection distance using larger coils. Extending the maximum distance may enable the sensor to detect chip unpacking as well. On the other hand, the proposed sensor can be combined with any other conventional countermeasures due to the low area and performance overheads. In practice, a combination of conventional countermeasures and the proposed technique would work well in a complementary manner.

The power and performance overheads are further reduced by the optimization of intermittent sensor operation. The sensor should operate continuously during the cryptographic operations for increased security. However, intermittent operation would be sufficient for many applications. For example, one-time calibration and sensing before continuous cryptographic operations might be practical. Designers and users can determine the operation timing according to the target application and intended use. The post-detection operations (e.g., termination or dummy operations) should also be optimized depending on the application. Such optimizations will also be examined in future work.

## 6 Conclusion

This paper presented the design methodology and validity verification of a new countermeasure against microprobe-based EM analysis and fault-injection attacks. The proposed countermeasure detects variations in the EM field caused by a micro EM probe approaching the cryptographic LSI, and therefore thwarts microprobe-based EMA that cannot be prevented by conventional algorithmicand circuit-level countermeasures. A dual-coil sensor architecture and an LUTprogramming-based digital sensor calibration can prevent such EM attacks in a variety of scenarios where one or more micro EM probes are used under different PVT conditions. All components of the sensor core are implemented in a fully digital circuit and therefore can be scaled together with the cryptographic LSI to be protected.

The proposed systematic design flow for the sensor is based on standard digital circuit design tools. All the sensor circuit components, including the sensor coils,

was semi-automatically designed by the synthesis and placement software once the coil parameters were fixed. The validity and performance of the sensor were demonstrated through experiments using a prototype integrated into an AES processor. The results show that our sensor successfully detects microscale EM probes approaching the AES processor for all assumed attack scenarios.

The sensor was designed based on the proposed design flow and integrated with overheads of only 2% in area, 9% in power, and 0.2% in performance, which are much lower than those of alternative active shield techniques. Such low overheads make it possible to implement the proposed technique together with conventional countermeasures developed for other types of attacks. Although the proposed countermeasure cannot thwart all types of EM attacks, it can significantly reduce the complexity and cost associated with conventional countermeasures against microprobe-based EMA. One direction of future work will be to find the most effective combination of the proposed and conventional countermeasures.

#### References

- Kocher, P.C.: Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems. In: Koblitz, N. (ed.) CRYPTO 1996. LNCS, vol. 1109, pp. 104–113. Springer, Heidelberg (1996)

- Kocher, P.C., Jaffe, J., Jun, B.: Differential power analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999)

- Mangard, S., Oswald, E., Popp, T.: Power Analysis Attacks Revealing the Secrets of Smart Cards. Springer (2007)

- Gandolfi, K., Mourtel, C., Olivier, F.: Electromagnetic analysis: Concrete results. In: Koç, Ç.K., Naccache, D., Paar, C. (eds.) CHES 2001. LNCS, vol. 2162, pp. 251–261. Springer, Heidelberg (2001)

- Quisquater, J., Samyde, D.: Electromagnetic analysis (EMA): Measures and counter-measures for smart cards. In: Attali, S., Jensen, T. (eds.) E-smart 2001. LNCS, vol. 2140, pp. 200–210. Springer, Heidelberg (2001)

- Agrawal, D., Archambeault, B., Rao, R., Rohatgi, P.: The EM side-channel(s). In: Kaliski Jr., B.S., Koç, Ç.K., Paar, C. (eds.) CHES 2002. LNCS, vol. 2523, pp. 29–45. Springer, Heidelberg (2003)

- Réal, D., Valette, F., Drissi, M.: Enhancing Correlation Electromagnetic Attack Using Planar Near-Field Cartography. In: DATE 2009, pp. 628–633 (2009)

- Peeters, E., Standaert, X., Quisquater, J.: Power and electromagnetic analysis: Improved model, consequences and comparisons. Integration, the VLSI Journal 40(1), 52–60 (2007)

- Moro, N., Dehbaoui, A., Heydemann, K., Robisson, B., Encrenaz, E.: Electromagnetic fault injection: towards a fault model on a 32-bit microcontroller. In: FDTC 2013, pp. 77–88 (August 2013)

- Sugawara, T., Suzuki, D., Saeki, M., Shiozaki, M., Fujino, T.: On Measurable Side-Channel Leaks Inside ASIC Design Primitives. In: Bertoni, G., Coron, J.-S. (eds.) CHES 2013. LNCS, vol. 8086, pp. 159–178. Springer, Heidelberg (2013)

- Tiri, K., Hwang, D., Hodjat, A., Lai, B.-C., Yang, S., Schaumont, P., Verbauwhede, I.: Prototype IC with WDDL and differential routing – DPA resistance assessment. In: Rao, J.R., Sunar, B. (eds.) CHES 2005. LNCS, vol. 3659, pp. 354–365. Springer, Heidelberg (2005)

- Suzuki, D., Saeki, M., Ichikawa, T.: Random Switching Logic: A Countermeasure against DPA based on Transition Probability, IACR Cryptology ePrint Archive 2004: 346 (2004)

- Van Geloven, J.A.J., Wolters, R.A.M., Verhaegh, N.: Sensing circuit for devices with protective coating, United States Patent no. US 2010/0090714 Al (2010)

- Beit-Grogger, A., Riegebauer, J.: Integrated circuit having an active shield. United States Patent no. 6,962,294 (2005)

- Briais, S., Cioranesco, J.-M., Danger, J.-L., Guilley, S., Jourdan, J.-H., Milchior, A., Naccache, D., Porteboeuf, T.: Random Active Shield. In: FDTC 2012, pp. 103–113 (September 2012)

- Briais, S., et al.: 3D Hardware Canaries. In: Prouff, E., Schaumont, P. (eds.) CHES 2012. LNCS, vol. 7428, pp. 1–22. Springer, Heidelberg (2012)

- Miura, N., Fujimoto, D., Tanaka, D., Hayashi, Y., Homma, N., Aoki, T., Nagata, M.: A Local EM-Analysis Attack Resistant Cryptographic Engine with Fully-Digital Oscillator-Based Tamper-Access Sensor. In: 2014 Symposium on VLSI Circuits, Dig. Tech. Papers, pp. 172–173 (June 2014)

- Saito, M., Kusaga, K., Takeya, T., Miura, N., Kuroda, T.: An Extended XY Coil for Noise Reduction in Inductive-coupling Link. A-SSCC Dig. Tech. Papers, pp. 305–308 (November 2009)

- Cryptographic Hardware Project (August 2007), http://www.aoki.ecei.tohoku.ac.jp/crypto/

- 20. Side-channel Attack Standard Evaluation Board, SASEBO-RII (2012), http://www.risec.aist.go.jp/project/sasebo/

# A New Framework for Constraint-Based Probabilistic Template Side Channel Attacks

Yossef Oren<sup>1</sup>, Ofir Weisse<sup>2</sup>, and Avishai Wool<sup>3</sup>

<sup>1</sup> Network Security Lab, Columbia University, USA

<sup>2</sup> School of Computer Science, Tel-Aviv University, Israel

<sup>3</sup> School of Electrical Engineering, Tel-Aviv University, Israel vos@cs.columbia.edu, ofirweisse@gmail.com, vash@eng.tau.ac.il

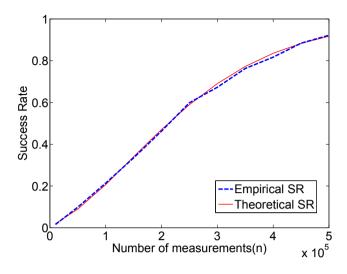

**Abstract.** The use of constraint solvers, such as SAT- or Pseudo-Boolean-solvers, allows the extraction of the secret key from one or two side-channel traces. However, to use such a solver the cipher must be represented at bit-level. For byte-oriented ciphers this produces very large and unwieldy instances, leading to unpredictable, and often very long, run times. In this paper we describe a specialized byte-oriented constraint solver for side channel cryptanalysis. The user only needs to supply code snippets for the native operations of the cipher, arranged in a flow graph that models the dependence between the side channel leaks. Our framework uses a soft decision mechanism which overcomes realistic measurement noise and decoder classification errors, through a novel method for reconciling multiple probability distributions. On the DPA v4 contest dataset our framework is able to extract the correct key from one or two power traces in under 9 seconds with a success rate of over 79%.

Keywords: Constraint solvers, power analysis, template attacks.

## 1 Introduction

In a constraint-based side-channel attack, the attacker is provided with a device under test (DUT) which performs a cryptographic operation (e.g., encryption). While performing this operation the device emits a data dependent side-channel leakage such as power consumption trace. As a result of the data dependence, a certain number of leaks are modulated into the trace together with some noise. In order to recover the secret key from a power trace the attacker performs the following steps:

*Profiling*: The DUT is analyzed in order to identify the position of the leaking operations in the traces, for instance by using classical side-channel attacks like CPA [4]. Then a decoding process is devised, that maps between a single power trace and a vector of leaks. A common output of the decoder is the Hamming weight of the processed data as in [22], but many other decoders are possible. An effective profiling method is a template attack, which was introduced in [5]. Profiling is an offline activity.

*Decoding*: After the profiling phase, the attacker is provided with a small number of power traces (typically, a single trace). The decoding process is applied

L. Batina and M. Robshaw (Eds.): CHES 2014, LNCS 8731, pp. 17-34, 2014.

<sup>©</sup> International Association for Cryptologic Research 2014

to the power trace, and a vector of leaks is recovered. This vector of leaks may contain some errors, e.g., due to the effect of noise.

Solving: The leak vector, together with a description of the algorithm implemented in the DUT, and additional auxiliary information, is converted to a representation that is suitable to a constraint solver: e.g., a SAT-solver [21,22,28] or a Pseudo-Boolean solver [17,18]. The solver solves the problem instance, outputting the best candidates satisfying the constraints. However, previously used solvers require a bit-level representation which creates several challenges. In this paper we suggest a new solver which uses a byte-level representation.

**Related Work.** Side channel cryptanalysis was first suggested in [12] (cf. [13]). Template attacks were introduced in [5] and further explored in papers such as [24,20,7]. Algebraic side-channel attacks were introduced by Renauld et al. in [21,22], and first applied to the block ciphers PRESENT [3] and AES [15]. These works showed how keys can be recovered from a single measurement trace of these algorithms implemented in an 8-bit microcontroller, provided that the attacker can identify the Hamming weights of several intermediate computations during the encryption process. Already in these papers, it was observed that noise was the main limiting factor for algebraic attacks. To mitigate this issue, a heuristic solution was introduced in [22], and further elaborated in [28,14]. The main idea was to adapt the leakage model in order to trade some loss of information for more robustness, for example by grouping hard-to-distinguish Hamming weight values together into sets. An alternative proposal [17] suggested to include the imprecise Hamming weights in the equation set, and to deal with these imprecisions via the solver.

Despite their success, using generic SAT solvers or Pseudo-Boolean solvers still leaves room for improvement. The difficulties stem from the fact that in order to use them, the cipher representation has to be reduced to the bit-level. For byte-oriented ciphers this produces very large and complex instances, that are challenging to construct and debug. [16] notes that an AES equations instance may reach a size of 2.3 MB, depending on the methodology used to construct the equations. However, the most problematic aspect of bit-level solvers is their unpredictable, and often very long, run times. In [18] the authors report that run times vary over an order of magnitude between 8.2 hours to more than 143 hours on instances belonging to the same data set. The solver behavior is very sensitive to technical representation issues, and is controlled by a myriad of configuration parameters that are unrelated to the cryptographic task. Algebraic side-channel attacks which use local calculations were also considered in [26] and in [8].

**Contribution.** The focus of this work is a new *constraint solver*. Our solver embeds a model of the encryption process, accepts the known plain-text, and the output of the *decoder*, and outputs the highest probability keys with an estimation of their likelihood. However, unlike the algebraic attacks of [22] and [18], our constraint solver is not a general purpose Pseudo-Boolean or SAT-solver.

We wrote a special solver that is targeted at the unique types of constraints that occur in a side channel cryptanalysis of byte-oriented ciphers. Our solver is fundamentally probabilistic. It tracks the likelihoods of values in the secret key bytes, and updates them step by step through the encryption process, utilizing the probability distributions output by the decoder. A key ingredient in our framework is a novel method for reconciling multiple probability distributions for the same variable.

Applying our framework to a byte-oriented cipher with available side-channel information is quite natural and does not involve complex representation conversions into bit-level equations: the user needs to supply code snippets for the native byte-level operations of the cipher, arranged in a flow graph that embeds the functional dependence between the side channel leaks. Our framework uses a soft decision mechanism which overcomes realistic measurement noise and decoder classification errors.

As in previous solver-based attacks, our framework requires a *decoder*. The decoder accepts a single power trace, and outputs estimates of multiple intermediate values that are computed during the encryption and leaked by the sidechannel. An estimate of a leaked value X in our framework is not a single "hard decision" value. Rather, as in [18], it is a probability distribution over the possible values of X. The decoder is usually constructed as a template decoder [5]. As in [18] we do not assume a Hamming-weight model for the leaked values - the decoder may output any probability distribution over the leak values. Note further that we do not impose a particular noise model on the decoder - e.g., it is not required to output only a single Hamming-weight value (or set of k values, as done by [28] and [18]).

We tested our framework on the DPA v4 contest dataset [2]. On this dataset, our framework is able to extract the correct key from one or two power traces with predictable and very short run times. Our results show a success rate of over 79% using just two measurements and typical run times are under 9 seconds. The source code can be downloaded from [27].

**Organization.** In the next section we introduce the probabilistic tools used in our solver. In Section 3 we describe the construction of the solver's flow graph. In Section 4 we show how we applied our method to AES. Section 5 includes the performance evaluation we conducted using the DPAv4 traces, and we conclude with Section 6.

#### 2 Probabilistic Methodology

#### 2.1 The Conflation Operator

A central part of our framework is a novel method of reconciling probability distributions. The basic scenario is as follows. Suppose we are trying to measure an unknown quantity X via two experiments. The outcome of the first experiment  $E_1$  is a probability distribution  $P_{E_1}$  such that  $P_{E_1}(X = i)$  is the likelihood that X has value *i*. The second experiment  $E_2$  measures the value of X using a different method, providing a second distribution  $P_{E_2}$ . We now wish to reconcile the results of these two experiments into a combined distribution  $\hat{P}$ . Intuitively, we want  $\hat{P}$  to "strengthen" values on which  $E_1$  and  $E_2$  agree, and "weaken" values on which  $E_1$  and  $E_2$  differ. Thus, we want a probabilistic analogue to the logical "AND" operator. At one extreme, if  $P_{E_1}(X = i) = 0$  (the value *i* is impossible according to  $E_1$ ) then we want  $\hat{P}(X = i) = 0$ . At another extreme, if  $P_{E_2}(X = i) = \frac{1}{N}$  for all N possible values of X ( $E_2$  provides no information about X) then we want  $\hat{P} = P_{E_1}$ .

This general question was tackled by [9,10,11,6]. In particular, Hill [9] suggests a method called *conflation*, which is essentially the point-product of the distributions. In the case of two experiments  $E_1, E_2$  the conflated probability  $\hat{P} = \&(P_{E_1}, P_{E_2}) = (\hat{p}_1, ..., \hat{p}_N)$  is defined as

$$\hat{p}_i = \hat{P}(X=i) = \frac{1}{\gamma} \cdot P_{E_1}(X=i) \cdot P_{E_2}(X=i)$$

where  $\gamma$  is a normalization factor to ensure  $\sum_{i=1}^{N} \hat{p}_n = 1$ . And in general, if multiple distributions  $P^1, ..., P^T$  are given then the conflated distribution is the normalized point product of all T distributions:  $\hat{P} = \&(P^1, ..., P^T) = (\hat{p}_1, ..., \hat{p}_N)$ such that  $\hat{p}_i = \frac{1}{2} \prod_{t=1}^T p_t^t$

Hill [9] thoroughly analyzes the properties of the *conflation* operator. The paper shows that conflation is the unique probability distribution that minimizes the loss of Shannon Information. Further, conflation automatically gives more weight to more accurate experiments with smaller standard deviation. Finally, as desired, conflation with the uniform distribution is an identity transformation (i.e., it is indifferent to experiments with no information), and if  $P^t(X = i) = 0$  for some i then  $\hat{P}(X = i) = 0$  regardless of all other experiments. As we shall see, using conflation as the main probabilistic reconciliation method is extremely effective in our solver.

#### 2.2 Conflating Probabilities of Single-Input Computation

In a byte-oriented cipher, many steps are transformations operating on a single byte. E.g., an XOR of a key byte X and a (known) plaintext byte is such a transformation. Similarly an SBox operation takes a single input X and produces f(X). Suppose a template-based side channel oracle  $E_1$  exists, that returns a probability distribution  $P_{E_1}$  of the values of X, and a second oracle  $E_2$  returns a probability distribution  $P_{E_2}$  of the values of f(X). Assuming the transformation f(X) is deterministic and 1-1, then  $P_{E_1}(X = a)$  should agree with  $P_{E_2}(f(X) = f(a))$ . Thus, we have two experiments measuring the value of f(X): one is  $E_2$ , and the other is a permutation of the distribution  $E_1$ . Combining the experiment results via conflation gives us a more accurate distribution of f(X) - and, equivalently, of values of X. Therefore, the reconciled probability for a single-input computation is defined to be:

$$\hat{P}(X=a) = \frac{1}{\gamma} P_{E_1}(X=a) \cdot P_{E_2}(f(X)=f(a))$$

(1)

#### 2.3 Conflating Probabilities of Dual-Input Computations

Suppose we have a function f of two independent byte values that outputs a byte: f(X,Y) = Z. We have oracles providing the probability distributions  $P_X, P_Y$  and  $P_Z$  for X, Y, Z respectively, and we wish to reconcile them. We first calculate the distribution  $P_f$  of f(X,Y) based on  $P_X, P_Y$ : assuming X and Yare independent we get  $P_f(c) = P(f(X,Y) = c) = \sum_{k,l:f(k,l)=c} P_X(k) \cdot P_Y(l)$ . Now  $P_f$  and  $P_Z$  are distributions from two experiments estimating the same value Z, which we can conflate as before:  $\hat{P} = \&(P_f, P_Z)$  so  $\hat{P}(c) = P_f(c) \cdot P_Z(c) \cdot \frac{1}{\gamma}$  (for some normalization constant  $\gamma$ ). However, we want to assign the reconciled probabilities  $\hat{P}()$  to the inputs X and Y. Specifically, we want to split the probability  $\hat{P}(c)$  among the pairs (X = a, Y = b) for which f(a, b) = csuch that each pair will get its weighted share of  $\hat{P}(c)$ . Assume as before that c = f(a, b), then the weighted split is:

$$\hat{P}(X = a, Y = b) = \hat{P}(c) \cdot \frac{P_X(a) \cdot P_Y(b)}{\sum_{k,l:f(k,l)=c} P_X(k) \cdot P_Y(l)} = \hat{P}(c) \cdot \frac{P_X(a) \cdot P_Y(b)}{P_f(c)} = \frac{1}{\gamma} P_f(c) P_Z(c) \cdot \frac{P_X(a) \cdot P_Y(b)}{P_f(c)} = \frac{1}{\gamma} P_X(a) P_Y(b) P_Z(c)$$

(2)

Thus we arrive at the following reconciled probability for the pair X = a, Y = b:

$$\hat{P}(X = a, Y = b) = \frac{1}{\gamma} P_X(a) P_Y(b) P_Z(f(a, b))$$

(3)

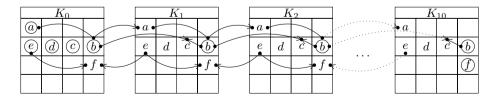

#### 3 Building Blocks

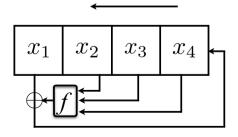

Our constraint model is a directed graph which describes the flow of information in the encryption process, as it affects the side channel leaks. The direction of the graph is from the unknown input bytes (the key in our case) to the output bytes (the ciphertext or intermediate values). Each part of the graph represents one of the following three constraint types: single-input constraint, dual-input constraint or data-redundancy constraint. There are two types of nodes in the graph:

- 1. Registry nodes used to store possible values of intermediate values and their corresponding probabilities.

- 2. Compute nodes used to connect registry nodes containing possible input values to registry nodes which should contain possible output values. Each compute node contains a code snippet implementing some step of the cipher.

#### 3.1 Single-Input Computation Constraint

Suppose one of the steps of the cipher is a single-input byte function f(X). Suppose we have two oracles,  $E_{in}$ ,  $E_{out}$  providing the probability distributions of X and f(X), respectively. Let  $\alpha_{b_n}^{in} = P_{E_{in}}(X = b_n)$ , and let  $\alpha_{f(b_n)}^{out} = P_{E_{out}}(f(X) = f(b_n))$ . These are the estimated probabilities of the input and output values given by the side channel information.

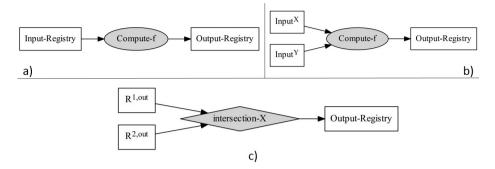

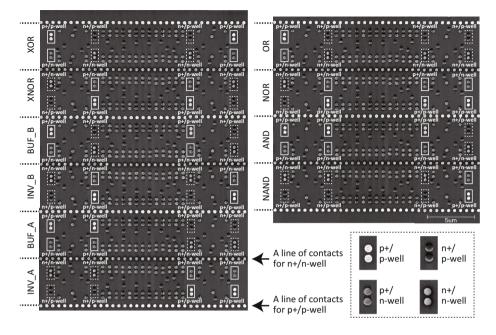

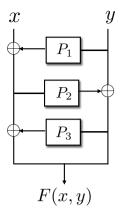

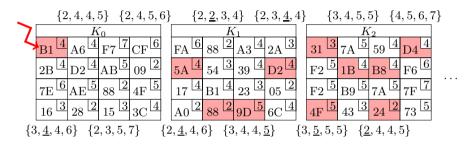

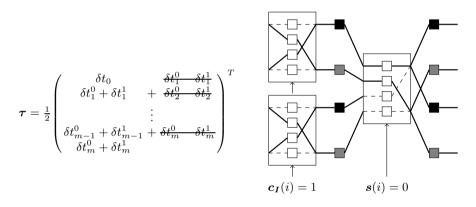

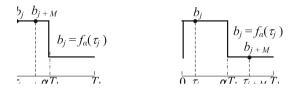

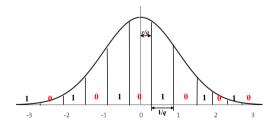

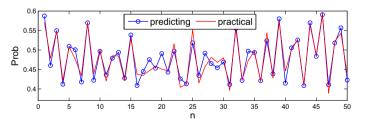

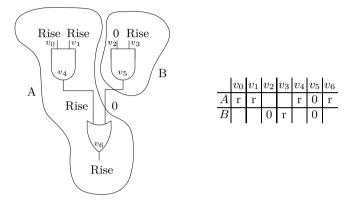

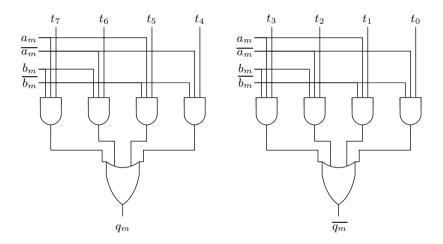

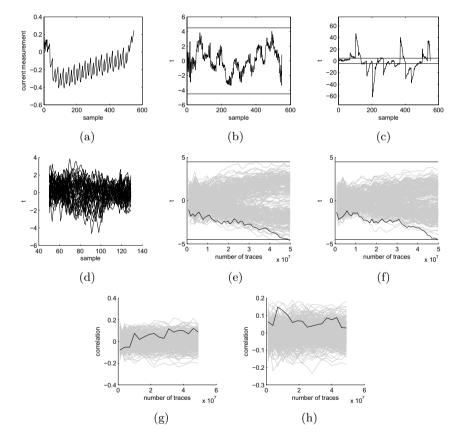

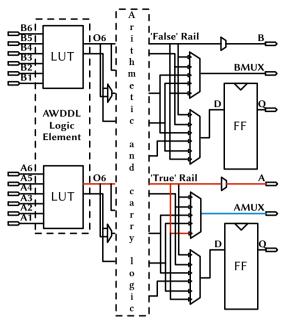

**Fig. 1.** Illustration of three types of constraints: a) single-input constraint, b) dual-input constraint, c) data-redundancy constraint

For a single input computation we define two registries: the *Input-Registry* contains the values  $\{(b_n, \alpha_{b_n}^{in})\}$ , and the *Output-Registry* contains the post-computation probabilities  $\{(v_n, \alpha_{v_n})\}$  s.t  $P(f(X) = v_n) = \alpha_{v_n}^{out}$ .

We connect the input registry to the output registry via the *Compute-f* node (see Figure 1a), which contains a code snippet. The *Compute-f* node receives the tuples  $\{(b_n, \alpha_{b_n}^{in})\}$  from the *Input-Registry*, computes the function f for each tuple, and for every value  $b_n$  outputs the tuple  $(b_n, \alpha_{b_n}^{in}, f(b_n))$  to the *Output Registry*. Upon receiving the results from the compute function, the *Output*-*Registry* conflates  $\alpha^{in}, \alpha^{out}$  as in Section 2.2:  $\hat{\alpha}_n = \frac{1}{\gamma} P(X = b_n) \cdot P(f(X) = f(b_n)) = \alpha_{b_n}^{in} \cdot \alpha_{f(b_n)}^{out}$ . After the computation is done the *Output-Registry* contains tuples of the form  $(b_n, f(b_n), \hat{\alpha}_n)$ .

#### 3.2 Dual-Input Computation Constraint

Suppose a step in the cipher is a dual input byte-function f(X, Y) such as an XOR of two intermediate values, and that side-channel information is available for f(X, Y). In our constraint model we represent such a computation by two input registries entering a single compute node which includes the relevant code snippet (see Figure 1b). The compute node has to take into account all possible input combinations  $\{b_n^X\} \times \{b_n^Y\}$ . For every possible combination  $(b_{n'}^X, b_{n''}^Y)$  the compute node outputs the tuple  $(b_{n'}^X, b_{n''}^Y, \alpha_{n''}^{in,X}, \alpha_{n''}^{in,Y}, f(b_{n'}^X, b_{n''}^Y))$ . The output registry now needs to compute the conflated probability for the combination  $(b_{n'}^X, b_{n''}^Y, f(b_{n'}^X, b_{n''}^Y))$ . As described in Section 2.3, the conflated probability in the output registry is computed by

$$\hat{\alpha}_{n',n''} = \frac{1}{\gamma} \cdot \alpha_n^{in,X} \cdot \alpha_n^{in,Y} \cdot P(f = f(b_{n'}^X, b_{n''}^Y))$$

for a normalization factor  $\gamma$ .

#### 3.3 Pruning Records from a Registry

The output size of a dual-input compute node is the product of sizes of the input registries. In some cases storing this much information is not feasible. For

example, when both input registries contain  $256^2$  records the output registry will have to hold  $256^4$  records, which is prohibitive. To avoid such a combinatorial explosion we can prune some of the records in the input registries by discarding all records with probabilities below a certain threshold t. Tuning the threshold is a trade off: selecting a tight threshold keeps combinatorial complexity low, but might cause pruning of records derived from the correct key bytes.

### 3.4 Data-Redundancy Constraint

We now deal with the case where some intermediate value X is used as input to more than one function. In our graph notation it means that some registry  $R^0$  was used as input to two or more compute nodes,  $C^1, C^2$ . Denote the output registries of these compute nodes  $R^{1,out}, R^{2,out}$ . Each record in these registries contains the relevant value of X for that record. Enforcing a data-redundancy constraint over the value of X means that the records from  $R^{1,out}, R^{2,out}$  should agree with each other probabilistically. For this purpose we introduce a special compute node which we call an *intersection* node (see Figure 1c). The records in  $R^{1,out}, R^{2,out}$  are observations on the same value of X thus we can conflate their probabilities as before. Note that unlike the single-input or dual-input constraints, for an intersection node we do not require a side channel oracle. Note also that if the input-probability of some value is 0 then the conflated probability for that value remains 0. This means that if the registries entering an intersection node were pruned, the intersection node's output-registry only includes combinations of the un-pruned values.

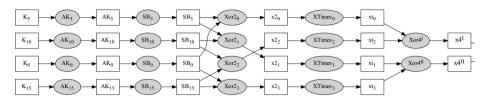

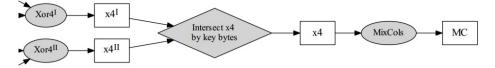

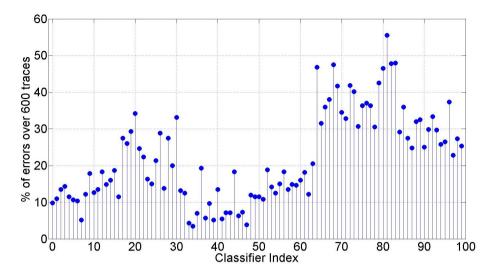

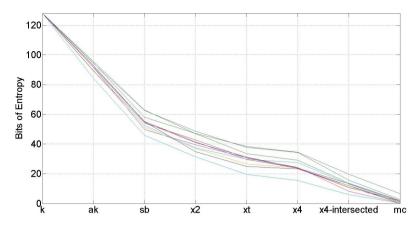

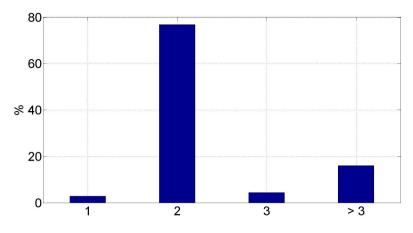

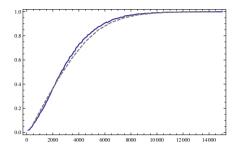

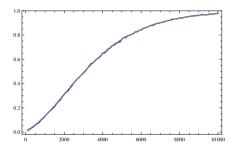

#### 3.5 Constructing a Solver for a Cipher