Armin Biere Amir Nahir Tanja Vos (Eds.)

# **LNCS 7857**

# Hardware and Software: Verification and Testing

8th International Haifa Verification Conference, HVC 2012 Haifa, Israel, November 2012 Revised Selected Papers

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany

# Hardware and Software: Verification and Testing

8th International Haifa Verification Conference, HVC 2012 Haifa, Israel, November 6-8, 2012 Revised Selected Papers

Volume Editors

Armin Biere Johannes Kepler University, 4040 Linz, Austria E-mail: biere@jku.at

Amir Nahir IBM Research Laboratory, 31905 Haifa, Israel E-mail: nahir@il.ibm.com

Tanja Vos Universidad Politecnica de Valencia, 46022 Valencia, Spain E-mail: tvos@dsic.upv.es

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-642-39610-6 e-ISBN 978-3-642-39611-3 DOI 10.1007/978-3-642-39611-3 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2013943016

CR Subject Classification (1998): D.2.4-5, D.3.1, F.3.1-2, D.2.11, I.2.2-3

LNCS Sublibrary: SL 2 – Programming and Software Engineering

© Springer-Verlag Berlin Heidelberg 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

This volume contains the proceedings of the Haifa Verification Conference (HVC 2012). The conference was hosted by IBM Research Haifa and took place during November 6–8, in 2012. It was the eighth event in this series of annual conferences dedicated to advancing the state of the art and state of practice in verification and testing.

The conference provided a forum for researchers and practitioners from academia and industry to share their work, exchange ideas, and discuss the future directions of testing and verification for hardware, software, and complex hybrid systems. In 2012, HVC extended the traditional focus on hardware and software verification to include verification, validation, and testing (VVT) of complex hybrid systems as a part of the systems-engineering paradigm.

The Intel DTS Symposium and a meeting of the COST Action IC0901 Rich-Model Toolkit were co-located events. The conference itself started with a tutorial day including "Idiom-Based Verification of Highly Concurrent Data Structures Using Temporal Separation Logic" by Noam Rinetzky, "Three-Valued Abstraction-Refinement" by Sharon Shoham Buchbinder, "Simulating Cyber-Physical Systems Using SysML and Numerical Simulation Tools" by Eldad Palachi, and on "Improving Verification Productivity with the Dynamic Load and Reseed Methodology" by Marat Teplitsky.

The Program Committee accepted 18 regular papers out of 36 submissions, whose post-conference versions are published in this volume. The conference chairs further selected three poster presentations out of four poster submissions submitted after the notification for regular papers.

The conference featured a keynote with the title "On Behavioral Programming" by David Harel and another keynote talk on "Verifying Real-Time Software Is Not Reasonable (Today)" by Edward Lee. There were two invited talks on "Reducing Costs While Increasing Quality" by Orna Raz and on "SMT in Verification, Modeling, and Testing at Microsoft" by Nikolaj Bjorner. The last day contained a session on security verification with talks on "A Vulnerability or a Bug? What's the Difference Anyway? Security Software Verification as Part of the Development Lifecycle" by Ofer Maor, another talk on "Formal Analysis of Security Data Paths in RTL Design" by Jamil Mazzawi, and a third presentation on "Simultaneous Information Flow Security and Circuit Redundancy in Boolean Gates" by Ryan Kastner.

The HVC Award, granted since 2007, recognizes the most promising academic and industrial contribution to the fields of testing and software and hardware verification from the last five years. The HVC 2012 Award Committee, chaired by Daniel Kroening, decided to give the 2012 award to Aaron R. Bradley of CU Boulder for the invention of the IC3 algorithm. Aaron Bradley gave the award talk on the last day of the conference. The Best Paper was selected by the Conference Chairs and awarded to Vasco Pessanha, Ricardo Dias, and João Lourenço for their paper with entitled "Precise Detection of Atomicity Violations."

The Conference Chairs would like to thank the members of the Program Committee for their hard work reading the papers and writing reviews under a very tight schedule during essentially one month in July and August 2012.

We are very grateful to IBM Research – Haifa for hosting and sponsoring HVC 2012.

April 2013

Armin Biere Amir Nahir Tanja Vos

# Organization

#### Program Committee

Cyrille Valentin Artho AIST, Japan Armin Biere **Roderick Bloem** Radu Calinescu Hana Chockler Kerstin Eder Maria Jose Escalona Eitan Farchi Harry Foster Franco Fummi Alex Gorvachev Ziyad Hanna Mark Harman Ian Harris Klaus Havelund Michael Hsiao Alan Hu Zurab Khasidashvili Mark Last João Lourenco Ken Mcmillan Thomas Melham Amir Nahir Martina Seidl **Onn Shehory** Armando Tacchella Helen Treharne Shmuel Ur Helmut Veith Tanja Vos Li-C Wang Joachim Wegener Heike Wehrheim

Johannes Kepler University Linz, Austria Graz University of Technology, Austria Aston University, UK IBM Research - Haifa, Israel University of Bristol, UK University of Seville, Spain IBM Research - Haifa, Israel Mentor Graphics, USA University of Verona, Italy IBM Research - Haifa. Israel University of Oxford, UK University College London, UK University of California Irvine, USA Jet Propulsion Laboratory, USA Virginia Tech, USA University of British Columbia, Canada Intel, Israel Ben-Gurion University, Israel CITI - Universidade Nova de Lisboa, Portugal Cadence Berkeley Labs, USA Oxford University, UK IBM Research - Haifa, Israel Johannes Kepler University Linz, Austria IBM Research - Haifa, Israel Università di Genova, Italy University of Surrey, UK Consultant, Israel Vienna University of Technology, Austria Researcher, Spain University of California Santa Barbara, USA Berner & Mattner, Germany University of Paderborn, Germany

# **Additional Reviewers**

Baars, Arthur Bustan, Doron Chen, Wen Egly, Uwe Finkbeiner, Bernd Heljanko, Keijo Heule, Marijn Hjort, Hakan Hofferek, Georg Ivrii, Alexander Jacobs, Swen Johnson, Kenneth Kikuchi, Shinji Koenighofer, Bettina Koenighofer, Robert Korchemny, Dmitry Nadel, Alexander Ryvchin, Vadim Schremmer, Alexander Sinn, Moritz Steenken, Dominik Timm, Nils Vizel, Yakir Wolfovitz, Guy

# Table of Contents

| On Behavioral Programming<br>David Harel                                                                | 1   |

|---------------------------------------------------------------------------------------------------------|-----|

| Verifying Real-Time Software Is Not Reasonable (Today)<br>Edward A. Lee                                 | 2   |

| SMT in Verification, Modeling, and Testing at Microsoft<br>Nikolaj Bjørner                              | 3   |

| Reducing Costs While Increasing Quality<br>Orna Raz                                                     | 4   |

| Special Session on Security Verification                                                                | 5   |

| Circuit Primitives for Monitoring Information Flow and Enabling<br>Redundancy<br><i>Ryan Kastner</i>    | 6   |

| Formal Analysis of Security Data Paths in RTL Design<br>Jamil Mazzawi and Ziyad Hanna                   | 7   |

| Precise Detection of Atomicity Violations<br>Ricardo J. Dias, Vasco Pessanha, and João M. Lourenço      | 8   |

| Proving Mutual Termination of Programs<br>Dima Elenbogen, Shmuel Katz, and Ofer Strichman               | 24  |

| Knowledge Based Transactional Behavior<br>Saddek Bensalem, Marius Bozga, Doron Peled, and Jean Quilbeuf | 40  |

| Repair with On-The-Fly Program Analysis<br>Robert Könighofer and Roderick Bloem                         | 56  |

| Computing Interpolants without Proofs                                                                   | 72  |

| MaxSAT-Based MCS Enumeration<br>Antonio Morgado, Mark Liffiton, and Joao Marques-Silva                  | 86  |

| Automated Reencoding of Boolean Formulas<br>Norbert Manthey, Marijn J.H. Heule, and Armin Biere         | 102 |

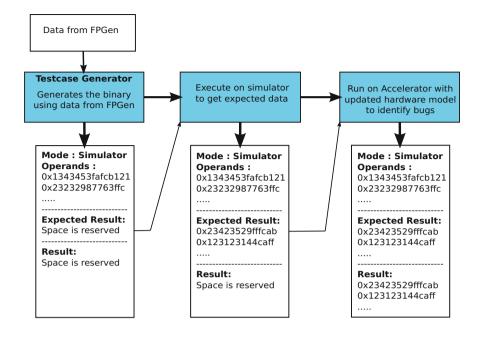

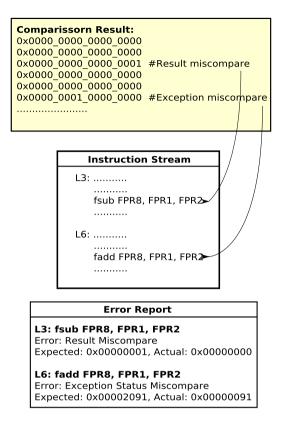

| Leveraging Accelerated Simulation for Floating-Point Regression<br>John Paul, Elena Guralnik, Anatoly Koyfman, Amir Nahir, and<br>Subrat K. Panda                                                                     | 118 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Coverage-Based Trace Signal Selection for Fault Localisation in<br>Post-silicon Validation                                                                                                                            | 132 |

| Charlie Shucheng Zhu, Georg Weissenbacher, and Sharad Malik<br>A Novel Approach for Implementing Microarchitectural Verification<br>Plans in Processor Designs<br>Yoav Katz, Michal Rimon, and Avi Ziv                | 148 |

| Statistical Model Checking for Safety Critical Hybrid Systems:<br>An Empirical Evaluation                                                                                                                             | 162 |

| A New Test-Generation Methodology for System-Level Verification<br>of Production Processes                                                                                                                            | 178 |

| Defining and Model Checking Abstractions of Complex Railway Models<br>Using CSP  B<br>Faron Moller, Hoang Nga Nguyen, Markus Roggenbach,<br>Steve Schneider, and Helen Treharne                                       | 193 |

| Word Equations with Length Constraints: What's Decidable?<br>Vijay Ganesh, Mia Minnes, Armando Solar-Lezama, and<br>Martin Rinard                                                                                     | 209 |

| Environment-Friendly Safety<br>Orna Kupferman and Sigal Weiner                                                                                                                                                        | 227 |

| Deterministic Compilation of Temporal Safety Properties in Explicit<br>State Model Checking<br><i>Kristin Yvonne Rozier and Moshe Y. Vardi</i>                                                                        | 243 |

| FoREnSiC- An Automatic Debugging Environment for C Programs<br>Roderick Bloem, Rolf Drechsler, Görschwin Fey, Alexander Finder,<br>Georg Hofferek, Robert Könighofer, Jaan Raik, Urmas Repinski,<br>and André Sülflow | 260 |

| Towards Beneficial Hardware Acceleration in HAVEN: Evaluation<br>of Testbed Architectures<br>Marcela Šimková and Ondřej Lengál                                                                                        | 266 |

| Using Domain Specific Languages to Support Verification in the<br>Railway Domain<br>Phillip James, Arnold Beckmann, and Markus Roggenbach                                                                             | 274 |

| From Fault Injection to Mutant Injection: The Next Step for Safety |     |

|--------------------------------------------------------------------|-----|

| Analysis?                                                          | 276 |

| Guillermo Rodriguez-Navas, Patrick Graydon, and Iain Bate          |     |

| Test Case Generation by Grammar-Based Fuzzing for Model-Driven     |     |

| Engineering                                                        | 278 |

| Magdalena Widl                                                     |     |

|                                                                    |     |

| Author Index                                                       | 281 |

# **On Behavioral Programming**

David Harel

The Weizmann Institute

The talk starts from a dream/vision paper I published in 2008, whose title, "Can Programming be Liberated, Period?", is a play on that of John Backus' famous Turing Award Lecture (and paper). I will propose that --- or rather ask whether --- programming can be made a lot closer to the way we humans think about dynamics, and the way we somehow manage to get others (e.g., our children, our employees, etc.) to do what we have in mind. Technically, the question is whether we can liberate programming from its three main straightjackets: (1) having to directly produce a precise artifact in some language; (2) having actually to produce two separate artifacts (the program and the requirements) and having then to pit one against the other; (3) having to program each piece/part/object of the system separately. The talk will then get a little more technical, providing some evidence of feasibility of the dream, via play-in/play-out approach **LSCs** and the to scenario-based programming, and its more recent Java variant. The entire body of work around these ideas can be framed as a paradigm, which we call behavioral programming.

# Verifying Real-Time Software Is Not Reasonable (Today)\* Abstract of Invited Talk

Edward A. Lee

UC Berkeley

**Abstract.** Verification is about demonstrating that a formal system holds certain properties. It is particularly important to verify safety-critical real-time control software, such as aircraft or automotive control systems. Unfortunately, many of the properties that need to be verified for such systems are not actually part of the formal system defined by the software. It therefore makes no sense to verify the software. So what should be verified? It is glib to say that "the system" must be verified, because "the system" is not a formal system. It is a bundle of silicon and wires. Only a model of the system can be verified. What model?

If the semantics of software is extended to include temporal properties, then verifying real-time software becomes possible. In this talk, I will argue that such extensions are practical and effective, but that they require rethinking software abstractions at a rather fundamental level. Moreover, they require reengineering of many performance optimizations that computer architects, compiler designers, and operating system designers have instituted. I will show for some of these that such reengineering yields designs that have competitive performance and verifiable timing.

<sup>\*</sup> The work reported in this talk was supported in part by the Center for Hybrid and Embedded Software Systems (CHESS) at UC Berkeley (supported by the National Science Foundation, NSF awards #0720882 (CSR-EHS: PRET) and #0931843 (ActionWebs), the Naval Research Laboratory (NRL #N0013-12-1-G015), and the following companies: Bosch, National Instruments, and Toyota).

A. Biere, A. Nahir, and T. Vos (Eds.): HVC 2012, LNCS 7857, p. 2, 2013.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2013

# SMT in Verification, Modeling, and Testing at Microsoft

Nikolaj Bjørner

Microsoft Research nbjorner@microsoft.com

The Satisfiability Modulo Theories (SMT) solver, Z3 [1], from Microsoft Research is a state-of-the art theorem prover that integrates specialized solvers for domains that are of relevance for program analysis, testing and verification. Z3 has been used within and outside of Microsoft for the past few years including the Windows 7 static driver verifier, the SAGE white-box fuzzer for finding security vulnerabilities, Pex, in a Verifying C Compiler, the Verve verified operating system kernel and the Dafny safe programming language. This talk delves into some of the more recent efforts around Z3, in particular using Z3 in a firewall analysis engine, and adventures in using Z3 for points-to analysis in JavaScript malware detection, and finally emerging support for reachability queries by solving Satisfiability Modulo Theories for Horn clauses.

Z3 is joint work with Leonardo de Moura and Christoph Wintersteiger.

## Reference

de Moura, L., Bjørner, N.: Z3: An Efficient SMT Solver. In: Ramakrishnan, C.R., Rehof, J. (eds.) TACAS 2008. LNCS, vol. 4963, pp. 337–340. Springer, Heidelberg (2008)

# **Reducing Costs While Increasing Quality**

#### Orna Raz

#### IBM Research - Haifa

**Abstract.** Non mission critical software systems have been challenged with conflicting requirements. On the one hand, these systems are becoming more and more complex and their quality is of paramount importance. On the other hand, to maintain competitiveness, there is a constant pressure to reduce the cost associated with developing such systems.

In this talk, I will raise some of the research questions stemming from these conflicting requirements. I will also present promising approaches to addressing the challenges of reduced costs while increasing quality that were explored at IBM Research.

# **Special Session on Security Verification**

Alex Goryachev

#### IBM Research - Haifa

**Abstract.** Alongside functionality, performance, and power, security is a critical aspect of any system. All software or hardware systems, web applications, and engineered systems built today must comply with stringent requirements in each of these aspects. Security requirements might include that a server must with-stand malicious attacks such as stealing or damaging the data or even denial of service. Each of these attacks can have disastrous effects. During the last year alone we saw several examples of such attacks in the media, including: stealing money from bank accounts and ATM machines, bringing down websites, and even breaking into a car computer system while it is driving.

In this session we address the challenges of verifying and validating that a system being built fulfills its security requirements.

This year is the centennial year for Alan Turing. There are many events taking place throughout the world to celebrate Turing's life and his scientific impact. HVC, and this session in particular, is part of these world-wide events.

During his relatively brief life, Turing had an enormous impact on many different fields within computer science: theory of computability, artificial intelligence, and of course cryptography and security. During World War II, Turing worked at the British codebreaking center at Bletchley Park. He stood at the head of the section responsible for decoding German naval ciphers. He also invented several methods for breaking codes, with the most famous associated with deciphering the Enigma machine.

We devote this session to honoring Alan Turing's leadership in breaking German ciphers during World War II and his contribution to cryptography in general.

We would like to thank several people who made this session possible: Hana Chockler, Ronny Morad, and Amir Nahir.

# Circuit Primitives for Monitoring Information Flow and Enabling Redundancy

Ryan Kastner

University of California, San Diego

**Abstract.** Critical systems require strict guarantees on information flow security and fault tolerance. We present a novel Boolean circuit methodology that can both monitor information flow throughout the hardware and simultaneously act as a triple modular redundant circuit. This is done by modifying the encoding technique for gate level information flow tracking (GLIFT). This new encoding not only has the added benefit of allowing for redundancy, it also reduces the size of the logic required for information flow tracking compared to the previous GLIFT encodings. This enables the development of high assurance systems on top of hardware with provable integrity and confidentiality properties. The new encoding also allows for these systems to be created with smaller area, lower power, and faster design time.

# Formal Analysis of Security Data Paths in RTL Design

Jamil Mazzawi and Ziyad Hanna

Consulting Services Manager, Jasper Design Automation PhD, Chief Architect, VP of Research, Jasper Design Automation

**Abstract.** Recently we have seen an increasing demand to have industrial hardware design verify security information. Complex systems-on-chip such as smart phones, game consoles, and advanced CPUs contain secure information. This likely leads to vulnerabilities and possibly unauthorized access to secure data. The potential for damage, whether direct or indirect, is huge. Checking if the secure information can be leaked is hard to achieve with conventional RTL validation methods. In this talk we present how formal methods can be used to detect unauthorized access to secure data, using a method called security path verification and analysis.

# **Precise Detection of Atomicity Violations**

Ricardo J. Dias, Vasco Pessanha, and João M. Lourenço\*

Departamento de Informática and CITI Universidade Nova de Lisboa, Portugal {ricardo.dias,v.pessanha}@campus.fct.unl.pt, joao.lourenco@fct.unl.pt

Abstract. Concurrent programs that are free of unsynchronized accesses to shared data may still exhibit unpredictable concurrency errors, called *atomicity violations*, which include both high-level data races and *stale-value* errors. Atomicity violations occur when programmers make wrong assumptions about the atomicity scope of a code block, incorrectly splitting it in two or more atomic blocks and allowing them to be interleaved with other atomic blocks. In this paper we propose a novel static analysis algorithm that works on a dependency graph of program variables and detects both high-level data races and *stale-value* errors. The algorithm was implemented for a Java Bytecode analyzer and its effectiveness was evaluated with well known faulty programs. The results obtained show that our algorithm performs better than previous approaches, achieving higher precision for small and medium sized programs, making it a good basis for a practical tool.

### 1 Introduction

The absence or misspecification of the scope of atomic blocks in a concurrent program may trigger atomicity violations and lead to runtime misbehaviors.

Low-level data races occur when the program includes unsynchronized accesses to a shared variable, and at least one of those accesses is a write, i.e., it changes the value of the variable. Although low-level data races are still a common source of errors and malfunctions in concurrent programs, they have been addressed by others in the past and are out of the scope of this paper. We will consider herein that the concurrent programs under analysis are free from low-level data races.

High-level data races results from the misspecification of the scope of an atomic block, by splitting it in two or more atomic blocks with other (possibly empty) non-atomic block between them. This anomaly is often referred as a high-level data race, and is illustrated in Fig. 1(a). A thread uses the method areEqual() to check if the fields 'a' and 'b' are equal. This method reads both fields in separate atomic blocks, storing their values in local variables, which are then compared. However, due to an interleaving with another thread running

<sup>\*</sup> This work was partially supported by the Euro-TM EU COST Action IC1001, and by the Portuguese National Science Foundation (FCT) in the research project Synergy-VM (PTDC/EIA-EIA/113613/2009) and the research grant SFRH/BD/41765/2007.

A. Biere, A. Nahir, and T. Vos (Eds.): HVC 2012, LNCS 7857, pp. 8–23, 2013.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2013

the method setPair (), between lines 12 and 13 the value of the pair may have changed. In this scenario the first thread observes an inconsistent pair, composed by the old value of 'a' and the new value of 'b'.

```

atomic void getA() {

1

return pair.a;

2

atomic int getX() {

3

3

1

atomic void getB() {

4

2

return x:

return pair.b;

3

5

}

6

4

atomic void setX(int p0) {

atomic void setPair(int a, int b){

7

5

x = p0;

8

pair.a = a;

6

}

void incX(int val) {

pair.b = b;

٩

7

10

8

int tmp = getX();

boolean areEqual(){

9

tmp = tmp + val;

11

int a = getA();

setX(tmp);

12

10

13

int b = getB();

11

}

return a == b;

14

(b) A stale value error.

}

15

```

(a) A high-level data race.

Fig. 1. Example of atomicity violations

Figure 1(b) illustrates a stale value error, another source of atomicity violations in concurrent programs. The non-atomic method incX() is implemented by resorting to two atomic methods, getX() (at line 1) and setX() (at line 4). During the execution of line 9, if the current thread is suspended and another thread is scheduled to execute setX(), the value of 'x' changes, and when the execution of the initial thread is resumed it overwrites the value in 'x' at line 10, causing a lost update. This program fails due to a stale-value error, as at line 8 the value of 'x' escapes the scope of the atomic method getX() and is reused indirectly (by way of its private copy 'tmp') at line 10, when updating the value of 'x' in setX().

In this paper we propose a novel approach for the detection of high-level data races and stale-value errors in concurrent programs. As our proposal only depends on the concept of atomic regions and is neutral concerning the mechanisms used for their identification, the atomic regions are not delimited using locks but rather using an **@Atomic** annotation. Our approach is based on a novel notion of variable dependencies, which we designate as *causal* dependencies. There is a *causal* dependency between two variables if the value of one of them influences the writing of the other. We also extended previous work from Artho et al. [2] by reflecting the read/write nature of accesses to shared variables inside atomic regions and additionally use the dependencies information to detect both high-level data races and stale-value errors. We formally describe the static analysis algorithms to compute the set of *causal* dependencies of a program and define safety conditions for both high-level data races and stale-value errors.

Our approach can yield both false positives and false negatives. However, the experimental results demonstrate that it still achieves high precision when detecting atomicity violations in well know examples from the literature, suggesting its usefulness for software development tools.

In the next Section of this paper we introduce the previous relevant work on detections of high-level data races and stale-value errors; in Section 3 we define a core language and introduce some definitions that support the remainder of the paper, namely Sections 4 and 5, where we propose algorithms for defining *causal dependencies* between variables and for detecting atomicity violations (data races). In Section 6 we briefly describe a tool that applies the proposed algorithms with static analysis techniques for Java Bytecode programs, and compare and discuss the results obtained. We terminate in Section 7 with some final concluding remarks.

## 2 Background and Related Work

Several past works have addressed the detection of the same class of atomicity violations in concurrent programs as addressed in this paper.

The work from Artho et al. [2] introduces the concept of view consistency, to detect high-level data races. A view of an atomic block is a set containing all the shared variables accessed (both for reading and writing) within that block. The maximal views of a process are those views that are not a subset of any other view. Intuitively, a maximal view defines a set of variables that should always be accessed atomically (inside the same atomic block). A program is free from high-level data races if all the views of one thread that are a subset of the maximal views from another thread form an inclusion chain among themselves.

Our work builds on the proposal from Artho et al. [2], but we extend it by incorporating the type of memory access (read or write) into the views, and refine the rules for detecting high-level data races to consider this additional information and the information given by the *causal* dependencies, with considerable positive impact in the precision of the algorithm, as demonstrated in Section 6.

Praun and Gross [9] introduce *method consistency* as an extension of view consistency. Based on the intuition that the variables that should be accessed atomically in a given method are all the variables accessed inside a synchronized block, the authors define the concept of *method views* that relates to Artho et al's maximal views, which aggregates all the shared variables accessed in a method and also differentiates between read and write memory accesses. Similarly to ours, this approach is more precise than Artho et al's because it also detects stale-value errors. Our algorithm however has higher precision than Praun's and give less false positives, as we use *maximal views* rather than *method views*.

Wang and Stoller [10] use the concept of *thread atomicity* to detect and prevent data races, where thread atomicity guarantees that all concurrent executions of a set of threads is equivalent to a sequential execution of those threads. In an attempt to reduce the number of false positives yield by [10], Teixeira et al. [7] proposed a variant of this algorithm based in the intuition that the majority of the atomicity violations come from two consecutive atomic blocks that should be merged into a single one. The authors detect data races by defining and detecting some anomalous memory access patterns for both high-level data races and stale-value errors. Our approach may be seen as a generalization of this

$C ::= \text{class } id \{ field^* (M | \text{atomic } M)^* \} (class \ decl) \qquad P ::= C^+ (program)$

Fig. 2. Core language syntax

concept of memory access patterns, but in our case supported by the notion of causal dependencies between variables, which allow to reduce considerably the number of both false negatives and false positives.

#### Core Language 3

We start by defining a core language that captures essential features of a subset of the Java programming language, namely class declaration (class  $id\{...\}$ ), object creation (new), field dereferencing (x.f), assignment (x := e), and method invocation  $(meth(\vec{x}))$ . The syntax of the language is defined by the grammar in Fig. 2.

A program in this language is composed by a set of class declarations. Atomic blocks correspond to methods that are declared using the **atomic** keyword. We require the restriction of not allowing nesting of atomic blocks i.e., we do not allow to call an atomic method inside another atomic method. Variables can hold integers or object references and boolean values are encoded as integers using the value 1 for true and value 0 for false. We also do not support exception handling as normally found in typical object-oriented languages.

We now define some sets that are necessary to the understanding of the following sections:

- Classes: is the set of all class identifiers of all classes declared in the program.

- Fields: is the set of all class fields defined in the program.

- Methods: is the the set of all methods defined in the program.

- Atomics  $\subseteq$  Methods: is the subset of methods that were declared as atomic.

We define a local (stack) variable as a pair of the form (x,m) where x is the variable identifier and  $m \in \mathsf{Methods}$  is the method where this variable is declared. For the sake of simplicity we write the pair (x, m) as only x whenever is not

11

ambiguous to do so. The set of all local variables of a program is denoted as LocalVars.

We define a global variable as an object field and we represent it as the pair (c, f) where  $c \in \mathsf{Classes}$  represents the class where field  $f \in \mathsf{Fields}$  is declared. The set of all global variables is denoted as  $\mathsf{GlobalVars}$ . These global variables appear in the code when dereferencing an object reference. For instance, in the statement x.f := 4, the expression x.f represents a global variable of the form (c, f) where c is the class of the object reference pointed by local variable x. We define a function typeof : LocalVars  $\rightarrow \mathsf{Classes}$ , which given a local variable returns the class of the object reference that it holds. So, in the example above  $c = \mathsf{typeof}(x)$ .

Please note that by deciding to represent an access to a field of an object as a pair with the class of the object reference and the field accessed, we are not able to differentiate between different object instances of the same class, and hence we may consider that there is always at most one object instance of each declared class in the program. This allows us to avoid pointer analysis at the cost of losing precision and becoming unsound in some cases but, as the results in Section 6 show, this design choice has proven to be very effective.

Finally we define the set  $Vars \equiv LocalVars + GlobalVars$ , which corresponds to all variables used in the program, both local and global variables.

### 4 Causal Dependencies

There is a *Causal* dependency, which we will designate herein only as dependency, between two program variables (local or global) if the value read from one variable influences the value written into the other. For instance, the following expression

y := x

generates a dependency between variable x and y because the value that is written into variable y was read from variable x. As another example, consider the following code:

if

$$(x = 0) \{ y := 4 \}$$

In this example, the variable y is written only if the condition x = 0 is true, thus it depends on the current value of variable x and therefore there is also a dependency between variables x and y. We represent a dependency between two variables x and y as  $x \hookrightarrow y$  where  $x \in \mathsf{Vars}$  is the variable read and  $y \in \mathsf{Vars}$  is the variable written.

For each program we can compute a directed graph of *causal* dependencies. The information provided by this graph plays an important role in finding correlations between variables, which can be used to detect atomicity violations. We can define two kinds of correlations between variables.

**Definition 1 (Direct Correlation).** There is a direct correlation between a read variable x and a written variable y if there is a path from x to y, in a dependency graph  $\mathcal{D}$ .

Fig. 3. Dependency graph example

**Definition 2 (Common Correlation).** There is a common correlation between a read variable x and a read variable y if there is a written variable z, where  $z \neq x$  and  $z \neq y$ , for which there is a path from x to z and another path from y to z, in a dependency graph  $\mathcal{D}$ .

In the following section we describe how to compute the graph of dependencies using symbolic execution.

#### 4.1 Dependency Analysis

The construction of the dependency graph is done in two steps. In the first step we only detect data dependencies between variables. In the second step we detect control dependencies between variables. In the end we merge all dependencies in a single graph.

**Data Dependencies.** The accurate detection of data dependencies relies on the precise localisation of where the variables are defined. SSA (Single Static Assignment) [1] could be used, because each variable would only have one definition site, but this only works for local variables, and we still need to track each definition site for global variables. Therefore we did not use SSA as internal representation and we solve the problem by defining a new variable version whenever the variable is updated.

A variable version is defined as a triple of the form (x, h, m) where  $x \in \mathsf{Vars}$  is a variable (local or global), h is a unique identifier, and  $m \in \mathsf{Atomics} \cup \{\bot\}$  indicates if this variable is used inside an atomic method or not  $(\bot)$ . The set of all variable versions is denoted as Versions.

The unique identifier h is a hash value based on the line of code of the respective definition site. If the version of the variable is not known in the current context, as in the case of method arguments, a special hash value is used. We denote this special hash value as  $h_{?}$ .

Figure 3 depicts the dependency graph for the method 'incX()' from Fig. 1(b). For the sake of simplicity, we omitted the method (m) part of the version representation. We denote getX. ret as the return value of method getX(), and setX. p0 as the parameter of method setX(int p0). Both the return value and the parameter do not need to have an hash value associated, and thus we omitted it from their representation.

In method incX(int val), the value returned by the method getX() is written into a temporary variable tmp, which is then incremented using parameter val and is then used as a parameter on the invocation of method setX(int p0).

While analyzing this method, we first start by creating the dependency  $getX. ret \hookrightarrow (tmp, h_2)$  between the return value of getX() method and variable tmp with an hash value  $h_2$ . In the next statement variable tmp is redefined with a value resulting from the sum of the previous tmp variable and the val parameter, and hence we create two dependencies  $(tmp, h_2) \hookrightarrow (tmp, h_3)$  and  $val \hookrightarrow (tmp, h_3)$ , where the new version of tmp variable has the hash value  $h_3$ . Finally, we invoke method setX(int p0) with the value of tmp as parameter and therefore we create the dependency  $(tmp, h_3) \hookrightarrow setX. p0$ .

The symbolic execution rules are defined as a transition system  $(\langle \mathcal{D}, \mathcal{H}, S \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle)$  over a state composed by a dependency graph  $\mathcal{D}$  and a set of versions, denoted has  $\mathcal{H} \subseteq$  Versions, which holds the current versions of each program variable. In a single program point, we may find different versions of the same variable because our analysis over-approximates the run-time state of a program. The rules can be depicted in Figure 4, and we always omit the method (m) parameter from the representation of a variable version.

Function  $\operatorname{ver}_{\mathcal{H}}$  is used to retrieve the set of current versions of a variable, and is defined as follows:

**Definition 3 (Version Retrieval).** Given a set of versions  $\mathcal{H}$  and a variable  $v \in \mathsf{Vars}$ :

$\mathsf{ver}: \mathcal{P}(\mathsf{Versions}) \times \mathsf{Vars} \to \mathcal{P}(\mathsf{Versions})$

$$\mathsf{ver}_{\mathcal{H}}(v) \triangleq \begin{cases} \{(v, h, m) \mid (v, h, m) \in \mathcal{H} \} & \text{if } \exists (v, h, m) \in \mathcal{H} \\ \{(v, h_{7}, m) \} & \text{otherwise} \end{cases}$$

If a variable version cannot be found in  $\mathcal{H}$ , a version with the special hash value  $h_{?}$  is returned.

Every time that a variable is written, it is created a new version for such variable and all other existing current versions are replaced by the new one. We define an helper function  $subs_{\mathcal{H}}$  for this purpose as:

**Definition 4 (Version Substitution).** Given a set of versions  $\mathcal{H}$  and a variable version  $(v, h, m) \in \text{Versions}$ :

subs :

$$\mathcal{P}(\mathsf{Versions}) \times \mathsf{Versions} \to \mathcal{P}(\mathsf{Versions})$$

$$\mathsf{subs}_{\mathcal{H}}((v,h,m)) \triangleq (\mathcal{H} \setminus \{(v,h',m') \mid (v,h',m') \in \mathcal{H}\}) \cup \{(v,h,m)\}$$

Each hash value is generated using the function nhash, which given a statement S generates a new and unique hash value based in the line number of that statement. This function is deterministic in the sense that for any statement S the same hash value is always returned.

At the beginning of the analysis, the sets  $\mathcal{D}$  and  $\mathcal{H}$  are empty. We represent the parameters of methods as *meth*.  $p_i$ , and the return value of a method as *meth*. *ret*.

$$\begin{split} & \frac{\langle \mathcal{D}, \mathcal{H}, S_1 \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle \quad \langle \mathcal{D}', \mathcal{H}', S_2 \rangle \Longrightarrow \langle \mathcal{D}'', \mathcal{H}'' \rangle}{\langle \mathcal{D}, \mathcal{H}, S_1; S_2 \rangle \Longrightarrow \langle \mathcal{D}'', \mathcal{H}'' \rangle} \\ & h = \mathsf{nhash}(x := y) \\ & \frac{\mathcal{H}' = \mathsf{subs}_{\mathcal{H}}((x,h)) \quad \mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (x,h) \mid v \in \mathsf{ver}_{\mathcal{H}}(y)\}}{\langle \mathcal{D}, \mathcal{H}, x := y \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle} \\ & (\mathsf{ASSIGN}) \\ \hline \\ & \frac{\mathcal{L}' = \mathsf{pupeof}(y) \quad h = \mathsf{nhash}(x := y, f) \quad \mathcal{H}' = \mathsf{subs}_{\mathcal{H}}((x,h))}{\langle \mathcal{D}, \mathcal{H}, x := y, f \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle} \\ & (\mathsf{HEAP READ}) \\ \hline \\ & \frac{\mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (x,h) \mid v \in \mathsf{ver}_{\mathcal{H}}(y,h)\}}{\langle \mathcal{D}, \mathcal{H}, x := y, f \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle} \\ & (\mathsf{HEAP READ}) \\ \hline \\ & \frac{\mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (c,f), h\} \mid v \in \mathsf{ver}_{\mathcal{H}}(y)\}}{\langle \mathcal{D}, \mathcal{H}, x, f := y \rangle \Longrightarrow \langle \mathcal{D}', \mathcal{H}' \rangle} \\ & (\mathsf{HEAP WRITE}) \\ \hline \\ & \frac{h = \mathsf{nhash}(x := \mathsf{new} C()) \quad \mathcal{H}' = \mathsf{subs}_{\mathcal{H}}((x,h))}{\langle \mathcal{D}, \mathcal{H}, x := \mathsf{new} C() \Rightarrow \langle \mathcal{D}, \mathcal{H}' \rangle} \\ & (\mathsf{ALLOCATION}) \\ \hline \\ & \frac{\langle \mathcal{D}, \mathcal{H}, x := \mathsf{new} C() \Rightarrow \langle \mathcal{D}, \mathcal{H}' \rangle}{\langle \mathcal{D}, \mathcal{H}, x := \mathsf{new} C() \Rightarrow \langle \mathcal{D}, \mathcal{H}' \rangle} \\ & (\mathsf{ALLOCATION}) \\ & \frac{\mathcal{H}' = \{(v,h) \mid (v,h) \in \mathcal{H}, v \in \mathsf{ver}_{\mathcal{H}}(y_i)\} \cup \{\mathsf{meth}, \mathsf{ret} \hookrightarrow (x,h)\}}{\langle \mathcal{D}, \mathcal{H}, x := \mathsf{new} f(y)} \\ & \mathsf{spec}(\mathsf{meth}) = \langle \mathcal{D}_f, \mathcal{H}_f \rangle \quad \mathcal{D}' = \mathcal{D}_f \cup \mathcal{D} \\ & \mathcal{D}'' = \mathcal{D}' \cup \{v_i \leftrightarrow \mathsf{meth}, y_i \mid \forall_i \in \mathcal{I}, v \in \mathsf{ver}_{\mathcal{H}}(y_i)\} \cup \{\mathsf{meth}, \mathsf{ret} \hookrightarrow (x,h)\} \\ & \mathcal{H}'' = \{(v,h) \mid (v,h) \in \mathcal{H} \land (v,h_2) \in \mathcal{H}_f \lor (v,h) \notin \mathcal{H}_f)\} \\ & \mathcal{H}'' = \{(v,h) \mid (v,h) \in \mathcal{H} \land (v,h_2) \notin \mathcal{H}'' \land (v,h_2) \notin \mathcal{H}' \land (v,h_2) \notin \mathcal{H} \land (v,h_2) \notin \mathcal{H} \land (v,h_2) \notin \mathcal{H} \land (v,h_2) \notin \mathcal{H}' \land (v,h_2) \notin \mathcal{H}' \land (v,h_2) \notin \mathcal{H}' \land (v,h_2) \notin \mathcal{H} \land (v,h_2) \notin \mathcal$$

Fig. 4. Symbolic execution rules of data dependencies analysis

When evaluating the RETURN statement, the return value of the method is denoted as retVar.

All assignment operations, namely ASSIGN, HEAP READ, and HEAP WRITE, create dependencies between all versions of the variables used in the right side of the assignment and the new version of the assigned variable. The newly generated version is then used to replace all existing versions of that same variable.

In the rule METH CALL, the function **spec** returns the result, denoted as  $\langle \mathcal{D}_p, \mathcal{H}_p \rangle$ , of the analysis of method *meth*. The dependencies in  $\mathcal{D}_p$  are merged with the current dependencies and we create a dependency between each value that is passed as an argument to *meth* and the respective declared parameter *meth*.  $p_i$ . We also need to update the variables' versions that are generated inside the method. If a variable was redefined  $(h \neq h_i)$  inside *meth* then we replace the

15

existing versions with the new version, otherwise we keep the current versions. Finally, we add one more dependency between the return value of method *meth* and the assigned value.

In the rule CONDITIONAL, the dependencies are generated in both branches and are merged with the initial  $\mathcal{D}$ . We also generate the versions for each branch, and if a variable x has a version  $h \neq h_{?}$  in one branch but there is no version for the same variable in the other branch, then we generate a special version  $h_{?}$  for variable x and we join it to all the other versions. The intuition behind this operation is that if a variable is written only in one of the branches then we also need to add the case that the variable might not have been written. The rule LOOP is similar to the CONDITIONAL rule. The remaining rules should be self-explanatory.

After analyzing all methods of the program we get a dependency graph for the whole program, based on data-flow information. Next, we have to add the remaining dependencies based on the control flow information.

**Control Dependencies.** If an assignment or return statement is guarded by some condition then that assignment or return statement depends on the variables used in the condition. This situation may occur with every conditional statement such as an if then else, or a while loop.

The analysis of control dependencies traverses the control flow graph and keeps the set of variables that the assignments may depend on. When an assignment or return statement is found we create a dependency between the current variables, that it may depend on, and the respective assigned variable.

The symbolic execution rules are shown in Figure 5 as a transition system  $(\langle \mathcal{IS}, \mathcal{D}, S \rangle \Longrightarrow \langle \mathcal{IS}', \mathcal{D}' \rangle)$ . The state is composed by a set of conditional variables  $\mathcal{IS} \subseteq \mathsf{Versions}$ , which correspond to the variable versions that the current statement depends on, and a dependency graph  $\mathcal{D}$ . In the beginning of the analysis the dependency graph is empty, and the set of conditional variables has the union of all conditional variables that are present at all calling contexts of the method that is going to be analyzed. For instance, given the program methods  $m_1, m_2$  and  $m_3$  where method  $m_1$  calls method  $m_2$  with the current conditional variables set  $\mathcal{IS} = \{c_1, c_2\}$ , and  $m_3$  calls method  $m_2$  with the current conditional variables set  $\mathcal{IS} = \{c_3, c_4\}$ , then the initial set of conditional variables when analyzing method  $m_2$  is  $\mathcal{IS} = \{c_1, c_2, c_3, c_4\}$ .

In the end of this analysis the resulting graph of dependencies is merged with the one that resulted from the data dependencies analysis, described in the previous section, thus forming the complete graph of *causal* dependencies.

For every kind of assignment we create a dependency between the current conditional variables and the assigned variable. This situation may occur in the rules ASSIGN, HEAP READ, HEAP WRITE, ALLOCATION and METH CALL. In the case of a return statement, as in rule RETURN, we create a dependency with the special variable retVar.

In the rules CONDITIONAL and LOOP, we analyze each branch with a new set of conditional variables, which include the current conditional variables plus the variable of the condition. Each variable is actually a variable version with

$$\frac{\langle \mathcal{IS}, \mathcal{D}, S_1 \rangle \Longrightarrow \langle \mathcal{IS}', \mathcal{D}' \rangle \qquad \langle \mathcal{IS}', \mathcal{D}', S_2 \rangle \Longrightarrow \langle \mathcal{IS}'', \mathcal{D}'' \rangle}{\langle \mathcal{IS}, \mathcal{D}, S_1; S_2 \rangle \Longrightarrow \langle \mathcal{IS}'', \mathcal{D}'' \rangle} (SEQ)$$

$$\frac{h = nhash(x := y) \qquad \mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (x, h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x := y \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (ASSIGN)$$

$$\frac{h = nhash(x := y.f) \qquad \mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (x, h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x := y.f \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (HEAP READ)$$

$$\frac{c = typeof(x)}{\langle \mathcal{IS}, \mathcal{D}, x := y \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (HEAP WRITE)$$

$$\frac{h = nhash(x.f := y) \qquad \mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow ((c, f), h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x.f := y \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (ALLOCATION)$$

$$\frac{h = nhash(x := new C()) \qquad \mathcal{D}' = \mathcal{D} \cup \{v \hookrightarrow (x, h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x := new C() \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (ALLOCATION)$$

$$\frac{h = nhash(x := new C()) \qquad \mathcal{D}' = \mathcal{D} \cup \mathcal{D}_f \cup \{v \hookrightarrow (x, h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x := new C() \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (METH CALL)$$

$$\frac{f(x, \mathcal{D}, x := new C()) \qquad \mathcal{D}' = \mathcal{D} \cup \mathcal{D}_f \cup \{v \hookrightarrow (x, h) \mid v \in \mathcal{IS}\}}{\langle \mathcal{IS}, \mathcal{D}, x := new f(y) \rangle \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \rangle} (CONDITIONAL)$$

$$\frac{f(x, \mathcal{D}, x)}{\langle \mathcal{IS}, \mathcal{D}, x := new h(y)} \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \cup \mathcal{D}' \rangle} (CONDITIONAL)$$

$$\frac{f(x, \mathcal{D}, x)}{\langle \mathcal{IS}, \mathcal{D}, x := new f(y)} \Longrightarrow \langle \mathcal{IS}, \mathcal{D}' \cup \mathcal{D}' \rangle} (LOOP)$$

$$\frac{f(x, \mathcal{D}, y)}{\langle \mathcal{IS}, \mathcal{D}, y \mapsto \langle \mathcal{IS}, \mathcal{D} \cup \mathcal{D}' \rangle} (RETURN) \qquad \overline{\langle \mathcal{IS}, \mathcal{D}, skip} \Longrightarrow \langle \mathcal{IS}, \mathcal{D} \rangle} (SKIP)$$

Fig. 5. Symbolic execution rules of control dependencies analysis

an unique hash value. When we exit the scope of the condition we remove the condition variable and proceed with the analysis. The remaining rules are self-explanatory.

The result of these two analysis generate the graph of *causal* dependencies that is used to detect the existence of atomicity violations in a concurrent program, as we will show in the following sections.

# 5 Atomicity Violations

The purpose of our work is to detect two kinds of atomicity errors, the highlevel data race and the stale-value error, that may occur during the execution of concurrent programs that use atomic blocks to guarantee mutual exclusion in the access to shared data.

The definition of both errors assume that the concurrent program has no lowlevel data races, meaning that all accesses to shared variables are done inside atomic blocks.

17

#### 5.1 High Level Data Races

A view, as described by Artho et al. in [2], expresses what variables are accessed inside a given atomic code block. We extend this definition by also keeping the kind of access (read or write) that was made for each variable in the view.

Please note that a *view* only stores global variables. Local variables are not shared between threads and thus do not require synchronized accesses.

We denote as Accesses the set of memory accesses made inside an atomic block. An access  $a \in$  Accesses is a pair of the form  $(\alpha, v)$  where  $\alpha \in \{r, w\}$ represents the kind of access (*r*-read or *w*-write) and  $v \in$  GlobalVars is a global variable<sup>1</sup>. A view is a subset of Accesses and the set of all views in a program is denoted as Views. A view is always associated with one atomic method, and we define the bijective function  $\Gamma$  that given a view returns the associated atomic method as:

$\Gamma: \mathsf{Views} \to \mathsf{Atomics}$

The inverse function, denoted as  $\Gamma^{-1}$ , returns the *view* associated with a given atomic method. The set of *generated views* of a process p, denoted as V(p), corresponds to the atomic blocks executed by one process, and is defined as:

$$v \in V(p) \Leftrightarrow m = \Gamma(v) \land \mathsf{executes}(p,m)$$

The predicate executes asserts if a method m may be executed by process p, and is defined by an auxiliary static analysis that computes the set of processes and the atomic methods that are called in each process.

We can refine the previous definition of V(p) with a parameter  $\alpha$ , where  $\alpha \in \{r, w\}$ , to get only the views of a process with read  $(V_r)$  or write accesses  $(V_w)$ .

#### **Definition 5 (Procedure Views)**

$$V_{\alpha}(p) = \{ v_2 \mid v_1 \in V(p) \land v_2 = \{ (\alpha, x) \mid (\alpha, x) \in v_1 \} \} \text{ where } \alpha \in \{ r, w \}$$

We defined a static analysis to compute a *view* of an atomic method. Every time a global variable is read or written, the corresponding read or write access is created and added to the *view*. The *view* resulting from a method call is merged with the current *view* that is being computed. In the case of conditional and loop statements we perform an over-approximation union of the *views* of each branch. In the end of the analysis we have the set of *views* corresponding to the atomic methods present in the program code.

The maximal views of a process, denoted as  $M_{\alpha}$ , are all the views of the process that are not a subset of any other view in that same process. A maximal view is defined as follows:

<sup>&</sup>lt;sup>1</sup> Please remember that global variables are represented as a pair with a class identifier and the field accessed.

**Definition 6 (Maximal Views).** Given a process p, a maximal view  $v_m$  is defined as:

$$v_m \in M_\alpha(p) \Leftrightarrow v_m \in V_\alpha(p) \land (\forall v \in V_\alpha(p) : v_m \subseteq v \Rightarrow v = v_m) \quad where \ \alpha \in \{r, w\}$$

Each *maximal view* represent the set of variables that should be accessed atomically, i.e., should always be accessed in the same atomic block.

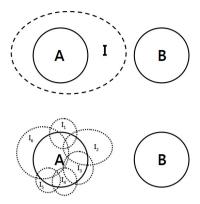

Given a set of views of a process p and a maximal view  $v_m$  of another process, we define the read or write overlapping views of process p with view  $v_m$  as all the non empty intersection views between  $v_m$  and the views of process p.

**Definition 7 (Overlapping Views).** Given a process p and maximal view  $v_m$ :

$\mathsf{overlap}_{\alpha}(p, v_m) \triangleq \{ v_m \cap v \mid v \in V_{\alpha}(p) \land v_m \cap v \neq \emptyset \} \quad where \; \alpha \in \{r, w\}$

The notion of compatibility between a process p and a view  $v_m$ , defined in [2], states that a process p and a view  $v_m$  are compatible if all their overlapping views form a chain. We extended this definition with the information given by the causal dependencies graph, and we additionally require that, even if the read overlapping views do not form a chain, there may not exist a common correlation (Definition 2) between the variables in the read overlapping views.

**Definition 8 (Process Compatibility).** Given a process p and maximal view  $v_m$ :

$$\operatorname{comp}_{w}(p, v_{m}) \Leftrightarrow \forall v_{1}, v_{2} \in \operatorname{overlap}_{w}(p, v_{m}) : v_{1} \subseteq v_{2} \lor v_{2} \subseteq v_{1}$$

$$\operatorname{comp}_{r}(p, v_{m}) \Leftrightarrow \forall v_{1}, v_{2} \in \operatorname{overlap}_{r}(p, v_{m}) : v_{1} \subseteq v_{2} \lor v_{2} \subseteq v_{1}$$

$$\lor \neg \operatorname{CommonCorrelation}(v_{1}, v_{2})$$

The intuition behind this additional condition is that, even if two shared variables that belong to a *maximal view* were read in different atomic blocks, we will only consider that there is an incompatibility if both variables are used in a common write operation.

We can now define the *view consistency* safety property in terms of the compatibility between all pairs of processes of a program. A process may only have *views* that are compatible with all *maximal views* of another process. A program is free from high-level data races if the following condition holds:

#### **Definition 9 (View Consistency)**

$\forall p_1, p_2 \in \mathcal{P}_{\mathcal{S}}, m_r \in M_r(p_1), m_w \in M_w(p_1) : \mathsf{comp}_w(p_2, m_r) \land \mathsf{comp}_r(p_2, m_w)$

where  $\mathcal{P}_{\mathcal{S}}$  is the set of processes.

#### 5.2 Stale-Value Error

Stale-value errors are a class of atomicity violations that are not detected by the view consistency property. Our approach to detect this kind of errors uses the

graph of *causal* dependencies to detect values that escape the scope of an atomic block (e.g., by assigning a shared variable to a local variable) and are later used inside another atomic block (e.g., by assigning the previous local variable to a shared variable).

First we define the set IVersions  $\subseteq$  Versions, which stores all global variable versions that were accessed inside an atomic block. Each variable version has a parameter m that indicates in which atomic method it was defined, or has the value  $\perp$  if it was not used inside an atomic method.

**Definition 10 (Atomic Variable Version).** A global variable version (x, h, m) is an atomic variable if:

$(x, h, m) \in \mathsf{IVersions} \Leftrightarrow (x, h, m) \in \mathsf{Versions} \land x \in \mathsf{GlobalVars} \land m \neq \bot$

Now we define a new graph, denoted as  $\mathcal{D}_{\mathcal{V}}$ , which represent the dependencies between views. A labeled edge of this graph  $\mathcal{D}_{\mathcal{V}}$  is represented as  $(m_1, x, m_2)$ where  $m_1, m_2 \in \text{Atomics}$  and  $x \in \text{GlobalVars}$ , and can be interpreted as atomic method  $m_2$  depends on atomic method  $m_1$  through global variable x. Intuitively, this means that the value of variable x exited the scope of method  $m_1$  and entered the scope of method  $m_2$ , and while it was out of the atomic scopes it might have become outdated.

Each edge  $(m_1, x_1, m_2)$  of a view dependency graph  $\mathcal{D}_{\mathcal{V}}$ , is created when, given two version variables  $a_1 = (x_1, h_1, m_1) \in \mathsf{IVersions}$  and  $a_2 = (x_2, h_2, m_2) \in \mathsf{IVersions}$ , and a causal dependency graph  $\mathcal{D}$ , the following conditions hold:

$(\mathsf{DirectCorrelation}(\mathcal{D}, a_1, a_2) \land m_1 \neq m_2) \lor (m_1 = m_2 \land \mathsf{DirectCorrelation}(\mathcal{D}, a_1, m_1. ret) \land \mathsf{DirectCorrelation}(\mathcal{D}, m_1. ret, m_1. p_i) \land \mathsf{DirectCorrelation}(\mathcal{D}, m_1. p_i, a_2))$

The predicate DirectCorrelation asserts if two variables are directly correlated according to Definition 1. These conditions state that there is a dependency between  $m_1$  and  $m_2$  through variable  $x_1$ , if the variable version  $a_1$  is directly correlated with  $a_2$  when  $m_1$  and  $m_2$  are two different atomic methods, or if the two methods  $m_1$  and  $m_2$  are the same, then we must be sure that the value of  $x_1$  left out the scope of the method and then entered it again.

A process p writes in a variable  $x \in Vars$  if there is a write access on variable x in one of the views of process p:

$$\mathsf{writes}(x,p) \Leftrightarrow \exists v \in V_w(p) : (w,x) \in v$$

The safety property for *stale-value* errors can be defined as the case where no process writes to a global variable that leaves, and then enters, the scope of an atomic method of another process.

#### Definition 11 (Stale-Value Safety)

$$\forall p \in \mathcal{P}_{\mathcal{S}}, (m_1, x, m_2) \in \mathcal{D}_{\mathcal{V}} : \neg \operatorname{writes}(x, p) \text{ where } \mathcal{P}_{\mathcal{S}} \text{ is the set of processes}$$

If there is a *view* dependency for variable x and there is a process p that writes on that variable then a *stale-value* error is detected.

| Tests                                                                | AV                                                                                | <b>False</b><br>MoTH | e <b>Negat</b><br>Artho                                                           |                                       | Fals<br>MoTH                           | e Posit<br>Artho |                                            | Acc.<br>Vars                                                            |                                                                                        | Time<br>(sec.)                                                                        |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------|---------------------------------------|----------------------------------------|------------------|--------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Connection [4]                                                       | 2                                                                                 | 0                    | 1                                                                                 | 1                                     | 0                                      | 0                | 1                                          | 34                                                                      | 112                                                                                    | 45                                                                                    |

| Coord03 [2]<br>Local [2]<br>NASA [2]                                 | 1<br>1<br>1                                                                       | 0<br>0<br>0          | $\begin{array}{c} 0 \\ 1 \\ 0 \end{array}$                                        | 0<br>0<br>0                           | 0<br>0<br>0                            | 0<br>0<br>0      | $\begin{array}{c} 3 \\ 1 \\ 0 \end{array}$ | $     \begin{array}{c}       13 \\       3 \\       7     \end{array} $ | $170 \\ 33 \\ 121$                                                                     | $     \begin{array}{r}       43 \\       42 \\       43     \end{array} $             |

| Coord04 [3]<br>Buffer [3]<br>DoubleCheck [3]                         | $\begin{array}{c} 1 \\ 0 \\ 0 \end{array}$                                        | 0<br>0<br>0          | 0<br>0<br>0                                                                       | 0<br>0<br>0                           | $egin{array}{c} 0 \ 1 \ 1 \end{array}$ | 0<br>0<br>0      | 3     7     2                              | 7<br>8<br>7                                                             | $47 \\ 64 \\ 51$                                                                       | $\begin{array}{c} 40\\ 41\\ 41\end{array}$                                            |

| StringBuffer [5]                                                     | 1                                                                                 | 0                    | 1                                                                                 | 1                                     | 0                                      | 0                | 0                                          | 12                                                                      | 52                                                                                     | 44                                                                                    |

| Account [9]<br>Jigsaw [9]<br>OverReporting [9]<br>UnderReporting [9] | $     \begin{array}{c}       1 \\       1 \\       0 \\       1     \end{array} $ | 0<br>0<br>0<br>0     | $     \begin{array}{c}       1 \\       0 \\       0 \\       1     \end{array} $ | 0<br>0<br>0<br>0                      | 0<br>0<br>0<br>0                       | 0<br>0<br>0<br>0 | 0<br>1<br>2<br>0                           | 3<br>33<br>6<br>3                                                       | $     \begin{array}{r}       65 \\       145 \\       52 \\       31     \end{array} $ | $     \begin{array}{r}       40 \\       40 \\       42 \\       39     \end{array} $ |

| Allocate Vector [6]                                                  | 1                                                                                 | 0                    | 1                                                                                 | 0                                     | 0                                      | 0                | 1                                          | 24                                                                      | 304                                                                                    | 41                                                                                    |

| Knight [7]<br>Arithmetic Database [7]                                | 1<br>3                                                                            | 0<br>0               | $\frac{1}{3}$                                                                     | $\begin{array}{c} 0 \\ 1 \end{array}$ | $\begin{array}{c} 0 \\ 1 \end{array}$  | 0<br>0           | $\begin{array}{c} 2 \\ 0 \end{array}$      | $\begin{array}{c} 10\\ 24 \end{array}$                                  | $\begin{array}{c} 223\\ 416 \end{array}$                                               | $\begin{array}{c} 41 \\ 54 \end{array}$                                               |

| Total                                                                | 15                                                                                | 0                    | 10                                                                                | 3                                     | 3                                      | 0                | 23                                         | -                                                                       | -                                                                                      | -                                                                                     |

Table 1. Results for benchmarks — Set 1

## 6 Evaluation

To evaluate the accuracy of our algorithms and techniques, we adapted and implemented the theoretical framework described in the previous sections to the Java Bytecode language, where the atomic methods are defined using the **@Atomic** method annotation. We used the data-flow analysis infrastructure of the Soot framework [8] to implement all the described analysis.

Our tool starts by parsing a Java bytecode program and computing a set of analysis, namely: process analysis to identify which threads may exist when executing the program; instance type analysis to handle Java interfaces and dynamic dispatching; views analysis, to compute the views of each atomic method; inter-procedural causal dependency analysis, to compute dependencies between variables used in assignments and conditional code blocks. Once all these analysis are concluded, the tool creates the causal dependency graph. Another analysis is then ran over this dependency graph to identify atomic blocks that break the atomicity violation safety properties.

Besides comparing our results with those reported on the literature for individual benchmarks, we did an exhaustive comparison with two other approaches: the work of Artho et al [2], because our approach is an extension of this work; and the work of Teixeira et al [7], because their results are currently a reference for the field. The results presented were obtained by running our tool with the algorithms described in this paper; by using Artho et al's algorithm implemented with static analysis techniques (rather than the dynamic analysis reported in [2]); and by running Teixeira's tool on the Java source (instead of the Bytecode).

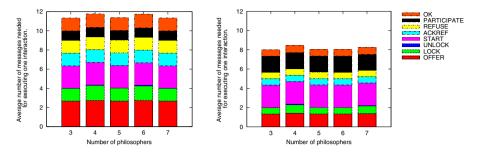

Tables 1 and 2 summarize the results achieved by applying our tool to a set of benchmarking programs, most of them well known from related works and compares them with the two works cited above. Teixeira's tool was unable to

| Tests                                         | AV                | False N<br>MoTH  | <b>legatives</b><br>Artho                                                          | <b>False F</b><br>MoTH |                                             | Acc.<br>Vars                   | LOC                     | ${f Time}\ ({ m sec.})$                                        |

|-----------------------------------------------|-------------------|------------------|------------------------------------------------------------------------------------|------------------------|---------------------------------------------|--------------------------------|-------------------------|----------------------------------------------------------------|

| Elevator [9]<br>Philo [9]<br>Tsp [9]<br>Store | 16<br>0<br>0<br>2 | 0<br>0<br>0<br>0 | $     \begin{array}{c}       16 \\       0 \\       0 \\       1     \end{array} $ | 6<br>2<br>2<br>0       | $\begin{array}{c} 4\\ 0\\ 0\\ 1\end{array}$ | $39 \\ 9/594 \\ 635 \\ 44/608$ | 558<br>96<br>795<br>901 | $\begin{array}{r} 46 \\ 45/612 \\ 869 \\ 149/1763 \end{array}$ |

| Total                                         | 18                | 0                | 17                                                                                 | 10                     | 5                                           | -                              | -                       | -                                                              |

Table 2. Results for benchmarks — Set 2

process some of the benchmarks, so they are reported in a separate second set. Columns AV indicate the number of known atomicity violations, *false negatives* indicate the number of known program atomicity violations that were missed by the approach<sup>2</sup>, *false positives* indicate the number of reported but non-existing atomicity violations, *Acc. Vars* indicate the number of variables accessed inside atomic regions and is an indication of the problem size, together with the number of *LOC*, and how long it took for our analysis to run.

In the case of Table 2, the benchmarks Philo and Store have two different values for *accessed variables* and *time*. The second values report on the original benchmarks, which includes some (non-essential) calls to I/O methods in the JDK library. The first values report on a tailored version of the benchmarks where those calls to the JDK library were commented.

For the benchmarks listed in Table 1, our approach revealed a very high accuracy by reporting no false negatives and only three false positives. The false positive in the Buffer benchmark is due to an assumption claim from its authors that is not implemented in the actual code. The information collected by the Causal Dependency Analysis is incomplete and imprecise and originates false positives in the Double Check and Arithmetic Database benchmarks while checking for stale-value errors, which are not detected by Artho et al's approach.

For the benchmarks listed in Table 2, our appropriate again reveled very high accuracy, as although it reported 10 false positives (vs. only 5 from Artho et al's), it reported zero false negatives (vs. 17 from Artho et al's). These benchmarks also indicate that our algorithms scale well with the the size of the problem, both in the number of accessed variables inside the atomic blocks and the number of lines of code.

#### 7 Conclusions

In this paper we presented a novel approach to detect high-level data races and stale-value errors in concurrent programs. The proposed approach relies on the notion of *causal* dependencies to improve the precision of previous detection techniques. The high-level data races are detected using an algorithm based on

$<sup>^2</sup>$  The identification of false negative is only possible because the sets of atomicity violations in the benchmarking programs are well known.

a previous work by Artho et al. refined to distinguish between read and write accesses and extended with the information given by the *causal* dependencies. The stale-value errors are detected using the information given by the *causal* dependencies, which exposes the values of variables that escaped an atomic block and entered into another atomic block.

Our detection analysis still remains unsound mainly due to the absence of pointer analysis and to the way that *views* are computed. But these design decisions allowed us to maintain the scalability of our approach without incurring in a strong precision loss, as our experimental results confirm.

We evaluated our analysis techniques with well known examples from the literature and compared them to previous works. Our results show that we are able to detect all atomicity violations present in the examples, while reporting a low number of false positives.

#### References

- Alpern, B., Wegman, M.N., Zadeck, F.K.: Detecting equality of variables in programs. In: Proc. of the 15th ACM SIGPLAN-SIGACT Symp. on Principles of Programming Languages, POPL 1988, pp. 1–11. ACM, San Diego (1988)

- Artho, C., Havelund, K., Biere, A.: High-level data races. Software Testing, Verification and Reliability 13(4), 207–227 (2003)

- Artho, C., Havelund, K., Biere, A.: Using block-local atomicity to detect stale-value concurrency errors. In: Wang, F. (ed.) ATVA 2004. LNCS, vol. 3299, pp. 150–164. Springer, Heidelberg (2004)

- Beckman, N.E., Bierhoff, K., Aldrich, J.: Verifying correct usage of atomic blocks and typestate. SIGPLAN Not. 43(10), 227–244 (2008)

- Flanagan, C., Freund, S.N.: Atomizer: a dynamic atomicity checker for multithreaded programs. In: Proc. of the 31st ACM SIGPLAN-SIGACT Symp. on Principles of Programming Languages, POPL 2004, Venice, Italy, pp. 256–267 (2004)

- 6. IBM HRL Concurrency Testing Repository

- Teixeira, B., Lourenço, J.M., Farchi, E., Dias, R.J., Sousa, D.G.: Detection of transactional memory anomalies using static analysis. In: Proc. of the 8th Workshop on Parallel and Distributed Systems: Testing, Analysis, and Debugging, PADTAD 2010, pp. 26–36. ACM, New York (2010)

- Vallée-Rai, R., Co, P., Gagnon, E., Hendren, L., Lam, P., Sundaresan, V.: Soot

a Java bytecode optimization framework. In: Proc. of the 1999 Conference of

the Centre for Advanced Studies on Collaborative Research, CASCON 1999, pp.

125–135. IBM Press (1999)

- von Praun, C., Gross, T.R.: Static detection of atomicity violations in objectoriented programs. Journal of Object Technology, 2004 (2003)

- Wang, L., Stoller, S.: Run-Time Analysis for Atomicity. Electronic Notes in Theoretical Computer Science 89(2), 191–209 (2003)

# **Proving Mutual Termination of Programs**

Dima Elenbogen<sup>1</sup>, Shmuel Katz<sup>1</sup>, and Ofer Strichman<sup>2</sup>

<sup>1</sup> CS, Technion, Haifa, Israel {katz,edima}@cs.technion.ac.il