Julian Martin Kunkel Thomas Ludwig Hans Werner Meuer (Eds.)

# Supercomputing

28th International Supercomputing Conference, ISC 2013 Leipzig, Germany, June 2013 Proceedings

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Julian Martin Kunkel Thomas Ludwig Hans Werner Meuer (Eds.)

# Supercomputing

28th International Supercomputing Conference, ISC 2013 Leipzig, Germany, June 16-20, 2013 Proceedings

Volume Editors

Julian Martin Kunkel University of Hamburg Department of Informatics Bundestraße 45a 20146 Hamburg, Germany E-mail: julian.martin.kunkel@informatik.uni-hamburg.de

Thomas Ludwig Deutsches Klimarechenzentrum Bundestraße 45a 20146 Hamburg, Germany E-mail: ludwig@dkrz.de

Hans Werner Meuer University of Mannheim, Germany and Prometeus GmbH Fliederstraße 2 74915 Waibstadt, Germany E-mail: hans.meuer@isc-events.com

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-642-38749-4 e-ISBN 978-3-642-38750-0 DOI 10.1007/978-3-642-38750-0 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2013939202

CR Subject Classification (1998): C.1, B.8, C.4, C.3, I.3.1, C.5, F.2, D.3.4, D.4, C.2.4

LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

© Springer-Verlag Berlin Heidelberg 2013

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

The International Supercomputing Conference, founded in 1986 as the Supercomputer Seminar by Professor Hans Meuer, has been held annually for the last 27 years. Originally, the seminar brought together a group of 81 scientists and industrial partners who all shared an interest in high-performance computing. Since then, the annual conference has become a major international event within the HPC community. Accompanying its growth in size over the years, the conference has moved from Mannheim via Heidelberg, Dresden, and Hamburg to Leipzig. With 2,400 attendees and 175 exhibitors from over 50 countries in 2012, we are optimistic that this steady growth of interest will also turn ISC'13 into a powerful and memorable event.

In 2007 we decided to strengthen the scientific part of the conference by presenting selected talks on relevant research results within the HPC field. These research paper sessions began as a separate day preceding the conference, where slides and accompanying papers were made available via the conference website. The research paper sessions have since evolved into an integral part of the conference, and this year the scientific presentations are scheduled over three days. The call for participation was issued in winter 2012, inviting researchers and developers to submit the latest results of their work as full research papers to the sessions Program Committee.

A total of 89 paper abstracts were submitted from authors all over the world. In a peer-review process an international committee selected the best 35 papers for publication and for presentation in the research paper sessions. This year's review process was modified to improve the overall quality of the reviews by including an early abstract submission and author rebuttal phase.

We are pleased to announce that many fascinating topics in HPC were presented this year. The papers address the following issues regarding the development of an environment for exascale supercomputers:

- Scalable applications with 50K+ cores

- Performance improvements in algorithms

- Accelerators

- Performance analysis and optimization

- Library development

- Administration and management of supercomputers

- Energy efficiency

- Parallel I/O

- Grid and cloud

We believe that this selection is highly appealing and that the presentations will foster inspiring discussions with the audience.

As in the previous years, two independent award committees selected two papers considered to be of exceptional quality and worthy of special recognition.

- The Gauss Centre for Supercomputing sponsors the Gauss Award. This award is assigned to the most outstanding paper in the field of scalable supercomputing.

- PRACE, the Partnership for Advanced Computing in Europe, awards a prize to the best scientific paper by a European student or scientist.

The award winners are announced on the website of ISC'13.

We would like to express our gratitude to all our colleagues for submitting papers to the ISC scientific sessions, as well as to the members of the Program Committee for organizing this year's attractive program.

June 2013

Julian M. Kunkel Thomas Ludwig Hans Meuer

# Organization

## **Program Committee**

Pavan Balaji Venkatramani Balaji Mahdi Bohlouli Xing Cai Anne Elster Michael Gerndt Lutz Gross David Ham Frank Hannig Magne Haveraaen Huynh Phung Huynh Kenichi Itakura Oleksiy Koshulko Julian M. Kunkel Dong Li Fang-Pang Lin Thomas Ludwig Muniyappa Manjunathaiah Simon McIntosh-Smith Bernd Mohr Pierre Moinier Alexander Moskovsky Matthias Müller Kengo Nakajima Alexander Nemukhin Ramon Nou

Julio Ortega Ying Qian

Michael M. Resch Henk Sips

Alexandros Stamatakis

Argonne National Laboratory, USA Princeton University, USA University of Siegen, Germany Simula Research Laboratory, Norway Norwegian University of Science and Technology, Norway Technische Universität München, Germany University of Queensland, Australia Imperial College London, UK Friedrich Alexander University Erlangen-Nürnberg, Germany University of Bergen, Norway A\*STAR, IHPC, Singapore JAMSTEC, Japan Glushkov Institute of Cybernetics NAS, Ukraine Deutsches Klimarechenzentrum, Germany Oak Ridge National Lab, USA National Center for High-Performance Computing, Taiwan Deutsches Klimarechenzentrum, Germany University of Reading, UK University of Bristol, UK Jülich Supercomputing Center, Germany BAE Systems, UK RSC SKIF, Russia RWTH Aachen, Germany University of Tokyo, Japan M.V. Lomonosov Moscow State University, Russia Barcelona Supercomputing Center, Spain University of Granada, Spain King Abdullah University of Science and Technology, Saudi Arabia HLRS Stuttgart, Germany Delft University of Technology, The Netherlands HITS, Germany

Guangming Tan Osamu Tatebe Jeyan Thiyagalingam Matthew E. Tolentino Yuichi Tsujita Zhonglei Wang Thomas Wild Ying Zhao Mikhail Zhizhin Chinese Academy of Sciences, China University of Tsukuba, Japan Oxford University, UK Intel, USA Kinki University, Japan Intel Mobile Communications, Germany Technische Universität München, Germany Tsinghua University, China CIRES/NOAA Boulder and Space Research Institute, Russia

# **External Reviewers**

| Ian Bland<br>Konstantinos Chasapis<br>Mihai-C. Duta<br>Joel Fenwick<br>Andriy Golovinsky<br>Jeff Hammond | Huynh-Bach Khoa<br>Mian Lu<br>Richard Membarth<br>Xiaoxuan Meng<br>Gihan Mudalige<br>Antonio Pena | Christian Schmitt<br>Konstantin Solnushkin<br>Marc Wiedemann<br>Michaela Zimmer |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Jeff Hammond<br>Qi Hu                                                                                    | Antonio Pena<br>Istvan Reguly                                                                     |                                                                                 |

# Table of Contents

| 591 TFLOPS Multi-trillion Particles Simulation on SuperMUC<br>Wolfgang Eckhardt, Alexander Heinecke, Reinhold Bader,<br>Matthias Brehm, Nicolay Hammer, Herbert Huber,<br>Hans-Georg Kleinhenz, Jadran Vrabec, Hans Hasse, Martin Horsch,<br>Martin Bernreuther, Colin W. Glass, Christoph Niethammer,<br>Arndt Bode, and Hans-Joachim Bungartz | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Up to 700k GPU Cores, Kepler, and the Exascale Future for Simulations<br>of Star Clusters around Black Holes<br>Peter Berczik, Rainer Spurzem, Shiyan Zhong, Long Wang,<br>Keigo Nitadori, Tsuyoshi Hamada, and Alexander Veles                                                                                                                 | 13 |

| Parallelizing a High-Order CFD Software for 3D, Multi-block,<br>Structural Grids on the TianHe-1A Supercomputer<br>Chuanfu Xu, Xiaogang Deng, Lilun Zhang, Yi Jiang, Wei Cao,<br>Jianbin Fang, Yonggang Che, Yongxian Wang, and Wei Liu                                                                                                         | 26 |

| Lattice QCD on Intel® Xeon Phi <sup>TM</sup> Coprocessors<br>Bálint Joó, Dhiraj D. Kalamkar, Karthikeyan Vaidyanathan,<br>Mikhail Smelyanskiy, Kiran Pamnany, Victor W. Lee,<br>Pradeep Dubey, and William Watson III                                                                                                                           | 40 |

| Towards Addressing CPU-Intensive Seismological Applications<br>in Europe                                                                                                                                                                                                                                                                        | 55 |

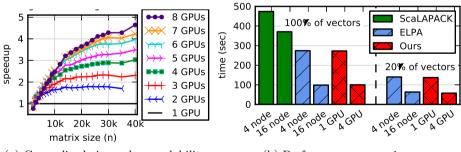

| Leading Edge Hybrid Multi-GPU Algorithms for Generalized<br>Eigenproblems in Electronic Structure Calculations<br>Azzam Haidar, Raffaele Solcà, Mark Gates, Stanimire Tomov,<br>Thomas Schulthess, and Jack Dongarra                                                                                                                            | 67 |

| <ul> <li>Heterogeneous Programming and Optimization of Gyrokinetic Toroidal</li> <li>Code and Large-Scale Performance Test on TH-1A</li></ul>                                                                                                                                                                                                   | 81 |

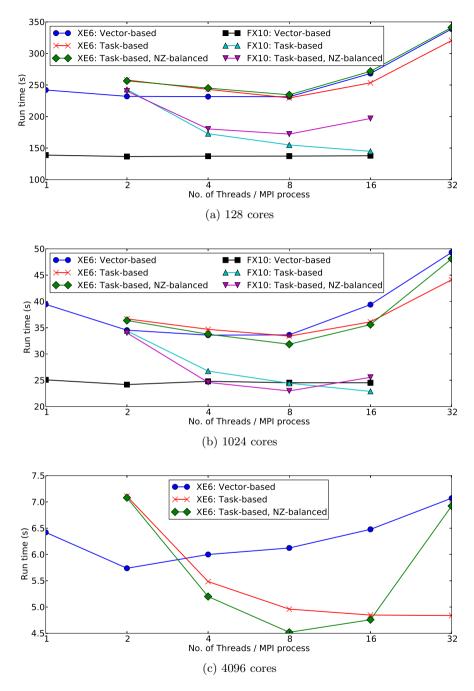

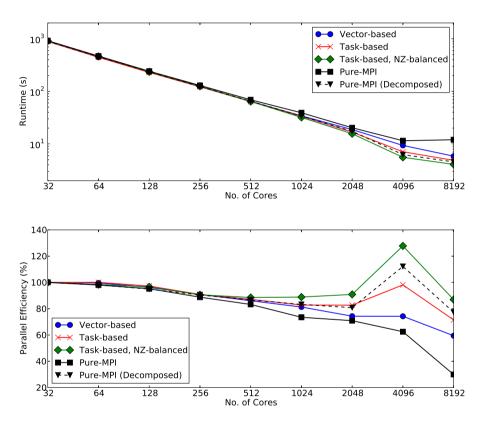

| Achieving Efficient Strong Scaling with PETSc Using Hybrid<br>MPI/OpenMP Optimisation                                                                                                                                                                             | 97  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Michael Lange, Gerard Gorman, Michèle Weiland,<br>Lawrence Mitchell, and James Southern                                                                                                                                                                           |     |

| Designing Scalable Graph500 Benchmark with Hybrid<br>MPI+OpenSHMEM Programming Models<br>Jithin Jose, Sreeram Potluri, Karen Tomko, and<br>Dhabaleswar K. Panda                                                                                                   | 109 |

| On the GPU Performance of 3D Stencil Computations Implemented<br>in OpenCL                                                                                                                                                                                        | 125 |

| Improving Performance Portability in OpenCL Programs<br>Yao Zhang, Mark Sinclair II, and Andrew A. Chien                                                                                                                                                          | 136 |

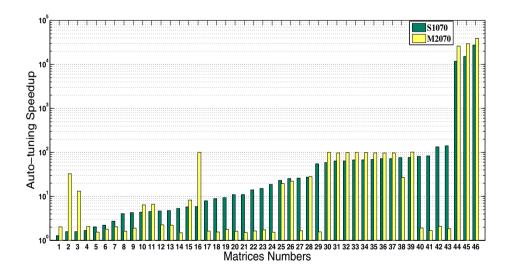

| Auto-tuning of Sparse Matrix-Vector Multiplication on Graphics<br>Processors                                                                                                                                                                                      | 151 |

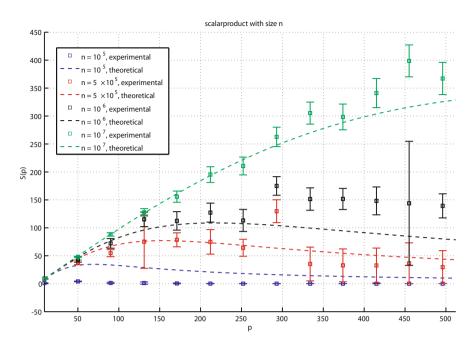

| A Simple Concept for the Performance Analysis<br>of Cluster-Computing                                                                                                                                                                                             | 165 |

| Using Simulation to Validate Performance of MPI(-IO)<br>Implementations<br>Julian Martin Kunkel                                                                                                                                                                   | 181 |

| Software Design Space Exploration for Exascale Combustion<br>Co-design<br>Cy Chan, Didem Unat, Michael Lijewski, Weiqun Zhang,<br>John Bell, and John Shalf                                                                                                       | 196 |

| Beyond the CPU: Hardware Performance Counter Monitoring on Blue<br>Gene/Q                                                                                                                                                                                         | 213 |

| Maximizing Application Performance in a Multi-core, NUMA-Aware<br>Compute Cluster by Multi-level Tuning<br>Gilad Shainer, Pak Lui, Martin Hilgeman, Jeffrey Layton,<br>Cydney Stevens, Walker Stemple, Scot Schultz, Guy Ludden,<br>Joshua Mora, and Georg Kresse | 226 |

| Offload Compiler Runtime for the Intel® Xeon Phi <sup>TM</sup> Coprocessor<br>Chris J. Newburn, Rajiv Deodhar, Serguei Dmitriev, Ravi Murty,<br>Ravi Narayanaswamy, John Wiegert, Francisco Chinchilla, and<br>Russell McGuire                                    | 239 |

| Fork-Join and Data-Driven Execution Models on Multi-core<br>Architectures: Case Study of the FMM<br>Abdelhalim Amer, Naoya Maruyama, Miquel Pericàs,<br>Kenjiro Taura, Rio Yokota, and Satoshi Matsuoka        | 255 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| VLI – A Library for High Precision Integer and Polynomial<br>Arithmetic<br><i>Timothée Ewart, Andreas Hehn, and Matthias Troyer</i>                                                                            | 267 |

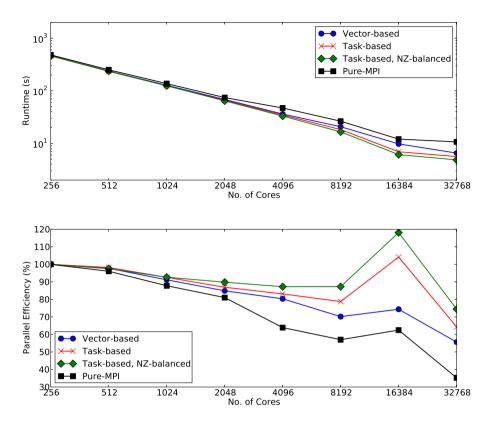

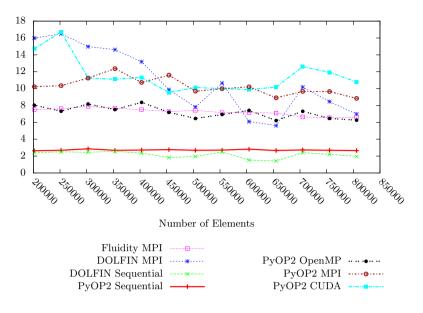

| Performance-Portable Finite Element Assembly Using PyOP2 and<br>FEniCSGraham R. Markall, Florian Rathgeber, Lawrence Mitchell,<br>Nicolas Loriant, Carlo Bertolli, David A. Ham, and Paul H.J. Kelly           | 279 |

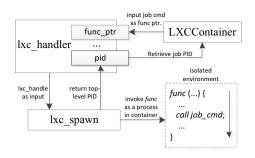

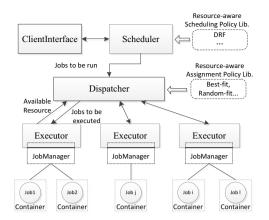

| Container-Based Job Management for Fair Resource Sharing<br>Jue Hong, Pavan Balaji, Gaojin Wen, Bibo Tu, Junming Yan,<br>Chengzhong Xu, and Shengzhong Feng                                                    | 290 |

| One Size Does Not Fit All: Clustering Supercomputer Failures Using<br>a Multiple Time Window Approach<br><i>Catello Di Martino</i>                                                                             | 302 |

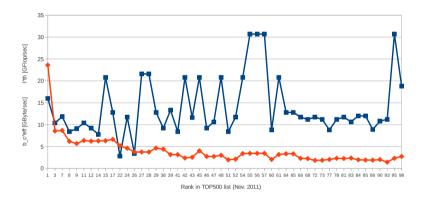

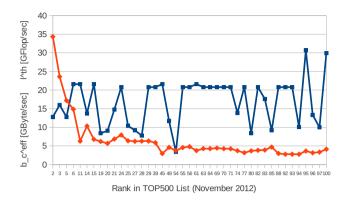

| Tracking the Performance Evolution of Blue Gene Systems<br>Darren J. Kerbyson, Kevin J. Barker, Diego S. Gallo,<br>Dong Chen, Jose R. Brunheroto, Kyung Dong Ryu,<br>George L. Chiu, and Adolfy Hoisie         | 317 |

| Accelerators for Technical Computing: Is It Worth the Pain? A TCO<br>Perspective<br>Sandra Wienke, Dieter an Mey, and Matthias S. Müller                                                                       | 330 |

| Evaluating Lossy Compression on Climate Data<br>Nathanael Hübbe, Al Wegener, Julian Martin Kunkel, Yi Ling, and<br>Thomas Ludwig                                                                               | 343 |

| The Effect of Topology-Aware Process and Thread Placement<br>on Performance and Energy<br>Albert Solernou, Jeyarajan Thiyagalingam, Mihai C. Duta, and<br>Anne E. Trefethen                                    | 357 |

| TUE, a New Energy-Efficiency Metric Applied at ORNL's Jaguar<br>Michael K. Patterson, Stephen W. Poole, Chung-Hsing Hsu,<br>Don Maxwell, William Tschudi, Henry Coles,<br>David J. Martinez, and Natalie Bates | 372 |

| iDataCool: HPC with Hot-Water Cooling and Energy Reuse<br>Nils Meyer, Manfred Ries, Stefan Solbrig, and Tilo Wettig                                                                                            | 383 |

| Pre-execution Data Prefetching with Inter-thread I/O Scheduling<br>Yue Zhao, Kenji Yoshigoe, and Mengjun Xie                                                                                                   | 395 |

| A Semantics-Aware I/O Interface for High Performance Computing<br>Michael Kuhn                                                                                      | 408 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Towards Self-optimization in HPC I/O<br>Michaela Zimmer, Julian Martin Kunkel, and Thomas Ludwig                                                                    | 422 |

| Using GPFS to Manage NVRAM-Based Storage Cache<br>Salem El Sayed, Stephan Graf, Michael Hennecke, Dirk Pleiter,<br>Georg Schwarz, Heiko Schick, and Michael Stephan | 435 |

| VM-MAD: A Cloud/Cluster Software for Service-Oriented Academic<br>Environments                                                                                      | 447 |

| Federating HPC Access via SAML: Towards a Plug-and-Play<br>Solution<br>Jens Köhler, Michael Simon, Martin Nussbaumer, and<br>Hannes Hartenstein                     | 462 |

| Author Index                                                                                                                                                        | 475 |

# 591 TFLOPS Multi-trillion Particles Simulation on SuperMUC

Wolfgang Eckhardt<sup>1</sup>, Alexander Heinecke<sup>1</sup>,

Reinhold Bader<sup>2</sup>, Matthias Brehm<sup>2</sup>, Nicolay Hammer<sup>2</sup>, Herbert Huber<sup>2</sup>, Hans-Georg Kleinhenz<sup>2</sup>, Jadran Vrabec<sup>3</sup>, Hans Hasse<sup>4</sup>, Martin Horsch<sup>4</sup>, Martin Bernreuther<sup>5</sup>, Colin W. Glass<sup>5</sup>, Christoph Niethammer<sup>5</sup>, Arndt Bode<sup>1,2</sup>, and Hans-Joachim Bungartz<sup>1,2</sup>

$^1\,$  Technische Universität München, Boltzmannstr. 3, D-85748 Garching, Germany $^2\,$ Leibniz-Rechenzentrum der Bayerischen Akademie der Wissenschaften,

Boltzmannstr. 1, D-85748 Garching, Germany

<sup>3</sup> University of Paderborn, Warburger Str. 100, D-33098 Paderborn, Germany

<sup>4</sup> Laboratory of Engineering Thermodynamics (LTD), TU Kaiserslautern,

Erwin-Schrödinger-Str. 44, D-67663 Kaiserslautern, Germany

<sup>5</sup> High Performance Computing Centre Stuttgart (HLRS), Nobelstr. 19, D-70569 Stuttgart, Germany

Abstract. Anticipating large-scale molecular dynamics simulations (MD) in nano-fluidics, we conduct performance and scalability studies of an optimized version of the code ls1 mardyn. We present our implementation requiring only 32 Bytes per molecule, which allows us to run the, to our knowledge, largest MD simulation to date. Our optimizations tailored to the Intel Sandy Bridge processor are explained, including vectorization as well as shared-memory parallelization to make use of Hyperthreading. Finally we present results for weak and strong scaling experiments on up to 146016 Cores of SuperMUC at the Leibniz Supercomputing Centre, achieving a speed-up of 133k times which corresponds to an absolute performance of 591.2 TFLOPS.

**Keywords:** molecular dynamics simulations, highly scalable simulation, vectorization, Intel AVX, SuperMUC.

# 1 Introduction and Related Work

MD simulation has become a recognized tool in engineering and natural sciences, complementing theory and experiment. Despite its development for over half a century, scientists still quest for ever larger and longer simulation runs to cover processes on greater length and time scales. Due to the massive parallelism MD typically exhibits, it is a preeminent task for high-performance computing.

An application requiring large-scale simulations is the investigation of nucleation processes, where the spontaneous emergence of a new phase is studied [8]. To enable such simulations, we optimized our program derived from the code 1s1 mardyn. A description of 1s1 mardyn focusing on use cases, software structure and load balancing considerations can be found in [1]. Based on the further development of the memory optimization described in [3], an extremely low memory requirement of only 32 Bytes per molecule has been achieved, which allows us to carry out the to our knowledge largest MD simulation to date on SuperMUC at Leibniz Supercomputing Centre. In order to run these large-scale simulations at satisfactory performance, we tuned the implementation of the molecular interactions outlined in [2] to the Intel Sandy Bridge processor and added a newly developed shared-memory parallelization to make use of Intel Hyperthreading. Thereby, this contribution continues a series of publications on extreme-scale MD. In 2000, Roth [18] performed a simulation of  $5 \cdot 10^9$  molecules, the largest simulation ever at that time. Kadau and Germann [4, 10] followed up, holding the current world record with  $10^{12}$  particles. These simulations demonstrated the state of the art on the one hand, and showed the scalability and performance of the respective codes. More recent examples include the simulation of blood flow [15] as well as the force calculation of  $3 \cdot 10^{12}$  particles by Kabadshow in 2011 [9], however without calculating particle trajectories.

The remainder of the paper is organized as follows: this Section describes the computational model of our simulation code. Section 2 describes the architecture of SuperMUC, Section 3 details the implementation with respect to vectorization and memory-efficiency, and Section 4 presents the results.

The fluid under consideration is modeled as a system of N discrete particles. Only particles *i* and *j* separated by a distance  $r_{ij}$  that is smaller than a cutoff radius  $r_c$  interact pairwise through the truncated and shifted Lennard-Jones potential [19], which is determined by the usual Lennard-Jones-12-6 potential (LJ-12-6)  $U_{LJ}(r_{ij})$  with the potential parameters  $\epsilon$  and  $\sigma$ :

$$U_{LJ}(r_{ij}) = 4\epsilon \cdot \left( \left(\frac{\sigma}{r_{ij}}\right)^{12} - \left(\frac{\sigma}{r_{ij}}\right)^6 \right).$$

The interactions with all neighbors results in a force  $F_i = \sum_{j \in particles} F_{ij}(r_{ij})$ on each of the particles, which is evaluated only once per particle pair, due to Newton's law  $F_{ij} = -F_{ji}$ .

In MD, the most time-consuming step is the force calculation. To efficiently search for neighboring particles, the linked-cell algorithm is employed in a similar way as in [10]. The computational domain is subdivided into cubic cells with an edge length  $r_c$ . Consequently, for a given particle, the distances to all other particles contained in the same cell as well as in the (in 3D) 26 adjacent cells have to be computed. This results in a linear complexity of the force calculation. The particles' data are stored in dynamic arrays, i.e. contiguous memory blocks, per cell, to avoid additional memory for pointers. Thus,

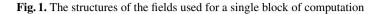

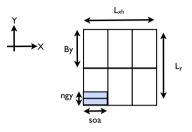

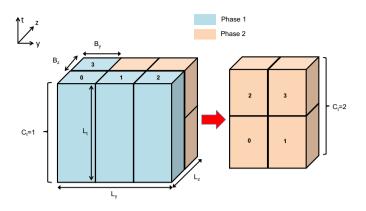

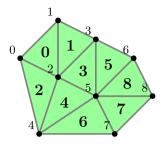

**Fig. 1.** Schematic of the linked-cell algorithm (2D)

the organization of the linked-cells data structure causes only small overhead.

In accordance with preceding large-scale simulations [4], single-precision variables are used for the calculation. For a particle we store only its position  $(3 \cdot 4 \text{ Bytes})$ , velocity  $(3 \cdot 4 \text{ Bytes})$  and an identifier (8 Bytes), i.e. 32 Bytes in total.

The force vector does not need to be stored permanently, because the time integration of the equations of motion is carried out on the fly, as detailed in Section 3.

To evaluate our implementation, single-center Lennard-Jones particles were distributed on a regular grid according to a body-centered cubic lattice, with a liquid-like number density of  $\rho\sigma^3 = 0.78$ , and the cut-off radius was specified to be  $r_c = 3.5\sigma$ . The time step length was set to 1 fs.

For the MPI parallelization, we employ a spatial domain decomposition scheme. For n processes, the domain is divided in n equally-sized sub-domains, which are assigned to one process each. Each sub-domain is surrounded by a layer of ghost cells residing on neighboring processes, so the particles at the process boundaries have to be exchanged at the beginning of each time step.

# 2 SuperMUC – The World's Largest x86 Machine

#### 2.1 System Topology

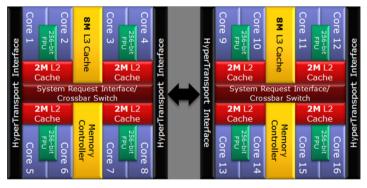

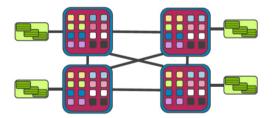

We optimized our MD code on the micro-architecture level for a specific processor: the Intel Sandy Bridge EP driving SuperMUC operated at the Leibniz Supercomputing Centre in Munich. This system features 147456 cores and is at present the biggest x86 system worldwide with a theoretical double precision peak performance of more than 3 PFLOPS, placed #6 on the current Top500 list. The system was assembled by IBM and features a highly efficient hot-water cooling solution. In contrast to supercomputers offered by Cray, SGI or even IBM's own BlueGene, the machine is based on a high-performance commodity network: a FDR-10 infiniband pruned tree topology by Mellanox. Each of the 18 leafs, or islands, consists of 512 nodes with 16 cores at 2.7 GHz clock speed (turbo mode is disabled) sharing 32GB of main memory. Within one island, all nodes can communicate at full FDR-10 data-rate. In case of inter-island communication, four nodes share one uplink to the spine switch. Since the machine is operated diskless, a significant fraction of the nodes' memory has to be reserved for the operation environment.

#### 2.2 Intel Sandy Bridge Architecture

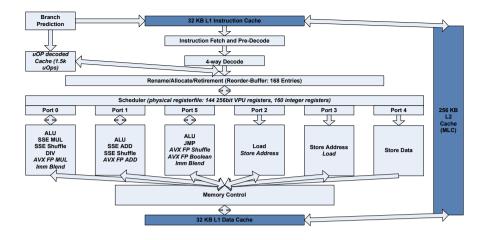

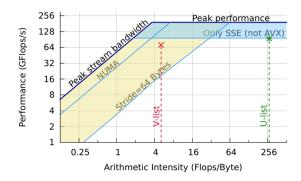

After a bird's eye view on the entire system, we now focus on its heart, the Intel Sandy Bridge EP processor that was introduced in January 2012, featuring a new vector instruction set called AVX. In order to execute code with high performance and to increase the core's instructions per clock, major changes to the previous core micro-architecture code-named Nehalem have been applied. These changes are highlighted by italic characters in Fig. 2. Since the vector-instruction width has been doubled with AVX (AVX is available with two vector widths: AVX128 and AVX256), also the load port's (port 2) width needs to be doubled. However, doubling a load port's width would impose tremendous changes to the entire chip architecture. In order to avoid this, Intel changed two ports by additionally implementing in each port the other port's functionality as shown for

Fig. 2. Intel Sandy Bridge, changes w.r.t. Intel Nehalem are highlighted with italic characters: trace-cache for decoded instructions, AVX support and physical register file

ports 2 and 3. Through this trick, the load bandwidth has been doubled from 16 Bytes to 32 Bytes per cycle at the price of reduced instruction level parallelism. Changes to the ALUs are straightforward: ports 0, 1 and 5 were simply doubled, and they provide classic SSE functionality for AVX instructions and extensions for blend and mask operations. However, this bandwidth improvement still does not allow for an efficient exploitation of AVX256 instructions as this would require a 64 Bytes per cycle load and 32 Bytes per cycle store bandwidth. This increase will be implemented with the up-coming Haswell micro-architecture [14]. Due to 32 Bytes load bandwidth and the non-destructive AVX128 instruction set, AVX128 codes can often yield the same performance as AVX256 on Sandy Bridge but much better than SSE4.2 on an equally clocked Nehalem chip. This can also be attributed to the fact that 16 Bytes load instructions have a three times higher throughput (0.33 cycles) than 32 Bytes load instructions (here ports 2 and 3 have to be paired and cannot be used independently). According to experiments we did with different applications and kernels using AVX256 on Sandy Bridge, the full performance enhancement of  $2 \times$  speed-up can be just exploited for kernels which can be perfectly register-blocked, e.g. DGEMM [7]. If in contrast only a standard 1D-blocking is possible, roughly a  $1.5-1.6 \times$  speed-up can be achieved in comparison to AVX128 [6].

Up to Nehalem, each unit had dedicated memory for storing register contents for executing operations on them. A so-called out-of-order unit took care of the correctness of the execution pipeline. With AVX, a register allocation in each compute unit of the core would be too expensive in terms of transistors required, therefore a so-called *register file* was implemented: Register contents are stored in a central directory. Shadow registers and pointers allow for an efficient outof-order execution. Furthermore, a general performance enhancement was added to the Sandy Bridge architecture: a cache for decoded instructions. This tracecache like cache boosts the performance of kernels with small loop bodies, such as the force calculation in MD. Furthermore, the Sandy Bridge EP cores feature Intel's SMT implementation called *Hyperthreading Technology* which helps to increase the core's utilization in workload scenarios where the instruction mix is not optimal or the application is suffering from high memory latencies.

#### 3 Implementation

#### 3.1 Vectorization of the Compute Kernel

Since our simulation code is written in C++ and therefore applies standard object-oriented design principles with cells and particles being single entities, we follow an approach of memory organization and vectorization, first sketched in [2]. That work describes, by using a simple proxy application and not the entire ls1 mardyn code base, how the LJ-12-6 force calculation inside a linked cell algorithm can be vectorized on x86 processors. That prototype implementation does not feature important statistical measurements such as virial pressure and potential energy which we added in this work.

The object-oriented memory layout is cache-efficient by design because particles belonging to a cell are stored closely together. However, implementing particles in a cell as a so-called *array of structures (AoS)* forbids easy vectorization, at least without gather and scatter operations (see [5]) which, unfortunately, are not available on Intel Sandy Bridge. Only in simple cases (e.g., updates of one member, etc.) this drawback does not matter, because prefetch logic inside the hardware loads only cache-lines containing data which have to be modified.

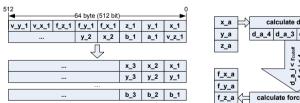

(a) AoS to SoA conversion: In order to allow for efficient vectorization, corresponding elements have to be stored for data streaming access.

(b) *Kernel vectorization*: The vectorization of the LJ-12-6 force calucation is optimized by duplicating one particle and streaming four other particles.

Fig. 3. Optimizing LJ-12-6 force calculation by SoA storage scheme and vectorization

Implementing the LJ-12-6 force calculation on AoS-structures poses major challenges: The upper part of Fig. 3a shows elements scattered across several cache-lines. Taking into account that only a small portion of the members is needed for the force calculation, a temporary *structure of arrays (SoA)* can be constructed in order to address cache-line pollution and vectorization opportunities, illustrated in the lower part of Fig. 3a. Figure 3b sketches the applied vectorization of the LJ-12-6 calculations. In contrast to other methods which vectorize across the spatial coordinates [11–13], the present approach can exploit vector-units of arbitrary length.

In this work, single-precision AVX128 instructions were employed. The calculation is performed on particle pairs, therefore we broadcast-load the required data of one particle in the first register (a), the second register is filled by data from four other particles (1, 2, 3 and 4). Dealing with four particle pairs at once, we can theoretically reduce the number of operations by a factor of four. Since the force calculation may be required for all, some or none of the pairs in the vector register, we need to apply some pre- and post-processing performed by regular logical operations: It has to be determined, if for any particle pair the distance is smaller than  $r_{\rm c}$  (pre-processing), because only then the force calculation has to be executed. If the force calculation has been executed, the calculated results need to be zeroed by a mask for all particle pairs whose distance is larger than  $r_{\rm c}$  (post-processing). In order to ensure vectorization of the kernel we employed intrinsics. Due to the cut-off radius if-condition inside the inner-most loop, current compilers (gcc and icc) deny to vectorize the loop structure iterating over particles in cell-pairs. For the chosen simulation scenario (cut-off radius  $r_{\rm c} = 3.5\sigma$ ) a speed-up of 3 × is possible on a single core by using the proposed SoA-structure and vectorization.

With increasing vector length, this masking technique becomes the major bottleneck. Here, it can easily happen that more elements are being masked than elements which have to be computed. Therefore, moving to a wider vectorinstruction set may result in more instructions being executed. However, if the vector-instruction set features *gather* and *scatter* instructions, this issue can be overcome because only the particle pairs taking part in the interaction are processed, which has been successfully demonstrated by Rapaport with the layeredlinked-cell algorithm [16, 17]. The first x86 processor which offers full gather/scatter support is the so-called Xeon Phi coprocessor. Enabling 1s1 mardyn for Xeon Phi is ongoing research.

A different issue inhibiting the most efficient usage of the Sandy Bridge core is the lack of instruction level parallelism in the compute kernel. The evaluation of distance, potential energy and force on the particles requires significantly more multiplications than additions, thus the ADD unit cannot be fully utilized. Even worse, the calculation of the power-12-term of the LJ-12-6 requires a sequence of dependent multiplications. Therefore, the superscalarity of a Sandy Bridge core can not be exploited optimally, a fact we address by using Hypterthreading Technology as described below.

We restricted ourselves to AVX128 instructions for several reasons. In Section 2.2 we described that Intel Sandy Bridge is not able to handle AVX256 instructions at full speed. This fact would also forbid to use Hyperthreading efficiently as currently ports 2 and 3 inside the core can be used by different threads. Switching to AVX256, these ports are operated in paired mode, available to just

one of both threads. Furthermore, we showed in the outlook of [2] that AVX256 instruction are only beneficial when increasing the cut-off radius. Last but not least we want to ensure that ls1 mardyn runs best on various x86 platforms. Besides Intel Sandy Bridge, AMD Interlagos plays an important role since this chip is used as processor in most of Cray's supercomputers. AMD Interlagos features two 128bit FPUs shared between two integer units. Therefore an AVX128 code is essential for best performance on Interlagos. With the current code base we only expect slight changes when moving to an Interlagos based machine.

#### 3.2 Memory and Utilization Optimizations

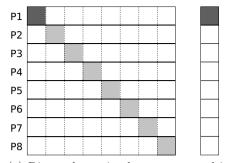

In order to achieve the low memory requirement of only 32 Byte per molecule, we refined the linked-cells algorithm with the sliding window that was introduced in [3]. It is based on the observation that the access pattern of the cells can be described by a sliding window, which moves through the domain. After a cell has been searched for interacting particles for the first time in a time step, its data will be required for several successive force calculations with particles in neighboring cells. If the force calculation proceeds according to the cells' index as depicted in Fig. 4a, these data accesses happen within a short time period, until the interactions with all neighbors have been computed. While the cells in the window are accessed several times, they naturally move in and out of the window in FIFO order.

| 20 | 21 | 22 | ~23 | 24 | 25 | 26 | 27 | 28 | 29 |

|----|----|----|-----|----|----|----|----|----|----|

| 11 | 12 | 13 | 1)  | 15 | 16 | 17 | 18 | 18 | 19 |

| 1  | 2  | 3  | 4   | 5  | 6  | 7  | 8  | 9  | 10 |

(a) Sliding window (cells in bold black frame) in 2D. Particles in cells in the window will be accessed several times, cells 2 through 23 are covered by the window in FIFO order. For the force calculation for the molecules in cell 13, cell 23 is searched for interacting particles for the first time in this iteration. The particles in cell 2 are checked for the last time for interactions.

| 20 | 21 | 22 | ~~~3 | 24 | 25 | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 27 | 28 | 29 |

|----|----|----|------|----|----|-----------------------------------------|----|----|----|

| 11 | 12 | 13 | 1)   | 15 | 16 | 1                                       | 18 | 18 | 19 |

| 1  | 2  | þ  | 4    | 5  | م  | 7                                       | 8  | 9  | 10 |

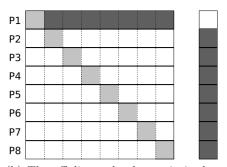

(b) Extension of the sliding window for multi-threading. By increasing the window by 5 cells, two threads can independently work on three cells each: thread 1 works on cells 13, 14, 15; thread 2 works on cells 16, 17, 18. To avoid that threads work on same cells (e. g., thread 1 on the cell pair 15–25, thread 2 on 16–25), a barrier is required after each thread finished its first cell.

Fig. 4. Basic idea of the sliding window algorithm and extension for multi-threading

Particle data outside the sliding window are stored in form of C++ objects in AoS-manner, only with position, velocity and an identifier. Per cell, particle objects are stored in dynamic arrays. When the sliding window is shifted further and covers a new cell, the positions and velocities of the particles in that cell are converted to SoA-representation. Additionally, arrays for the forces have to be allocated. The force calculation is now performed on the particles as described above. When a cell has been considered for the last time during an iteration, its particles are converted back to AoS-layout. Therefore, the calculation of forces, potential energy and virial pressure can be performed memory- and runtimeefficiently on the SoA, while the remaining parts of the simulation code can be kept unchanged according to their object-oriented layout. To avoid the overhead of repeated memory (de-)allocations when particle data in a cell are converted. we initially allocate dynamic arrays fitted to the maximum number of particles per cell for each cell in the window, and reuse that memory. Since the sliding window covers three layers of cells, these buffers consume a comparably small amount of memory, while the vast majority of the particles is stored memoryefficiently. At this point, it becomes apparent that the traversal order imposed by the sliding window also supports cache reusage: when particle data are converted to SoA-representation, that data are placed in the cache and will be reused several times soon after.

In order to reduce the memory requirement to 32 Byte per particle and to further improve the hardware utilization, this algorithm needs two further revisions: the time integration has to be performed on the fly, and opportunity for multi-threading needs to be created. Since the forces are not stored with the molecule objects, the time integration has to be performed during that conversion, i. e., the particles' new positions and velocities have to be calculated at that moment. Nevertheless, the correct traversal of the particles is ensured, because cells that have been converted are not required for the force calculation during this time step any more and the update of the linked-cells data structure, i.e. the assignment of particles to cells, takes place only between two time steps.

As stated above, the LJ-12-6 kernel is not well instruction-balanced, impeding the use of the superscalarity of a Sandy Bridge core. In order to make use of Hyperthreading Technology, we implemented a lightweight shared-memory parallelization. By extending the size of the sliding window as shown in Fig. 4b, two threads can perform calculations concurrently on three independent cells. Exploiting Newtons third law  $F_{ij} = -F_{ji}$  for the force calculation and considering cell pairs only once, it must be avoided that threads work on directly neighboring cells simultaneously. Therefore, a barrier, causing comparably little overhead on a Hyperthreading core, is required after each thread has processed the first of its three cells. This allows the execution of one MPI rank per core with two (OpenMP-)threads to create sufficient instruction level parallelism, leading to a 12% performance improvement.

#### 4 Strong and Weak Scaling on SuperMUC

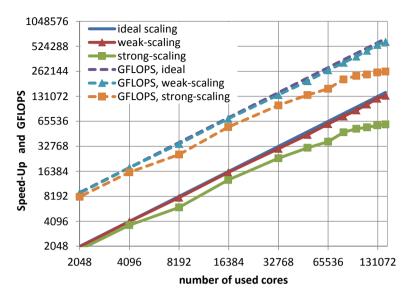

In order to evaluate the performance of the MD simulation code ls1 mardyn, we executed different tests on SuperMUC. With respect to strong scaling behavior, we ran a scenario with  $N = 4.8 \cdot 10^9$  particles, which perfectly fits onto 8 nodes; 18 GB per node are needed for particle data. Fig. 5 shows that a very good

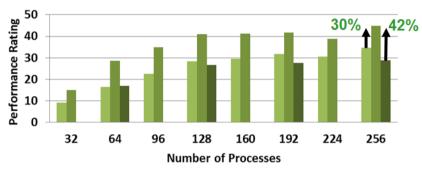

**Fig. 5.** Weak and strong scaling for 2048 to 146016 cores with respect to speed-up and GFLOPS on SuperMUC. Ideal scaling was achieved in case of weak scaling whereas as a parallel efficiency of 42% was obtained in the strong scaling tests. We cut off the plot at 2048 cores, here we obtained a parallel efficiency of 91.1% in case of strong scaling (compared to 128 cores) and 98.6% in case of weak scaling (compared to one core).

scaling was achieved for up to 146016 cores using 292032 threads at a parallel efficiency of 42 % comparing 128 to 146016 cores.

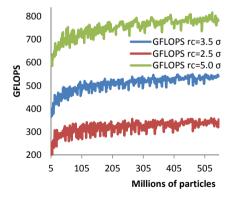

In this case, less than 20 MB  $(5.2 \cdot$  $10^5$  particles) of main memory per node, which fits basically into the processors' caches, are used. This excellent scaling behavior can be explained by analyzing Fig. 6. Here we measured achievable GFLOPS depending on the number of particles simulated on 8 nodes. Already for  $N = 3 \cdot 10^8$  particles (approx. 8% of the available memory) we are able to hit the performance of roughly 550 GFLOPS which we also obtained for  $N = 4.8 \cdot 10^9$ .

It should be pointed out that the performance only decreases slightly for systems containing fewer particles (reducing the particle system size by a factor of 100): for  $N = 10^7$  (which corresponds to the strong scaling setting in case of 146016 cores w.r.t. particles per node) we see a drop by 27% which only increases to the mentioned 58% when moving from 128 to 146016 cores. We have

Fig. 6. GFLOPS dependeding on particle count and cut-off on 128 cores

9

to note that the overall simulation time in this case was 1.5 s for 10 time steps, thereof 0.43 s were communication time. Since 0.43 s are roughly 29% of 1.5 s, it becomes clear that the biggest fractions of the 58% decrease are stemming from low particle counts per process and relatively high communication costs.

Moreover, we performed a weak scaling analysis which is, to our knowledge, the largest MD simulation to date. Due to MPI buffers on all nodes, we were not able to keep the high number of particles per node  $(6.0 \cdot 10^8)$  and were forced to reduce it to  $4.52 \cdot 10^8$ . Particularly, buffers for eager communication turned out to be the most limiting factor. Although we reduced them to a bare minimum (64 MB buffer space for each process), roughly 1 GB per node had to be reserved as we use one MPI rank per core. By keeping Fig. 6 in mind, we know that this slight reduction has no negative impact on the overall performance of our simulation. In case of 146016 cores we were able to run a simulation of  $4.125 \cdot 10^{12}$ particles with one time step taking roughly 40 s. For this scenario, a speed-up of  $133183 \times$  (compared to a single core) with an absolute performance of 591.2 TFLOPS was achieved, which corresponds to 9.4% peak performance efficiency.

These performance numbers can be easily improved by increasing simulation parameters like the cut-off radius  $r_c$  which results in a higher vector-register utilization. However, preceding publications [18, 10, 4] used cut-off radii within the interval  $2.5\sigma < r_c < 5.0\sigma$ . Therefore we restricted ourselves to  $r_c = 3.5\sigma$  in order to ensure fairness, please consult Fig. 6 for a performance comparison of ls1 mardyn for different cutoff radii in this interval.

### 5 Conclusions

In this paper we showed that MD simulations can be scaled up to more than 140000 cores and a multi-trillion  $(4.125 \cdot 10^{12})$  number of particles on modern supercomputers. Due to the sliding window technique, only 32 Bytes are required per particle, and with the help of a shared memory parallelization and a carefully optimized force calculation kernel we achieved 591.2 TFLOPS, which is 9.4% of the system's theoretical peak performance.

We achieved not only perfect weak scaling, but also excellent strong scaling results together with a good performance of the kernel also for comparably small particle numbers per core. These properties are essential for the investigation of large inhomogeneous molecular systems. Such scenarios are characterized by highly heterogeneous particle distributions, which requires a powerful load balancing method implementation. Therefore, we are working on the incorporation of the load balancing from the original **ls1 mardyn** code.

As indicated during the force kernel's discussion, the current kernel implementation suffers from not fully exploited vector-registers. Increasing the net-usage of vector-registers is subject of ongoing research. The most promising instruction set is currently provided by the Intel Xeon Phi coprocessor which features a full blown gather/scatter implementation.

Beside tuning 1s1 mardyn for better performance on emerging architectures, energy efficiency with focus on the energy to solution ratio is an additional research direction, especially when targeting MD scenarios with millions of time steps. Since SuperMUC is capable of dynamic frequency scaling, it provides an optimal testbed for such activities.

## References

- Buchholz, M., Bungartz, H.-J., Vrabec, J.: Software design for a highly parallel molecular dynamics simulation framework in chemical engineering. Journal of Computational Science 2(2), 124–129 (2011)

- Eckhardt, W., Heinecke, A.: An efficient vectorization of linked-cell particle simulations. In: ACM International Conference on Computing Frontiers, Cagliari, pp. 241–243 (May 2012)

- Eckhardt, W., Neckel, T.: Memory-efficient implementation of a rigid-body molecular dynamics simulation. In: Proceedings of the 11th International Symposium on Parallel and Distributed Computing - ISPDC 2012, Munich, pp. 103–110. IEEE (2012)

- 4. Germann, T.C., Kadau, K.: Trillion-atom molecular dynamics becomes a reality. International Journal of Modern Physics C 19(09), 1315–1319 (2008)

- Gou, C., Kuzmanov, G., Gaydadjiev, G.N.: SAMS multi-layout memory: providing multiple views of data to boost SIMD performance. In: Proceedings of the 24th ACM International Conference on Supercomputing, ICS 2010, pp. 179–188. ACM, New York (2010)

- Heinecke, A., Pflüger, D.: Emerging architectures enable to boost massively parallel data mining using adaptive sparse grids. International Journal of Parallel Programming 41(3), 357–399 (2013)

- Heinecke, A., Trinitis, C.: Cache-oblivious matrix algorithms in the age of multiand many-cores. Concurrency and Computation: Practice and Experience (2013); accepted for publication

- Horsch, M., Vrabec, J., Bernreuther, M., Grottel, S., Reina, G., Wix, A., Schaber, K., Hasse, H.: Homogeneous nucleation in supersaturated vapors of methane, ethane, and carbon dioxide predicted by brute force molecular dynamics. The Journal of Chemical Physics 128(16), 164510 (2008)

- Kabadshow, I., Dachsel, H., Hammond, J.: Poster: Passing the three trillion particle limit with an error-controlled fast multipole method. In: Proceedings of the 2011 Companion on High Performance Computing Networking, Storage and Analysis Companion, SC 2011 Companion, pp. 73–74. ACM, New York (2011)

- Kadau, K., Germann, T.C., Lomdahl, P.S.: Molecular dynamics comes of age: 320 billion atom simulation on bluegene/l. International Journal of Modern Physics C 17(12), 1755–1761 (2006)

- 11. Lindahl, E., Hess, B., van der Spoel, D.: Gromacs 3.0: a package for molecular simulation and trajectory analysis. Journal of Molecular Modeling 7, 306–317 (2001)

- Olivier, S., Prins, J., Derby, J., Vu, K.: Porting the gromacs molecular dynamics code to the cell processor. In: IEEE International Parallel and Distributed Processing Symposium, IPDPS 2007, pp. 1–8 (March 2007)

- Peng, L., Kunaseth, M., Dursun, H., Nomura, K.-i., Wang, W., Kalia, R., Nakano, A., Vashishta, P.: Exploiting hierarchical parallelisms for molecular dynamics simulation on multicore clusters. The Journal of Supercomputing 57, 20–33 (2011)

- 14. Piazza, T., Jiang, H., Hammarlund, P., Singhal, R.: Technology Insight: Intel(R) Next Generation Microarchitecture Code Name Haswell (September 2012)

- 15. Rahimian, A., Lashuk, I., Veerapaneni, S., Chandramowlishwaran, A., Malhotra, D., Moon, L., Sampath, R., Shringarpure, A., Vetter, J., Vuduc, R., Zorin, D., Biros, G.: Petascale direct numerical simulation of blood flow on 200k cores and heterogeneous architectures. In: Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, SC 2010, pp. 1–11. IEEE Computer Society, Washington, DC (2010)

- Rapaport, D.C.: The Art of Molecular Dynamics Simulation. Cambridge University Press (2004)

- Rapaport, D.C.: Multibillion-atom molecular dynamics simulation: Design considerations for vector-parallel processing. Computer Physics Communications 174(7), 521–529 (2006)

- Roth, J., Gähler, F., Trebin, H.-R.: A molecular dynamics run with 5 180 116 000 particles. International Journal of Modern Physics C 11(02), 317–322 (2000)

- Vrabec, J., Kedia, G.K., Fuchs, G., Hasse, H.: Comprehensive study of the vapourliquid coexistence of the truncated and shifted lennard-jones fluid including planar and spherical interface properties. Molecular Physics 104(9), 1509–1527 (2006)

# Up to 700k GPU Cores, Kepler, and the Exascale Future for Simulations of Star Clusters Around Black Holes

Peter Berczik<sup>1,2,3</sup>, Rainer Spurzem<sup>1,3,4</sup>, Shiyan Zhong<sup>1</sup>, Long Wang<sup>4,1</sup>, Keigo Nitadori<sup>5</sup>, Tsuyoshi Hamada<sup>6</sup>, and Alexander Veles<sup>2</sup>

<sup>1</sup> National Astronomical Observatories of China, CAS, Beijing, P.R. China berczik@nao.cas.cn

<sup>2</sup> Main Astronomical Observatory, NASU, Kyiv, Ukraine

<sup>3</sup> Astronomisches Rechen-Institut, ZAH, Univ. of Heidelberg, Germany

<sup>4</sup> Kavli Institute for Astronomy and Astrophysics, Peking University, Beijing, P.R. China

<sup>5</sup> RIKEN Institute, Tokyo, Japan

<sup>6</sup> Nagasaki Advanced Computing Center, Nagasaki, Japan

Abstract. We present benchmarks on high precision direct astrophysical N-body simulations using up to several 100k GPU cores; their soft and strong scaling behaves very well at that scale and allows further increase of the core number in the future path to Exascale computing. Our simulations use large GPU clusters both in China (Chinese Academy of Sciences) as well as in Germany (Judge/Milkyway cluster at FZ Jülich). Also we present first results on the performance gain by the new Kepler K20 GPU technology, which we have tested in two small experimental systems, and which also runs in the titan supercomputer in the United States, currently the fastest computer in the world. Our high resolution astrophysical N-body simulations are used for simulations of star clusters and galactic nuclei with central black holes. Some key issues in theoretical physics and astrophysics are addressed with them, such as galaxy formation and evolution, massive black hole formation, gravitational wave emission. The models have to cover thousands or more orbital time scales for the order of several million bodies. The total numerical effort is comparable if not higher than for the more widely known cosmological N-body simulations. Due to a complex structure in time (hierarchical blocked time steps) our codes are not considered "brute force".

## 1 Introduction

Theoretical numerical modeling has become a third pillar of sciences in addition to theory and experiment (in case of astrophysics the experiment is mostly substituted by observations). Numerical modeling allows one to compare theory with experimental or observational data in unprecedented detail, and it also provides theoretical insight into physical processes at work in complex systems. Similarly, data processing of e.g. astrophysical observations comprises the use of complex software pipelines to bring raw data into a form digestible for observational astronomers and ready for exchange and publication. Required algorithms are, for example, mathematical transformations like Fourier analyses of time series or spatial structures, complex template analyses or huge matrix-vector operations. Here fast access to and transmission of data, too, require supercomputing capacities. However, sufficient resolution of multi-scale physical processes still poses a formidable challenge, such as in the examples of few-body correlations in large astrophysical many-body systems, or in the case of turbulence in physical and astrophysical flows.

We are undergoing a new revolution on parallel processor technologies, and a change in parallel programming paradigms, which may help to advance current software towards the Exaflop/s scale and help better resolving and understanding typical multi-scale problems. The current revolution in parallel programming has been mostly catalyzed by the use of graphical processing units (GPU) for general purpose programming, but it is not clear whether this will remain the case in the future. GPU's have become widely used nowadays to accelerate a broad range of applications, including computational physics and astrophysics, image/video processing, engineering simulations, quantum chemistry, just to name a few [10,25,24,5,15]. GPU's are rapidly emerging as a powerful and cost-effective platform for high performance parallel computing. The GPU Technology Conferences held annually in San Jose (and offsprings in other parts of the  $(world)^{1,2}$  regularly provides a snapshot of the breadth and depth of present day GPU (super)computing applications. Recent GPU's, such as the NVIDIA Kepler K20 Computing Processor, offer 2496 CUDA processor cores and extremely fast on-chip-memory chip, as compared to only 4-8 cores on a standard Intel or AMD CPU. Groups of cores have access to very fast shared memory pieces. A single Kepler Tesla K20 device supports double precision operations fully with a peak speed of about 1 Tflop/s (double precision) and a little less than 4 Tflop/s (single precision). In this paper we use a code which still uses the single precision operations, which was originally developed for previous GPU architectures, which had no or very inefficient support for double precision. We circumvented this by emulation of a few critical parts of the code with the double precision operations "emulation" using a combination of few single precision operations (see: [22]). More details can be found in the Ph.D. thesis of one of us (Keigo Nitadori), "New approaches to high-performance N-body simulations with high-order integrator, new parallel algorithm, and efficient use of SIMD hardware", Univ. of Tokyo, 2009.

Dynamical modeling of dense star clusters with and without massive black holes poses extraordinary physical and numerical challenges. One of them is that gravity cannot be shielded such as electromagnetic forces in plasmas, therefore long-range interactions go across the entire system and couple non-linearly with small scales. High-order integration schemes and direct force computations for large numbers of particles have to be used to properly resolve all physical processes in the system. On small scales inevitably correlations form already early

<sup>&</sup>lt;sup>1</sup> http://www.gputechconf.com

<sup>&</sup>lt;sup>2</sup> http://www.nvidia.com/gtc

during the process of star formation in a molecular cloud. Such systems are dynamically extremely rich, they exhibit a strong sensitivity to initial conditions and regions of phase space with deterministic chaos.

Direct N-Body Codes in astrophysical applications for galactic nuclei, galactic dynamics and star cluster dynamics usually have a kernel in which direct particle-particle forces are evaluated. Astrophysical structures can develop also the high density contrasts. High-density regions created by gravitational collapse co-exist with low-density fields, as is known from structure formation in the universe or the turbulent structure of the interstellar medium. A high-order time integrator in connection with individual, hierarchically blocked time steps for particles in a direct N-body simulation provides the best compromise between accuracy, efficiency and scalability [21,1,2,23,14]. With GPU hardware up to a few million bodies could be reached for our models [6,7,12]. Note that while [11]already mention that their algorithm can be used to compute gravitational forces between particles to high accuracy, [21] find that the self-adaptive hierarchical time-step structure inherited from Aarseth's codes improves the performance for spatially structured systems by  $\mathcal{O}(\mathcal{N})$  - it means that at least for astrophysical applications with high density contrast FMM is not a priori more efficient than direct N-body (which sometimes is called "brute force", but that should only be used if a shared time step is used, which is not the case in our codes). One could explain this result by comparing the efficient spatial decomposition of forces (in FMM, using a simple shared time step) with the equally efficient temporal decomposition (in direct N-body, using a simple spatial force calculation). Some exemplary research papers on dynamics of black holes in dense stellar systems, which illustrate the application domain of our code, can be found in [16,17].

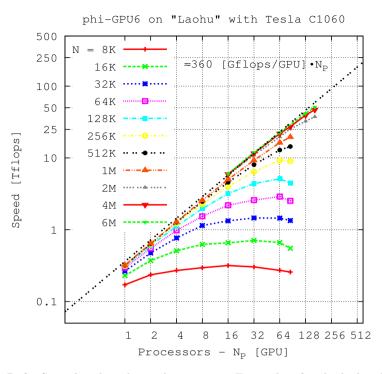

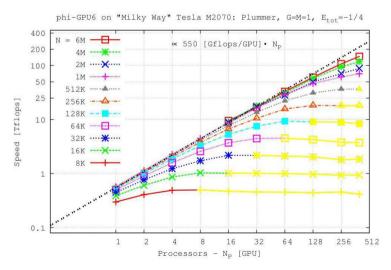

## 2 Hardware

We present here results obtained from our GPU clusters in China and Germany: the Laohu at NAOC/CAS in Beijing with 85 Dual Intel Xeon nodes and 170 NVIDIA Tesla C1060 GPU's), the Mole-8.5 at IPE/CAS in Beijing with 362 Dual Intel Xeon nodes integrating totally 2088 GPU's (NVIDIA Tesla C2050), and the Milkyway Judge cluster at Jülich supercomputing center (JSC) in Germany, with 200 Dual Intel Xeon nodes and 400 NVIDIA Tesla M2070 GPU's. In addition to that a first benchmark on a recently installed cluster with GPU's based on the Kepler architecture is added.

## 3 Software

The test code which we use for benchmarking on our clusters is a direct Nbody simulation code for astrophysics, using a high order Hermite integration scheme and individual block time steps (the code supports time integration of particle orbits with 4<sup>th</sup>, 6<sup>th</sup> and 8<sup>th</sup> order schemes). The code is called  $\varphi$ GPU, it has been developed from our earlier published version  $\varphi$ GRAPE [14] (which originally use the **GRAPE6a** cards as a hardware accelerator for the calculus of the particles mutual gravitational interaction). The code is fully parallelized using the MPI library, and on each node using many cores of the special hardware. The code was mainly developed and tested by two of us (Keigo Nitadori and Peter Berczik, see also [13]) and is based on an earlier C code version<sup>3</sup> for GRAPE6a clusters [14]. The new code is written from scratch in C++ and based on [22] earlier CPU serial *N*-body code (yebisu). More details and also the  $\varphi$ GPU code public version will be published in an upcoming publication [8].

The MPI parallelization was done in the same "j" particle parallelization mode as in the earlier  $\varphi$ GRAPE code [14]. All the particles are divided equally between the working nodes (using the MPI\_Bcast() commands) and in each node we calculate only the fractional forces for the, so call, "active" – "i" particles at the current time step. Due to the hierarchical block time step scheme the average number  $\langle N_{act} \rangle$  of active particles (due for a new force computation at a given time level) is usually small compared to the total particle number N, but its actual value can vary from  $1 \dots N$ . The full forces from all the particles acting on the active particles we get after using the global MPI\_Allreduce() communication routines.

The present version of  $\varphi$ GPU code we used and tested only with the recent GNU compilers (ver. 4.x). We use native GPU support and direct code access to the GPU using only the NVIDIA native CUDA library<sup>4</sup>. We use CUDA 3.2 and 4.0, the code is rather robust against the different CUDA versions. One first test was done with a single Kepler K20 and CUDA 5.0 (see Fig. 4). Multi GPU support is achieved through MPI parallelization. Each MPI process uses only a single GPU, but we can start two MPI processes per node (to use effectively for example the dual quad core CPU's and the multi GPU's in the NAOC, CAS and IPE, CAS GPU cluster). In this case each MPI process uses its own GPU inside the node. Communication always (even for the processes inside one node) works via MPI. We do not use any of the possible OMP (multi-thread) features of recent gcc 4.x compilers inside one node.

The  $\varphi$ GPU code uses a blocked hierarchical individual time step scheme (HITS) and a Hermite high order time integration scheme of at least 4<sup>th</sup> order for integration of the equation of motions for all particles [20]. At every time we integrate the motion only for  $\langle N_{\rm act} \rangle$  particles, a number which is usually much less compared to the total number of particles N. The average value  $\langle N_{\rm act} \rangle$  depends on the details of the algorithm and on the particle configuration integrated. According to a simple theoretical estimate it is  $\langle N_{\rm act} \rangle \propto N^{2/3}$  [18], but the real value of the exponent deviates from 2/3, depending on the initial model and details of the time step choice [21] (see our actual measurements given by equation (8).

For the time step itself first the so-called individual "Aarseth" time step is used [1]:

<sup>&</sup>lt;sup>3</sup> ftp://ftp.ari.uni-heidelberg.de/staff/berczik/phi-GRAPE/

<sup>&</sup>lt;sup>4</sup> http://www.nvidia.com/object/cuda\_home\_new.html

$$\Delta t = \sqrt{\eta \; \frac{|\boldsymbol{a}||\boldsymbol{a}^{(2)}| + |\boldsymbol{a}^{(1)}||^2}{|\boldsymbol{a}^{(1)}||\boldsymbol{a}^{(3)}| + |\boldsymbol{a}^{(2)}|^2}},\tag{1}$$

where  $\boldsymbol{a}^{(k)}$  is the  $k^{\text{th}}$  derivative of acceleration and  $\eta$  is a parameter which controls the accuracy. Usually, a value around 0.02 is used for  $\eta$ . This time step choice is known to work well with fourth-order schemes, but it is less efficient for higher-order schemes [19]. In our  $\varphi$ GPU code we use the generalized "Aarseth" type criterion already proposed in the paper [22]:

$$\Delta t = \eta_p \, \left(\frac{A^{(1)}}{A^{(p-2)}}\right)^{1/(p-3)} \tag{2}$$

where

$$A^{(k)} = \sqrt{|\boldsymbol{a}^{(k-1)}||\boldsymbol{a}^{(k+1)}| + |\boldsymbol{a}^{(k)}|^2}.$$

(3)

Here, p is the order of the integrator. We moved the accuracy parameter  $\eta_p$  out of the fractional power, so that the time step is directly proportional to  $\eta_p$ . The enumerator is the same as that for the Aarseth criterion for the fourth-order scheme, and for the denominators we used the terms of highest orders available. The fractional power is chosen to give the correct dimension of time.

For efficient parallelization and vectorization we introduce the block time step scheme [20]. Particles are grouped together in time by replacing their original individual time steps  $\Delta t_i$  with a common block time step  $\Delta t_{i,b} = (1/2)^n$ , where n is chosen according to

$$\left(\frac{1}{2}\right)^n \le \Delta t_i < \left(\frac{1}{2}\right)^{n-1}.$$

(4)

The commensurability is enforced by requiring that  $t_i/\Delta t_i$  be an integer.

For the performance analysis we run the code for a fixed physical time span, one time unit (TU) in our dimensionless N-body units, which is approximately one orbital time around the half-mass radius of the system. We count time steps and floating point operations and also analyse the cumulative number  $\sum N_{\text{act}}$ of active particles, as well as the average number of active particles during at intermediate time points  $\langle N_{\text{act}} \rangle$ .  $n_{\text{ts}}$  is the number of advancements of time in the simulation:

$$\langle N_{\rm act} \rangle \equiv \frac{\sum N_{\rm act}}{n_{\rm ts}} \tag{5}$$

Empirically, we get the following best fits for the number of steps:

$$n_{\rm ts}(4^{\rm th}) \propto N^{0.575}, n_{\rm ts}(6^{\rm th}) \propto N^{0.585}, n_{\rm ts}(8^{\rm th}) \propto N^{0.581}.$$

(6)

$$\sum_{nact} N_{act}(4^{th}) \propto N^{1.185}, \\ \sum_{nact} N_{act}(6^{th}) \propto N^{1.259}, \\ \sum_{nact} N_{act}(8^{th}) \propto N^{1.273}.$$

(7)

Hence:

These numbers depend on several parameters, such as the chosen time step parameter, and the density and velocity distribution of the particles (here we use a rather simple example of a Plummer model, which has a homogeneous core and a halo with decreasing density outside). For the more detail study of this dependences we refer the reader to the paper [21] and also to our more detailed analyis in preparation[8].

In a simple theoretical model our code should asymptotically scale with  $N^2$ , so we would expect  $N \cdot \langle N_{\text{act}} \rangle \cdot n_{\text{ts}} \propto N^2$ . However, the measurements (see equation (7)) deliver a slightly smaller number  $\langle N_{\text{act}} \rangle \cdot n_{\text{ts}} \propto N^{1+x}$ , with  $x_{4^{\text{th}}} = 0.18$ ,  $x_{6^{\text{th}}} = 0.26$  and  $x_{8^{\text{th}}} = 0.27$ , which is in good agreement with the earlier results of [21].

#### 4 Results of Benchmarks

In this section we describe some results of our extensive performance testing of the  $6^{th}$  order HITS scheme on several different GPU clusters. The wall clock time  $T_{\text{TOT}}$  needed for our particle based algorithm to advance the simulation by the fixed time integration interval (1 TU, see definition above) is decomposed into several components:

$$T_{\rm TOT} = T_{\rm host} + T_{\rm GPU} + T_{\rm comm} + T_{\rm MPI} \tag{9}$$

We have from left to right: the computing time spent on the host –  $T_{\rm host}$ , on the GPU –  $T_{\rm GPU}$ , the communication time to send data between host and GPU –  $T_{\rm comm}$ , and the communication time for MPI data exchange between the nodes –  $T_{\rm MPI}$ . In our present implementation all components are blocking, so there is no hiding of communication. This could be improved in further code versions, but for now it eases profiling.

We use a detailed timing model for the determination of the wall clock time needed for different components of our code on CPU and GPU, which is then fitted to the measured timing data. Its full definition is given in Table. 1.

In practice we see that only two terms play the dominant role ( $\sim 90\%$  of the time) in the understanding of the strong and weak scaling behavior of our code. These are the:

- Force computation time (on GPU) -  $T_{\text{GPU}}$ :  $n_{\text{ts}} \cdot \mathcal{O}(N \cdot \langle N_{\text{act}} \rangle / N_{\text{GPU}}).$  Table 1. Breaking down the computational tasks in a parallel direct N-body code with individual hierarchical block time steps. At every block time step level we denote  $\langle N_{\rm act} \rangle \leq N$  particles, which should be advanced by the high order corrector as active or "i" particles, while the field particles, which exert forces on the "i" particles to be computed are denoted as "j" particles. Note that the number of "j" particles in our present code is always  $N/N_{\rm GPU}$  (in each node, where Ngpu is the number of GPU's used for the simulation). We also have timing components for low-order prediction of all "j" particles and distinguish communication of data from host to GPU and return, and through the MPI message passing network.

| Components of our timing model for $\varphi$ GPU code. One time step integration |                                                                          |                 |  |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------|--|--|--|--|

| task                                                                             | expected scaling                                                         | timing variable |  |  |  |  |

| active particle determination                                                    | $\mathcal{O}(N_{\mathrm{act}}\log(N_{\mathrm{act}}))$                    | $T_{\rm host}$  |  |  |  |  |

| all particle prediction                                                          | $\mathcal{O}(N/N_{ m GPU})$                                              | $T_{\rm host}$  |  |  |  |  |

| active ("i") particle prediction                                                 | $\mathcal{O}(N_{ m act})$                                                | $T_{\rm host}$  |  |  |  |  |

| "j" part. send. to GPU                                                           | $\mathcal{O}(N/N_{ m GPU})$                                              | $T_{\rm comm}$  |  |  |  |  |

| "i" part. send. to GPU                                                           | $\mathcal{O}(N_{ m act})$                                                | $T_{\rm comm}$  |  |  |  |  |

| force computation on GPU                                                         | $\mathcal{O}(N \cdot N_{ m act}/N_{ m GPU})$                             | $T_{\rm GPU}$   |  |  |  |  |

| receive the force from GPU                                                       | $\mathcal{O}(N_{ m act})$                                                | $T_{\rm comm}$  |  |  |  |  |

| MPI global communication                                                         | $\mathcal{O}((\tau_{\text{lat}} + N_{\text{act}}) \log(N_{\text{GPU}}))$ | $T_{\rm MPI}$   |  |  |  |  |

| correction/advancing "i" particle                                                | $\mathcal{O}(N_{ m act})$                                                | $T_{\rm host}$  |  |  |  |  |

- Message passing communication time -  $T_{\text{MPI}}$ :  $n_{\text{ts}} \cdot \mathcal{O}((\tau_{\text{lat}} + \langle N_{\text{act}} \rangle) \log(N_{\text{GPU}})).$

Within the  $T_{\text{MPI}}$  we can distinguish a bandwidth dependent part (scaling as  $\langle N_{\text{act}} \rangle \cdot \log(N_{\text{GPU}})$ ) and a latency dependent part (scaling as  $\tau_{\text{lat}} \cdot \log(N_{\text{GPU}})$ ).

Hence, for this short paper we only discuss the simplified form of the equation (9):

$$T_{\rm TOT} \approx T_{\rm GPU} + T_{\rm MPI}$$

(10)

or:

$$T_{\rm TOT} \approx \frac{\alpha N \sum N_{\rm act}}{N_{\rm GPU}} + \beta (n_{\rm ts} \tau_{\rm lat} + \sum N_{\rm act}) \log(N_{\rm GPU})$$

(11)

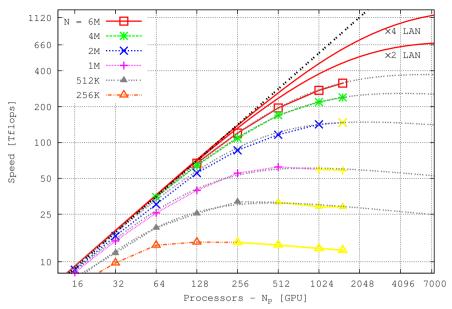

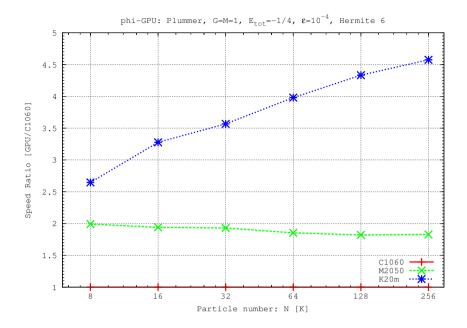

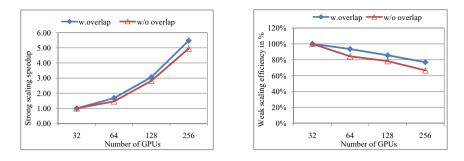

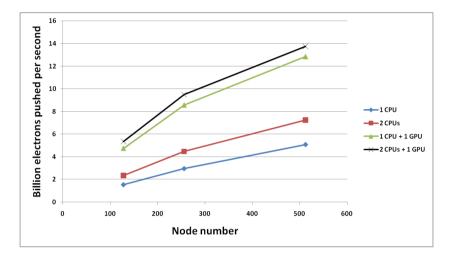

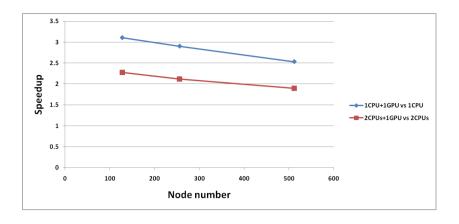

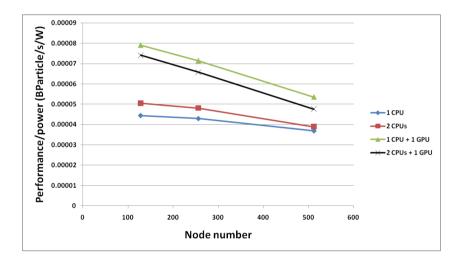

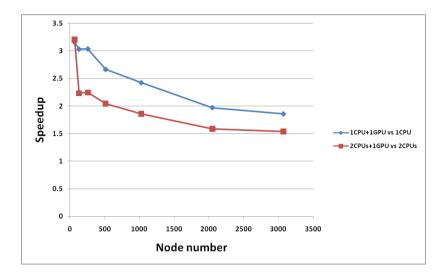

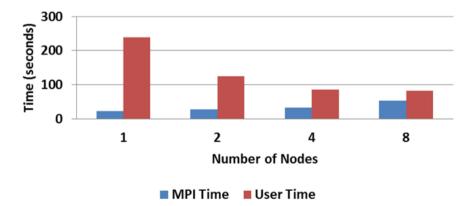

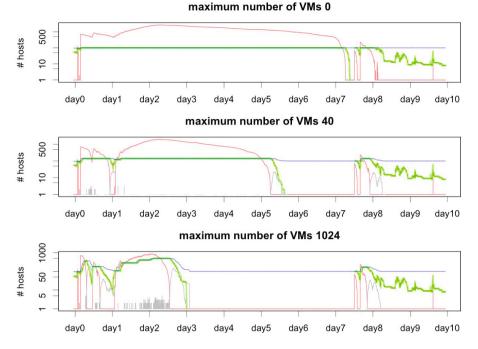

The latency is only relevant for a downturn of efficiency for strong scaling at relatively large numbers of  $N_{\rm GPU}$ . Starting in the strong scaling curves from the dominant term at small  $N_{\rm GPU}$  there is a linearly rising part in Fig. 1., just the force computation on GPU, while the turnover to a flat curve is dominated by the time of MPI communication between the computing nodes –  $T_{\rm MPI}$ .

To find a model for our performance measurements we use the ansatz:

$$P = \frac{\text{(total flop operations)}}{T_{\text{TOT}}} \approx \frac{\gamma \cdot N \cdot \sum N_{\text{act}}}{T_{\text{TOT}}}$$

(12)

where  $T_{\text{TOT}}$  is the computational wall clock time needed to integrate the system for 1 TU. Here  $\gamma$  defines how many floating point operations our particular Hermite scheme requires per particle per interaction per step. Based on the detail flop count (see Table. 1. in [22]) we have:  $\gamma_{4^{\text{th}}} = 60$ ,  $\gamma_{6^{\text{th}}} = 97$  and  $\gamma_{8^{\text{th}}} = 144$ .

Replacing here the  $T_{\text{TOT}}$  with the approximation from equation (11) we have:

$$P \approx \frac{\gamma \ N \ \sum N_{\rm act}}{\frac{\alpha N \sum N_{\rm act}}{N_{\rm GPU}} + \beta (n_{\rm ts} \tau_{\rm lat} + \sum N_{\rm act}) \log(N_{\rm GPU})}$$

(13)

The reader with interest in more detail how this formula can be theoretically derived for general purpose parallel computers is referred to [9]. The  $\alpha$ ,  $\beta$  and  $\tau_{\text{lat}}$  are hardware time constants for the floating point calculation on GPU, for the bandwidth of the interconnect hardware used for message passing and its latency, respectively.

Putting to the equation (13) our earlier power approximations for the  $n_{\rm ts}$  and  $\sum N_{\rm act}$  as a function of total particle numbers N (see equations (6) and (7)) we get P as a function only of N and  $N_{\rm GPU}$ :

$$P \approx \frac{\gamma \ N^{2+x}}{\frac{\alpha N^{2+x}}{N_{\rm GPU}} + \beta (N^{0.33+x} \tau_{\rm lat} + N^{1+x}) \log(N_{\rm GPU})}$$

(14)

The parameter x = 0.26 is a particular result for our case of the 6<sup>th</sup> order HITS and the particular initial model used for the *N*-body system, virial Plummer's model as in [21].

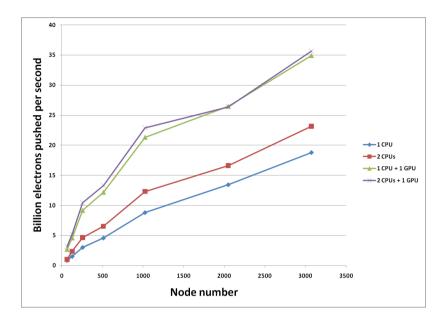

Comparison of the functional form of Eq. 14 yields to a very good match for x = 0.26, as can be seen in Fig. 1. The dotted gray lines for 0.5M, 1M, 2M, 4M and 6M particles show our approximation formula results. The real maximum performance data which we get for the largest 1536 GPU simulations (using in total about 700k GPU cores) for these above particle numbers are (approximately): 29 Tflop/s, 58 Tflop/s, 147 Tflop/s, 239 Tflop/s and 315 Tflop/s.

The parameters  $\alpha$ ,  $\beta$  and  $\tau_{\text{lat}}$  can be determined for each particular hardware used. The timing formula (14) can then be used to approximate our  $\varphi$ GPU 6<sup>th</sup> order code calculation "speed" for any other number of particles, GPU's, or different hardware parameters (possible faster MPI LAN on the other GPU clusters).

For example, on the Mole-8.5 system, we see, that for N = 6M particles if we are using  $N_{\rm GPU} = 2000$  GPU cards we expect to get  $\approx 330$  Tflop/s (see: Fig. 1.). If we use our scaling formula for the much higher node-to-node bandwidth (4 times faster MPI LAN) of the Tianhe-1A<sup>5</sup> system at National Supercomputing Center, Tianjin, China (this is the number one supercomputer according to the Top500 list of November 2010, with  $\sim 7000$  NVIDIA Fermi Tesla C2050 GPU's and 160 Gbit/s node-to-node bandwidth) we can possibly reach sustained performance of  $\sim 1.1$  Petaflop/s (see the faster LAN approximation lines on: Fig. 1.). This is subject of our near future research application.

To our knowledge the direct N-body simulation with four million and six million bodies in the framework of a so-called Aarseth style high precision N-body

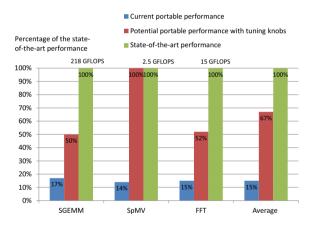

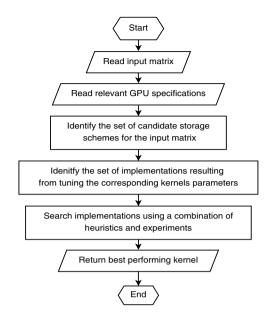

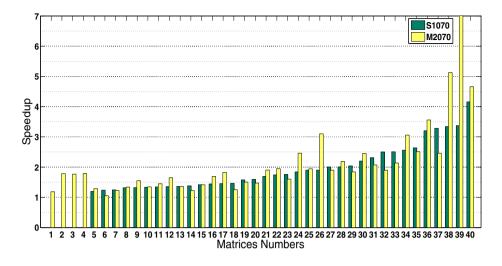

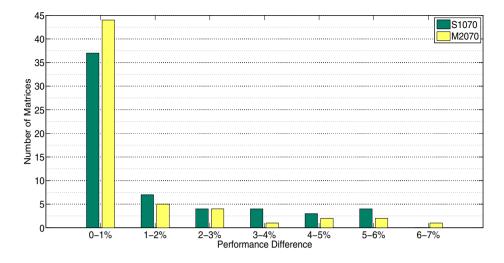

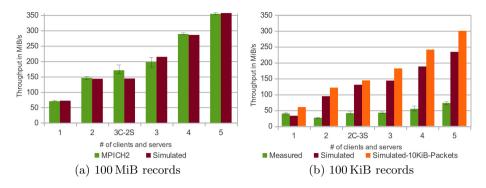

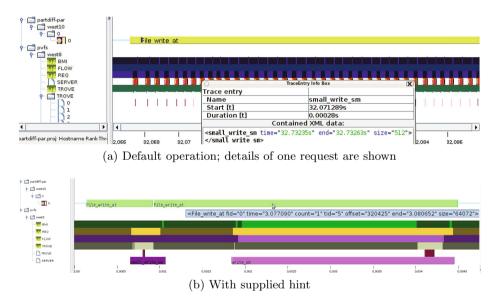

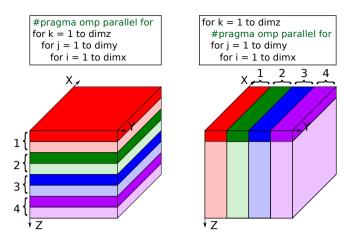

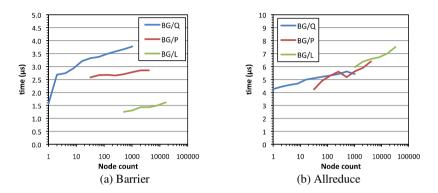

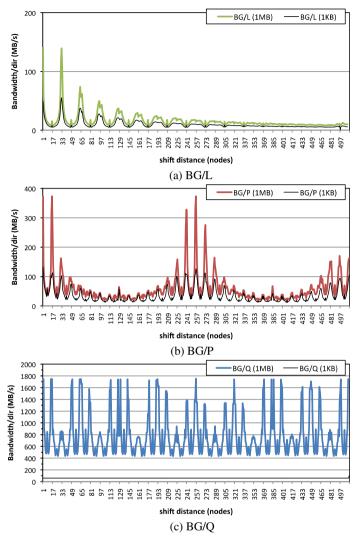

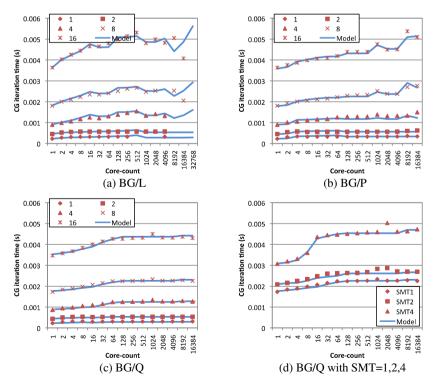

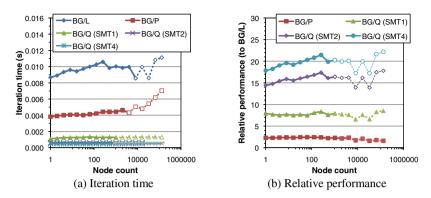

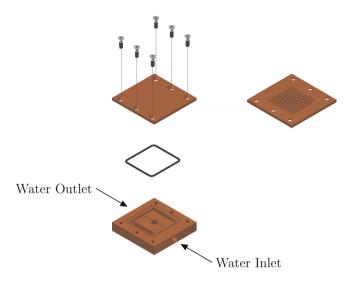

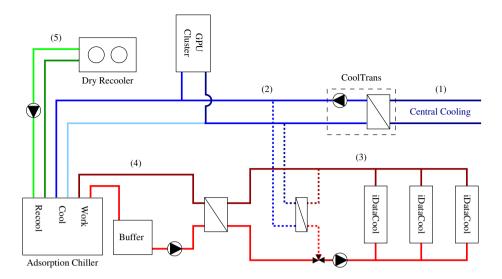

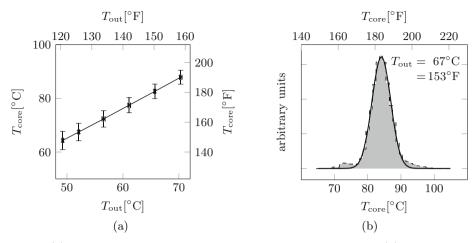

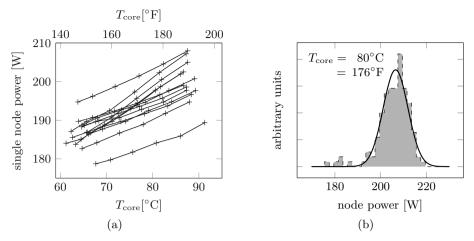

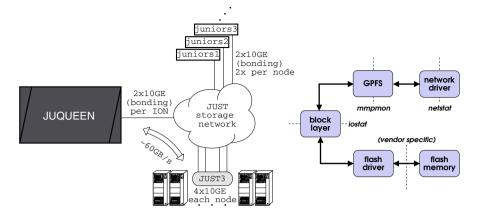

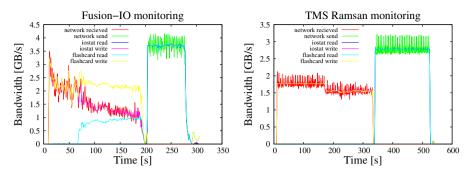

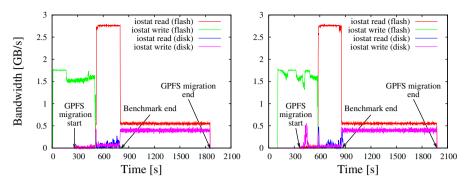

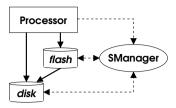

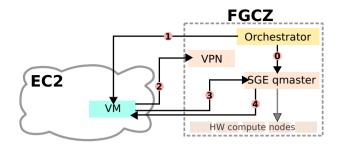

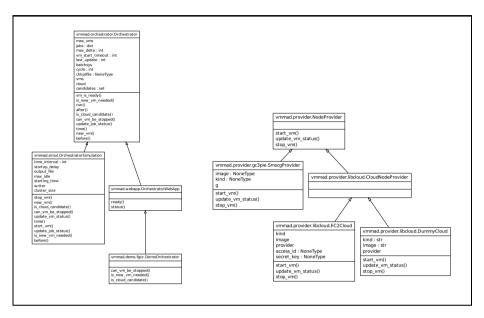

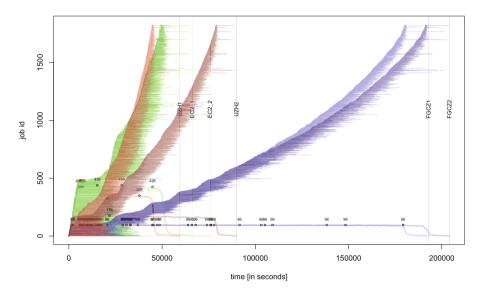

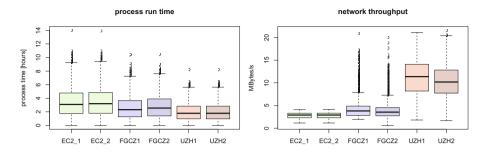

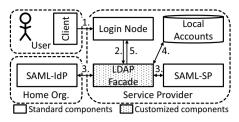

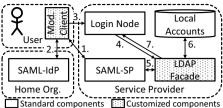

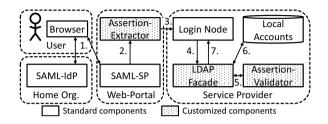

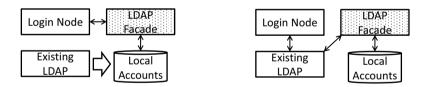

<sup>&</sup>lt;sup>5</sup> http://en.wikipedia.org/wiki/Tianhe-I#Tianhe-1A