Alexey Cheptsov · Steffen Brinkmann José Gracia · Michael M. Resch Wolfgang E. Nagel *Editors*

# Tools for High Performance Computing 2012

Tools for High Performance Computing 2012

Alexey Cheptsov • Steffen Brinkmann José Gracia • Michael M. Resch Wolfgang E. Nagel Editors

# Tools for High Performance Computing 2012

*Editors* Alexey Cheptsov Steffen Brinkmann José Gracia Michael M Resch Höchstleistungsrechenzentrum, Stuttgart (HLRS) Universität Stuttgart Stuttgart Germany

Wolfgang E Nagel Zentrum für Informationsdienste, und Hochleistungsrechnen (ZIH) Technische Universität Dresden Dresden Germany

*Front cover figure*: Simulation of waterflow through a Francis-runner. Illustration by Stellba Hydro GmbH & Co KG, Eiffelstr. 4, 89542 Herbrechtingen, Germany.

ISBN 978-3-642-37348-0 ISBN 978-3-642-37349-7 (eBook) DOI 10.1007/978-3-642-37349-7 Springer Heidelberg New York Dordrecht London

Library of Congress Control Number: 2013940607

Mathematics Subject Classification (2010): 68M20, 65Y20, 65Y05

#### © Springer-Verlag Berlin Heidelberg 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

The latest advances in the high-performance computing (HPC) hardware, such as increased capabilities of a single NUMA node or heterogeneous architectures combining traditional CPU nodes with accelerators, have significantly raised the level of principally available compute performance. At the same time, the growing hardware capabilities of modern supercomputing architectures have caused an increasing complexity of the parallel application development technology. While a number of new programming paradigms, e.g., task-based parallelization and data-driven programming frameworks, have been introduced to fully exploit the available compute resources, very little has been done in terms of tools for performance optimization and debugging for new programming models nor for the latest generation of hardware.

Despite numerous efforts to improve and simplify application development, there is still a lot of manual tuning work required in order to take full advantage of modern HPC architectures. The process of identifying and eliminating performance issues, ranging from simple memory leaks to inefficient design of communication patterns, is very difficult, unless special tools are used. The HPC tools for debugging, performance analysis, and optimization of parallel applications make a major contribution to development of the robust and efficient parallel software.

In order to enable a technology exchange and cross-fertilization in the optimization techniques and development approaches across the HPC tools' developers, the Center for Information Services and High Performance Computing of the University of Dresden (ZIH-TUD)<sup>1</sup> and the High-Performance Computing Center Stuttgart (HLRS)<sup>2</sup> jointly organize the International Parallel Tools Workshop. The workshop is an annual event, which addresses challenges in parallel software performance assurance and discusses novel trends in HPC tools development.

The workshop has two major goals. The first is serving as discussion forum for tool developers on the latest advances in performance analysis techniques and

<sup>&</sup>lt;sup>1</sup>http://tu-dresden.de/die\_tu\_dresden/zentrale\_einrichtungen/zih/

<sup>&</sup>lt;sup>2</sup>http://www.hlrs.de/

software technologies for them. Approaches of eliminating typical performance issues in complex application scenarios by coupling techniques used in different tools were of a special interest for the last workshop's edition. The second goal is to offer the users of parallel tools a unique opportunity to gain a consolidated outlook on state-of-the-art HPC tools. The workshop has proved successful among the application providers, who get an opportunity to have a discussion with the other developers sharing similar performance issues or establish new contacts with tools' developers. On the other hand, the users' feedback helps tools' developers define obstacles to newly raising performance issues and identify engineering or research approaches to overcome them.

This book comprises a continuation of a successful series of publications that started in 2007. It contains contributed papers presented at the 6th International Parallel Tools Workshop,<sup>3</sup> held 25–26 September 2012 in Stuttgart, Germany. The workshop's audience represent leading scientific and industrial organizations worldwide. The presentations covered different aspects of the software optimization, ranging from parallel debugging to complex performance data visualization technology. More than ten different tools were addressed in workshop presentations or hands-on tutorials.

Along with the newest features of the well-known tools, such as Vampir (a performance analysis framework for a wide range of parallel applications) or DDT (a debugging framework with a big set of extensive analysis features), the book introduces new tools which were presented for the first time in the Parallel Tools series, e.g., Temanejo (a debugging environment for StarSs) or MemPin (an automatic memory detection tool for MPI applications). The book's material is organized in four sections: Debugging, Automatic Error Detection, Performance Analysis and Optimization, and Performance Data Visualization.

We believe that the presented material offers a comprehensive outlook on the mainstream application analysis and optimization technology in the highperformance computing domain for both categories of readers – parallel tools' developers and developers of parallel applications.

Stuttgart, Germany February 2013 Alexey Cheptsov Steffen Brinkmann José Gracia Michael M. Resch Wolfgang E. Nagel

<sup>&</sup>lt;sup>3</sup>http://toolsworkshop.hlrs.de/2012/

# Contents

# Part I Debugging

| Deb  | ugging at Scale with Allinea DDT                              | 3  |

|------|---------------------------------------------------------------|----|

| Davi | id Lecomber and Patrick Wohlschlegel                          |    |

| 1    | Why Scalability Matters for Debugging                         | 3  |

| 2    | The Ability to Debug at-Scale Changes Everything              | 4  |

| 3    | How Allinea DDT Helps to Fix Bugs                             | 5  |

| 4    | Understanding Multiple Processes                              | 5  |

| 5    | Simple and Effective Process Control                          | 6  |

| 6    | Smart Highlighting and Sparklines                             | 7  |

| 7    | Searching Data Sets                                           | 8  |

| 8    | Visualizing Large Data Sets in Real-Time                      | 9  |

| 9    | Deadlocks                                                     | 10 |

| 10   | Memory Debugging                                              | 11 |

| 11   | Summary                                                       | 11 |

| 12   | Further Readings                                              | 12 |

| Task | C Debugging with TEMANEJO                                     | 13 |

|      | fen Brinkmann, José Gracia, and Christoph Niethammer          |    |

| 1    | Introduction                                                  | 13 |

| 2    | What Debugging Means in the Context of Task-Based Parallelism | 15 |

| 3    | The Debugging Process                                         | 16 |

|      | 3.1 Communication                                             | 16 |

|      | 3.2 Graph Display                                             | 17 |

|      | 3.3 Execution Control                                         | 20 |

| 4    | Conclusion                                                    | 20 |

| Refe | erences                                                       | 21 |

## Part II Automatic Error Detection

| MP   | I Runtime Error Detection with MUST: Advanced Error Reports | 25 |

|------|-------------------------------------------------------------|----|

| Joac | him Protze, Tobias Hilbrich, Bronis R. de Supinski,         |    |

| Mar  | tin Schulz, Matthias S. Müller, and Wolfgang E. Nagel       |    |

| 1    | Introduction                                                | 25 |

| 2    | MUST                                                        | 27 |

| 3    | Shortcoming of Current Error Views                          | 29 |

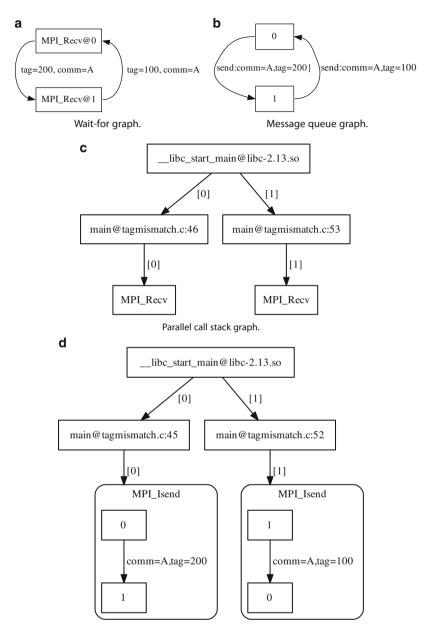

|      | 3.1 Example 1: Pinpointing Deadlocks                        | 29 |

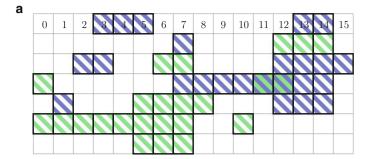

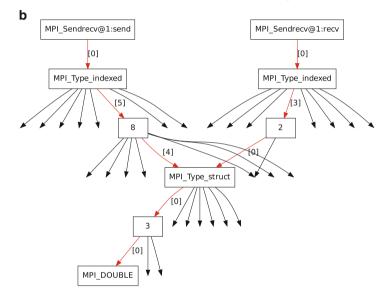

|      | 3.2 Example 2: Viewing Datatype Related Problems            | 31 |

| 4    | Deadlock View in MUST                                       | 31 |

| 5    | Type Tree View                                              | 33 |

| 6    | Related Work                                                | 35 |

| 7    | Conclusion                                                  | 36 |

| Refe | erences                                                     | 37 |

| Adv  | anced Memory Checking for MPI Parallel Applications         |    |

|      | ng MemPin                                                   | 39 |

|      | ing Fan, Rainer Keller, and Michael Resch                   | 39 |

| 3mg  | Introduction                                                | 40 |

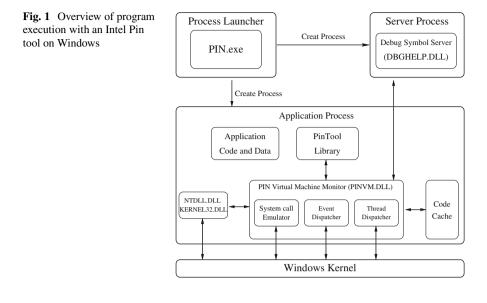

| 2    | Overview of Intel Pin                                       | 40 |

| 2    |                                                             |    |

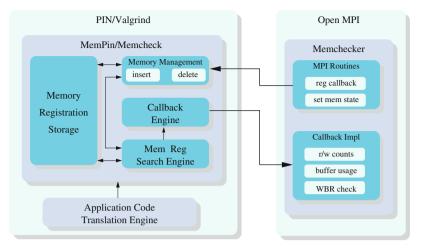

| 3    | Design and Implementation                                   | 42 |

|      | 3.1 MemPin                                                  | 43 |

|      | 3.2 Integration of MemPin with Open MPI                     | 44 |

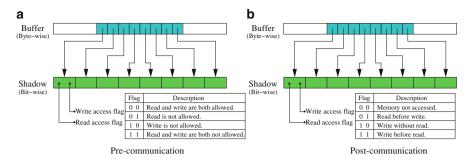

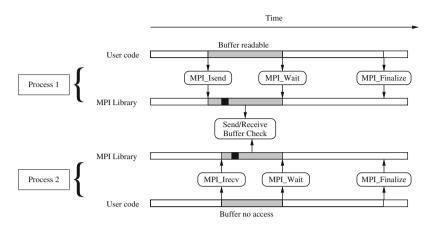

| 4    | Memory Checks in Parallel Application                       | 46 |

|      | 4.1 Pre-communication Checks                                | 46 |

|      | 4.2 Post-communication Checking                             | 47 |

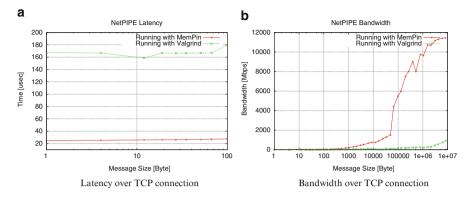

| 5    | Performance Comparison                                      | 48 |

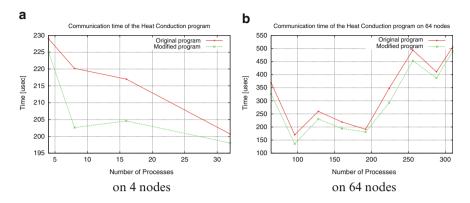

| 6    | 2D Heat Conduction Program with MemPin                      | 49 |

| 7    | Conclusion                                                  | 51 |

| Refe | erences                                                     | 52 |

## Part III Performance Analysis and Optimization

| Gen  | eric S | Support for Remote Memory Access Operations        |    |

|------|--------|----------------------------------------------------|----|

| in S | core-  | P and OTF2                                         | 57 |

| And  | reas 1 | Knüpfer, Robert Dietrich, Jens Doleschal,          |    |

| Mar  | kus C  | Beimer, Marc-André Hermanns, Christian Rössel,     |    |

| Ron  | ny Ts  | chüter, Bert Wesarg, and Felix Wolf                |    |

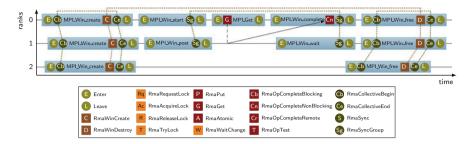

| 1    | Intro  | duction                                            | 57 |

| 2    | Over   | view of Score-P and OTF2                           | 58 |

|      | 2.1    | The Score-P Instrumentation and Measurement System | 59 |

|      | 2.2    | The Open Trace Format 2                            | 59 |

|      | 2.3    | Existing Event Record Types                        | 60 |

|      | 2.4    | Current and Future Directions                      | 60 |

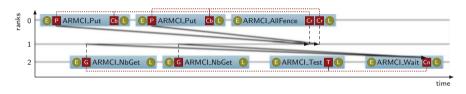

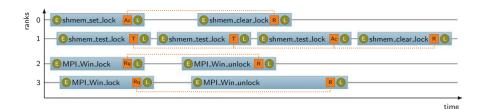

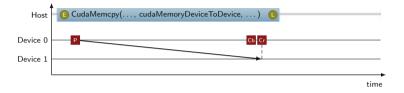

| 3   | RM         | A in HPC Parallel Programming                                  |

|-----|------------|----------------------------------------------------------------|

|     | 3.1        | RMA Operations in HPC Parallelization Libraries                |

|     | 3.2        | Concepts in RMA Parallelization Models                         |

| 4   | Gen        | eric RMA Event Types                                           |

|     | 4.1        | RMA Window Handling                                            |

|     | 4.2        | Specification of the Passive Side                              |

|     | 4.3        | Get and Put                                                    |

|     | 4.4        | Atomic RMA Operations                                          |

|     | 4.5        | Completion Records                                             |

|     | 4.6        | Notification via RMA                                           |

|     | 4.7        | Synchronization                                                |

|     | 4.8        | Collective Operations and Synchronization                      |

|     | 4.9        | Locking of Resources                                           |

| 5   |            | mple Cases with RMA Event Types                                |

| 6   |            | clusions and Outlook                                           |

|     |            | es                                                             |

|     |            |                                                                |

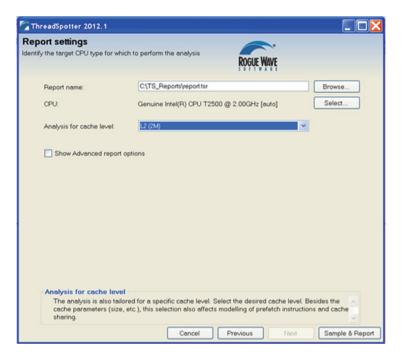

| Cac | che-R      | elated Performance Analysis Using Rogue Wave                   |

| Sof | tware      | s's ThreadSpotter                                              |

| Roy | d Lü       | dtke and Chris Gottbrath                                       |

| 1   | Intro      | oduction                                                       |

| 2   | Basi       | c Overview on Caching                                          |

|     | 2.1        | Motivation for Caching                                         |

|     | 2.2        | Cache Architectures                                            |

|     | 2.3        | Cache Organization                                             |

|     | 2.4        | Prefetching                                                    |

|     | 2.5        | Eviction of Cache Lines (Replacement Policies)                 |

|     | 2.6        | Complexity Added by Coherence                                  |

|     | 2.7        | Important Statistics                                           |

|     | 2.8        | Optimal Cache Utilization                                      |

|     | 2.9        | What Performance Improvement Is Possible When                  |

|     |            | Optimizing an Application's Cache Utilization?                 |

| 3   | Thre       | eadSpotter: A Statistical Approach for Cache-Related Profiling |

| 2   | 3.1        | Different Approaches of Cache Related Performance Analysis     |

|     | 3.2        | What Kind of Data Is ThreadSpotter Looking at in               |

|     | 5.2        | Order to Create a Report?                                      |

|     | 3.3        | Sampling an Application                                        |

|     | 3.4        | Report Generation                                              |

|     | 3.4<br>3.5 | •                                                              |

|     | 5.5        | Presenting Optimization Opportunities That                     |

| 4   | <b>T</b>   | ThreadSpotter Discovers                                        |

| 4   |            | es of Performance Optimization Opportunities Discovered        |

|     |            | ThreadSpotter                                                  |

|     | 4.1        | What Kind of Cache-Related Opportunities                       |

|     |            | for Performance Optimization Can Be Discovered                 |

|     |            | by ThreadSpotters Statistical Approach?                        |

|     | 4.2        | Reuse                                                          |

|          | 4.3 Non-temporal Data                                     | 92  |

|----------|-----------------------------------------------------------|-----|

|          | 4.4 Cache Hot Spots                                       | 92  |

| 5        | Conclusion                                                | 93  |

| Ref      | rences                                                    | 93  |

| <b>C</b> | un Hat Smath Analysis of HDC Saftmans with the Vermin     |     |

|          | com Hot Spot Analysis of HPC Software with the Vampir     | 05  |

|          | ormance Tool Suite                                        | 95  |

|          | er Brunst and Matthias Weber                              | 0.5 |

| 1        | Introduction                                              | 95  |

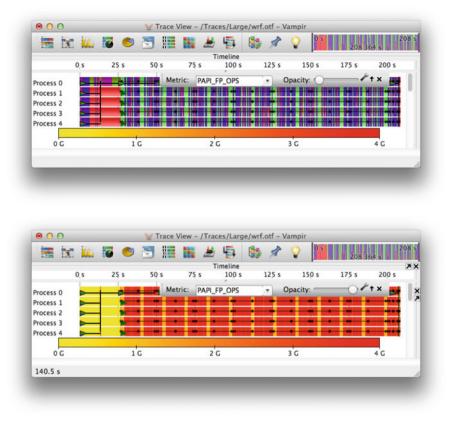

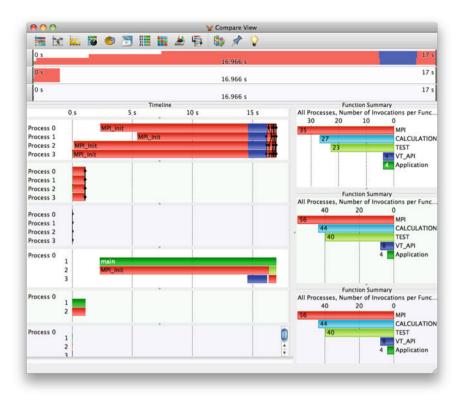

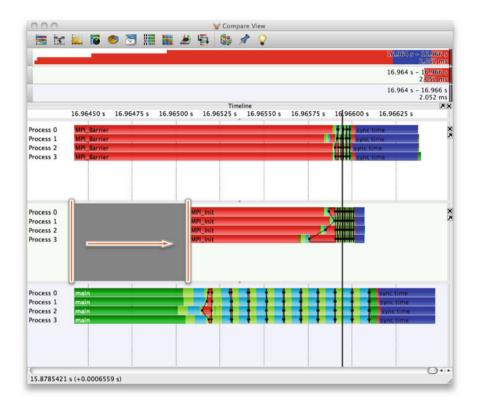

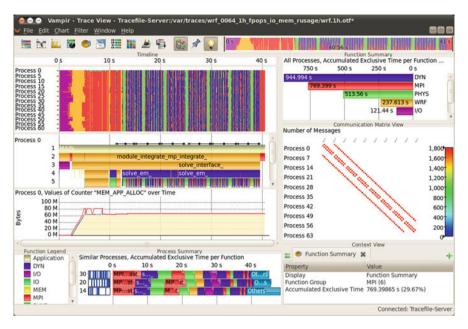

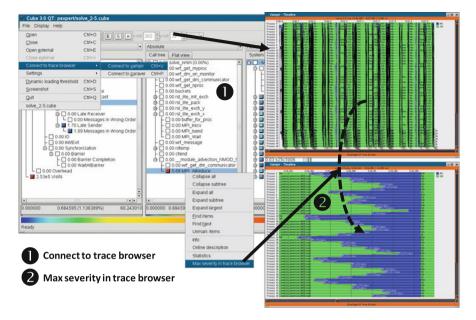

| 2        | Heat Map Overlay for the Master Timeline                  | 97  |

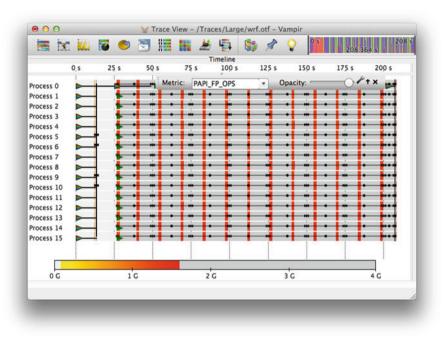

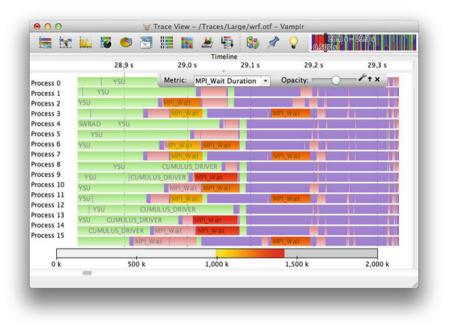

| 3        | Customization of Performance Metrics                      | 100 |

|          |                                                           | 101 |

|          | 3.2 Conditional Floating Point Performance                | 101 |

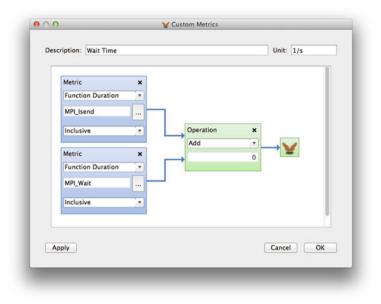

| 4        | 1                                                         | 102 |

|          | 4.1 Rules                                                 | 104 |

|          | 4.2 Examples                                              | 105 |

| 5        | Comparison of Multiple Program Runs                       | 110 |

|          | 5.1 Multiple Program Executions at a Glance               | 111 |

|          | 5.2 Alignment of Multiple Trace Files                     | 112 |

| 6        | Conclusion                                                | 114 |

| Ref      | rences                                                    | 114 |

| Fvt      | nding Scalasca's Analysis Features                        | 115 |

|          | el Lorenz, David Böhme, Bernd Mohr, Alexandre Strube,     | 115 |

|          | Zoltán Szebenyi                                           |     |

| 1        |                                                           | 115 |

| -        |                                                           | 117 |

| 2        | Root Cause Analysis                                       |     |

| 3        | Critical Path Analysis                                    | 118 |

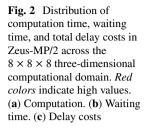

| 4        | e                                                         | 120 |

| 5        | I C                                                       | 122 |

|          |                                                           | 123 |

|          |                                                           | 124 |

|          |                                                           | 124 |

|          |                                                           | 124 |

| 6        | Future Work                                               | 125 |

| Ref      | rences                                                    | 125 |

| The      | HOPSA Workflow and Tools                                  | 127 |

|          | d Mohr, Vladimir Voevodin, Judit Giménez, Erik Hagersten, | 121 |

|          | reas Knüpfer, Dmitry A. Nikitenko, Mats Nilsson,          |     |

|          | ld Servat, Aamer Shah, Frank Winkler, Felix Wolf,         |     |

|          | lya Zhukov                                                |     |

|          | Introduction                                              | 100 |

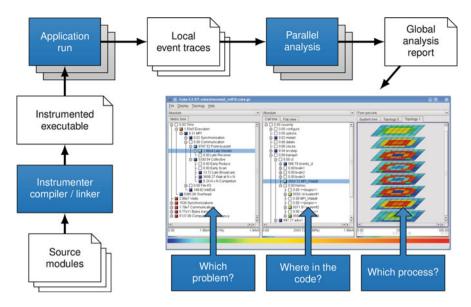

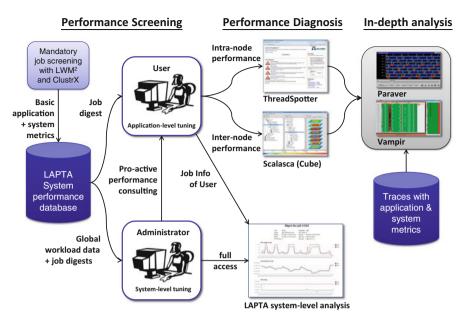

| 1        |                                                           | 128 |

| 2        | The HOPSA Workflow                                        | 129 |

|          | 2.1 Overview                                              | 129 |

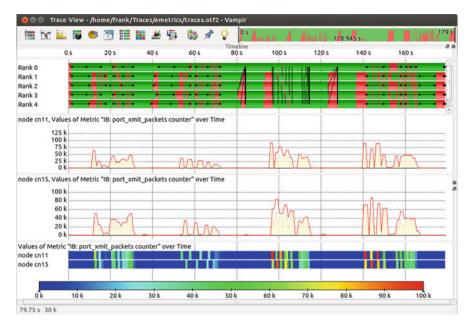

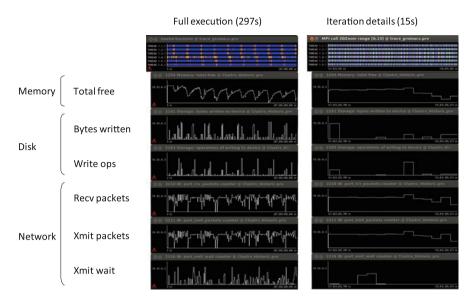

|          | 2.2 Performance Screening                                 | 130 |

#### Contents

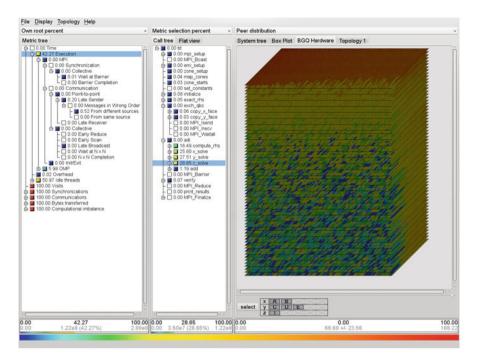

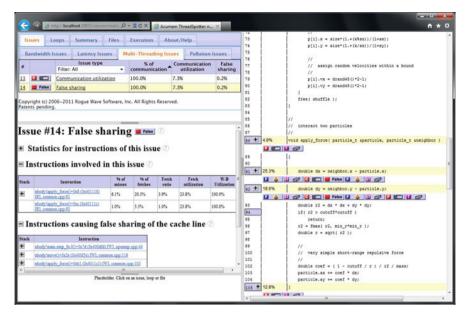

|      | 2.3    | Performance Diagnosis                                     | 132 |

|------|--------|-----------------------------------------------------------|-----|

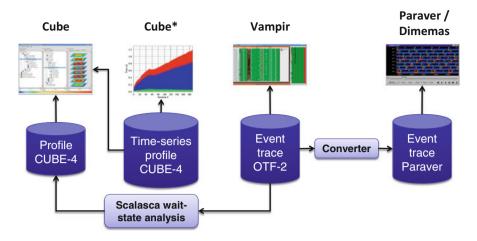

|      | 2.4    | The HOPSA Performance Tools                               | 136 |

|      | 2.5    | Integration Among Performance Analysis Tools              | 141 |

|      | 2.6    | Integration of System Data and Performance Analysis Tools | 142 |

|      | 2.7    | Opportunities for System Tuning                           | 144 |

| 3    | Conc   | lusion                                                    | 145 |

| Refe | erence | S                                                         | 145 |

## Part IV Performance Data Visualization

| Visualizing More Performance Data Than What Fits on Your Screen | 149 |

|-----------------------------------------------------------------|-----|

| Lucas M. Schnorr and Arnaud Legrand                             |     |

| 1 Introduction                                                  | 149 |

| 2 Motivation and Discussion                                     | 151 |

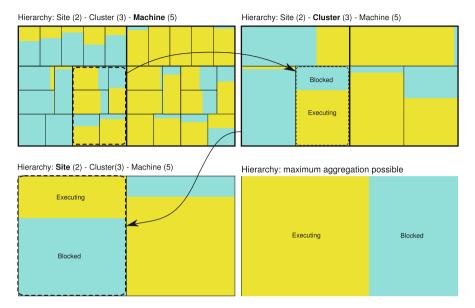

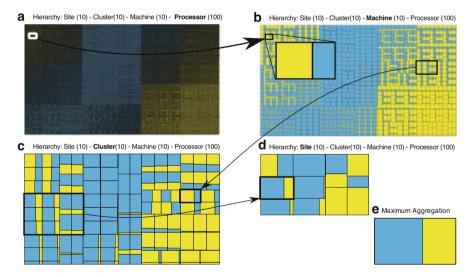

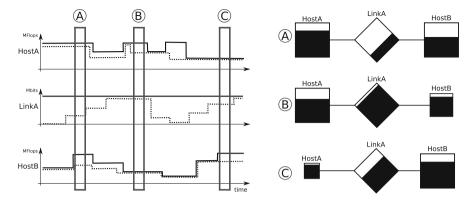

| 3 Multi-scale Trace Aggregation for Visualization               | 153 |

| 4 Visualization Techniques                                      | 155 |

| 4.1 Squarified Treemap View                                     | 155 |

| 4.2 Hierarchical Graph View                                     | 157 |

| 5 The Viva Visualization Tool                                   | 159 |

| 6 Conclusion                                                    | 159 |

| References                                                      | 160 |

# Part I Debugging

# Debugging at Scale with Allinea DDT

**David Lecomber and Patrick Wohlschlegel**

**Abstract** As core counts in HPC clusters grow, almost every application user is trying to run software at higher scale than before. It is not always an easy task and can end in failure as the limitations of existing software are discovered. Users and developers quickly find new (and old) bugs as scale increases: software can be complex when it seeks to use more threads or processes to exploit the hardware. In this document, we show how using a debugger at the scale of the bug is the most effective way to tackle parallel software problems today. We introduce Allinea DDT – the world's only scalable parallel debugger – and show how it is fast, capable, and lets you debug your parallel or multithreaded application, no matter how big or small a system you use, easily. Allinea DDT has been setting standards for usability for many years and has torn up scalability records. It is used on the world's largest systems – debugging over 220,000 processes simultaneously in some cases. Bugs can be fixed easily for all developers – not just those with extreme scale – by using Allinea DDT at your scale.

# 1 Why Scalability Matters for Debugging

Studies of job failure on larger HPC systems have shown that software problems account for a significant proportion of failures.

Increasingly errors appear at higher scales: exhaustive testing at high scale is often infeasible due to the cost of machine access, or lack of machine access. There are regularly differing development and production environments. This means that errors often occur at scale in production environments – and fixing them is a very high priority.

D. Lecomber · P. Wohlschlegel (🖂)

The Innovation Centre, Allinea Software Ltd, Warwick Technology Park, Gallows Hill, Warwick CV34 6UW, UK

e-mail: patrick@allinea.com

Software developers are used to trying many tricks to find software bugs – and no trick is more common than inserting a quick print statement. This technique can be revealing – but it is one that can scarcely handle a small parallel cluster, let alone 1,000 cores! The difficulty of knowing where to place the print statements in the first place leads to a repetitive task – but the killer problem for debugging larger parallel jobs is making sense of the interleaved print outputs of multiple processes – and this gets much worse as the number of cores increases.

Another approach is to try and make the bug appear at a smaller scale – but this is often an impossible task. Real users have discovered scale-related defects whenever applications are scaled to a higher level of concurrency – and then that it is difficult to observe such defects at reduced scales. Some bugs just do not exist at small scale – or can't be found in smaller datasets. If a stable application suddenly fails when moving to a larger system, it is unlikely that a smaller test will exhibit the issue.

Whilst many bugs are not random, many are and can be the hardest to track down. Developers familiar with array overruns or memory corruption will recognize the random consequences of such errors, and those with multithreaded applications or MPI applications with point-to-point communications or RDMA, will know that timing and ordering of events is a major source of random behaviour.

A bug that is random may fail to occur frequently enough to reproduce it on a job of say, 16 cores, but on 128 cores, it would be more likely to happen just by the cumulative effect of probability or the increase in the number of permutations of event orderings. So, again, reducing the scale of the application doesn't help in fix the problem.

We have seen that scale-related bugs are observed to occur frequently and that two of the tools in the developer's bug-fixing toolbox are just not able to deliver the help required as scale increases.

You might want to spend days or weeks trying to reproduce at a smaller scale or deciphering print output – or you could get straight to the problem by debugging at scale.

## 2 The Ability to Debug at-Scale Changes Everything

Allinea DDT is a graphical parallel debugger – used by many scientific computing centres, universities and corporations to help in the everyday task of finding and fixing bugs, from single process workstations through to the very largest supercomputers.

It has many features not present in ordinary debuggers – such as memory debugging, data visualization and support for the many MPI and OpenMP implementations that are used by parallel software developers. It also has an interface that makes debugging easy, at any scale.

With Allinea DDT, it's possible to take debugging to as high a scale as you want to take your application - it is there and it is fast! For the first time in

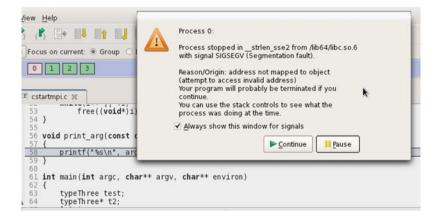

Fig. 1 A typical application crash

history, a debugger with performance logarithmic in the number of cores is giving fraction-of-a-second performance for global (or subset) operations on applications running all the way up from the humble workstation to Petascale.

### **3** How Allinea DDT Helps to Fix Bugs

Let's start by looking at how Allinea DDT can help in some of those straightforward cases – like a simple crash. Typically, when an application crashes on a HPC system, very little information is available – the job is cleaned up and all trace of the cause removed. It's usual not to generate core files – as most filesystems would not want multi-gigabyte core files being written by every process on application crash! With a bit of luck, there would be some output, perhaps some print statement that could explain roughly where the job had reached before it crashed – but beyond that, it would all be guesswork!

With Allinea DDT, the bug fixing is easier. Run the job inside Allinea DDT at the scale of the problem, and when the job crashes, this is what you see (Fig. 1).

It's immediately clear exactly where the crash happened – to the exact line, and exactly which processes. The error message conveys exactly what the problem is, and the source code is highlighted to tell you where things happened.

#### 4 Understanding Multiple Processes

Sometimes just knowing the source file and line is enough – but often you will need to see the bigger picture. Allinea DDT's Parallel Stack View enables a rapid identification of where processes and threads are. It displays the stacks of every

| Stacks (AII) |                                                |

|--------------|------------------------------------------------|

| Processes    | Function                                       |

| 150120       | i≜_start                                       |

| 150120       | 📋libc_start_main                               |

| 150120       | 🛓 main                                         |

| 150120       | Ėpop (POP.f90:81)                              |

| 150120       | initialize_pop (initial.f90:119)               |

| 150120       | init_communicate (communicate.f90:87)          |

| 150119       | -create_ocn_communicator (communicate.f90:300) |

| 1            | create_ocn_communicator (communicate.190:303)  |

Fig. 2 A parallel stack view of 150,120 cores

process in the application in a tree view – with alike stacks merged together and a process counter shown.

This component does not become any more complex as the process or thread counts increase, as you can see (Fig. 2). This is also one of the bedrocks of hybrid debugging, where it is still of great value even as the number of threads is increasing by many orders of magnitude. It's not unusual to see 20,000 threads in a single GPU device!

One of the great things about Allinea DDT is its speed in giving you this information – Allinea DDT takes a fraction of a second to report where every thread is in a job on the largest machines in the world, which means even if you are using of a few hundred cores you can be confident of incredibly responsive debugging. If a crash like this happens at 16 cores, 128 cores or 200,000 cores, it'll still be quick to fix.

Debugging is not just about the speed and responsiveness of the debugger, it's also about how to let the user see and control what's happening, easily. At scale this is extremely important.

#### 5 Simple and Effective Process Control

Not all bugs are as simple as a crash – there could instead be incorrect output, say. In these cases it is helpful to step through an application and to watch progress unfold by manually controlling the application with a debugger – perhaps running first to a breakpoint in a known good location.

With Allinea DDT, you can quickly jump to a location in the source code, and a simple one click command will let your application run all the processes to that location.

Playing, pausing or stepping groups of processes at scale is scarcely different when working on a workstation or on a cluster. Source code highlighting and the parallel stack view both scale to the task very well.

| Session Control Sear      | ch View Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🕨 🔢 🕄 🞝                   | ) 📅 🖪 🕒 📑 📑 📕 📫 🖓 🕶                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Current Group: All        | Step Threads Togethe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| All                       | 200004 processes (0-200003) Paused: 200004 Running: 0 Finished: 0 Currently selected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Create Group              | Currently selected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Project Files 💿 🗵         | C hello.c X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Project Files Source Tree | <pre>81 for(x=0;x&lt;12;x++) 82 for(y=0;y&lt;12;y++) 83 tables[x][y] = (x+1)*(y+1); 84 MPI_Init(&amp;argc, &amp;argv); 85 MPI_Comm_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank); 85 MPI_COMM_MORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_WORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_WORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_WORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank); 85 MPI_COMM_WORLD, &amp;mv_rank(MPI_COMM_WORLD, &amp;mv_rank(M</pre> |

Fig. 3 Summary view of process status

If you've seen Allinea DDT before, perhaps running at smaller job sizes, you might remember the graphical tools Allinea DDT used to tell you that processes are paused or which are still playing. But you might ask, how can Allinea DDT tell you such information about a very large job?

Yet again Allinea DDT has the answer: it has a scalable way to show you this – a summary view, as seen on (Fig. 3) – and the GUI automatically mutates to use this when you have more than 64 cores.

In just a glimpse you can see how many processes are busy – and if you hover the mouse over the Paused or Running numbers, Allinea DDT will tell you which processes they are scalably – showing 0,16,21-251, for example.

## 6 Smart Highlighting and Sparklines

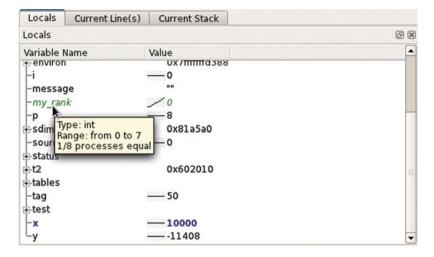

One of the recent innovations in Allinea DDT is Smart Highlighting. Allinea DDT's raw speed enables variables to be compared across processes automatically in negligible time.

Forgetting to check the error code of function calls within software is a regular source of bugs – it happens too easily – those system call errors seem so unlikely to happen at the time a client function is written – but they bite hard when they do error and the code doesn't check! Smart Highlighting is ideal for this situation.

With Smart Highlighting, Allinea DDT compares variables across processes automatically every time processes pause after stepping or playing. It will then use colour highlighting when data changes or when different values occur on other processes. This means you see unintrusive hints that may be relevant to why a code has diverged.

Those unexpectedly returned error values we mentioned earlier are a great example of where this feature helps – it would not be practical for a user to repeatedly, manually, check for errors after every step through the code, but with the debugger colour-highlighting a difference, it quickly indicates something is wrong.

Fig. 4 Smart highlighting and sparklines, showing data change and process differences

We also added a fancy new feature called sparklines, which draws a tiny graph next to each variable in the interface. It compares its value across all the processes, instantly. As a consequence, you don't even need to consider each process one by one - just look at the picture (Fig. 4), and you will intuitively understand if something is going wrong.

#### 7 Searching Data Sets

Large datasets can also be a challenge – with single errors rapidly propogating across the dataset and then across to other processes. For a long time Allinea DDT has given users a spreadsheet like view of arrays, with the ability to filter – to search for NaN or Inf, or some outliers.

This array viewing capability has been extended in Allinea DDT to give access to arrays distributed across multiple processes: It is simple to stitch together arrays distributed over a regular arrangement of processes, such as a 1, 2, or 3D process grid.

This feature lets you search for rogue elements across processes. Filtering data across many processes can be achieved in similar time to on a single processes. This can be seen on (Fig. 5). This is coupled with lazy evaluation where only the visible portion of the array is fetched to the GUI at any time, which means Allinea DDT is always responsive and never swamped.

There is also multi-process multi-dimension array viewing capability – and a built-in export capability to HDF5 and CSV. Exporting data is a theme in Allinea DDT: it is even possible to export, scalably, the stack traces in XML or CSV of

| tribu                      |               |                       |           |           |          |        |         | ibuted a |      |      |                 |     |

|----------------------------|---------------|-----------------------|-----------|-----------|----------|--------|---------|----------|------|------|-----------------|-----|

| ange                       | e of s        | \$x (Dist             | ributed)  | Rang      | e of \$i |        |         |          |      |      | Auto-up         | dat |

| r <u>o</u> m:              | : [           | 0                     | ÷         | From      | n: 0     |        | -       |          |      |      | <u>E</u> valuat | te  |

| ō:                         | [             | 7                     | -         | To:       | 999      | 9      | •       |          |      |      | Cance           | 1   |

| Displa                     | ay:           | Rows                  | \$        | Disp      | lay: C   | olumns | \$      |          |      |      |                 |     |

|                            |               |                       |           |           |          |        |         |          |      |      |                 |     |

|                            |               |                       |           |           |          |        |         |          |      |      |                 |     |

| Only                       | y sho         | ow if:                | \$value = | -= 1      |          |        | See Exa | mples    |      |      |                 |     |

| Only                       | y sho         | ow if: (              | \$value = | -= 1      |          |        | See Exa | mples    |      |      |                 |     |

|                            |               |                       |           | 1         |          |        | See Exa | mples    |      |      |                 |     |

| <u>O</u> nly<br>Data       |               |                       | \$value = | -= 1      |          |        | See Exa | mples    |      |      |                 |     |

|                            |               |                       |           |           |          |        | See Exa | mples    |      |      |                 |     |

|                            | Ta <u>b</u> l | e <u>S</u> ta         | atistics  |           | 2105     |        |         |          | 7001 | 0100 | 0467            |     |

| Data                       | Ta <u>b</u> l |                       |           | 1<br>3011 | 3185     | 4704   | See Exa | 6795     | 7881 | 9108 | 9467            |     |

| Data<br>x 0                | Ta <u>b</u> l | e <u>S</u> ta         | atistics  |           | 3185     |        |         |          | 7881 | 9108 | 9467            |     |

| Data                       | Ta <u>b</u> l | e <u>S</u> ta         | atistics  |           | 3185     |        |         |          | 7881 | 9108 | 9467            |     |

| Data<br>x 0                | Ta <u>b</u> l | e <u>S</u> ta         | atistics  | 3011      | 3185     |        |         |          |      | 9108 | 9467            |     |

| Data T                     | Ta <u>b</u> l | e <u>S</u> ta         | atistics  | 3011      |          |        |         |          |      | 9108 | 9467            |     |

| Data<br>x 0<br>1<br>2<br>3 | Ta <u>b</u> l | e <u>S</u> ta<br>2444 | atistics  | 3011      |          |        |         |          |      | 9108 | 9467            |     |

| x 0<br>1<br>2<br>3<br>4    | Ta <u>b</u> l | e <u>S</u> ta         | 2733      | 3011      |          | 4704   |         |          |      |      | 9467            |     |

| Data<br>x 0<br>1<br>2<br>3 | Ta <u>b</u> l | e <u>S</u> ta<br>2444 | atistics  | 3011      |          |        |         |          |      | 9108 | 9467            |     |

Fig. 5 Filtered search accross multiple processes

processes from the Parallel Stack View we saw earlier. This is particularly useful for reporting bugs to other people!

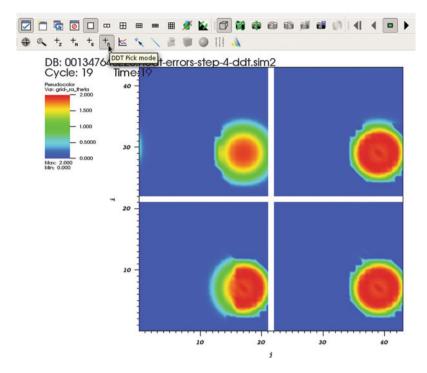

#### 8 Visualizing Large Data Sets in Real-Time

For scientists, Allinea DDT includes the integration of time-based distributed and scalable visualization tool called VisIT. This is illustrated in (Fig. 6). As there is no need to instrument the code or to write complex scripts, this feature allows easier access to data. Moreover, it integrates the ability to click back from observable troublespots to application processes.

Scientific simulations are inherently about the data, and the integration of fullstrength scientific visualization within a debugging session is key to exploring – by visualizing – the behavior of data and its interaction with code in an application. VisIt is recognized by the major supercomputing centers as one of the most capable visualization packages for data intensive HPC.

If you are already using VisIt on your cluster, you are aware of how painful it can be to look at data: you either need to store huge data sets on your storage or to instrument your code using an external library to tell VisIt what to do. With this

Fig. 6 Visualizing data at runtime and in parallel with VisIt

feature, this era is over: visualize a 1D, 2D or 3D array in real-time just as easily as you would look at it using the Multi-Dimensional Array Viewer. Allinea DDT will instrument the code with VisIt automatically for you!

#### 9 Deadlocks

Deadlock is one of the easier bugs to track down with Allinea DDT. The symptom will be that an application appears to make no progress – perhaps failing to terminate in a timely manner, or the stream of progress output in the job log dries up.

At this point is a dilemma: cancel the job, and waste the cycles so far in the belief that it has locked up – or give the job another "five minutes" in the hope that it will get somewhere. The dilemma is readily solved by just attaching a debugger to the job. Allinea DDT is able to scalably attach to running jobs or subsets of a job – ranks can be specified as a subset such as "1,4,121–140". Subsets can even be psuedo-randomly selected if the user wishes to just look at (say) one percent of the job.

On attaching, processes are paused and the location of processes, and the data values can be easily seen. This allows a quick decision to be made as to whether the application has hung – and if so where – or whether the application should continue. Detaching from the session will allow it to continue as normal.

### **10** Memory Debugging

The final class of bug we'll mention today is the memory problem. We don't mean a hardware problem, in this case we're referring to things like memory leaks – forgetting to deallocated memory – or reading beyond the end of an array. Such crashes can often appear to be quite random and can be difficult to detect.

Allinea DDT's memory debugging feature is able to help with these kinds of issues – and fixing this kind of bug is still important at scale. Many aspects of memory debugging translate to large scale very easily – for example checks for out of bound array access or for double deallocation of pointers are entirely parallel operations. Allinea DDT scalably merges and displays error messages when errors happen.

The random nature of these bugs means that being able to have the entire job under the control of a debugger is essential to not missing a crash – yet another reason to have a debugger that can cope with whatever scale you are trying to deploy applications at.

Memory leak detection is also there to help at any scale. Allinea DDT maintains information about the memory usage of the entire job – but crucially it finds the usage issues in a chosen current process, and in the worst processes (in terms of memory usage). This lets you interrogate the problem processes very easily – giving the scalability and focus that is needed to tackle the problem.

#### 11 Summary

The same capabilities that users expect of single process debugging or when working with small clusters are still needed to find bugs at higher scale.

Without debuggers, users often "work blind" – and this is increasingly true as the limitations of print statements and other techniques to fix bugs become evident.

By introducing a debugger that can reach the scale at which users are having problems, Allinea is helping users to scale applications successfully. Features, such as Smart Highlighting help users to work quickly, and smartly at all scales.

With Petascale debugging now a reality, we continue to improve the existing performance and optimize where possible. We are also addressing challenges of debugging large scale hybrid systems of GPUs, and working to ensure that the scalability results so far will carry over as machines head towards Exascale.

# 12 Further Readings

- "Understanding failures in petascale computers", B. Schroeder and G. A. Gibson, Journal of Physics Conf. Ser. 78, 2007.

- "Vrisha: Using Scaling Properties of Parallel Programs for Bug Detection and Localization", B. Zhou, M. Kulkarni and S. Bagchi, Symposium on High Performance Parallel and Distributed Computing (HPDC), June 2011.

- "Debugging Exascale: To heck with complexity, full steam ahead!", B. Feldman, The Exascale Report, September 2010.

# Task Debugging with TEMANEJO

Steffen Brinkmann, José Gracia, and Christoph Niethammer

**Abstract** In recent years memory layouts have become more and more complex and bandwidth turned out to be the crucial performance parameter. This reflects in new programming paradigms which focus on data flow rather than instruction sequence. A very successful approach is StarSs, where the parallel programme consists of small computing units called *tasks* and dependencies between these tasks which are defined by the programmer. At runtime a dependency graph is created which determines the parallel or sequential execution of the tasks. When it comes to debugging StarSs applications, traditional debuggers such as gdb don't provide enough information and control to uncover shortcomings of the program. We present a new type of debugger which acts on the task level giving the user access to the dependency graph. Information is extracted from the running application with the lightweight library AYUDAME and the information is passed to the remote client TEMANEJO which visualises the dependency graph and passes user requests, such as blocking or prioritising a task, to the application.

# 1 Introduction

Due to the complexity of parallel programming and the different approaches to parallelism, debugging has become increasingly difficult. The main problems are that (a) threads share resources such as signals, file descriptors and memory address space and (b) threads have to synchronise access to the resources to avoid race conditions. The rules controlling resource access and synchronisation can be explicitly set by the programmer or implicitly generated by the runtime environment

High Performance Computing Center Stuttgart (HLRS), University of Stuttgart, 70550 Stuttgart, Germany e-mail: brinkmann@hlrs.de

S. Brinkmann (🖂) · J. Gracia · C. Niethammer

A. Cheptsov et al. (eds.), *Tools for High Performance Computing 2012*, DOI 10.1007/978-3-642-37349-7\_2, © Springer-Verlag Berlin Heidelberg 2013

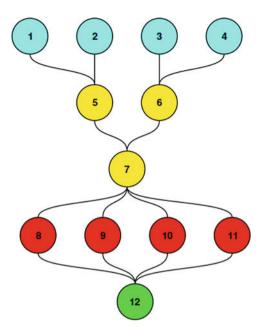

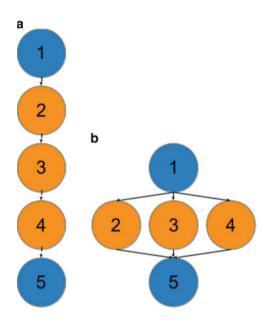

#### Fig. 1 Example task graph

(referred to simply as *runtime* hereafter) which controls the parallel execution of the application.

The implicit behaviour of parallel applications often causes problems in application development. What a runtime does is many times per se hard to understand, poorly documented and will almost certainly produce bugs that are hard to find. To avoid these problems many programmers increase the use of explicit synchronisation, e.g. in the form of barriers, which conflicts with the idea of parallel design and will decrease performance.

Many debuggers exist and many of them are capable of debugging multi threaded applications. Nevertheless all of these tools, being originally designed for single threaded programs, work on the base of threads and instructions. The natural unit is the *line of code*. Contrary to that many parallel programming models support so called *tassk parallelism*. A task in this context is a self contained piece of code with well-define input and output dependencies. Namely the growing family of StarSs compilers and libraries (e.g. SMPSs [1], OmpSs [2], StarPU [3], KAAPI [4] among others) are based on the task as their natural unit.

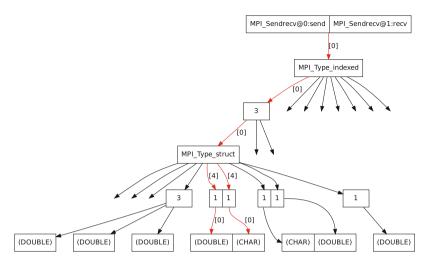

The tasks generally have implicit and explicit dependencies on other tasks forming a acyclic directed graph (*dependency graph* or *task graph* hereafter) which set the rules for executing the application in parallel (see Fig. 1). Tasks that do not depend on each other can in principle run concurrently. When a given thread runs a specific task is decided by the runtime, which also creates the tasks and dependencies, ergo the task graph.

In order to debug such an application it is necessary to add a new kind of debugger to the developers toolbox. This tool must visualise the task graph and

enable the programmer to interact with the application on the basis of tasks and dependencies.

We present the next version 0.9 of TEMANEJO [5], a tool for debugging taskparallel applications visually. It communicates with the runtime (presently SMPSs is supported fully, StarPU and OmpSs are under development) via the library AYUDAME which was written for that purpose.

In the following we will discuss the new approach to debugging imposed by task parallelism (Sect. 2). Thereafter we will describe how TEMANEJO and AYUDAME cope with these new necessities (Sect. 3) and finally draw our conclusions (Sect. 4).

## 2 What Debugging Means in the Context of Task-Based Parallelism

The debugging process of a task parallel application is best divided in three stages: (1) checking the code *without* tasks enabled, (2) checking the code with tasks enabled and executing the tasks in the order of creation on one thread and (3) checking the code with tasks enabled on multiple threads. This scheme must naturally be enhanced as more complex features such as running with various queues or a communicator thread are not taken into account.

For the first and second stage a debugger like gdb will suffice enabling the programmer to find bugs of the kind you would have in a serial program. Not so for the third stage. When running separate tasks on different threads two consecutive actions on one thread may (and generally will) be totally independent of each other. Choosing a thread in a gdb session for instance can provide valuable information about what is happening inside a task. But when the execution reaches the end of the task, the thread will proceed with a seemingly random and most probably unrelated other task.

Here the problem of the order of execution becomes apparent: How can the task-parallel application be debugged as a whole?

Another problem is not as obvious: While one thread is being debugged, i.e. halted and stepped through, what should the other threads do? Or more generically asked: What is a breakpoint in task-based parallelism?

The answer to the first question is seeing the dependency graph and stepping task-wise instead of instruction-wise.

The second question is far more challenging and allows for different solutions a few of which are roughly outlined in the following.

- Stop (= Block) one task and let the rest of the application run undisturbed. Arbitrarily many tasks can be marked with such a breakpoint.

- The whole application stops when a marked task is reached. *Stopping* can have two meanings in this context: Actually halting the whole execution, or finishing tasks which are already running but not launching any new tasks. We take the *task* as the smallest unit of an application, therefore we favour the second definition of *stopping*. Again, many tasks can be marked with such a breakpoint.

- The whole application stops due to a user request (e.g. a clicked button or other control widget). The above described ambiguity of *stopping* applies equally.

- The thread reaching a marked task stops. The rest of the program will run undisturbed with one thread less.

- Block a task conditionally, i.e. blocking it until a specific event occurs. Usually the event will be finishing another task. This way one can add dependencies to the application's task graph while running the application.

Each of these strategies can be very useful in some situations and totally meaningless in others. That is why a tool for debugging task-parallel applications must provide not only the graphical interface to the dependency graph but also numerous ways of interacting with the running application through the visual representation of the graph.

In the following section we will describe how TEMANEJO accomplishes this.

## **3** The Debugging Process

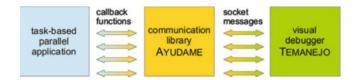

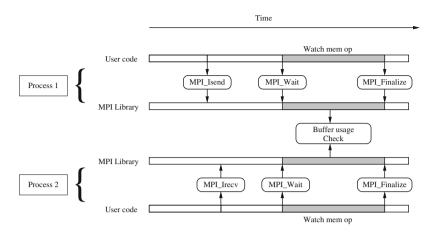

The first and not to be underestimated aid that TEMANEJO can provide is *displaying the graph*. When the dependencies are correct, the programmer will proceed to run the application within TEMANEJO. Both of these parts of the debugging process require communication between the application and the debugger. This is accomplished in two steps (see Fig. 2).

### 3.1 Communication

The runtime environment which runs the actual application is instrumented with callback routines of the lightweight communication library AYUDAME. As runtimes differ drastically in how tasks are created, ordered and executed and what is more, what a task can be, the instrumentation cannot be done generically. In fact it has to be "tailor-made" for each runtime and both AYUDAME and TEMANEJO grow with each runtime they support.

In the next step AYUDAME passes the information to TEMANEJO via a previously established socket connection using tcp/ip. This way we assure that the application can run on any remote computer while the programmer can debug it from his desktop. The relevant information consists of eight 64-bit unsigned integer which is send as a package to the socket client TEMANEJO. While the first number always identifies the runtime environment and the last one always is a timestamp, the meaning of the other six numbers differs according to the communicated event.

On the other hand the programmer can launch control requests such as executing one or more tasks (*stepping*), setting breakpoints (see Sect. 2), changing the priority level of a task or the number of active threads. These requests are passed from

Fig. 2 Information flow between the application, AYUDAME and TEMANEJO

Fig. 3 Typical error as displayed by TEMANEJO. (a) Tasks 2, 3 and 4 implement a reduction but run serial in this program. (b) Corrected version, tasks 2, 3 and 4 run in parallel

TEMANEJO via the tcp/ip socket to AYUDAME which reacts accordingly. This can mean to call a function implemented by the runtime or to set certain variables which in turn can be accessed by the runtime through callback functions.

#### 3.2 Graph Display

TEMANEJO receives the information and displays, analyses and logs the execution of the application. Often times the mere display of the actual graph hints at bugs, unwanted behaviour or even optimisation options not foreseen by the programmer. As an example see Fig. 3.

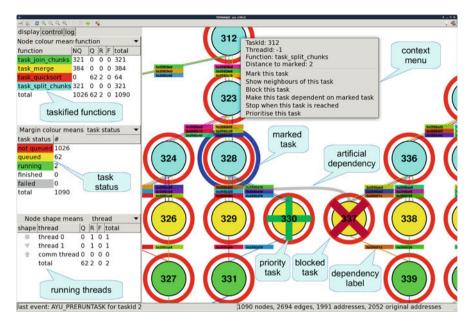

The information displayed in TEMANEJO are described in the following (see also Fig. 4).

Fig. 4 Annotated screenshot of TEMANEJO

#### 3.2.1 Nodes

The nodes represent tasks which are the natural unit of a task-parallel application. Tasks can consist of a function (subroutine, method), a part of a vectorised loop, a block of code or any other sequence of instructions depending on the runtime. The information displayed by the nodes is:

- **Label** The label is an arbitrary number used to identify the task. It must be unique for each task. Future versions of TEMANEJO will allow for strings to be task labels.

- **Function** By default the fill colour of the node denotes the taskified function or code block. It is communicated by a unique number, the *function id*. These numbers must be consecutive an start with 0. Future versions will allow for arbitrary function ids, consisting of a number or string.

This information is most useful for correctness checking of the structure of the dependency graph.

**Task status** By default an extra margin is drawn around the nodes which shows the task status. It is red for tasks which still depend on other tasks to finish (*not queued*), yellow for tasks which do not (any more) depend on other tasks but are not yet to be executed because there is no execution resource available (*queued*), green for tasks which are dispatched to run on a specific thread (*running*) and no margin for tasks which ran successfully (*finished*).

The programmer will use this information for checking the basic runtime behaviour of the application. For instance the number of queued tasks (see Sect. 3.2.3) is equivalent to the potential parallelism at a certain point in the execution.

**Thread** By default the shape of the node indicates the thread on which a task is scheduled to run, is running or has run.

This information can be used by runtime developers to check the correct dispatching of tasks to the threads and by application developers if it is possible to control the dispatch mechanism of the runtime in order to find the optimal setting.

**Task duration** TEMANEJO offers a rough insight in the execution time of each task. The difference of the cycle counters immediately before and after task execution can be displayed as the node colour. In order to get useful results one has to switch off any type of breakpoint and run the application with the "Fast Forward" button, ignoring at least so many stops as there are threads. The Program will run until the end and the task duration in CPU cycles can be shown as node colour.

This feature does not replace a performance tool but it may give a first hint to tasks which run too long (work balance!) or too short (overhead!).

**Distance between tasks** When a node is marked using the context menu, the node colours in the graph can be set to indicate the distance to the marked node. As node that are not connected are drawn in white it becomes instantly clear on which part of the graph the task represented by the marked node depends on and which part of the graph depends on this task.

This feature enables the programmer to gain a quick overview over a given application and to analyse the deeper connectivity within the task graph.

#### 3.2.2 Edges

The edges indicate dependencies between tasks. Generally these will consist in data addresses which one task will write to and another will read from. TEMANEJO can indicate the memory address by a label end a colour which uniquely identifies the memory address.

For runtimes which support dependency renaming, a feature equivalent to register renaming which allows the runtime to enhance parallel execution of logically independent tasks working on the same memory, the user can choose to see the original or the renamed memory address.

#### 3.2.3 Other Information

TEMANEJO keeps track of the number of tasks for each function, each thread and the status of each task. Tables indicate how many tasks are queued, running or finished in total and for each thread or function (see Fig. 4). This information can be used

for instance to identify bottlenecks (no queued tasks) or the maximal parallelism at a given stage of execution (number of queued tasks).

Also all messages received from AYUDAME are logged so the exact order of execution can be traced by the programmer.

#### 3.3 Execution Control

By default TEMANEJO will halt the execution before each task. This enables to examine the status of the application while executing it task-wise. On of these steps can consist of one or an arbitrary number of tasks. Halting the application can be switched of in order to run the whole application, e.g. for time measurements.

Individual tasks can be blocked (compare Sect. 2). They are marked with a red cross in the graph display (see Fig. 4). A blocked task is not executed until unblocked. Consequently tasks dependent on a blocked task are not executed.

The mechanism of blocking tasks can be used to add artificial dependencies during the debugging process, i.e. during runtime of the application without recompiling it. When a task is marked (blue margin in the graph display, see Fig. 4) and the programmer right-click on another task, the option "make dependent on marked task" appears active in the context menu. When clicked, the task is blocked and remains so until the previously marked task is finished.

Furthermore it is possible to keep the runtime from running tasks at all (compare Sect. 2). This can be achieved by pressing the button "stop scheduling tasks" in the control tab.

In order to debug a task internally or to debug the main thread it is possible to launch gdb from TEMANEJO. gdb is automatically attached to the applications process and opens with the option -tui (terminal/text user interface) in a separate window.

#### 4 Conclusion

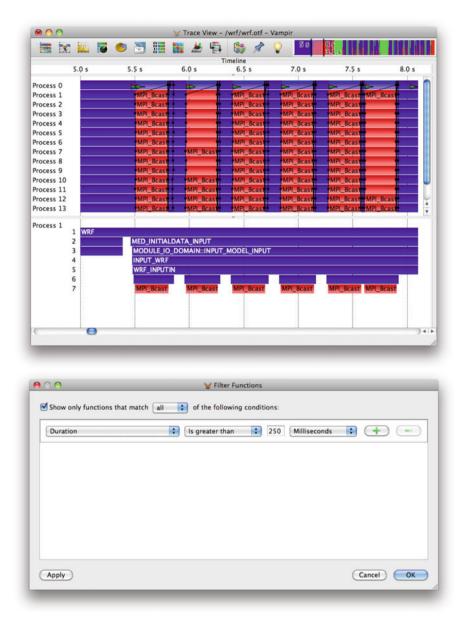

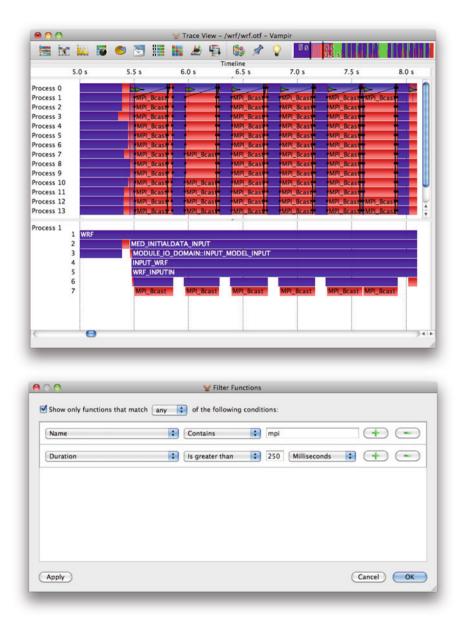

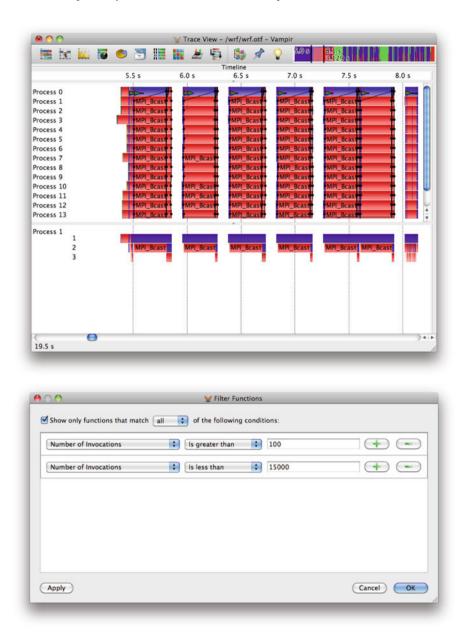

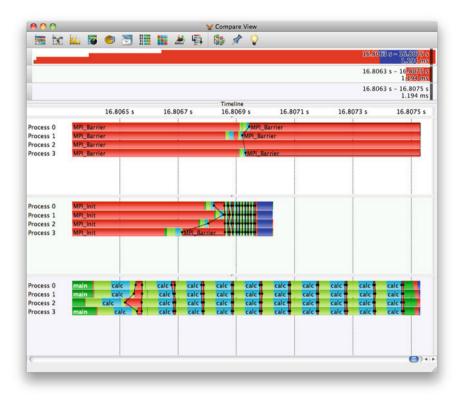

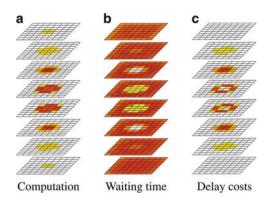

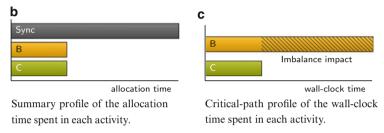

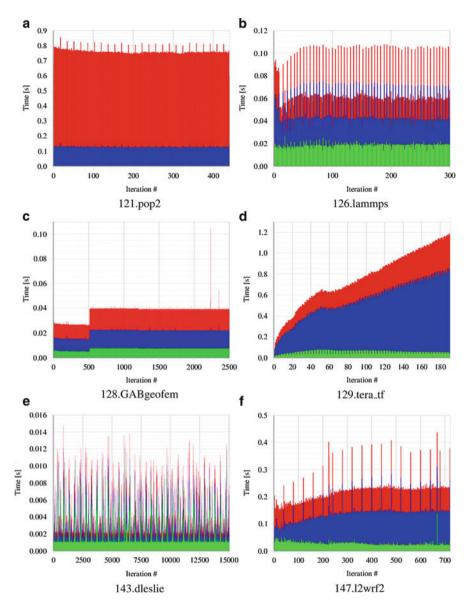

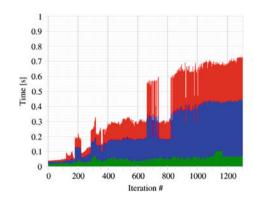

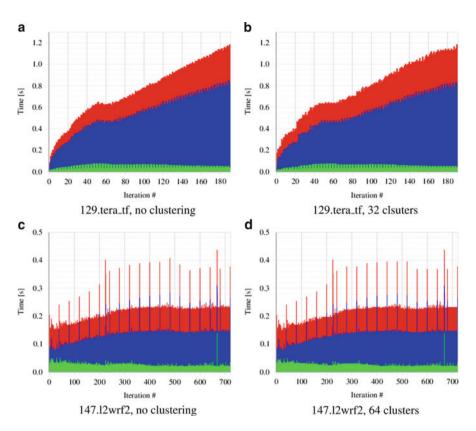

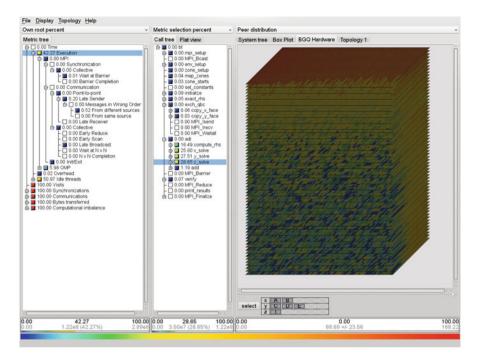

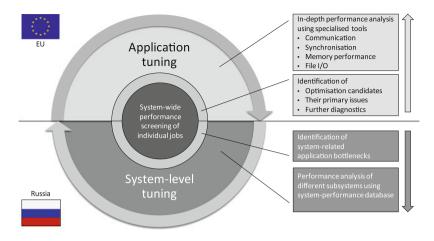

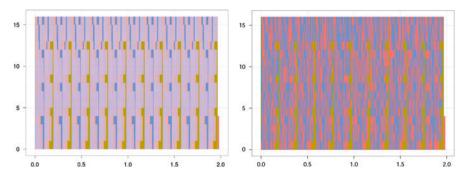

We present a debugging toolset for task-parallel applications consisting of the graphical user interface TEMANEJO and the communication library AYUDAME. It has proven very useful to application and runtime developers. With TEMANEJO it is possible to display detailed information about the dependency graph, namely executed functions, state of tasks and threads, duration of tasks, connectivity of subgraphs, memory addresses which cause dependencies, and some statistics.