Hana Kubátová Christian Hochberger Martin Daněk Bernhard Sick (Eds.)

# Architecture of Computing Systems – ARCS 2013

26th International Conference Prague, Czech Republic, February 2013 Proceedings

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Hana Kubátová Christian Hochberger Martin Daněk Bernhard Sick (Eds.)

# Architecture of Computing Systems– ARCS 2013

26th International Conference Prague, Czech Republic, February 19-22, 2013 Proceedings

#### Volume Editors

Hana Kubátová Czech Technical University Thákurova 9 160 00 Prague 6, Czech Republic E-mail: kubatova@fit.cvut.cz

Christian Hochberger Technische Universität Darmstadt Merckstraße 25 64283 Darmstadt, Germany E-mail: hochberger@rs.tu-darmstadt.de

Martin Daněk Institute of Information Theory and Automation Pod Vodárenskou věží 4 18208 Prague 8, Czech Republic E-mail: danek@utia.cas.cz

Bernhard Sick Universität Kassel Wilhelmshöher Allee 73 34121 Kassel, Germany E-mail: bsick@uni-kassel.de

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-642-36423-5 e-ISBN 978-3-642-36424-2 DOI 10.1007/978-3-642-36424-2 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2013930452

CR Subject Classification (1998): C.2, C.5.3, D.4, D.2.11, H.3.5, H.4, H.5.4

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2013

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in ist current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

# Preface

The Architecture of Computing Systems (ARCS) series of conferences has a long tradition of reporting high-quality results in computer architecture research and closely related fields. ARCS represents a dynamic, evolving community that closely follows new research trends and also defines new research areas such as the field of organic computing. Over the years, ARCS has evolved from a small national event to an important international forum. The 26th ARCS, with a special focus on application acceleration, was hosted by the renowned Czech Technical University in Prague, one of the oldest technical universities in the world, in one of the most beautiful European cities.

ARCS 2013 attracted 73 submissions coming from 26 countries spread over all but one inhabited continent. Of those, 29 were accepted for presentation at the conference and have been published in this book. We would like to acknowledge the efforts of all researchers who submitted their work to ARCS 2013, even though many papers could not be be included in the final program due to the packed conference schedule.

We would like to express our gratitude to all those who made this ARCS possible. This includes the Chairs, the members of the Steering Committee (GI/ITG Fachausschuss ARCS), the members of the Technical Program Committee, the additional reviewers, and in particular the authors that submitted their work to ARCS 2013. We would also like to thank all our sponsors and supporters. Finally, we wish to express our appreciation to Petr Fišer, for the web support, and André Gensler, for typesetting the proceedings.

We hope you enjoyed ARCS 2013.

December 2012

Hana Kubátová Christian Hochberger Martin Daněk Bernhard Sick

# Organization

## **Organizing Committee**

#### General Chair

| Hana Kubátová        | CTU in Prague, Czech Republic |

|----------------------|-------------------------------|

| Christian Hochberger | TU Dresden, Germany           |

## PC Chairs

| Martin Daněk  | UTIA AV CR, Czech Republic    |

|---------------|-------------------------------|

| Bernhard Sick | University of Kassel, Germany |

#### Workshop and Tutorial Chair

| Mladen Berekovic | TU Braunschweig, Germany |

|------------------|--------------------------|

|------------------|--------------------------|

#### **Publicity Chairs**

| Josef Hlaváč | CTU in Prague, Czech Republic            |

|--------------|------------------------------------------|

| Dietmar Fey  | University of Erlangen-Nürnberg, Germany |

#### **Conference Web Chairs**

| Petr Fišer      | CTU in Prague, Czech Republic |

|-----------------|-------------------------------|

| Martin Chloupek | CTU in Prague, Czech Republic |

#### **Industry Liaison**

Robert Lórencz

CTU in Prague, Czech Republic

#### Local Organization

| Rudolf Kinc          | AMCA, Czech Republic |

|----------------------|----------------------|

| Eva Uhrová (Finance) | AMCA, Czech Republic |

## **Program Committee**

Michael Beigl Karlsruhe Institute of Technology, Germany Mladen Berekovic TU Braunschweig, Germany Technical University of Delft, The Netherlands Koen Bertels Jürgen Brehm University of Hanover, Germany Uwe Brinkschulte University of Frankfurt, Germany Philip Brisk University of California, USA Hong Kong Polytechnic University, Hong Kong Jiannong Cao Joao Cardoso University of Porto, Portugal Luigi Carro Universidade Federal do Rio Grande do Sul, Brazil Martin Daněk Akademie věd České Republiky, Czech Republic Koen De Bosschere Ghent University, Belgium Oliver Diessel University of New South Wales, Australia Nikitas Dimopoulos University of Victoria, Canada Ahmed El-Mahdy E-JUST, Egypt Fabrizio Ferrandi Politecnico di Milano, Italy Alois Ferscha University of Linz, Austria Petr Fišer Czech Technical University in Prague, Czech Republic Università di Pisa, Italy Pierfrancesco Foglia William Fornaciari Politecnico di Milano, Italy University of Edinburgh, UK Björn Franke Roberto Giorgi University of Siena, Italy Daniel Gracia-Pérez CEA. France Jan Haase Technical University Vienna, Austria Jörg Henkel Karlsruhe Institute of Technology, Germany Andreas Herkersdorf Technical University of Munich, Germany Christian Hochberger TU Dresden, Germany Michael Hübner University of Bochum, Germany Murali Javapala IMEC, Belgium University of Tallinn, Estonia Gert Jervan TU Berlin, Germany Ben Juurlink Wolfgang Karl Karlsruhe Institute of Technology, Germany Andreas Koch TU Darmstadt, Germany Jan Kořenek Brno University of Technology, Czech Republic Hana Kubátová Czech Technical University in Prague, Czech Republic

| Olaf Landsiedel<br>Róbert Lórencz                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Paul Lukowicz                                                                                                                                                                 |

| Erik Mähle<br>Christian Müller-Schloer<br>Alex Orailoglu<br>Francois Pacull<br>Raphael Poss<br>Kay Römer<br>Pascal Sainrat<br>Silvia Santini<br>Toshinori Sato<br>Jan Schmidt |

| Martin Schulz                                                                                                                                                                 |

| Karsten Schwan<br>Lukáš Sekanina                                                                                                                                              |

| Bernhard Sick<br>Cristina Silvano<br>Leonel Sousa<br>Rainer Spallek<br>Olaf Spinczyk<br>Benno Stabernack<br>Walter Stechele<br>Jarmo Takala<br>Diamshid Tayanagrajan          |

| Djamshid Tavanagraian<br>Jürgen Teich<br>Pedro Trancoso<br>Theo Ungerer<br>Hans Vandierendonck<br>Stéphane Vialle<br>Lucian Vintan<br>Klaus Waldschmidt                       |

| Stephan Wong                                                                                                                                                                  |

KTH Stockholm, Sweden Czech Technical University in Prague, Czech Republic DFKI and University of Kaiserslautern, Germany University of Lübeck, Germany Leibniz Universität Hannover, Germany UC San Diego, USA Commissariat à l'énergie atomique, France University of Amsterdam, The Netherlands ETH Zürich, Switzerland Université de Toulouse. France ETH Zürich. Switzerland Fukuoka University, Japan Czech Technical University in Prague, Czech Republic Lawerence Livermore National Laboratory, Canada Georgia Institute of Technology, USA Czech Technical University in Prague, Czech Republic University of Kassel, Germany Politecnico di Milano, Italy TU Lisboa, Portugal TU Dresden, Germany TU Dortmund, Germany Fraunhofer HHI, Germany TU München, Germany Tampere University of Technology, Finland Universität Rostock, Germany Universität Erlangen, Germany University of Cyprus, Cyprus University of Augsburg, Germany Queens University Belfast, UK Supelec, France University of Sibiu, Romania Universität Frankfurt, Germany Delft University of Technology, The Netherlands

## Additional Referees

| F. Terraneo | T. Schuster | J. Wenninger |

|-------------|-------------|--------------|

| N. Moser    | R. Pujari   | J. Paul      |

| Y. Chaaban  | R. Paseman  | G. Mariani   |

| G. Nazar    | S. Roloff      | G. Bournoutian |

|-------------|----------------|----------------|

| R. Seedorf  | J. Mottin      | A. Portero     |

|             |                |                |

| C. Kang     | C. Li          | S. Metzlaff    |

| T. Preußer  | S. Lal         | B. Thielmann   |

| R. Backasch | H. Mushtaq     | S. Wildermann  |

| J. Lucas    | D. Matos       | F. Kluge       |

| A. Ilic     | B. Motruk      | A. Ostadzadeh  |

| I. Zgeras   | A. Brandon     | G. Gabrielli   |

| M. Kicherer | S. Campanelli  | S. Xydis       |

| L. Kuan     | M. Zabel       | F. Anjam       |

| G. Thomas   | I. Koutras     | R. Ferreira    |

| H. Amrouch  | F. Stock       | A. Barenghi    |

| M. Solinas  | S. Boppu       | F. Hameed      |

| F. Miller   | F. Nowak       | T. Martinek    |

| J. Matousek | V. Lari        | S. Mühlbach    |

| M. Pacher   | S. Schlingmann | Z. Vasicek     |

| M. Kohlik   | F. Nadeem      | S. Michalik    |

| M. Gunia    | G. Hempel      | M. Kajan       |

| M. Raitza   | A. Garbade     | B. Schmidt     |

| J. Mische   | T. Wink        | M. Vogt        |

| L. Cassano  | J. Sykora      | S. Niemann     |

We also thank all additional referees whose names are unknown to the Executive Committee.

# Table of Contents

| An Unstructured Termination Detection Algorithm Using Gossip in<br>Cloud Computing Environments<br>JongBeom Lim, Kwang-Sik Chung, Joon-Min Gil,<br>TaeWeon Suh, and HeonChang Yu | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Power Monitoring for Mixed-Criticality on a Many-Core Platform<br>Boris Motruk, Jonas Diemer, Rainer Buchty, and Mladen Berekovic                                                | 13  |

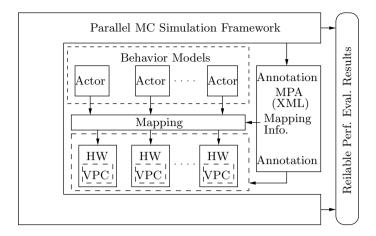

| On Confident Task-Accurate Performance Estimation<br>Yang Xu, Bo Wang, Rafael Rosales, Ralph Hasholzner, and<br>Jürgen Teich                                                     | 25  |

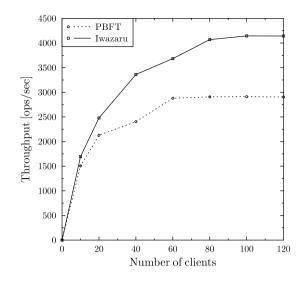

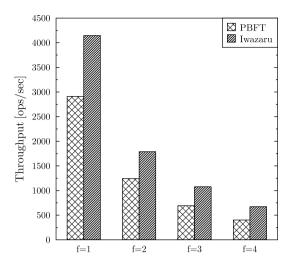

| Iwazaru: The Byzantine Sequencer<br>Maciej Zbierski                                                                                                                              | 38  |

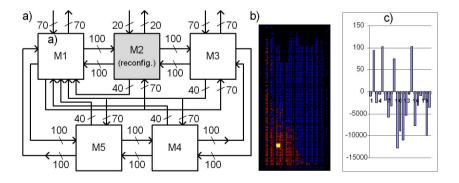

| Exploiting Thermal Coupling Information in MPSoC Dynamic Thermal<br>Management<br>Simone Corbetta and William Fornaciari                                                         | 50  |

| A Multi-core Memory Organization for 3-D DRAM as Main Memory<br>Jared Sherman, Krishna Kavi, Brandon Potter, and Mike Ignatowski                                                 | 62  |

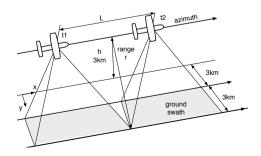

| Synthetic Aperture Radar Data Processing on an FPGA Multi-core<br>System<br>Pascal Schleuniger, Anders Kusk, Jørgen Dall, and Sven Karlsson                                      | 74  |

| Virtual Register Renaming<br>Mageda Sharafeddine, Haitham Akkary, and Doug Carmean                                                                                               | 86  |

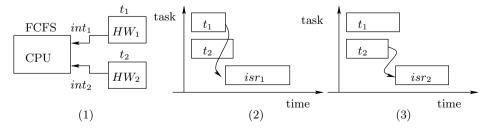

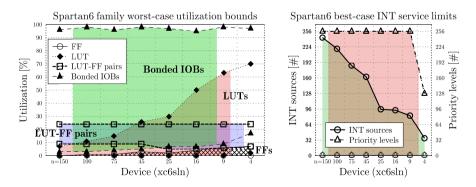

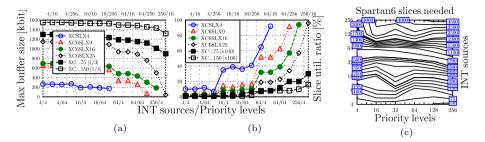

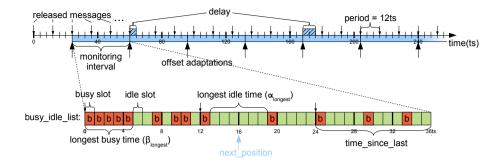

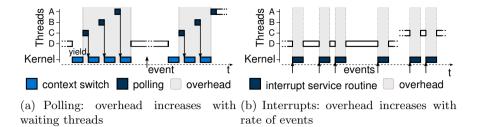

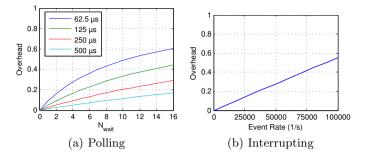

| Load-Adaptive Monitor-Driven Hardware for Preventing Embedded<br>Real-Time Systems from Overloads Caused by Excessive Interrupt<br>Rates                                         | 98  |

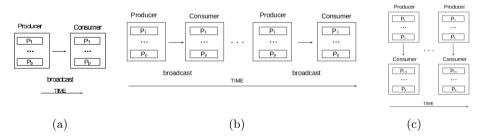

| Producer-Consumer: The Programming Model for Future Many-Core<br>Processors<br>Arnau Prat-Pérez, David Dominguez-Sal,<br>Josep-Lluis Larriba-Pey, and Pedro Trancoso             | 110 |

| A Highly Dependable Self-adaptive Mixed-Signal Multi-core<br>System-on-Chip<br>Benjamin Betting, Julius von Rosen, Lars Hedrich, and<br>Uwe Brinkschulte                         | 122 |

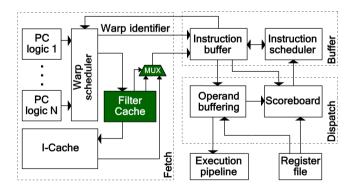

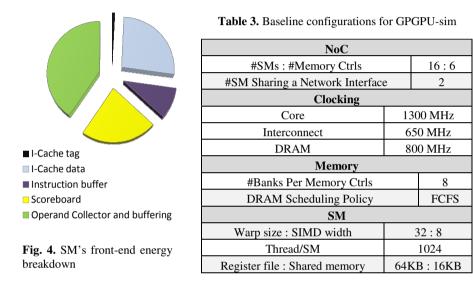

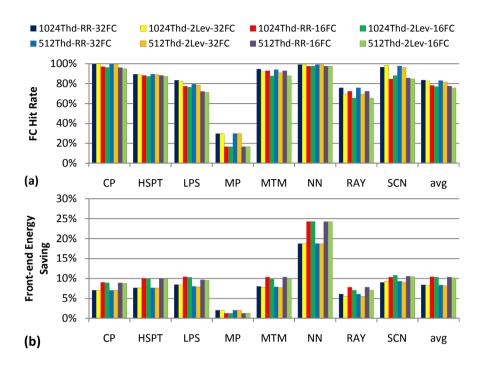

| Inter-warp Instruction Temporal Locality in Deep-Multithreaded<br>GPUs                                                                                                                                            | 134 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Ahmad Lashgar, Amirali Baniasadi, and Ahmad Khonsari                                                                                                                                                              | 104 |

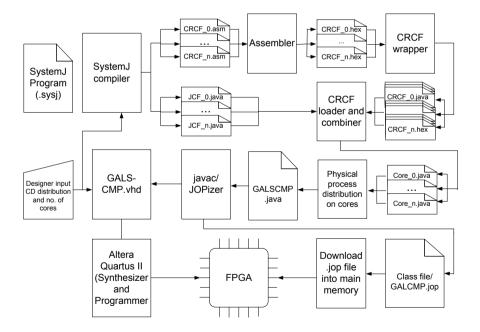

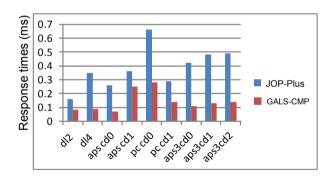

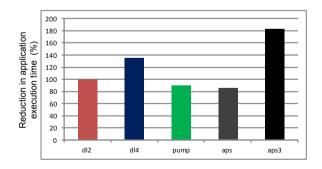

| GALS-CMP: Chip-Multiprocessor for GALS Embedded Systems<br>Muhammad Nadeem, HeeJong Park, Zhenmin Li,<br>Morteza Biglari-Abhari, and Zoran Salcic                                                                 | 147 |

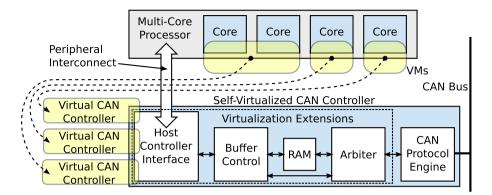

| HW/SW Tradeoffs for Dynamic Message Scheduling in Controller AreaNetwork (CAN)Tobias Ziermann, Zoran Salcic, and Jürgen Teich                                                                                     | 159 |

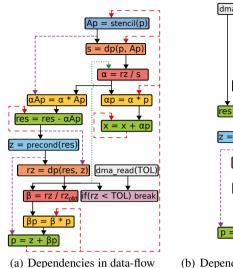

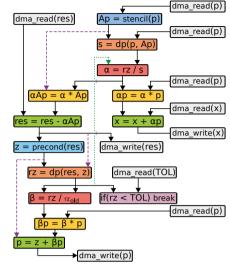

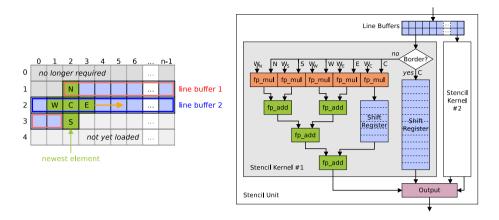

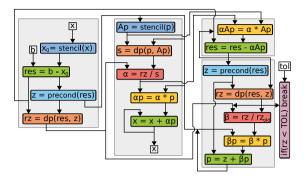

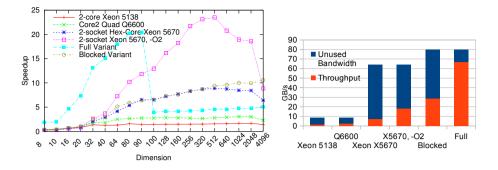

| A Data-Driven Approach for Executing the CG Method on<br>Reconfigurable High-Performance Systems<br>Fabian Nowak, Ingo Besenfelder, Wolfgang Karl,<br>Mareike Schmidtobreick, and Vincent Heuveline               | 171 |

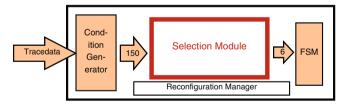

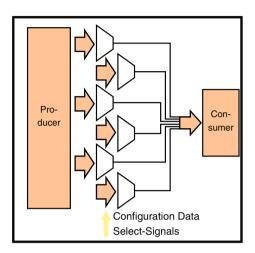

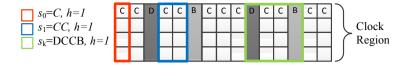

| Custom Reconfigurable Architecture Based on Virtex 5 Lookup<br>Tables<br><i>Rico Backasch and Christian Hochberger</i>                                                                                            | 183 |

| Profiling Energy Consumption of I/O Functions in Embedded<br>Applications<br>Shiao-Li Tsao, Cheng-Kun Yu, and Yi-Hsin Chang                                                                                       | 195 |

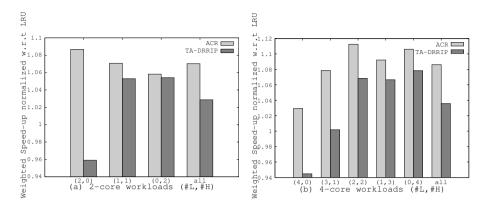

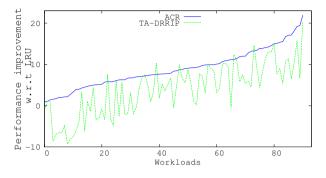

| An Application-Aware Cache Replacement Policy for<br>Last-Level Caches                                                                                                                                            | 207 |

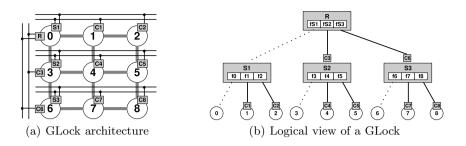

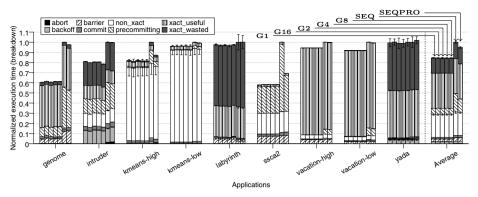

| Deploying Hardware Locks to Improve Performance and Energy<br>Efficiency of Hardware Transactional Memory<br>Epifanio Gaona, José L. Abellán, Manuel E. Acacio, and<br>Juan Fernández                             | 220 |

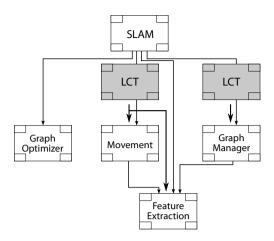

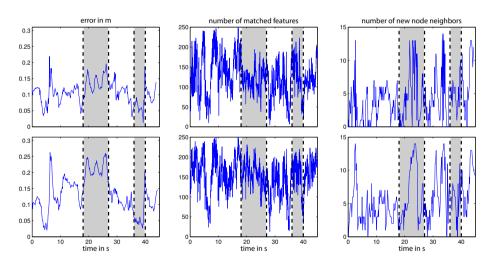

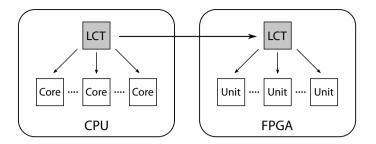

| Self-adaptation for Mobile Robot Algorithms Using Organic Computing<br>Principles                                                                                                                                 | 232 |

| Self-virtualized CAN Controller for Multi-core Processors in Real-Time<br>Applications<br>Christian Herber, Andre Richter, Holm Rauchfuss, and<br>Andreas Herkersdorf                                             | 244 |

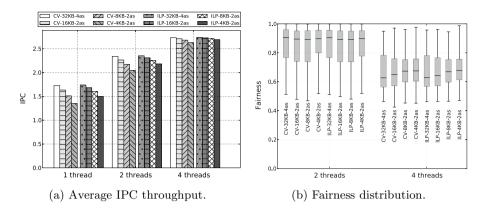

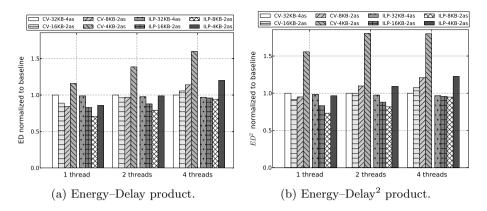

| Shrinking L1 Instruction Caches to Improve Energy–Delay in SMT<br>Embedded Processors<br>Alexandra Ferrerón-Labari, Marta Ortín-Obón,<br>Darío Suárez-Gracia, Jesús Alastruey-Benedé, and<br>Víctor Viñals-Yúfera | 256 |

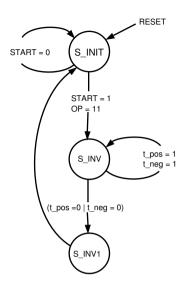

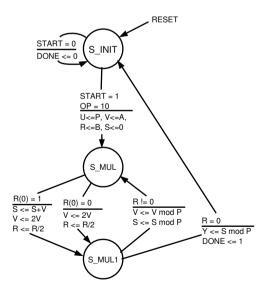

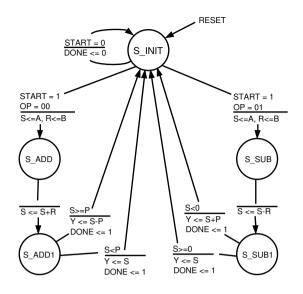

| Arithmetic Unit for Computations in $GF(p)$ with the Left-Shifting<br>Multiplicative Inverse Algorithm                                                                | 268 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

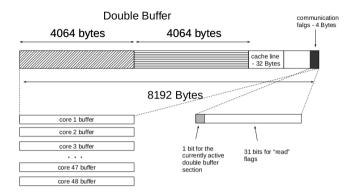

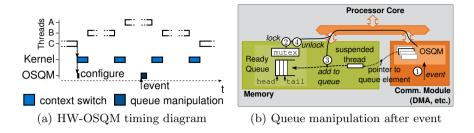

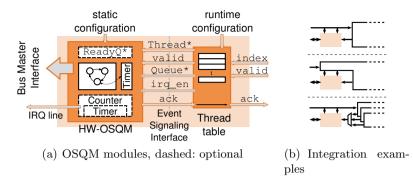

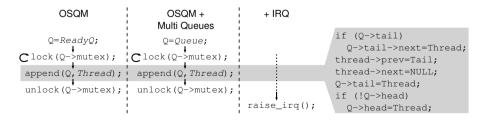

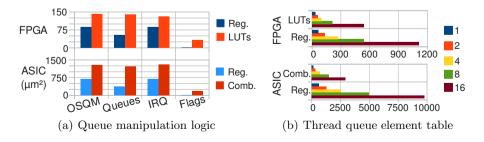

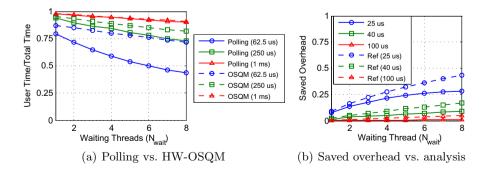

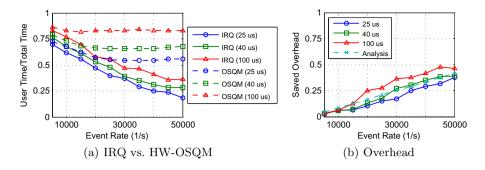

| HW-OSQM: Reducing the Impact of Event Signaling by<br>Hardware-Based Operating System Queue Manipulation<br>Stefan Wallentowitz, Thomas Wild, and Andreas Herkersdorf | 280 |

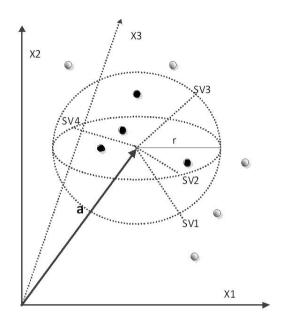

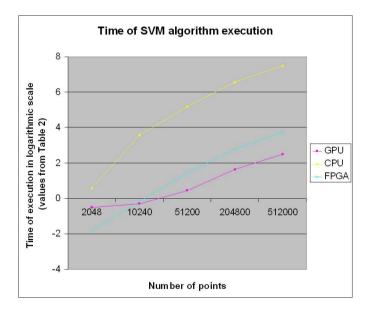

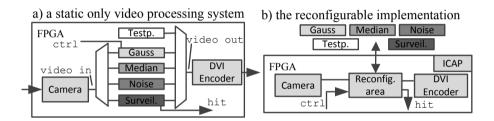

| Comparison of GPU and FPGA Implementation of SVM Algorithm for<br>Fast Image Segmentation                                                                             | 292 |

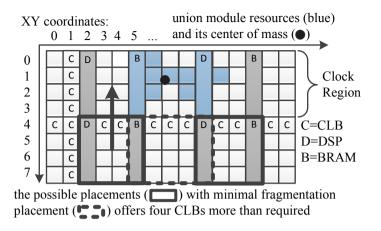

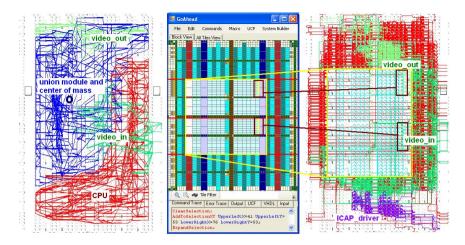

| Automatic Floorplanning and Interface Synthesis of Island Style<br>Reconfigurable Systems with GOAHEAD<br>Christian Beckhoff, Dirk Koch, and Jim Torreson             | 303 |

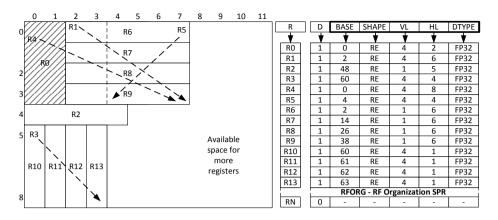

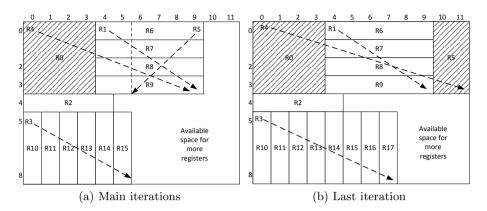

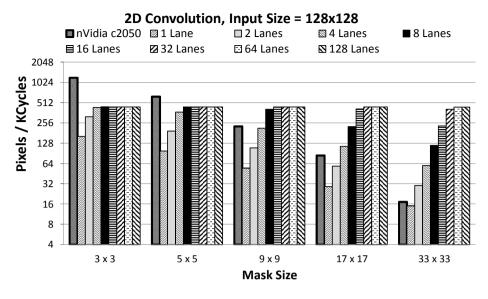

| Separable 2D Convolution with Polymorphic Register Files<br>Cătălin B. Ciobanu and Georgi N. Gaydadjiev                                                               | 317 |

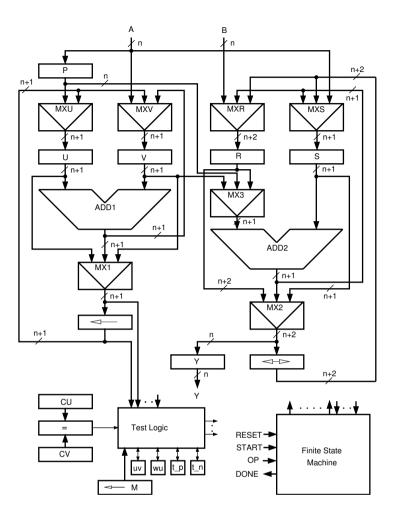

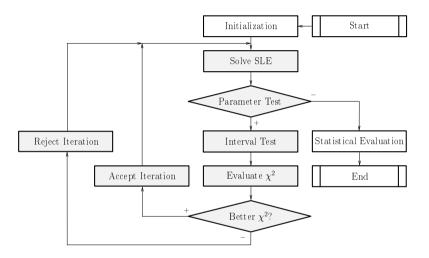

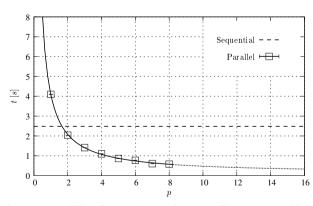

| Architecture of a Parallel MOSFET Parameter Extraction System<br>Tomáš Zahradnický and Róbert Lórencz                                                                 | 329 |

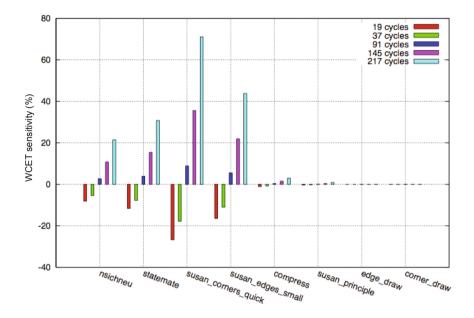

| Predictable Two-Level Bus Arbitration for Heterogeneous Task Sets<br>Roman Bourgade, Christine Rochange, and Pascal Sainrat                                           | 341 |

| Author Index                                                                                                                                                          | 353 |

# An Unstructured Termination Detection Algorithm Using Gossip in Cloud Computing Environments<sup>\*</sup>

Jong<br/>Beom Lim<sup>1</sup>, Kwang-Sik Chung<sup>2</sup>, Joon-Min Gil<sup>3</sup>, TaeWeon Suh<sup>1</sup>, and HeonChang Yu<sup>1,\*\*</sup>

<sup>1</sup> Department of Computer Science Education, Korea University, Seoul, Korea {jblim, suhtw, yuhc}@korea.ac.kr

<sup>2</sup> Department of Computer Science, Korea National Open University, Seoul, Korea kchung0825@knou.ac.kr

<sup>3</sup> School of Computer & Information Communications Engineering, Catholic University of Daegu, Daegu, Korea jmgil@cu.ac.kr

Abstract. Determining termination in dynamic environments is hard due to node joining and leaving. In previous studies on termination detection, some structures, such as spanning tree or computational tree, are used. In this work, we present an unstructured termination detection algorithm, which uses a gossip based scheme to cope with scalability and fault-tolerance issues. This approach allows the algorithm not to maintain specific structures even when nodes join and leave during runtime. These dynamic behaviors are prevalent in cloud computing environments and little attention has been paid by existing approaches. To measure the complexity of our proposed algorithm, a new metric, *self-centered message complexity* is used. Our evaluation over scalable settings shows that an unstructured approach has a significant merit to solve scalability and fault-tolerance problems with lower message complexity over existing algorithms.

**Keywords:** Termination detection, Unstructured algorithm, Gossip, Cloud computing.

### 1 Introduction

In the termination detection problem, a set of nodes in the system collectively execute a distributed computation and the purpose of termination detection algorithms is to safely detect the termination of the distributed computation, whereupon the next distributed computation can progress. Determining whether a distributed computation has terminated or not is a non-trivial task because no

<sup>&</sup>lt;sup>\*</sup> This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST) (No. 2012046684).

<sup>\*\*</sup> Corresponding author.

C. Hochberger et al. (Eds.): ARCS 2013, LNCS 7767, pp. 1–12, 2013.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2013

node has complete knowledge of the global state, and there is no notion of global time or global memory. Each node only knows its own local state and local time, and communication among nodes can be done only by passing messages.

Termination detection problem has been extensively studied for static distributed systems where all of the nodes are stationary in terms of node joining and leaving from the beginning to the end (e.g., 1, 2, 3, 4, 5 and 6). One of the systems where termination detection algorithms can be used is the cloud computing system in which constituent nodes can easily join and leave with dynamic behavior due to loosely-coupled environments. However, although numerous research efforts for the termination detection problem in recent years mainly focus on reducing message complexity, little attention has been paid to the aforementioned dynamic behavior. Most of the studies assumed that the system is static without considering node failures and joining which are vital aspects in cloud computing environments and should not be dismissed.

Recently, gossip-based algorithms have received much attention due to its inherent scalable and fault-tolerant properties which offer additional benefits in distributed systems [I]. Correctness of a gossip-based protocol is presented in [S] and [9]. In gossip-based algorithms, each node maintains some number of neighbors called a *PartialView*. With this PartialView, at each cycle (round), every node in the system selects f (fanout) number of nodes at random and then communicates using one of the following ways: 1) Push, 2) Pull, and 3) Push-pull mode. Gossip-based algorithms guarantee message delivery to all nodes with high probability and their variation can be found in [10], [11], [12], [13], [14] and [15]. Applications of gossip-based algorithms include message dissemination, failure detection services, data aggregation etc.

In this paper, we present an unstructured termination detection algorithm based on the gossip-based algorithm. Having PartialView in the gossip-based algorithm is the essential key to solve the scalability issue. In other words, each node does not have to maintain all the nodes in the system, but the small number of nodes. Furthermore, in structured termination detection algorithms (using spanning tree or computational tree), reconstruction of the structure of algorithms is required when node joining and leaving occur. Otherwise, detecting the termination of a distributed computation is virtually impossible since node connection has not established or has broken.

The rest of the paper is organized as follows. We present the system model and formally describe the termination detection problem in Section 2 Section 3 provides our gossip-based termination detection algorithm. Experimental results for the algorithm and their interpretation are given in Section 4 this section also analyzes the message complexity. Finally, Section 5 gives our conclusions.

#### 2 Model and Problem Specifications

#### 2.1 System Model

We assume that the cloud computing infrastructure consists of numerous nodes of resources, and individual nodes perform arbitrary programs to achieve a common goal. Because of the absence of shared memory, each process or node should communicate with other nodes only by passing messages through a set of channels. In addition, we assume that all channels are reliable but are not restricted to FIFO (first-in, first-out). The message delay is bounded. There is no global clock. However, we assume that each node synchronizes its time by gossiping with other nodes. This approach has been justified by [16]. Furthermore, the communication model is asynchronous.

#### 2.2 Model and Problem Specifications

Termination detection is a fundamental problem in distributed systems; it is not an exception in cloud computing systems. The importance of determining termination derives from the observation that some nodes may execute several sub-problems, and in some cases, there are precedence dependencies among them. Because there is no shared memory, message passing is the only way to deal with the termination detection problem satisfying following properties:

- Safety: If the termination detection algorithm announces termination, then the underlying computation has indeed terminated.

- Liveness: If termination holds in the underlying computation, then eventually the termination detection algorithm announces termination and henceforth termination is not revoked.

- Non-Interference: The termination detection algorithm must not influence the underlying computation.

The definition of termination detection is as follows: Let  $P_i(t)$  denote the state (active or passive) of process  $P_i$  at time t and  $C_{i,j}(t)$  denote the number of messages in transit in the channel at time t from  $P_i$  to  $P_j$ . A distributed computation is said to be terminated at time t if and only if:

$$(\forall_i :: P_i(t) = passive) \land (\forall_{i,j} :: C_{i,j}(t) = null)$$

(1)

#### 2.3 Performance Metrics

Traditionally, the following metric has been used to measure the performance of termination detection algorithms:

Message complexity: The number of messages required to detect the termination.

In addition to the message complexity, we propose a new metric called *self-centered message complexity*. Self-centered message complexity counts the number of messages required to detect the termination from a requester point of view rather than from the whole nodes in the system. Self-centered message can be defined as follows:

Self-centered message complexity: The number of messages required to detect the termination from a requester point of view. It is believed that this is more flexible and simpler metric to measure the structured and unstructured termination detection algorithms because some algorithms are not always intuitive and observable from a high-level domain.

#### 3 Unstructured Termination Detection Algorithm

In this section, we first review the basic gossip-based protocol based on **[17]** to describe our gossip-based termination detection algorithm. The termination detection algorithm proposed in this section can be viewed as an extension of the gossip-based algorithm to support the termination detection functionality.

#### 3.1 Basic Idea

In the gossip-based algorithm, there are two different kinds of threads in each node: active and passive. At each cycle (round), an active thread selects a neighbor at random and sends a message. The active thread then waits for the message from the receiver. Upon receiving the message from the neighbor, the active thread updates its local state with the received message and its previous information. A passive thread waits for messages from active threads and replies to the senders. Afterwards, the passive thread updates its local state with the received message from the received message from the senders.

A simple way to solve the termination detection problem is to use distributed snapshots (e.g., [3]). If a consistent snapshot of a distributed computation is taken after the distributed computation has terminated, the snapshot will capture the termination of the computation. However, the algorithm that uses distributed snapshots broadcasts to all other nodes when a process goes passive; this involves a large number of request messages. Furthermore, detecting whether all the other processes have taken a snapshot is not a trivial job even though all of processes are passive and taken a snapshot.

Hence, we take the distributed approach with the gossip-based algorithm. To let a process decide whether all of the nodes are passive and distributed computation has terminated, we use a piggy-backing mechanism by which a node adds additional information of neighbors to the message during gossiping. By using the piggy-backing mechanism, any node wishing to detect termination can eventually detect whether distributed computation is terminated or not.

In the previous researches using the distributed approach, however, they assumed that the number of nodes is static. Few studies have focused on the dynamic behavior such as adding and removing nodes while request operations are ongoing, which is that we want to deal with.

#### 3.2 Details of Termination Detection Algorithm

The unstructured termination detection algorithm using the gossip-based approach is summarized in Algorithm . We explain only our extensions to the gossip algorithm. We assume that each process has a unique identifier, which

Algorithm 1. Unstructured termination detection algorithm for  $P_i$

```

1 begin initialization

\mathsf{State}_i[j] = passive, where \forall_i \in \{1 \dots n\};

2

3

isActive = false;

4 begin at each cycle

begin upon sending <basicMessage> to P_i

5

6

State_i[j].state = State_j[j].state = active;

7

State_i[j].timestamp = State_j[j].timestamp = LC_{current};

call updateStatesArray ();

8

begin upon receiving \langle \text{basicMessage} \rangle from P_i

9

State_i[j].state = State_i[j].state = active;

10

State_i[j].timestamp = State_j[j].timestamp = LC_{current};

11

call updateStatesArray ();

12

call checkTermination ();

13

14 begin upon local computation is completed

State_i[i].state = passive;

15

State_i[i].timestamp = LC_{current};

16

17 function updateStatesArray ()

for each elements in State_i/k and State_i/k do

18

if State_i/k.timestamp < State_i/k.timestamp then

19

State_i[k].state = State_i[k].state;

20

State_i[k]. timestamp = State_i[k]. timestamp;

21

else

\mathbf{22}

State_i[k].state = State_i[k].state;

23

State_{j}[k].timestamp = State_{i}[k].timestamp;

24

25 function checkTermination ()

isActive = false;

26

foreach element in State_i/k/do

\mathbf{27}

isActive |= State<sub>i</sub>[k].state;

28

if isActive == false then

29

Termination is detected;

30

else

31

Termination is not detected;

32

```

is indexed by from 1 to n, where n is the number of processes (nodes) in the system. Henceforth, the terms a node and a process are used interchangeably. Each process  $P_i$  maintains the following data structure:

- State<sub>i</sub>[1 : n]: An array of states for  $P_i$ . This data structure consists of two components for each array element: *state* and *timestamp*. State value can be active or passive, and timestamp value is logical clock (*LC*) at which state value is updated.

#### Algorithm 2. Extended algorithm for Alg.

```

1 begin at each cycle

begin upon sending <basicMessage> to P_i

\mathbf{2}

timestamp = LC_{current};

3

BasicMsgSet_i = BasicMsgSet_i \cup (j, timestamp);

4

5 function updateStatesArray ()

if \mathsf{BasicMsgSet}_i \neq null \lor \mathsf{BasicMsgSet}_i \neq null then

6

7

foreach elements in State_i/k and State_i/k do

8

if State<sub>i</sub>/k/.timestamp < timestamp > State<sub>i</sub>/k/.timestamp <

timestamp then

// where timestamp\in (k, timestamp) in BasicMsgSet_i \cup

9

BasicMsgSet_i

\mathsf{State}_i[k].state = \mathsf{State}_i[k].state = active;

10

State_i[k].timestamp = State_j[k].timestamp = timestamp;

11

```

We describe our extensions as follows:

- 1. If  $P_i$  selects  $P_j$  during gossiping the following states are performed:

- (a) When P<sub>i</sub> sends a basic message to P<sub>j</sub>, State array is updated as follows:

i. jth elements (i.e., state and timestamp) of array of both processes are updated with active and LC<sub>current</sub>.

- (b) When P<sub>j</sub> sends a basic message to P<sub>i</sub>, State array is updated as follows:

i. *i*th elements (i.e., state and timestamp) of array of both processes are updated with active and LC<sub>current</sub>.

- (c) Each element of State[k] of both processes, where  $\forall k \in \{1 \dots n\}$ , is updated with the one whose timestamp value is fresher.

- 2. When local computation is completed, State values are updated as follows:

- (a)  $\text{State}_i[i].state$  and  $\text{State}_i[i].timestamp$  are updated with passive and  $LC_{current}$ , respectively.

- 3. In order to decide whether local computation of whole processes is completed, following states are performed:

- (a) State array is checked:

- i. If  $\text{State}_i[k]$ .state == passive, where  $\forall k \in \{1 \dots n\}$ , then it concludes that termination is detected.

- ii. Otherwise, it concludes that termination is not detected and local computation of some processes is ongoing.

Obviously, Algorithm  $\square$  works correctly if computation is distributed at the initial stage and no further basic messages are sent out. However, when basic messages are sent at arbitrary time, then the algorithm could violate the safety property. For instance, let  $P_i$  be an initiator, and  $P_j$ 's state is active and other nodes' state are passive. If  $P_j$  sends a basic message (immediately before  $P_j$  changes its state from active to passive) to  $P_k$  whose state is passive and then  $P_j$  selects  $P_i$  as a gossip target, then  $P_i$  could announce termination without knowing  $P_k$ 's state is active.

To enable our algorithm working safely, we introduce the modified algorithm. Algorithm [2] shows only the added procedures from Algorithm [1] When  $P_i$  sends a basic message to  $P_j$ , (j, timestamp) is added to BasicMsgSet<sub>i</sub>, where timestamp is the time the basic message is sent out. Then,  $P_i$  sets State<sub>i</sub>[j].state to active and State<sub>i</sub>[j].timestamp to the time the basic message is sent out.

In the updateStatesArray procedure, if BasicMsgSet<sub>i</sub> or BasicMsgSet<sub>j</sub> is not *null*, and timestamp value of k's element of State arrays is less than that of (k, timestamp), where  $(k, \texttt{timestamp}) \in \text{BasicMsgSet}_i \cup \text{BasicMsgSet}_j$ , then k's elements of State arrays are updated with active and timestamp that are in BasicMsgSet. Thus, even if a process sends a basic message at arbitrary time, our algorithm can safely announce the termination.

#### 4 Experimental Evaluation

In this section, we evaluate our unstructured termination detection algorithm compared with the broadcast algorithm and the tree-based algorithm. Due to restriction of node scalability on physical machines, we used the PeerSim simulator **13**, which supports extreme scalability and dynamicity of nodes. Furthermore, message complexity is compared to show the efficiency of our unstructured termination detection algorithm with existing algorithms. For simplicity, we assume that every node completed its local computation before a request for the termination detection is initiated.

#### 4.1 Experimental Setup and Methodology

Table II summarizes our experimental setup parameters. We assume that a request for termination detection is initiated before cycles begin. We set the size of PartialView to 20, which is 0.2% of the number of nodes. Because of the nature of dynamism of cloud computing environments, some nodes may join and leave at any time. Thus, we consider the following scenarios:

- 1. Nodes are static: nodes does not fail and join during runtime.

- 2. Nodes join during execution: some numbers of nodes are added during gossip cycle 1 through 10.

- 3. Nodes leave during execution: some numbers of nodes are removed during gossip cycle 1 through 10.

#### 4.2 PartialView Size and the Requisite Number of Cycles

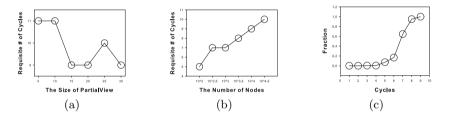

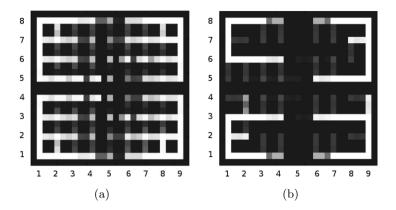

We first evaluate the impact of the size of PartialView on the requisite number of cycles. Figure 1(a) and 1(b) show the results for the requisite number of cycles to detect termination with varying the size of PartialView from 5 to 30 for  $10^4$  nodes, and with varying the number of nodes from  $10^2$  to  $10^{4.5}$  with 20 of PartialView size.

| Parameter                                 | Value          |  |  |

|-------------------------------------------|----------------|--|--|

| The number of nodes                       | 10,000         |  |  |

| Fanout                                    | 1              |  |  |

| The size of PartialView                   | 20             |  |  |

| Cycles for node joining and leaving       | 1 through $10$ |  |  |

| The number of nodes that join at a cycle  | 500            |  |  |

| The number of nodes that leave at a cycle | 100            |  |  |

Table 1. Experimental Setup Parameters

We have confirmed that the impact of the size of PartialView is unpredictable because the gossip algorithm relies on random samples. Notice that in Figure 1(b), the requisite number of cycles grows linearly as the total number of nodes increases exponentially. In Figure 1(c) shows the fraction data of the requester's State array whose state value is passive. At the early cycles, the fraction data increase slowly, but increase sharply at later cycles.

Fig. 1. The requisite numbers of cycles to detect termination and its fraction data. The number of nodes is set to  $10^4$  in (a) and (c). The size of PartialView is set to 20 in (b) and (c).

#### 4.3 Impact on Node Joining

To show the impact of node joining during a request to detect termination is in progress, we compared with existing algorithms, that is, the broadcast algorithm and tree-based algorithm. Because of node joining, the broadcast algorithm and the tree-based algorithm should re-initiate the request to detect termination. In the broadcast algorithm, the requester sends a request message to all nodes. After that, some nodes may join. In this case, the requester should receive acknowledges from all the nodes. Therefore, the broadcast algorithm should re-initiate the request to safely announce the termination. The tree-based algorithm also requires the re-initiation because it is possible that a node joins with an active state. In this case, the tree-based algorithm involves two steps: 1) rebuild a computational tree, and 2) re-initiate the request.

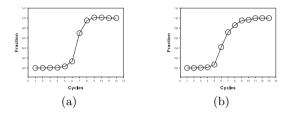

On the other hand, the unstructured algorithm does not require re-initiating the request due to its inherent property. In our scenario such that some nodes are joined at cycle 1 through 10, the number of trial for the termination detection is 11, 11 and 1 for the broadcast algorithm, the tree-based algorithm, and the unstructured algorithm, respectively. Hence, the requisite number of cycles to detect termination is 11 for the broadcast algorithm and tree-based algorithm. However, in the unstructured algorithm, it requires 13 cycles to detect termination because information about newly joined nodes should also be taken into account (see Figure 2(a)).

Fig. 2. Fraction data for the node joining scenario (a) and leaving scenario (b)

#### 4.4 Impact on Node Leaving

Like the node joining scenario, we compared three algorithms to see the impact of node leaving. As in the node joining scenario, if some nodes leave due to failure or unavailability, the broadcast algorithm and the tree-based algorithm should re-initiate the request to detect termination. Thus, the requisite number of cycles is 11 for the two algorithms.

For the unstructured algorithm, the requisite number of cycles is 12 and its fraction data are shown in Figure 2(b). The curve of the graph is changing uncertainly. This phenomenon can be explained from two extreme points of view. First, because some nodes leave from the system, the requester only needs to know information about nodes that alive. Therefore, the fraction data may increase sharply. The other extreme is that when nodes contact a node that has failed frequently, the requisite number of cycles may get delayed and the fraction data may increase slowly.

#### 4.5 Message Complexity

We analyze the message complexity of our unstructured algorithm compared with the broadcast algorithm and the tree-based algorithm. Obviously, message complexity of the broadcast algorithm is  $2 \cdot (n-1)$ , n-1 for request messages and n-1 for acknowledge messages, where n is the number of nodes. For the tree-based algorithm, message complexity is 2t, t for request messages and t for acknowledge messages, where t is the number of tasks distributed. In the worst case, message complexity of the tree-based algorithm is equivalent to the broadcast algorithm.

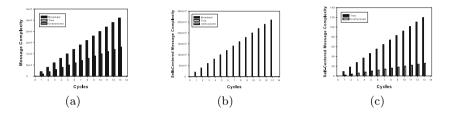

On the other hand, the message complexity of the unstructured algorithm is cn, where c is the requisite number of cycles, and n is the number of nodes. However, the message complexity of the unstructured algorithm amortized by a cycle is n. The rationale of amortizing it by a cycle is that cycles of the gossip algorithm may become infinite periodic events when we use it as, for example, a failure detection service, and that the amortized message complexity is more intuitive regarding the gossip algorithm because c will vary each run due to random uncertainty. Figure 3(a) shows the comparison of the message complexity for the static scenario.

When we analyze the self-centered message complexity, we count the messages from a requester point of view. In other words, in the unstructured algorithm, each node sees 2 messages on average because at each cycle a node selects a neighbor as a gossip target (if fanout is set to 1) and the probability of being selected as a gossip target from other nodes at a cycle is 1. Specifically,  $P_s = v/n$  $\cdot 1/v \cdot n = 1$ , where v is the size of PartialView and n is the number of nodes. For the tree-based algorithm, we assume that each node sends e basic messages, where e is the base of natural logarithm. Thus the height of the tree-based algorithm is ln(n).

The self-centered message complexity of the three algorithms for the static scenario is shown in Figure 3(b). Because the requester of the broadcast algorithm sees the whole  $2 \cdot (n-1)$  messages, the self-centered message complexity of the broadcast algorithm is huge enough to offset the other two algorithms' data. Therefore, the two algorithms' data is shown in Figure 3(c) separately. Besides the broadcast algorithm, the requester of the tree-based algorithm sees 2e messages, whereas the requester of the unstructured algorithm sees 2 messages on average at each cycle.

Figure 4(a) shows the message complexity of the three algorithms for each scenario. Note that data in Figure 4(a) are used at which until the requisite number of cycles is reached. Apart from the static scenario, the unstructured algorithm has a lower message complexity than other algorithms. Figure 4(b) shows the fraction data for the number of times that is selected from other nodes. The expectation of being selected from other nodes is 1 because  $\sum_{i=1}^{n} i \times \frac{s_i}{n} = 1$ ,

where  $s_i$  is the number of nodes selected *i* times, and *n* is the number of nodes.

Finally, Figure 4(c), 4(d) show the self-centered message complexity for each scenario. As in Figure 4(a), data for the self-centered message complexity is used at which until the requisite number of cycles is reached. The broadcast algorithm always has higher self-centered message complexity than that of the two algorithms. When we compare the tree-based algorithm and the unstructured algorithm, the phenomenon is similar to that appeared in Figure 4(a). In the static scenario, the tree-based algorithm has lower complexity but higher complexity in node joining and leaving scenarios than the unstructured algorithm.

Besides message complexity, we analyze the algorithmic properties of the three algorithms with respect to maintenance cost, re-initiating, and fault-tolerance as shown in Table 2. The tree-based algorithm is required to maintain the computational tree when node joining and leaving occur as well as when sending a basic message. The unstructured algorithm does not require re-initiating the request due to node joining and leaving but others do. In this regard, the unstructured algorithm is also fault-tolerant.

11

Table 2. Comparison of algorithms with respect to maintenance cost, re-initiating, and fault-tolerance

| Algorithm    | Maintenance cost | Re-initiating due to joins and leave | Fault tolerance |

|--------------|------------------|--------------------------------------|-----------------|

| Broadcast    | No               | Required                             | No              |

| Tree         | Required         | Required                             | No              |

| Unstructured | No               | No                                   | Yes             |

Fig. 3. Comparison of self-centered message complexity of algorithms for the static scenario

**Fig. 4.** Comparison of message complexity for each scenario (a) and the fraction data for the number of times selected from other nodes (b), and self-centered message complexity for each scenario (c) and (d)

#### 5 Conclusion

In this work, we presented a termination detection algorithm using a gossip-based approach to cope with scalability and fault tolerance issues. A cloud environment, in which the behavior of their constituting nodes is dynamic (i.e., a node may join and leave at any time), is an example to which our algorithm can be applied. Furthermore, our gossip-based termination detection algorithm could be embedded seamlessly into other existing gossip-based algorithms. In other words, if a gossip-based algorithm is implemented for the failure detection service, then the termination detection algorithm proposed in our work can be embedded into the existing gossip-based algorithm. A self-centered message complexity allows us to measure the distribution of messages of in the system. The self-centered message complexity of our proposed termination detection algorithm shows that messages are diffused among nodes almost evenly without a bottleneck.

## References

- Dijkstra, E.W., Scholten, C.S.: Termination detection for diffusing computations. Inf. Proc. Letters 11(1), 1–4 (1980)

- Mattern, F.: Algorithms for distributed termination detection. Distributed Computing 2(3), 161–175 (1987)

- Huang, S.T.: Termination detection by using distributed snapshots. Inf. Process. Lett. 32(3), 113-120 (1989)

- Mahapatra, N.R., Dutt, S.: An efficient delay-optimal distributed termination detection algorithm. J. Parallel Distrib. Comput. 67(10), 1047–1066 (2007)

- 5. Mittal, N., Venkatesan, S., Peri, S.: A family of optimal termination detection algorithms. Distributed Computing 20, 141–162 (2007)

- Livesey, M., Morrison, R., Munro, D.: The doomsday distributed termination detection protocol. Distributed Computing 19, 419–431 (2007)

- Ganesh, A., Kermarrec, A.M., Massoulie, L.: Peer-to-peer membership management for gossip-based protocols. IEEE Transactions on Computers 52(2), 139–149 (2003)

- 8. Allavena, A., Demers, A., Hopcroft, J.E.: Correctness of a gossip based membership protocol. In: Proceedings of the Twenty-Fourth Annual ACM Symposium on Principles of Distributed Computing, PODC 2005, pp. 292–301. ACM, New York (2005)

- Gurevich, M., Keidar, I.: Correctness of gossip-based membership under message loss. In: Proceedings of the 28th ACM Symposium on Principles of Distributed Computing, PODC 2009, pp. 151–160. ACM, New York (2009)

- Ganesh, A.J., Kermarrec, A.M., Massoulié, L.: Hiscamp: self-organizing hierarchical membership protocol. In: Proceedings of the 10th Workshop on ACM SIGOPS European Workshop, EW 10, pp. 133–139. ACM, New York (2002)

- Voulgaris, S., Gavidia, D., Steen, M.: Cyclon: Inexpensive membership management for unstructured p2p overlays. Journal of Network and Systems Management 13, 197–217 (2005)

- Matos, M., Sousa, A., Pereira, J., Oliveira, R., Deliot, E., Murray, P.: CLON: Overlay Networks and Gossip Protocols for Cloud Environments. In: Meersman, R., Dillon, T., Herrero, P. (eds.) OTM 2009, Part I. LNCS, vol. 5870, pp. 549–566. Springer, Heidelberg (2009)

- Jelasity, M., Montresor, A., Babaoglu, O.: T-man: Gossip-based fast overlay topology construction. Comput. Netw. 53(13), 2321–2339 (2009)

- Lim, J.B., Lee, J.H., Chin, S.H., Yu, H.C.: Group-Based Gossip Multicast Protocol for Efficient and Fault Tolerant Message Dissemination in Clouds. In: Riekki, J., Ylianttila, M., Guo, M. (eds.) GPC 2011. LNCS, vol. 6646, pp. 13–22. Springer, Heidelberg (2011)

- Lim, J., Chung, K.-S., Chin, S.-H., Yu, H.-C.: A Gossip-Based Mutual Exclusion Algorithm for Cloud Environments. In: Li, R., Cao, J., Bourgeois, J. (eds.) GPC 2012. LNCS, vol. 7296, pp. 31–45. Springer, Heidelberg (2012)

- Iwanicki, K., van Steen, M., Voulgaris, S.: Gossip-Based Clock Synchronization for Large Decentralized Systems. In: Keller, A., Martin-Flatin, J.-P. (eds.) SelfMan 2006. LNCS, vol. 3996, pp. 28–42. Springer, Heidelberg (2006)

- Jelasity, M., Guerraoui, R., Kermarrec, A.-M., van Steen, M.: The Peer Sampling Service: Experimental Evaluation of Unstructured Gossip-Based Implementations. In: Jacobsen, H.-A. (ed.) Middleware 2004. LNCS, vol. 3231, pp. 79–98. Springer, Heidelberg (2004)

- Montresor, A., Jelasity, M.: Peersim: A scalable p2p simulator. In: IEEE Ninth International Conference on Peer-to-Peer Computing, P2P 2009, pp. 99–100 (September 2009)

# Power Monitoring for Mixed-Criticality on a Many-Core Platform

Boris Motruk<sup>1</sup>, Jonas Diemer<sup>1</sup>, Rainer Buchty<sup>2</sup>, and Mladen Berekovic<sup>2</sup>

<sup>1</sup> Institute of Computer and Network Engineering

<sup>2</sup> Chair for Chip Design for Embedded Computing Technische Universität Braunschweig, Germany {motruk,diemer}@ida.ing.tu-bs.de, {buchty,berekovic}@c3e.cs.tu-bs.de

**Abstract.** Mixed-critical applications on a many-core platform have to be sufficiently independent to be certified separately. This does not only include independence in terms of time and space, but also in terms of power consumption as the available energy for a many-core system has to be shared by all running applications. Increased power consumption of one application may reduce the available energy for other applications or the reliability and lifetime of the complete chip. This paper presents a monitoring and control mechanism based on event-driven power estimation to isolate dynamic power consumption of mixed-critical applications running on a many-core platform. Isolating dynamic power consumption significantly reduces safety requirements for lower critical applications and therefore overall certification costs, making many-core systems more attractive for safety-critical applications.

**Keywords:** embedded systems, dependability, energy, fault-tolerance, isolation, many-core, mixed-criticality, monitoring, multi-core, power.

#### 1 Introduction

Time and space partitioning are mandatory for fault containment in safetycritical systems [14]. Power is another resource that has to be shared among individual applications running on the same platform. Increased power consumption of one application could negatively influence other applications of other or the same criticality. Power can be described by a dynamic and a static part. The static part is mainly due to leakage, and the dynamic part can further be divided into switching power and short-circuit power:

$$P = P_{dyn} + P_{sta} = P_{swi} + P_{sc} + P_{leak} \quad . \tag{1}$$

Switching power has the largest share of power consumption in CMOS circuits and can be expressed by

$$P_{swi} = \alpha C_L V^2 f \quad , \tag{2}$$

where V is the supply voltage,  $C_L$  are parasitic capacitances that are charged and discharged with frequency f when the corresponding component is active  $\boxed{7}$ . The

C. Hochberger et al. (Eds.): ARCS 2013, LNCS 7767, pp. 13-24, 2013.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2013

switching activity  $\alpha$  is highly dependent on the running applications and their input data **[13]**. Therefore, the amount of dynamic power consumption cannot be guaranteed in case of unspecified or faulty behavior of running applications.

A chip's overall power budget is defined at design time based on packaging and cooling, battery capacity (if applicable), and environmental conditions. Meeting this budget is especially important for battery-powered devices **18** as increased power consumption of one application would reduce the available energy for all other running applications. Moreover, high local power consumption could lead to hotspots influencing neighboring components, or may reduce the entire chip's lifetime and reliability **[21**]. Detecting over consuming applications potentially endangering safe execution of other applications requires monitoring of dynamic power consumption for each application and region separately. As the internal logic of most silicon devices is supplied by a single or few external voltage sources, it is only possible to physically measure the power consumption of the whole internal logic and not of individual regions. Even systems like Intel's Single Chip Cloud Computer (SCC) that provide several voltage islands only allow measuring the accumulated supply current, and herewith power consumption, of all cores 15. Moreover, it is impossible to identify the originator (application) of the consumed energy in a shared component  $\mathbf{3}$ , which is important to avoid thermal hazards. This makes physical measurements inapplicable to isolate dynamic power consumption of different applications at run time.

Isolation of dynamic power consumption of all individual applications is especially important for devices implementing functions of different criticality (mixedcriticality). The generic standard *IEC 61508* [1] defines four discrete criticality levels. Each level specifies requirements to be fulfilled to reduce the residual risk. If multiple functions of different criticality are implemented on the same platform without proper isolation, all have to fulfill the highest level's requirements [1]. This significantly increases certification cost for non- or low-critical applications if implemented on a shared platform together with high-critical applications. Mechanisms for time and space separation are available in most embedded systems including our platform [17], but to the best of our knowledge, this work is the first that concentrates on dynamic power isolation of mixed-critical applications on a shared platform.

The main contributions of this paper are: (1) We introduce a power analysis method for embedded systems based on an existing performance analysis method. (2) We develop a fast and lightweight monitoring and control mechanism for dynamic power consumption of individual mixed-critical applications on a single platform. (3) We implement and evaluate our mechanism on a many-core platform hosting several mixed-critical applications and show its effectiveness in case of failure of one of the running applications.

Starting with background information and related work in Section 2, we introduce our power model and analysis method in Section 3. In Section 4, we shortly explain our many-core platform and introduce its monitoring and control mechanisms. We present experiments showing the effectiveness of our approach in Section 5 before concluding in Section 6.

#### 2 Background and Related Work

The last decade saw much work on run-time power monitoring using performance monitoring counters (PMC). PMCs are available in various processors for performance measurement, but have successfully been used for power estimation. Bellosa et al. [4] discovered a strong correlation between system performance events, like floating-point operations or cache misses, and required energy. The dynamic power consumption of a system with n PMCs can then be described by multiplying the performance counter readings  $PMC_i$  with the corresponding energy per performance event  $e_i$  divided by the sampling interval  $t_{sample}$ ,

$$P_{dyn} = \frac{\sum_{i=1}^{n} (PMC_i \cdot e_i)}{t_{sample}} \quad . \tag{3}$$

The authors of [4] used microbenchmarks exclusively triggering single performance events with variable sleep intervals, e.g., floating point operations, while measuring the system's power consumption. They found a linear correlation between sleep intervals in the microbenchmarks and consumed energy. Thus, the energy consumption per performance event could be computed using linear regression technique. Bhattacharjee et al. [6] used gate-level simulations of their system instead of live measurements for event characterization. They used a power analysis tool to calculate component-wise power consumption using the system's switching activity gathered during simulation of their microbenchmarks.

To be able to estimate power consumption by counting events, power models of all components in the system are required. These power models assign one or more activating events and the corresponding consumed energy to a component or to a group of components. The number and kind of events determine the power monitoring's overhead and accuracy. Existing solutions range from very few existing counters available in standard CPUs for performance measurement [11] to counters for almost every gate activity [10]. The authors of [18] and [6] added additional counters dedicated to collect power events to existing processors. State-of-the-art microprocessors, like Intel's Sandy Bridge microprocessor [19], implement a digital power meter based on dedicated counters to track activity of the main building blocks but without allowing to identify the originator of power consumption in shared components, e.g., memories or graphics processor.

Since PMCs are not dedicated to power monitoring, additional effort must be made to extract power information from them. It is especially complicated to estimate power consumption of components outside the processor. For example, cache misses counted by PMCs are used to estimate memory activity [II]. The authors of [S] connected a monitoring unit to the system bus to estimate power consumption in memory devices based on bus traffic. Their approach could also be used for systems-on-chip (SoC) based on existing IPs without any counters that could or should be used for power monitoring. For safety-critical applications, it is even desirable not to use available counters or to add counters to existing IPs to separate monitor and monitored function [I]. In this case, power consumed in these IP cores can be modeled from their external behavior by monitoring transactions on the local busses or transactions sent over a network-on-chip (NoC). We extend this approach to estimate and control the power consumption of a many-core system as described in Section 4.1

The power information gathered by run-time power monitoring has been used for various applications, but to the best of our knowledge, has not been applied to isolate power consumption of mixed-critical applications on a shared platform. In 6, the monitored data is used for hardware-accelerated power emulation to reduce extensive simulation times for complex SoCs. Monitored data can also be used for application profiling **12**, enabling software engineers to develop poweraware applications before the chip is produced. The authors of 5 applied power information emulated by the use of PMCs for energy accounting for virtual machines in server farms. There has been much work on power management based on run-time power information. In 22, dynamic voltage scaling, and in 4, energy-aware scheduling is applied. Associated problems of heat dissipation are modeled in **2**. Hazards arising in case of extensive power consumption or occurrence of hotspots are tackled in 6.16. Tasks from overheated processors are migrated to cooler ones, or the system performance is degraded by the reduction of the frequency. Chung et al. 9 presented how activity counts translate to temperature and detected fine-grained hotspots based on PMCs, which could not be detected by the use of regular temperature sensors.

#### 3 Power Model and Analysis

Our power analysis is based on the performance analysis described by Henia et al. 13. They analyzed the system performance based on task execution times and task activating event functions  $\eta_T^+(\Delta t)$  and  $\eta_T^-(\Delta t)$ .  $\eta_T^+(\Delta t)$  specifies the maximum number of activating events for task T that can occur during any time interval of length  $\Delta t$  and  $\eta_T^-(\Delta t)$  specifies the minimum number of events. Schliecker et al. 20 extended this model with the definition of the shared-resource request bound  $\tilde{\eta}_{T\to S}^+(\Delta t)$  and the aggregate busy time.  $\tilde{\eta}_{T\to S}^+(\Delta t)$  is the maximum number of requests that may be issued from a task T to a shared resource S within a time-window of size  $\Delta t$  and the aggregate busy time accumulates the product of the number of operations to a shared resource and the corresponding amount of time to be completed. For our power analysis, we replace the required amount of time per operation with the amount of energy per operation. The weights of these energy events can be gathered using microbenchmarks and linear regression technique 4.6.12. Since we estimate power consumption from component's external interfaces and transactions sent over local busses and the NoC, energy weights that depend on the corresponding component's internal state or on past events are modeled with an energy interval. Following the notation introduced by Schliecker et al.,  $\tilde{e}^+_{T\to S}$  and  $\tilde{e}^-_{T\to S}$  are the maximum and minimum energy required for a task T to access a resource S. For example, an event for a component in idle state may cost more energy because of a possible wake-up overhead. Another example is writing data to the same location in memory twice. Writing both times the same data would cost less energy than writing different data because reloading the capacitance of that memory location is not required. To be able to give power guarantees to different applications, we are mainly interested in safe upper bounds for power consumption of individual applications and energy density in components in close proximity. Therefore, we use the upper bounds  $\tilde{e}_{T\to S}^+$  for our analysis and power/energy budget allocation.

From event functions and energy weights, the maximum dynamic energy consumed by the set of all running tasks  $\mathbf{T}$  using the set of all available resources  $\mathbf{S}$  in any time interval of length  $\Delta t$  is expressed by

$$E^{+}_{\mathbf{T}\to\mathbf{S}}(\Delta t) = \sum_{T_i\in\mathbf{T}} \left( \sum_{S_k\in\mathbf{S}} \tilde{\eta}^{+}_{T_i\to S_k}(\Delta t) \cdot \tilde{e}^{+}_{T_i\to S_k} \right) \quad . \tag{4}$$

The worst-case average dynamic power consumption of the analyzed system in any time interval of length  $\Delta t$  is then given by

$$P_{dyn}^{+}(\Delta t) = \frac{E_{\mathbf{T}\to\mathbf{S}}^{+}(\Delta t)}{\Delta t} \ . \tag{5}$$

To detect a possible hotspot in a specific area on the die, the maximum possible power density for this area in any time interval of length  $\Delta t$  has to be calculated. Therefore, the subset  $\mathbf{S}^* \subseteq \mathbf{S}$  of all resources in this area has to be used in Equation **5** can also be used to get the worst-case average dynamic power consumption per application. In this case, the subset of all tasks  $\mathbf{T}^* \subseteq \mathbf{T}$  of the investigated application has to be entered into the equation.

From the overall power budget of the device and analyzed power requirements of all applications, power/energy budgets can be assigned to individual applications and regions. If, at run time, the number of energy events originated by a low-critical application differs from the one used for analysis, e.g., due to less strict safety requirements, power guarantees given to high-critical applications may not hold any longer. Therefore, we introduce a monitoring and control mechanism in Section 4.1 to limit the number of energy events per application to the number used during analysis. This requires the monitoring and control mechanism to be certified to the highest level of criticality but not the lower critical applications.

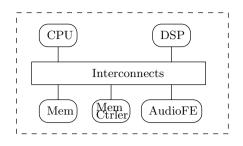

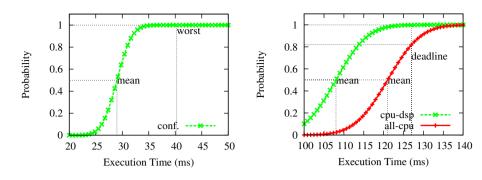

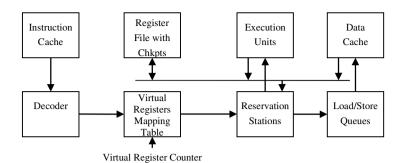

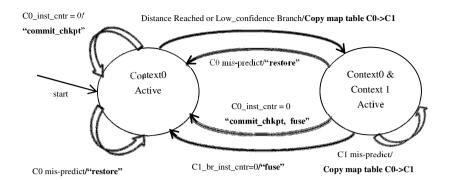

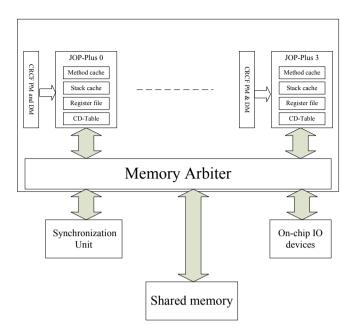

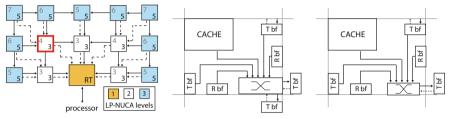

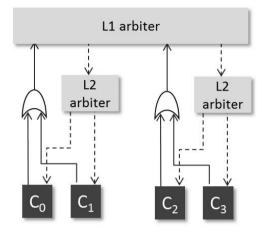

#### 4 Architecture

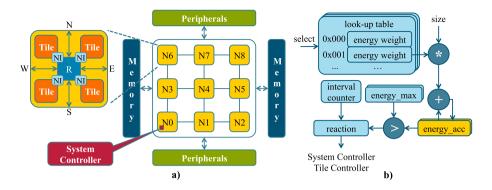

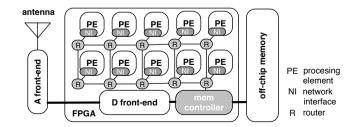

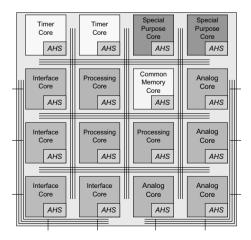

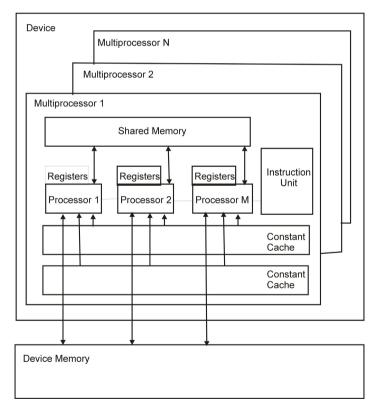

Our Integrated Dependable Architecture for Many-Cores (IDAMC) [IT] is a research vehicle for developing and evaluating methods and mechanisms for reduced certification cost for trusted multi-core platforms. It consists of nodes (N) connected by a network-on-chip. The number of nodes as well as the network topology is configurable. Fig. [I] shows 9 nodes connected by a 2D mesh network. Each node includes a router (R) and up to 4 tiles connected by network interfaces (NI). Tiles are based on Gaisler's *GRLIB* IP library including the open-source *LEON3* processor and various other IPs connected to local buses. Tiles are configurable as well and reach from simple processing or memory tiles, containing a

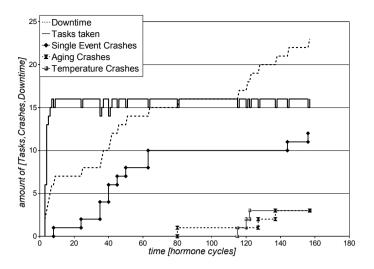

Fig. 1. System Overview and Power Monitoring

single core or memory controller respectively, to complete systems with multiple cores, peripherals and memory interfaces. One of the tiles acts as system controller, assigning resources to applications and supervising their safe execution. Mapping of physical memory interfaces and peripherals to local applications is done by address translation tables (ATT) in the network interfaces. The ATT translates local tile addresses to addresses in destination tiles and contains required routing information. The system controller can re-program the tables at run time. This enables replacing faulty peripherals or memory interfaces, and re-mapping of applications to other tiles without interaction or knowledge of the running application.

#### 4.1 Power Monitoring and Control

Activity in local masters, and peripheral and memory usage in local and remote tiles cost energy. Energy consumption estimation is performed using event counters as described in Section <sup>[2]</sup>. First, the local per-tile power consumption is monitored to detect hotspots caused by an application running locally or a remote application accessing a local resource. Second, the power consumption caused by every application is monitored separately even if power is consumed in another tile, e.g., shared memory. This way, the total available power budget, like any other shared resource, can be allocated to individual applications in the system. The collected power information is used to detect and prevent excessive dynamic power consumption of individual applications, assuring independence of the running applications, especially high-critical ones. We monitor and isolate power consumption in the network interfaces connecting the tiles and the rest of the system, separating monitor and monitored function [1]. Thus, only single applications or applications of same criticality should be mapped to the same processing tile representing an error containment zone.

Per-tile energy density is monitored by counting and weighting activity in local masters and slaves. Increased local dynamic power consumption could also be caused by a master in another tile sending an unexpectedly high number of requests to local slaves. For local power density monitoring it does not matter if the originator of local activity is an application running locally or on a core in another tile. The expected thermal emission based on the estimated energy density can be calculated using the approach presented by [21].

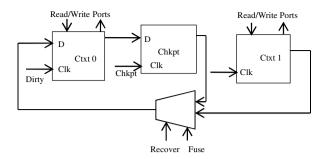

To monitor local power consumption within each tile, two of the look-up tables (LUT) shown in Fig.  $\square$  are programmed with energy weights for activity in local masters and slaves. When an event is detected, the corresponding energy amount multiplied by access size (in words) is added to an energy accumulator (*energy\_acc*). For increased accuracy, the local masters' table may include weights for different events per master, e.g., activity in floating-point units or coprocessors. Our experiments presented in Section 5.2 showed that the difference in energy consumption of different operations within the *LEON3* core compared to such of remote memory accesses is negligible. Therefore, the LUTs for local masters contain a single (the largest) energy weight per master. The LUT entries for local masters are selected by signals extracted from the cores' debug interfaces. Similar to [S], the table for local slaves contains weights for local slave accesses. This table's entries are selected by slave select signals of the local bus.

Dynamic per-application energy consumption, monitored in the network interfaces, is calculated by accumulating and weighting all activity issued by the locally running application, no matter if consumed locally or outside the tile. For estimating a locally running application's power, energy consumed in local slaves is only accumulated if originated by a local master. Monitoring dynamic power consumption caused by a local application but consumed in other tiles is done by utilizing *IDAMC*'s ATTs: each activation selects a corresponding entry in the third LUT shown in Fig. D, containing required energy to access a module in the respective address range. The energy weights contain an entire request's consumed energy, including local busses and the NoC. Thus, the energy weights of two resources of same type may differ if located in tiles with different distances to the source tile.

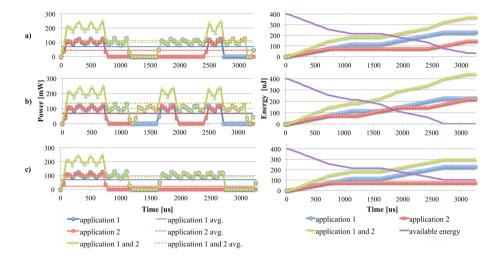

To not only isolate applications on *IDAMC* in terms of time and space but also in terms of energy, energy budgets (energy max) per time period have to be monitored for each tile and application individually, especially of low-critical applications to prevent any interference with high-critical ones. Two different energy accumulators and maximum energy values are implemented. One is required for power consumption (energy density) per tile independent of the originator, the other for power consumption per application including power consumed in other tiles and the NoC. Appropriate budgets are derived from analyzing the power requirements of all applications and the chip's overall power budget as described in Section 3. The system controller stores these upper bounds in the power monitoring and control modules in the network interfaces of all tiles. Moreover, an interval counter is programmed with the corresponding time period. When this counter elapses without any energy budget exceeding its maximum, the energy accumulators are reset. If one of the limits exceeds within the corresponding time period at run time due to a possible fault or unexpected input data. the following reactions can be taken: (1) A message can be sent to the system

controller for further analysis, advanced reactions like remapping of applications, or simple error collection. (2) The tile can be paused until the end of the time period preventing further activity and herewith dynamic power consumption in the current time period. At the end of the time period, the application continues where it was stopped. (3) The tile can be reset to recover from a possible transient error. It is not restarted before the end of the selected time period; an immediate restart could lead to further dynamic power consumption. (4) The tile can be disabled, isolating a tile potentially containing a permanent defect.

The last three listed reactions could also be executed by the system controller after receiving a message. Due to network latency and overhead of software running on the system controller, this option's reaction time to prevent further dynamic power consumption of an application exceeding it budgets is much longer than a reaction executed directly by hardware in the NIs. Moreover, this time increases with the size of the system and is hard to predict. Therefore, a centralized solution can not be used to guarantee separation of applications of different criticality on a many-core platform.

Note that the implemented reactions do not target the optimization of power consumption of the running applications but only preventing a faulty (low-critical) application from negatively affecting a high-critical application running on another tile. Therefore, neither effects of the reactions on the locally running (faulty) application, nor other possible reactions, like power/clock gating or voltage/frequency scaling, are further investigated.

Our proposed dynamic power estimation and control mechanism is done in parallel with address translation or local slave access and hence does not add any latency. On detecting an exceeded power budget, a faulty application can be prevented from consuming further dynamic power without delay. This reaction time can be guaranteed and does not increase with a larger number of tiles. Our mechanism's area overhead depends on the number of events required for estimating power consumption of local masters and slaves, and distributed resources supported by the ATTs. An implementation of our mechanism supporting a single local master, 16 local slaves, and 32 distributed resources per tile increases area by around 2.4%. Every additional event to be monitored increases only the memory requirements by 8 additional bits per energy weight. The amount of required logic stays constant also for a large number of monitored events.

#### 5 Evaluation

We implemented an *IDAMC* baseline system on a *Virtex-6 LX760* FPGA to evaluate our proposed mechanism at minimal synthesis/simulation time. Since our distributed power monitoring and control mechanism does not require a central instance at run time **17**, our setup's small number of tiles does not limit general applicability. The approach is also applicable for ASICs using a standard cell library similar to **6**. Our baseline system comprises 4 routers with a single connected tile each. Tile 0, the system controller, includes a debug interface, UART, timer unit, interrupt controller and 256 kB on-chip memory. It

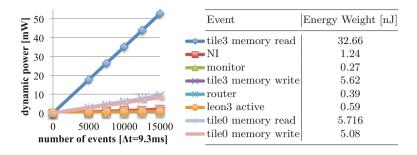

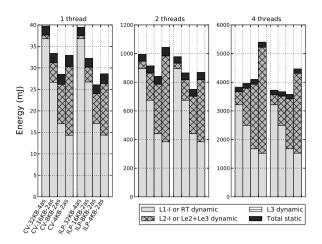

Fig. 2. Energy Weights

controls the other tiles and assigns resources to applications. Tile 1 and Tile 2 are memory-less processing tiles with a single core, 1 kB of data and instruction cache each, timer unit, and interrupt controller. Tile 3 contains 2 MB of on-chip memory shared by applications running on the processing tiles.

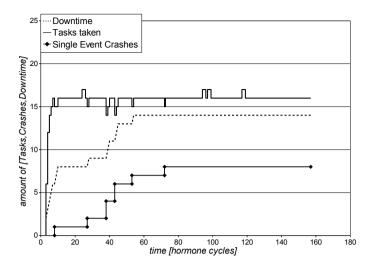

#### 5.1 Event Characterization

We used microbenchmarks and linear regression technique as described in [4.6] for characterizing all events in local masters and slaves, and remote slaves with the largest impact on dynamic power consumption. These microbenchmarks consist of a variable number of operations exclusively triggering single or a small number of components. For example, we used microbenchmarks that write/read a different number of words to/from the shared memory in Tile 3 to get the energy per read/written word consumed in the network interfaces, the NoC's routers, and the on-chip memory. The overall switching activity of the placed and routed design gathered during simulating the individual microbenchmarks is fed into Xilinx' XPower Analyzer tool. With this method, we get component-wise power consumption for each microbenchmark as proposed by 6. From power consumption of a specific microbenchmark and number and type of operations used in it, we calculate per-event energy (energy weight) using linear regression technique, similar to 12 and as shown in Fig. 2 Reading the large on-chip memory in Tile 3 consumes much more power than the different operations in the LEON3 core. Therefore, we use a single energy weight (the largest measured) for all operations of the LEON3 core with only a small impact on the overall accuracy. Systems with different components, memory or cache sizes require an additional one-time effort for event selection and characterization but no changes to the proposed methodology. Reading and writing the on-chip memory in Tile 3 includes the complete transfer's energy (2x NI, 1x monitor, 2x router). In larger systems, a single router's weight as in Fig. 2 can be used to calculate energy weights for memory accesses in tiles requiring a different number of hops in the NoC.

We evaluated the accuracy of our model while running more complex workloads based on the Dhrystone benchmark [23]. The error of estimated power consumption vs. real power consumption taken from post place-and-route

|       |             | Activation | Run-          | Memo  | ry Acc. | LEON3         | Worst-case      | e Energy per   | Worst-case |

|-------|-------------|------------|---------------|-------|---------|---------------|-----------------|----------------|------------|

| App.  | Criticality | Interval   | time          | Reads | Writes  | (act. cycles) | activation      | interval       | Avg. Power |

| A1    | high        | 1.6ms      | 1.2ms         | 3337  | 291     | 2625          | $112.17  \mu J$ | $224.34 \mu J$ | 69.03  mW  |

| A2    | none/low    | 2.4ms      | $720 \ \mu s$ | 2107  | 180     | 1640          | $70.73  \mu J$  | $141.46 \mu J$ | 43.53mW    |