Kerstin Eder João Lourenço Onn Shehory (Eds.)

# LNCS 7261

# Hardware and Software: Verification and Testing

7th International Haifa Verification Conference, HVC 2011 Haifa, Israel, December 2011 Revised Selected Papers

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Kerstin Eder João Lourenço Onn Shehory (Eds.)

# Hardware and Software: Verification and Testing

7th International Haifa Verification Conference, HVC 2011 Haifa, Israel, December 6-8, 2011 Revised Selected Papers

Volume Editors

Kerstin Eder University of Bristol, Department of Computer Science Merchant Venturers Building 3.25, Woodland Road, Bristol BS8 1UB, UK E-mail: kerstin.eder@bristol.ac.uk

João Lourenço NOVA University of Lisbon, Department of Computer Science and Engineering FCT-UNL, Quinta da Tore, 2829-516 Caparica, Portugal E-mail: joao.lourenco@fct.unl.pt

Onn Shehory IBM Research Labs at Haifa Haifa University Campus, Mount Carmel, Haifa 31905, Israel E-mail: onn@il.ibm.com

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-642-34187-8 e-ISBN 978-3-642-34188-5 DOI 10.1007/978-3-642-34188-5 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2012950042

CR Subject Classification (1998): D.2.4-5, D.3.1, F.3.1-2, D.2.11, I.2.2-3

LNCS Sublibrary: SL 2 – Programming and Software Engineering

© Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

This volume contains the papers presented at the Haifa Verification Conference 2011, the 7th in the series of annual conferences dedicated to advancing the state of the art and state of the practice in verification and testing of hardware and software. HVC provides a forum for researchers and practitioners from both academia and industry to share their work, exchange ideas, and discuss challenges and future directions of testing and verification for hardware, software, and hybrid systems.

Academic research in system verification and testing is roughly divided into two major paradigms: formal verification and dynamic verification (testing). Within each paradigm, algorithms, techniques and even terminology may differ considerably between hardware-related solutions and software-related solutions. However, the common underlying goal of verification, across paradigms and system types, is to gain confidence in a system meeting its functional as well as its non-functional requirements. HVC is the only conference that brings together researchers and practitioners from all verification and testing sub-fields, thereby encouraging the migration of methods and ideas among domains. One key asset of HVC is the strong participation from industry. HVC provides a platform for the academic and industrial research communities to mix and mingle, thereby creating new opportunities for collaborative research. We are particularly proud to say that the papers selected for presentation at HVC 2011 covered a wide range of sub-fields related to testing and verification applicable to software, hardware, and hybrid systems, thus stimulating discussion within the wider verification community.

From a total of 43 submissions, the Program Committee selected 15 regular papers for full presentation, three tools papers for short presentation, and four posters for the student poster session on day one of the conference. HVC 2011 was organized in five technical sessions devoted to topics including synthesis, formal verification, software quality, testing, and coverage. The best paper selection jury considered both the quality of the technical paper as well as the presentation at the conference. The best paper prize was awarded to Marijn Heule, Oliver Kullmann, Siert Wieringa, and Armin Biere for their paper entitled "Cube and Conquer: Guiding CDCL SAT Solvers by Lookaheads."

Granted since 2007, the HVC award recognizes the most promising academic and industrial contribution to the fields of testing and software and hardware verification from the last five years. The HVC 2011 award went to Daniel Kroening from Oxford for his contribution of CBMC, a bounded model checker for C programs. CBMC is the first and most influential industrial-strength verification engine for a non-academic programming language, and hence a major milestone in automated verification. To date, CBMC is the only verification engine that supports the full functionality of C, including precise modeling of floating-point operations and bit-precise arithmetic. CBMC promotes the industrial adoption of formal software verification more than any other tool in existence and is therefore a significant contribution to the verification community.

The conference was hosted by IBM at the IBM Research Labs in Haifa. We would like to thank all who made HVC 2011 run smoothly and gratefully acknowledge the invaluable support by many on the IBM administrative team, without which this event could not meet its goals and match the high standards established over the years. We would like to thank the Program Committee, the HVC Award Committee, the Best Paper Prize Jury, the authors of all submissions to HVC 2011 and, of course, the presenters of the papers and posters accepted. All these contributed toward making HVC 2011 another success in the HVC conference series. We would also like to thank the tutorial presenters Avner Engel, Ofer Strichman, and Rachel Tzoref-Brill for an informative first day prior to the main conference. Special thanks are due to our invited speakers who enriched the program with insightful and inspiring presentations: Kathryn Kranen, Jasper Design Automation, Ben Liblit, University of Wisconsin-Madison, Klaus-Dieter Schubert, IBM Deutschland Research and Development GmbH, and Armin Biere, Johannes Kepler University, Linz.

Finally, we would like to thank our sponsors, IBM, Cadence, Mentor Graphics, and Jasper Design Automation, for their generous support in preparation and throughout the event.

July 2012

Kerstin Eder João Lourenço Onn Shehory

# Organization

# General Chair

| Onn Shehory                   | IBM Haifa Labs, Israel                                             |  |

|-------------------------------|--------------------------------------------------------------------|--|

| Program Chairs                |                                                                    |  |

| Kerstin Eder<br>João Lourenço | University of Bristol, UK<br>New University of Lisbon,<br>Portugal |  |

| Tutorials Chair               |                                                                    |  |

#### **Tutorials** Chair

| Oz Hershkovitz I | IBM Haifa Labs, Israel |

|------------------|------------------------|

|------------------|------------------------|

# Local Organization

| Yair Harry    | IBM Haifa Labs, Israel | (Webmaster)       |

|---------------|------------------------|-------------------|

| Shirley Namer | IBM Haifa Labs, Israel | (Local Logistics) |

| Onn Shehory   | IBM Haifa Labs, Israel | (Coordinator)     |

# **Program Committee**

| Sharon Barner       | IBM Haifa Labs, Israel                                |

|---------------------|-------------------------------------------------------|

| Geoff Barrett       | Broadcom, UK                                          |

| Armin Biere         | Institute for Formal Models and Verification, Austria |

| Eyal Bin            | IBM Haifa Labs, Israel                                |

| Roderick Bloem      | Graz University of Technology, Austria                |

| Michael Browne      | IBM, USA                                              |

| Michael Butler      | University of Southampton, UK                         |

| Radu Calinescu      | University of Aston, UK                               |

| Hana Chockler       | IBM Haifa Labs, Israel                                |

| Kerstin Eder        | University of Bristol, UK                             |

| Eitan Farchi        | IBM Haifa Labs, Israel                                |

| Harry Foster        | Mentor Graphics, USA                                  |

| Franco Fummi        | University of Verona, Italy                           |

| Ian G. Harris       | University of California Irvine, USA                  |

| Ziyad Hanna         | Jasper DA, USA                                        |

| Klaus Havelund      | JPL, USA                                              |

| Alan Hu             | University of British Columbia, USA                   |

| Mika Katara         | Tampere University of Technology, Finland             |

| Zurab Khasidashvili | Intel, Israel                                         |

| University of Haifa, Israel              |

|------------------------------------------|

| Ben Gurion University, Israel            |

| New University of Lisbon, Portugal       |

| Oxford University, UK                    |

| IBM Haifa Labs, Israel                   |

| University of Lugano, Switzerland, and   |

| University of Milano Bicocca, Italy      |

| IBM Haifa Labs, Israel                   |

| VirginiaTech, USA                        |

| Microsoft Research, USA                  |

| IBM Haifa Labs, Israel                   |

| University of Genova, Italy              |

| University of Surrey, UK                 |

| Innovations Ltd., Israel                 |

| Vienna University of Technology, Austria |

| Paderborn University, Germany            |

|                                          |

### HVC Award Committee

| Shmuel Ur      | Innovations Ltd., Israel (Chair)          |

|----------------|-------------------------------------------|

| Ian G. Harris  | University of California Irvine, USA      |

| Klaus Havelund | JPL, USA                                  |

| Mika Katara    | Tampere University of Technology, Finland |

| Ofer Strichman | Technion, Israel                          |

# Additional Referees

Sam Bayless Christian Bird John Colley Chris Derobertis Ricardo Dias Andrew Edmunds Cindy Eisner Ranan Fraer Jim Grundy Georg Hofferek Andreas Holzer Alexander Ivrii Kenneth Johnson Antti Jääskeläinen Robert Koenighofer Dmitry Korchemny Anatoly Koyfman

Yael Meller Madanlal Musuvathi Ziv Nevo Avigail Orni Andrey Rybalchenko Alexander Schremmer Carl Seger Martina Seidl Dominik Steenken Dorian Thomas Rachel Tzoref-Brill Heikki Virtanen Matti Vuori Sven Walther Nick Wiggins Chao Yan

# Table of Contents

# Invited Talks

| Preprocessing and Inprocessing Techniques in SAT<br>Armin Biere                                                                    | 1  |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| Pioneering the Future of Verification: A Spiral of Technological<br>and Business Innovation                                        | 2  |

| Automated Detection and Repair of Concurrency Bugs<br>Ben Liblit                                                                   | 3  |

| Verification Challenges of Workload Optimized Hardware Systems<br>Klaus-Dieter Schubert                                            | 4  |

| Synthesis                                                                                                                          |    |

| Synthesis with Clairvoyance<br>Orna Kupferman, Dorsa Sadigh, and Sanjit A. Seshia                                                  | 5  |

| Generalized Reactivity(1) Synthesis without a Monolithic Strategy<br>Matthias Schlaipfer, Georg Hofferek, and Roderick Bloem       | 20 |

| Formal Verification                                                                                                                |    |

| IIS-Guided DFS for Efficient Bounded Reachability Analysis of Linear<br>Hybrid Automata<br>Lei Bu, Yang Yang, and Xuandong Li      | 35 |

| Cube and Conquer: Guiding CDCL SAT Solvers by Lookaheads<br>Marijn J.H. Heule, Oliver Kullmann, Siert Wieringa, and<br>Armin Biere | 50 |

| Implicative Simultaneous Satisfiability and Applications<br>Zurab Khasidashvili and Alexander Nadel                                | 66 |

| Liveness vs Safety – A Practical Viewpoint<br>B.A. Krishna, Jonathan Michelson, Vigyan Singhal, and Alok Jain                      | 80 |

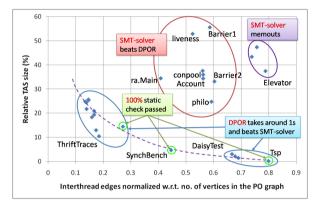

| Predicting Serializability Violations: SMT-Based Search vs.<br>DPOR-Based Search                                                   | 95 |

# Software Quality

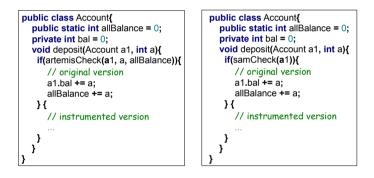

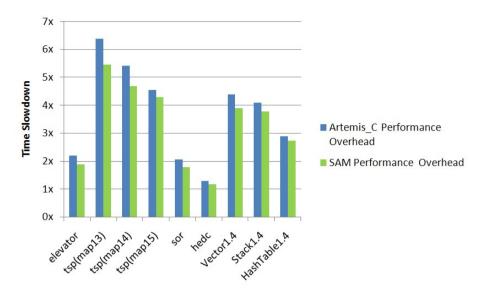

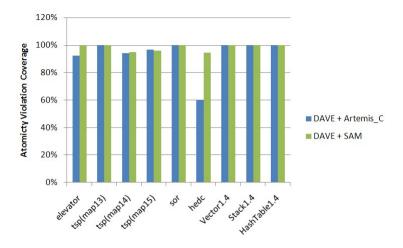

| SAM: Self-adaptive Dynamic Analysis for Multithreaded Programs<br>Qichang Chen, Liqiang Wang, and Zijiang Yang                 | 115 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Concurrent Small Progress Measures<br>Michael Huth, Jim Huan-Pu Kuo, and Nir Piterman                                          | 130 |

| Specification and Quantitative Analysis of Probabilistic Cloud<br>Deployment Patterns                                          | 145 |

| Interpolation-Based Function Summaries in Bounded Model<br>Checking<br>Ondrej Sery, Grigory Fedyukovich, and Natasha Sharygina | 160 |

| Can File Level Characteristics Help Identify System Level<br>Fault-Proneness?<br>Thomas J. Ostrand and Elaine J. Weyuker       | 176 |

# Testing and Coverage

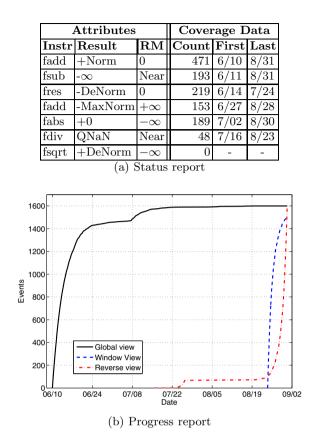

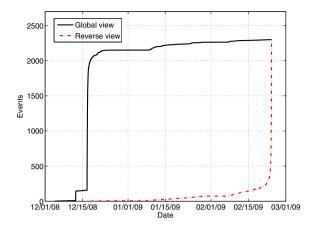

| Reverse Coverage Analysis<br>Ariel Birnbaum, Laurent Fournier, Steve Mittermaier, and Avi Ziv            | 190 |

|----------------------------------------------------------------------------------------------------------|-----|

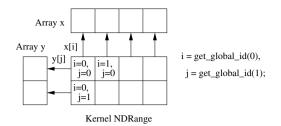

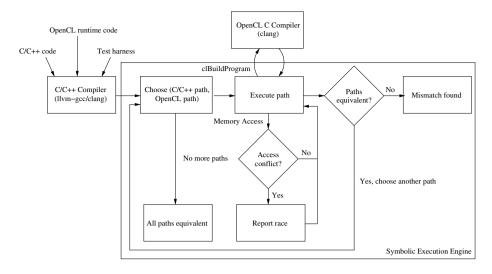

| Symbolic Testing of OpenCL Code<br>Peter Collingbourne, Cristian Cadar, and Paul H.J. Kelly              | 203 |

| Dynamic Test Data Generation for Data Intensive Applications<br>Allon Adir, Ronen Levy, and Tamer Salman | 219 |

# Experience and Tools

| Injecting Floating-Point Testing Knowledge into Test Generators<br>Merav Aharony, Emanuel Gofman, Elena Guralnik, and<br>Anatoly Koyfman | 234 |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Combining Theorem Proving and Symbolic Trajectory Evaluation<br>in THM&STE                                                               | 242 |

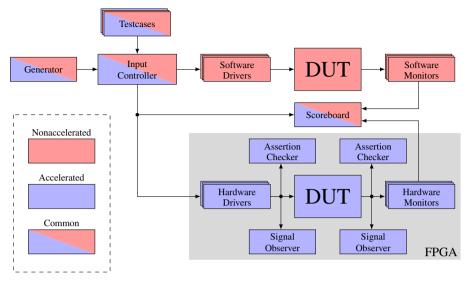

| HAVEN: An Open Framework for FPGA-Accelerated Functional<br>Verification of Hardware<br>Marcela Šimková, Ondřej Lengál, and Michal Kajan | 247 |

# Posters – Student Event

| On-Line Detection and Prediction of Temporal Patterns<br>Shlomi Dolev, Jonathan Goldfeld, and Rami Puzis                             | 254 |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Function Summaries in Software Upgrade Checking<br>Grigory Fedyukovich, Ondrej Sery, and Natasha Sharygina                           | 257 |

| The Rabin Index of Parity Games (Extended Abstract)<br>Michael Huth, Jim Huan-Pu Kuo, and Nir Piterman                               | 259 |

| Using Computational Biology Methods to Improve Post-silicon<br>Microprocessor Testing<br>Ron Zeira, Dmitry Korchemny, and Ron Shamir | 261 |

| Author Index                                                                                                                         | 263 |

# Preprocessing and Inprocessing Techniques in SAT

Armin Biere

Johannes Kepler University Altenbergerstr. 69 4040 Linz Austria

**Abstract.** SAT solvers are used in many applications in and outside of Computer Science. The success of SAT is based on the use of good decision heuristics, learning, restarts, and compact data structures with fast algorithms. But also efficient and effective encoding, preprocessing and inprocessing techniques are important in practice. In this talk we give an overview of old and more recent inprocessing and preprocessing techniques starting with ancient pure literal reasoning and failed literal probing. Hyper-binary resolution and variable elimination are more recent techniques of this century. We discuss blocked-clause elimination, which gives a nice connection to optimizing encodings and conclude with our recent results on unhiding redundancy fast.

#### Speaker Bio

Since 2004 Prof. Armin Biere chairs the Institute for Formal Models and Verification at the Johannes Kepler University in Linz, Austria. Between 2000 and 2004 he held a position as Assistant Professor within the Department of Computer Science at ETH Zürich, Switzerland. In 1999 Biere was working for a start-up company in electronic design automation after one year as Post-Doc with Edmund Clarke at CMU, Pittsburgh, USA. In 1997 Biere received a Ph.D. in Computer Science from the University of Karlsruhe, Germany.

His primary research interests are applied formal methods, more specifically formal verification of hardware and software, using model checking, propositional and related techniques. He is the author and coauthor of more than 60 papers and served on the program committee of more than 45 international workshops and conferences. His highest influential work is the contribution to Bounded Model Checking. Decision procedures for SAT, QBF and SMT, developed by him or under his guidance rank at the top of many international competitions. Besides organizing several workshops Armin Biere was co-chair of SAT'06 and FMCAD'09. He is on the editorial board of the Journal on Satisfiability, Boolean Modeling and Computation (JSAT), and is one of the editors of the Handbook of Satisfiability. He also organizes the Hardware Model Checking Competition.

# Pioneering the Future of Verification: A Spiral of Technological and Business Innovation

Kathryn Kranen

Jasper Design Automation 100 View St., Suite 101 Mountain View 94041 United States

**Abstract.** Changing the way the world verifies semiconductors and systems takes far more than algorithmic or methodological breakthroughs. Over the past two decades, there have been four or five great verification breakthroughs, while many other promising technologies have been relegated to the dust bin. Bringing a nascent EDA technology to mainstream use and commercial success requires alternating technological and business innovations to accelerate adoption.

In this session, you'll learn key concepts about bringing a disruptive technology to widespread adoption. Kathryn Kranen will share insights gained as a market pioneer of three technologies that have become the major pillars of today's mainstream system-on-chip verification: hardware emulation, constrained-random simulation, and formal property verification. You will also hear some of her visions of what the future of design and verification may hold.

#### Speaker Bio

Kathryn Kranen is responsible for leading Jasper's team in successfully bringing the company's pioneering technology to the mainstream design verification market. She has more than 20 years EDA industry experience and a proven management track record. While serving as president and CEO of Verisity Design, Inc., US headquarters of Verisity Ltd., Kathryn and the team she built created an entirely new market in design verification. (Verisity later became a public company, and was the top-performing IPO of 2001.) Prior to Verisity, Kathryn was vice president of North American sales at Quickturn Systems. She started her career as a design engineer at Rockwell International, and later joined Daisy Systems, an early EDA company. Kathryn graduated Summa cum Laude from Texas A&M University with a B.S. in Electrical Engineering. Kathryn is serving her fifth term on the EDA Consortium board of directors, and was elected its vice chairperson. In 2005, Kathryn was recipient of the prestigious Marie R. Pistilli Women in Electronic Design Automation (EDA) Achievement Award. In 2009, EE Times listed Kathryn as one of the "Top 10 Women in Microelectronics".

# Automated Detection and Repair of Concurrency Bugs

Ben Liblit

Computer Sciences Department University of Wisconsin–Madison 1210 West Dayton Street Madison, WI 53706-1685 United States

**Abstract.** Finding and fixing concurrency bugs is critical in modern software systems. This talk examines two recent efforts to automate both the detection and the repair of certain types of concurrency bugs using a mixture of static, dynamic, and statistical methods.

First, we present a low-overhead instrumentation framework to diagnose production-run failures caused by concurrency bugs. We track specific thread interleavings at run-time, using sparse random sampling to limit overhead. Methods drawn from work in statistical debugging let us identify strong failure predictors among the sampled concurrent behaviors. Our approach offers a spectrum of performance and diagnosis capabilities suitable for wide deployment to real user desktops.

Second, we describe a strategy for automatically fixing one of the most common types of concurrency bugs in real-world code. Starting with descriptions of bad interleavings, our tool automatically inserts synchronization operations to steer future executions away from danger. Static analyses help us maintain good performance while reducing the risk of deadlocks. Dynamic monitoring allows for run-time recovery from deadlocks that could not be statically avoided.

Overall, our approach yields overheads too low to reliably measure; produces small, simple, understandable patches; and completely eliminates detected bugs in the targeted class across a variety of complex, real-world applications.

#### Speaker Bio

Ben Liblit is an associate professor in the Computer Sciences Department of the University of Wisconsin–Madison, with research interests in programming languages and software engineering. Professor Liblit worked as a professional software engineer for four years before beginning graduate study. His experience has inspired a research style that emphasizes practical, best-effort solutions that bring formal methods to bear against the ugly complexities of real-world software development.

Professor Liblit completed his Ph.D. in 2004 at UC Berkeley with advisor Alex Aiken. He earned the 2005 ACM Doctoral Dissertation Award for his work on post-deployment statistical debugging, and has received AFOSR Young Investigator and NSF CAREER awards in support of his research.

# Verification Challenges of Workload Optimized Hardware Systems

Klaus-Dieter Schubert

IBM Deutschland Research and Development GmbH Systems & Technology Group 71032 Böblingen Germany

**Abstract.** Over the last couple of years it became more and more obvious that improvements in chip technology get smaller and smaller with each generation. Processor frequency is stagnating for some time now and single thread performance of general purpose processor cores is only increasing very slowly from generation to generation despite the fact that designers have more and more transistors they can utilize.

However, to stay competitive in the Compute Server business it is necessary to follow Moore's law and provide significant performance improvements to the customer every year. This begs the question how this can be achieved when traditional ways like cycle time improvements and the usage of more transistors are not yielding the desired results. The answer has to be a combination of logic, system and software design.

This talk will first describe why continuing with "business as usual" will fail going forward. It will then discuss a number of scenarios for workload optimized systems to overcome these hurdles before the focus will shift to the question: What challenges will that present to the area of hardware verification?

#### Speaker Bio

Klaus-Dieter Schubert received the Dipl.-Ing. degree in electrical engineering in 1990 from Stuttgart University (Germany). Subsequently, he joined IBM in Boeblingen and has been responsible for hardware verification of various IBM mainframe systems and its components. He was the technical lead for the hardware verification of the z900 2064 system before he moved to the field of hardware and software co-verification where he established the concept of virtual power-on (VPO) for zSeries and pSeries systems. From 2006 to 2008, Mr. Schubert was on a work assignment in Austin, Texas, where he has led the verification team for the POWER7 microprocessor. Today he is an IBM Distinguished Engineer and the technical leader for the hardware verification of future POWER processors. He has received two IBM Outstanding Achievement Awards for his contributions in the field of hardware verification.

# Synthesis with Clairvoyance\*

Orna Kupferman<sup>1</sup>, Dorsa Sadigh<sup>2</sup>, and Sanjit A. Seshia<sup>2</sup>

<sup>1</sup> Hebrew University, School of Engineering and Computer Science, Jerusalem, Israel <sup>2</sup> UC Berkeley, EECS Department, Berkeley CA, USA

**Abstract.** We consider the problem of automatically synthesizing, from a linear temporal logic (LTL) specification, a system that is guaranteed to satisfy the specification with respect to all environments. Algorithms for solving the synthesis problem reduce it to the solution of a game played between the system and its environment, in which the system and environment alternate between generating outputs and inputs respectively. Typically, the system is required to generate an output right after receiving the current input. If a solution to the game exists, the specification is said to be realizable.

In this paper, we consider the role of clairvoyance in synthesis, in which the system can "look into the future," basing its output upon future inputs. An infinite look-ahead transforms the realizability problem into a problem known as universal satisfiability. A thesis we explore in this paper is that the notion of clairvoyance is useful as a heuristic even in the general case of synthesis, when there is no lookahead. Specifically, we suggest a heuristic in which we search for strategies where the system and the environment try to force each other into hopeless states in the game — states from which they cannot win, no matter how large the lookahead. The classification to hopeful and hopeless states is thus based on a modified notion of universal satisfiability where the output prefix is constrained. Our approach uses the automata for the specification in the process of classification into hopeful and hopeless states, and uses the structure of the automata in order to construct the game graph, but the important point is that the game itself is a reachability game. We demonstrate the efficiency of our approach with examples, and outline some directions for future work exploring the proposed approach.

#### 1 Introduction

A frequent criticism against verification methods is that verification is done after significant resources have already been invested in the development of the system. The critics argue that the desired goal is to use the specification in the system development process in order to guarantee the design of correct systems. This is called *automatic synthesis*. Formally, given a specification to a reactive system, typically by means of an LTL formula, the goal in automatic synthesis is to transform it into a system that is guaranteed to satisfy the specification.

<sup>\*</sup> This research was supported in part by NSF grant CNS-0644436 and the Gigascale Systems Research Center, one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity.

<sup>&</sup>lt;sup>1</sup> To make life interesting, several different methodologies in system design are all termed "synthesis". The automatic synthesis we study should not be confused with *logic synthesis*, which is a process by which an abstract form of a desired circuit behavior (typically, register transfer level, which by itself may be the outcome of yet another synthesis procedure, termed *high-level synthesis*) is turned into a design implementation by means of logic gates.

K. Eder, J. Lourenço, and O. Shehory (Eds.): HVC 2011, LNCS 7261, pp. 5-19, 2012.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2012

In the late 1980s, several researchers realized that the classical approach to system synthesis, where a system is extracted from a proof that the specification is satisfiable, is well suited to *closed* systems, but not to *open* (also called *reactive* [10]) systems [114]21]. A reactive system interacts with its environment, and a correct system should satisfy the specification with respect to all environments. The right way to approach synthesis of reactive systems is to consider the situation as a (possibly infinite) game between the environment and the system. More formally, a strategy for a system with inputs in I and outputs in O maps finite sequences of inputs — words in  $(2^I)^*$ , which correspond to the actions of the environment so far, to an output in  $2^O$  — a suggested action for the system. A specification  $\psi$  over  $I \cup O$  is then *realizable* iff there is a strategy all of whose computations satisfy  $\psi$ , whre the computation of a strategy  $f : (2^I)^* \to 2^O$  on a infinite sequence  $i_0, i_1, i_2, \ldots \in (2^I)^{\omega}$  is  $i_0 \cup f(\epsilon), i_1 \cup f(i_0), i_2 \cup f(i_0 \cdot i_1), \ldots$ . The synthesis problem for  $\psi$  is to return a finite-state transducer that realizes it (or an answer that  $\psi$  is not realizable).

While model-checking theory has led to industrial development and use of formalverification tools, the integration of synthesis in the industry is slow. This has to do with *theoretical limitations*, like the complexity of the problem (the synthesis problem for linear temporal logic (LTL) is 2EXPTIME-complete [21]), methodological reasons (the traditional solutions to the synthesis problem require the determinization of automata on infinite words [23] and the solution of parity games [15]), and *practical reasons*: the difficulty of writing complete specifications and environment assumptions, the lack of satisfactory compositional synthesis algorithms, and suboptimal results (current algorithms produce systems that satisfy the specification, but may be larger or less well-structured than systems constructed manually, and may satisfy the specification in a peculiar way).

In the last decade there has been a significant advances in the development of practical algorithms for synthesis. In the theoretical fronts, researchers have suggested LTL synthesis algorithms that circumvent determinization and parity games [17], algorithms for fragments of LTL that can be implemented symbolically [20], and algorithms that reduce LTL synthesis to the solution of safety games [6]. These algorithms have been implemented [7113,14,20], and they also support basic compositional synthesis [7116]. Synthesis tools that are based on them give encouraging recent results (c.f., synthesis of an arbiter for RAM's on-chip AMBA advanced high-performance bus from temporal specifications [9], an electronic voting machine [5], and more). Work has also been done on generating environment assumptions to reduce the specification burden for synthesis [18].

In this paper we describe a new approach for solving LTL synthesis. Consider an LTL formula  $\psi$ . Like earlier approaches, our main goal is to circumvent the determinization of the automaton for  $\psi$  and the solution of parity games. Unlike earlier approaches, our algorithm is based on reducing the synthesis problem to a solution of a reachability game, played between the system and the environment on a graph obtained by combining the subset constructions of the automata for  $\psi$  and  $\neg \psi$ . Our algorithm is a heuristic – the goals of the system and the environment in the reachability game are not dual, and it may be that no player can force the opponent to its target states. Even in that case, the information obtained from the game enables us to restrict standard synthesis algorithms to a subset of

the game, which is often much smaller. In addition, as we elaborate below, our algorithm involves theoretical issues at the heart of the synthesis problem that we believe should get more attention. In particular, we study *synthesis with clairvoyance (look-ahead)*, which is strongly related to the need to work with deterministic automata [11,12].

Let us now explain the idea behind our algorithm. Recall that satisfiability of an LTL formula  $\psi$  only guarantees that there is a collaborative input sequence  $x \in (2^I)^{\omega}$  with which the system can interact and generate an output sequence  $y \in (2^O)^{\omega}$  such that the composition of x and y into a computation in  $(2^{I\cup O})^{\omega}$  satisfies  $\psi$ . On the other hand, in realizability, the system should have a strategy that satisfies the specification with respect to all possible environments. Between the satisfiability and the realizability problems, one can consider universal satisfiability, where for every input sequence  $x \in (2^I)^{\omega}$ , there is an output sequence  $y \in (2^O)^{\omega}$  such that the composition of x and y satisfies  $\psi$ . Clearly, not all satisfiable specifications are universally satisfiable. Also, it is not hard to see that while universal satisfaction is a necessary condition for realizability, it is not a sufficient condition. A good way to understand the difference between realizability and universal satisfiability is to consider realizability with lookahead – a notion that generalizes both of them. In realizability with look-ahead k, for  $k \ge 0$ , we also seek a strategy for the system. Here, however, the system generates the output at position j only after seeing the input in all positions up to j + k. It is easy to see that realizability coincides with realizability with look-ahead 0, whereas universal satisfiability coincides with realizability with look-ahead  $\infty$ .

Look-ahead helps the system in two ways. First, when the ability to satisfy the specification depends on information from the future, the look-ahead reveals the future. Second, when different futures with the same prefix require different outputs, look-ahead postpones the need to commit to the same output for both futures. One may wonder if these two ways are not two different interpretation of the same extra burden that realizability poses on universal satisfiability, and indeed this is the case. In fact, this is exactly the same burden that requires us to determinize the specification automaton in the process of solving the realizability problem: different input sequences that share the same prefix may need to follow different runs of the nondeterministic automaton, and the run may differ already in the joint prefix. A look-ahead enables us to follow different runs in the joint prefix, as long as the difference between the sequences is "in the range of visibility" of the strategy.

With all this in mind, our algorithm works as follows. First, we try our luck and check whether  $\psi$  is universally satisfiable. If it is not, then clearly  $\psi$  is also non-realizable and we are done. If it is, then we again try our luck and check whether  $\neg \psi$  is strongly satisfiable by the environment. If it is not, then again we are done, as we can conclude that  $\neg \psi$ is not realizable by the environment, making  $\psi$  realizable by the system, and in fact it is easy to find a transducer for it – the transducer can ignore the input and just generates the output that witnesses the fact  $\neg \psi$  is not universally satisfiable by the environment. Note that checking universal satisfaction is much simpler than checking realizability, not just from a theoretical point of view (the problem is EXPSPACE-complete [24]), but also in practice – universal satisfaction amounts to checking universality of a non-

<sup>&</sup>lt;sup>2</sup> This is similar to the link between online/offline algorithms and deterministic/nondeterministic automata [2].

deterministic Büchi word automaton. Our experiments show that we may actually be lucky quite often.

Our algorithm becomes more interesting when both  $\psi$  and  $\neg \psi$  are universally satisfiable. Then, we know that with an infinite look-ahead, both the system and the environment can satisfy their dual goals, and it is only the nature of the interaction, which requires both of them to proceed on-line, that makes only one of  $\psi$  and  $\neg \psi$  realizable. Consider a prefix  $w \in (2^{I \cup O})^*$  of a computation. We can say that the system is *hopeful* after w if  $\psi$  stays universally satisfiable even when the interaction is restricted to start with w. Note that in the definition of universal satisfaction, the outputs are existentially quantified. Thus, fixing the outputs in w may indeed prevent  $\psi$  from being universally satisfiable. Dually, the environment is hopeful after w if  $\neg \psi$  stays universally satisfiable. Our algorithm checks whether the system has a strategy to force the environment to a prefix of a computation after which only the system is hopeful, and dually for the environment. In the first case, we can conclude that  $\psi$  is realizable, and we also get a transducer for it. In the second, we know that  $\neg \psi$  is realizable by the environment. The good news is that the classification of prefixes can be reduced to a sequence of checks for universal satisfaction, and is needed only for prefixes the lead to different states in the subset construction of the automata for  $\psi$  and  $\neg \psi$ , with no determinization needed. Also, as noted above, in case neither the system nor the environment have a strategy to make the opponent hopeless, we can restrict traditional synthesis algorithms to take into an account the need of the system and the environment to stay in a hopeful set of states. As our examples show, our algorithm often terminates with a definite answer, and it may also leads to a significant reduction in the state space. In Section  $\mathbf{6}$  we also point to other advantages of our algorithm.

Finally, we study synthesis with look-ahead and describe an algorithm for solving it. A solution for the problem is described already in [12] in the context of sequential calculus, Here, we adjust the solution to the modern setting of LTL and parity games, and relate it to our heuristic. Beyond the theoretical interest in realizability with look-ahead as a notion between universal satisfiabaility and realizability, look-ahead is interesting also from a practical point of view. As we demonstrate in the paper (see also [3111]), look-ahead can make the difference between a specification being realizable and not being realizable. Since in practice we often do have a look-ahead (say, when the environment buffers its actions), it makes sense to use it.

#### 2 Preliminaries

#### 2.1 Satisfiability, Universal Satisfiability, and Realizability

Let *I* and *O* be finite sets of input and output signals, respectively. For an input sequence  $x = i_0, i_1, \ldots \in (2^I)^{\omega}$  and an output sequence  $y = o_0, o_1, \ldots \in (2^O)^{\omega}$ , the *computation*  $x \oplus y$  is the interleaved sequence  $i_0 \cup o_0, i_1 \cup o_1, \ldots \in (2^{I \cup O})^{\omega}$ .

Consider an LTL formula  $\psi$  over  $I \cup O$ . We consider three levels of satisfaction of  $\psi$ .

- The formula  $\psi$  is *satisfiable* if there is a computation that satisfies  $\psi$ .

<sup>&</sup>lt;sup>3</sup> An orthogonal research direction is to study the cases in which this happens, and the setting in which a bounded lookahead is sufficient. As shown in [11], such problems are decidable.

- The formula  $\psi$  is *universally satisfiable* if for every input sequence  $x \in (2^I)^{\omega}$ , there is an output sequence  $y \in (2^O)^{\omega}$  such that  $x \oplus y$  satisfies  $\psi$ .

- The formula  $\psi$  is *realizable* if there is a strategy  $f : (2^I)^* \to 2^O$  such that for every input sequence  $x = i_0, i_1, i_2, \ldots \in (2^I)^\omega$ , the computation of f on x, that is  $i_0 \cup f(\epsilon), i_1 \cup f(i_0), i_2 \cup f(i_0 \cdot i_1), \ldots$  satisfies  $\psi$ .

It is not hard to see that realizability implies universal satisfiability, which implies satisfiability, but not the other way around. For example, let  $I = \{q\}$  and  $O = \{p\}$ . It is easy to see that the formula Gq is satisfiable but not universally satisfiable. Also, the formula  $G(p \leftrightarrow q)$  is universally satisfiable but not realizable. Indeed, if, by way of contradiction, f is a strategy that realizes it, then an input sequence x that starts with qif  $f(\epsilon) = \emptyset$  and starts with  $\{\emptyset\}$  if  $f(\epsilon) = \{p\}$  is such that the computation of f on xdoes not satisfy  $p \leftrightarrow q$ , and hence does not satisfy  $G(p \leftrightarrow q)$ .

We note that in our definition of realizability, we did not require the strategy f to be finite state. Since LTL formulas induce regular languages, adding such a requirement would result in an equivalent definition [22]. Formally, a strategy  $f : (2^I)^* \to 2^O$  is finite state if for every  $o \in 2^O$ , the language  $f^{-1}(o)$ , which is a subset of  $(2^I)^*$ , is regular. Equivalently, f is finite state if it is induced by a finite-state transducer – a deterministic automaton over the alphabet  $2^I$  in which each state is labeled by a letter in  $2^O$ . Then, given a sequence  $w \in (2^I)^*$ , the strategy f induced by the transducer is such that f(w) is the label of the state that the transducer visits after reading w.

#### 2.2 Automata on Infinite Words

A specification over  $I \cup O$  can be viewed as a language over the alphabet  $2^{I \cup O}$ . The decision procedures for the three levels of satisfaction discussed above follow this view, and are based on automata on infinite words.

A nondeterministic automaton is a tuple  $\mathcal{A} = \langle \Sigma, Q, Q_0, \delta, \alpha \rangle$ , where  $\Sigma$  is a finite nonempty alphabet, Q is a finite nonempty set of states,  $Q_0 \subseteq Q$  is a nonempty set of initial states,  $\delta : Q \times \Sigma \to 2^Q$  is a transition function, and  $\alpha$  is an acceptance condition. The automaton  $\mathcal{A}$  is *deterministic* if  $|Q_0| = 1$  and  $|\delta(q, \sigma)| \leq 1$  for all states  $q \in Q$  and symbols  $\sigma \in \Sigma$ .

A run r of  $\mathcal{A}$  on an infinite word  $w = \sigma_1 \cdot \sigma_2 \cdots \in \Sigma^{\omega}$  is an infinite sequence  $q_0, q_1, \ldots$  of states such that  $q_0 \in Q_0$ , and for all  $i \ge 0$ , we have  $q_{i+1} \in \delta(q_i, \sigma_{i+1})$ . The acceptance condition  $\alpha$  determines which runs are accepting. In the *Büchi* acceptance condition,  $\alpha \subseteq Q$ , and a run r is accepting if it visits some state in  $\alpha$  infinitely often. Formally, let  $inf(r) = \{q : q_i = q \text{ for infinitely many } i$ 's  $\}$ . Then, r is accepting iff  $inf(r) \cap \alpha \neq \emptyset$ . A word w is accepted by an automaton  $\mathcal{A}$  if there is an accepting run of  $\mathcal{A}$  on w. The language of  $\mathcal{A}$ , denoted  $L(\mathcal{A})$ , is the set of words that  $\mathcal{A}$  accepts. We say that  $\mathcal{A}$  is empty if  $L(\mathcal{A}) = \emptyset$  and that  $\mathcal{A}$  is universal if  $L(\mathcal{A}) = \Sigma^{\omega}$ . A pre-automaton is an automaton without an acceptance condition. We use NBW and DBW to abbreviate nondeterministic and deterministic Büchi automata, respectively.

We are going to mention also the *co-Büchi* and the *parity* acceptance conditions. The condition co-Büchi is dual to Büchi, thus a run is accepting if it visits  $\alpha$  only finitely often. The parity is more complicated and for our purposes here it is enough to note that determistic parity automata (DPWs) are sufficiently expressive to recognize

all the languages recognized by nondeterministic Büchi automata. Thus, NBWs can be translated to DPWs [19.23].

**Theorem 1.** [25] For every LTL formula  $\psi$ , there is an NBW  $\mathcal{A}_{\psi}$  with  $2^{O(|\psi|)}$  states such that  $L(\mathcal{A}_{\psi}) = \{w : w \models \psi\}.$

#### 2.3 Traditional Decision Procedures

In this section we briefly review the traditional algorithms for solving satisfiability, universal satisfiability, and realizability.

Deciding satisfiability is PSPACE-complete: given  $\psi$ , one can follow Theorem and constructs the NBW  $\mathcal{A}_{\psi}$ . Clearly,  $\psi$  is satisfiable iff  $L(\mathcal{A}_{\psi})$  is not empty. Since the size of  $\mathcal{A}_{\psi}$  is exponential in the length of  $\psi$  and checking its nonemptiness can be done on-the-fly in NLOGSPACE, the PSPACE complexity follows.

Deciding universal satisfiability is more complicated and is EXPSPACE-complete: Starting with  $\mathcal{A}_{\psi}$ , we construct an NBW  $\mathcal{A}_{\psi}^{\exists O}$ , obtained from  $\mathcal{A}_{\psi}$  by taking its projection on I. That is, if  $\mathcal{A} = \langle 2^{I \cup O}, Q, Q_0, \delta, \alpha \rangle$ , then  $\mathcal{A}_{\psi}^{\exists O} = \langle 2^I, Q, Q_0, \delta^{\exists O}, \alpha \rangle$ , where for a state  $q \in Q$  and input  $i \in 2^I$ , we have that  $\delta^{\exists O}(q, i) = \{s : \exists o \in 2^O \text{ such that } s = \delta(q, i \cup o)\}$ . It is not hard to see that a word  $x \in (2^I)^{\omega}$  is accepted by  $\mathcal{A}_{\psi}^{\exists O}$  iff there is a word  $y \in (2^O)^{\omega}$  such that  $x \oplus y$  is accepted by  $\mathcal{A}$ . Hence,  $\mathcal{A}_{\psi}^{\exists O}$  is universal iff  $\psi$  is strongly satisfiable. Checking the universality of  $\mathcal{A}_{\psi}^{\exists O}$  can be done by checking the emptiness of its complement. Since the size of  $\mathcal{A}_{\psi}$ , and hence also of  $\mathcal{A}_{\psi}^{\exists O}$  is exponential in the length of  $\psi$ , complementation involves an exponential blow-up, and emptiness can be checked in NLOGSPACE, the EXPSPACE complexity follows.

Finally, deciding realizability is even more complicated, and is 2EXPTIME-complete. The traditional algorithm determinizes  $\mathcal{A}_{\psi}$ , and transforms the obtained DPW into a two-player game between the system and the environment. Formally, let  $\mathcal{D}_{\psi} = \langle 2^{I \cup O}, Q, q_0, \delta, \alpha \rangle$  be the DPW for  $\psi$ . Then, the game is  $G_{\psi} = \langle V, E \rangle$ , where the set of vertices  $V = V_{sys} \cup V_{env}$  is such that  $V_{sys} = Q$  and  $V_{env} \subseteq 2^Q$ . For  $S \in 2^Q$ , we have that  $S \in V_{env}$  iff there is  $q \in Q$  and  $o \in 2^O$  such that  $S = \delta^{\exists I}(q, o)$ , in which case E(q, S). Also, E(S, q') iff  $q' \in S$ . Deciding the realizability problem then amounts to deciding the winner in the game  $G_{\psi}$  with winning objective  $\alpha$ . Intuitively, each transition of  $\mathcal{D}_{\psi}$  is partitioned in the game  $G_{\psi}$  into two transitions: consider a vertex  $q \in V_{sys}$ . First, the system chooses an output  $o \in 2^O$ , and the game moves to the vertex  $\delta^{\exists I}(q, o) \in V_{env}$ . Then, the environment chooses an input  $i \in 2^I$  and the game continues to the state in  $\delta^{\exists I}(q, o)$  that i leads to, namely to  $\delta(q, i \cup o) \in V_{sys}$ .

It is sometimes convenient to refine  $G_{\psi}$  to include more information, which enables a labeling of the edges by the actions taken by the players. Thus, here  $E \subseteq (V_{sys} \times 2^O \times V_{env}) \cup (V_{env} \times 2^I \times V_{sys})$ . For that, we define,  $V_{sys} = Q$  and  $V_{env} \subseteq Q \times 2^O \times 2^Q$ is such that  $\langle q, o, S \rangle \in V_{env}$  iff  $S = \delta^{\exists I}(q, o)$ . Then, we also have  $E(q, o, \langle q, o, S \rangle)$ . In addition, for all vertices  $\langle q, o, S \rangle \in V_{env}$  and  $q' \in V_{sys}$ , we have that  $E(\langle q, o, S \rangle, i, q')$ iff  $q' = \delta(q, i \cup o)$ . Note that  $q' \in S$ .

The system and the environment are dual, in the sense that we can view the setting as one in which the environment is trying to satisfy  $\neg \psi$  when it interacts with all systems. Thus, the roles of the system and the environment may be switched, and we can talk about a formula  $\psi$  being universally satisfied by the environment, meaning that for

every output sequence  $y \in (2^O)^{\omega}$ , there is an input sequence  $x \in (2^I)^{\omega}$  such that  $x \oplus y$ satisfies  $\psi$ . We can also talk about  $\psi$  being realizable by the environment, meaning that there is a finite-state strategy  $g : (2^O)^* \to 2^I$  such that for every output sequence  $y = o_0, o_1, o_2, \ldots \in (2^O)^{\omega}$ , the computation of g on y, that is  $o_0 \cup g(o_0), o_1 \cup g(i_0 \cdot o_1), o_2 \cup g(o_0 \cdot o_1 \cdot o_2), \ldots$  satisfies  $\psi$ . Note that in both types of realizability (by the system and by the environment), the system moves first. Thus, the settings are not completely dual. For universal satisfiability, the identity of the player that moves first is irrelevant, and the definitions are completely dual. From determinancy of games, we know that either  $\psi$  is realizable by the system or  $\neg \psi$  is realizable by the environment.

#### **3** Using Universal Satisfiability

In this section we describe the first steps in our methodology for using universal satisfiability in the process of checking realizability. We also point to realizability with look-ahead as a notion between universal satisfiability and realizability.

Given a property  $\psi$  over I and O, we proceed as follows.

- (1) Check universal satisfiability of  $\psi$ .

- (1.1) If the answer is negative, we are done. Indeed, if  $\psi$  is not universally satisfiable, then clearly  $\psi$  is also not realizable.

- (1.2) If the answer is positive, proceed to (2).

- (2) Check universal satisfiability of  $\neg \psi$  by the environment.

- (2.1) If the answer is negative, we are done. Indeed, if ¬ψ is not universally satisfiable by the environment, then clearly ¬ψ is also not realizable by the environment, implying that ψ is realizable by the system. Moreover, a transducer for ψ can simply generate the output sequence y ∈ (2<sup>O</sup>)<sup>ω</sup> for which for all x ∈ (2<sup>I</sup>)<sup>ω</sup> we have that x ⊕ y ⊨ ψ.

- (2.2) If the answer is positive, proceed to (3).

- (3) This is the interesting case: both ψ and ¬ψ are universally satisfiable. Note that while it cannot be that both ψ and ¬ψ are realizable, they can both be universally satisfiable. When this happens, we know that one of the players, the system or the environment, cannot arrange the responses that work for the universal satisfiability in the form of the strategy that is needed for realizablity. For example, consider the formula ψ = G(p ↔ q), with I = {q} and O = {p}. Note that ¬ψ = F(¬(p ↔ q)). While both ψ and ¬ψ are universally satisfiable, only ¬ψ is realizable by the environment.

The example of a robotic vehicle controller from [18], demonstrates how our heuristic detects that the system is not realizable when sufficient assumptions are not provided. The example of the robotic vehicle controller aims to synthesize a discrete planner that allows an autonomous robot to move in a rectangular grid, while avoiding obstacles. The obstacles are put and cleared by the environment at arbitrary times and squares. In this example, the specification  $\psi$  is of the form  $\mathbf{A} \to \mathbf{G}$ , where  $\mathbf{A}$  is a conjunction of

<sup>&</sup>lt;sup>4</sup> The cleanest way to handle this lack of duality is to parameterize the synthesis problem with a "who moves first" flag. We decided to keep the setting simpler and let the system move first in both settings.

assumptions on the environment, and **G** is a conjunction of guarnatees. The guarantees require the car to start at the initial square, and in each step to move to an adjacent square or to stay in the current one. The car cannot move to an occupied square, and it eventually have to reach the destination square. The assumptions on the environment require that there are no obstacles at the initial and destination squares. With this weak assumption,  $\psi$  is not universally satisfied and our heuristic terminates at Step (1.1). In order to make the specification realizble, we need to add stronger assumptions to **A**. Adding the assumption that "all the squares must be clear of obstacles infinitely often" resolves the problem, and makes  $\psi$  realizable. Here too, out heuristic is helpful, as with the stronger assumption we get that  $\neg \psi$  is not universally satisfied by the environment, thus our heuristic terminates at Step (1.2).

Before we proceed to describe how our algorithm continues in Step (3), let us discuss the situation in more detail. Consider again the formula  $\psi = G(p \leftrightarrow q)$ . As noted above,  $\psi$  is not realizable. Intuitively, once the system generates an output, the environment can generate an input that does not agree with the polarity of the output, thus violating the specification. But what if the system can generate its output only after seeing the next input? Then, the specification is realizable. In general, the difference between universal satisfiability and realizability is the fact that in universal satisfiability the system has to react online and generate the next output without knowing the inputs yet to come. Between these two extreme cases, we can talk about *realizability with look-ahead*, where the system has to generate the next output after seeing a prefix of the inputs yet to arrive.

**Definition 1.** [realizable with look-ahead] An LTL formula  $\psi$  over  $I \cup O$  is realizable with look-ahead k (k-realizable, for short), if there is a strategy  $f : (2^I)^{\geq k} \to 2^O$  such that for every input sequence  $w = i_0, i_1, i_2, \ldots \in (2^I)^{\omega}$ , the computation of f on w, that is  $i_0 \cup f(i_0, i_1, \ldots, i_{k-1}), i_1 \cup f(i_0, i_1, \ldots, i_k), i_2 \cup f(i_0, i_1, \ldots, i_{k+1}), \ldots, i_j \cup f(i_0, i_1, \ldots, i_{k+j-1}), \ldots$  satisfies  $\psi$ .

As explained in Section  $\blacksquare$  both universal satisfiability and realizability are a special cases of k-realizability; the first with  $k = \infty$  and the second with k = 0. Also, realizability with look-ahead is interesting also in practice, as it corresponds to realistic settings and can make specifications realizable [11]12].

#### 4 When Both $\psi$ and $\neg \psi$ Are Universally Satisfiable

In this section we continue the description of our algorithm, namely what to do when we get to Step (3). Let  $\mathcal{A}_{\psi} = \langle 2^{I\cup O}, S, S_0, \rho, \alpha \rangle$  and  $\mathcal{A}_{\neg \psi} = \langle 2^{I\cup O}, S', S'_0, \rho', \alpha' \rangle$  be NBWs for  $\psi$  and  $\neg \psi$ , respectively. Let  $\mathcal{U}_{\psi}$  be the pre-automaton obtained by applying the subset construction to  $\mathcal{A}_{\psi}$  and  $\mathcal{A}_{\neg\psi}$ . Thus,  $\mathcal{U}_{\psi} = \langle 2^{I\cup O}, 2^S \times 2^{S'}, \langle S_0, S'_0 \rangle, \delta \rangle$ , where for all  $\langle P, P' \rangle \in 2^S \times 2^{S'}$  and  $\sigma \in 2^{I\cup O}$ , we have that  $\delta(\langle P, P' \rangle, \sigma) =$  $\langle \rho(P, \sigma), \rho'(P', \sigma) \rangle$ . For a state  $\langle P, P' \rangle$  of  $\mathcal{U}_{\psi}$ , let  $L(\mathcal{A}_{\psi}^P)$  and  $L(\mathcal{A}_{\neg\psi}^P)$  be the languages of  $\mathcal{A}_{\psi}$  and  $\mathcal{A}_{\neg\psi}$  with initial sets P and P', respectively. We say that a set  $P \in 2^S$  is *system hopeful* (sys-hopeful, for short) if for all  $x \in (2^I)^{\omega}$  there is  $y \in (2^O)^{\omega}$  such that  $x \oplus y \in L(\mathcal{A}_{\psi}^P)$ . We say that a set  $P' \in 2^{S'}$  is *environment hopeful* (env-hopeful, for short) if for all  $y \in (2^O)^{\omega}$  there is  $x \in (2^I)^{\omega}$  such that  $x \oplus y \in L(\mathcal{A}^{P'}_{\neg\psi})$ . Thus, system hopefulness coincides with universal satisfaction, except that instead of talking about satisfaction of an LTL formula we talk about the membership in the language of  $\mathcal{A}^P_{\psi}$ . Dually, environment hopefulness refer to membership in  $\mathcal{A}^{P'}_{\neg\psi}$ .

Consider a state  $\langle P, P' \rangle \in 2^S \times 2^{S'}$  of  $\mathcal{U}_{\psi}$ . It is possible to decide in space exponential in the length of  $\psi$  whether P is system hopeful and whether P' is environment hopeful. Indeed, the check is similar to the check for universal satisfaction described in Section [2]. For the case of system hopefulness, we project  $\mathcal{A}_{\psi}^P$  on  $2^I$  and check that the obtained NBW is universal. For environment hopefulness we do the same, with  $\mathcal{A}_{\neg\psi}^{P'}$  and a projection on  $2^O$ .

*Remark 1.* In case we start with a deterministic automaton  $\mathcal{D}_{\psi}$  for the specification, we do not have to apply the subset construction, and we can work directly with  $\mathcal{D}_{\psi}$ . Then, the notion of system and environment hopefulness applies to single states, and checking whether a state *s* is env-hopeful is done by dualizing  $\mathcal{D}_{\psi}$ , thus getting a deterministic co-Büchi automaton for the negation of  $\psi$ . We can then project the co-Büchi automaton existentially on  $2^O$ , and check whether the result is universal (see Example []).

We can now describe the continuation of the algorithm:

- (3) Consider the game induced by the pre-automaton  $\mathcal{U}_{\psi}$ .

- (3.1) If the system has a strategy to reach a state  $\langle P, P' \rangle$  such that P is sys-hopeful and P' is not env-hopeful, then we are done. Indeed,  $\psi$  is realizable, and we can also have a transducer for it.

- (3.2) If the environment has a strategy to reach a state  $\langle P, P' \rangle$  such that P' is envhopeful and P is not sys-hopeful, then we are done. Indeed, in a manner dual to the one above,  $\neg \psi$  is realizable by the environment.

- (3.3) If we got here, both the system and the environment have strategies to stay forever in the region of states that are both sys-hopeful and env-hopeful. At this point we give up and turn to solve the realizability problem using one of the traditional algorithms. The information gathered during our algorithm is still useful and enables us to restrict the realizability game to states in the region of hopeful states (all the other states are replaced by two states – one is winning for the system and one is winning for the environment).

We conclude the description of the algorithm with the following theorem.

**Theorem 2.** Consider an LTL specification  $\psi$  over  $I \cup O$ .

- 1. If the algorithm reaches Step (3), then all the states  $\langle P, P' \rangle$  that are reachable in  $\mathcal{U}_{\psi}$  are such that at least one of the sets P and P' is hopeful.

- 2. If the algorithm terminates in Steps (2.1) or (3.1), then  $\psi$  is realizable and the checks done by the algorithm induce a transducer for the system that satisfies  $\psi$ .

- 3. If the algorithm terminates in Steps (1.1) or (3.2), then  $\psi$  is not realizable and the check done induce a transducer for the environment that satisfies  $\neg \psi$ .

**Proof:** We start with the first point. Consider a state  $\langle P, P' \rangle$  that is reachable in  $\mathcal{U}_{\psi}$ . Let w be a word that leads to  $\langle P, P' \rangle$ . Consider now the parity game that corresponds to the realizability problem for  $\psi$  and the vertex  $v_w$  that the game reaches after the system and the environment proceeds according to w. Since parity games are determined,  $v_w$ is a winning vertex for either the system (in which case P must be hopeful) or the environment (in which case P' must be hopeful).

Now, if the algorithm terminates Step (2.1), then  $\psi$  is realizable as a transducer for it can simply generate the output sequence  $y \in (2^O)^{\omega}$  for which for all  $x \in (2^I)^{\omega}$  we have that  $x \oplus y \models \psi$ ; the fact  $\neg \psi$  is not universally realizable by the environment guarantees that such a sequence y exists, and we know how to find it: this is the sequence that witnesses the nonemptiness of the complement of  $\mathcal{A}_{\neg\psi}^{\exists I}$ .

Finally, when the algorithm terminates in Step (3.2), then  $\psi$  is realizable as a transducer for it can start with the strategy that reaches  $\langle P, P' \rangle$  such that P is sys-hopeful and P' is not env-hopeful. It is guaranteed that when we apply Steps (1+2) of the algorithm with  $\mathcal{A}_{\psi}^{P}$  instead of  $\psi$  and  $\mathcal{A}_{\neg\psi}^{P'}$  instead of  $\neg\psi$ , we would end up end up in Step (2.1), thus once generating the prefix that leads to  $\langle P, P' \rangle$ , the transducer can continue with a fixed output sequence, as described above. The case  $\psi$  is not realizable is dual.

We now demonstrate our algorithm with three examples. In all of them, we have for  $I = \{q\}$  and  $O = \{p\}$ .

*Example 1.* We start with an example in which the NBW for the specification is deterministic. Let  $\psi = G(p \leftrightarrow Fq)$ . Note that  $\psi$  is equivalent to  $G(p \to Fq) \land G(\neg p \to G\neg q)$ . The specification is universally satisfiable: given a sequence  $x \in (q, \neg q)^{\omega}$ , it is not hard to see that the sequence  $y \in (p, \neg p)^{\omega}$  in which p holds in position j iff q holds in a position grater than j is such that  $x \oplus y \models \psi$ . Consider the negation of the specification, that is  $\neg \psi = F(p \land G\neg q) \lor F(\neg p \land Fq)$ . It is not hard to see that  $\neg \psi$  is universally satisfiable by the environment. Indeed, given a sequence  $y \in (p, \neg p)^{\omega}$ , a sequence  $x \in (q, \neg q)^{\omega}$  in which q holds exactly when p does not hold, is such that  $x \oplus y \models \neg \psi$ .

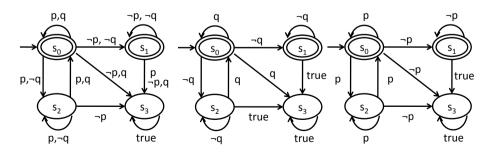

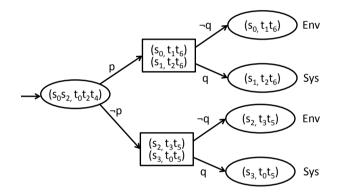

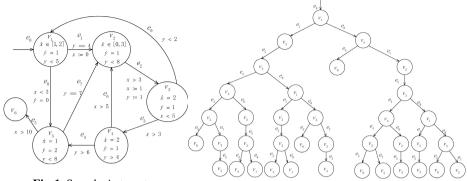

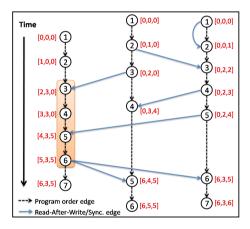

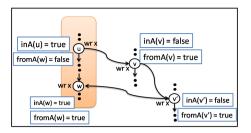

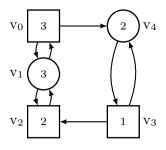

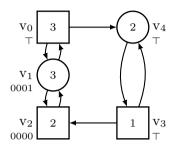

On the left of Figure  $\blacksquare$  below we describe a DBW  $\mathcal{D}_{\psi}$  for  $\psi$ . Since  $\mathcal{D}_{\psi}$  is deterministic, we do not have to apply the subset construction on it. On the right, we describe the two projections of  $\mathcal{D}_{\psi}$  on I and on O.

Note that in  $\mathcal{D}_{\psi}^{\exists O}$ , only  $s_0$  is universal (the other states are not universal since, for example,  $q^{\omega}$  is not accepted from them). Thus, only  $s_0$  is sys-hopeful in  $\mathcal{D}_{\psi}$ . In order to

**Fig. 1.** A DBW  $\mathcal{D}_{\psi}$  for  $\psi = G(p \leftrightarrow Fq)$  (left), and its projections  $\mathcal{D}_{\psi}^{\exists O}$  and  $\mathcal{D}_{\neg\psi}^{\exists I}$  on I (middle) and O (right), respectively

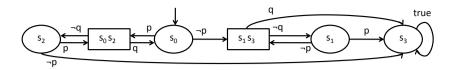

**Fig. 2.** The game induced by  $\mathcal{D}_{\psi}$

find the env-hopeful states we consider the co-Büchi automaton  $\mathcal{D}_{\neg\psi}^{\exists I}$ . Here, all states are universal. Indeed,  $s_3$  is an accepting sink,  $s_1$  can get with both p and  $\neg p$  to  $s_3$  in one transition,  $s_2$  can stay in  $s_2$  forever with  $p^{\omega}$ , and with all other words it can reach  $s_3$ , and finally,  $s_0$  can reach  $s_2$  and  $s_1$  with p and  $\neg p$ , respectively. It follows that all the states in  $\mathcal{D}_{\psi}$  are env-hopeful.

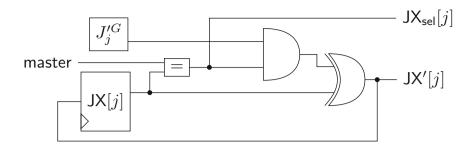

The game induced by  $\mathcal{D}_{\psi}$  appears in Figure 2 The system states are ovals (and in them, the system chooses between p and  $\neg p$ ), and the environment states are rectangles (the environment chooses q or  $\neg q$ ). It is not hard to see that the environment has a strategy to force the system to a state that is not sys-hopeful while staying within env-hopeful states. Thus, we can conclude that  $\psi$  is not realizable.

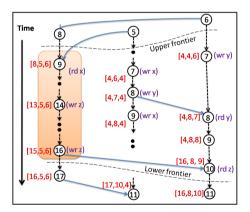

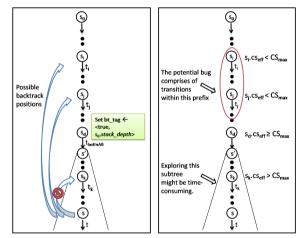

*Example 2.* We now consider a case where  $\mathcal{A}_{\psi}$  is nondeterministic, thus we proceed with NBWs for both  $\psi$  and  $\neg \psi$ . Consider the specification  $\psi = (Gp \land Fq) \lor (G \neg p \land F \neg q)$ . Thus, either the system always generates p and the environment generates q eventually, or the system always generates  $\neg p$ , and the environment generates  $\neg q$  eventually. Note that  $\neg \psi = (Fp \land F \neg p) \lor (G \neg q \land Fp) \lor (Gq \land F \neg p)$ . It is not hard to see that  $\psi$  is universally satisfiable by the system and  $\neg \psi$  is universally satisfiable by the environment.

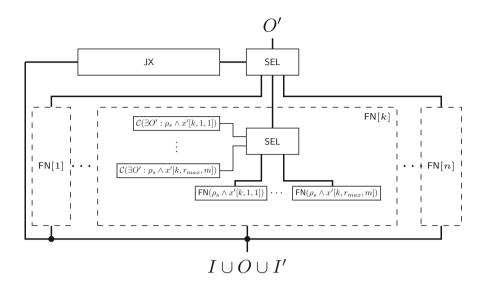

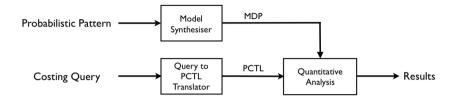

In Figure 3 we describe the NBWs  $A_{\psi}$  (on the left, a union of two components) and  $A_{\neg\psi}$  (on the right, a union of three components).

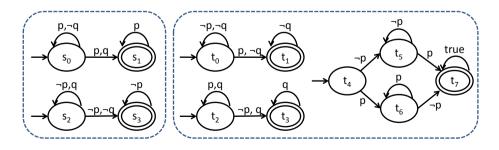

We now check the system and environment hopefulness of sets that are reachable in the subset construction of the two NBWs. If we get to a set that is not hopeful, there is no need to continue the construction from it. In Figure 4 we describe the obtained deterministic pre-automata. In the figure, we indicate by dashed lines that the set is not hopeful. For example, the set  $\{s_0\}$  is not sys-hopeful since there is no output sequence  $y \in (p, \neg p)^{\omega}$  such that  $x \oplus y$  is accepted from  $\mathcal{A}_{\psi}^{\{s_0\}}$  for  $x = (\neg q)^{\omega}$ . Similarly, the set

**Fig. 3.** The NBWs  $A_{\psi}$  (left) and  $A_{\neg\psi}$  (right)

**Fig. 4.** The pre-automata obtained by applying the subset construction to  $\mathcal{A}_{\psi}$  (left) and  $\mathcal{A}_{\neg\psi}$  (right)

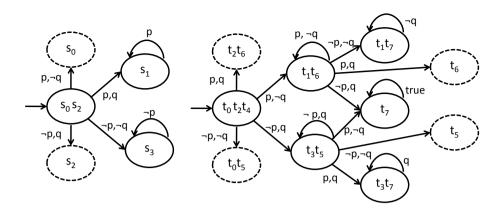

**Fig. 5.** The game corresponding to  $\mathcal{U}_{\psi}$

$\{t_0, t_5\}$  is not env-hopeful since there is no input sequence  $x \in (q, \neg q)^{\omega}$  such that  $x \oplus y$  is accepted from  $\mathcal{A}_{\neg \psi}^{\{t_0, t_5\}}$  for  $y = (\neg q)^{\omega}$ .

In Figure 5 we describe the game corresponding to  $\mathcal{U}_{\psi}$ , obtained by combining the two pre-automata. As indicated in the figure, the states  $(\{s_1\}, \{t_2, t_6\})$  and  $(\{s_3\}, \{t_0, t_5\})$  are winning states for the system. Indeed,  $\{s_1\}$  is sys-hopeful whereas  $\{t_2, t_6\}$  is not env-hopeful, and likewise,  $\{s_3\}$  is sys-hopeful whereas  $\{t_0, t_5\}$  is not env-hopeful. Dually, the states  $(\{s_0\}, \{t_1, t_6\})$  and  $(\{s_2\}, \{t_3, t_5\})$  are winning states for the environment. It is not hard to see that the environment has a strategy to reach its winning states, thus we conclude that  $\psi$  is not realizable.

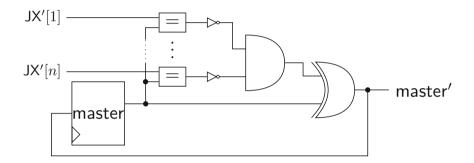

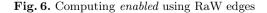

*Example 3.* In this example we demonstrate a case in which our algorithm does not reach a definite answer. Consider the specification  $\psi = F(p \leftrightarrow q)$ . Again, both  $\psi$  and  $\neg \psi$  are universally satisfiable, so we get to Step (3). The deterministic automaton  $\mathcal{D}_{\psi}$  of  $\psi$  appears in Figure 6. It is easy to see that both  $s_0$  and  $s_1$  are system hopeful, whereas only  $s_0$  is environment hopeful. However, the system does not have a strategy to force the game induced by  $\mathcal{D}_{\psi}$  to  $s_1$ : if the system proceeds from  $s_0$  with p, the environment will respond with  $\neg q$ , and if the system proceeds with  $\neg p$ , the environment will respond

**Fig. 6.** A DBW for  $\psi = F(p \leftrightarrow q)$  and the game corresponding to it

with q. Also, since both  $s_0$  and  $s_1$  are system hopeful, the environment does not have a strategy to force the game into states that are not system hopeful. So, we have to solve the realizability problem. We can use, however, the fact that game would get stuck in  $s_0$ , which would not satisfy the Büchi condition, thus  $\psi$  is not realizable.

#### 5 LTL Realizability with Look-Ahead

In Section 3 we defined LTL realizability with look-ahead. This notion is not fundamentally new, and the problem of k-realizability was studied already in 1972, in the context of sequential calculus 12. Here, we adjust the solution to the modern setting of LTL and DPWs, and describe how our algorithm can be adjusted to handle k-realizability too.

**Theorem 3.** Consider an LTL formula  $\psi$  and an integer  $k \ge 0$ . Let  $\mathcal{A}_{\psi}^k$  be such that  $L(\mathcal{A}_{\psi}^k) = \{x \oplus y : x \oplus y^k \in L(\mathcal{A}_{\psi})\}$ , where  $y^k$  is the suffix of y from position k.

- We can construct an NBW  $\mathcal{A}_{\psi}^k$  as above with number of states exponential in  $|\psi|$  and k.

- We can construct an DPW  $\mathcal{A}_{\psi}^k$  as above with number of states doubly-exponential in  $|\psi|$  and exponential in k.

- Applying synthesis algorithms with respect to  $\mathcal{A}_{\psi}^{k}$  rather than  $\mathcal{A}_{\psi}$  solves the *k*-realizability problem.

**Proof:** Let  $\mathcal{A}_{\psi} = \langle 2^{I \cup O}, Q, \delta, q_0, \alpha \rangle$  be an NBW for  $\psi$ . We define  $\mathcal{A}_{\psi}^k = \langle 2^{I \cup O}, Q', \epsilon, \delta', \alpha' \rangle$ , where

- $Q' = (\bigcup_{0 \le j < k} (2^I)^j) \cup (Q \times (2^I)^k)$ . The first type of states is for accumulating the vector of the last k 1 inputs. The second type is to be used after we have accumulated the first k inputs. Then, we follow the runs of  $\mathcal{A}_{\psi}$ , with the output being combined with the input read k letters earlier.

- The transition function is defined as follows.

- For the first type of states, if 0 ≤ j < k − 1, we ignore the output component of the letter read (intuitively, since we shift the output by k, the output in the first k − 1 levels is not important) and only accumulate inputs in the vector. Accordingly, δ'(⟨i<sub>1</sub>,...,i<sub>j</sub>⟩, i ∪ o) = {⟨i<sub>1</sub>,...,i<sub>j</sub>⟩}.

- In the last level of states from the first type, we still ignore the output read but get ready to start following the runs of A<sub>ψ</sub>. Accordingly, δ'((i<sub>1</sub>,...,i<sub>k-1</sub>), i ∪ o) = Q<sub>0</sub> × {(i<sub>1</sub>,...,i<sub>k-1</sub>,i)}.

- Then, we continue to follow the runs of  $\mathcal{A}_{\psi}$ , where *o* is combined with the input read *k* transitions earlier. Accordingly,  $\delta'(\langle q, i_1, \ldots, i_k \rangle, i \cup o) = \delta(q, i_1 \cup o) \times \{\langle i_2, \ldots, i_k, i \rangle\}.$

-  $\alpha'$  is obtained from  $\alpha$  by replacing a set  $F \subseteq Q$  by the set  $F \times (2^I)^k$ .

The construction of the DPW  $\mathcal{A}_{\psi}^{k}$  is similar, starting from a DPW  $\mathcal{A}_{\psi}$  for the property. Note that we could have also determinized the NBW described above, but the blow-up in terms of I could then have been doubly exponential. Note that  $\mathcal{A}_{\psi}^{k}$  proceeds according to the input that was read k positions earlier, combined with the current output. This captures the fact that in k-realizability, the output is combined with the input only after knowing what the previous k inputs were. Accordingly, the game induced by the DPW  $\mathcal{A}_{\psi}^{k}$  solves the k-realizability problem.

Applying our algorithm in order to solve the k-realizability problem, we proceed with the game obtained from the subset construction applied on the the NBWs  $\mathcal{A}^k_{\psi}$  and  $\mathcal{A}^k_{\neg\psi}$ . Note that in both automata, the O-component of a letters is combined with the I-component of the letter read k positions earlier. All the other details of the algorithm are the same.

#### 6 Discussion

We described a simple heuristic that replaces the parity game corresponding to LTL synthesis with a game in which the system and the environment try to force each other into hopeless states in the game. Our definition of hopeless is based on universal satisfaction – the game-free variant of realizability, and is therefore easier to reason about.

Below we discuss some further advantages of our heuristic, and some directions for future research. First, several challenges in the context of realizability are easier to cope with using our approach. This includes compositional synthesis [16], mining for assumptions [18], and testing for inherent vacuity in specifications [8]. In all these problems, one can try to circumvent the need to work with parity games by using our heuristic that use instead hopeless finite prefixes.

Our definition of hopeful states can be replaced by other definitions, leading to looser (but even more efficient) or tighter (but more complex to achieve) heuristics. On the loose side, one can work with the nondeterministic automaton (rather than the subset construction on it). Under this definition, a prefix of a computation is hopeful if there is a single state s in  $\mathcal{A}_{\psi}$  such that the prefix can lead to s and  $\mathcal{A}_{\psi}^{s}$  is universally satisfiable. Note that now, states that are not hopeful may still be reachable by hopeful prefixes, thus the heuristic can be used in order to direct the subset construction to construct subsets only when such a construction is needed. On the tighter side, one can replace universal satisfaction by definitions that are game-based, but are easier to solve than parity.

Finally, in case our algorithm does not terminate with a definite answer, we suggested to continue with traditional synthesis algorithms, with actions being restricted to these that keep the system and the environment in their hopeful regions. We found this case very interesting: both the system and the environment can stay hopeful forever, yet only one of them can satisfy the acceptance condition of  $A_{\psi}$  (the system) or  $A_{\neg\psi}$  (the environment). We plan to study whether this special situation can be of help when we solve the parity game on the restricted region.

#### References

Abadi, M., Lamport, L., Wolper, P.: Realizable and Unrealizable Concurrent Program Specifications. In: Ausiello, G., Dezani-Ciancaglini, M., Ronchi Della Rocca, S. (eds.) ICALP 1989. LNCS, vol. 372, pp. 1–17. Springer, Heidelberg (1989)

- Aminof, B., Kupferman, O., Lampert, R.: Reasoning about Online Algorithms with Weighted Automata. In: Proc. 20th SODA, pp. 835–844 (2009)

- 3. Breslauer, D.: On competitive on-line paging with lookahead. TCS 209(1-2), 365-375 (1998)

- Dill, D.L.: Trace theory for automatic hierarchical verification of speed independent circuits. MIT Press (1989)

- 5. Dworkin, L., Li, W., Seshia, S.A.: Automatic synthesis of a voting machine design (2010) (Unpublished Manuscript)

- Filiot, E., Jin, N., Raskin, J.-F.: An Antichain Algorithm for LTL Realizability. In: Bouajjani, A., Maler, O. (eds.) CAV 2009. LNCS, vol. 5643, pp. 263–277. Springer, Heidelberg (2009)

- Filiot, E., Jin, N., Raskin, J.-F.: Compositional Algorithms for LTL Synthesis. In: Bouajjani, A., Chin, W.-N. (eds.) ATVA 2010. LNCS, vol. 6252, pp. 112–127. Springer, Heidelberg (2010)

- Fisman, D., Kupferman, O., Sheinvald, S., Vardi, M.Y.: A Framework for Inherent Vacuity. In: Chockler, H., Hu, A.J. (eds.) HVC 2008. LNCS, vol. 5394, pp. 7–22. Springer, Heidelberg (2009)

- Godhal, Y., Chatterjee, K., Henzinger, T.A.: Synthesis of AMBA AHB from formal specification. CoRR abs/1001.2811 (2010)

- Harel, D., Pnueli, A.: On the development of reactive systems. In: NATO Advanced Science Institutes, vol. F-13, pp. 477–498. Springer (1985)

- Holtmann, M., Kaiser, L., Thomas, W.: Degrees of Lookahead in Regular Infinite Games. In: Ong, L. (ed.) FOSSACS 2010. LNCS, vol. 6014, pp. 252–266. Springer, Heidelberg (2010)

- 12. Hosch, F., Landweber, L.: Finite delay solutions for sequential conditions. In: Proc. 1st ICALP, pp. 45–60 (1972)

- Jobstmann, B., Bloem, R.: Game-based and simulation-based improvements for LTL synthesis. In: Proc. 3nd GDV (2006)

- Jobstmann, B., Galler, S., Weiglhofer, M., Bloem, R.: Anzu: A Tool for Property Synthesis. In: Damm, W., Hermanns, H. (eds.) CAV 2007. LNCS, vol. 4590, pp. 258–262. Springer, Heidelberg (2007)

- Jurdzinski, M., Paterson, M., Zwick, U.: A deterministic subexponential algorithm for solving parity games. SIAM Journal on Computing 38(4), 1519–1532 (2008)

- Kupferman, O., Piterman, N., Vardi, M.Y.: Safraless Compositional Synthesis. In: Ball, T., Jones, R.B. (eds.) CAV 2006. LNCS, vol. 4144, pp. 31–44. Springer, Heidelberg (2006)

- Kupferman, O., Vardi, M.Y.: Safraless decision procedures. In: Proc. 46th FOCS, pp. 531– 540 (2005)

- Li, W., Dworkin, L., Seshia, S.A.: Mining assumptions for synthesis. In: Proc. 9th MEMOCODE (July 2011)