Tiziana Margaria Bernhard Steffen (Eds.)

# LNCS 6416

# Leveraging Applications of Formal Methods, Verification, and Validation

4th International Symposium on Leveraging Applications, ISoLA 2010 Heraklion, Crete, Greece, October 2010, Proceedings, Part II

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Tiziana Margaria Bernhard Steffen (Eds.)

# Leveraging Applications of Formal Methods, Verification, and Validation

4th International Symposium on Leveraging Applications, ISoLA 2010 Heraklion, Crete, Greece, October 18-21, 2010 Proceedings, Part II

Volume Editors

Tiziana Margaria University of Potsdam August-Bebel-Str. 89 14482 Potsdam Germany E-mail: margaria@cs.uni-potsdam.de

Bernhard Steffen TU Dortmund University Otto-Hahn-Str. 14 44227 Dortmund Germany E-mail: steffen@cs.tu-dortmund.de

#### Library of Congress Control Number: 2010936699

CR Subject Classification (1998): F.3, D.2.4, D.3, C.2-3, D.2, I.2

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-642-16560-5 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-642-16560-3 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### springer.com

© Springer-Verlag Berlin Heidelberg 2010 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper 06/3180

# Preface

This volume contains the conference proceedings of the 4th International Symposium on Leveraging Applications of Formal Methods, Verification and Validation, ISoLA 2010, which was held in Greece (Heraklion, Crete) October 18–21, 2010, and sponsored by EASST.

Following the tradition of its forerunners in 2004, 2006, and 2008 in Cyprus and Chalchidiki, and the ISoLA Workshops in Greenbelt (USA) in 2005, in Poitiers (France) in 2007, and in Potsdam (Germany) in 2009, ISoLA 2010 provided a forum for developers, users, and researchers to discuss issues related to the adoption and use of rigorous tools and methods for the specification, analysis, verification, certification, construction, testing, and maintenance of systems from the point of view of their different application domains. Thus, the ISoLA series of events serves the purpose of bridging the gap between designers and developers of rigorous tools, and users in engineering and in other disciplines, and to foster and exploit synergetic relationships among scientists, engineers, software developers, decision makers, and other critical thinkers in companies and organizations. In particular, by providing a venue for the discussion of common problems, requirements, algorithms, methodologies, and practices, ISoLA aims at supporting researchers in their quest to improve the utility, reliability, flexibility, and efficiency of tools for building systems, and users in their search for adequate solutions to their problems.

The program of the symposium consisted of special tracks devoted to the following hot and emerging topics:

- Emerging services and technologies for a converging telecommunications/Web world in smart environments of the Internet of Things

- Learning techniques for software verification and validation

- Modeling and formalizing industrial software for verification, validation and certification

- Formal methods in model-driven development for service-oriented and cloud computing

- Tools in scientific workflow composition

- New challenges in the development of critical embedded systems—an "aeromotive" perspective

- Web science

- Leveraging formal methods through collaboration

- Resource and timing analysis

- Quantitative verification in practice

- Worst case traversal time (WCTT)

- Model transformation and analysis for industrial scale validation

- Certification of software-driven medical devices

- Formal languages and methods for designing and verifying complex engineering systems

#### VI Preface

- CONNECT: status and plan

- EternalS: mission and roadmap

and five co-located events

- Graduate/postgraduate course on "Soft Skills for IT Professionals in Science and Engineering"

- RERS—challenge on practical automata learning

- IT Simply Works—editorial meeting (ITSy)

- CONNECT internal meeting

- EternalS Task Force meetings

We thank the Track organizers, the members of the Program Committee and their subreferees for their effort in selecting the papers to be presented.

Special thanks are due to the following organization for their endorsement: EASST (European Association of Software Science and Technology), and our own institutions—the TU Dortmund, and the University of Potsdam.

August 2010

Tiziana Margaria Bernhard Steffen

# Organization

# Committees Symposium Chair

Tiziana Margaria University of Potsdam, Germany

# **Program Chair**

Bernhard Steffen

TU Dortmund, Germany

#### **Program Committee**

Yamine Ait Ameur Frédéric Boniol Anne Bouillard Marc Bover Karin Breitman Marco Antonio Casanova Samarjit Chakraborty Noel Crespi Rémi Delmas Howard Foster Pierre-Loïc Garoche Dimitra Giannakopoulou Stefania Gnesi Kevin Hammond Boudewijn Haverkort Michael Hinchey Valérie Issarny Visar Januzaj He Jifeng Joost-Pieter Katoen Joost Kok Jens Knoop Stefan Kugele Anna-Lena Lamprecht Kim G. Larsen Boris Langer

LISI/ENSMA, France **IRIT/ENSEEIHT**, France ENS Cachan, France **ONERA**, France PUC-Rio, Brazil PUC-Rio, Brazil TU München, Germany Institut Telecom, France **ONERA**, France City University London, UK **ONERA**, France CMU/NASA Ames, USA ISTI-CNR, Pisa, Italy University of St Andrews, UK ESI. The Netherlands LERO. Ireland INRIA, France TU Darmstadt, Germany East China Normal University, China **RWTH** Aachen University, Germany Leiden University, The Netherlands Vienna University of Technology, Austria TU München, Germany TU Dortmund, Germany Aalborg University, Denmark Diehl Aerospace, Germany

Mark Lawford Gyu Myoung Lee Björn Lisper Zhiming Liu Tom Maibaum Steven Martin Dominique Mery Pascal Montag Alessandro Moschitti Corina Pasareanu Alexander K. Petrenko Abhik Roychoudhury Christian Schallhart Jean-Luc Scharbarg Amal Seghrouchni Laura Semini Giovanni Stea Eric Thierry Helmut Veith Alan Wassyng Virginie Wiels Mark D. Wilkinson Rostislav Yavorskiy Lenore Zuck

McMaster University, Canada Institut Télécom, France Mälardalen University, Sweden UNU-IIST, Macao McMaster University, Canada LRI, France University Nancy, France Daimler AG, Germany University of Trento, Italy CMU/NASA Ames, USA ISPRAS, Moscow, Russia NUS, Singapore Oxford University, UK IRIT, France University Pierre and Marie Curie, France Pisa University, Italy Pisa University, Italy ENS Lyon, France Vienna University of Technology, Austria McMaster University, Canada **ONERA**. France Heart and Lung Institute, and Canada Microsoft UK/Moscow, Russia University of Illinois at Chicago, USA

# Table of Contents – Part II

# **EternalS: Mission and Roadmap**

| Introduction to the EternalS Track: Trustworthy Eternal Systems via<br>Evolving Software, Data and Knowledge   | 1  |

|----------------------------------------------------------------------------------------------------------------|----|

| HATS: Highly Adaptable and Trustworthy Software Using Formal<br>Methods<br><i>Reiner Hähnle</i>                | 3  |

| SecureChange: Security Engineering for Lifelong Evolvable Systems<br>Riccardo Scandariato and Fabio Massacci   | 9  |

| 3DLife: Bringing the Media Internet to Life<br>Ebroul Izquierdo, Tomas Piatrik, and Qianni Zhang               | 13 |

| LivingKnowledge: Kernel Methods for Relational Learning and<br>Semantic Modeling                               | 15 |

| Task Forces in the Eternals Coordination Action                                                                | 20 |

| Modeling and Analyzing Diversity: Description of EternalS Task<br>Force 1<br>Ina Schaefer                      | 23 |

| Modeling and Managing System Evolution: Description of EternalS<br>Task Force 2<br><i>Michael Hafner</i>       | 26 |

| Self-adaptation and Evolution by Learning: Description of EternalS<br>Task Force 3<br><i>Richard Johansson</i> | 30 |

| Overview of Roadmapping by EternalS<br>Jim Clarke and Keith Howker                                             | 32 |

| Formal Methods in Model-Driven Development for<br>Service-Oriented and Cloud Computing                         |    |

| Adaptive Composition of Conversational Services through Graph<br>Planning Encoding                             | 35 |

Pascal Poizat and Yuhong Yan

| Performance Prediction of Service-Oriented Systems with Layered<br>Queueing Networks<br>Mirco Tribastone, Philip Mayer, and Martin Wirsing                                      | 51  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Error Handling: From Theory to Practice<br>Ivan Lanese and Fabrizio Montesi                                                                                                     | 66  |

| Modeling and Reasoning about Service Behaviors and Their<br>Compositions<br>Aida Čaušević, Cristina Seceleanu, and Paul Pettersson                                              | 82  |

| Design and Verification of Systems with Exogenous Coordination Using<br>Vereofy<br>Christel Baier, Tobias Blechmann, Joachim Klein,<br>Sascha Klüppelholz, and Wolfgang Leister | 97  |

| A Case Study in Model-Based Adaptation of Web Services<br>Javier Cámara, José Antonio Martín, Gwen Salaün,<br>Carlos Canal, and Ernesto Pimentel                                | 112 |

| Quantitative Verification in Practice                                                                                                                                           |     |

| Quantitative Verification in Practice (Extended Abstract)<br>Boudewijn R. Haverkort, Joost-Pieter Katoen, and<br>Kim G. Larsen                                                  | 127 |

| Ten Years of Performance Evaluation for Concurrent Systems Using<br>CADP<br>Nicolas Coste, Hubert Garavel, Holger Hermanns, Frédéric Lang,<br>Radu Mateescu, and Wendelin Serwe | 128 |

| Towards Dynamic Adaptation of Probabilistic Systems<br>S. Andova, L.P.J. Groenewegen, and E.P. de Vink                                                                          | 143 |

| UPPAAL in Practice: Quantitative Verification of a RapidIO<br>Network                                                                                                           | 160 |

| Schedulability Analysis Using Uppaal: Herschel-Planck Case Study<br>Marius Mikučionis, Kim Guldstrand Larsen,                                                                   | 175 |

Jacob Illum Rasmussen, Brian Nielsen, Arne Skou, Steen Ulrik Palm, Jan Storbank Pedersen, and Poul Hougaard

Model-Checking Temporal Properties of Real-Time HTL Programs ..... 191 André Carvalho, Joel Carvalho, Jorge Sousa Pinto, and Simão Melo de Sousa

# **CONNECT: Status and Plans**

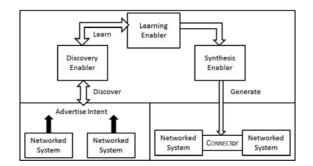

| Towards an Architecture for Runtime Interoperability<br>Amel Bennaceur, Gordon Blair, Franck Chauvel,<br>Huang Gang, Nikolaos Georgantas, Paul Grace, Falk Howar,<br>Paola Inverardi, Valérie Issarny, Massimo Paolucci,<br>Animesh Pathak, Romina Spalazzese, Bernhard Steffen, and<br>Bertrand Souville | 206 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| On Handling Data in Automata Learning: Considerations from the<br>CONNECT Perspective<br>Falk Howar, Bengt Jonsson, Maik Merten, Bernhard Steffen, and<br>Sofia Cassel                                                                                                                                    | 221 |

| A Theory of Mediators for Eternal Connectors<br>Paola Inverardi, Valérie Issarny, and Romina Spalazzese                                                                                                                                                                                                   | 236 |

| On-The-Fly Interoperability through Automated Mediator Synthesis<br>and Monitoring<br>Antonia Bertolino, Paola Inverardi, Valérie Issarny,<br>Antonino Sabetta, and Romina Spalazzese                                                                                                                     | 251 |

| Dependability Analysis and Verification for CONNECTED Systems<br>Felicita Di Giandomenico, Marta Kwiatkowska, Marco Martinucci,<br>Paolo Masci, and Hongyang Qu                                                                                                                                           | 263 |

| Towards a Connector Algebra<br>Marco Autili, Chris Chilton, Paola Inverardi,<br>Marta Kwiatkowska, and Massimo Tivoli                                                                                                                                                                                     | 278 |

| Certification of Software-Driven Medical Devices                                                                                                                                                                                                                                                          |     |

| Certification of Software-Driven Medical Devices<br>Mark Lawford, Tom Maibaum, and Alan Wassyng                                                                                                                                                                                                           | 293 |

| Arguing for Software Quality in an IEC 62304 Compliant Development<br>Process<br>Michaela Huhn and Axel Zechner                                                                                                                                                                                           | 296 |

| Assurance Cases in Model-Driven Development of the Pacemaker |     |

|--------------------------------------------------------------|-----|

| Software                                                     | 343 |

| Eunkyoung Jee, Insup Lee, and Oleg Sokolsky                  |     |

# Modeling and Formalizing Industrial Software for Verification, Validation and Certification

| Improving Portability of Linux Applications by Early Detection of                                     | 357 |

|-------------------------------------------------------------------------------------------------------|-----|

| Interoperability Issues<br>Denis Silakov and Andrey Smachev                                           | 397 |

| v                                                                                                     |     |

| Specification Based Conformance Testing for Email Protocols<br>Nikolay Pakulin and Anastasia Tugaenko | 371 |

| Covering Arrays Generation Methods Survey<br>Victor Kuliamin and Alexander Petukhov                   | 382 |

# **Resource and Timing Analysis**

| A Scalable Approach for the Description of Dependencies in Hard<br>Real-Time Systems                                                                                                   | 397 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Steffen Kollmann, Victor Pollex, Kilian Kempf, and Frank Slomka                                                                                                                        |     |

| Verification of Printer Datapaths Using Timed Automata<br>Georgeta Igna and Frits Vaandrager                                                                                           | 412 |

| Resource Analysis of Automotive/Infotainment Systems Based on<br>Domain-Specific Models – A Real-World Example<br>Klaus Birken, Daniel Hünig, Thomas Rustemeyer, and<br>Ralph Wittmann | 424 |

| Source-Level Support for Timing Analysis<br>Gergö Barany and Adrian Prantl                                                                                                             | 434 |

| Practical Experiences of Applying Source-Level WCET Flow Analysis<br>on Industrial Code                                                                                                | 449 |

| Worst-Case Analysis of Heap Allocations<br>Wolfgang Puffitsch, Benedikt Huber, and Martin Schoeberl                                                                                    | 464 |

| Partial Flow Analysis with oRange<br>Marianne de Michiel, Armelle Bonenfant, Clément Ballabriga, and<br>Hugues Cassé                                                                   | 479 |

| Towards an Evaluation Infrastructure for Automotive Multicore<br>Real-Time Operating Systems<br>Jörn Schneider and Christian Eltges                                                    | 483 |

| Context-Sensitivity in IPET for Measurement-Based Timing                                            |     |

|-----------------------------------------------------------------------------------------------------|-----|

| Analysis                                                                                            | 487 |

| Michael Zolda, Sven Bünte, and Raimund Kirner                                                       |     |

| On the Role of Non-functional Properties in Compiler Verification<br>Jens Knoop and Wolf Zimmermann | 491 |

| Author Index                                                                                        | 497 |

# Table of Contents – Part I

# New Challenges in the Development of Critical Embedded Systems – An "aeromotive" Perspective

| New Challenges in the Development of Critical Embedded Systems—An<br>"aeromotive" Perspective<br>Visar Januzaj, Stefan Kugele, Boris Langer,<br>Christian Schallhart, and Helmut Veith | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Certification of Embedded Software – Impact of ISO DIS 26262 in the<br>Automotive Domain<br>Bernhard Schätz                                                                            | 3  |

| Enforcing Applicability of Real-Time Scheduling Theory Feasibility<br>Tests with the Use of Design-Patterns                                                                            | 4  |

| Seamless Model-Driven Development Put into Practice<br>Wolfgang Haberl, Markus Herrmannsdoerfer, Stefan Kugele,<br>Michael Tautschnig, and Martin Wechs                                | 18 |

| Timely Time Estimates<br>Andreas Holzer, Visar Januzaj, Stefan Kugele, and<br>Michael Tautschnig                                                                                       | 33 |

| Compiler-Support for Robust Multi-core Computing<br>Raimund Kirner, Stephan Herhut, and Sven-Bodo Scholz                                                                               | 47 |

| Formal Languages and Methods for Designing and<br>Verifying Complex Embedded Systems                                                                                                   |    |

| Thematic Track: Formal Languages and Methods for Designing and<br>Verifying Complex Embedded Systems<br>Yamine Ait Ameur, Frédéric Boniol, Dominique Mery, and<br>Virginie Wiels       | 58 |

| Analyzing the Security in the GSM Radio Network Using Attack<br>Jungles<br>Parosh Aziz Abdulla, Jonathan Cederberg, and Lisa Kaati                                                     | 60 |

| Formal Modeling and Verification of Sensor Network Encryption<br>Protocol in the OTS/CafeOBJ Method<br>Iakovos Ouranos, Petros Stefaneas, and Kazuhiro Ogata                           | 75 |

| Model-Driven Design-Space Exploration for Embedded Systems:    |     |

|----------------------------------------------------------------|-----|

| The Octopus Toolset                                            | 90  |

| Twan Basten, Emiel van Benthum, Marc Geilen, Martijn Hendriks, |     |

| Fred Houben, Georgeta Igna, Frans Reckers, Sebastian de Smet,  |     |

| Lou Somers, Egbert Teeselink, Nikola Trčka, Frits Vaandrager,  |     |

| Jacques Verriet, Marc Voorhoeve, and Yang Yang                 |     |

| Contract-Based Slicing                                         | 106 |

Daniela da Cruz, Pedro Rangel Henriques, and Jorge Sousa Pinto

| Worst-Case | Traversal | Time | (WCTT) |  |

|------------|-----------|------|--------|--|

| Special Track on Worst Case Traversal Time (WCTT)<br>Anne Bouillard, Marc Boyer, Samarjit Chakraborty, Steven Martin,<br>Jean-Luc Scharbarg, Giovanni Stea, and Eric Thierry         | 121 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| The PEGASE Project: Precise and Scalable Temporal Analysis for<br>Aerospace Communication Systems with Network Calculus<br>Marc Boyer, Nicolas Navet, Xavier Olive, and Eric Thierry | 122 |

| NC-Maude: A Rewriting Tool to Play with Network Calculus                                                                                                                             | 137 |

| DEBORAH: A Tool for Worst-Case Analysis of FIFO Tandems<br>Luca Bisti, Luciano Lenzini, Enzo Mingozzi, and Giovanni Stea                                                             | 152 |

| A Self-adversarial Approach to Delay Analysis under Arbitrary<br>Scheduling<br>Jens B. Schmitt, Hao Wang, and Ivan Martinovic                                                        | 169 |

| Flow Control with (Min,+) Algebra<br>Euriell Le Corronc, Bertrand Cottenceau, and Laurent Hardouin                                                                                   | 184 |

| An Interface Algebra for Estimating Worst-Case Traversal Times in<br>Component Networks<br>Nikolay Stoimenov, Samarjit Chakraborty, and Lothar Thiele                                | 198 |

| Towards Resource-Optimal Routing Plans for Real-Time Traffic<br>Alessandro Lori, Giovanni Stea, and Gigliola Vaglini                                                                 | 214 |

| Partially Synchronizing Periodic Flows with Offsets Improves<br>Worst-Case End-to-End Delay Analysis of Switched Ethernet<br>Xiaoting Li, Jean-Luc Scharbarg, and Christian Fraboul  | 228 |

| Analyzing End-to-End Functional Delays on an IMA Platform<br>Michaël Lauer, Jérôme Ermont, Claire Pagetti, and Frédéric Boniol                                                       | 243 |

# Tools in Scientific Workflow Composition

| Tools in Scientific Workflow Composition<br>Joost N. Kok, Anna-Lena Lamprecht, and Mark D. Wilkinson                                                                                | 258  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Workflows for Metabolic Flux Analysis: Data Integration and Human<br>Interaction                                                                                                    | 261  |

| Intelligent Document Routing as a First Step towards Workflow<br>Automation: A Case Study Implemented in SQL<br>Carlos Soares and Miguel Calejo                                     | 276  |

| Combining Subgroup Discovery and Permutation Testing to Reduce<br>Reduncancy<br>Jeroen S. de Bruin and Joost N. Kok                                                                 | 285  |

| Semantically-Guided Workflow Construction in Taverna: The SADI<br>and BioMoby Plug-Ins<br>David Withers, Edward Kawas, Luke McCarthy,<br>Benjamin Vandervalk, and Mark D. Wilkinson | 301  |

| Workflow Construction for Service-Oriented Knowledge Discovery<br>Vid Podpečan, Monika Žakova, and Nada Lavrač                                                                      | 313  |

| Workflow Composition and Enactment Using jORCA<br>Johan Karlsson, Victoria Martín-Requena, Javier Ríos, and<br>Oswaldo Trelles                                                      | 328  |

| A Linked Data Approach to Sharing Workflows and Workflow                                                                                                                            | 9.40 |

| Results<br>Marco Roos, Sean Bechhofer, Jun Zhao, Paolo Missier,<br>David R. Newman, David De Roure, and M. Scott Marshall                                                           | 340  |

| Emerging Services and Technologies for a<br>Converging Telecommunications / Web World in<br>Smart Environments of the Internet of Things                                            |      |

| Towards More Adaptive Voice Applications                                                                                                                                            | 355  |

| Telco Service Delivery Platforms in the Last Decade - A R&D<br>Perspective<br>Sandford Bessler                                                                                      | 367  |

| Ontology-Driven Pervasive Service Composition for Everyday Life<br>Jiehan Zhou, Ekaterina Gilman, Jukka Riekki,<br>Mika Rautiainen, and Mika Ylianttila                             | 375  |

| Navigating the Web of Things: Visualizing and Interacting with<br>Web-Enabled Objects<br>Mathieu Boussard and Pierrick Thébault                                                       | 390 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Shaping Future Service Environments with the Cloud and Internet of<br>Things: Networking Challenges and Service Evolution<br><i>Gyu Myoung Lee and Noel Crespi</i>                    | 399 |

| Relay Placement Problem in Smart Grid Deployment<br>Wei-Lun Wang and Quincy Wu                                                                                                        | 411 |

| Web Science                                                                                                                                                                           |     |

| Towards a Research Agenda for Enterprise Crowdsourcing<br>Maja Vukovic and Claudio Bartolini                                                                                          | 425 |

| Analyzing Collaboration in Software Development Processes through<br>Social Networks<br>Andréa Magalhães Magdaleno, Cláudia Maria Lima Werner, and<br>Renata Mendes de Araujo         | 435 |

| A Web-Based Framework for Collaborative Innovation<br>Donald Cowan, Paulo Alencar, Fred McGarry, Carlos Lucena, and<br>Ingrid Nunes                                                   | 447 |

| A Distributed Dynamics for WebGraph Decontamination<br>Vanessa C.F. Gonçalves, Priscila M.V. Lima, Nelson Maculan, and<br>Felipe M.G. França                                          | 462 |

| Increasing Users' Trust on Personal Assistance Software Using a<br>Domain-Neutral High-Level User Model<br>Ingrid Nunes, Simone Diniz Junqueira Barbosa, and<br>Carlos J.P. de Lucena | 473 |

| Understanding IT Organizations<br>Claudio Bartolini, Karin Breitman,<br>Simone Diniz Junqueira Barbosa, Mathias Salle,<br>Rita Berardi, Glaucia Melissa Campos, and Erik Eidt         | 488 |

| On the 2-Categorical View of Proofs<br>Cecilia Englander and Edward Hermann Haeusler                                                                                                  | 502 |

| Model Transformation and Analysis for Industrial<br>Scale Validation                                                                                                                  |     |

| WOMM: A Weak Operational Memory Model            | 519 |

|--------------------------------------------------|-----|

| Arnab De, Abhik Roychoudhury, and Deepak D'Souza |     |

| A Memory Model for Static Analysis of C Programs<br>Zhongxing Xu, Ted Kremenek, and Jian Zhang                                                          | 535 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Analysing Message Sequence Graph Specifications<br>Joy Chakraborty, Deepak D'Souza, and K. Narayan Kumar                                                | 549 |

| Optimize Context-Sensitive Andersen-Style Points-To Analysis by<br>Method Summarization and Cycle-Elimination<br>Li Qian, Zhao Jianhua, and Li Xuandong | 564 |

| A Formal Analysis of the Web Services Atomic Transaction Protocol<br>with UPPAAL<br>Anders P. Ravn, Jiří Srba, and Saleem Vighio                        | 579 |

| SPARDL: A Requirement Modeling Language for Periodic Control<br>System                                                                                  | 594 |

| AutoPA: Automatic Prototyping from Requirements<br>Xiaoshan Li, Zhiming Liu, Martin Schäf, and Ling Yin                                                 | 609 |

| Systematic Model-Based Safety Assessment Via Probabilistic Model<br>Checking                                                                            | 625 |

# Learning Techniques for Software Verification and Validation

| Learning Techniques for Software Verification and Validation – Special<br>Track at ISoLA 2010<br>Dimitra Giannakopoulou and Corina S. Păsăreanu                                                 | 640 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Comparing Learning Algorithms in Automated Assume-Guarantee<br>Reasoning<br>Yu-Fang Chen, Edmund M. Clarke, Azadeh Farzan, Fei He,<br>Ming-Hsien Tsai, Yih-Kuen Tsay, Bow-Yaw Wang, and Lei Zhu | 643 |

| Inferring Compact Models of Communication Protocol Entities<br>Therese Bohlin, Bengt Jonsson, and Siavash Soleimanifard                                                                         | 658 |

| Inference and Abstraction of the Biometric Passport<br>Fides Aarts, Julien Schmaltz, and Frits Vaandrager                                                                                       | 673 |

| From ZULU to RERS Lessons Learned in the ZULU Challenge<br>Falk Howar, Bernhard Steffen, and Maik Merten                                                                                        | 687 |

| Author Index                                                                                                                                                                                    | 705 |

# Introduction to the EternalS Track: Trustworthy Eternal Systems via Evolving Software, Data and Knowledge

Alessandro Moschitti

Department of Computer Science and Information Engineering University of Trento Via Sommarive 14, 38100 POVO (TN) - Italy moschitti@disi.unitn.it

Latest research work within ICT has outlined that future systems must possess the ability of adapting to changes in user requirements and application domains. Adaptation and evolution depend on several dimensions, e.g., time, location, and security conditions, expressing the diversity of the context in which systems operate.

The Coordination Action (CA): Trustworthy Eternal Systems via Evolving Software, Data and Knowledge (EternalS) aims at coordinating research in the above-mentioned areas by means of a researcher Task Force and community building activities, where the organization of workshops and conferences is one of the important tools used for such purpose. EternalS aims at creating the conditions for mutual awareness and cross-fertilization among the four ICT-Forever Yours - FET projects (FP7-ICT-Call 3): LivingKnowledge, HATS, Connect and SecureChange. These projects are currently conducting research in key ICT areas: (i) automatic learning of systems capable of analyzing knowledge and diversity with respect to their complex semantic interactions and evolution over time, (ii) exploitation of formal methods for the design and networking of adaptive and evolving software systems; and (iii) design of security policies and fully connected environment. The above-mentioned projects will help EternalS to actively involve many researchers from both academic and industrial world in its action.

The EternalS track at ISOLA 2010 represents a first milestone on establishing task forces and in recruiting stakeholders of its research topics. For this issue, the track presents aims and results of three FET projects, HATS and SecureChange and LivingKnowledge, outlined in three different talks. Moreover, the 3D-Life project, which aims at fostering the creation of sustainable and long-term relationships between existing research groups in Media Internet, will be introduced in the fourth talk.

The work above represents the initial material on which the CA is working by means of three different task forces. These will be illustrated along with their current results and future plans in the following talks: (i) *Modeling and Analyzing Diversity*, (ii) *Modeling and Managing System Evolution* and (iii) *Self-adaptation and Evolution by Learning*. Moreover, since one of the most valuable contribution

T. Margaria and B. Steffen (Eds.): ISoLA 2010, Part II, LNCS 6416, pp. 1–2, 2010.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2010

of EternalS will be the indications for future promising and needed research, the last talk will be devoted to an *Overview of Roadmapping by EternalS*.

Finally, although there is no talk about the Connect project in this track, it will be presented in many contributions of the other ISOLA tracks, e.g. in the afternoon meeting (following EternalS sessions), a series of six talks will detail the current research and results of Connect.

The exciting program of the EternalS track will be concluded with a general discussion on the presented ideas and topics, which aims at creating future research collaborations.

EternalS track chair Alessandro Moschitti

# HATS: Highly Adaptable and Trustworthy Software Using Formal Methods

Reiner Hähnle

Department of Computer Science and Engineering Chalmers University of Technology, 41296 Gothenburg, Sweden http://www.cse.chalmers.se/~reiner, http://www.hats-project.eu

Abstract. The HATS project develops a formal method for the design, analysis, and implementation of highly adaptable software systems that are characterized by high demand on trustworthiness. Existing modeling formalisms leave gap between highly abstract, largely structural models and executable code on the implementation level. HATS aims to close this gap with an object-oriented, executable modeling language for adaptable, concurrent software components. It comes with tool suite based on analysis methods developed hand in hand with the language.

#### 1 Introduction

The HATS project develops a formal method for the design, analysis, and implementation of highly *adaptable* software systems that are at the same time characterized by a high demand on *trustworthiness*.

Adaptability includes two aspects: anticipated variability as well as evolvability, i.e., unanticipated change. The first is, to a certain extent, addressed in modern software architectures such as software product families (SWPF). However, increasing product complexity (features, deployment) is starting to impose serious limitations. Evolvability over time is an even more difficult problem.

Current development practices do not make it possible to produce highly adaptable *and* trustworthy software in a large-scale and cost-efficient manner. The crucial limitation is the *missing rigour* of models and property specifications: informal or semi-formal notations lack the means to describe precisely the *behavioural* aspects of software systems: concurrency, modularity, integrity, security, resource consumption, etc.

#### 2 Mind the Gap

Existing formal notations for specification of systems at the modeling level such as UML or FDL are mainly *structural* and lack adequate means to specify detailed behavior including datatypes, compositionality, concurrency. But without a formal notation for the behavior of distributed, component-based systems it is impossible to achieve automation of consistency checking, enforcement of security, trusted code generation, test case generation, specification mining, etc.

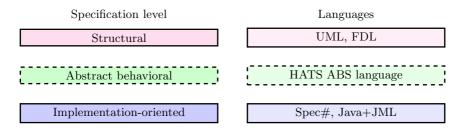

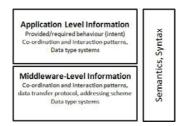

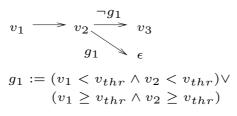

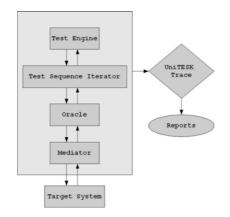

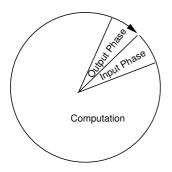

Fig. 1. Positioning of the HATS ABS language

At the same time, formal specification and reasoning about executable programs on the implementation level is by now well understood even for commercial languages such as JAVA or C and it is reasonably well supported by tools. The size and complexity of implementation languages, however, makes specification and verification extremely expensive. In addition, re-use is very hard to realize.

In conclusion, there is a gap between highly abstract modeling formalisms and implementation-level tools, visualized in Fig. []. The HATS project addresses this specification gap by providing the following three ingredients:

- 1. An object-oriented, executable modeling language for adaptable, concurrent software components: the *Abstract Behavioral Specification* (ABS) language. Its design goal is to permit formal specification of concurrent, component-based systems on a level that abstracts away from implementation details but retains essential behavioral properties: concurrency model, component structure, execution histories, datatypes. The ABS language has a formal operational semantics which is the basis for unambiguous usage and rigorous analysis methods. The ABS language closes the mentioned gap, see Fig. []

- 2. A tool suite for analysis and development of ABS models as well as for analysis of executable code derived from these models:

- "Hard methods" typically strive for completeness or full coverage and require expert knowledge in the form of user interaction or detailed specifications. These include feature consistency, data integrity, security, property verification, and code generation.

- "Soft methods" typically are incomplete or non-exhaustive, but do not presuppose expert knowledge and are fully automatic. These include visualization, test case generation, specification mining, and type checking.

One decisive aspect of the HATS project is to develop the analysis methods *hand in hand* with the ABS language to ensure *feasibility* of the resulting analyses.

3. A methodological and technological framework that integrates the HATS tool architecture and the ABS language.

<sup>&</sup>lt;sup>1</sup> For example, KeY (www.key-project.org), Krakatoa (krakatoa.lri.fr), or VCC (research.microsoft.com/en-us/projects/vcc).

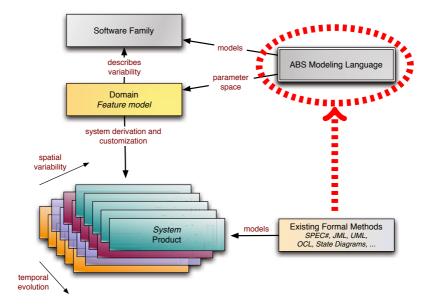

Fig. 2. Lifting formal methods to Family Engineering

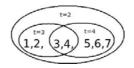

As a main challenge in the development of the ABS language and HATS tool suite we identified (in addition to the technical difficulties) the need to make it *relevant* for industrial practice. Therefore, to keep the project firmly grounded, we orient the design of the ABS language and the HATS methodology along an empirically highly successful *informal* software development paradigm. In software product family-based development one separates *Family Engineering* which includes feature modeling and library development from *Application Engineering* where code is derived via selection, instantiation and composition.

In HATS we turn SWPF-based development into a rigorous approach based on formal specification. As visualized in Fig. [2] constructing a software family requires architecting both the *commonality*, that is, features, properties, and resources that are common to all products in the family, as well as the *adaptability*, that is, the varying aspects across the software family, in order to exploit them during the customization and system derivation process. Adaptability encompasses both anticipated differences among products in the family (*variability*), as well as the different products which appear over time due to evolving requirements (*evolvability*). Handling evolution is crucial as software undergoes changes during its lifetime; indeed, most future usages of a piece of software are not anticipated during its development. Therefore, variability and evolvability are the technological challenges that have to be addressed, when lifting formal modeling and analysis methods from the implementational level to the ABS level:

Variability. With this we mean functional variability and the invasive composition techniques used to instantiate feature models. A major challenge is to understand which linguistic primitives are suited to formalize the desired concurrency-related aspects (including feature interactions but also failures, distribution, and parametrization on scheduling policies).

**Evolvability.** The key challenge here is to develop the theory, algorithms, and core mechanisms needed to build software systems that can be dynamically reconfigured—possibly even without service interruption—to adapt to changes that were *not anticipated* at the time the components which make up the running system were initially constructed.

Both aspects are strongly present in SWPF-based development where variability inherent to the feature space and deployment scenarios are an essential part of family engineering. Evolvability comes into play when new products with unanticipated features are to be created.

# 3 Main Results Achieved

During the first phase, the HATS project established a number of crucial results of which we highlight the most important ones:

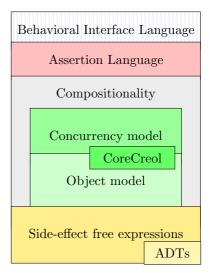

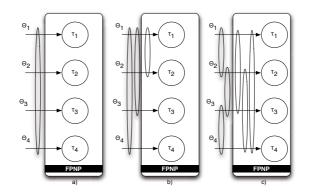

Core ABS Language. The central achievement of HATS so far is the definition of the core of the ABS language. It consists of a (JAVA-like) syntax with a parser, a decidable type system with a compile-time type checker, and a formal operational semantics that permits simulation of ABS programs within the term rewriting engine Maude. To achieve maximal modularity and extensibility of the ABS language we decided a *layered* architecture with clearly defined tiers as depicted in Fig. 3 The core ABS is described in Deliverable D1.1A of the HATS project Report on the Core ABS Language and Methodology: Part A<sup>2</sup>

Delta Modeling. For the integration of features in the ABS language, we studied various formalisms and mechanisms; e.g., traits,

Fig. 3. ABS language layers

context-oriented programming techniques, and delta modeling. We identified *delta modeling* as a promising approach to bridge the gap between features and ABS code. In delta modeling one distinguishes between a core implementation, containing the code common to each product, and deltas, containing code specific to some feature configuration(s). Deltas make changes to the core in order to integrate one or multiple features. Details are available in Deliverable D2.2.a *First Report on Feature Selection and Integration*.

<sup>&</sup>lt;sup>2</sup> All HATS deliverables are public and are available from www.hats-project.eu

Incremental Verification. We started work on formal verification of ABS models: we developed a symbolic execution engine for the language CREOL whose concurrency model is the basis for the one in ABS. This will allow us to develop rapidly a formal verification framework for core ABS in the second project phase. We have studied three incremental verification techniques that are particularly suited to formal SWPF-based development with ABS: (i) combining symbolic execution and partial evaluation; (ii) proof reuse techniques in combination with the core/delta modeling methodology; (iii) lazy behavioral subtyping, based on combining syntax-driven inference systems such as type and effect systems with Hoare logics in order to track behavioral dependencies between classes.

Assertion Language. We investigated the foundation of an assertion language for the ABS which supports the specification and verification of properties of message sequences between objects, components, features. A major challenge is finding a proper formalization that is user-friendly, corresponds to the level of the ABS (clear object-oriented flavour) and lends itself easily to automated verification (both runtime testing and static checking). A promising framework for this formalization is provided by Attribute Grammars. We started to integrate histories of method calls and returns in JML and perform run-time testing of these assertions.

Behavior of Evolving Systems. In the evolution of systems, a central question is how to prove that the modification of a module does not affect the overall system behavior. We investigated this question with respect to object-oriented program modules as the modeling language was not fixed when we started. The first result is a compatibility criterion that allows to check whether a refactored module can be integrated into all possible contexts of the old module. We also worked on security monitor inlining for JAVA bytecode and started one of the first systematic investigations of monitor correctness for multi-threaded JVM. This work is reported in HATS Deliverable 3.1.a First Report On Evolvable Systems.

*Resource Guarantees.* Regarding trustworthiness we concentrated on resource guarantees. We took as a starting point an existing framework for the analysis of the *resource consumption* of JAVA and JAVA bytecode and its corresponding analyzer COSTA We obtained several extensions of this towards a cost analysis framework for HATS, including numeric fields, specifying and inferring *asymptotic* upper bounds, comparing cost expressions, and estimating the memory usage in the presence of *garbage collection*.

Requirements Analysis and Case Studies. In close collaboration with the HATS End-User Panel, we elicited high-level requirements of the HATS methodology. In addition, we described three representative case studies that will be refined and employed for evaluation purposes later on. The case studies should also be valuable for related projects. The case studies are reported in Deliverable 5.1 Requirement Elicitation.

<sup>&</sup>lt;sup>3</sup> https://costa.ls.fi.upm.es/

In conclusion, a number of scalable and incremental approaches to analyze ABS models have been presented and are currently implemented/evaluated. Some of these generalize existing technology while others are completely new ideas that arose in the HATS context.

In order to keep this paper short, we decided not to supply references. A complete list of publications related to HATS is available from the www.hats-project.eu

# SecureChange: Security Engineering for Lifelong Evolvable Systems

Riccardo Scandariato<sup>1</sup> and Fabio Massacci<sup>2</sup>

<sup>1</sup> IBBT-DistriNet Katholieke Universiteit Leuven 3001 Leuven, Belgium

<sup>2</sup> Dipartimento di Ingegneria e Scienza dell'Informazione Università di Trento 38050 Trento, Italy

**Abstract.** The challenge of SECURECHANGE is to re-invent security engineering for "eternal" systems. The project focuses on methods, techniques and tools to make change a first-class citizen in the software development process so that security is built into software-based systems in a resilient and certifiable way. Solving this challenge requires a significant re-thinking of all development phases, from requirements engineering to design and testing.

Keywords: Security, evolvability, software life-cycle.

#### 1 Introduction

A reality-check on complex critical systems reveals that their life-cycle is characterized by a short design time (months) compared to the much longer operational time (many years or even decades). Due to these considerations, it is unlikely that such systems will remain unchanged during their life time. Hence, a primary need for those software-based systems is to be highly flexible and evolvable. At the same time, those systems expose strong security and dependability requirements as they handle sensitive data, impact our daily life, or put people's lives at stake. Current software engineering techniques are not equipped to deal with this conflicting situation. On one side, state-of-the-art research has unearthed methods and techniques to support *adaptability*. In this respect, autonomic systems represent, for instance, one of the most promising directions. However, the high flexibility of adaptable systems comes with the cost of little or no guarantees that the security properties are preserved with change. On the opposite side, very precise *verification* techniques work under the assumption that the properties to-be-verified and the system under verification are fixed over time. That is, they are conceived for rigid, inflexible systems.

The challenge of SECURECHANGE is to re-invent security engineering for "eternal" systems. The project focusses on methods, techniques and tools to make *change* a first-class citizen in the software development process so that security is built and certified in software-based systems in a way that is resilient to

T. Margaria and B. Steffen (Eds.): ISoLA 2010, Part II, LNCS 6416, pp. 9–12, 2010.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2010

change. Solving the above-mentioned challenge requires a significant re-thinking of all development phases, from requirements engineering to design and testing.

#### 2 The Project at a Glance

All the activities carried out by the project consortium revolve around a common theme: understanding the effect of change on a given development artifact, conceive a way to trace such change, and develop techniques to incrementally deal with its impact. Evolution is categorized as being driven by (i) a change in the context (environment), (ii) a change in the behavioral or security requirements, and (iii) a change in the specification (design and implementation) of the system.

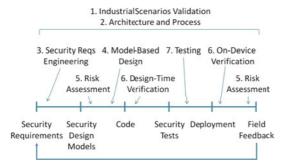

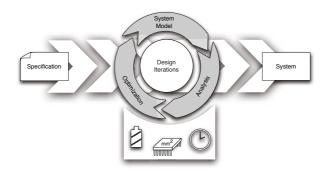

In order to achieve the ambitious objective stated in the previous section and in light of the above-mentioned flavors of change, the project has defined the following array of integrated activities, as summarized in Figure 1. which visualizes how these activities fit together in the life-cycle of an adaptive securitycritical system.

Industrial Scenarios Validation (WP1). The techniques and tools developed within the project are validated in the context of three case studies: (i) evolvability of software running on portable devices like smart cards, (ii) evolvability of software running on a residential gateway providing digital home services, and (iii) evolvability of software running on the workstation of air traffic control operators.

Architecture and Process (WP2). As configuration management can no longer be separated from the development of the application, one objective is a configuration management process that is tightly intertwined with the development and life-cycle processes defined in the project. This process is supported by modelbased tools that allow for automated reconfiguration as a reaction to change as well as verification of security properties in a changing context. To successfully validate this process in the proposed case-studies, it needs to be instantiated on the basis of a common architecture, which is rich enough to address the challenges of incompatible versions, hardware reconfiguration, scalability, and heterogeneity.

Fig. 1. Structure of the SECURECHANGE project

Security Requirements Engineering (WP3). The project defines a new method that addresses the two possible interpretations of the concept of "evolving requirements". The first are the inventions that are necessary to consider in the current design, which are unknown but potentially vital future requirements. The second is how to redefine the flow from requirements to system, so that we can reconstruct how the system can evolve when requirements evolve.

Model-Based Design (WP4). The project develops a model-based design approach that is tailored to the needs of the secure development of adaptable systems. The approach glues requirement techniques to the final code and provides tools that allow the user to automatically analyze the models against its a-priori requirements, also taking into account the change scenarios that the risk analysis has defined likely. In particular, the approach takes into account various system views, including infrastructure elements, stakeholders, and hardware configurations—all of which may be subject to change during the system evolution.

*Risk Assessment (WP5).* The project also has the goal of generalizing existing methods and techniques for security assessment to cope with longevity. This addresses the issue of system documentation to facilitate assessment of security modulo changes as well as techniques, methods and tools for automatic or semi-automatic revalidation of existing assessment results modulo changes.

Design-Time and On-Device Verification (WP6). The project attempts to identify software programming models that can provably resist future errors, and how we can change the V&V process in order to cope with changes. Furthermore, the project provides embedded verification techniques targeting two goals. First, new code on an autonomous system must be verified in order to be safely loaded, and second, when new security requirements are provided, the verification process itself must be adapted.

Testing (WP7). The project also provides solutions for evaluating the impacts of changes, by means of model-based testing. By analyzing the differences between each model and their evolutions, testing strategies are defined that highlight the evolution or non-regression of the system.

#### 3 Key Results

During the first project year, the SECURECHANGE project obtained key results within all work packages. In the rest of this Section, a few highlights are presented:

- 1. Industrial Scenarios Validation. Based on change scenarios observed in the context of the industrial case studies, a taxonomy of change has been defined as a consortium-wide effort. The taxonomy provides the "scope" of the project activities. The classification has two sides: (i) how things change (problems) and (ii) how we deal with changes (solutions).

- 2. Architecture and Process. A methodology based on so-called Change Patterns has been defined to support adaptability to changing requirements at

the architectural level (i.e., co-evolution of security at the requirements and architectural level). Further, the framework for an artefact-centric change management process has been defined. The process keeps track of, and orchestrates the ripple effects among artifacts when a change is injected at any level.

- 3. Security Requirements Engineering. An approach to manage the evolution process of the requirements specification has been defined. The approach leverages so-called Change Rules. Evolution rules are specified as event-condition-action tuples. Events are changes in the requirements artifact (e.g., something is added and consequently a security inconsistency is detected) that trigger corrective actions, (e.g., the artefact is transformed to preserve the key security requirements).

- 4. Model-Based Design. Based on UMLsec, the UMLseCh extension has been defined. The extended notation allows to insert expected changes as predefined markers in the design models. These markers are leveraged for the formal security analysis carried out by a companion tool. The markers provide an indication of model elements that are added, deleted, or replaced. The tool performs an incremental analysis starting from both the original model (assumed correct) and the model of change.

- 5. Risk Assessment. A systematic approach has been defined (among others, as an extension of the CORAS method for security risk analysis) to identify the updates made to the target of evaluation, identify which security risks and parts of the security risk model are affected by the updates, and update the security risk model without having to change the unaffected parts.

- 6. Design-Time and On-Device Verification. At design-time, a programming model (failboxes) for verifying absence of dependency safety violations has been defined. At run-time, a programming model for writing safe programs that dynamically (un)load modules has been defined. Note that dynamically (un)loading modules is a key feature of adaptable systems.

- 7. Testing. An algorithm has been defined that, given the old test suite and the new design model, is able to compute: security tests that are outdated in light of the modeled change (obsolete), tests that are unchanged (reusable), tests that must be adapted or added (evolution).

The above results have led to several scientific publications that are available through the project portal  $\mathbf{P}$ .

<sup>&</sup>lt;sup>1</sup> http://www.securechange.eu

# **3DLife: Bringing the Media Internet to Life**

Ebroul Izquierdo, Tomas Piatrik, and Qianni Zhang

Queen Mary University of London, School of Electronic Engineering and Computer Science, Mile End Road, London

**Abstract.** "Bringing the Media Internet to Life" - or simply, 3DLife - is a European Union funded project that aims to integrate research conducted within Europe in the field of Media Internet. In this contribution, we give an overview of the project's main objectives and activities.

#### **1** Introduction

It is widely argued that the next generation of Media Computing services will become the cornerstone of Information Society in our century. Its impact on the entertainment industry is already clear. However, its impact is expected to be much broader in changing the way that society delivers key services such as health care, learning and commerce.

3DLife is a Network of Excellence (NoE), funded under the "Cooperation" segment of the Seventh Framework Programme (FP7). It fosters the creation of sustainable and long-term relationships between existing national research groups and lays the foundations for a Virtual Centre of Excellence (VCE) in Media Internet. The key factors making the 3DLife consortium capable of reaching the posed objectives are reflected in the scientific quality of the partners and the diverse yet complementary research background they bring to the project. Those partners are Queen Mary, University of London (United Kingdom, Coordinator), Dublin City University (Ireland), Heinrich Hertz Institute, Fraunhofer (Germany), Informatics & Telematics Institute (Greece), Korea University (Korea), MIRALab, University of Geneva (Switzerland) and Telecom ParisTech (France). Since the 3DLife project comprehensively addresses several challenges of Media Internet, its impact is expected to be vast in several aspects of modern life including industry, academic and societal.

#### 2 Highlights of 3DLife Activities

An important objective of the 3DLife NoE is to create sufficient momentum by integrating an existing large number of researchers and resources to enable realistic, efficient and to some extent autonomic media communication and interaction over the Internet. Three important integrative activities revolve around the project concept. A more detailed description of these activities is given in this section.

#### 2.1 Integration and Sustainability

The 3DLife NoE promotes a series of collaborative activities of various types including Phd Student Exchanges, Researcher and Senior Researcher Visits, Industrial Placements, and Joint Postgraduate Courses. Furthermore, the ambition of 3DLife is to launch a VCE, namely the European Centre of Excellence in Media Computing and Communication (EMC<sup>2</sup>), during the lifetime of the project. EMC<sup>2</sup> aims at nurturing Media Computing R&D in Europe and beyond by fostering integration and promoting cooperation between Academia and Industry. EMC<sup>2</sup> will promote additional collaborative activities such as Fellowships, Grand Challenges, Distinguished Lecture Series, Journal Special Issues, Workshop/Conference Series, and Short Term Collaborative Projects. It will bring together members' capabilities, knowledge and expertise to facilitate R&D funding through cooperative projects, joint research publications and technology transfer, while advancing the state of the art in Media Computing. Regarding scientific impact, EMC2 will endeavour to secure a dominant role in other well established scientific bodies, as IEEE Technical Committees, IET professional networks and EURASIP special interest groups. Several dissemination forums, standardization bodies, international conferences and exhibitions will be targeted and used to cement the ties between EMC<sup>2</sup> and the broad research community.

#### 2.2 Cooperative Research

The 3DLife NoE is about media networking with enhanced interactivity and "autonomy". The project promotes cooperative research between its core partners on the following research areas: 3D Computer Graphics Methods, Media Analysis for 3D Data Generation, Virtual Humans Rendering and Animation, Distributed Immersive Virtual Worlds, Media Networking, Secure Networked Data Representations, etc. In the heart of this cooperative research lies the 3DLife software Framework for Integration, an internal section of 3DLife's web and network presence. It aims to enhance the collaboration between the project partners and to help compile and transfer their expert knowledge and technologies.

#### 2.3 Spreading Excellence

3DLife plans to spread excellence in training, dissemination, and technology transfer. Spreading excellence of the scientific results and integrative efforts of this NoE targets three main groups: academics, industry/business and the non-specialist citizen. An important tool of dissemination is constituted by the 3DLife web site (www.3dlife-noe.eu). The website is part of the project's Collaboration Space aimed to be not only a mere repository of R&D results, but also a facilitator of the interaction between researchers, companies and experts, improving knowledge sharing, and supporting a culture of innovation among them. In addition, 3DLife has active social groups on popular social network platforms such as FaceBook, Twitter and LinkedIn. Latest activities and news in the project are constantly broadcasted through these channels to interested audience. Another important aspect of this activity is joint publications and coordination of special sessions at important international and well established conferences. These will help to spread excellence outside the network and to enlarge the network audience.

#### **3** Conclusion

The 3DLife NoE aims at heavily impacting and influencing main constituents of the Media Internet by integrating, disseminating and sharing the different technologies. We believe that by helping you to understand the project activities, we are paving the way towards cooperation between your institution and the 3DLife project.

# LivingKnowledge: Kernel Methods for Relational Learning and Semantic Modeling

Alessandro Moschitti

Department of Computer Science and Information Engineering University of Trento Via Sommarive 14, 38100 POVO (TN) - Italy moschitti@disi.unitn.it

Abstract. Latest results of statistical learning theory have provided techniques such us pattern analysis and relational learning, which help in modeling system behavior, e.g. the semantics expressed in text, images, speech for information search applications (e.g. as carried out by Google, Yahoo,..) or the semantics encoded in DNA sequences studied in Bioinformatics. These represent distinguished cases of successful use of statistical machine learning. The reason of this success relies on the ability of the latter to overcome the critical limitations of logic/rule-based approaches to semantic modeling: although, from a knowledge engineer perspective, hand-crafted rules are natural methods to encode system semantics, noise, ambiguity and errors, affecting dynamic systems, prevent them from being effective.

One drawback of statistical approaches relates to the complexity of modeling world objects in terms of simple parameters. In this paper, we describe kernel methods (KM), which are one of the most interesting results of statistical learning theory capable to abstract system design and make it simpler. We provide an example of effective use of KM for the design of a natural language application required in the European Project LivingKnowledge.

**Keywords:** Kernel Methods; Structural Kernels; Support Vector Machines; Natural Language Processing.

#### 1 The Data Representation Problem

In recent years, a considerable part of Information Technology research has been addressed to the use of machine learning for the automatic design of critical system components, e.g. automatic recognition/classification of critical data patterns. One of the most important advantages with respect to manually coded system modules is the ability of learning algorithms to automatically extract the salient properties of the target system from training examples. This approach can produce semantic models of system behavior based on a large number of attributes, where the values of the latter can be automatically learned. The

<sup>&</sup>lt;sup>1</sup> http://livingknowledge-project.eu/

T. Margaria and B. Steffen (Eds.): ISoLA 2010, Part II, LNCS 6416, pp. 15–19, 2010.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2010

statistically acquired parameters make the overall model robust and flexible to unexpected system condition changes. Unfortunately, while attribute values and their relations with other attributes can be learned, the design of attributes suitable for representing the target system properties (e.g. a system state) has to be manually carry out. This requires expertise, intuition and deep knowledge about the expected system behavior. For example, how can system module structures be converted into attribute-value representations?

Previous work on applied machine learning research (see the proceedings of ICML, ECML, ACL, SIGIR and ICDM conferences) has shown that, although the choice of the learning algorithm affects system accuracy, feature (attribute) engineering more critically impacts the latter. Feature design is also considered the most difficult step as it requires expertise, intuition and deep knowledge about the target problem. Kernel methods is a research line towards alleviating the problem above.

#### 2 Data Representation via Kernel Methods

Kernel Methods (KM) are powerful techniques developed within the framework of statistical learning theory **IS**. They can replace attributes in learning algorithms simplifying data encoding. More specifically, kernel functions can define structural and/or semantic similarities between data objects at abstract level by replacing the similarity defined in terms of attribute matching.

The theory of KM in pattern analysis is widely discussed in [17] whereas an easier introduction can be grasped from the slides available at http://disi.unitn.eu/~moschitt/teaching.html. The main idea of KM is expressed by the following two points:

- (a) directly using a similarity function between instances in learning algorithms, thus avoiding explicit feature design; and

- (b) such function implicitly corresponds to attribute matching (more precisely scalar product) defined in huge feature spaces (possibly infinite), e.g. similarity between structures can be defined as substructure matching in the substructure space.

The first point states that instead of describing our data, e.g. a data stream, in terms of features (which aim at capturing the most interesting properties or behavior), it is enough to define a function capable to measure the similarity between any pair of different data objects, e.g. pairs of streams.

The second bullet emphasizes the great power of KM as the representations that can be modeled with them are extremely rich and are not computationally limited by the size of feature spaces.

<sup>&</sup>lt;sup>2</sup> ICML and ECML are the International and European Conferences of Machine Learning, respectively. ACL is the Conference for Association of Computational Linguistics; IR is the most important conference for Information Retrieval and ICDM is the International Conference on Data Mining.

KM effectiveness has been shown in many ICT fields, e.g. in Bioinformatics [16], Speech Processing [1], Image Processing [5], Computational Linguistics [9], Data Mining [4] and so on. In particular, KM have been used to encode syntactic and/or semantic structures in the form of trees and sequences in learning algorithms, e.g. [2]3/7/19/10/20/14/11/13/12.

Given the wide and successful use of KM, they have been applied in the Living-Knowledge project to model several aspects of automatic knowledge acquisition and management, which are basic building blocks required by the project.

#### 3 Using Kernels for Semantic Inference in LivingKnowledge

Judgements, assessments and opinions play a crucial role in many areas of our societies, including politics and economics. They reflect knowledge diversity in perspective and goals. The vision inspiring LivingKnowledge (LK) is to consider diversity as an asset and to make it traceable, understandable and exploitable, with the goal to improve navigation and search in very large multimodal datasets (e.g., the Web itself).

To design systems that are capable of automatically analyzing opinions in *free text*, it is necessary to consider syntactic/semantic structures of natural language expressed in the target documents. Although several sources of information and knowledge are considered in LK, we here illustrate an example focused on text. Given a natural language sentence like for example:

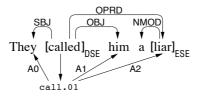

#### They called him a liar.

the opinion analysis requires to determine: (i) the opinion holder, i.e. *They*, (ii) the direct subjective expressions (DSEs), which are explicit mentions of opinion, i.e. *called*, and (iii) the expressive subjective elements (ESEs), which signal the attitude of the speakers by means of the words they choose, i.e. *liar*.

In order to automatically extract such data, the overall sentence semantics must be considered. In turn, this can be derived by representing the syntactic and shallow semantic dependencies between sentence words. Figure 11 shows a graph representation, which can be automatically generated by off-the-shelf syntactic/semantic parsers, e.g. 61, 81. The oriented arcs, above the sentences, represent syntactic dependencies whereas the arcs below are shallow semantic

Fig. 1. Syntactic and shallow semantic structure

(or semantic role) annotations. For example, the predicate *called*, which is an instance of the PropBank [15] frame call.01, has three semantic arguments: the Agent (A0), the Theme (A1), and a second predicate (A2), which are realized on the surface-syntactic level as a subject, a direct object, and an object predicative complement, respectively.

Once the richer representation above is available, we need to encode it in the learning algorithm, which will be applied to learn the functionality (subjective expression segmentation and recognition) of the target system module, i.e. the opinion recognizer. Since such graphs are essentially trees, we exploit the ability of tree kernels 10 to represent them in terms of subtrees, i.e. each subtree will be generated as an individual feature of the huge space of substructures.

Regarding practical design, kernels for structures such us trees, sequences and sets of them are available in the SVM-Light-TK toolkit (http://disi. unitn.it/moschitti/Tree-Kernel.htm). This encodes several structural kernels in Support Vector Machines, which is one of the most accurate learning algorithm [18].

Our initial test on the LivingKnowledge tasks suggests that kernel methods and machine learning are an effective approach to model the complex semantic phenomena of natural language.

# 4 Conclusion

Recently, Information Technology research has been addressed to the use of machine learning for automatic design of critical system components, e.g. automatic recognition of critical data patterns. The major advantage is that the system behavior can be automatically learned from training examples. The most critical disadvantage is the complexity to model effective system parameters (attributes), especially when they are structured.

Kernel Methods (KM) are powerful techniques that can replace attributevalue representations by defining structural and/or semantic similarities between data objects (e.g. system states) at abstract level. For example, to encode the information in a data stream, we just define a function measuring the similarity between pairs of different streams: such function can be modeled in extremely rich and large feature spaces.

A considerable amount of previous work shows the benefit of employing KM and our initial study in LivingKnowledge, whose application domain requires to model complex textual and image information, further demonstrate their benefits.

#### Acknowledgements

This research has been supported by the EC project, EternalS: Trustworthy Eternal Systems via Evolving Software, Data and Knowledge, project number FP7 247758.

### References

- Campbell, W.M.: Generalized linear discriminant sequence kernels for speaker recognition. In: International Conference on Acoustics, Speech, and Signal Processing (2002)

- Collins, M., Duffy, N.: New Ranking Algorithms for Parsing and Tagging: Kernels over Discrete Structures, and the Voted Perceptron. In: Proceedings of ACL 2002 (2002)

- 3. Culotta, A., Sorensen, J.: Dependency Tree Kernels for Relation Extraction. In: Proceedings of ACL 2004 (2004)

- 4. Gärtner, T.: A survey of kernels for structured data. SIGKDD Explor. Newsl. 5(1), 49–58 (2003)

- 5. Grauman, K., Darrell, T.: The pyramid match kernel: Discriminative classification with sets of image features. In: International Conference on Computer Vision (2005)

- Johansson, R., Nugues, P.: Dependency-based syntactic–semantic analysis with PropBank and NomBank. In: Proceedings of the Shared Task Session of CoNLL 2008 (2008)

- 7. Kudo, T., Matsumoto, Y.: Fast methods for kernel-based text analysis. In: Proceedings of ACL 2003 (2003)

- Moschitti, A., Coppola, B., Giuglea, A., Basili, R.: Hierarchical semantic role labeling. In: CoNLL 2005 shared task (2005)

- 9. Moschitti, A.: A study on convolution kernels for shallow semantic parsing. In: Proceedings of ACL 2004 (2004)

- Moschitti, A.: Efficient convolution kernels for dependency and constituent syntactic trees. In: Fürnkranz, J., Scheffer, T., Spiliopoulou, M. (eds.) ECML 2006. LNCS (LNAI), vol. 4212, pp. 318–329. Springer, Heidelberg (2006)

- 11. Moschitti, A.: Making tree kernels practical for natural language learning. In: Proccedings of EACL 2006 (2006)

- Moschitti, A.: Kernel methods, syntax and semantics for relational text categorization. In: Proceeding of CIKM 2008 (2008)

- Moschitti, A., Quarteroni, S., Basili, R., Manandhar, S.: Exploiting syntactic and shallow semantic kernels for question/answer classification. In: Proceedings of ACL 2007 (2007)

- 14. Moschitti, A., Zanzotto, F.M.: Fast and effective kernels for relational learning from texts. In: ICML 2007 (2007)

- 15. Palmer, M., Gildea, D., Kingsbury, P.: The proposition bank: An annotated corpus of semantic roles. Comput. Linguist. 31(1), 71–106 (2005)

- Schšlkopf, B., Guyon, I., Weston, J.: Statistical learning and kernel methods in bioinformatics. In: Artificial Intelligence and Heuristic Methods in Bioinformatics (2003)

- 17. Taylor, J.S., Cristianini, N.: Kernel Methods for Pattern Analysis. Cambridge University Press, Cambridge (2004)

- 18. Vapnik, V.N.: Statistical Learning Theory. Wiley-Interscience, Hoboken (1998)

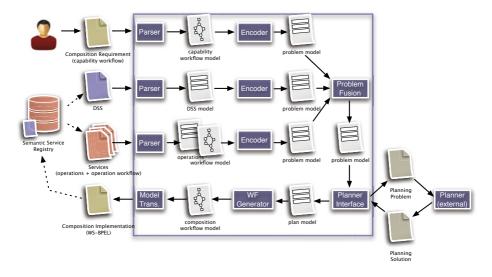

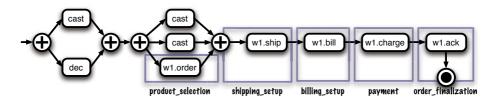

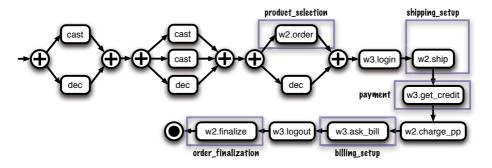

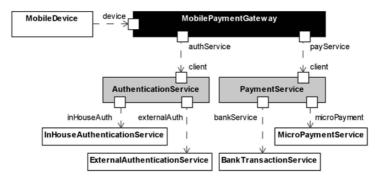

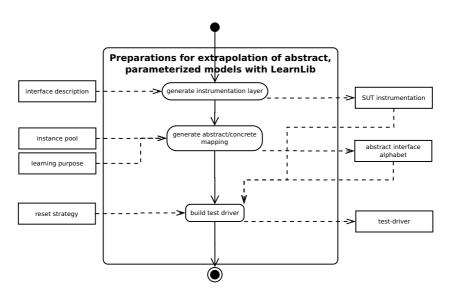

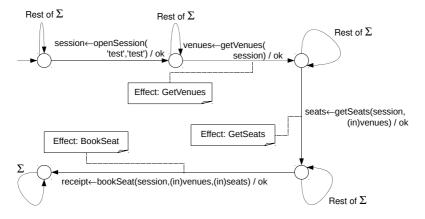

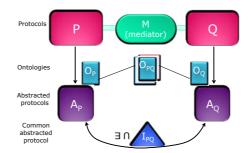

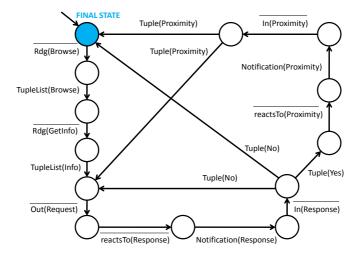

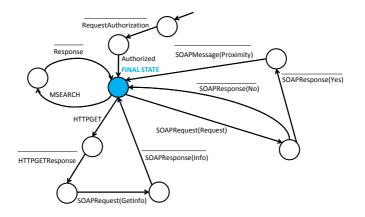

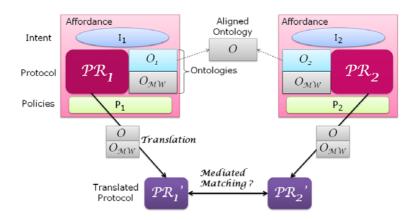

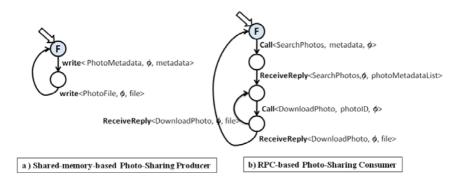

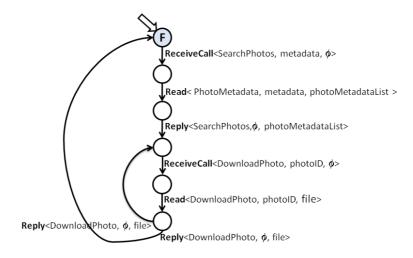

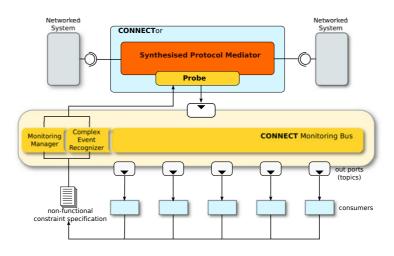

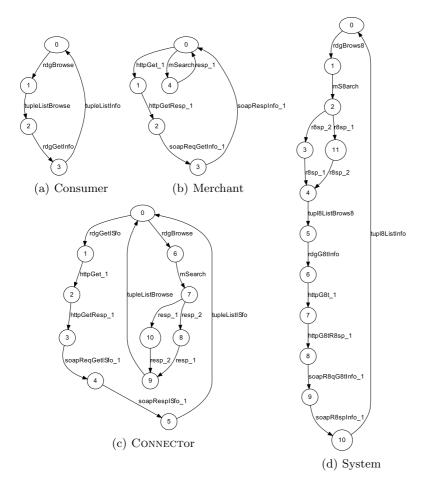

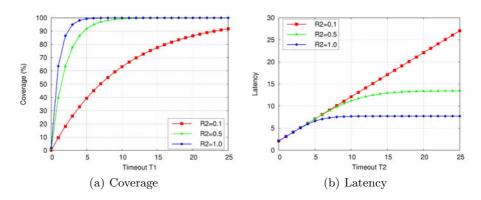

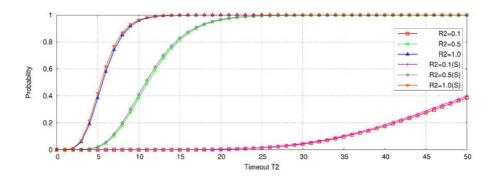

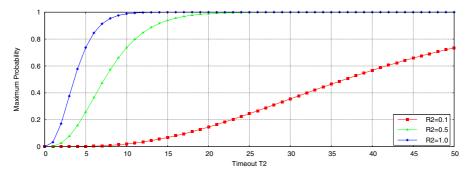

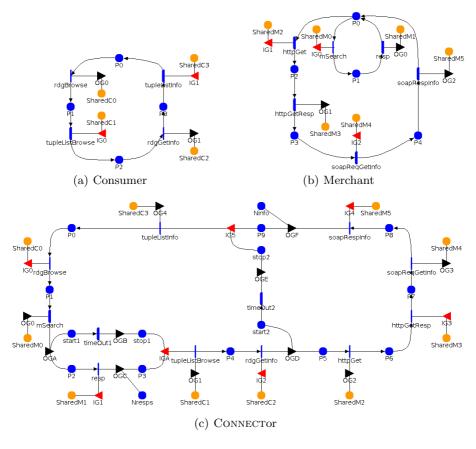

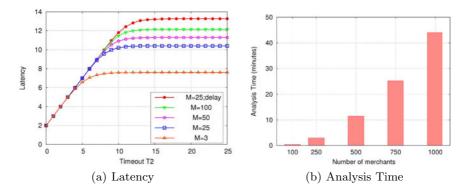

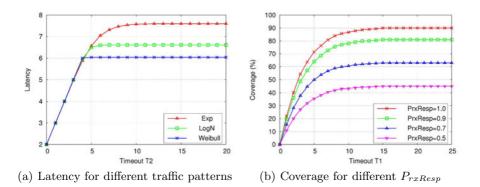

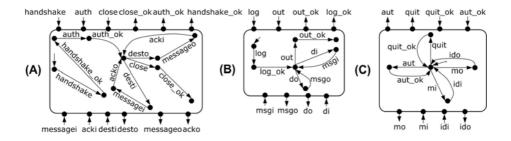

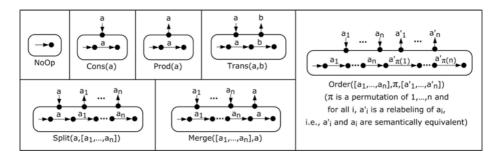

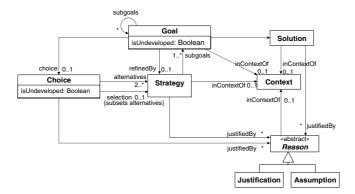

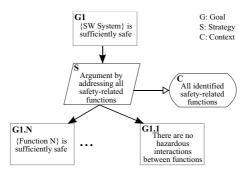

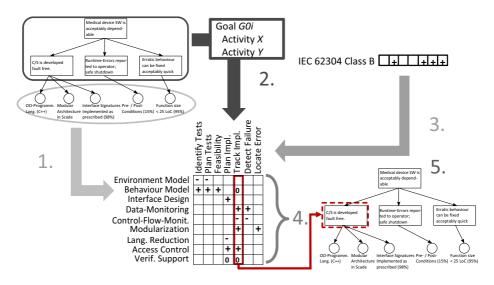

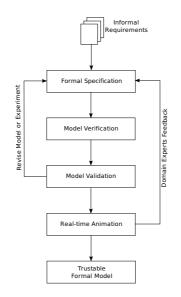

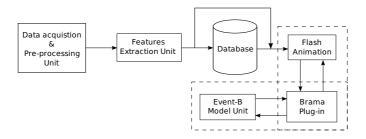

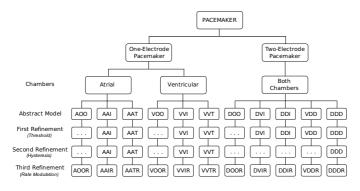

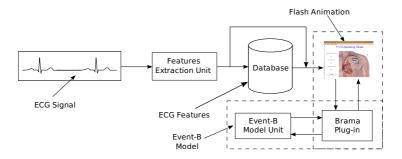

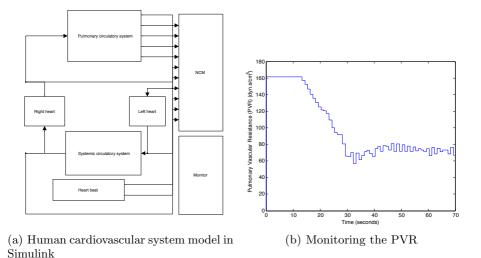

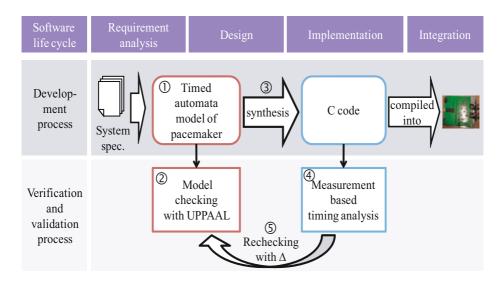

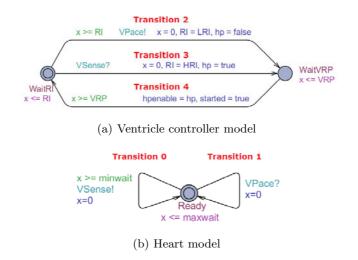

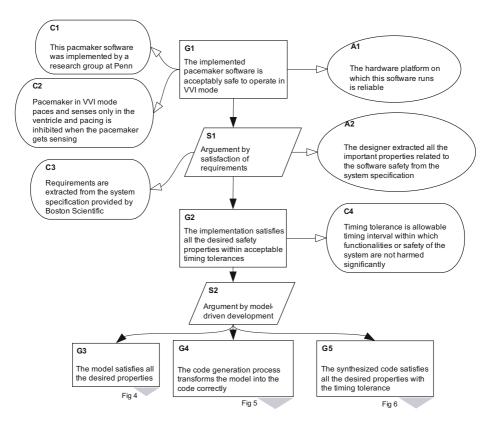

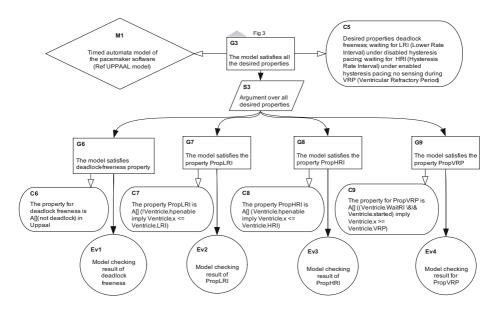

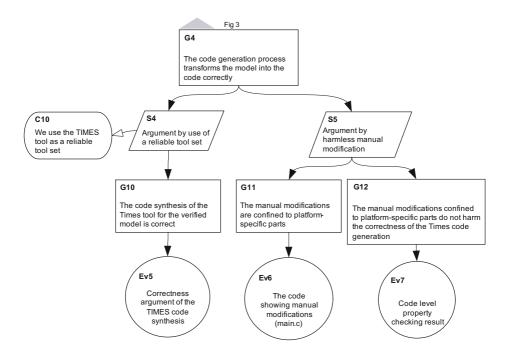

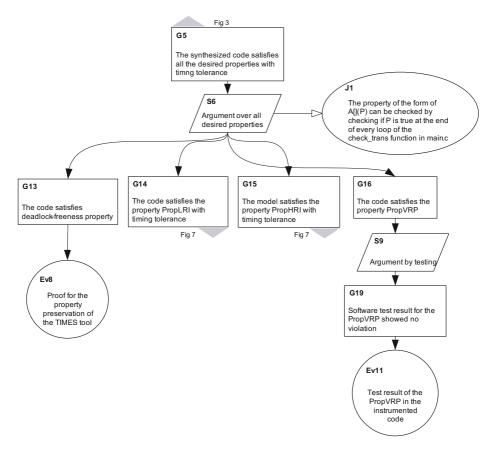

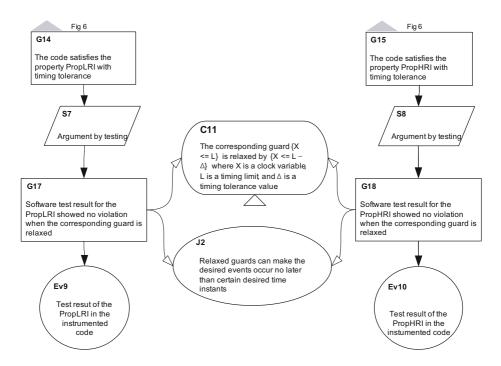

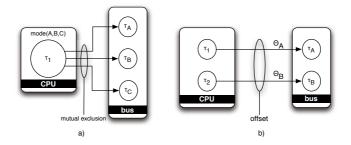

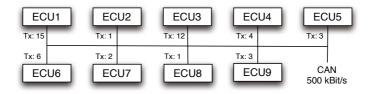

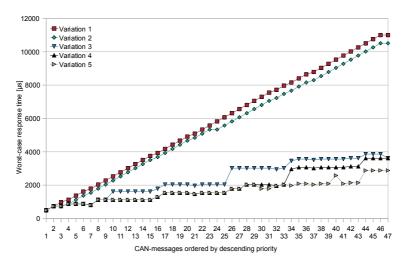

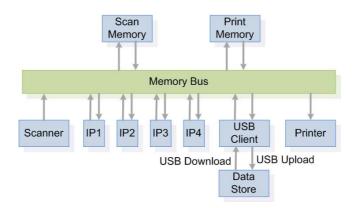

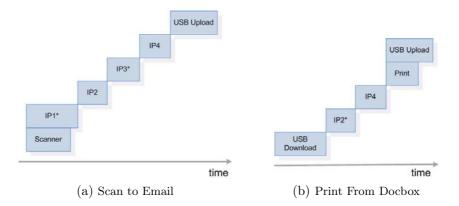

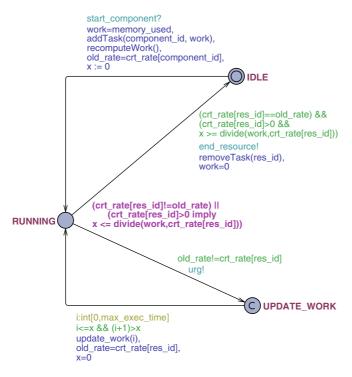

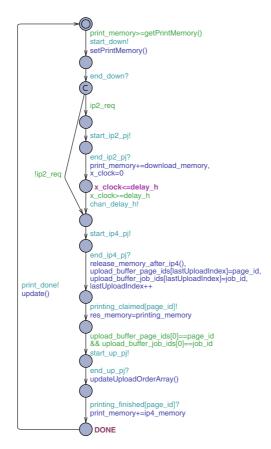

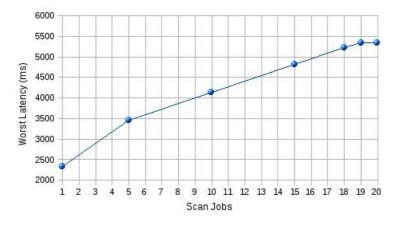

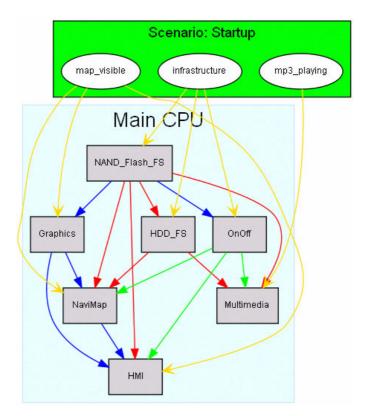

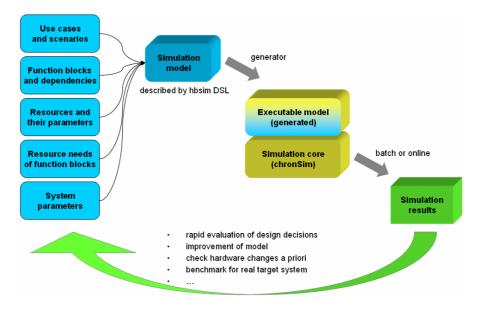

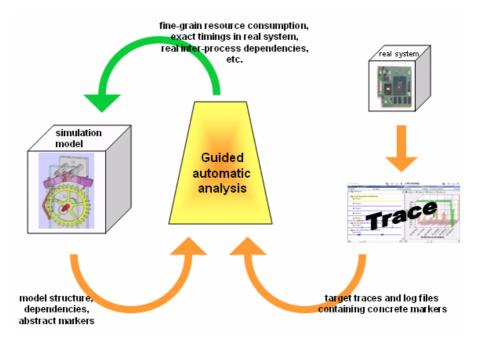

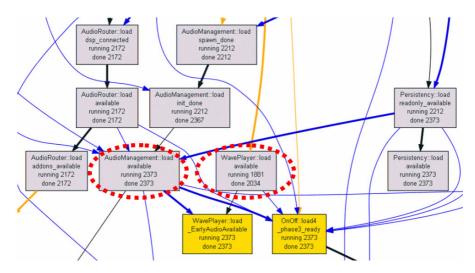

- Zhang, D., Lee, W.S.: Question classification using support vector machines. In: Proceedings of the 26th annual international ACM SIGIR conference on Research and development in information retrieval, pp. 26–32. ACM Press, New York (2003)