Rainer Keller David Kramer Jan-Philipp Weiss (Eds.)

# LNCS 6310

# Facing the Multicore-Challenge

Aspects of New Paradigms and Technologies in Parallel Computing

# Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Rainer Keller David Kramer Jan-Philipp Weiss (Eds.)

# Facing the Multicore-Challenge

Aspects of New Paradigms and Technologies in Parallel Computing

#### Volume Editors

Rainer Keller High Performance Computing Center Stuttgart (HLRS) Universität Stuttgart Nobelstr. 19 70569 Stuttgart, Germany E-mail: keller@hlrs.de

David Kramer Institute of Computer Science and Engineering Karlsruhe Institute of Technology, Germany Haid-und-Neu-Str. 7 76131 Karlsruhe, Germany E-mail: kramer@kit.edu

Jan-Philipp Weiss Engineering Mathematics and Computing Lab (EMCL) & Institute for Applied and Numerical Mathematics 4 Karlsruhe Institute of Technology, Germany Fritz-Erler-Str. 23 76133 Karlsruhe, Germany E-mail: jan-philipp.weiss@kit.edu

#### Library of Congress Control Number: 2010935359

#### CR Subject Classification (1998): D.1-3, C.1.4, C.4, I.3.1, F.2.1, G.1

LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-642-16232-0 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-642-16232-9 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### springer.com

© Springer-Verlag Berlin Heidelberg 2010 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper 06/3180

## Preface

The proceedings at hand are the outcome of the conference for young scientists titled *Facing the Multicore-Challenge* held at the Heidelberger Akademie der Wissenschaften, March 17–19, 2010. The conference focused on topics related to the impact of multicore and coprocessor technologies in science and for large-scale applications in an interdisciplinary environment. The conference was funded by the Heidelberger Akademie der Wissenschaften and placed emphasis on the support and advancement of young scientists.

The aim of the conference was to bring together leading experts as well as motivated young researchers in order to discuss, recent developments, the present status of the field, and its future prospects the exchange of ideas, in a pleasant atmosphere that stimulates. It was the designated goal to address current issues including mathematical modeling, design of parallel algorithms, aspects of microprocessor architecture, parallel programming languages, compilers, hardware-aware computing, heterogeneous platforms, emerging architectures, tools, performance tuning, and requirements for large-scale applications. This broad range of issues is reflected by the present conference proceedings. The results of the presented research papers clearly show the potential of emerging technologies in the area of multicore and manycore processors that are paving the way towards personal supercomputing. However, many issues related to parallel programming environments, development of portable and future-proof concepts, and the design of scalable and manycore-ready algorithms still need to be addressed in future research. Some of these points are the subject of the presented papers.

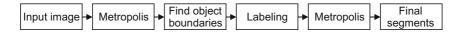

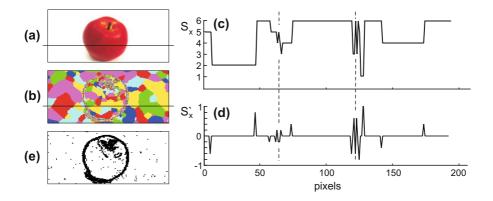

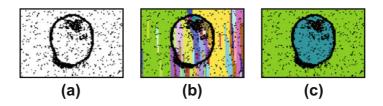

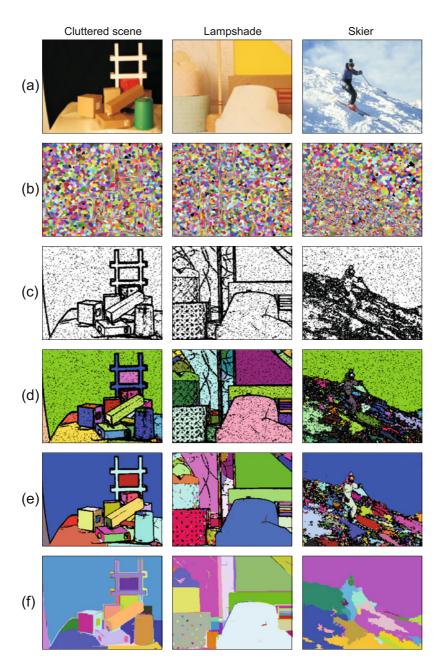

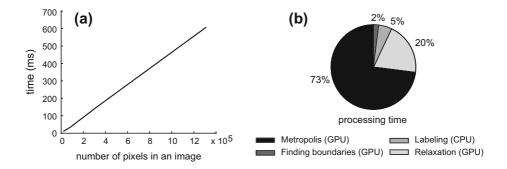

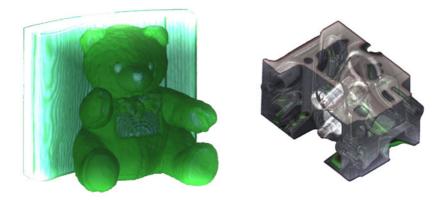

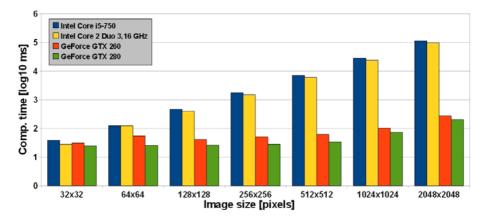

These proceedings include diverse and interdisciplinary research work. An assessment of parallel programming environments like the RapidMind platform and the perspective of GPGPU computing in large data centers is presented. The proceedings further address issues of hardware architecture by exploring way-adaptable caches. The management of parallel units is considered in papers on thread affinities and on thread creation. Application aspects on modern processor technologies are investigated for the Cell Broadband Engine by means of the G-means application for data mining and a numerical study on 3D multigrid methods. A complex fluid dynamic application modeled by the lattice Boltzmann equations is considered on multi- and manycore processors like the multicore CPUs, GPUs, and Cell. The potential of FPGA and GPU technology is outlined for a sorting problem. Application studies on GPUs include image segmentation and parallel volume rendering. Furthermore, fault tolerance of pipeline workflows is the subject of presented research work.

The conference organizers and editors would like to thank the Heidelberger Akademie der Wissenschaften for giving us the opportunity to organize this conference at this inspiring venue. Without the funding of the Heidelberger Akademie der Wissenschaften and the comprehensive support for this fruitful event this conference would not have been possible. In particular, we would like to thank all the friendly people at the Heidelberger Akademie der Wissenschaften for making this conference happen. Last but not least, thank you very much to all the contributors submitting exciting, novel work and providing multi-facetted input to the discussions.

March 2010

Rainer Keller David Kramer Jan-Philipp Weiss

#### Preface from the Heidelberg Academy of Sciences and Humanities

The focus of this publication is: How are innovative computer systems going to have a crucial impact on all branches of science and technology? Multicore systems are opening up new perspectives to cope with challenges which seemed to have been out of range to be mastered up to now. However, they are also posing new challenges in adapting all domains, ranging from mathematical modeling, numerical methods and algorithms to software and hardware design and development. The contributions presented in this volume offer a survey on the state of the art, the concepts and perspectives for future developments. They are an outcome of an inspiring conference conceived and organized by the editors within the junior scientist program of Heidelberg Academy for Sciences and Humanities. The Academy is happy to promote junior scientists getting involved in innovative research and daring to break new ground. Springer deserves high recognition for handling the publication efficiently and thus helping to face the multicore challenges.

Willi Jäger

#### Acknowledgements

The conference *Facing the Multicore-Challenge* has been kindly funded and supported by the Heidelberger Akademie der Wissenschaften, Karlstr. 4, 69117 Heidelberg. The Shared Research Group 16-1 of Jan-Philipp Weiss has received financial support by the Concept for the Future of Karlsruhe Institute of Technology in the framework of the German Excellence Initiative and the industrial collaboration partner Hewlett-Packard.

# Organization

#### General Chair

| Jan-Philipp Weiss | Karlsruhe Institute of Technology, Germany |

|-------------------|--------------------------------------------|

| Rainer Keller     | Oak Ridge National Laboratory, USA         |

| David Kramer      | Karlsruhe Institute of Technology, Germany |

#### Mentorship

Willi Jäger

University of Heidelberg, Germany

#### **Program Committee**

David A. Bader Michael Bader Rosa Badia **Richard Barrett** Mladen Berekovic Arndt Bode George Bosilca Jim Bovay Rainer Buchty Mark Bull Hans-Joachim Bungartz Franck Cappello Claudia Fohrv Richard Graham Thomas Herault Hans Herrmann Vincent Heuveline Michael Hübner Ben Juurlink Wolfgang Karl Rainer Keller Hiroaki Kobayashi Manfred Krafczyk Hsin-Ying Lin Anton Lokhmotov Dieter an Mey Bernd Mohr Claus-Dieter Munz

Georgia Tech, Atlanta, USA University of Stuttgart, Germany Barcelona Supercomputing Center, Spain Oak Ridge National Labs, USA TU Braunschweig, Germany TU Munich, Germany University of Tennessee Knoxville, USA Hewlett-Packard, USA Karlsruhe Institute of Technology, Germany EPCC, Edinburgh, UK TU Munich, Germany LRI. Université Paris Sud. France Kassel University, Germany Oak Ridge National Labs, USA Université Paris Sud. France ETH. Zürich. Switzerland Karlsruhe Institute of Technology, Germany Karlsruhe Institute of Technology, Germany TU Berlin, Germany Karlsruhe Institute of Technology, Germany Oak Ridge National Labs, USA Tohoku University, Japan TU Braunschweig, Germany Intel, USA Imperial College, London, UK **RWTH** Aachen, Germany FZ Jülich, Germany Stuttgart University, Germany

Norihiro Nakajima Wolfgang Nagel Christian Perez Franz-Josef Pfreundt Rolf Rabenseifner Thomas Rauber Michael Resch Gudula Rünger **Olaf Schenk** Martin Schulz Masha Sosonkina Thomas Steinke Carsten Trinitis Stefan Turek Wolfgang Wall Gerhard Wellein Josef Weidendorfer Jan-Philipp Weiss Felix Wolf Stephan Wong

JAEA and CCSE, Japan TU Dresden, Germany INRIA, France ITWM Kaiserslautern, Germany HLRS, Stuttgart, Germany Bayreuth University, Germany HLRS, Stuttgart, Germany Chemnitz Technical University, Germany Basel University, Basel, Switzerland Lawrence Livermore National Labs, USA Ames Lab, USA ZIB, Berlin, Germany TUM, Munich, Germany Dortmund University, Germany TUM, Munich, Germany RRZE, Erlangen, Germany TUM, Munich, Germany Karlsruhe Institute of Technology, Germany FZ Jülich, Germany TUD, Delft, The Netherlands

# Table of Contents

# Invited Talks

| Analyzing Massive Social Networks Using Multicore and Multithreaded<br>Architectures                                                                                                                  | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| MareIncognito: A Perspective towards Exascale<br>Jesus Labarta                                                                                                                                        | 2  |

| The Natural Parallelism<br>Robert Strzodka                                                                                                                                                            | 3  |

| Computer Architecture and Parallel Programming                                                                                                                                                        |    |

| RapidMind: Portability across Architectures and Its Limitations<br>Iris Christadler and Volker Weinberg                                                                                               | 4  |

| A Majority-Based Control Scheme for Way-Adaptable Caches<br>Masayuki Sato, Ryusuke Egawa, Hiroyuki Takizawa, and<br>Hiroaki Kobayashi                                                                 | 16 |

| Improved Scalability by Using Hardware-Aware Thread Affinities<br>Sven Mallach and Carsten Gutwenger                                                                                                  | 29 |

| Thread Creation for Self-aware Parallel Systems<br>Martin Schindewolf, Oliver Mattes, and Wolfgang Karl                                                                                               | 42 |

| Applications on Multicore                                                                                                                                                                             |    |

| G-Means Improved for Cell BE Environment<br>Aislan G. Foina, Rosa M. Badia, and Javier Ramirez-Fernandez                                                                                              | 54 |

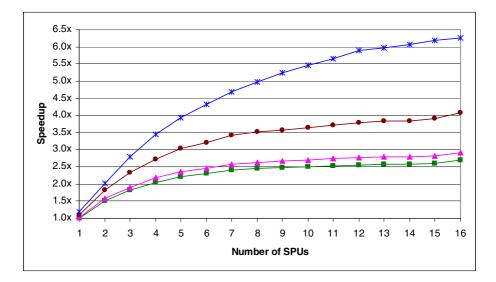

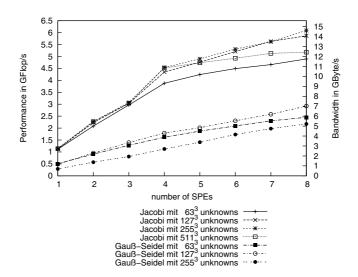

| Parallel 3D Multigrid Methods on the STI Cell BE Architecture<br>Fabian Oboril, Jan-Philipp Weiss, and Vincent Heuveline                                                                              | 66 |

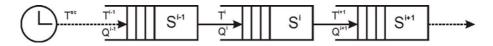

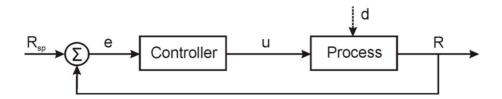

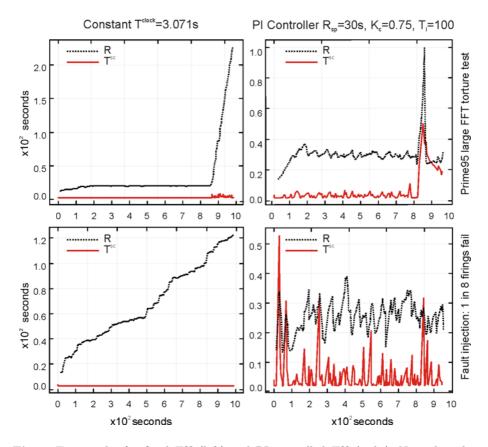

| Applying Classic Feedback Control for Enhancing the Fault-Tolerance<br>of Parallel Pipeline Workflows on Multi-core Systems<br><i>Tudor B. Ionescu, Eckart Laurien, and Walter Scheuermann</i>        | 79 |

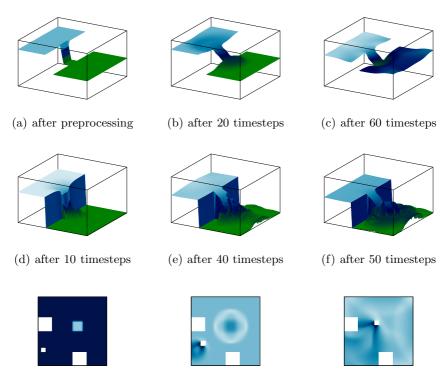

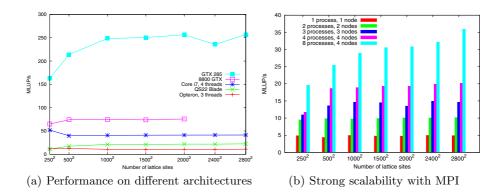

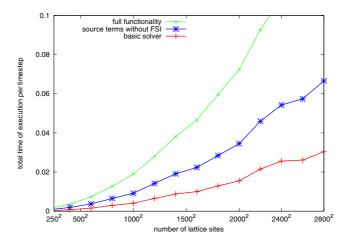

| Lattice-Boltzmann Simulation of the Shallow-Water Equations with<br>Fluid-Structure Interaction on Multi- and Manycore Processors<br>Markus Geveler, Dirk Ribbrock, Dominik Göddeke, and Stefan Turek | 92 |

|                                                                                                                                                                                                       |    |

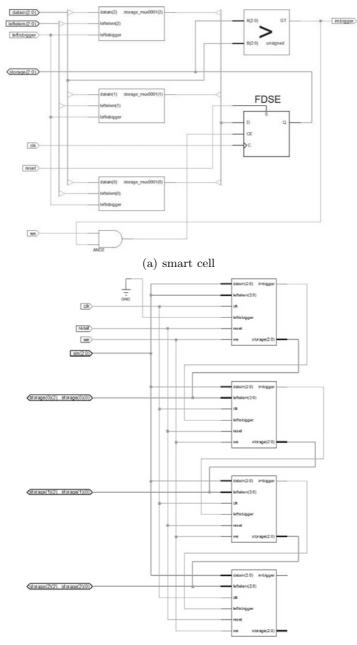

| FPGA vs. Multi-core CPUs vs. GPUs: Hands-On Experience with a |     |

|---------------------------------------------------------------|-----|

| Sorting Application                                           | 105 |

| Cristian Grozea, Zorana Bankovic, and Pavel Laskov            |     |

# **GPGPU** Computing

| Considering GPGPU for HPC Centers: Is it Worth the Effort?<br>Hans Hacker, Carsten Trinitis, Josef Weidendorfer, and<br>Matthias Brehm | 118 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Real-Time Image Segmentation on a GPU<br>Alexey Abramov, Tomas Kulvicius, Florentin Wörgötter, and<br>Babette Dellen                   | 131 |

| Parallel Volume Rendering Implementation on Graphics Cards Using<br>CUDAJens Fangerau and Susanne Krömker                              | 143 |

| Author Index                                                                                                                           | 155 |

# Analyzing Massive Social Networks Using Multicore and Multithreaded Architectures

David Bader

Georgia Institute of Technology, USA

Abstract. Emerging real-world graph problems include detecting community structure in large social networks, improving the resilience of the electric power grid, and detecting and preventing disease in human populations. Unlike traditional applications in computational science and engineering, solving these problems at scale often raises new challenges because of sparsity and the lack of locality in the data, the need for additional research on scalable algorithms and development of frameworks for solving these problems on high performance computers, and the need for improved models that also capture the noise and bias inherent in the torrential data streams. The explosion of real-world graph data poses a substantial challenge: How can we analyze constantly changing graphs with billions of vertices? Our approach leverages the Cray XMT's finegrained parallelism and flat memory model to scale to massive graphs. On the Cray XMT, our static graph characterization package GraphCT summarizes such massive graphs, and our ongoing STINGER streaming work updates clustering coefficients on massive graphs at a rate of tens of thousands updates per second.

## MareIncognito: A Perspective towards Exascale

Jesus Labarta

Barcelona Supercomputing Centre, Spain

**Abstract.** MareIncognito is a cooperative project between IBM and the Barcelona Supercomputing Center (BSC) targeting the design of relevant technologies on the way towards exascale. The initial challenge of the project was to study the potential design of a system based on a next generation of Cell processors. Even so, the approaches pursued are general purpose, applicable to a wide range of accelerator and homogeneous multicores and holistically addressing a large number of components relevant in the design of such systems.

The programming model is probably the most important issue when facing the multicore era. We need to offer support for asynchronous data flow execution and decouple the way source code looks like and the way the program is executed and its operations (tasks) scheduled. In order to ensure a reasonable migration path for programmers the execution model should be exposed to them through a syntactical and semantic structure that is not very far away from current practice. We are developing the StarSs programming model which we think addresses some the challenges of targeting the future heterogeneous / hierarchical multicore systems at the node level. It also integrates nicely into coarser level programming models such as MPI and what is more important in ways that propagate the asynchronous dataflow execution to the whole application. We are also investigating how some of the features of StarSs can be integrated in OpenMP.

At the architecture level, interconnect and memory subsystem are two key components. We are studying in detail the behavior of current interconnect systems and in particular contention issues. The question is to investigate better ways to use the raw bandwidth that we already have in our systems and can expect to grow in the future. Better understanding of the interactions between the raw transport mechanisms, the communication protocols and synchronization behavior of applications should lead to avoid an exploding need for bandwidth that is often claimed. The use of the asynchronous execution model that StarSs offers can help in this direction as a very high overlap between communication and computation should be possible. A similar effect or reducing sensitivity to latency as well as the actual off chip bandwidth required should be supported by the StarSs model.

The talk will present how we target the above issues, with special details on the StarSs programming model and the underlying idea of the project of how tight cooperation between architecture, run time, programming model, resource management and application are needed in order to achieve in the future the exascale performance.

# The Natural Parallelism

Robert Strzodka

Max Planck Institut Informatik, Saarbruecken, Germany

**Abstract.** With the advent of multi-core processors a new unwanted way of parallel programming is required which is seen as a major challenge. This talk will argue in exactly the opposite direction that our accustomed programming paradigm has been unwanted for years and parallel processing is the natural scheduling and execution model on all levels of hardware.

Sequential processing is a long outdated illusionary software concept and we will expose its artificiality and absurdity with appropriate analogies of everyday life. Multi-core appears as a challenge only when looking at it from the crooked illusion of sequential processing. There are other important aspects such as specialization or data movement, and admittedly large scale parallelism has also some issues which we will discuss. But the main problem is changing our mindset and helping others to do so with better education so that parallelism comes to us as a friend and not enemy.

# RapidMind: Portability across Architectures and Its Limitations

Iris Christadler and Volker Weinberg

Leibniz-Rechenzentrum der Bayerischen Akademie der Wissenschaften, D-85748 Garching bei München, Germany

**Abstract.** Recently, hybrid architectures using accelerators like GP-GPUs or the Cell processor have gained much interest in the HPC community. The "RapidMind Multi-Core Development Platform" is a programming environment that allows generating code which is able to seamlessly run on hardware accelerators like GPUs or the Cell processor and multi-core CPUs both from AMD and Intel. This paper describes the ports of three mathematical kernels to RapidMind which have been chosen as synthetic benchmarks and representatives of scientific codes. Performance of these kernels has been measured on various RapidMind backends (cuda, cell and x86) and compared to other hardware-specific implementations (using CUDA, Cell SDK and Intel MKL). The results give an insight into the degree of portability of RapidMind code and code performance across different architectures.

#### 1 Introduction

The vast computing horsepower which is offered by hardware accelerators and their usually good power efficiency has aroused interest of the high performance computing community in these devices. The first hybrid system which entered the Top500 list  $\blacksquare$  was the TSUBAME cluster at Tokyo Institute of Technology in Japan. Several hundred Clearspeed cards were used to accelerate an Opteron based cluster; the system was ranked No. 9 in the Top500 list in November 2006. Already in June 2006, a sustained Petaflop/s application performance was firstly reached with the RIKEN MD-GRAPE 3 system in Japan, a special purpose system dedicated for molecular dynamics simulations. In 2008, the first system ever to reach a sustained High Performance LINPACK (HPL) performance of more than one Petaflop/s was "Roadrunner", the No. 1 system on the lists in July 2008 and November 2008. Roadrunner is a hybrid system based on Opteron processors and accelerated with PowerXCell8i processors, a variant of the Cell B.E. (Broadband Engine) with increased double-precision capability.

However, applicability of hardware accelerators for general-purpose HPC systems is still a source of debate. In 2008, the landscape was quite diverse; many different hardware solutions existed (Cell, Nvidia and AMD/ATI GPUs, Clear-Speed accelerator boards, FPGA based systems) and every system had its own programming language and paradigm. At the same time, the x86 processors started to become multi-core processors and first HPC systems were based on

R. Keller et al. (Eds.): Facing the Multicore-Challenge, LNCS 6310, pp. 4-15, 2010.

hundred thousands of cores. Improving the scalability of HPC codes to be able to utilize the increased core counts was already difficult for the scientific communities; trying to add support for one of the new accelerators was a huge porting effort with a high risk: what if either the hardware or the software would not be supported on the long run? Solutions which offered support for different hardware architectures became appealing.

While in the meantime several solutions (e.g. OpenCL 2, PGI accelerator compiler 3, CAPS hmpp 4, StarSs 5) exist which provide an abstraction of the underlying hardware characteristics from the programmer, the situation was different two years ago: RapidMind Inc. was one of the first companies providing support for general purpose computing on graphic processing units, nowadays known as GPGPUs. RapidMind started in 2004 based on the academic research related to the Sh project 6 at the University of Waterloo. Their work was started at a time when the first "programmable" GPUs were just released and the only way to program these devices was by using "shading languages". Already at that time people tried porting simulation codes to GPUs 7. Since then, RapidMind has subsequently added the Cell processor backend (2007) and the x86 multi-core processor backend with the rise of multi-core processor CPUs for the consumer market (2008). In 2009, version 4.0 was released which introduced the cuda backend, necessary to support double-precision arithmetic on GPUs. Even today, RapidMind is still the only product that fully supports Cell, GPUs and multi-core CPUs. All other solutions are either limited by the hardware which they support or require an adaptation of the code.

At SC06 a paper was published which showed impressive performance gains by using RapidMind for porting three algorithms (SGEMM, FFT and Black-Scholes) to the GPU [8]. This is a follow-on work assessing the state-of-theart three years later. However, the main reason for choosing RapidMind for a deeper investigation has been its programming paradigm which differs from serial programming languages and abstracts the massive parallelism of the underlying hardware more than any other language concept currently discussed for HPC.

#### 2 Overview

#### 2.1 Software

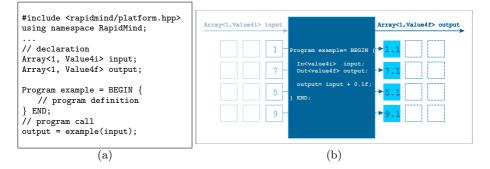

The "RapidMind Multi-Core Development Platform" promises easy and portable access not only to multi-core chips from Intel and AMD but also to hardware accelerators like GPUs and Cell. The basic concept of the RapidMind language is called "data-stream processing"; a powerful technology to express data parallelism. A simple example of a RapidMind program is given in Fig. (a). Figure (b) represents a schematic view of the executed stream program. A call to a RapidMind program can be inserted in any valid C++ program and needs to include the RapidMind library in the header of the file and during linkage. Unless specified explicitly, the RapidMind runtime environment will automatically search for available accelerator hardware and compile the program at runtime using the RapidMind backend for the detected hardware.

Fig. 1. RapidMind programming scheme

RapidMind adds special types and functions to C++ which allow the programmer to define sequences of operations (RapidMind programs) on streams of data (special arrays). With these, data dependencies and data workflows can be easily expressed and will naturally contain all necessary information for an efficient (data-) parallelization. The compiler and the runtime environment then have maximum information to decide how to auto-parallelize the code.

The structure of RapidMind code forces the programmer to decide early in the development process which operations could be performed in parallel without any side-effects. This usually results in many small code snippets that can run in parallel which is optimal to fill the pipeline of a GPU or other massively parallel devices.

#### 2.2 Hardware

Three different platforms are used for the performance measurements. An Nvidia Tesla based system is used to measure the cuda backend from RapidMind against implementations based on CUDA and the CUDA libraries cuBLAS and cuFFT. Tesla is Nvidia's first dedicated general purpose GPU with enhanced double-precision capability. A C1060 supports partly IEEE-754, consists of 240 thread processors with an overall performance of 78 GFlop/s in double-precision and 933 GFlop/s in single-precision. One Nvidia Tesla S1070 1U rack consists of four

| Hardware                                         |                          | DP peak perf. |

|--------------------------------------------------|--------------------------|---------------|

| 1 C1060 GPU                                      |                          | 78 GFlop/s    |

| 1 Tesla S1070                                    | 4140  GFlop/s            | 345  GFlop/s  |

| Nehalem-EP $(2.53 \text{ GHz}, 1 \text{ core})$  | 20  GFlop/s              | 10  GFlop/s   |

| Nehalem-EP $(2.53 \text{ GHz}, 8 \text{ cores})$ | $162 \ \mathrm{GFlop/s}$ | 81  GFlop/s   |

| 1 PowerXCell8i (8 SPUs)                          |                          | 102  GFlop/s  |

| 1 QS22-blade 2 PowerXCell8i (16 SPUs)            | $410 \ \mathrm{GFlop/s}$ | 205  GFlop/s  |

Table 1. Hardware overview

C1060 computing processors with a total single-precision performance of around 4 TFlop/s.

An IBM QS22-blade based system is used to compare RapidMind's cell backend with code using Cell intrinsics which is taken from the SDK. Each QS22blade hosts two PowerXCell8i, the processors used to accelerate Roadrunner [9]. Each PowerXCell8i is running at 3.2 GHz, is partly IEEE-754 conform and has a single-precision peak performance of 204.8 GFlop/s and a double-precision peak performance of 102.4 GFlop/s. A QS22-blade has therefore a total of slightly more than 400 GFlop/s single-precision performance. The main difference between the Cell processor and GPUs or current multi-core CPUs is its inhomogeneity; eight synergistic processor units (SPUs) are added to one PowerPC processor unit (PPU). The Cell processor has a very good performance per Watt ratio and the 6 most energy efficient supercomputers, as ranked by Green500 [10] in November 2009, are based on PowerXCell8i technology.

RapidMind's x86 backend is benchmarked against code using Intel's Math Kernel Library (MKL) on one of the latest Intel processors, a Xeon E5540 known as "Nehalem-EP". A Nehalem-EP core running at 2.53 GHz has a singleprecision peak performance slightly above 20 GFlop/s and a double-precision peak performance of around 10 GFlop/s. One Nehalem-EP node consists of 2 sockets with four cores per socket. A Nehalem-EP node with 8 cores reaches 162 GFlop/s single and 81 GFlop/s double-precision performance.

The performance figures of all three architectures are summarized in Table 1. Since the double-precision peak performance of one Nehalem-EP node (8 cores, 81 GFlop/s) is quite comparable with the double-precision performance of 1 Nvidia C1060 GPU (78 GFlop/s) and 1 PowerXCell8i (102 GFlop/s) we tried to compare these platforms directly where possible.

#### **3** The RapidMind Ports and Their Performance

To judge the suitability of recent accelerator hardware for scientific computing and high-performance computing, three mathematical kernels from the Euroben benchmark suite 11 have been chosen:

- mod2am: a dense matrix-matrix multiplication,

- mod2as: a sparse matrix-vector multiplication,

- mod2f: a one-dimensional Fast Fourier Transformation (FFT).

The kernels have been selected to show both the advantages and the pitfalls of current accelerators. They are representatives of three (dense linear algebra, sparse linear algebra and spectral methods) of the "seven dwarfs", an ontology for scientific codes introduced by **12**. According to Fig. 11 in **13** these three dwarfs account for approximately one third of the workload of current European HPC Tier-1 centers. The selection of kernels was performed by the EU FP7-project PRACE, published in **14** and should be extended to cover all important dwarfs in the future.

#### 3.1 Dense Matrix-Matrix Multiplication (mod2am)

The dense matrix-matrix multiplication  $(C = A \times B)$  is one of the most basic algorithms used in scientific computing. It is the basis of the High Performance LINPACK code, which determines the Top500 rank of a system. The schoolbook version of the algorithm is composed of three nested for-loops. Many sophisticated optimization strategies exist, and one of the fastest implementations is the MKL version. Making use of the MKL functions is straightforward and basically needs a call to cblas\_dgemm (double-precision arithmetic) or cblas\_sgemm (single-precision arithmetic).

A first implementation in RapidMind is straightforward. In a first step, the RapidMind data types must be used to express the matrices A (of size  $m \times l$ ), B  $(l \times n)$  and C  $(m \times n)$ . All matrices can be represented by two-dimensional arrays of floating point data:

```

Array<2,Value1f> A(m,1);

Array<2,Value1f> B(1,n);

Array<2,Value1f> C(m,n);

```

In a second step the RapidMind program mxm needs to be declared. Since there are no clear data streams which could be fed into the program a helper index array is used. This index array ensures that the defined program mxm can sum up the corresponding entries of the input matrices A and B. All matrices are automatically transferred to the GPU memory at execution time. The RapidMind control flow construct RM\_FOR is used to allow manipulation of the streamed data.

```

Program mxm = BEGIN {

In<Value2i> ind;

Out<Value1f> c = Value1f(0.);

Value1i k;

// Computation of C(i,j)

RM_FOR (k=0, k < Value1i(1), k++) {

c += A[Value2i(ind(0),k)]*B[Value2i(k,ind(1))];

} RM_ENDFOR;

} END;</pre>

```

The call to the RapidMind program then looks as follows:

```

C= mxm(grid(m,n));

```

The call to the RapidMind function grid(m,n) generates a virtual helper array of size  $m \times n$  which does not require additional storage. The whole helper array is automatically initialized with integers from (0,0) to (m,n) and is directly passed to the program and used for the index computation.

After this first naive approach a second, *GPU-optimized version* of the matrix multiplication has been produced. This version is based on code available at the

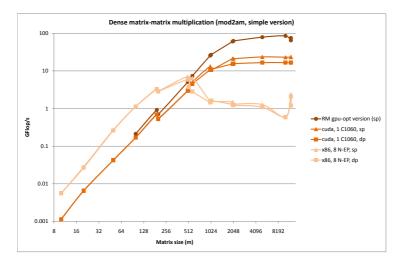

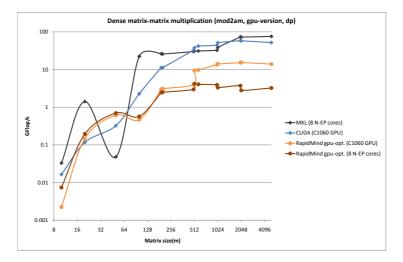

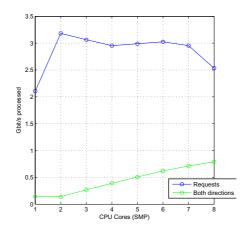

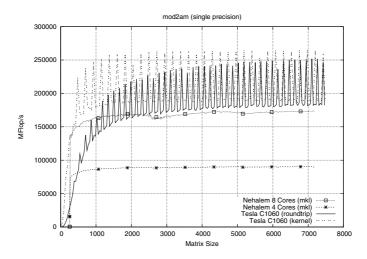

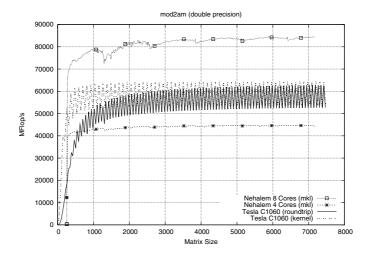

Fig. 2. Performance comparison of the simple mod2am version on various RapidMind backends and associated hardware. The simple version is also compared to the GPU-optimized version running on 1 C1060 GPU in single-precision.

RapidMind developer portal [15]. The basic difference between both versions is the fact, that the GPU-optimized version operates on arrays of Value4f, to optimal use the GPU vector registers;  $4 \times 4$  submatrices are multiplied and accumulated.

Figure <sup>[2]</sup> shows the performance of the simple version using the cuda and x86 RapidMind backends and compares the single-precision cuda backend performance with the GPU-optimized version. It can be seen that the GPU-optimized version is indeed four times faster than the naive approach for single-precision arithmetic. This means that the use of Value4f instead of Value1f really improves performance. It is important to note, that neither the language nor the program definition of the simple approach should prevent the compiler from doing this optimization by itself.

Measurements for double-precision reveal that the simple approach is actually faster than the GPU-optimized version. This is counterintuitive and only becomes understandable if one takes into account, that the cuda backend is the latest RapidMind backend and was introduced with version 4.0 in July 2009. The target of this version was to enable RapidMind to support Nvidia Tesla cards; a RapidMind version with improved performance of the cuda backend was scheduled for version 4.1.

Figure 3 shows the performance of the GPU-optimized version on various backends and compares it with hardware-specific languages (CUDA and MKL). It shows that the performance of the RapidMind implementation is more than an

<sup>&</sup>lt;sup>1</sup> Time is always measured for the execution of the whole kernel. This includes the time to transfer data between host and accelerator for GPU and Cell results. The y-axis uses log-scale to better cover the whole performance range for all matrix sizes.

Fig. 3. Performance comparision of the GPU-optimized version on various backends. Performance measurements have been performed both on an Nvidia GPU and a Nehalem-EP socket with eight cores. The RapidMind version is compared to a CUDA version based on cuBLAS and an MKL implementation of the dense matrix-matrix multiplication. Performance measurements are based on double-precision arithmetic.

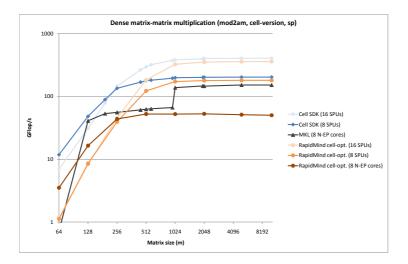

Fig. 4. Performance comparison of the Cell-optimized version on various RapidMind backends. Performance measurements have been performed on 1 PowerXCell8i (8 SPUs), 1 QS22-blade (16 SPUs) and an 8-core Nehalem-EP node. The RapidMind version is compared to a dense matrix-matrix multiplication example from the Cell SDK and the MKL implementation. All performance results are based on single-precision arithmetic.

order of magnitude slower than the MKL implementation, while the difference between RapidMind and CUDA performance is only a factor of 3. Comparing Fig. 2 with Fig. 3 reveals that the performance difference between the two RapidMind implementations varies extremely for certain matrix sizes, although the implementations vary only slightly.

The performance of both the simple version and the GPU-optimized version are not able to deliver decent performance on the Cell platform. A third version *optimized for the Cell processor* is based on another code available through the RapidMind developer portal. This time, computation is performed using a block partitioning of 64 by 64 blocks. All matrices are in a "block swizzled" format so that these blocks are contiguous in memory. The computations and memory transfers are overlapped using double buffering and are partly based on the matrix-matrix multiplication example from the IBM Cell SDK (/opt/cell/sdk/src/demos/matrix\_mul/). The Cell SDK version is also used for performance comparison.

Figure 4 gives an insight into the performance of the Cell-optimized version. Again the RapidMind figures have been compared with implementations in other languages. Since the Cell SDK version is based on single-precision arithmetic, it has been compared to single-precision results obtained with the RapidMind cell and x86 backends and an SGEMM implementation using MKL on 8 Nehalem-EP cores. This time, the RapidMind version is able to nearly meet the performance of the hardware-specific and highly optimized Cell SDK version; it reaches 88% of the SDK version. However, this comes at the price of a hardware-specific RapidMind implementation and contradicts the idea of seamlessly portable code.

In conclusion, the three different implementations illustrate the current limitations of code and performance portability. Hardly any problems were experienced when moving the code to other platforms, but in many cases the performance was not predictable. Tuning the code to better exploit certain characteristics of the employed hardware normally yields better performance but requires to stick with this hardware. The idea behind RapidMind is that the language and program definitions are generic enough to allow the compiler to do hardware-specific optimizations itself.

#### 3.2 Sparse Matrix-Vector Multiplication (mod2as)

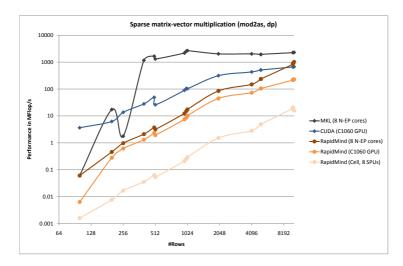

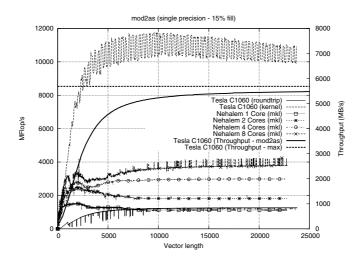

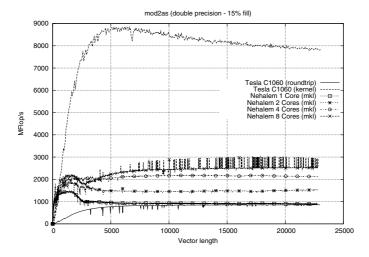

Sparse linear algebra is another building block of many scientific algorithms. The sparse matrix-vector multiplication exposes a low computational intensity and is usually memory bound. It is a good example for code that will not perform well on recent hardware accelerators on which the transfer between the x86 host memory and the accelerator memory is a severe bottleneck. Even x86 hardware will only run at a small percentage of its theoretical peak performance. While mod2am reaches more than 90% of peak, mod2as runs at rates less than 5% of peak on Nehalem-EP. Since this algorithm is not well suited for accelerators, we provided only one RapidMind mod2as implementation and put a special focus on the performance achieved with the x86 backend on Nehalem-EP (shown in Fig. [5]).

The implementation of mod2as is based on **I6**. The input matrix A of mod2as is stored in a 3-array variation of the CSR (compressed sparse row) format which can be easily transferred to RapidMind. The array **matvals** contains the non-zero elements of A, the element **i** of the integer array **indx** is the number of the column in A that contains the **i**-th value in the **matvals** array and element **j** of the integer array **rowp** gives the index of the element in the **matvals** array that is the first non-zero element in row **j** of A. The input and output vectors are declared as:

```

Array<1,Value1i> indx(nelmts);

Array<1,Value1i> rowp(nrows+1);

Array<1,Value1f> matvals(nelmts);

Array<1,Value1f> invec(ncols);

Array<1,Value1f> outvec(nrows);

```

Once again a helper array based on a call to grid(nrows) is created and used as input vector to allow the correct index computation. The RapidMind program is very clean: using RapidMind's RM\_FOR() control structure, the program loops over one row of the input matrix and computes the matrix-vector product.

```

Program spMXV = BEGIN {

In<Value1i> i;

Out<Value1f> c;

c = Value1f(0.);

Value1i j;

RM_FOR(j=rowp[i], j < rowp[i+1], j++) {

c += matvals[j] * invec[indx[j]];

} RM_ENDFOR;</pre>

```

} END;

#### 3.3 One-Dimensional Fast Fourier Transformation (mod2f)

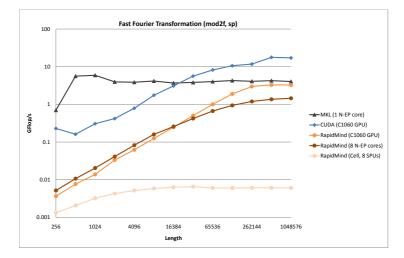

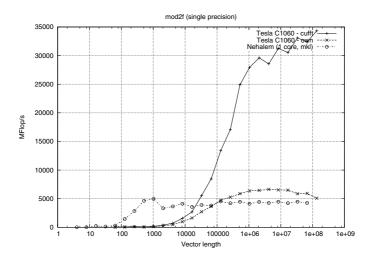

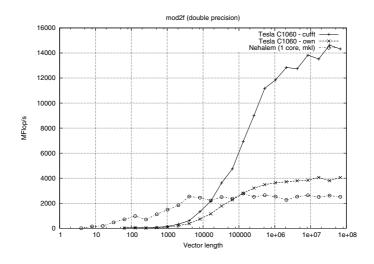

The Fast Fourier Transformation (FFT) is widely used in many scientific programs. Its computational intensity is not as high as for mod2am, but is already in a range where accelerators should be beneficial. The RapidMind version of mod2f computes the FFT using a split-stream algorithm as described in [17]. The implementation is a straightforward conversion of a one butterfly Cooley-Tukey radix-2 FFT; the butterfly kernels are defined as RapidMind programs. Figure [6] gives the achieved performance for different platforms and shows that one implementation is able to deliver performance on at least two backends.

Fig. 5. Performance comparison of the sparse matrix-vector multiplication. Performance results for the RapidMind implementation on various backends are given and compared with implementations in CUDA and based on MKL. The difference between the MKL and the RapidMind x86-results is less than a factor of 3 for big matrix sizes.

Fig. 6. Performance comparison of the one-dimensional Fast Fourier Transformation. The RapidMind implementation is compared to a CUDA version of mod2f based on cuFFT and the corresponding MKL implementation. The gap between the RapidMind cuda-results and the highly-optimized cuFFT version is a factor of 5, the difference between the x86-results and the MKL version is again less than a factor of 3.

#### 4 Conclusions and Future Work

The work presented in this paper has shown that RapidMind really offers code portability across various architectures, both multi-core x86 CPUs and accelerators like GPUs or the Cell processor. Using RapidMind for the Euroben kernels has been straightforward: the code development of the first naive implementation took only a few days for each. Adapting the original version to new backends comes practically for free and is a matter of hours and of getting used to the new environments.

However, performance portability differs: code written naturally without a deep understanding of the hardware and RapidMind's internal mode of operation will not deliver optimal performance in most circumstances and hardly exploit the potential of the hardware. For mod2am, the highly optimized cell-version is able to reach 88% of the SDK implementation but will deliver poor performance when used on GPUs. The fastest mod2am implementation using CUDA is three times faster than any RapidMind code. For none of the used benchmarks, RapidMind code was able to fully reach the performance of hardware-specific implementations. This is not a big surprise, since it is one of the drawbacks of the achieved code portability. But it is important to state, that the language design optimally supports the compiler. To efficiently use this information to full capacity requires that many people constantly improve all backends, adapting them to the latest hardware and its accompanying language features.

Recently, RapidMind Inc. has been acquired by Intel. Their product will dissolve in Intel's new language Ct (C for throughput computing) [18]. The basic concepts of both languages have always been very similar. The acquisition has pros and cons: on one hand, it is up to speculations if – or when – Ct will support non-Intel architectures. On the other hand, Intel has much experience with mantaining high-performance compilers and analyzing tools.

Future work will focus on Intel's Ct and other approaches that are able to deliver support for multiple accelerators. This might include OpenCL, the PGI accelerator compiler, hmpp from CAPS and the StarSs concept. Our work will focus on the question of portability, both in terms of source code and in terms of achievable performance. The number of kernels will be increased to get a better coverage of the "Berkeley dwarfs".

#### Acknowledgements

This work was financially supported by the KONWIHR-II project "OMI4papps" and by the PRACE project funded in part by the EU's 7th Framework Programme (FP7/2007-2013) under grant agreement no. RI-211528. We specially thank our colleague Hans Hacker for providing the CUDA ports and performance figures, and JSC and CEA for access to their accelerator systems and support.

#### References

- 1. The Top500 supercomputing sites, http://www.top500.org/

- 2. OpenCL, http://www.khronos.org/opencl/

- 3. PGI Accelerator Compiler, http://www.pgroup.com/resources/accel.htm

- 4. CAPS hmpp workbench, http://www.caps-entreprise.com/hmpp.html

- Planas, J., Badia, R.M., Ayguade, E., Labarta, J.: Hierarchical Task-Based Programming with StarSs. The International Journal of High Performance Computing Applications 23(3), 284–299 (2009)

- 6. Sh project, http://libsh.org/

- Ernst, M., Vogelgsang, C., Greiner, G.: Stack Implementation on Programmable Graphics Hardware. In: VMV 2004, pp. 255–262 (2004)

- McCool, M., Wadleigh, K., Henderson, B., Lin, H.-Y.: Performance evaluation of GPUs using the RapidMind development platform. In: Proceedings of the 2006 ACM/IEEE Conference on Supercomputing (2006)

- 9. Los Alamos Lab: Roadrunner, http://www.lanl.gov/roadrunner/

- 10. The Green500 list of energy efficient supercomputers, http://www.green500.org/

- 11. The Euroben benchmark home page, http://www.euroben.nl/

- 12. Asanovic, K., et al.: The Landscape of Parallel Computing Research: A View from Berkeley (2006),

http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-183.pdf

- Simpson, A., Bull, M., Hill, J.: PRACE Deliverable D6.1 Identification and Categorisation of Applications and Initial Benchmarks Suite, http://www.prace-project.eu/documents/Identification\_and\_

- Categorisation\_of\_Applications\_and\_Initial\_Benchmark\_Suite\_final.pdf

- Cavazzoni, C., Christadler, I., Erbacci, G., Spiga, F.: PRACE Deliverable D6.6 Report on petascale software libraries and programming models (to appear), http://www.prace-project.eu/documents/public-deliverables-1/

- 15. RapidMind developer site, https://developer.rapidmind.com/sample-code/ matrix-multiplication-samples/rm-sgemm-gpu-5938.zip

- 16. Bell, N., Garland, M.: Efficient Sparse Matrix-Vector Multiplication on CUDA, http://www.nvidia.com/object/nvidia\_research\_pub\_001.html

- Jansen, T., von Rymon-Lipinski, B., Hanssen, N., Keeve, E.: Fourier Volume Rendering on the GPU Using a Split-Stream-FFT. In: VMV 2004, pp. 395–403 (2004)

- 18. Intel Ct Technology, http://software.intel.com/en-us/data-parallel/

# A Majority-Based Control Scheme for Way-Adaptable Caches

Masayuki Sato<sup>1</sup>, Ryusuke Egawa<sup>2,3</sup>, Hiroyuki Takizawa<sup>1,3</sup>, and Hiroaki Kobayashi<sup>2,3</sup>

<sup>1</sup> Graduate School of Information Sciences, Tohoku University <sup>2</sup> Cyberscience Center, Tohoku University <sup>3</sup> JST CREST {masayuki@sc.,egawa@,tacky@,koba@}isc.tohoku.ac.jp

Abstract. Considering the trade-off between performance and power consumption has become significantly important in microprocessor design. For this purpose, one promising approach is to employ wayadaptable caches, which adjust the number of cache ways available to a running application based on assessment of its working set size. However, in a very short period, the estimated working set size by cache access locality assessment may become different from that of the overall trend in a long period. Such a locality assessment result will cause excessive adaptation to allocate too many cache ways to a thread and, as a result, deteriorate the energy efficiency of way-adaptable caches. To avoid the excessive adaptation, this paper proposes a majority-based control scheme, in which the number of activated ways is adjusted based on majority voting of locality assessment results of several short sampling periods. By using majority voting, the proposed scheme can make way-adaptable caches less sensitive to the results of the periods including exceptional behaviors. The experimental results indicate that the proposed scheme can reduce the number of activated ways by up to 37% and on average by 9.4%, while maintaining performance compared with a conventional scheme, resulting in reduction of power consumption.

#### 1 Introduction

In the last four decades, a continuous increase in the number of transistors on a chip realizes high-performance microprocessors. However, this advance also induces high energy consumption. Considering the trade-off between performance and energy has become significantly important in modern microprocessor design. Especially, power management of on-chip caches has been attracting attention, because a large on-chip cache is essential to achieve high performance but also increases power consumption.

Among a lot of studies on energy-efficient cache managements, one promising approach is a *way-partitioned cache* [1], in which each way of a set-associative cache is independently managed to find a good trade-off between performance and power consumption. One of such mechanisms called *dynamic cache partitioning mechanisms* for multi-core processors [2], 3], 4] can exclusively allocate ways to

R. Keller et al. (Eds.): Facing the Multicore-Challenge, LNCS 6310, pp. 16–28, 2010.

each thread and avoid *inter-thread kickouts* [5], which cause performance degradation on multi-core processors. Albonesi et al. have discussed the effects of changing the number of ways on the performance and power consumption [6]. *The way-adaptable cache* [7] dynamically allocates an appropriate number of cache ways to each thread, and also inactivates unused cache ways for energy saving. *Power-aware dynamic cache partitioning* [8] was also proposed to achieve both resource partitioning among threads and power management.

In these energy-efficient cache mechanisms, it is important to correctly estimate the amount of the cache resource required by individual threads. Almost all the mechanisms estimate the working set size of a thread by sampling cache accesses in a certain period, and estimate the minimum number of cache ways to keep the performance. As a result, the number of cache ways allocated to each thread is decided so as to provide the cache capacity larger than the working set size. If there are unused cache ways not allocated to any thread, power supply to those ways is cut off to reduce the energy consumption

In this paper, we first discuss estimation accuracy of the cache capacity necessary for a thread. Here, we assume the way-adaptable cache [7] as the cache power management mechanism. Observing the cache access behavior during a certain period, we point out that irregular accesses with a little impact on the overall performance temporarily happen. In addition, if such accesses are included in the statistic data used to estimate the working set size, the required cache capacity is inaccurately estimated, resulting in degradation of energy efficiency.

To solve the problems caused by the sensitiveness to these unexpected and irregular accesses, this paper proposes a new control scheme for the way-adaptable cache. In the scheme, the number of activated ways is decided by the majority voting of working set assessment results of several short sampling periods to eliminate the effect of exceptional cache behavior occurring in a short period. Using the proposed scheme in the way-adaptable cache, the number of ways required by each thread is reduced without performance degradation. Consequently, this will lead to a reduction in power consumption and improvement of energy efficiency of caches.

The rest of this paper is organized as follows. In Section 2, we show the wayadaptable cache mechanism and discuss the effect of exceptional and temporary cache access behavior. In Section 3, we propose a new control scheme for wayadaptable caches based on the discussions in Section 2. In Section 4, the proposed scheme is evaluated with the number of activated ways on the way-adaptable cache. Finally, Section 5 concludes this paper.

#### 2 The Way-Adaptable Cache Mechanism

#### 2.1 Mechanism Overview

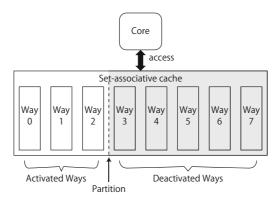

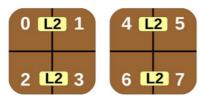

This paper assumes the situation where each thread is executed on the wayadaptable cache mechanism [7] under the single-thread execution environment. Figure [1] shows the basic concept of the way-adaptable cache. The mechanism is designed for a set-associative cache and manages each way individually. The

Fig. 1. Basic concept of the way-adaptable cache (in the case of eight ways)

Fig. 2. Stack Distance Profiling

mechanism estimates the minimum number of required ways to run a thread, allocates them to keep the performance, and inactivates unused ways. When inactivating these ways, the mechanism writes back dirty lines in the ways to the lower-level memory hierarchy. After that, power supply to the ways are disabled by power-gating to reduce power consumption.

Metric for Locality Assessment. To estimate the number of ways required by a thread, a metric is required to judge whether the thread requires more ways or not. The way-adaptable cache mechanism uses *stack distance profiling*  $[\Omega]$  for this purpose. From the profiling result, metric D for locality assessment is calculated.

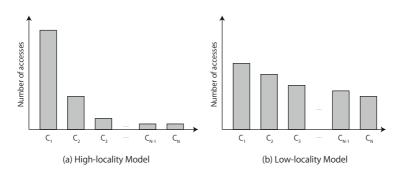

Figure 2 shows two examples of the results of stack distance profiling. Let  $C_1, C_2, ..., C_n$  be N counters for an N-way set-associative cache with the LRU replacement policy.  $C_i$  counts the number of accesses to the *i*-th line in the LRU stack. Therefore, counters  $C_1$  and  $C_n$  are used to count the numbers of accesses to MRU lines and LRU lines, respectively. If a thread has a high locality, cache accesses are concentrated on the MRU lines as shown in Figure 2(a). In this case, the ratio of LRU accesses to MRU accesses becomes lower. However, if

Fig. 3. The 3-bit state machine to decide the way-adaptation

a thread has a low locality, cache accesses are widely distributed from MRU to LRU as shown in Figure 2(b); the ratio of LRU accesses to MRU accesses becomes higher. From the above observations, this ratio, which is defined as D in the following equation, represents the cache access locality of a thread.

$$D = \frac{LRU_{count}}{MRU_{count}}.$$

(1)

A Control Mechanism of the Way-Adaptable Cache. To adjust the number of activated ways to dynamic phase changes of an application, the mechanism samples cache accesses in a certain period, called a *sampling period*. After the sampling period, the mechanism has an opportunity to judge a demand of cache resizing, i.e., changing the number of activated ways. If the mechanism actually judges that resizing is needed, the number of activated ways is changed one by one. We call this opportunity an *adaptation opportunity*. The sampling period and the adaptation opportunity are alternately repeated as the execution proceeds.

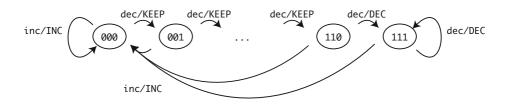

At the adaptation opportunity, the mechanism uses a cache-resizing control signal of a state machine to judge whether the number of activated ways should be changed or not. The state machine records the locality assessment results of the past sampling periods as its state. The locality assessment result of each sampling period is input to the state machine at the following adaptation opportunity. These past results are used for stabilizing the adaptation control.

In the locality assessment of each sampling period, D is compared with thresholds  $t_1, t_2$  ( $t_1 < t_2$ ). If  $D < t_1$ , the mechanism sends a result *dec* to the state machine to suggest decreasing the number of ways. On the other hand, if  $t_2 < D$ , the mechanism sends a result *inc* to suggest increasing the number of ways. If  $t_1 < D < t_2$ , the mechanism sends a result *inc* to suggest increasing the number of suggest keeping the current number of ways.

Figure  $\square$  shows the state transition diagram of the 3-bit state machine used in this mechanism. The state machine changes its state when signal *inc* or *dec* is input. When *inc* is given to the state machine, it outputs the cache up-sizing control signal *INC* and then always transits to State 000 from any state. However, in the case of *dec* given, the machine works conservatively to generate the down-sizing signal *DEC*. Before moving into State 111 for generating the *DEC* signal, the machine transits to intermediate states from 001 to 110 to judge the continuity of the down-sizing requests. During these states, it outputs *KEEP* to keep the current activated ways. After continuing *dec* requests, the machine eventually outputs the *DEC* signal for down-sizing and then transits to State 111. That is, *dec* does not immediately change the number of ways but *inc* does. According to this behavior of the state machine, the mechanism can avoid performance degradation caused by insensitivity to *inc* and frequent changes of the number of activated ways.

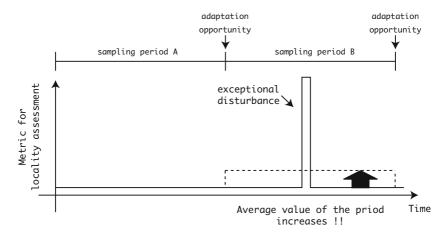

#### 2.2 Exceptional Disturbances of Cache Accesses

We define temporal and exceptional cache behaviors that generate a lot of LRU accesses in a short period as *exceptional disturbances*, which have little impact on the overall performance in thread execution. When exceptional disturbances happen, D becomes large and hence the cache access locality will be judged excessively low, even if the cache access locality is almost always high except the short period of exceptional disturbances, and thus additional ways are not required. Figure  $\square$  shows the examples of two sampling periods. In the figure, the sampling period A does not include exceptional disturbance. Comparing average locality assessment metric D in each period, average D of the period B is obviously larger than that of the period A. In this case, the way-adaptable cache will increase the number of activated ways, even though this does not increase the thread performance but the power consumption.

To reduce the effect of exceptional disturbances, one solution is to increase the interval, because average D of the sampling period B in Figure 4 decreases as the sampling period B becomes longer. However, there are drawbacks of a long sampling period. If the sampling period becomes long, the probability of including multiple exceptional disturbances in one sampling period increases. If multiple exceptional disturbances are in a long period, the effect of reducing average D of a long period gets balanced out, and average D in a long period is eventually comparable to average D in a short period. As a result, the effect of exceptional disturbances in locality assessment at an adaptation opportunity is not reduced even if using a long period, and the number of activated ways cannot be reduced. Moreover, once the number of ways is increased by exceptional disturbances, a long time is required to reduce the number of activated ways because the interval between adaptation opportunities is long. As a result, the number of activated ways is increased because excessive activated ways are maintained for a long time. Consequently, a new technique is required to alleviate the effect of exceptional disturbances, resulting in a reduction in the number of activated ways, while the interval between adaptation opportunities is unchanged.

Fig. 4. Exceptional disturbances and the effect to locality assessment

Fig. 5. Timing chart of the proposed mechanism

### 3 A Majority-Based Control Scheme for Way-Adaptable Caches

In this paper, we focus on the problem that the way-adaptable cache mechanism excessively adapts to exceptional disturbances. To reduce the effect of exceptional disturbances, a majority-based cache-resizing control scheme is proposed in this section. The proposed scheme uses locality assessment results of several short sampling periods in locality assessment between two consecutive adaptation opportunities, in order to reduce the effect of the locality assessment results of sampling periods with exceptional disturbances on the assessment. Using this scheme in the way-adaptable cache, the reduction in the number of activated ways and, as a result, the reduction in power consumption of the cache can be expected without performance loss.

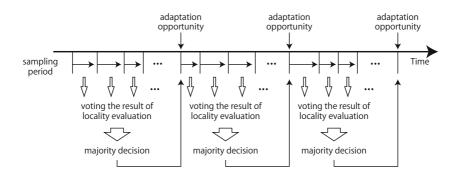

Figure [5] illustrates the relationship between adaptation opportunities and sampling periods in the proposed scheme. The end of each sampling period does not always mean an adaptation opportunity; a sampling period ends at a fixed interval, and then a new sampling period may immediately begin without an adaptation opportunity. At the end of every sampling period, the result of locality assessment of an application in the period, i.e. *inc*, *dec*, or *keep* is decided with Eq. [1] and two thresholds  $(t_1, t_2)$ . If an adaptation opportunity comes during a sampling period, the period is immediately terminated and the locality assessment in the period is performed using the statistic information collected until then.

At an adaptation opportunity, the number of activated ways should be considered based on the series of locality assessment results of several sampling periods. However, to relax the negative effects of exceptional disturbances, the mechanism needs to take account of the results by the sampling periods including exceptional disturbances. If there are fewer periods that produce different results against the other periods, the scheme decides that these periods are affected by exceptional disturbances. On the other hand, if almost all the periods since the last adaptation opportunity produce the same result, the scheme decides that the cache access behavior is stable and consistent, and hence adjust the number of activated ways based on the result.

To realize such a control mechanism, the proposed scheme uses majority voting by the locality assessment results of multiple periods between consecutive adaptation opportunities. In the proposed scheme, each sampling period votes to *inc*, *dec*, or *keep*. The proposed scheme adjusts the number of activated ways based on the majority of votes. If the number of votes to *dec* is equal to that to *inc*, or if that to *keep* is the largest, the mechanism does not change the number of activated ways. On the other hand, if the number of votes to *dec* is larger than those to the others, the mechanism decreases the number of activated ways. Similarly, if the number of votes to *inc* is larger than those to the others, the mechanism increases the number of ways.

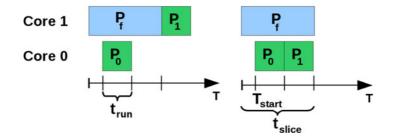

In the proposed scheme, the length of sampling period and the interval between adaptation opportunities are important parameters to appropriately estimate the number of ways. The number of votes available at an adaptation opportunity should be as large as possible to allow the mechanism to correctly identify sampling periods including exceptional disturbances. Hence, the length of sampling period should be as short as possible in terms of the identification accuracy. However, a certain number of accesses are required to obtain the statistically-reliable results to evaluate the locality in a period. In the proposed scheme, *access-based interval* [S] is used for deciding sampling periods, in which the end of a period comes after a certain number of cache accesses. By using this interval, the proposed scheme can ensure that a certain number of sampled accesses are included in one sampling period. In addition, an adaptation opportunity comes at a fixed *time-based interval* [3] to make the adaptation frequency moderate.

| Parameter                              | Value                                   |  |

|----------------------------------------|-----------------------------------------|--|

| fetch, decode, issue, and commit width | 8 instructions                          |  |

| Working frequency                      | 1GHz                                    |  |

| L1 I-Cache                             | 32kB, 4-way, 64B-line, 1 cycle latency  |  |

| L1 D-Cache                             | 32kB, 4-way, 64B-line, 1 cycle latency  |  |

| L2 Cache                               | 1MB, 32-way, 64B-line, 14 cycle latency |  |

| Main Memory                            | 100 cycle latency                       |  |

Table 1. Processor and memory model

#### 4 Evaluations

#### 4.1 Experimental Setup

In this paper, the proposed mechanism is examined in single-thread execution with the way-adaptable cache. We have developed a simulator including the wayadaptable cache based on the M5 simulator 10. Table 1 shows the simulation parameters of a modeled processor and memory hierarchy. The way-adaptable cache mechanism with the proposed control scheme is applied to the L2 cache. We assume a 32-way set-associative cache in our evaluation, because caches with more than 16 ways are employed in some latest industrial microprocessors. For example, AMD Phenom II processor has a 64-way maximum set-associative cache increases with the number of ways.

In the proposed scheme, thresholds  $(t_1, t_2)$  are required as mentioned in Section [2.1] According to the previous work [8],  $(t_1, t_2) = (0.001, 0.005)$  is a finetuned parameter set to maintain performance, and we use these values as the thresholds. Benchmarks examined on the simulator are selected from the SPEC CPU2006 benchmark suite [13]. Each simulation is done by executing first one billion cycles of the simulated processor.

#### 4.2 Deciding the Length of the Periods

As mentioned in Section  $\square$  the number of votes available at one adaptation opportunity should be as large as possible. This means that the sampling period should be as short as possible, because the interval between adaptation opportunities is fixed. However, in terms of the statistic reliability of a vote, the number of cache accesses in a sampling period should be as large as possible. Therefore, we first investigate an appropriate length of a sampling period.

In the preliminary evaluation, we assume that the end of a sampling period and an adaptation opportunity come simultaneously at a fixed number of cache accesses, and hence we use an n-bit saturating counter for counting the number of cache accesses. A sampling period ends when the counter overflows. The purpose of the preliminary evaluation is to find the minimum number of cache accesses that is large enough for locality assessment, and hence to obtain reliable votes as many as possible.

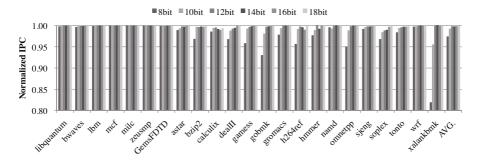

Fig. 6. Effect of sampling period length on performance

Figure **6** shows the evaluation results. In this figure, "8-bit" means that an 8bit counter is used; the end of a sampling period and an adaptation opportunity come at every 256 accesses. These results clearly indicate that the use of 8-bit and 10-bit counters often leads to severe performance degradation. On the other hand, if the number of bits in the counter is 12 or more, the performance does not change significantly. From these observations, 4096 accesses saturating a 12-bit counter are at least required to properly assess the cache access locality. Since a shorter sampling is better to increase the number of votes at an adaptation opportunity, a 12-bit counter is used in the proposed scheme in the following evaluation.

In addition, the interval between adaptation opportunities is set to 5 ms in the following evaluation as with [3]. Specially, an adaptation opportunity comes at every 5 million cycles, because the clock rate of the simulated microprocessor is 1GHz.

#### 4.3 Evaluation Results of the Proposed Scheme

For each benchmark, we evaluated the proposed scheme in terms of performance and the average number of activated ways. In our evaluation, there is no significant difference in performance between the conventional scheme and the proposed scheme. In the following, therefore, this paper discusses only the average number of activated ways of each scheme.

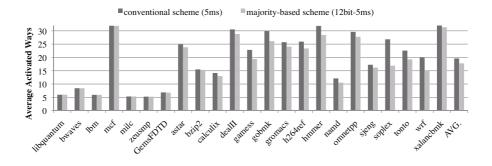

Figure 7 shows the average number of activated ways for each benchmark. In the figure, the "conventional scheme (5 ms)" indicates a original scheme, in which the end of a sampling period and an adaptation opportunity simultaneously come at every 5 ms. The "majority-based scheme (12 bit-5 ms)" indicates our proposed scheme, in which the length of a sampling period is decided with a 12-bit counter, and the interval between consecutive adaptation opportunity is 5 ms. According to Figure 7, the average number of activated ways in the majority-based scheme is 9.4% less than that in the conventional scheme. This indicates that the majority-based scheme can decrease the number of activated ways, and thereby is more effective to reduce the energy consumption with keeping the same performance.

Fig. 7. Average number of activated ways

From the evaluation results, the benchmarks can be classified as follows.

Category I: libquantum. For this benchmark, the average number of activated ways of the majority-based scheme is slightly increased compared to that of the conventional scheme. This benchmark causes redundant activations of the ways in the proposed scheme. In this case, when the number of votes to *keep* in a period is equal to that to *inc*, the locality assessment by the conventional scheme results in *keep* at the following adaptation opportunity. On the other hand, the locality assessment by the majority-based scheme results in *inc*. However, such a case rarely happens and has little effect in evaluated benchmarks through all categories.

Category II: bwaves, 1bm, mcf, milc, and zeusmp. For each benchmark in this category, the average number of activated ways of the majority-based scheme is almost the same as that of the conventional scheme. These benchmarks in this category do not include exceptional disturbances. This is because the number of L2 accesses is very small in these benchmarks. However, in mcf, all the ways are used and hence the average numbers of activated ways are larger than those of the others in this category. Even in mcf, cache access patterns are relatively regular and predictable.

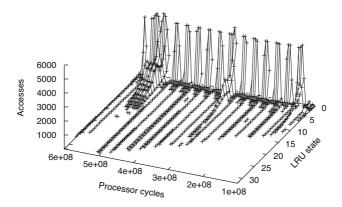

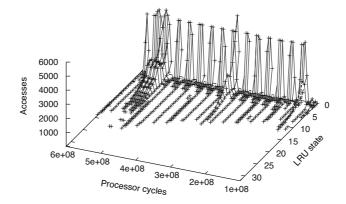

Category III: GemsFDTD, astar, bzip2, calculix, dealII, gamess, gobmk, h264ref, hmmer, namd, omnetpp, sjeng, soplex, tonto, wrf, and xalancbmk. For each benchmark in this category, the average number of activated ways of the majority-based scheme is smaller than that of the conventional scheme. Especially for soplex, the average number of activated ways is reduced by up to 37%. These benchmarks often cause exceptional disturbances because they frequently access the cache. The difference in the number of activated ways indicates that the proposed scheme can properly eliminate the negative effect of exceptional disturbances. Figures S and S show the cache access distributions of wrf with the conventional scheme and the majority-based scheme, respectively. These distributions are observed by stack distance profiling in the same period in cycles of the simulated processor. In this period, exceptional disturbances are clearly observed. In Figure , the number of accesses with high LRU states

Fig. 8. Cache access distribution observed by stack distance profiling (the conventional scheme)

Fig. 9. Cache access distribution observed by stack distance profiling (the majoritybased scheme)

gradually increases as the number of cycles proceeds. This means that the number of activated ways in the conventional scheme also increases due to the exceptional disturbances. However, the majority-based scheme can successfully inhibit the increase as shown in Figure [9]. From the above results, it is obvious that the majority-based scheme is robust to an unstable situation frequently causing exceptional disturbances. The superiority of the majority-based scheme against the conventional one becomes more remarkable in the benchmarks with frequent cache accesses.

Consequently, these results clearly demonstrate that the majority-based scheme can reduce the number of activated ways to achieve the same performance, compared to the conventional scheme with time-based interval. As the number of activated ways is strongly correlated with the static leakage power of the cache, the majority-based scheme will be effective to save the energy consumption. In the future work, we will thoroughly evaluate how much power consumption of the way-adaptable cache is reduced by the majority-based scheme.

## 5 Conclusions

Way-partitioned caches are promising approaches to realize energy-efficient computing on multi-core processors. In these caches, it is important to accurately estimate the number of ways required by a thread, because inaccurate partitioning and adaptation degrade energy efficiency. This paper has discussed the exceptional disturbances of cache accesses and their effects on the locality assessment results used to estimate the number of required ways. To reduce the effects, this paper also proposed a scheme that decides the number of activated ways based on majority voting of the results in several short sampling periods. By using the proposed scheme for the way-adaptable cache, the average number of activated ways is decreased by up to 37%, and 9.4% on an average without performance degradation. From this observation, the way-adaptable cache mechanism with the proposed scheme enables the lower-power and higher-performance execution than that with the conventional scheme. This also indicates that the proposed scheme can estimate the number of ways required for maintaining performance more accurately than the conventional scheme.

In our future work, we will evaluate the power consumption of the wayadaptable cache with the proposed scheme. We will also apply the proposed scheme to estimation the number of ways in other way-partitioned cache mechanisms, and cache-aware thread scheduling **14**.

# Acknowledgement

The authors would like to thank the anonymous reviewers for constructive comments, and also thank all members of our laboratory for valuable discussions. This research was partially supported by Core Research for Evolutional Science and Technology (CREST), Japan Science and Technology Agency (JST).

## References

- Ravindran, R., Chu, M., Mahlke, S.: Compiler-Managed Partitioned Data Caches for Low Power. In: Proc. the 2007 ACM SIGPLAN/SIGBED Conference on Languages, Compilers, and Tools for Embedded Systems, pp. 237–247 (2007)

- Suh, G., Rudolph, L., Devadas, S.: Dynamic Partitioning of Shared Cache Memory. Journal of Supercomputing 28(1), 7–26 (2004)

- Qureshi, M.K., Patt, Y.N.: Utility-Based Cache Partitioning: A Low-Overhead, High-Performance, Runtime Mechanism to Partition Shared Caches. In: Proceedings of 39th Annual IEEE/ACM International Symposium on Microarchitecture, pp. 423–432 (2006)

- Settle, A., Connors, D., Gibert, E., Gonzáles, A.: A Dynamically Reconfigurable Cache for Multithreaded Processors. Journal of Embedded Computing 2(2), 221– 233 (2006)

- 5. Kihm, J., Settle, A., Janiszewski, A., Connors, D.: Understanding the Impact of Inter-Thread Cache Interference on ILP in Modern SMT Processors. The Journal of Instruction-Level Parallelism 7 (2005)

- Albonesi, D.H.: Selective Cache Ways: On-Demand Cache Resource Allocation. In: Proceedings of 32nd Annual International Symposium on Microarchitecture, pp. 248–259 (1999)

- Kobayashi, H., Kotera, I., Takizawa, H.: Locality Analysis to Control Dynamically Way-Adaptable Caches. ACM SIGARCH Computer Architecture News 33(3), 25– 32 (2005)

- Kotera, I., Abe, K., Egawa, R., Takizawa, H., Kobayashi, H.: Power-Aware Dynamic Cache Partitioning for CMPs. Transaction on High-Performance Embedded Architectures and Compilers 3(2), 149–167 (2008)

- Chandra, D., Guo, F., Kim, S., Solihin, Y.: Predicting Inter-Thread Cache Contention on a Chip Multi-Processor Architecture. In: Proceedings of the 11th International Symposium on High-Performance Computer Architecture, pp. 340–351 (2005)

- Binkert, N.L., Dreslinski, R.G., Hsu, L.R., Lim, K.T., Saidi, A.G., Reinhardt, S.K.: The M5 Simulator: Modeling Networked Systems. IEEE Micro 26(4), 52–60 (2006)

- 11. AMD: Family 10h AMD Phenom II Processor Product Data Sheet. Technical Documents of Advanced Micro Devices (June 2009)

- Yang, S.H., Powell, M.D., Falsafi, B., Vijaykumar, T.N.: Exploiting choice in resizable cache design to optimize deep-submicron processor energy-delay. In: Proceedings of The Eighth International Symposium on High-Performance Computer Architecture (2002)

- Henning, J.L.: SPEC CPU2006 Benchmark Descriptions. ACM SIGARCH Computer Architecture News 34(4), 1–17 (2006)

- Sato, M., Kotera, I., Egawa, R., Takizawa, H., Kobayashi, H.: A Cache-Aware Thread Scheduling Policy for Multi-Core Processors. In: Proceedings of the IASTED International Conference on Parallel and Distributed Computing and Networks, pp. 109–114 (2009)

# Improved Scalability by Using Hardware-Aware Thread Affinities

Sven Mallach<sup>1</sup> and Carsten Gutwenger<sup>2</sup>

$^{1}\,$ Universität zu Köln, Germany $^{2}\,$  Technische Universität Dortmund, Germany

Abstract. The complexity of an efficient thread management steadily rises with the number of processor cores and heterogeneities in the design of system architectures, e.g., the topologies of execution units and the memory architecture. In this paper, we show that using information about the system topology combined with a hardware-aware thread management is worthwhile. We present such a hardware-aware approach that utilizes thread affinity to automatically steer the mapping of threads to cores and experimentally analyze its performance. Our experiments show that we can achieve significantly better scalability and runtime stability compared to the ordinary dispatching of threads provided by the operating system.

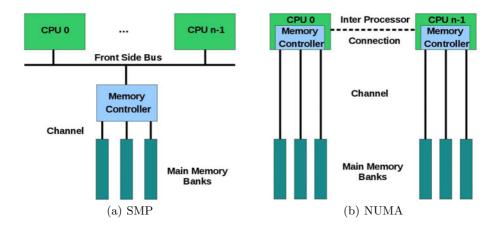

## 1 Introduction

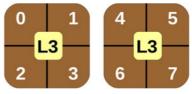

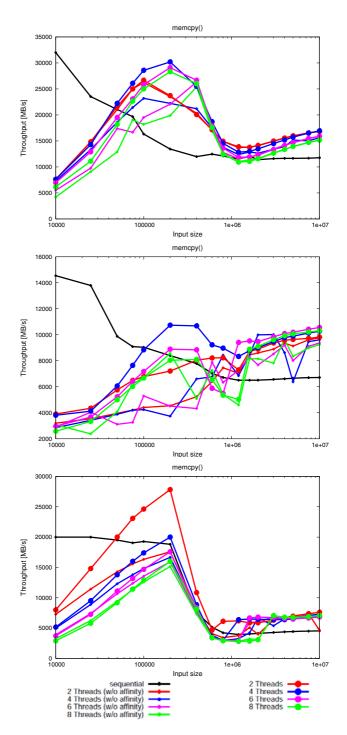

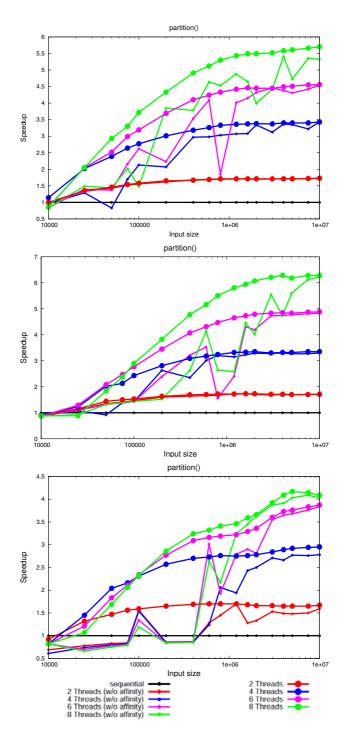

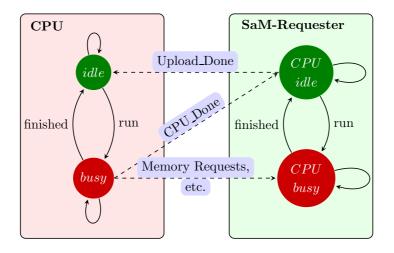

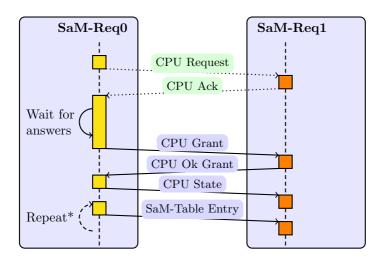

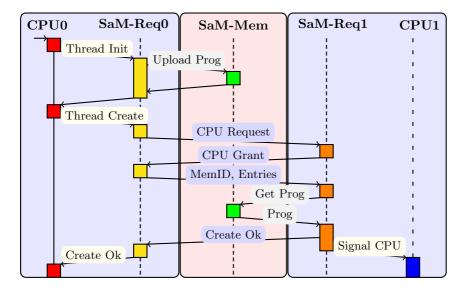

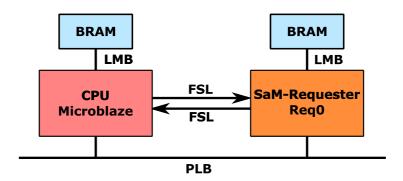

Today, multicore processors have become an ultimate commodity in private and scientific computing allowing multiple levels of parallelism. Namely one can achieve parallelism by superscalarity, SIMD instructions, multiple cores, and simultaneous multithreading using only a single processor. Under these conditions cache/memory considerations become more complex and, when combining two or more processors within one system, complexity rises extremely if an implementation shall scale on different architectures.