# 2 State-of-the-Art on Analog Design Automation

**Abstract.** This chapter presents the State-of-the-Art (SOA) in analog circuit design automation. First, the analog design flow is reviewed and the fundamental trends in design automation are discussed. Then, the existing approaches to circuit sizing are presented, outlining in each case their advantages and limitations. Next, a detailed discussion over the existing tools approaches is provided. Finally, conclusions concerning the specification and design of a new analog design automation methodology implementation will be drawn.

## 2.1 Trends in Design Automation Methodology

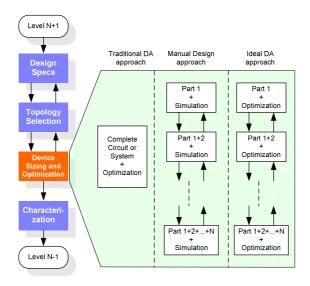

A typical design flow for *analog and mixed-signal* IC circuits (AMS) consists of a series of design steps repeated from the system level to the device-level, and bottom-up for layout generation and verification. The steps between any two of these hierarchical levels are: topology selection, circuit sizing, design verification and layout generation task, illustrated in Fig. 2.1.

Fig. 2.1 Hierarchical level and design tasks of design flow architectures [1]

M.F.M. Barros et al.: Analog Circuits and Systems Optimization, SCI 294, pp. 19–47. springerlink.com © Springer-Verlag Berlin Heidelberg 2010 In order to handle the increasing complexity of analog and mixed-signal IC design, a clear definition of a hierarchical design flow is essential. Despite the advances made during the last decades, the *design automation* (DA) tools in analog domain cannot support the complete design process, since they either concentrate on specific parts of the design flow or require the intervention of an expert designer. Moreover, they mainly address circuit level design as a whole (traditional design approach), which makes it difficult to apply to highly complex circuits and systems. Therefore, as the SoC complexity increases, the design automation tools must incorporate an hierarchical design decomposition feature in order to apply the well-known divide-to-conquer strategy already applied by most analog designers in a manual design approach.

Trends in this area have been running towards a class of design automation methodology under three aspects, improving:

- Flexibility, allowing the designer to have a higher interaction during the synthesis process and providing a more general approach to deal with multiple architectures or circuit types.

- Modularity, allowing the use of different tools and techniques to address different design tasks, such as topology selection, circuit sizing and layout.

- Hierarchy, allowing the handling of complex system designs and implementing strategies involving several abstraction levels.

## 2.1.1 Automated Topology Selection

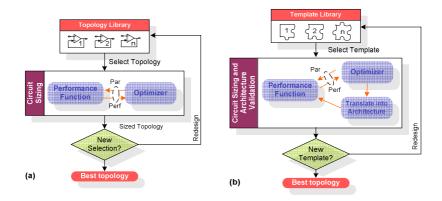

The selection of an adequate architecture is fundamental to achieve a high performance design [2]. The topology selection task receives the performance specifications, for a particular class of circuits or systems, and delivers the most promising topology, traditionally from a predefined library. In IDAC [3] the decision is taken directly by the designer. *Heuristic rules* [4] have been used in the first attempts by TAGUS [5]-[6], OASYS [7], BLADES [8], and OPASYN [9] to automate the topology selection task. The tool FASY [10] uses fuzzy-logic based reasoning to select one topology among a fixed set of alternatives. The decision rules are introduced by an expert designer or automatically generated by means of a learning process. Another method comprises computing the feasible performance space for each topology within the library and, then compare with the desired performance specs, by AMGIE [2] and [11]. A different method consists of combining the topology selection with the device sizing task and employing an optimization based approach by DARWIN [12] using genetic algorithms. This design mechanism illustrated in Fig. 2.2, uses a template rather than an architecture library. This template specifies the topology in terms of blocks, each one with possible different alternatives. In short, this last method is more reliable since it treats the problem in a more deterministic way and at the same time decreases the setup time, as it does not need to rearrange a new set of rules each time a new topology is added to the library; the computation time, however, is worse than in all methods described above.

A new step towards the increase of the automation level is given by a new set of tools where topology selection is performed at a higher abstraction level. Instead of selecting the architecture from a library, a high level functionality of the system is defined now by a *hardware description language*. Then, an automatic translation is carried out, mapping the functional description into an internal representation and then into a specific topology. The mapping step is implemented after or during the device sizing process. This class of tools usually differs from the type of internal representation used. In the case of [13] the internal representation is a data flow graph, whereas in TAGUS [5]-[6], [14] and Konczykowska [15] it is a *symbolic signal flow graph* and in ARCHGEN [16] a *state-space description* is used. Then, a mapping operation is performed, resulting in a connection of lower-level building blocks whose parameters are optimized, obeying to some design constraints. The operation flow is executed in a top-down basis.

Fig. 2.2 Topology selection mechanism before (a) and during (b) device sizing

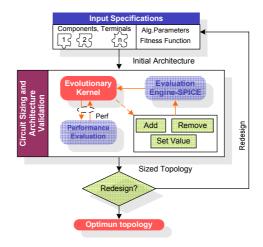

Finally, a design methodology able to create new topologies explores the immense potential from low abstraction level. Small elementary blocks are connected bottom-up to each other to form a new topology. The general description of this design methodology illustrated in Fig. 2.3 begins by selecting an initial topology, having in mind the desired specifications. As the design process takes place, an optimizer selects a transformation, adding or deleting a basic entity and/or attributing a value to a parameter. Various fundamental entities can be applied, such as, single transistors, elementary building blocks or node connections. As soon as the architecture is generated, the performance function is evaluated, providing some hints to the optimizer who makes a new selection of transformation. Essentially two exploration methods can be applied in topology generation for analog design. The knowledge-based exploration is based on a systematic or a random strategy where the circuit elements can be added, replaced or removed by an experienced designer with the help of standard CAD tools, like SPICE, and a circuit schematic editor. This method mimics the daily basis design approach supported mainly by simulation tools, and, therefore, suffers from the same drawbacks, i.e., as the number of entities in the system rise, the computational time increases accordingly. The computation time at the circuit description level can become intolerable if no efficient guidance is provided during the exploration step.

Fig. 2.3 A general description of the topology selection bottom-up methodology

New automation tools appeared, based on stochastic evolutionary computation methods, which apply an appropriate representation for standard circuit-level descriptions and recombination operations. Population-based optimizers provide multiple dimensioned architectures which are then simulated by SPICE-like simulators. In [17] the optimizer is based on a genetic algorithm and in [18]-[19] uses genetic programming techniques. Table 2.1 summarizes the general characteristics of automated topology selection and generation mechanisms.

Table 2.1 General characteristics of automated topology selection and generation

|           | Topology Selec                                                                                                                                                                                                     | tion                                           | Topology Generation                                            |                                                                                                                                                             |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | Heuristic Rules                                                                                                                                                                                                    | Feasible Region                                | Top-down*                                                      | Bottom-up                                                                                                                                                   |  |

| Too       | BLADES [8], OPASYN [9]                                                                                                                                                                                             | AMGIE [11], and<br>Gielen [2],<br>DARWIN [12]  | Graeb [13],<br>TAGUS[5]-[6],<br>[14], Konc-<br>zykowska [15]   | Colombano[17], Koza[18],<br>Toumazou [19]                                                                                                                   |  |

| Drawbacks | <ul> <li>(-) Large set up time in order<br/>to update the selection rules to<br/>a new topology.</li> <li>(-) Qualitative approach and<br/>sometimes extremely difficult<br/>to codify heuristic rules.</li> </ul> | (-) Time<br>consumption                        |                                                                | <ul> <li>(-) Large time consumption.</li> <li>(-) No technological param.</li> <li>(-) No corner validation.</li> <li>(-) Not in a mature state.</li> </ul> |  |

| Advant.   | (+) Reduced execution time.                                                                                                                                                                                        | (+) Quantitative<br>and general ap-<br>proach. | (+) Reduced exe-<br>cution time and<br>well defined<br>process | <ul><li>(+) Extremely promising.</li><li>(+) Generic Approach.</li><li>(+) No expert knowledge.</li></ul>                                                   |  |

\* Properties depend on methodology. This column considers knowledge-based approach.

#### 2.1.2 Automated Circuit Sizing/Optimization

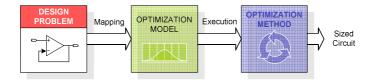

The sizing stage receives a topology description, a set of performance specs and a technology reference and, based on these inputs, produces a sizing solution for each block or component depending on the abstraction level. Several solutions were proposed derived from either knowledge-based methods, using some kind of knowledge and heuristics, or optimization-based approaches for both topology selection and specification translation or circuit sizing [1],[20]. The knowledge-based approach requires the expert knowledge of a designer to produce a set of rules and equations for every new circuit topology or technology. Another alternative is obtained considering the circuit sizing as an optimization problem. In these approaches the design problem is first mapped or modeled into an optimization problem and then solved by an appropriate optimization method, as illustrated in Fig. 2.4.

Fig. 2.4 Steps in optimization of circuit design

In this approach, there is a strong correlation between the modeling of a design problem and the way the modeled problem is solved. Since these steps are not independent and have influence on each other, the optimization method will be decided by the chosen model of the problem. For example, if the design problem is formulated in a set of *posynomial* equations the optimization method candidate could be the *geometric programming* (GP) algorithm or other computation algorithm able to process the convex optimization problem defined by posynomial equations [21]. If the design problem is formulated by SPICE models, a simulated annealing or a stochastic pattern algorithm could be used instead. Section 2.2 will explore the main optimization methods and alternative models in the area of analog IC design problems.

#### 2.1.3 Automated Layout Generation

The earliest approaches to automate the layout generation followed a *procedural module generation* [22]-[23] with the codification of the entire circuit layout and its generation during the run time for the parameters attained during the sizing task. The procedural generators define a parametric representation of the geometric layout developed by the designer, accomplished either through a procedural

language or a graphical user interface. The disadvantages of this approach are the lack of flexibility and generality and the high cost of the generation task.

Next, a *template-based approach* was developed [24] allowing the employment of geometric templates, which define the relative position and interconnection of devices. The templates are used to incorporate the designer knowledge into the optimization task. In spite of the low level of reusability achieved by procedural generators, the efficiency of this approach can be improved when user-defined templates are designed to be independent of both technology and specifications [4]. This approach is also suited when modifications in circuit parameters end in small adjustments to the global circuit layout structure, like technology migrations.

Later on the optimization-based approaches emerged, using optimization techniques to determine and predefine the layout solution. Small database of procedural cell generators, ANAGRAM [25]-[26], LAYLA [27] and ALDAC [28] synthesize an optimized layout configuration, searching the solution space formed by each cell layout positioning. The ALG [29] approach allows the generation of "optimal layout" of a circuit either automatically or by designer directives. On one hand these approaches require more computation time, but, on the other hand, they are more flexible and general, which compensates largely the weakness mentioned above. Significant technological solutions have resulted from this method [30]-[33], ranging from rule driven to performance driven layout generation tasks [27], reaching a more mature state when compared to what happens in the design automation tasks concerning circuit sizing [1]. The most frequent used optimization techniques in analog IC layout generation tools are simulated-annealing (ILAC [34], KOAN [25]-[26] and LAYLA [27]) and genetic algorithms (LAYGEN [35]-[36]). Simulated-annealing based approaches attained better results but lately the evolutionary approach has become a common option in many situations, like the hybrid solution defined by the genetic approach to simulated-annealing GASA [37] or the combined GA and Tabu Search (TS) used in [38] to develop a polycell placement algorithm for analog LSI chips. As both KOAN and LAYLA employ very simple cells on the database, some highly efficient structures, such as stacked or interdigited transistors, cannot be generated. Recent approaches, however, are tending to hybrid solutions employing optimization on blocks derived from knowledge-based systems. In the case of ALADIN [37], [39], the database usually relies on a hierarchical model where a cell is built using already defined cells. The use of compound cells reduces the search space because the number of cells handled during placement is lower and consequently reduces the computation times. Another knowledge-based approach with optimization is given by IPRAIL [40] and LAYGEN [35]-[36] in which the information presented in the template is defined manually or automatically and used to guide the layout generator during the synthesis procedure. The constraints defined in the template reduce the solution space, and allow the designer a higher control of the layout generation unlike the general optimization approaches [35]. Table 2.2 resumes the general characteristics of layout tools.

| Tool                                                                                   | Year  | Description                                                                                                                                                                                                                                                                                                              | Techniques                                                                                                                | Obs.                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KOAN/ANAGRAM<br>[25],[26]                                                              | [1991 | Macro-cell Place and Route; uses<br>pre-defined small module genera-<br>tors data-base; synthesizes an op-<br>timized layout configuration from<br>a given Spice netlist with symme-<br>try, matching and tech. specs.                                                                                                   | Optimization<br>based with Simu<br>lated Annealing.                                                                       | The chosen library<br>constitutes a limit of<br>this method since an<br>enormous number of<br>pre-designed layout<br>blocks is required                                                      |

| Layla<br>[27]                                                                          | 1995  | It takes into account symmetry<br>constraints, performance degrada-<br>tion due to interconnect parasitics<br>and device mismatches and com-<br>bines this with geometrical opti-<br>mization techniques (devices<br>merges, abutment, etc.)                                                                             | Optimization<br>based with Simu-<br>lated Annealing.                                                                      | A performance-<br>driven methodology<br>where all perform-<br>ance constraints are<br>satisfied. Optimize<br>the layout quantifying<br>the performance deg-<br>radation.                     |

| A SKILLTM-based<br>Library for Retarge-<br>table Embedded<br>Analog Cores<br>[32]-[33] | 2001  | Automatic generation and reus-<br>ability of physical layouts of ana-<br>log and nixed-signal blocks based<br>on high-functionality pCells that<br>are fully independent of technolo-<br>gies.                                                                                                                           | Knowledge-based                                                                                                           | Parameterized cells<br>(pCells) are organ-<br>ized hierarchically.                                                                                                                           |

| ALDAC<br>[28]                                                                          | 2002  | This tool providing means to gen-<br>erate multiple versions of full-<br>stacked layout modules for the<br>same circuit. The differences<br>come from different MOS transis-<br>tor splitting and grouping into<br>stacks that can be performed ei-<br>ther fully-automatically or user-<br>controlled                   | Simulated<br>Annealing                                                                                                    | This approach mini-<br>mizes parasitic diffu-<br>sion capacitances of<br>the circuit and per-<br>mits economical post-<br>layout simulation of<br>multiple layouts for<br>performance-driven |

| IPRAIL<br>[40]                                                                         | 2004  | Retargeting is achieved using an<br>automatically extracted template<br>and using a circuit optimizer to<br>size the cells. It uses either a rule<br>or a performance driven approach.<br>It uses optimization based with<br>knowledge-based.                                                                            | Linear Program-<br>ming and graph<br>short path on the<br>relational tem-<br>plate extracted<br>from the source<br>layout | <ul><li>(+) General approach.</li><li>(-) Larger run-time required.</li></ul>                                                                                                                |

| ALADIN<br>[25],[32]                                                                    | 2004  | The layout generation is based on<br>relatively complex sub-circuits.<br>Designers can construct layouts of<br>parameterizable modules in a<br>technological and application in-<br>dependent way. The placement<br>and routing of modules are per-<br>formed automatically under the<br>constraints defined by designer |                                                                                                                           | Design platform for<br>analog circuits, based<br>on a user managed<br>device generators li-<br>brary.                                                                                        |

| Tool             | Year | Description                                                                                                                                                                                                                                                                                                                                                                                                                 | Techniques                                                                                                    | Obs.                                                                                                                                                                                                 |

|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAYGEN [35],[36] | 2007 | Expert knowledge is used to<br>guide an evolutionary algo-<br>rithm during the automatic<br>generation of the layout The<br>designer provides a high level<br>layout description where posi-<br>tion and interconnections are<br>predefined. This template con-<br>tains placement and routing<br>constrains and is independent<br>from technology. It deals with<br>hierarchically templates for<br>more complex circuits. | 1                                                                                                             | <ul> <li>(+) Speeds up retargeting operations or technology migration</li> <li>(-) Works better when changes in circuit parameters result in small adjustments. for the target technology</li> </ul> |

| ALG [29]         | 2007 | ALG is composed by three<br>functional blocks: module<br>generator, placer and router<br>offering performance oriented<br>layout generation in some of<br>these blocks.                                                                                                                                                                                                                                                     | Cost function is<br>a weighted sum<br>function para-<br>sitics level, as-<br>pect ratio and<br>mismatch, etc. | The user may<br>choose the level of<br>automation between<br>full automation and<br>user control.                                                                                                    |

#### Table 2.2 (continued)

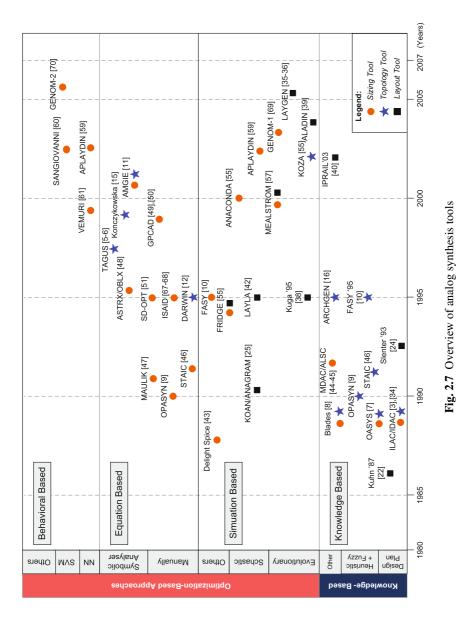

# 2.2 Automated Circuit Synthesis Approaches

The computer-aided design methodology for AMS circuits foresees in a short-run the use of design automation tools to accomplish several tasks of the design methodology [41]. This trend began in 80's when the first automation tools applied to different tasks of analog design appeared like LAYLA [42], IDAC [3],[22], DELIGHT.SPICE [43], BLADES [8] and OASYS [7]. The following sections review some of the most significant approaches for analog IC design including the knowledge-based, optimization-based approaches as well as the first commercial tools.

## 2.2.1 Knowledge-Based Approach

The knowledge-based approach presented, for instance, in programs like BLADES [8], IDAC [3], OASYS [7] and MDAC/ALSC [44]-[45], was the first to appear and is characterized by including a complete design plan describing how the circuit components must be sized to reach the solution for the design problem, even though, there is no guarantee of finding the optimum solution [2]. For example, the IDAC tool [3] takes advantage of the designer experience to manually derive or rearrange design plans to carry out the circuit sizing. OASYS [7] was built

over a library of design plans defined for each elementary building block allowing the hierarchical representation of topologies, defined as the interconnection of several elementary building blocks. This system also implements a back tracking mechanism in order to recover from a malfunction implementation. The Fig. 2.5 illustrates the general design flow of knowledge-based approach.

Fig. 2.5 Knowledge-based approach

In these methods, the main purpose is to encapsulate the designer's knowledge, building a pre-design plan with design equations and a design strategy that produce the component sizes in order to meet the performance requirements. This approach presents as major drawbacks the large overhead required to define a new design plan, the reformulation of the entire design plan when expanding the system to new topologies, and, finally, the migration to other technologies. Not only, it is a very time-consuming process to encode design knowledge for a given set of specifications, but design knowledge also has a limited lifetime. The rapid progress in process technologies made the acquired knowledge quickly out-of-date. Therefore, the application of these tools in industrial environments has been limited. However, after defining the design plan, the execution speed associated to the sizing procedure is extremely fast and the solution quality only depends on the models precision [1]. Naturally, this approach finds its applications restricted to small circuits or to more complex circuits but using simplified equations with the goal of achieving the first cut design.

### 2.2.2 Optimization-Based Approach

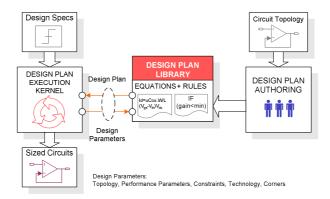

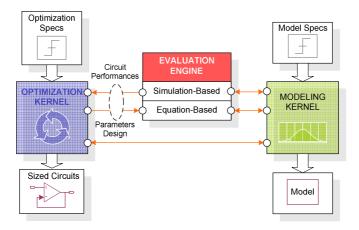

The optimization-based approach uses an optimization engine instead of a design plan to perform the design task. The optimization process is an iterative procedure where design variables are updated at each iteration until they achieve an equilibrium point. The optimization-based approaches illustrated in Fig. 2.6, consist of an iterative loop, including an optimization engine or kernel together with an evaluation engine.

Fig. 2.6 Optimization-based approach

The optimization algorithm searches through the design space for values for each circuit component, whereas the performance evaluation tool verifies if the erformance constraints are met. If the system requirements are satisfied, then a solution is found and the component sizes are associated to the selected topology. The optimization engine should apply the appropriate techniques to efficiently guide the search mechanism in order to minimize the number of iterations required for the optimization process.

Different approaches can be described depending on the type of performance evaluation and the optimization technique employed. Concerning performance, the evaluation engine is typically implemented using an equation-based optimization, a simulation-based optimization or modeling-based optimization approach.

#### 2.2.2.1 Equation-Based Methods

The equation-based methods use analytic design equations to evaluate the circuit performance. These equations can be derived manually or automatically by symbolic analysis tools. Then, the problem can be formulated as an optimization problem and normally solved using a numerical algorithm. Some of the most relevant approaches are OPASYN [9], STAIC [46], MAULIK [47], ASTRX/OBLX [48], AMGIE [11], GPCAD [49][50], SD-OPT [51]. This approach presents the advantage of allowing a performance evaluation speed-up (short evaluation time). The main drawback is that analytical models have to be used to derive the design

equations for each new topology and, despite recent advances in symbolic circuit analysis [52]-[53], not all design characteristics can be easily captured by analytic equations. The approximations introduced in the analytic equations yields low accuracy designs especially in complex circuit's designs.

A promising methodology that has received much attention is related to circuit problems formulated in *posynomial form* (expression 2.1) and seen in tools like GPCAD and [21], [54]. This methodology solves the convex formulated problem by *geometric programming* techniques in a very short time. These techniques take advantage of the development of extremely powerful interiorpoint methods for general convex optimization problems [21],[50]. Besides the extreme efficiency of these methods they have another great advantage, as the global solution is always found, regardless of the starting point. However, a significant drawback still exists due to the difficulty to reformulate high-accuracy device models as posynomials equations, "performance specifications, and objectives that can be handled are far more restricted than any of the methods described above" [50]. Despite the progress presented in [54] the lack of an automated scheme to generate these equations limit the usage of this tool to a few, predefined, circuit structures.

$$f(x_1, \dots, x_n) = \sum_{k=1}^{t} c_k x_1^{\alpha_{1k}} x_2^{\alpha_{2k}} \cdots x_n^{\alpha_{nk}}$$

where,  $c_i \ge 0$  and  $\alpha_{ii} \in \Re$  (2.1)

#### 2.2.2.2 Simulation-Based Methods

The simulation-based approaches such as DELIGHT.SPICE [43], FRIDGE [55], FASY [10], ANACONDA [56], MAELSTROM [57] and DARWIN [12] consist of using some form of simulation to evaluate the circuit's performance. In general, these types of tools for analog circuits design employ a circuit analysis tool in the inner loop of the optimization cycle to determine the circuit's performance. This is pointed out as a very flexible solution when compared with other methodologies (equation-based, knowledge-based) once it accommodates to any type of circuit topology and yields superior accuracy (depends on simulator models). Presently, the use of SPICE-like simulators are almost generalized and essential to support the optimization engine with all the feedback related to an accurate circuit evaluation, involving different performance characteristics, technological parameters and worst case corners analysis. Moreover, within this approach the same circuit can be optimized several times for different specs as long as the goal function is adapted, therefore, with this approach virtually all types of circuits can be sized and optimized with low setup time.

Despite these advantages, automated circuit sizing is not as commonly used as for example, circuit simulation, since it is computationally too expensive to evaluate electrical simulations. However, with the exponential increase of computer power and efficient use of optimization algorithms it has become increasingly favorable. Nevertheless, a key difficulty is that the analog design problem, with all the involved design knowledge and heuristics, has to be formulated as an optimization problem, which often presents a high threshold for using a circuit-sizing tool.

#### 2.2.2.3 Learning-Based Methods

A step forward to enhance the efficiency of optimization based methods corresponds to the introduction of modeling techniques [58] based in *learning strategies*, which are clearly more time-efficient, during the optimization cycle. In this class of methods, the behavior of the circuit to be optimized is modeled by a learning mechanism based on the distribution of variation parameters, thus allowing a quick evaluation of the performance for a specific set of design parameters. Nevertheless, these methods require a set of training samples in order to build the model in the target region. Generally, a high accuracy evaluation engine is used, such as a circuit simulator to evaluate the performance of the training sample. The amount of the training data will influence the accuracy of the performance predictions made by the learning machine. However, an increase on the training data means that the evaluation of the performance will take more time. Like in equation-based methods, there will always be a trade-off between accuracy and efficiency.

Some of the most significant behavioral-based methodologies are described by Rutenbar [58], Alpaydin [59], Vincentelli [60] and Vemuri [61]. In the basis of Alpaydin tool is a neural-fuzzy model approach combined with an evolutionary optimization strategy and simulated annealing where some of the AC performance metrics are computed using an equation-based approach.

In [60] Sangiovanni-Vincentelli and al. use a learning tool based in support vectors machines (SVM) to represent the performance space of analog circuits. Based on the knowledge acquired from a training set, the performance space is modeled as mathematical relations translating the analog functionality. In this work two classes of SVM are confronted in an optimization-less strategy where additionally two improvements of the basic one-class SVM performances, conformal mapping and active learning, are proposed by enhancing the resolution in the support region boundaries. SVMs are trained with simulation data, and false positives are controlled based on a randomized testing procedure.

The Vemuri approach [61] presents a performance macro-model for use in the synthesis of analog circuits based in a neural network approach. On the basis of this mathematical model is a neural network model approach that, once constructed, may be used as substitute for full SPICE simulation, in order to obtain an efficient computation of performance parameter estimates. The training and validation data set is constructed with discrete points sampling over the design space. The work explores several sampling methodologies to adaptively improve model

quality and applies a sizing rules methodology in order to reduce the design space and ensure the correct operation of analog circuits.

#### 2.2.3 Commercial Tools

Besides the efforts introduced above some commercial EDA tools for circuit sizing have emerged in the past few years, such as the ADA's [63] Genius product line now integrated in Synopsis, Barcelona Design [49] which employ convex optimization techniques and recently the NeoCircuit from Neolinear Inc. [62], which implements a simulation-based approach.

The ADA (Analog Design Automation) Genius line of optimization tools, including Creative Genius, which automates device sizing and biasing to optimize circuit performance, and IP Explorer, which graphically provides N-dimensional circuit performance tradeoffs, were recently acquired [63] and integrated within the analog design environment from Synopsys [62], Mentor Graphics and other EDA vendors. The Genius tool builds its database of circuit from a transistor-level netlist, testbenches, objectives, process and environmental variations and variables. This system is comparable to NeoCircuit once it implements a simulation-based approach and interfaces with several industrial circuit simulators using parallel computation architecture.

The now extinct Barcelona Design was founded in 1999 by Stanford University researchers that apply advanced optimization techniques based in convex optimization to develop optimization solutions for a broad spectrum of circuit design problems including analog, RF and digital circuits. The final product introduces the synthesizable IP (intellectual property) block, which contains the required design equations written as posynomial expressions. The particularity of these products is that in opposition to standard IP blocks, which meet the given specifications, these blocks, may be synthesized to meet a range of different specifications. This implementation was reported to be able to increase design speed by 100 times and reduce total design costs by up to 50%.

The Neolinear package, now acquired by CADENCE [65], is composed by the NeoCircuit package, a simulation-based analog circuit sizing engine and the Neo-Cell module to automate the layout generation process. Both design packages to-gether with the optimization engine based on a "genetic annealing" scheme creates a complete analog design flow. The integration of Neolinear's products in the Virtuoso design environment takes advantages of Cadence's multi-mode simulation and extensive layout design capabilities.

### 2.3 Design Automation Tools: Comparative Analysis

The existing design automation approaches are here compared, taking into account some qualitative and quantitative measures described in subsection 2.3.1. Table 2.3 presents the analog sizing tools used in this study and the conclusions are presented in the following subsections.

|                                 | ary<br>tics                                                                                                      | ry.                                                                                       | s                                                                                                           | est to                                                                                                                                                                                                            |

|---------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Properties                      | a libr<br>hema<br>n of<br>and<br>ock                                                                             | ithms<br>ith<br>ith                                                                       | on,<br>esign<br>out<br>irface                                                                               | le and<br>ttegy 1<br>if-the<br>nility 1<br>vuit<br>trate t<br>rrate t<br>oke<br>lator                                                                                                                             |

| and Parti-<br>cular             | size<br>og sc<br>nctior<br>logy a<br>ig-blo                                                                      | large<br>algor<br>ms w<br>tor<br>gence                                                    | task<br>positi<br>fies de<br>Find e<br>e and<br>ble su                                                      | divid<br>ar stra<br>on blo<br>on blo<br>s". At<br>s". At<br>ar circ<br>di circ<br>on circ<br>di nv<br>di nv<br>simu<br>aticall                                                                                    |

| 29863n6VbA                      | Able to size a library<br>of analog schematics<br>as a function of<br>technology and<br>building-block<br>specs. | Uses a large library<br>of opt. algorithms.<br>Problems with<br>simulator<br>convergence. | Apply task<br>decomposition,<br>simplifies design<br>reuse. Find out<br>feasible and<br>infeasible surfaces | Uses a divide and<br>conquer strategy to<br>partition blocks<br>written by "if-then<br>clauses". Ability to<br>perform circuit<br>design, generate test<br>files and invoke<br>circuit simulator<br>automatically |

| Encapsula-<br>tion              | tion Encapsu                                                                                                     |                                                                                           |                                                                                                             |                                                                                                                                                                                                                   |

| Bookkeeping                     |                                                                                                                  |                                                                                           |                                                                                                             |                                                                                                                                                                                                                   |

| Interactive<br>Design           |                                                                                                                  |                                                                                           |                                                                                                             |                                                                                                                                                                                                                   |

| qutə2<br>9miT                   | Long time to<br>add a new cir-<br>cuit (months).<br>Employs worst-<br>case design.                               | Moderate<br>setup                                                                         | Long setup<br>time (approx. 6<br>months),<br>including<br>circuit analysis                                  | Long time to<br>create and<br>maintain look-<br>up tables.                                                                                                                                                        |

| Computa-<br>tion Time<br>Effort | A few seconds<br>(VAX780)                                                                                        | MC 500) setup                                                                             | 3 sec.<br>(VAXstation II/ months),<br>GPX) including<br>circuit an                                          | A few seconds<br>to design and<br>20 min to<br>complete<br>simulation                                                                                                                                             |

| Circuit<br>Complexity           | 5-20<br>devices (                                                                                                | 20 Par.<br>28<br>devices                                                                  | 19 Par.<br>17<br>devices<br>OpAmp                                                                           | 34 th<br>devices 22<br>OpAmp 6                                                                                                                                                                                    |

| Robust<br>Besign                |                                                                                                                  | >                                                                                         | >                                                                                                           |                                                                                                                                                                                                                   |

| .nəməlqml<br>9gsugns.J          |                                                                                                                  |                                                                                           |                                                                                                             |                                                                                                                                                                                                                   |

| Design<br>Ann                   | olic<br>cer +<br>ally                                                                                            |                                                                                           | ally<br>becific<br>h                                                                                        | ally                                                                                                                                                                                                              |

| \ nottenpA                      | Symbolic<br>analyzer +<br>manually                                                                               |                                                                                           | Manually<br>and specil<br>to each<br>class                                                                  | Manually                                                                                                                                                                                                          |

| mdiroglA<br>29upində9T          | (KB) Design plan<br>fifed + Post Options mization                                                                | Feasible<br>Directions                                                                    | Design Plan + and specific<br>Backtracking to each<br>class                                                 | Artificial<br>Intelligence.<br>Uses divide<br>and conquer<br>strategy.                                                                                                                                            |

| Evaluation<br>Class             | Knowledge<br>Based (KB)<br>Simplified<br>Equations                                                               | CircuitFeasible1988Simulatorwith SPICEDirections                                          | KB<br>1989 Simplified<br>Equations                                                                          | (1989) Tables and Uses divide and conquer Rules strategy.                                                                                                                                                         |

| Date                            | 1987                                                                                                             | 1988                                                                                      | 1989                                                                                                        | 1989                                                                                                                                                                                                              |

| Features                        |                                                                                                                  |                                                                                           |                                                                                                             | S                                                                                                                                                                                                                 |

| Fe<br>Tools                     | IDAC<br>[3]                                                                                                      | DELIGHT<br>SPICE [43]                                                                     | 0ASYS [7]                                                                                                   | BLADES<br>[8]                                                                                                                                                                                                     |

Table 2.3 Overview of analog sizing tools (1/4)

| лоп<br>Аdvantages<br>and Parti-<br>cular<br>Properties | Interface with<br>Berkeley CAD envi-<br>ronment. Includes<br>layout simul.    | Topology selection<br>+ device sizing        | Presents an analog<br>description lan-<br>guage with 4 levels | Has only been dem-<br>onstrated for prob-<br>lems of a small<br>number of opt. var. | Design for switch-<br>ed-capacitor delta-<br>sigma modulators                       | Hybrid SA for<br>coarse and gradient<br>for fine simula-tions.<br>Fuzzy logic for<br>topology select. |                                                                        |

|--------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Encapsula-<br>tion                                     |                                                                               |                                              |                                                               |                                                                                     | X                                                                                   |                                                                                                       | tool"                                                                  |

| Bookkeeping                                            |                                                                               |                                              |                                                               |                                                                                     | X                                                                                   | X                                                                                                     | in b                                                                   |

| Interactive<br>Design                                  |                                                                               |                                              |                                                               |                                                                                     | X                                                                                   | X                                                                                                     | nente                                                                  |

| qut92<br>9miT                                          | 2 weeks for<br>known circuits<br>and a few days<br>for simpler cir-<br>cuits. | 6 months, in-<br>cluding<br>circuit analysis | Entering new descriptions take long time.                     | Effort to add a circuit in about                                                    | Exhaustive<br>analysis<br>Required. High<br>cost to imple-<br>ment new<br>structure |                                                                                                       | ✓ = Means "implemented in tool                                         |

| Computa-<br>tion Time<br>Effort                        | 7 Par., 5 min<br>60 devices (VAX 8800)<br>OpAmp                               | 1 min. DEC<br>3100                           | 3 min. MIPS<br>2000                                           | 45 min. Li-<br>mited to a few<br>thousand eval-<br>uations.                         | 1.5 weeks                                                                           | 6 hours (96<br>MIPs worksta-<br>tion)                                                                 |                                                                        |

| Circuit<br>Complexity                                  | 7 Par.,<br>60 devices<br>OpAmp                                                | 39 Pararm.,<br>19 devices                    | 22<br>device<br>OpAmp                                         | 10<br>Pararam<br>OpAmp                                                              | 4th-order<br>sigma-delta 1.5 weeks<br>modulator                                     | 9 devices<br>OpAmp                                                                                    | ot implemen                                                            |

| Robust<br>Design                                       | >                                                                             |                                              |                                                               | X                                                                                   | ×                                                                                   | ×                                                                                                     | ans "n                                                                 |

| .nəməlqml<br>Language                                  | C<br>and<br>Lisp                                                              |                                              | C++                                                           |                                                                                     |                                                                                     |                                                                                                       | ⊠=Me                                                                   |

| Equation /<br>Design<br>Plan                           | Manually. Sim-<br>ple analytical<br>model                                     | Manually                                     | Manually                                                      |                                                                                     | Manually                                                                            | SPICE as the<br>evaluation en-<br>gine.                                                               | Legend: Z=There was no mention of it X=Means "not implemented in tool" |

| mdtivoglA<br>SoupindosT                                | Grid +<br>Steepest<br>Descent                                                 | Branch and<br>Bound                          | Two Step<br>Optimization                                      | SA with<br>SPICE<br>+local<br>Method                                                | SA                                                                                  | Fuzzy + SA<br>+ Gradient+<br>NN                                                                       | Z=There was                                                            |

| Evaluation<br>Class                                    | 1990 Simplified<br>Equations                                                  | Simplified<br>Equations<br>+ BSIM            | 1992 Simplified<br>Equations                                  | 1994 Circuit<br>Simulator                                                           | 995 Behavioral<br>Simulations                                                       | 1995 Based                                                                                            | Legend:                                                                |

| Date                                                   | 1990                                                                          | 1661                                         | 1992                                                          | 1994                                                                                | 1995                                                                                | 1995                                                                                                  |                                                                        |

| Features<br>Tools                                      | OPASYN<br>[9]                                                                 | MAULIK<br>[47]                               | STAIC<br>[46]                                                 | FRIDGE<br>[55]                                                                      | SD-OPT<br>[51]                                                                      | FASY<br>[10]                                                                                          |                                                                        |

Table 2.3 Overview of analog sizing tools (continued 2/4)

| Advantages<br>and Parti-<br>cular<br>Properties | Replace exact per-<br>formance relations<br>with quantitative re-<br>lations. | Simulation + equa-<br>tion Based on<br>waveform evalua-<br>tion. | Achieves short<br>execution times by<br>the use of Geometric<br>programming.                   | Uses simulator in<br>distributed envi-<br>ronment.                                | Add constraints on<br>devices to ensure a<br>safety margin from<br>manuf. or envir.<br>variations. Paral-<br>lelism. |

|-------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Encapsula-<br>tion                              |                                                                               | >                                                                | X                                                                                              | >                                                                                 | >                                                                                                                    |

| Bookkeeping                                     |                                                                               | X                                                                | X                                                                                              | >                                                                                 | >                                                                                                                    |

| Interactive<br>Design                           |                                                                               | X                                                                | X                                                                                              | >                                                                                 | >                                                                                                                    |

| qu192<br>9miT                                   |                                                                               | A few days to<br>add new cir-<br>cuits.                          | Doesn't specify<br>setup time.<br>Doesn't include<br>automatic<br>generations of<br>equations. | Uses Cadence<br>GUI. Long<br>times are asso-<br>ciated with si-<br>mulations run. | Encapsulate<br>commercial<br>simulators<br>(TISpice).                                                                |

| Computa-<br>tion Time<br>Effort                 |                                                                               | 11.8h (IBM<br>RS/6000-550)                                       | Very fast run<br>time, in the or-<br>der of a few<br>seconds                                   | 3.6 h (15)<br>SunSparc - 1)                                                       | 10 h (24 Sun<br>Ultra 10)                                                                                            |

| Circuit<br>Complexity                           | 8 Par.,<br>13 devices<br>OpAmp                                                | 33<br>devices                                                    | 10<br>devices<br>OpAmp                                                                         | 27 Par.,<br>32<br>devices                                                         | 20 Par.,<br>37<br>devices                                                                                            |

| Robust<br>Design                                |                                                                               | X                                                                | X                                                                                              | X                                                                                 | X                                                                                                                    |

| Implemen.<br>Language                           |                                                                               | С                                                                | MAT-<br>LAB                                                                                    | C++                                                                               | C++                                                                                                                  |

| Equation /<br>Design<br>Plan                    | Manually                                                                      | Automated.<br>Setup highly<br>automated                          | Equations for<br>Opamps are<br>generated ma-<br>nually.                                        |                                                                                   |                                                                                                                      |

| Mlgorithm<br>Algorithm                          | Qualitative<br>Reasoning<br>+ Post<br>Optimization                            | SA                                                               | Simple<br>Primal<br>Barrier Me-<br>thod                                                        | GA+SA                                                                             | Stochastic<br>Pattern<br>Search                                                                                      |

| Evaluation<br>Class                             | Simplified<br>Equations,<br>Qualitative<br>Reasoning                          | 1996 AWE +<br>Equations                                          | Simplified Sim<br>1998 Equations + Prin<br>Geometric Barr<br>Progr. (GP) thod                  | Circuit Si-<br>mulator                                                            | 2000 Circuit Si-                                                                                                     |

| Date                                            | 1995                                                                          | 1996                                                             | 1998                                                                                           | 6661                                                                              | 2000                                                                                                                 |

| Features<br>Tools                               | ISAID<br>[66]-[68]                                                            | ASTRX-<br>OBLX [48]                                              | GPCAD<br>[48],[55]                                                                             | MEALSTROM 1999 Circuit [57]                                                       | ANACONDA<br>[56]                                                                                                     |

Table 2.3 Overview of analog sizing tools (continued 3/4)

Table 2.3 Overview of analog sizing tools (continued 4/4)

| dvantages<br>Advantages<br>and Parti-<br>Cular<br>Properties | Com<br>flow<br>is a c<br>tools     | The N-F model uses<br>a set of training data<br>from SPICE.                    | Improve accuracy<br>of estimator using an<br>Active Learning<br>strategy | Explores sampling<br>methodologies to<br>improve model<br>quality.                              | Apply learning<br>strategies. Distri-<br>buted processing and<br>robust design.                  |

|--------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Encapsula-<br>tion                                           | X                                  | X                                                                              |                                                                          |                                                                                                 | >                                                                                                |

| 300kkeeping                                                  |                                    | X                                                                              |                                                                          |                                                                                                 | >                                                                                                |

| Interactive<br>Design                                        | $\mathbf{X}$                       | X                                                                              |                                                                          |                                                                                                 | >                                                                                                |

| quts2<br>9miT                                                | 8 hours                            | Model accuracy<br>depends on<br>training points.<br>Cannot handle<br>mismatch. |                                                                          | It takes<br>1h47min in a<br>SunBlade 100<br>to generate the<br>model training<br>samples(3125). | Encapsulate in-<br>house environ-<br>ment (AIDA).<br>Can use dynam-<br>ic model gen-<br>eration. |

| Computa-<br>tion Time<br>Effort                              | 5 min                              | 45 min. (124<br>min. with<br>mismatch<br>model)                                | 10's min 50.000<br>samples                                               | 51.9 µs of<br>execution time                                                                    | 20 min.<br>with robust<br>design (Intel<br>Core2 CPU<br>@ 2.40GHz<br>PC)                         |

| Circuit<br>Complexity                                        | 14 Par<br>9 devices                | 31<br>devices<br>OpAmp                                                         | 4 opt. va-<br>riables                                                    | 5-33<br>devices.<br>Up 10<br>opt. var.                                                          | 31 Par.<br>21<br>devices<br>41 const.                                                            |

| Besign<br>Besign                                             | X                                  | >                                                                              |                                                                          |                                                                                                 | >                                                                                                |

| Implemen.<br>Language                                        |                                    |                                                                                |                                                                          | MAT-<br>LAB                                                                                     | U                                                                                                |

| Equation /<br>Design<br>Plan                                 | Symbolic ana-<br>lyzer + manual    | Training<br>points<br>+ circuit<br>simulator                                   | Performance<br>model of<br>analog circuits                               | performance<br>parameter<br>macro-models                                                        | SPICE/<br>HSPICE<br>engines +<br>"feasibility<br>models"                                         |

| mdiiroglA<br>səupindəəT                                      | SA + several<br>Local Me-<br>thods | Evolutionary<br>Strategies +<br>SA                                             | Use<br>LIBSVM<br>Package.                                                | MIT GAlib                                                                                       | GA / SVM                                                                                         |

| Evaluation<br>Class                                          | 2001 Simplified<br>Equations       | 2003 Fuzzy<br>Neural<br>Network                                                | MVS                                                                      | NN                                                                                              | Circuit<br>2006 Simulator<br>+SVM                                                                |

| Date                                                         | 2001                               | 2003                                                                           | 2003                                                                     | 2004 NN                                                                                         | 2006                                                                                             |

| Features<br>Tools                                            | AMGIE<br>[11]                      | ALPAYDIN<br>[59]                                                               | VINCENTELLI 2003 SVM [60]                                                | VEMURI<br>[61]                                                                                  | GENOM<br>[69]-[70]                                                                               |

Legend: Z=There was no mention of it M=Means "not implemented in tool" 🗸 = Means "implemented in tool"

# 2.3.1 Specific Characteristics

The tools described in Table 2.3 can be evaluated by several metrics that measure the final solution quality. The first column "date" is performance independent. There is no correlation between the availability of the design tool and its efficiency or accuracy. On the contrary, the next three characteristics columns "Evaluation Class", "Algorithm Techniques" and "Equation/Design Plan", which are often used for classification purposes, will have an important influence in the performance and accuracy as will be shown later in this chapter.

Particularly, the following metrics were considered in order to compare the characteristics of the presented applications.

- (a) Robust Design: As far as sizing is concerned, robust design has to do with the accuracy and robustness of the solution. Accuracy is a measure of the quality that shows the difference between the synthesis tool's performance prediction mechanisms and the real performance of the obtained solutions, possibly including the layout-induced degradation. Robustness can be described as the capacity of the sizing tool to build and test circuits tolerant to manufacturing faults and operating point variations.

- (b) *Automation Level*: It can be described as the ratio of time needed to accomplish the task of designing a circuit manually to the time spent on designing the same circuit with the help of a synthesis tool. In this metric two aspects must be considered:

- Run time response: The period of time taken by the optimization tool to give the first solution to the problem.

- Setup time: The setup time is a measure of the time spent by the designer to adequate the problem to the synthesis tool. This time is often longer than the execution of the synthesis tool. This feature is particularly important because it is strongly correlated with the success and acceptability of the tool. What is the advantage of a design tool which has the remarkable prodigy to output some results in seconds, if it is necessary two months to setup the complete algorithm of a hypothetic circuit when it is known it could be designed by hand in one month? Excluding a reusedbased scenario, the answer is obvious "None".

- (c) Scope of the tool: It can be described as a group of analog design problems, which can be solved by this tool. This is an important feature for analog design, because these problems usually require several types of optimization techniques. An analog synthesis tool which aims at solving a wide range of design problems will be successful in the long run, whereas tools planned to solve a narrow range of problems will soon be out of date. Although, it is not shown in Table 2.3, it will be used later for comparative analysis.

- (d) *Design facilities*: It can be described as the set of additional features that can enrich a synthesis tool.

- Multi-objective Optimization. The DA tool presents the final solution in terms of a set of designs representing complementary tradeoffs of specific

objectives (for example, area versus consumption) instead of single design response.

- Interactive Design. The tool optionally produces intermediate performance reports (in the form of text or graphics) throughout the design execution time to inform the IC designer on the optimization progress. At the same time, the IC designer optionally has the possibility to interact with the tool in real time manner to tune up some parameters, e.g., the dimension of a transistor or the redefinition of some design bias.

- Bookkeeping Facilities. The tool should have additional capacities to help with the introduction and management of all the necessary data including the management of different technological files, different classes of circuits (e.g., operational amplifiers, phase-locked-loops, etc.), different performance measurements, different design parameters, different components, different topologies, and so on.

- Encapsulate Details. Some tools interact with external programs and so it makes sense that the interface with these additional tools can be made in an automatically way hiding unused options.

### 2.3.2 Performance Analysis

Performance results are intrinsically correlated with several factors, like the evaluation engine, the search mechanism, the technological model precision, the computer platform used to run the application, etc.

The computation time is highly correlated with the nature of the evaluation engine. All approaches leading with models derived either by numeric equations or by some artificial learning machine method are able to reach solutions quickly, however, the quality of results are always estimated approaches and the solution quality only depends on the models precision [1]. This important trade-off between accuracy and computation time can be observed in Table 2.4. By contrast, simulation based methods that play with a high accurate circuit simulator in each optimization loop cycle are able to produce good quality results, but at the expense of higher execution times.