Rick Reed Attila Bilgic Reinhard Gotzhein (Eds.)

# SDL 2009: Design for Motes and Mobiles

14th International SDL Forum Bochum, Germany, September 2009 Proceedings

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Rick Reed Attila Bilgic Reinhard Gotzhein (Eds.)

# SDL 2009: Design for Motes and Mobiles

14th International SDL Forum Bochum, Germany, September 22-24, 2009 Proceedings

#### Volume Editors

Rick Reed Telecommunications Software Engineering The Laurels, Victoria Road Windermere, Cumbria LA23 2DL, UK E-mail: rickreed@tseng.co.uk

Attila Bilgic Ruhr-Universität Bochum Chair of Integrated Systems 44801 Bochum, Germany E-mail: attila.bilgic@is.rub.de

Reinhard Gotzhein University of Kaiserslautern Networked Systems Group 67653 Kaiserslautern, Germany E-mail: gotzhein@informatik.uni-kl.de

#### Library of Congress Control Number: 2009934524

CR Subject Classification (1998): C.2, D.2, D.3, F.3, C.3, H.4

LNCS Sublibrary: SL 5 – Computer Communication Networks and Telecommunications

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-642-04553-7 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-642-04553-0 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### springer.com

© Springer-Verlag Berlin Heidelberg 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, IndiaPrinted on acid-free paperSPIN: 1276399306/31805 4 3 2 1 0

# Preface

This volume contains the papers presented at the 14th SDL Forum, Bochum, Germany entitled *Design for Motes and Mobiles*. The SDL Forum has been held every two years for the last three decades and is one of the most important open events in the calendar for anyone from academia or industry involved in System Design Languages and modelling technologies. It is a primary conference event for discussion of the evolution and use of these languages. The most recent innovations, trends, experiences, and concerns in the field are discussed and presented. The SDL Forum series addresses issues related to the modelling and analysis of reactive systems, distributed systems, and real-time and complex systems such as telecommunications, automotive, and aerospace applications. The intended audience of the series includes users of modelling techniques in industrial, research, and standardization contexts, as well as tool vendors and language researchers.

Of course, during the last three decades languages, associated methods, and tools have evolved and new ones have been developed. The application domain has changed almost beyond recognition. Three decades ago the mobile technology of today was science fiction, whereas now we find software systems embedded in inexpensive childrens' toys. More recently multi-core processors have become common technology for consumer computers, and are beginning to be applied in small devices. Even in small co-operating, independently powered remote devices (such as motes and mobile phones), there is enough memory and processing power to support quite sophisticated operating systems and applications. No longer do these need to be hand-coded in a machine-level language, and it is cost effective to apply the languages, tools, and methods that previously applied to systems for telephony routing or automated manufacture.

Many programming language support systems assume a single processor, or that distribution of processes over processors is handled by the operating system. System Design Languages such as the Unified Modeling Language or ITU-T Specification and Description Language allow engineers to defer the distribution until later in product engineering, and also to defer whether the distributed components of systems are loosely (or tightly) coupled. However, these issues still need to be tackled, and therefore a focus of SDL 2009 was on multi-processor and multi-core issues. The concern is what impact does development for this kind of system have on the model-driven approach, engineering languages, and operating system support. Papers in this volume address such issues or applications that use motes.

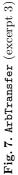

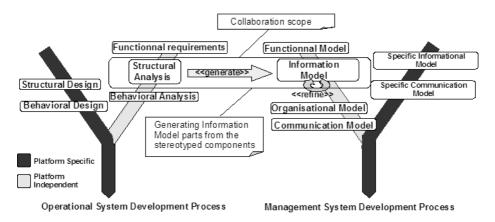

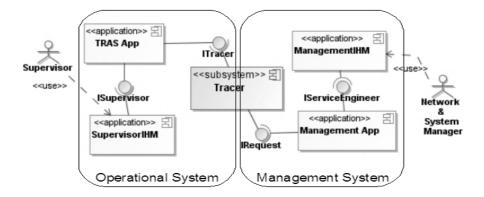

Based on experience with the previous SDL Forum, it was decided to not only call for papers based on well-advanced or established work, but also to invite short papers describing work-in-progress. One submitted paper that appears in this volume is very clearly in the category: "Towards Model-Based Development of Managed Networked Embedded Systems." This work is at an early stage, but the topic is certainly an important one, as we can anticipate further development of MDD and increasing numbers of networked embedded systems with individual components that are even more powerful. The method for developing the management system is the focus of this work. It will be interesting to see the results.

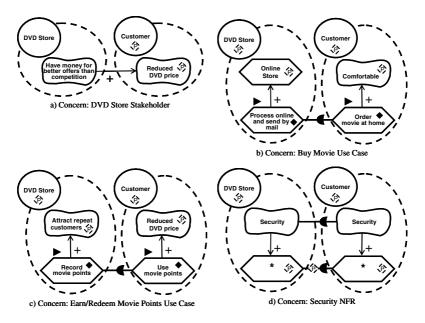

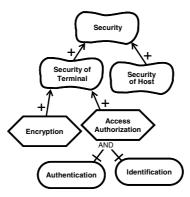

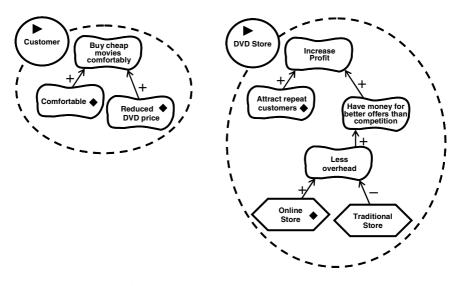

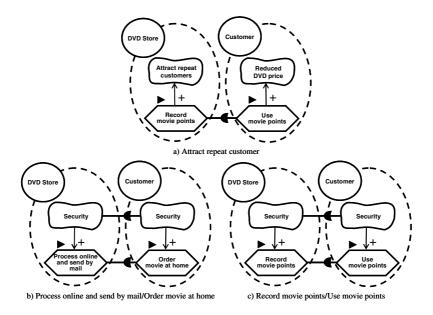

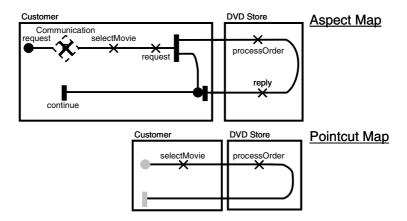

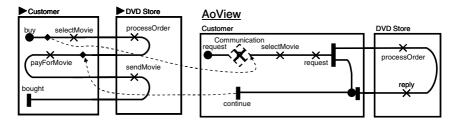

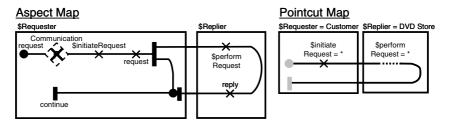

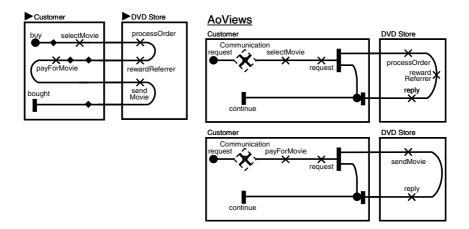

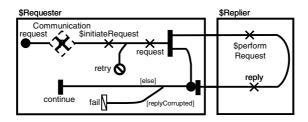

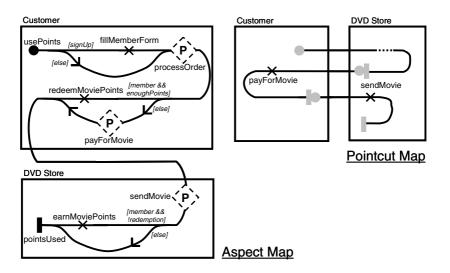

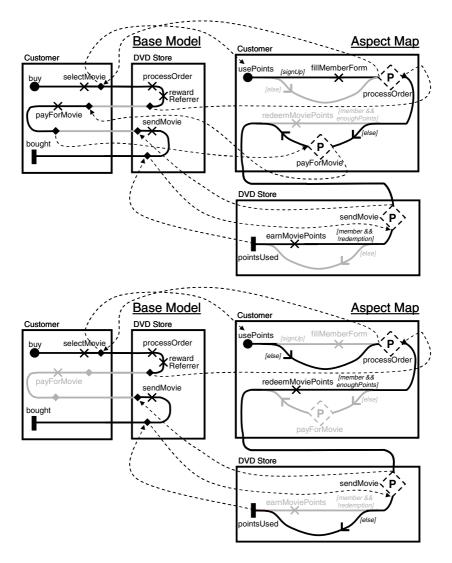

Another paper applies aspect orientation to the User Requirements Notation (URN). This language has only recently reached the status of a standard, and illustrates that it is not just the applications that are changing in nature over the years: URN has extended the range of formal languages to the requirements area, and the proposal to add aspect orientation shows that it is a *living language* that is evolving to user needs. In a few years' time URN, supporting tools, and use of the language will have evolved. In that case URN may be considered the natural way to design products with state-based models being thought of as intermediate languages, in the same way that currently the ITU-T Specification and Description Language is considered as the design with transcompilation into C. All that we can really predict is that after another decade, at the  $19^{th}$  SDL Forum, it is likely that system design will be at a higher level, with more advanced languages, methods, and tools.

# Thanks

As always, the event and this volume would not exist without the contributions of authors, who are thanked for their work.

The Programme Committee and Anders Olsen (Cinderella, Denmark) were reviewers of the papers, and are thanked for their work selecting the papers and the programme.

The organization of SDL 2009 was assisted by sponsorship and support from:

- IBM Rational

- Forschungsschwerpunkt "Ambient Systems"

- International Telecommunication Union

July 2009

Rick Reed Atilla Bilgic Irv Badr Reinhard Gotzhein

## SDL Forum Society

The SDL Forum Society is a not-for-profit organization that in addition to running the SDL Forum series of events:

- Has usually run<sup>1</sup> the SAM (System Analysis and Modeling) workshop every two years between SDL Forum years.

- Is a body recognized by ITU-T as co-developing the Z.100 to Z.109 and Z.120 to Z.129 and other language standards.

- Promotes the ITU-T System Design Languages.

For more information on the SDL Forum Society, see www.sdl-forum.org.

<sup>&</sup>lt;sup>1</sup> In 2008 there was no SAM workshop, but instead a one-day workshop on System Design Languages was held in collaboration with ITU-T at ITU-T in Geneva.

# Organization

Each SDL Forum is organized by the SDL Forum Society with the help of local organizers. The Organizing Committee consists of the Board of the SDL Forum Society plus the local organizers and others as needed depending on the actual event. For SDL 2009 the local organizers from Ruhr-Universität Bochum and hosting sponsor IBM Rational need to be thanked for their effort to ensure that everything was in place for the presentation of the papers in this volume.

## **Organizing Committee**

Chair

Atilla Bilgic

Ruhr-Universität Bochum

#### SDL Forum Society

Chairman: Rick Reed (TSE) Treasurer: Martin von Löwis (Hasso-Plattner-Institut) Secretary: Reinhard Gotzhein (Universität Kaiserslautern)

#### Hosting Sponsor

Irv Badr

**IBM** Rational

## Programme Committee

#### **Conference Co-chairs**

| Atilla Bilgic     | Ruhr-Universität Bochum, Germany    |

|-------------------|-------------------------------------|

| Reinhard Gotzhein | Universität Kaiserslautern, Germany |

#### Members

| Université d'Ottawa, Canada             |

|-----------------------------------------|

| IBM Rational, USA                       |

| Ruhr-Universität Bochum, Germany        |

| NTNU, Norway                            |

| Isoscope, France                        |

| IBM Rational, Sweden                    |

| Devotek, Norway                         |

| Humboldt-Universität zu Berlin, Germany |

| SINTEF, Norway                          |

| PragmaDev, France                       |

|                                         |

**Birgit Geppert** Reinhard Gotzhein Jens Grabowski Peter Graubmann Øystein Haugen Josef Hausner Loïc Hélouët Dieter Hogrefe Ferhat Khendek Tae-Hyong, Kim Alexander Kraas Thomas Kuhn Martin von Löwis Anna Medve Pedro Merino Gómez Thomas Musch Ostap Monkewich Elie Najm Javier Poncela González Andreas Prinz Rick Reed Manuel Rodríguez Cayetano Ahmad Sadeghi **Richard Sanders** Amardeo Sarma Ina Schieferdecker Georges Sebek Bran Selic Edel Sherratt York Tuechelmann Thomas Weigert

Avaya Labs Research, USA Universität Kaiserslautern, Germany Georg-August-Universität Göttingen, Germany Siemens, Germany SINTEF, Norway Infineon, Germany **INRIA** Rennes, France Georg-August-Universität Göttingen, Germany Concordia University, Canada KIT, Korea Fraunhofer ESK, Germany Fraunhofer IESE, Germany Hasso-Plattner-Institut Potsdam, Germany University of Pannonia, Hungary Universidad de Málaga, Spain Ruhr-Universität Bochum, Germany OMCI, Canada **ENST** Paris. France Universidad de Málaga, Spain Universitetet i Agder, Norway TSE. UK Universidad de Valladolid, Spain Ruhr-Universität Bochum, Germany SINTEF, Norway NEC, Germany Fraunhofer FOKUS, Germany ITU, SG17 Counsellor, Switzerland Canada University of Wales, UK Ruhr-Universität Bochum, Germany University of Missouri-Rolla, USA

# Table of Contents

# Model-Driven Development

| Model-Driven Construction of Embedded Applications Based on                                                               | 1  |

|---------------------------------------------------------------------------------------------------------------------------|----|

| Reusable Building Blocks – An Example<br>Frank Alexander Kraemer, Vidar Slåtten, and Peter Herrmann                       | 1  |

| Energy-Aware System Design with SDL                                                                                       | 19 |

| Model-Driven Development of Time-Critical Protocols with<br>SDL-MDD                                                       | 34 |

| Philipp Becker, Dennis Christmann, and Reinhard Gotzhein<br>Towards Model Based Development of Managed Networked Embedded | 50 |

| Systems                                                                                                                   | 53 |

## Analysis and Assessment

| Towards an Integrated Quality Assessment and Improvement Approach |    |

|-------------------------------------------------------------------|----|

| for UML Models                                                    | 63 |

| Akhtar Ali Jalbani, Jens Grabowski, Helmut Neukirchen, and        |    |

| Benjamin Zeiss                                                    |    |

| Optimal String Edit Distance Based Test Suite Reduction for SDL   |    |

| Specifications                                                    | 82 |

| Gábor Kovács, Gábor Árpád Németh,                                 |    |

| Mahadevan Subramaniam, and Zoltán Pap                             |    |

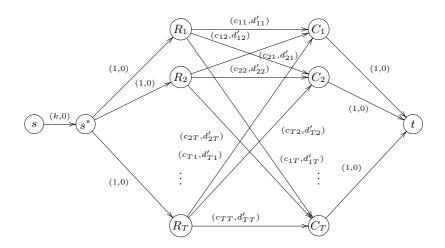

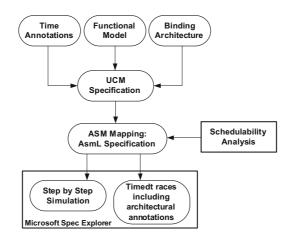

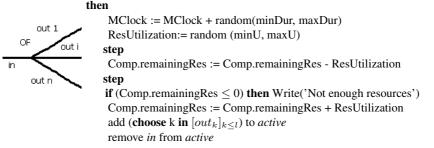

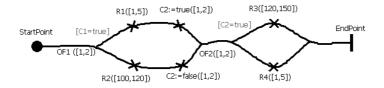

| Early Schedulability Analysis with Timed Use Case Maps            | 98 |

| Jameleddine Hassine                                               |    |

# Evolution of Development Languages

| Extending the User Requirements Notation with Aspect-Oriented |     |

|---------------------------------------------------------------|-----|

| Concepts                                                      | 115 |

| Gunter Mussbacher and Daniel Amyot                            |     |

|                                                               |     |

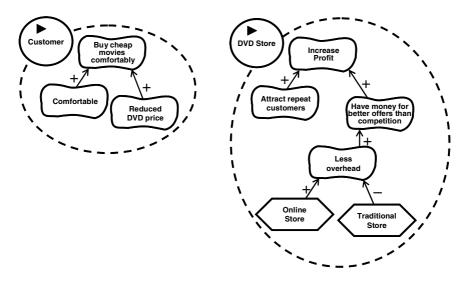

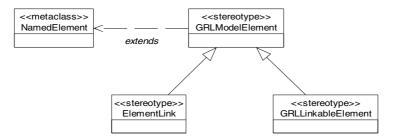

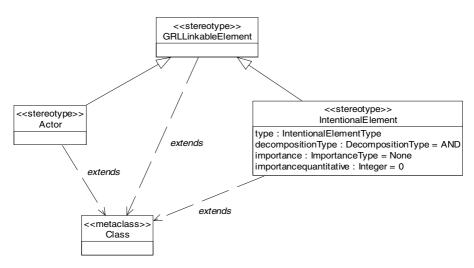

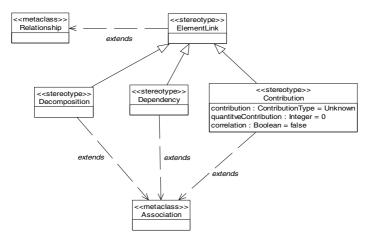

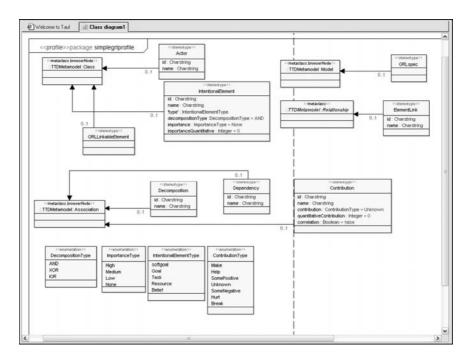

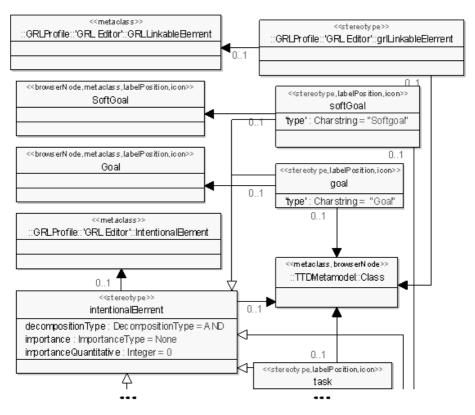

| A UML Profile for Goal-Oriented Modeling                      | 133 |

| Muhammad R. Abid, Daniel Amyot, Stéphane S. Somé, and         |     |

| Gunter Mussbacher                                             |     |

# Language Implementation and Support

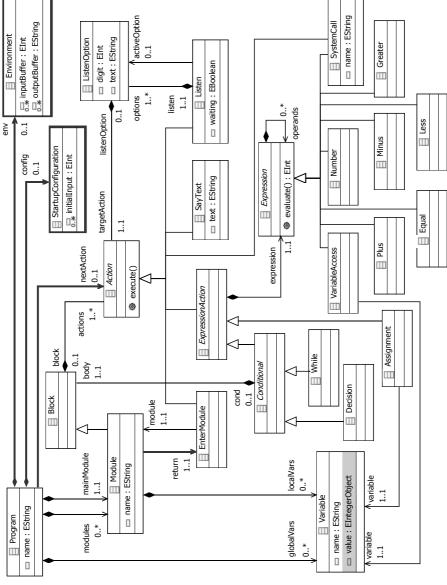

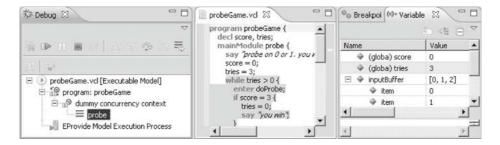

| Modelling a Debugger for an Imperative Voice Control Language<br>Andreas Blunk, Joachim Fischer, and Daniel A. Sadilek | 149 |

|------------------------------------------------------------------------------------------------------------------------|-----|

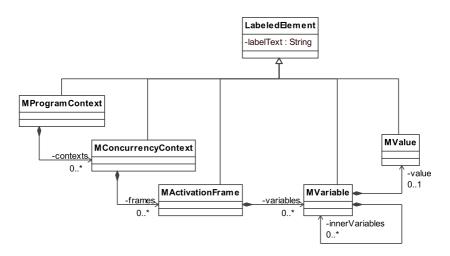

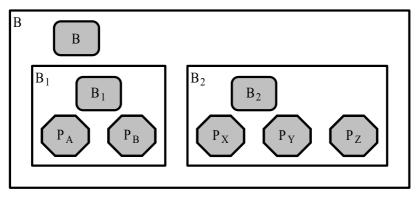

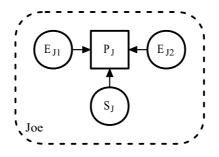

| The ARC Programming Model                                                                                              | 165 |

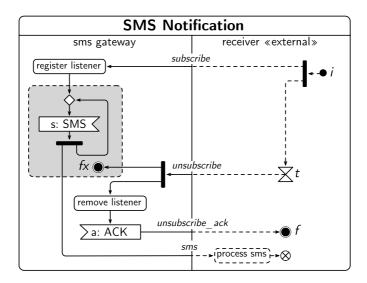

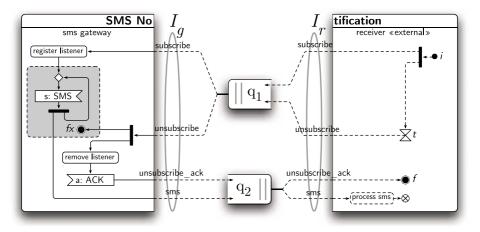

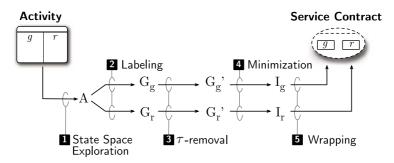

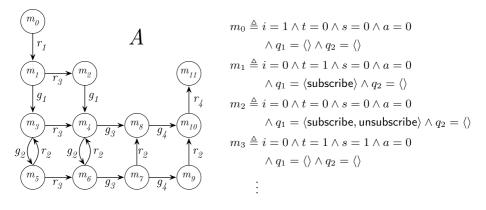

| Automatic Generation of Compatible Interfaces from Partitioned UML<br>Activities<br>Frank Alexander Kraemer            | 182 |

# **Application Studies**

| The Challenges of Using SDL for the Development of Wireless Sensor  |     |

|---------------------------------------------------------------------|-----|

| Networks                                                            | 200 |

| Klaus Ahrens, Ingmar Eveslage, Joachim Fischer,                     |     |

| Frank Kühnlenz, and Dorian Weber                                    |     |

| Modeling LTE Protocol for Mobile Terminals Using a Formal           |     |

| Description Technique                                               | 222 |

| Anas Showk, David Szczesny, Shadi Traboulsi, Irv Badr,              |     |

| Elizabeth Gonzalez, and Attila Bilgic                               |     |

| SDL/Virtual Prototype Co-design for Rapid Architectural Exploration |     |

| of a Mobile Phone Platform                                          | 239 |

| Shadi Traboulsi, Felix Bruns, Anas Showk, David Szczesny,           |     |

| Sebastian Hessel, Elizabeth Gonzalez, and Attila Bilgic             |     |

| Author Index                                                        | 257 |

|                                                                     | -0. |

# Model-Driven Construction of Embedded Applications Based on Reusable Building Blocks – An Example

Frank Alexander Kraemer, Vidar Slåtten, and Peter Herrmann

Norwegian University of Science and Technology (NTNU), Department of Telematics, N-7491 Trondheim, Norway {kraemer,herrmann,vidarsl}@item.ntnu.no

**Abstract.** For the rapid engineering of reactive systems we developed the SPACE method, in which specifications can be composed of reusable building blocks from domain-specific libraries. Due to the mathematical rigor and completeness with which the building blocks are designed, we can provide tool support facilitating a high degree of automation in the development process. In this paper, we focus on the design of embedded Java applications executed on Sun SPOTs by providing dedicated blocks to access platform-specific functionality. These building blocks can be used in combination with other blocks realizing protocols such as leader election to build more comprehensive applications. We present an example specification and discuss its automatic verification, transformation and implementation.

#### 1 Introduction

Maybe it is just that engineers still love the LEGO bricks of their childhood, but creating software systems by connecting reusable building blocks seems to be an attractive development paradigm that can facilitate reuse and enable an incremental development style in which problems can be solved block by block. Yet the everyday practice by developers often does not work as smoothly as simply plugging together bricks: Major challenges lie in the nature of reusable modules in the first place, especially in how to encapsulate and how to compose them. Our engineering method SPACE [12] aims to address these issues. As reusable units we use special building blocks that express their behavior in terms of UML activities. These can be composed by pins, and a system can be constructed as a hierarchy of building blocks. While building blocks can describe local behavior executed by a single component, they can in general also cover *collaborative* behavior among *several* components. This facilitates the reuse of solutions to problems that require the coordination of several components, and is especially useful to describe services.

While our method is general and useful in a variety of domains, we demonstrate in this article its application in the area of embedded systems. For that, we present the results of a case study on a sensor network carried out as part

R. Reed, A. Bilgic, and R. Gotzhein (Eds.): SDL 2009, LNCS 5719, pp. 1–18, 2009.

of the applied research project ISIS<sup>1</sup> (Infrastructure for Integrated Services  $\square$ ), in which we develop methods, platforms and tools for the model-driven development of reactive systems for applications in home network systems. The case study is implemented on small processing devices from Sun Microsystems, called *Sun SPOTs*  $\square$  that run Java.

In the following, we cover all steps needed to realize deployable code from high-level specifications. We will focus especially on the definition of building blocks for the domain of Sun SPOTs and on a protocol for fault-tolerant leader election. We start with an introduction of Sun SPOTs including the runtime support system, followed by a brief overview of our method. In Sect. 2, we present the example system and its high-level specification based on UML activities. The next two sections document our library for Sun SPOTs and the leader election algorithm. In Sect. 5 and 6, explanations of the automated analysis and implementation follow, in which state machines similar to SDL processes are synthesized, from which code is generated.

#### 1.1 Embedded Java on Sun SPOTs

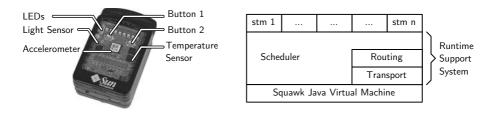

A sketch of a Sun SPOT is shown on the left side of Fig.  $\blacksquare$  Each SPOT is equipped with two buttons and sensors for temperature, light and acceleration. SPOTs can also carry extension cards to interact with various other devices. A Sun SPOT is controlled by a 32-bit ARM 9 processor that can run the Java virtual machine *Squawk* [5] executing Java 1.3 code following the CLDC 1.1 specification. SPOTs can communicate among each other using IEEE 802.15.4 radio communication, and build a mobile ad hoc network.

Fig. 1. Sun SPOT and Runtime Support System

#### 1.2 Runtime Support System

To facilitate the execution of many concurrent processes on Sun SPOTs, we have implemented a runtime support system **[6]**, sketched on the right side of Fig. **[1]** It includes a scheduler that is responsible for triggering the execution of state machine transitions whenever signals are received or timers expire. Further, a router and an object responsible for the transport of signals support communication using the SPOT's radio communication. For a detailed description of

$<sup>^1</sup>$  Partially funded by the Research Council of Norway, project #180122.

the execution mechanisms and their formal behavior in temporal logic, we refer to [7]. To generate the state machine classes from UML state machines, we use the code generator described in [8], which produces the necessary Java code.

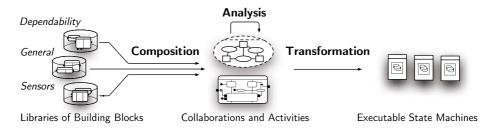

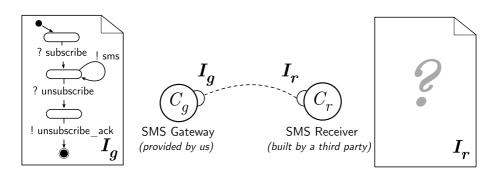

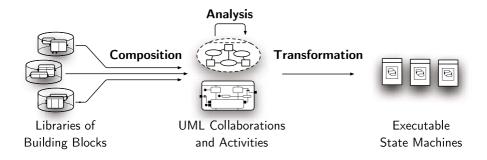

#### 1.3 The SPACE Engineering Method

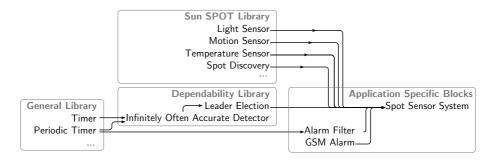

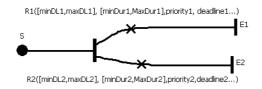

We developed the method SPACE [12] for the engineering of reactive systems. This method focuses on the definition of reusable building blocks expressed as UML activities and collaborations, combined with Java code for detailed operations. Building blocks are grouped into libraries for specific domains, as illustrated on the left hand side of Fig. [2] Developers can use these blocks by composing them together within UML collaborations and activities: the collaborations describe the structural binding of roles and provide a high-level overview and activities describe the detailed behavioral composition of events, with some additional glue logic where necessary. Each block has an associated *external* state machine, abbreviated ESM, that provides a behavioral contract describing in which sequence parameters must be provided to or may be emitted by a block. This description is useful for understanding a block without looking at its internal details, and enables compositional model checking, as we describe below.

Fig. 2. The SPACE engineering method

Once a specification is complete, it is analyzed to ensure various properties that should hold for any application. For example, a composition of blocks should never harm any of the contracts (ESMs) and a collaboration should terminate consistently. For this behavioral analysis, we use model checking. Due to the compositional semantics and the encapsulation of building blocks by their ESMs, the state space needed for model checking tends to be very small, since only one building block on a single decomposition level has to be considered at a time.<sup>2</sup>

Complete systems are represented by special system collaborations and activities. When a system is sound, it can be transformed automatically into executable state machines and components, using a model transformation [10,11]. From the resulting state machines, code for different platforms (such as the Sun SPOTs introduced above) can be generated.

$<sup>^2\,</sup>$  We observe that most building blocks in our libraries require far less than 100 states.

## 2 A Sensor Network for Remote Home Monitoring

An increasingly popular area for home automation is to remotely monitor vacation homes and cabins. Several sensors can be installed in a cabin. One of the assumptions in our project is that embedded sensors with processing capacity similar to Sun SPOTs are so cheap they can also be used in a consumer market. For instance, the sensors can register the temperature at several places, detecting frost or fire. Further, they can detect sudden changes in light or measure acceleration on doors and windows, indicating that somebody is breaking in. With the extension card presented in **[12**], we further assume that each Sun SPOT is capable of GSM communication to set off an alarm to a remote user, for example by means of an SMS.

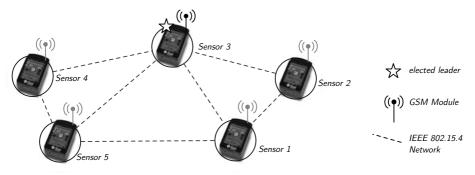

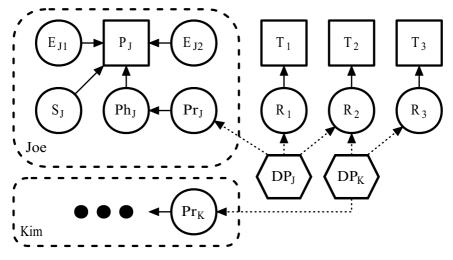

To improve the quality and robustness of the system, the sensors communicate among each other before sending an alarm via GSM. This serves several purposes: First, multiple sensors can be used redundantly, so that important conditions are monitored by more than one sensor, whereas only one alarm should be issued. Second, some conditions may give rise to alarm if the sensors are triggered in a certain pattern. For example, while changes in light of one sensor could indicate a broken window shutter, a change observed by several sensors may simply be due to a cloud moving in front of the sun. This means that alarms need to be coordinated. For that reason, we use a leader election protocol that points out one SPOT sensor to filter and issue alarms. If the leader runs out of battery or otherwise fails, a new leader takes over. Such a network is illustrated in Fig.  $\square$

Fig. 3. Sensor network with the elected leader

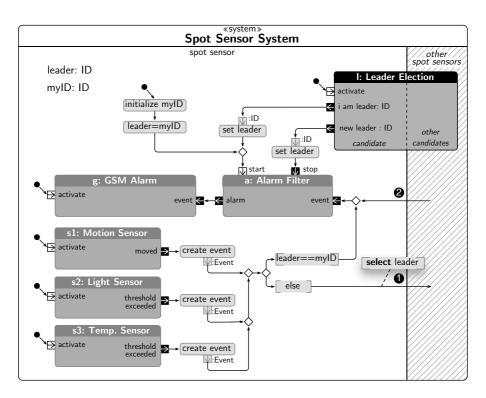

Figure 4 shows the UML activity describing the behavior of a SPOT sensor as composed from our reusable building blocks. Since the SPOT sensors of the system all have the same behavior, it suffices to specify only one of them. To visualize the relationship of a SPOT sensor to the other sensors explicitly, however, we use two activity partitions. The left one, *spot sensor*, describes how a SPOT sensor is composed from building blocks, which defines the behavior. The

<sup>&</sup>lt;sup>3</sup> We will not discuss detailed patterns describing when an alarm should be triggered, and we will also disregard the configuration of individual SPOT sensors.

Fig. 4. Activity describing the composition of SPOT sensors from building blocks

right partition, *other spot sensors*, enables us to represent the communication with the other sensors. This partition is only sketched, as only the left one will be used for the transformation and code generation.

A sensor consists of a block<sup>4</sup> for GSM communication g, the alarm filter a and three building blocks accessing the Sun SPOT's sensors for motion (s1) light (s2) and temperature (s3). While these blocks encapsulate local behavior, a building block can also comprise collaborative behavior that is executed by several participants. The leader election, contributed by building block l in Fig. 4 is a typical example for that. It is a collaboration among several SPOT sensors, and therefore crosses the activity partitions. Internally, the block specifies the establishment of contact between all the sensors and how a leader is selected amongst them. This behavior is detailed in Sect. 4

The activity also contains references to the operation *create event*. Since UML does not have a concrete language for actions, the details of these operations are specified by Java methods, managed by our editor. The other elements in the activity are initial nodes ( $\bullet$ ) as well as merge and decision nodes ( $\diamond$ ). Decision nodes are followed by flows that are guarded (1).

<sup>&</sup>lt;sup>4</sup> Technically, blocks are modeled as UML elements of type *Call Behavior Action*, which can refer to subordinate activities.

Fig. 5. Overview of reused block from libraries and application-specific blocks

Upon the start of a SPOT sensor, the initial nodes emit a token and start all blocks, including the collaboration for the leader election. The alarm filter is started as well, so that the SPOT by default uses its own GSM Alarm block to send any SMS notifications, until it finds another leader. The leader election emits a token through *new leader* once it detects a SPOT that is pointed out as the new leader, carrying its ID. In case a SPOT itself is pointed out as leader, a token is emitted through *i am leader*. In both cases, the ID of the leader is stored in variable *leader*. If a SPOT becomes leader, the alarm filter is started, and if the SPOT loses its leader status, the alarm filter is terminated.

Whenever one of the sensors s1, s2 or s3 registers a condition, it emits a token via its output pin, upon which an event is created containing the kind of condition and ID of the sensor. If the SPOT owning the sensors has the leader role (i.e., guard *leader==myID* is valid), the event is directly passed to the alarm filter. Otherwise, the SPOT sensor forwards the event to the current leader. In this case, the leader is one of the other SPOT sensors, and sending to it is specified by the transfer edge **0**. Since the other SPOTs are potentially many, we have to select which one to address, using the **select** operator introduced in [10]. It refers to the ID of the leader. Vice versa, if a SPOT sensor has the leader role, it may receive events from other SPOT sensors (at **2**).

Figure provides an overview of the dependencies between the building blocks used for the specification of the SPOT sensor system. Most of them are taken from our existing libraries (listed here with only those blocks used in the example). The Alarm Filter, the experimental GSM Alarm, and the complete system are specific for the example.

#### **3** Building Blocks Specific for Sun SPOTs

Our library for Sun SPOTs contains twelve building blocks dedicated to the specific capabilities of the devices, such as the buttons, all sensors on the SPOTs, and the LEDs. In the following we present some of those that are used in the SPOT sensor system.

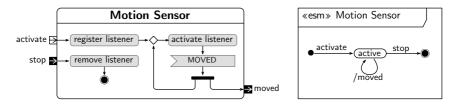

#### 3.1 Building Block for Sensors

Figure **[5]** shows the internal details of the block for the detection of movements. The accelerometers of the Sun SPOTs are accessible via a special API. To react on sudden accelerations that exceed a certain threshold value, a listener is registered at the SPOT classes that provide access to the hardware. To keep the execution of the code reacting upon an event under the control of the scheduler of our runtime support system (RTS), the building block uses an internal signal as buffer, to decouple the processes. For this reason, operation *register listener* creates a listener, which, upon its invocation following a sudden movement, produces a signal *MOVED*, that is fed into the RTS. Once this signal is processed, the behavior following the accept signal action declared for *MOVED* in Fig. **[6]** is executed: a token is emitted via output node *moved*, and the listener is reactivated, to listen for further movements. The blocks controlling the light and temperature sensors access the SPOT API in a similar way.

On the right hand side of Fig. **6**, the ESM for the motion sensor is shown. As mentioned previously, it documents the behavior visible at the pins of an activity, so that we know its external behavior when it is instantiated as a block as in Fig. **4**. Due to the ESM, we know that after a token enters *activate*, tokens may be emitted via *moved* until we terminate the block via *stop*.

Fig. 6. Building block for the motion sensor

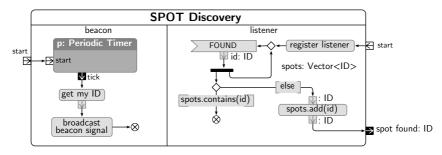

#### 3.2 SPOT Discovery

To dynamically find other SPOTs in the sensor network, we provide a collaborative building block which uses the Sun SPOT's broadcasting functions so that they can discover each other. The corresponding activity is shown in Fig. [7]The partition *beacon* describes how a SPOT that wants to be discovered sends out periodic messages. Since these messages are specific for Sun SPOTS, they are sent directly from the Java operation, instead of using our runtime support system. The partition *listener* describes the logic to be implemented by a Sun SPOT that wants to discover other SPOTs. For that, it listens to the incoming beacon messages. To decouple the receiving processes from the scheduling of state machine transitions, once such a message arrives, it is fed into our RTS via signal *FOUND*, similar to the listener reacting to the movement of a SPOT explained above. If the ID is not yet known, a token is emitted via *found spot*. Notice that if a SPOT wants to both discover other SPOTS and be discovered, it instantiates this collaboration twice, once as a beacon and once as a listener.

Fig. 7. Building block for the service discovery

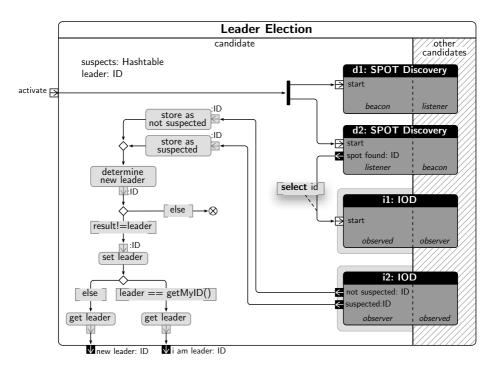

Fig. 8. Collaboration for the leader election

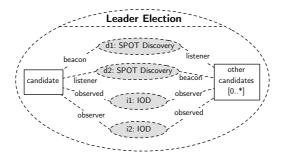

#### 4 Collaborative Building Blocks for Leader Election

To make sure that only one of the SPOT sensors forwards an alarm over GSM, we use a fault-tolerant leader election protocol. Should the leader SPOT run out of battery or otherwise fail, another one must take its place so that alarms are still sent if necessary. To solve this problem, we implemented an algorithm from **[13]**. The algorithm uses an *Infinitely Often Accurate Detector* (IOD) as failure detector, a concept from **[14]**, which is used by a component to monitor if any of its communication partners have crashed **[5]** In Sect. **[4.1]** we provide a dedicated building block for this function.

The collaboration in Fig.  $\[B]$  specifies the structural aspects of the leader election. It depicts the participant *candidate* as collaboration role, and refers to the sub-services for SPOT discovery and failure detection by collaboration uses d1, d2 and i1, i2. The leader election is a symmetric collaboration, in which all participating roles have the same behavior, and the role for the candidate is therefore represented twice. For the model transformation and the code generation, the left *candidate* is used. To make the collaboration with the other candidates explicit, we refer to the *other candidates* on the right hand side, similar to our proceedings with the SPOT sensors in Sect. [2].

$<sup>^{5}</sup>$  In the fault-tolerance domain, a node is said to *crash* if it from some point on permanently ceases all operations, but works correctly until then (see 15).

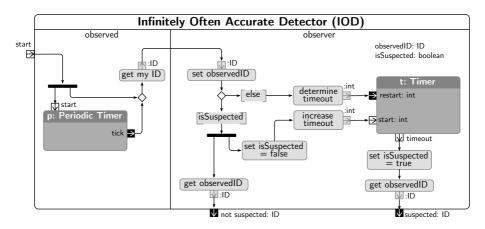

Fig. 9. Building block for the Infinitely Often Accurate Detector

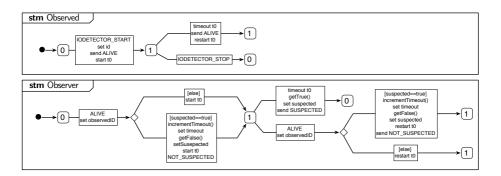

#### 4.1 Infinitely Often Accurate Detector (IOD)

In our example, we use the Infinitely Often Accurate Detector (IOD,  $\square3$ ) as specified in Fig.  $\square$  The partition on the left side models the observed SPOT, which periodically sends so-called "alive" messages to the observing SPOT, represented by partition observer. These messages are triggered by the periodic timer p and carry the ID of the observed SPOT. The observer SPOT maintains two variables to store the status of the observed SPOT; observedID for its ID and the boolean isSuspected. Moreover, the observer has a timer t to determine if the alive message from the observed SPOT is delayed.

Whenever the observer receives an alive message from the observed SPOT, it reacts depending on the current value of *isSuspected*:

- If the observer does not suspect the observed SPOT sensor of having crashed, it will simply restart timer t and wait for the next alive message.

- If, on the other hand, the observer currently suspects the observed SPOT of having crashed, the observer will change *isSuspected*, increment the timeout period<sup>6</sup> and emit the observed's ID through output node *not suspected*.

If, however, timer t expires (i.e., no alive message was received in time), the observer will suspect the observed SPOT of having crashed, set *isSuspected* accordingly and emit a token carrying the observed SPOT's ID through output node *suspected*.

Since a message could also be delayed in the communication medium, a timeout does not always mean that a SPOT has crashed. Hence there may exist transient states in which two SPOTs are both considered the leader. This, however, is acceptable for our application domain. For a detailed analysis and proof of the properties of the Infinitely Often Accurate Detector, we refer to **13**.

<sup>&</sup>lt;sup>6</sup> Incrementing the timeout period upon detecting a false suspicion ensures that the observer will wrongly suspect the observed only a limited number of times.

#### 4.2 Composed Building Block for the Leader Election

The detailed behavior of the leader election is expressed by the activity in Fig. [1]. Similar to the overall system of Fig. [4], the leader election is symmetric. The partition *candidate* on the left side represents one participant and its detailed behavior, while the partition to the right represents its communication partners.

As part of the leader election, a SPOT participates in the Infinitely Often Accurate Detector (IOD) collaboration as both *observer* and *observed* entity. This is represented by blocks i1 and i2, which both refer to the activity in Fig. but which are bound to partition *candidate* with roles *observed* resp. *observer*. Moreover, this collaboration is executed as multiple concurrent sessions (once towards each communication partner). This is signified by the shadow around them, a notation introduced in  $\Pi 0$ .

When the leader election collaboration is activated, the SPOT Discovery collaboration is initialized as both beacon (d1) and listener (d2), according to the role binding in Fig. 8, so that a SPOT sensor can both detect others and be detected by others. For each sensor found, a token with its ID is emitted via pin spot found of d2. This ID is used to start a new session of the IOD collaboration i1, so that a SPOT is observed by any other SPOT it detects. For that we use again the **select** statement, which this time refers to the value provided by the token flow. Vice versa, once a SPOT is detected by other SPOTS, they start a new instance of the IOD collaboration (in this direction represented by i2).

Fig. 10. Building block for leader election

Via the output pins suspected and not suspected on i2, a SPOT is notified about perceived changes in the state of each of the other SPOTs. The logic that follows determines the current leader status. For that, hash table suspects maps the ID of the other SPOTs to their respective status (suspected or not suspected). Whenever i2 issues a change in state of another SPOT via one of its output pins, the subsequent operations store this change to the hash table and determine the new leader. If several SPOTs qualify for the leader status, the one with the lowest ID is chosen. If the leader has changed, we store the new leader and check if the new leader is this SPOT. Depending on the outcome, a token is emitted through either the *i* am leader or new leader output node.

#### 5 Automated Analysis

The analysis of the specification is based on model checking. This process is automated, since our tool also generates the corresponding theorems to be verified. Currently, we check the following generally desirable system properties **16**:

- A building block must conform with its own ESM. The motion sensor of Fig. 6, for instance, may not emit a token via node *moved* after the surrounding context provided one via *stop*.

- A building block must also obey all ESMs of the subordinate blocks it is composed from.

- Building blocks with more than one participant are checked for bounded communication queues. For the IO detector in Fig. 9, for instance, we find that the periodic timer could, in principle, overflow the queue between the observing and the observed component.

The analysis focuses on the soundness of interactions among collaboration participants as well as the correct composition of all building blocks with respect to event orderings. The content of operations (that is, the Java code) is not part of the analysis. In cases where decisions are involved that depend on variables, the analysis always examines all alternative branches. If the executions of some branches may harm certain properties, we reason manually if these cases may in fact happen. For instance, in the IO detector of Fig. [9], the else branch may restart the timer before it is started. This, however, never happens in the final system because of the value of *isSuspected*.

The results of the analysis are presented to the user by explanatory annotations within the original UML model, so that no expertise in the underlying formalism is required, as demonstrated in [17]. In addition, counter examples illustrating design flaws are presented as animations within the activities. In our experience, checking the above mentioned properties is of great value in the practical development of specifications. Although these properties may appear simple when considered in isolation, even experienced engineers usually harm

<sup>&</sup>lt;sup>7</sup> In this case, however, we estimate the time needed for the transmission and subsequent processing and conclude that this is not an issue in a real system.

several of them in initial designs, especially when more complex collaborations are constructed.

Due to the compositional semantics of our method, each building block can be analyzed separately. Internal building blocks are abstracted by their ESMs, so that the global state space of the specification in Fig. 4 has only 15 distinct reachable states. Moreover, since most of the building blocks are taken from libraries and are already analyzed, only the new ones created for the specific applications have to be examined. These are the ones for the SPOT Sensor System, the Alarm Filter and the GSM Alarm.

#### 6 Automated Implementation

As briefly mentioned in the introduction, the implementation is performed by a completely automated process with two steps: In a first step, executable state machines are synthesized from the activities. In a second step, code is generated. This is possible since the activities provide descriptions that are behaviorally complete, and the details of operations are provided as Java methods as part of the building blocks.

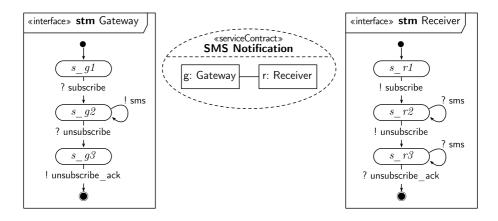

#### 6.1 Transformation to Executable State Machines

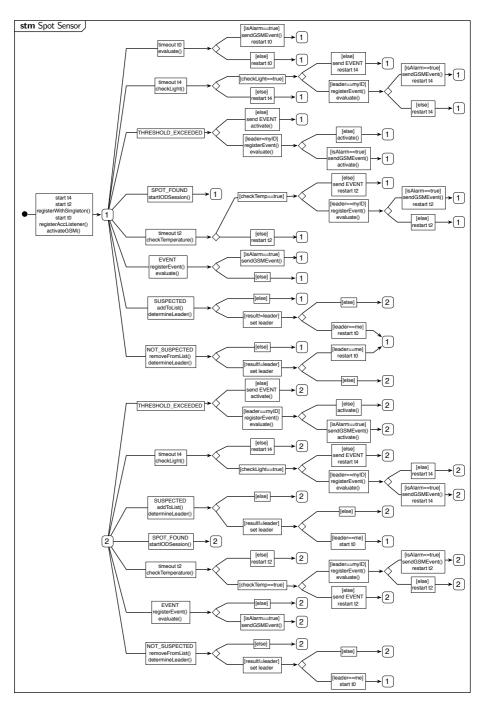

In Fig. 11 and 12, we present the state machines as generated by the transformation. In our method, they are only an intermediate result used as input for the subsequent code generation; developers do not have to edit or read them. In the following, we highlight some properties to demonstrate the soundness of the transformation.

For the partitioning of components into state machines (or *processes* in SDL), our algorithm follows the guidelines from [6]. In particular, the algorithm merges all behavior of building blocks that is executed one at a time by the component under construction into one single state machine. All blocks that denote multi-session collaborations (behavior that is executed multiple times towards a changing number of different communication partners) are implemented by dedicated state machines, one instance for each session, as presented in [10]. For the SPOT sensor system, for instance, the algorithm creates the state machine *Spot Sensor*, depicted in Fig. [11], which takes care of the main component behavior. This includes all logic contained in the building blocks used in Fig. [2]. However, since the behavior of the Infinite Often Accurate Detector is executed concurrently within each SPOT sensor (once for each other sensor detected), its behavior is implemented by dedicated state machines. These are state machines *Observer* and *Observed* in Fig. [12].

The main state machine *Spot Sensor* has two distinct control states, 1 and 2. This is because the transition behavior only has to distinguish if a SPOT is

<sup>&</sup>lt;sup>8</sup> This is less than the 15 states from the previous analysis because the analysis also captures the interleaving with other SPOTs and the queues for communication, which do not contribute any control states for a local component.

Fig. 11. Bird's eye view of the synthesized state machine for the Spot Sensor

Fig. 12. The synthesized state machines for the IO detector

the leader or not. When a spot is the leader, the alarm filter is active and the state machine is in state 1. When another SPOT is the leader, the alarm filter is inactive and the state machine is in state 2. The transitions from either state handle the periodic checks of the sensors, the periodic discovery protocol and react to the events of the Infinitely Often Accurate Detector. In state 1, which is entered by the initial transition, the SPOT assumes it is the leader and therefore starts the alarm filter, which constantly evaluates the log of events, shown by the topmost transition.

#### 6.2 Code Generation for Sun SPOTs

Since the Sun SPOTs execute Java, the code generator described in 9 is largely based on the standard Java code generator, described in **18**. As introduced in Sect. 1.2. the execution is based on a runtime support system, which takes care of scheduling, routing and transport of messages. The scheduler (see Fig. 1) maintains event queues for each state machine in which incoming messages and active timers are placed. In a round-robin manner, the scheduler triggers the execution of state machine transitions by feeding the event into a dedicated transition method, which is specific for each state machine type. The transition method contains nested if-statements that distinguish the current control state and input event and then execute the effect as specified by the UML transitions in Fig.  $\square$ and 12. Effects referring to operation calls on the activity level, such as *determine* new leader in Fig. 10, are copied into the transition method. Other actions that are part of a transition effect, such as sending signals or operations on timers, are synthesized from the UML model. The transport module (see Fig. D), responsible for sending and receiving messages from and to other SPOTs, uses the radio stream protocol from the Sun SPOT API to transmit messages. This protocol provides buffered, reliable, stream-based communications over multiple hops on top of the IEEE 802.15.4 radio protocol. The content of the messages sent via the radio channels are SOAP-documents generated with the help of the kSOAP libraries **19**, as described in **8**. For the necessary serialization of objects, the code generator adds methods that convert objects and primitive types to strings.

#### 7 Estimation of Reuse Proportions

To estimate the degree of reuse for the exemplified system, we distinguish between the building blocks that are part of our libraries and intended for reuse, and those building blocks constructed specifically for the application. These are shown in Fig. 5, with the libraries on the left hand side. As application-specific we count the *Alarm Filter*, the *GSM Alarm* and the overall *SPOT sensor* system. The effort necessary for the construction of a building block consists of the UML models on the one hand and Java code contained within the call operation actions (like *determine new leader* in Fig. 10) on the other hand.

- By counting the lines of code contained in the call operation actions in each building block, we find that there are  $l_{blocks} = 443$  lines of code within the call operation actions for all building blocks used in the system in total. Those building blocks taken from libraries contribute with  $l_{lib} = 333$  lines, so that the reuse proportion  $R_{code} = l_{lib}/l_{blocks}$  is 75 %.

- As an estimate for the effort spent UML modeling, we use a simple metric that just counts the number of activity nodes and activity edges  $n = n_{nodes} + n_{edges}$  within a building block. This metric shows that all building blocks used in the system consist of n = 276 edges and nodes in total. Those building blocks taken from the library contribute with  $n_{lib} = 195$  elements, so that the reuse proportion  $R_{model} = (n_{lib}/n)$  is 71 %.

Of course, these numbers vary for different systems. For the given example, we have programmed a relatively simple logic for the alarm filter, which contributes only 50 lines of code. Since the GSM module is not yet finalized, we estimate another 50 lines for that building block.

To get an impression of the overall gains including the automatic implementation, we consider also the complete code needed for the execution on top of the runtime support system. The code generated automatically for the state machine logic adds up to  $l_{stm} = 634$  lines, and the number of code lines written manually for the Java operations copied from the building blocks as mentioned above is  $l_{blocks} = 443$ . This means that the code necessary for the entire application has  $l_{total} = l_{stm} + l_{blocks} = 1077$  lines. from which  $l_{stm}/l_{total} = 59$  % are generated automatically. If we add up these numbers, we find that  $(l_{lib} + l_{stm})/l_{total} = 90$  % of the Java code lines are either reused or generated from the UML models.

#### 8 Related Work

There exist a number of approaches for the model-based design of reactive systems that are also suitable for embedded applications. Some of them based on SDL such as TIMe [20], SPECS [21], SOMT [22] and SDL-MDD [23]. Others,

<sup>&</sup>lt;sup>9</sup> The underlying runtime support system has about 1900 lines of code. Since it is provided as a library that can be reused also in manual approaches, it is not part of our calculation.

such as ROOM [24] (later UML-RT) or Catalysis [25], are oriented towards UML as language. As design models that describe the behavior of individual components, these approaches use state machines, either in the form of SDL processes or as UML state charts (called *ROOM charts* in [24]). To capture collaborative behavior among several components, most of these approaches rely on MSCs. Catalysis [25], inspired by the Object-Oriented Role Analysis Method (OOram, [26]) and DisCo [27], on the other hand, uses collaborations more explicitly in specific diagrams, albeit in a rather informal way that requires manual synchronization by the developers. Micro protocols [28] are another approach to capture and encapsulate communication protocols within self-contained units, by using pairs of SDL processes or composite states.

In principle, these approaches are compatible with the one presented here, since all the design models based on state machines with their emphasis on event-driven transitions are quite similar. The difference lies in the models on which developers work: To enable the composition of collaborative behavior as self-contained building blocks, we use UML activities, from which the state machine-based design models are derived automatically. This enables a number of opportunities for the reusability, the analysis and the overall specification style, as we will argue below.

#### 9 Concluding Remarks

In our experience, the composition as enabled by activities, shown for example in Fig. 4 is quite flexible. We attribute this to two major reasons: First, the complete but cross-cutting nature of UML activities, in which the coordination of several participants can be described within the same diagram. If, for example, we would like to exchange the selected leader election protocol with another one, we would just have to replace the building block l in Fig.  $\underline{\mathbf{A}}$  and its connections to the other blocks, which can be achieved by focusing on one single diagram. Second, the way activities enable the encapsulation of functionality related to a certain purpose as separate, self-contained building blocks. While state machines offer some means of structuring (for example composite states), they do not offer the same degree of flexibility and separation as activities. The functions encapsulated by the building blocks in Fig. 4, for example, are dispersed among several transitions in the state machines of Fig. 11 and 12. One reason for that is that state machines represent their states by explicit control states, while activities use concurrent flows that may execute independently. Although such behavior can to a certain degree be described in state machines by concurrent regions, such a description style gets intricate once the behaviors in these regions need to be synchronized. However, since state machines are very suitable for the specification of the executable behavior of components, we generate them in the described way, so that we have both the compositional features of UML activities and the efficient scheduling of state machines.

Besides these properties coming from the chosen notation, an important feature of our method is the compositional verification it enables, based on the underlying semantics in cTLA [29]. Not only does this reduce the state space during model checking, but it also has important effects on the larger scale development process. Since building blocks can be verified individually, proven solutions can be encapsulated in building blocks, and these can be checked and stored in a library. Whenever a building block is reused, the verified properties are enforced automatically and do not have to be re-verified. This enables "true reuse" as mentioned in [25], in which reuse does not mean to simply copy and paste some parts of a specification, but also ensures that important properties are maintained.

All things considered, we think that the chosen principles and the way they are combined enable a reuse-oriented specification style, one that encourages the use of encapsulated building blocks to a high degree, but that still allows us to adapt systems to match the requirements of the individual application. This is a crucial step towards the cost-effective LEGO-brick like development paradigm.

Acknowledgements. We would like to thank Fritjof Boger Engelhardtsen from Telenor for support with the GSM module, as well as Marius Bjerke and Bemnet Tesfaye Merha for their enthusiastic work on the Sun SPOTs in their theses.

#### References

- Kraemer, F.A.: Engineering Reactive Systems: A Compositional and Model-Driven Method Based on Collaborative Building Blocks. PhD thesis, Norwegian University of Science and Technology, Trondheim (August 2008)

- Kraemer, F.A., Herrmann, P.: Service Specification by Composition of Collaborations — An Example. In: Proceedings of the 2006 WI-IAT Workshops (2006 IEEE/WIC/ACM International Conference on Web Intelligence and Intelligent Agent Technology), pp. 129–133. IEEE Computer Society Press, Los Alamitos (2006)

- 3. ISIS Project Website, http://www.isisproject.org

- 4. http://www.sunspotworld.com

- 5. http://squawk.dev.java.net/

- Bræk, R., Haugen, Ø.: Engineering Real Time Systems: An Object-Oriented Methodology Using SDL. Prentice-Hall, Englewood Cliffs (1993)

- Kraemer, F.A., Herrmann, P., Bræk, R.: Aligning UML 2.0 state machines and temporal logic for the efficient execution of services. In: Meersman, R., Tari, Z. (eds.) DOA 2006. LNCS, vol. 4276, pp. 1612–1632. Springer, Heidelberg (2006)

- Bjerke, M.: Asynchronous Messaging between Embedded Java Devices. Project Thesis. Norwegian University of Science and Technology, Trondheim (December 2008)

- Merha, B.T.: Code Generation for Executable State Machines on Embedded Java Devices. Project Thesis. Norwegian University of Science and Technology, Trondheim (December 2008)

- Kraemer, F.A., Bræk, R., Herrmann, P.: Synthesizing Components with Sessions from Collaboration-Oriented Service Specifications. In: Gaudin, E., Najm, E., Reed, R. (eds.) SDL 2007. LNCS, vol. 4745, pp. 166–185. Springer, Heidelberg (2007)

- Kraemer, F.A., Herrmann, P.: Transforming Collaborative Service Specifications into Efficiently Executable State Machines. In: Ehring, K., Giese, H. (eds.) Proceedings of the 6th International Workshop on Graph Transformation and Visual Modeling Techniques (GT-VMT 2007). Electronic Communications of the EASST, vol. 7. EASST (2007)

- 12. Arseneau, E., Engelhardtsen, F.B.: Project playSIM: Experimenting with Java Card 3 System Programming. In: JavaOne (June 2009)

- Garg, V.K.: Elements of Distributed Computing. John Wiley & Sons, Inc., New York (2002)

- 14. Chandra, T.D., Toueg, S.: Unreliable Failure Detectors for Reliable Distributed Systems. Journal of the ACM 43(2), 225–267 (1996)

- Tanenbaum, A.S.: Distributed Systems: Principles and Paradigms. Prentice-Hall, New Jersey (2002)

- Kraemer, F.A., Slåtten, V., Herrmann, P.: Engineering Support for UML Activities by Automated Model-Checking — An Example. In: Proceedings of the 4th International Workshop on Rapid Integration of Software Engineering Techniques, RISE (2007)

- 17. Kraemer, F.A., Bræk, R., Herrmann, P.: Compositional Service Engineering with Arctis. Telektronikk 105(1) (2009)

- Kraemer, F.A.: Rapid Service Development for Service Frame. Master's thesis, University of Stuttgart (2003)

- 19. http://ksoap2.sourceforge.net/

- Bræk, R., Gorman, J., Haugen, Ø., Melby, G., Møller-Pedersen, B., Sanders, R.: Quality by Construction Exemplified by TIMe — The Integrated Methodology. Telektronikk 95(1), 73–82 (1997)

- Olsen, A., Færgemand, O., Møller-Pedersen, B., Reed, R., Smith, J.R.W.: Systems Engineering Using SDL-92, Chapter 6 Systems Engineering. Elsevier North-Holland, Inc., Amsterdam (1994)

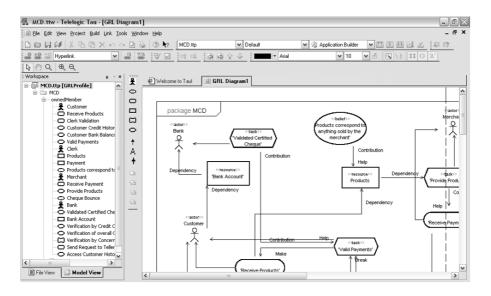

- 22. Telelogic: Tau 4.4 User's Manual. Malmö (2002)

- Kuhn, T., Gotzhein, R., Webel, C.: Model-Driven Development with SDL Process, Tools, and Experiences. In: Nierstrasz, O., Whittle, J., Harel, D., Reggio, G. (eds.) MoDELS 2006. LNCS, vol. 4199, pp. 83–97. Springer, Heidelberg (2006)

- 24. Selic, B., Gullekson, G., Ward, P.T.: Real-Time Object-Oriented Modeling. John Wiley & Sons, Inc., New York (1994)

- D'Souza, D.F., Wills, A.C.: Objects, Components, and Frameworks with UML: the Catalysis Approach. Addison-Wesley, Reading (1999)

- Reenskaug, T., Wold, P., Lehne, O.A.: Working with Objects, The OOram Software Engineering Method. Prentice-Hall, Englewood Cliffs (1995)

- Jarvinen, H., Kurki-Suonio, R., Sakkinen, M., Systa, K.: Object-Oriented Specification of Reactive Systems. In: Proceedings of the 12th International Conference on Software Engineering, pp. 63–71. IEEE Computer Society Press, Los Alamitos (1990)

- Fliege, I., Gotzhein, R.: Automated generation of micro protocol descriptions from SDL design specifications. In: Gaudin, E., Najm, E., Reed, R. (eds.) SDL 2007. LNCS, vol. 4745, pp. 150–165. Springer, Heidelberg (2007)

- Herrmann, P., Krumm, H.: A Framework for Modeling Transfer Protocols. Computer Networks 34(2), 317–337 (2000)

# Energy-Aware System Design with SDL<sup>\*</sup>

Reinhard Gotzhein<sup>1</sup>, Marc Krämer<sup>1</sup>, Lothar Litz<sup>2</sup>, and Alain Chamaken<sup>2</sup>

<sup>1</sup> Networked Systems Group University of Kaiserslautern, Germany {gotzhein,kraemer}@cs.uni-kl.de <sup>2</sup> Institute of Automatic Control University of Kaiserslautern, Germany {litz,chamaken}@eit.uni-kl.de

**Abstract.** Energy consumption is a major concern during the development of wireless networks consisting of battery-powered nodes. In this paper, we study possibilities of specifying energy aspects in the system design phase, with SDL as design language. In particular, we strive for suitable abstractions, by establishing a design view that is largely platform-independent. We achieve this objective by identifying and realizing *energy mode signaling* and *energy scheduling* as two complementary approaches to incorporate energy aspects into SDL. We provide details on how to apply these approaches in order to control the energy consumption of CPU and transceiver, and how to implement them on the Imote2 platform. A case study illustrates the use of both approaches in a wireless networked control system.

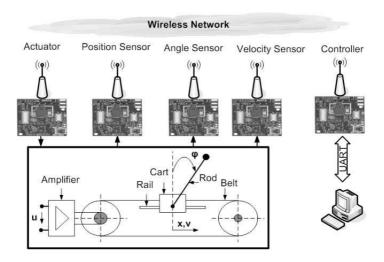

### 1 Introduction

In systems consisting of battery-powered nodes, energy consumption is a major concern, constraining the uptime of nodes and therefore of networks. Among these systems are wireless sensor networks [1], ad-hoc networks [2], and networked control systems [3]. As a general rule, energy consumption should be minimized. This can, for instance, be achieved by choosing low-power hardware platforms, such as micro controllers and motes, and by devising energy-efficient algorithms and protocols. Also, hardware components can be temporarily shut off or switched to an energy saving mode when not needed. Such techniques are being applied with great success to laptop computers and mobile phones.

When minimizing energy consumption, it is important that the application requirements are taken into consideration from the beginning. For instance, in a networked control system, consisting of a set of sensors, actuators, and a controller communicating over a wireless medium, the stability of the controlled system is of primary concern. Energy consumption must only be reduced if the system can still be kept sufficiently stable. This calls for a cross-layer design approach, addressing

<sup>\*</sup> This work is supported by the German Research Foundation (DFG) within the priority program SPP 1305 "Control Theory of Digitally Networked Dynamical Systems" under grants GO 503/8-1 and LI 724/15-1.

R. Reed, A. Bilgic, and R. Gotzhein (Eds.): SDL 2009, LNCS 5719, pp. 19-33, 2009.

energy aspects already in the early development phases. In this paper, we focus on the design phase, referred to as *energy-aware system design*.

In the design phase, modeling techniques such as SDL [4] or UML [5] are often used. With these techniques, design models can be specified on an abstract level, relieving the developer from implementation-specific details. The design view would typically exclude resource aspects such as memory size, CPU speed, transmission rates, and energy consumption. However, if these aspects are a major concern and part of the system requirements, then suitable abstractions that can be exploited to optimize resource usage must be included in the design. For instance, in order to minimize energy consumption, it should be possible to identify periods of inactivity at execution time, based on the system design. Also, it should be possible to explicitly control the energy modes of individual hardware components on design level.

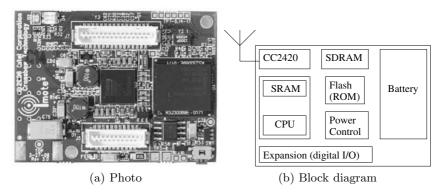

In this paper, we address energy-aware system design, with SDL as the design language. We examine the requirements of energy-aware design, and exploit existing language constructs of SDL for this purpose. Furthermore, we extend the implementation of the SDL virtual machine (SVM) in order to identify periods of inactivity and thereby reduce energy consumption. To further enhance energy-aware system design, we propose to exploit existing language constructs of SDL. Finally, we address implementation issues and provide a case study from the networked control systems domain to illustrate our findings. Our work uses the Imote2 platform **6** (see Fig. **1**).

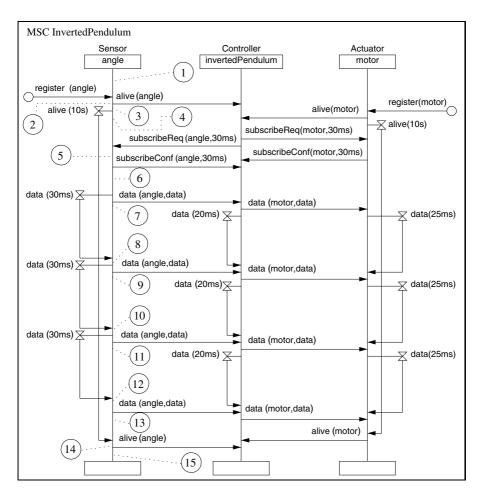

The paper is organized as follows: In Sect. 2, we survey related work. Section 3 introduces an energy model, which forms the basis for energy-aware design. In Sect. 4, we identify and realize two complementary approaches, called *energy mode signaling* and *energy scheduling*, to incorporate energy aspects into SDL. Section 5 shows how energy-aware design is implemented, by extending the SVM and SEnF, our SDL Environment Framework. Section 6 presents an excerpt of an inverted pendulum system, controlled over a wireless network. We draw conclusions in Sect. 7

Fig. 1. The Imote2 hardware platform

#### 2 Related Work

In the literature, a wealth of results on energy-aware systems and protocols has been reported. Practical system deployments are constrained by the available hardware components and energy sources. In [7], *battery models* for energy-aware system designs are considered. Benini et al. [8] give an overview of energy-aware designs of *embedded memories*. Current techniques to reduce the energy consumption of the CPU include *voltage scaling* [9]. An energy model of the *XScale platform* has been reported in [10].

To minimize the energy consumed by *transceivers*, a variety of energy-aware protocols have been devised. Among these are so-called duty cycling protocols on MAC level. Generally, the term *duty cycle* denotes the fraction of time a component (CPU, transceiver) or system is in an active state. If the traffic load of a network is below its capacity, it is possible to save energy by systematically switching transceivers to inactive mode. In the optimal case, a transceiver needs to be active only if it has to transmit or receive. The difficulty here is to determine this in advance. Several MAC protocols for duty cycling that attempt to approximate the optimal case have been reported, including S-MAC **11** and RMAC **12**. Similar considerations apply to routing in ad-hoc networks **13**.

The *formal specification* of energy aspects as part of the system design has received little attention so far. Mohsen et al. **14** present an integrated methodology and tool support for voltage scheduling and energy-aware co-synthesis of real-time systems. It is mentioned that SDL has been used as design language; however, no details are given in the paper.

It is certainly straightforward to specify the *functionality* of energy-aware duty-cycling or routing protocols in SDL. Compiling these designs using available tools (e.g. Cmicro **15**, ConTraST **16**) may even yield runtime-efficient code. However, without additional measures, this does not exploit the energy saving mechanisms of embedded platforms. Also, energy aspects are currently not incorporated into existing SDL runtime systems controlling the execution of code generated from SDL, nor are they made explicit in the SDL design.

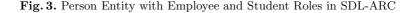

#### 3 Energy Model

To assess and minimize the energy consumption of a specific hardware platform, an *energy model* is needed. The energy model determines, for each hardware component, modes of operation, the energy consumed in each mode, and possible transitions between modes. Some of these transitions are triggered by the hardware itself. For instance, in case of a power fault due to a discharged battery, operation may be reduced to a minimum by switching to a deep sleep state, or even by switching off the entire node. This is usually done in a controlled fashion, i.e. outstanding memory transactions are completed, and volatile memory is placed in self-refresh mode or is saved to persistent memory. Other transitions between modes of operation may be accessible to the system programmer by setting a special power mode register, which provides the basis for the implementation of energy scheduling strategies. Based on the energy model, strategies for saving energy can be developed and evaluated. For instance, a CPU may be switched to idle mode or sleep mode during inactive periods. Also, a transceiver may be switched off between active phases of a duty cycle. As a general rule, the mode consuming the least energy should be chosen when components are temporarily not used. However, when changing a mode, the duration and power consumption to return to full activity must be considered. For instance, to switch from sleep mode to active mode may take considerably longer than from idle mode to active mode, as more hardware units have to be powered on. Which mode to choose therefore depends on the required reaction time and the total energy balance.

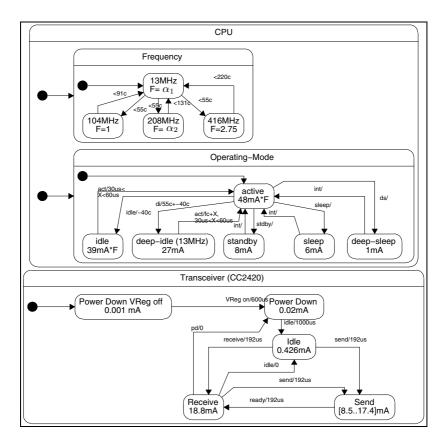

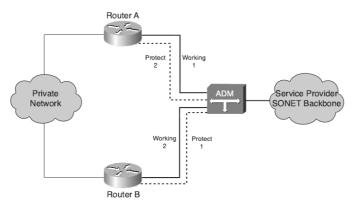

Figure 2 shows an excerpt of our energy model for the Imote2 platform: the upper part shows the CPU model; the lower part shows the transceiver model. The modes and transitions of the CPU model are documented in the Intel PXA27x Processor Family Developer's Manual 17. Values for energy consumption are taken from 18. The CC2420 data sheet 19 is used for the transceiver.

The CPU energy model is decomposed into two transition systems, representing mode of operation and CPU speed (frequency). In total, 6 modes of operation

Fig. 2. Energy model of the Imote2

are distinguished, with power consumption ranging from 132 mA in active mode to 1 mA in deep sleep mode. In active and idle mode, power consumption also depends on the current CPU speed, which is expressed by the factor F. By frequency scheduling, the CPU speed may be adapted to the current task situation. There are 4 different speeds, ranging from 13 MHz up to 416 MHz. The (normal) speed of 104 MHz is the basis for energy calculations, therefore, F = 1. Transition durations are given in clock cycles. Note that some values are not reported in the available literature and therefore omitted.

The transceiver energy model shows 4 modes of operation and an intermediate mode during initialization. Interestingly, receiving consumes more energy than sending, which is typical for low power transmitters and must be considered by duty cycling protocols. Transition durations are given in s. When not needed, the transceiver may be switched to idle mode or even to power down mode, if the additional delay of 1000s to activate the transceiver can be granted.

#### 4 Specifying Energy Control Aspects with SDL

In this section, we present our methodology for energy-aware system design with SDL. We assume the existence of an energy model, as discussed in Sect. In Sect. Multi we introduce two conceptual approaches to incorporate energy aspects into SDL. We then apply these approaches to reduce energy consumption of CPU and transceiver in Sect. Multi and Sect. Multi can be achieved in an intuitive, conceptually clean way on a level of abstraction that is entirely adequate for SDL designs.

#### 4.1 Energy Mode Signaling and Energy Scheduling

To incorporate energy aspects into SDL, we have identified two complementary conceptual approaches. The first approach, called *energy mode signaling*, requires that the system developer specifies transitions of the energy model as part of the SDL design. In other words, transitions between modes of operation and thus the energy consumption of individual hardware components are controlled *explicitly*. This can be done, for instance, by sending special SDL signals to the environment, or by using special SDL procedures. In both cases, a specific treatment during system implementation is required to map energy mode signaling to the native operating system, and finally to the hardware platform. This treatment is different from the exchange of regular SDL signals with the environment, which are addressed to other processes of the local node or remote nodes. To distinguish between these cases, we apply naming conventions.

The second approach, called *energy scheduling*, incorporates additional functionality into the implementation of the *SDL Virtual Machine* (*SVM*) [20]. The SVM is the core of the SDL formal semantics [21] and provides typical operating system functionality on top of a logical hardware called *SDL Abstract Machine* (*SAM*). It controls the dynamic system architecture, the activity of SDL processes at runtime, the selection of transitions, and their firing. The additional functionality consists, for each hardware component, of an energy scheduler, which is responsible for triggering transitions of the energy model. The energy scheduler uses state information available to the SVM in order to determine when the mode of operation is to be changed. To derive this information, signal queues and active SDL timers are inspected. As this does not require modifications of the SDL design, energy scheduling is an *implicit* approach to controlling energy consumption.

Energy mode signaling and energy scheduling both have limitations. With energy mode signaling, the decision about changing the energy mode of a hardware component has to be based on information available to the SDL process executing the corresponding SDL action. In particular, this means that global conditions such as "currently no fireable transitions in the SDL system" cannot be used to switch the CPU to sleep mode. Furthermore, it means that the duration of the sleep period cannot be determined from the global set of active SDL timers. However, both kinds of information are available to the SVM, and can be used for energy scheduling, i.e. for implicit energy control. On the other hand, energy scheduling cannot determine, for instance, duty cycles of the transceiver from the current state of the SDL system. Duty cycles can be applied by using energy mode signaling to explicitly switch the transceiver between modes of operation based on SDL timers. In summary, we observe that energy mode signaling and energy scheduling are complementary and therefore should be applied together.

#### 4.2 Controlling Energy Consumption of the CPU

In this section, we study how to apply energy mode signaling and energy scheduling in SDL in order to control the energy consumption of the CPU. Recall that *energy mode signaling* requires explicit action: the specification of SDL actions changing the mode of operation. For these actions to be executed, the CPU is required and therefore has to be in active mode (see Fig. 2). For the CPU, the following two cases can be considered:

CPU frequency signaling. Here, the designer adapts CPU speed to control energy consumption, thereby scaling system performance up or down. For this purpose, he defines a frequency scheduling strategy and uses energy mode signaling to switch between frequency modes. For instance, in case of the Imote2 energy model (see Fig. 2), switching between 13 MHz, 104 MHz, 208 MHz, and 416 MHz is possible. To signal frequency modes in SDL, we define a special SDL signal CPU\_FREQ\_MODE, which carries the frequency as parameter (see List. 11 Line 5). A specific frequency mode can then be signaled by sending CPU\_FREQ\_MODE to the environment (Line 7), where it is mapped to the native operating system.

*CPU operation signaling.* The designer switches the CPU from active mode to inactive mode for a specified period of time. For this purpose, he defines a duty cycling strategy for the CPU and uses energy mode signaling to switch to a

Listing 1. SDL excerpt: CPU frequency signaling in SDL

```

syntype CPU_Frequency = Integer

constants 13, 104, 208, 416

sendsyntype

signal CPU_FREQ_MODE (CPU_Frequency);

output CPU_FREQ_MODE (104);

```

particular inactive mode. For instance, in case of the Imote2 energy model (see Fig. 2), idle, standby, and sleep are inactive modes. Our SDL solution is analogous to CPU frequency signaling, and is shown in List. 4.2. Note that after the signal CPU\_OP\_MODE is sent (Line 7), the execution of the current SDL transition is suspended. It will be resumed after the CPU is switched back to active mode, triggered by a hardware timer expiring after the specified duration (since SDL timers are not available in inactive mode).

Listing 2. SDL excerpt: CPU operation signaling in SDL

```

1 newtype CPU_Operation

2 literals active, idle, deepIdle, standby, sleep, deepSleep;

3 endnewtype

4

5 signal CPU_OP_MODE (CPU_Operation, Duration);

6

7 output CPU_OP_MODE (idle, 0.01);

```

Next, we consider *energy scheduling*, which is achieved by incorporating additional functionality into the implementation of the SDL Virtual Machine (SVM) (cf. Sect. [4.1]). For this, a scheduling strategy that is based on state information available to the SVM is to be devised. For the exposition, we assume that in the SVM implementation, transition selection for all agents of a node is done in a centralized manner, and that there are separate queues signalQueue and timerQueue for SDL signals and active SDL timers, respectively.

Listing is shows the CPU energy scheduler, written in pseudo code. It uses the SDL transition scheduler selectTransition, the transition handler fireTransition, and the timer routine selectNextExpiringTimer. If no transition is currently enabled, the scheduler searches the timer queue for the next expiring timer. If an active timer is found, the CPU is switched to sleep mode until either the timer expires, or an external interrupt occurs. Otherwise, the sleep time is eventually terminated by an external interrupt, which may e.g. be triggered by the environment of the SDL system when the transceiver receives a message.

It should be noted that the use of the SDL energy scheduler requires certain stylistic restrictions. First, we rule out the use of now in continuous signals, such as in the condition (t>now). Instead, SDL timers should be used in this case. Second, we either disallow spontaneous transitions, or assume that they are never enabled when the CPU is in inactive mode.

Listing 3. CPU energy scheduler

```

while (running) do

1

selectTransition

2

if

(transitionFound) then

3

fireTransition

4

else

5

selectNextExpiringTimer in timerQueue

6

if (timerFound) then

7

sleep until (timer expires or interrupt occurs)

8

else

q

sleep until (interrupt occurs)

10

fi

11

fi

12

13 od

```

#### 4.3 Controlling Energy Consumption of the Transceiver

In this section, we study how to apply energy mode signaling and energy scheduling in SDL in order to control the energy consumption of the transceiver. As energy mode signaling requires explicitly specified SDL actions to be executed at runtime, the CPU has to be in active mode. Since the energy model of the CC2420 transceiver has only modes of operation (see Fig. 2), it suffices to support transceiver operation signaling. Based on some duty cycling strategy, the transceiver is switched between active and inactive modes. For this purpose, we introduce a special SDL signal CC2420\_OP\_MODE (see List. 4), which carries the mode of operation as parameter. A specific mode of operation can then be signaled by sending CC2420\_OP\_MODE to the environment (Line 7), where it is mapped to the transceiver hardware. Note that the send mode is only signaled implicitly, i.e. when a frame is to be transmitted, and therefore omitted in the type definition CC2420\_OP\_ention.

Listing 4. SDL excerpt: transceiver operation signaling in SDL

```

1 newtype CC2420_Operation

2 literals powerDown, idle, receive;

3 endnewtype

4

5 signal CC2420_OP_MODE (CC2420_Operation);

6

7 output CC2420_OP_MODE (powerDown);

```

Compared to the CPU, the transceiver's potential for *energy scheduling* is rather limited. Recall that we have defined energy scheduling to be an implicit approach, relying on state information available to the SVM only. As we want to have explicit control over the transceivers inactive states, the only leeway for energy scheduling is the transition to send mode, which is implicitly signaled when a frame is transmitted. Thus, no further scheduling strategy needs to be devised and incorporated into the SVM.

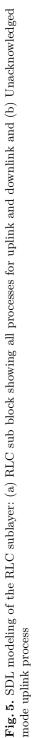

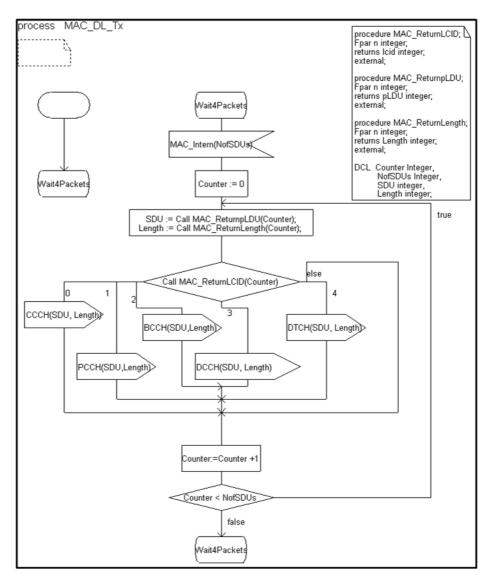

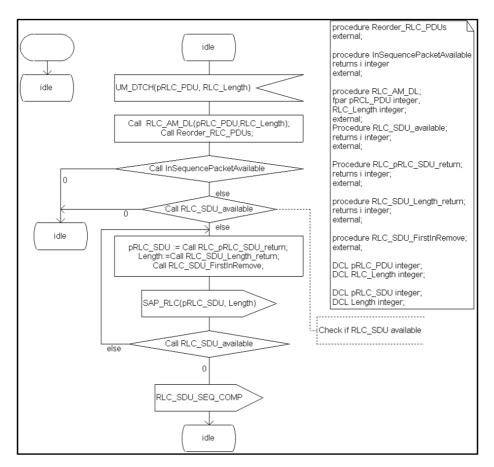

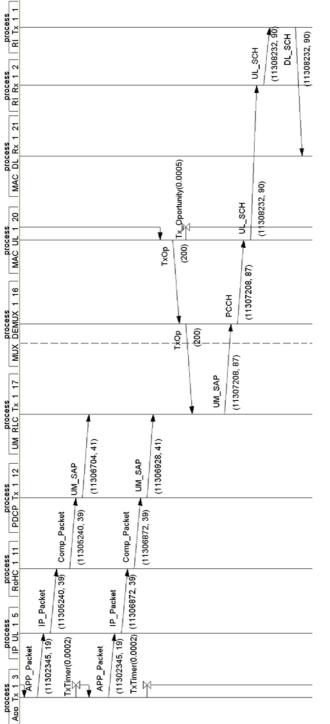

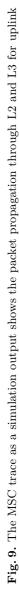

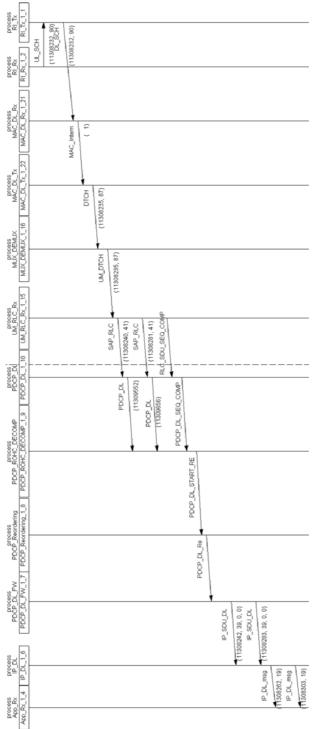

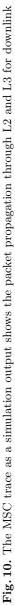

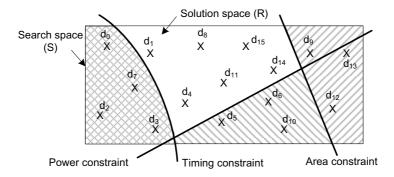

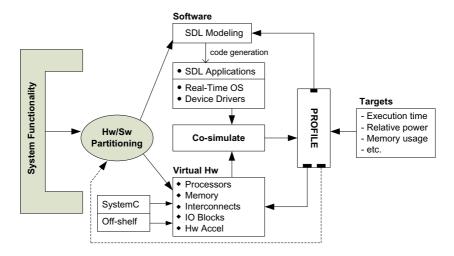

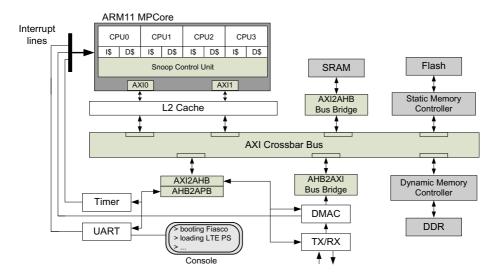

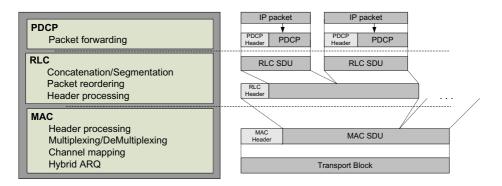

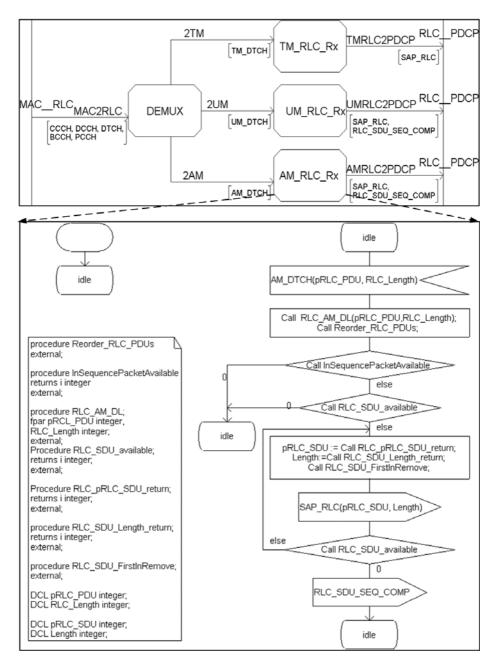

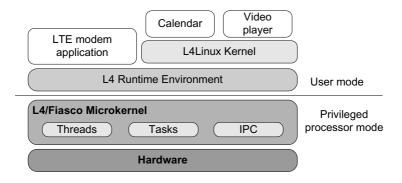

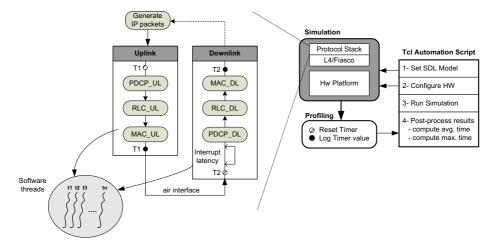

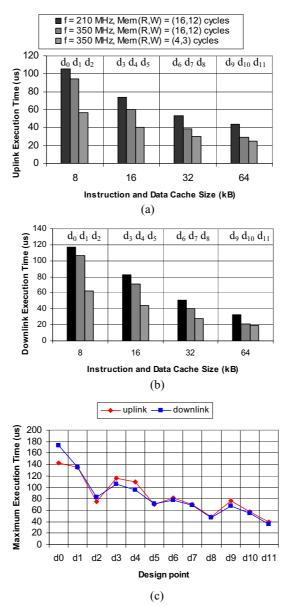

# 5 Implementation of Energy Control Aspects