# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Christophe Clavier Kris Gaj (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2009

11th International Workshop Lausanne, Switzerland, September 6-9, 2009 Proceedings

Volume Editors

Christophe Clavier Université de Limoges Département de Mathématiques et d'Informatique 83 rue d'Isle, 87000 Limoges, France E-mail: christophe.clavier@unilim.fr and Institut d'Ingénierie Informatique de Limoges (3iL) 42 rue Sainte Anne, 87000 Limoges, France E-mail: christophe.clavier@3il.fr

Kris Gaj George Mason University Department of Electrical and Computer Engineering Fairfax, VA 22030, USA E-mail: kgaj@gmu.edu

#### Library of Congress Control Number: 2009933191

CR Subject Classification (1998): E.3, D.4.6, K.6.5, E.4, C.2, H.2.7

LNCS Sublibrary: SL 4 – Security and Cryptology

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-642-04137-X Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-642-04137-2 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### springer.com

© International Association for Cryptologic Research 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12753017 06/3180 5 4 3 2 1 0

## Preface

CHES 2009, the 11th workshop on Cryptographic Hardware and Embedded Systems, was held in Lausanne, Switzerland, September 6–9, 2009. The workshop was sponsored by the International Association for Cryptologic Research (IACR).

The workshop attracted a record number of 148 submissions from 29 countries, of which the Program Committee selected 29 for publication in the workshop proceedings, resulting in an acceptance rate of 19.6%, the lowest in the history of CHES. The review process followed strict standards: each paper received at least four reviews, and some as many as eight reviews. Members of the Program Committee were restricted to co-authoring at most two submissions, and their papers were evaluated by an extended number of reviewers.

The Program Committee included 53 members representing 20 countries and five continents. These members were carefully selected to represent academia, industry, and government, as well as to include world-class experts in various research fields of interest to CHES. The Program Committee was supported by 148 external reviewers. The total number of people contributing to the review process, including Program Committee members, external reviewers, and Program Co-chairs, exceeded 200.

The papers collected in this volume represent cutting-edge worldwide research in the rapidly growing and evolving area of cryptographic engineering. The submissions were sought in several general areas, including, but not limited to, cryptographic hardware, cryptographic software, attacks against implementations and countermeasures against these attacks, tools and methodologies of cryptographic engineering, and applications and implementation environments of cryptographic systems. Ten years after its first workshop, CHES is now very firmly established as the premier international forum for presenting scientific and technological advances in cryptographic engineering research, the event that bridges the gap between theoretical advances and their practical application in commercial products.

In order to further extend the scope of CHES, this year's CHES included for the first time a special Hot Topic Session. The goal of this session was to attract new authors and attendees to CHES by highlighting a new area, not represented at CHES before, but of potential interest to CHES participants. The topic of this year's Hot Topic Session was: Hardware Trojans and Trusted ICs. The session was chaired by Anand Raghunathan from Purdue University, USA, who prepared a separate call for papers, and oversaw an evaluation of papers submitted to this session. This evaluation was supported by a special Hot Topic Session Committee, composed of six experts in the field of trusted integrated circuit manufacturing. The session included two regular presentations, and an invited talk, entitled "The State-of-the-Art in IC Reverse Engineering," delivered by Randy Torrance from Chipworks, Inc., Canada.

Additionally, the workshop included two other excellent invited talks. Christof Paar from Ruhr-Universität Bochum, one of the two founders of CHES, discussed his vision of cryptographic engineering, and its evolution over years, in a talk entitled "Crypto Engineering: Some History and Some Case Studies." Srini Devadas, MIT, an inventor of PUF (Physical Unclonable Function), and a founder of a company that develops practical products based on this new technology, described his experiences in a talk entitled "Physical Unclonable Functions and Secure Processors."

The workshop also included two special sessions. Elisabeth Oswald chaired a session on the DPA contest, which included an introduction and discussion of the contest by one of the primary contest organizers, Sylvain Guilley from Telecom ParisTech. Following the introduction was a short presentation by the winners of the contest and a panel discussion devoted to the current and future rules of the contest and the ethical issues associated with inadvertently facilitating through the contest practical attacks against implementations of cryptography. The second special session, chaired by Patrick Schaumont from Virginia Tech, was on benchmarking of cryptographic hardware. The session included several interesting short talks on problems and solutions related to fair and comprehensive evaluation of the performance of cryptographic hardware. This session was of particular significance in light of the ongoing evaluation of the SHA-3 candidates competing to become a new American, and a de-facto worldwide, hash function standard. Additionally, the workshop included two traditional events: a rump session, chaired by Guido Bertoni from STMicroelectronics, Italy, and a poster session chaired by Stefan Mangard, Infineon Technologies, Germany. Our great thanks go to all Special Session Chairs for their initiative, enthusiasm, commitment, innovative spirit, and attention to every detail of their respective sessions.

Through a nomination process and a vote, the Program Committee awarded three CHES 2009 Best Paper Awards. The selected papers represent three distinct areas of cryptographic engineering research: efficient hardware implementations of public key cryptography, efficient and secure software implementations of secret key cryptography, and side-channel attacks and countermeasures. The winners of the three equivalent awards were: Jean-Luc Beuchat, Jérémie Detrey, Nicolas Estibals, Eiji Okamoto, and Francisco Rodríguez-Henríquez for their paper "Hardware Accelerator for the Tate Pairing in Characteristic Three Based on Karatsuba-Ofman Multipliers," Emilia Käsper and Peter Schwabe for their paper "Faster and Timing-Attack Resistant AES-GCM," and Thomas Finke, Max Gebhardt, and Werner Schindler for their paper "A New Side-Channel Attack on RSA Prime Generation."

The selection of 29 best papers out of 148 predominantly very strong submissions was a very challenging and difficult task. The Program Committee members dedicated a very significant amount of time and effort in order to comprehensively and fairly evaluate all submitted papers and provide useful feedback to the authors. Our deepest thanks go to the members of the Program Committee for their hard work, expertise, dedication, professionalism, fairness, and team spirit.

We deeply thank Marcelo Kaihara, the General Chair of CHES 2009, for his excellent and always timely work on managing the local organization and orchestrating conference logistics. Only because of his tireless effort, flexibility, and team spirit were we able to fit so many additional events and special sessions in the program of this year's CHES. We would like to also thank EPFL for providing an excellent venue for holding the workshop, and for assisting with many local arrangements. Our gratitude also goes to the generous sponsors of CHES 2009, namely, Cryptography Research, Inc., Nagravision Kudelski Group, Oberthur Technologies, RCIS AIST Japan, Riscure, and Telecom ParisTech.

We are also very grateful to Çetin Kaya Koç for managing conference announcements and advertising as the Publicity Chair, and to Jens-Peter Kaps for diligently maintaining the CHES website. The review and discussion process was run using an excellent Web Submission and Review System developed and maintained by Shai Halevi, who was always very quick and precise in addressing our questions and concerns regarding the operation of the system.

We would like to deeply thank the Steering Committee of CHES, for their trust, constant support, guidance, and kind advice on many occasions. Special thanks go to Jean-Jacques Quisquater and Colin Walter, who were always first to respond to our questions and concerns, and often volunteered the advice and support needed to resolve a wide array of challenging issues associated with the fair, firm, and transparent management of the evaluation process.

Finally, we would like to profoundly thank and salute all the authors from all over the world who submitted their papers to this workshop, and entrusted us with a fair and objective evaluation of their work. We appreciate your creativity, hard work, and commitment to push forward the frontiers of science. All your submissions, no matter whether accepted or rejected at this year's CHES, represent the vibrant field of research that CHES is proud to exemplify.

September 2009

Christophe Clavier Kris Gaj

# **CHES 2009**

Workshop on Cryptographic Hardware and Embedded Systems Lausanne, Switzerland, September 6–9, 2009

Sponsored by International Association for Cryptologic Research

## **General Chair**

## **Program Co-chairs**

| Christophe Clavier | Université de Limoges, France |

|--------------------|-------------------------------|

| Kris Gaj           | George Mason University, USA  |

## **Publicity Chair**

| Çetin Kaya Koç | University of California Santa Barbara, U | JSA |

|----------------|-------------------------------------------|-----|

|----------------|-------------------------------------------|-----|

## **Program Committee**

| Lejla Batina<br>Daniel J. Bernstein<br>Guido Bertoni<br>Jean-Luc Beuchat | Katholieke Universiteit Leuven, Belgium<br>University of Illinois at Chicago, USA<br>STMicroelectronics, Italy<br>University of Tsukuba, Japan |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Luca Breveglieri                                                         | Politecnico di Milano, Italy                                                                                                                   |

| Ernie Brickell                                                           | Intel, USA                                                                                                                                     |

| Dipanwita Roy                                                            |                                                                                                                                                |

| Chowdhury                                                                | Indian Institute of Technology, Kharagpur,<br>India                                                                                            |

| Jean-Sébastien Coron                                                     | University of Luxembourg, Luxembourg                                                                                                           |

| Joan Daemen                                                              | STMicroelectronics, Belgium                                                                                                                    |

| Ricardo Dahab                                                            | University of Campinas, Brazil                                                                                                                 |

| Markus Dichtl                                                            | Siemens AG, Germany                                                                                                                            |

| Benoît Feix                                                              | Inside Contactless, France                                                                                                                     |

| Viktor Fischer                                                           | Université de Saint-Étienne, France                                                                                                            |

| Pierre-Alain Fouque                                                      | ENS, France                                                                                                                                    |

| Catherine H. Gebotys                                                     | University of Waterloo, Canada                                                                                                                 |

| Christophe Giraud                                                        | Oberthur Technologies, France                                                                                                                  |

Louis Goubin Université de Versailles, France Jorge Guajardo Philips Research Europe, The Netherlands Frank K. Gürkaynak ETH Zurich, Switzerland Peter Gutmann University of Auckland, New Zealand Helena Handschuh Katholieke Universiteit Leuven, Belgium Naofumi Homma Tohoku University, Japan Josh Jaffe Cryptography Research, USA Marc Joye Thomson R&D, France Jens-Peter Kaps George Mason University, USA Pusan National University, South Korea Howon Kim Çetin Kaya Koç University of California Santa Barbara, USA Markus Kuhn University of Cambridge, UK Soonhak Kwon Sungkyunkwan University, South Korea Kerstin Lemke-Rust University of Applied Sciences Bonn-Rhein-Sieg, Germany Marco Macchetti Nagracard SA, Switzerland Stefan Mangard Infineon Technologies, Germany Liam Marnane University College Cork, Ireland Mitsuru Matsui Mitsubishi Electric, Japan David Naccache ENS. France Dag Arne Osvik EPFL, Switzerland Elisabeth Oswald University of Bristol, UK Christof Paar Ruhr-Universität Bochum, Germany Dan Page University of Bristol, UK Gemalto, France Pascal Paillier Jean-Jacques Quisquater Université catholique de Louvain, Belgium Francisco Rodríguez-Henríquez CINVESTAV-IPN, Mexico IBM T.J. Watson Research Center, USA Pankaj Rohatgi Erkay Savas Sabanci University, Turkey Patrick Schaumont Virginia Tech, USA Florida Atlantic University, USA Rainer Steinwandt Berk Sunar Worcester Polytechnic Institute, USA Elena Trichina STMicroelectronics, France Colin Walter Royal Holloway, UK Michael J. Wiener Cryptographic Clarity, Canada Johannes Wolkerstorfer IAIK TU Graz, Austria Sung-Ming Yen National Central University, Taiwan

## Program Committee Advisory Member

| François-Xavier |                                           |

|-----------------|-------------------------------------------|

| Standaert       | Université catholique de Louvain, Belgium |

## Hot Topic Session Committee

| Anand Raghunathan  |                                      |

|--------------------|--------------------------------------|

| (Chair)            | Purdue University, USA               |

| Farinaz Koushanfar | Rice University, USA                 |

| Jim Plusquellic    | University of New Mexico, USA        |

| Pankaj Rohatgi     | IBM T.J. Watson Research Center, USA |

| Patrick Schaumont  | Virginia Tech, USA                   |

| Berk Sunar         | Worcester Polytechnic Institute, USA |

|                    |                                      |

Guerric Meurice

## **External Reviewers**

**Onur** Aciicmez Guido Costa Souza de Araújo Kubilav Atasu Alain Aubert Maxime Augier Jean-Claude Bajard Brian Baldwin Alessandro Barenghi Florent Bernard Alex Birvukov Andrey Bogdanov Simone Borri Joppe Bos Arnaud Boscher Lilian Bossuet Nicolas Brisebarre Marco Bucci Philippe Bulens Anne Canteaut Nathalie Casati Mathieu Chartier Sanjit Chatterjee Chien-Ning Chen Zhimin Chen Ray Cheung Fred Chong Baudoin Collard René Cumplido Jean-Luc Danger Pascal Delaunay Elke De Mulder Jérémie Detrey

de Dormale Emmanuelle Dottax Saar Drimer Milos Drutarovsky Sylvain Duquesne Thomas Eisenbarth Nicolas Estibals Martin Feldhofer Wieland Fischer Georges Gagnerot Berndt Gammel Pierrick Gaudry Willi Geiselmann Benedikt Gierlichs Guy Gogniat Michael Gora Aline Gouget Johann Großschädl Svlvain Guillet Eric Xu Guo Ghaith Hammouri Dong-Guk Han Neil Hanley Guillaume Hanrot Christoph Herbst Clemens Heuberger Michael Hutter Laurent Imbert Sevvd Hasan Mir Jalili Pascal Junod Marcelo Kaihara Deniz Karakoyunlu

Markus Kasper Chang Hoon Kim Chong Hee Kim Minkvu Kim Mario Kirschbaum Ilya Kizhvatov Thorsten Kleinjung Heiko Knospe Sandeep S. Kumar Yun-Ki Kwon Tanja Lange Cédric Lauradoux Hee Jung Lee Arjen K. Lenstra Gaëtan Leurent Yann L'Hvver Wei-Chih Lien Feng-Hao Liu Pierre Loidreau Raimondo Luzzi François Mace Abhranil Maiti Theo Markettos Marcel Medwed Filippo Melzani Nele Mentens Giacomo de Meulenaer Bernd Meyer Atsushi Miyamoto Amir Moradi Csaba Andras Moritz Sergev Morozov Andrew Moss

Debdeep Mukhopadhyay David Oswald Siddika Berna Ors Yalcin Young-Ho Park Hervé Pelletier Gerardo Pelosi Christophe Petit Gilles Piret Thomas Plos Thomas Popp Axel Poschmann Bart Preneel Emmanuel Prouff Carine Raynaud Francesco Regazzoni Mathieu Renauld Matthieu Rivain Bruno Robisson

Mylène Roussellet Christian Rust Akashi Satoh Werner Schindler Jörn-Marc Schmidt Michael Scott Christian Scwarz Hermann Seuschek Chang Shu Hervé Sibert Sergei Skorobogatov Takeshi Sugawara Ruggero Susella Daisuke Suzuki Yannick Teglia Nicolas Thériault Hugues Thiebeauld Stefan Tillich

Kris Tiri Arnaud Tisserand Lionel Torres Michael Tunstall Jonny Valamehr Gilles Van Assche Jérôme Vasseur Ihor Vasyltsov Vincent Verneuil Nicolas Vevrat-Charvillon Karine Villegas Hassan Wassel Christopher Wolf Tugrul Yanik Yu Yu

# Table of Contents

# Software Implementations

Martin Hlaváč

| Faster and Timing-Attack Resistant AES-GCM<br>Emilia Käsper and Peter Schwabe                                                                                                                                 | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Accelerating AES with Vector Permute Instructions<br>Mike Hamburg                                                                                                                                             | 18  |

| SSE Implementation of Multivariate PKCs on Modern x86 CPUs<br>Anna Inn-Tung Chen, Ming-Shing Chen, Tien-Ren Chen,<br>Chen-Mou Cheng, Jintai Ding, Eric Li-Hsiang Kuo,<br>Frost Yu-Shuang Lee, and Bo-Yin Yang | 33  |

| MicroEliece: McEliece for Embedded Devices<br>Thomas Eisenbarth, Tim Güneysu, Stefan Heyse, and Christof Paar                                                                                                 | 49  |

| Invited Talk 1                                                                                                                                                                                                |     |

| Physical Unclonable Functions and Secure Processors<br>Srini Devadas                                                                                                                                          | 65  |

| Side Channel Analysis of Secret Key Cryptosystems                                                                                                                                                             |     |

| Practical Electromagnetic Template Attack on HMAC<br>Pierre-Alain Fouque, Gaëtan Leurent, Denis Réal, and<br>Frédéric Valette                                                                                 | 66  |

| First-Order Side-Channel Attacks on the Permutation Tables                                                                                                                                                    | 01  |

| Countermeasure<br>Emmanuel Prouff and Robert McEvoy                                                                                                                                                           | 81  |

| Algebraic Side-Channel Attacks on the AES: Why Time also Matters<br>in DPA<br>Mathieu Renauld, François-Xavier Standaert, and<br>Nicolas Veyrat-Charvillon                                                    | 97  |

| Differential Cluster Analysis<br>Lejla Batina, Benedikt Gierlichs, and Kerstin Lemke-Rust                                                                                                                     | 112 |

| Side Channel Analysis of Public Key Cryptosystems                                                                                                                                                             |     |

| Known–Plaintext–Only Attack on RSA–CRT with Montgomery<br>Multiplication                                                                                                                                      | 128 |

| A New Side-Channel Attack on RSA Prime Generation | . 141 |

|---------------------------------------------------|-------|

| Thomas Finke, Max Gebhardt, and Werner Schindler  |       |

## Side Channel and Fault Analysis Countermeasures

| An Efficient Method for Random Delay Generation in Embedded<br>Software                                                                                                                                                                         | 156 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Higher-Order Masking and Shuffling for Software Implementations of<br>Block Ciphers                                                                                                                                                             | 171 |

| A Design Methodology for a DPA-Resistant Cryptographic LSI with<br>RSL Techniques                                                                                                                                                               | 189 |

| A Design Flow and Evaluation Framework for DPA-Resistant<br>Instruction Set Extensions<br>Francesco Regazzoni, Alessandro Cevrero,<br>François-Xavier Standaert, Stephane Badel, Theo Kluter,<br>Philip Brisk, Yusuf Leblebici, and Paolo Ienne | 205 |

## Invited Talk 2

| Crypto Engineering: Some History and Some Case Studies |     |

|--------------------------------------------------------|-----|

| (Extended Abstract)                                    | 220 |

| Christof Paar                                          |     |

# Pairing-Based Cryptography

| 0                          | <b>JI</b> 0               |                     | v             |                                                                                |     |

|----------------------------|---------------------------|---------------------|---------------|--------------------------------------------------------------------------------|-----|

|                            | fman Mu<br><i>Jérémie</i> | ltipl<br><i>Det</i> | iers<br>trey, |                                                                                | 225 |

| Curves                     |                           |                     |               | Pairings on Barreto-Naehrig<br>and Ingrid Verbauwhede                          | 240 |

| Curves<br>David Kammler, I | Diandian<br>ter, Mark     | <br>Zhai<br>rus 1   | ng,<br>Lang   | Pairings over Barreto-Naehrig<br><br>Peter Schwabe,<br>penberg, Dominik Auras, | 254 |

## New Ciphers and Efficient Implementations

| KATAN and KTANTAN — A Family of Small and Efficient<br>Hardware-Oriented Block Ciphers<br>Christophe De Cannière, Orr Dunkelman, and Miroslav Knežević                  | 272 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Programmable and Parallel ECC Coprocessor Architecture: Tradeoffs<br>between Area, Speed and Security<br>Xu Guo, Junfeng Fan, Patrick Schaumont, and Ingrid Verbauwhede | 289 |

| Elliptic Curve Scalar Multiplication Combining Yao's Algorithm and<br>Double Bases<br>Nicolas Méloni and M. Anwar Hasan                                                 | 304 |

## **TRNGs and Device Identification**

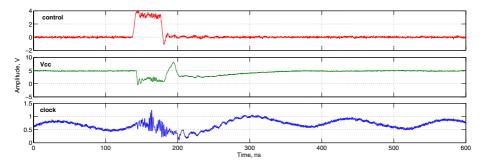

| The Frequency Injection Attack on Ring-Oscillator-Based True Random<br>Number Generators                                                     | 317 |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Low-Overhead Implementation of a Soft Decision Helper Data<br>Algorithm for SRAM PUFs<br><i>Roel Maes, Pim Tuyls, and Ingrid Verbauwhede</i> | 332 |

| CDs Have Fingerprints Too<br>Ghaith Hammouri, Aykutlu Dana, and Berk Sunar                                                                   | 348 |

## Invited Talk 3

| The State-of-the-Art in IC Reverse Engineering | 363 |

|------------------------------------------------|-----|

| Randy Torrance and Dick James                  |     |

## Hot Topic Session: Hardware Trojans and Trusted ICs

| Trojan Side-Channels: Lightweight Hardware Trojans through |     |

|------------------------------------------------------------|-----|

| Side-Channel Engineering                                   | 382 |

| Lang Lin, Markus Kasper, Tim Güneysu, Christof Paar, and   |     |

| Wayne Burleson                                             |     |

| MERO: A Statistical Approach for Hardware Trojan Detection | 396 |

| Rajat Subhra Chakraborty, Francis Wolff, Somnath Paul,     |     |

| Christos Papachristou, and Swarup Bhunia                   |     |

## **Theoretical Aspects**

| On Tamper-Resistance from a Theoretical Viewpoint: The Power of |     |

|-----------------------------------------------------------------|-----|

| Seals                                                           | 411 |

| Paulo Mateus and Serge Vaudenay                                 |     |

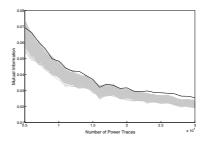

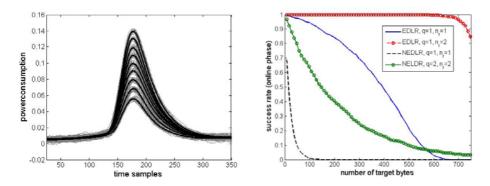

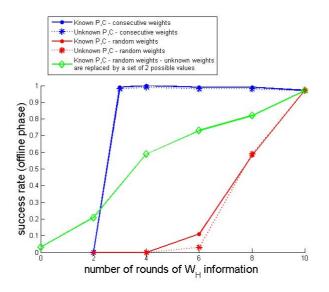

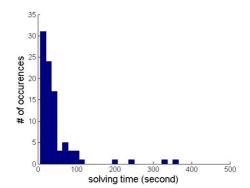

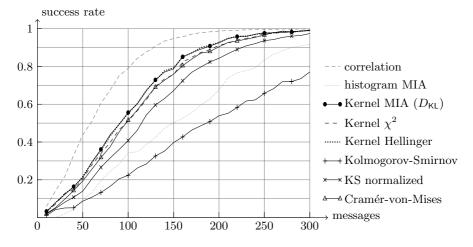

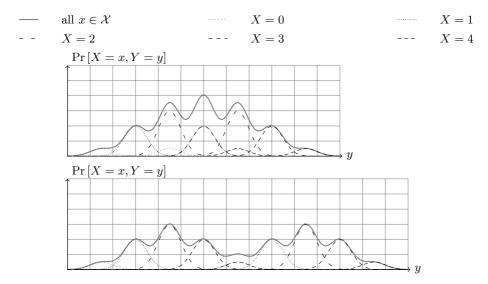

| Mutual Information Analysis: How, When and Why?         | 429 |

|---------------------------------------------------------|-----|

| Nicolas Veyrat-Charvillon and François-Xavier Standaert |     |

# Fault Analysis

| Fault Attacks on RSA Signatures with Partially Unknown Messages<br>Jean-Sébastien Coron, Antoine Joux, Ilya Kizhvatov,<br>David Naccache, and Pascal Paillier | 444 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Differential Fault Analysis on DES Middle Rounds<br>Matthieu Rivain                                                                                           | 457 |

| Author Index                                                                                                                                                  | 471 |

# Faster and Timing-Attack Resistant AES-GCM

Emilia Kä<br/>sper  $^1$  and Peter Schwabe  $^{2,\star}$

<sup>1</sup> Katholieke Universiteit Leuven, ESAT/COSIC Kasteelpark Arenberg 10, B-3001 Leuven-Heverlee, Belgium emilia.kasper@esat.kuleuven.be <sup>2</sup> Department of Mathematics and Computer Science Technische Universiteit Eindhoven, P.O. Box 513, 5600 MB Eindhoven, Netherlands peter@cryptojedi.org

Abstract. We present a bitsliced implementation of AES encryption in counter mode for 64-bit Intel processors. Running at 7.59 cycles/byte on a Core 2, it is up to 25% faster than previous implementations, while simultaneously offering protection against timing attacks. In particular, it is the only cache-timing-attack resistant implementation offering competitive speeds for stream as well as for packet encryption: for 576-byte packets, we improve performance over previous bitsliced implementations by more than a factor of 2. We also report more than 30% improved speeds for lookup-table based Galois/Counter mode authentication, achieving 10.68 cycles/byte for authenticated encryption. Furthermore, we present the first constant-time implementation of AES-GCM that has a reasonable speed of 21.99 cycles/byte, thus offering a full suite of timing-analysis resistant software for authenticated encryption.

**Keywords:** AES, Galois/Counter mode, cache-timing attacks, fast implementations.

## 1 Introduction

While the AES cipher has withstood years of scrutiny by cryptanalysts, its *implementations* are not guaranteed to be secure. Side-channel attacks have become the most promising attacks, and cache-timing attacks pose a security threat to common AES implementations, as they make heavy use of lookup tables. Countermeasures against cache-timing attacks on software implementations include hardware-based defenses to limit cache leakage; or obscuring timing data, e.g.,

<sup>\*</sup> The first author was supported in part by the European Commission through the ICT Programme under Contract ICT-2007-216646 ECRYPT II, the IAP– Belgian State–Belgian Science Policy BCRYPT and the IBBT (Interdisciplinary institute for BroadBand Technology) of the Flemish Government, and by the FWO-Flanders project nr. G.0317.06 Linear Codes and Cryptography. The second author was supported by the European Commission through the ICT Programme under Contract ICT–2007–216499 CACE, and through the ICT Programme under Contract ICT–2007-216646 ECRYPT II. Permanent ID of this document: cc3a43763e7c5016ddc9cfd5d06f8218. Date: June 15, 2009.

C. Clavier and K. Gaj (Eds.): CHES 2009, LNCS 5747, pp. 1–17, 2009.

<sup>©</sup> International Association for Cryptologic Research 2009

via adding dummy instructions. However, both approaches are generally deemed impractical due to a severe performance penalty.

This leaves us with the third option: writing dedicated constant-time software. While several cryptographic algorithms such as the Serpent block cipher [8] have been designed with a lookup-table-free implementation in mind, it is generally extremely difficult to safeguard a cipher against side-channel attacks *a posteriori*.

Matsui and Nakajima were the first to show a constant-time implementation of AES on an Intel Core 2 processor faster than any other implementation described before [24]. However, the reported speed of 9.2 cycles/byte<sup>1</sup> is only achieved for chunks of 2 KB of input data that are transposed into a dedicated bitsliced format. Including format conversion, this implementation thus runs at around 10 cycles/byte for stream encryption. On the other hand, encrypting, say, 576-byte packets would presumably cause a slowdown by more than a factor of 3, making the approach unsuitable for many network applications.

Könighofer presents an alternative implementation for 64-bit platforms that processes only 4 input blocks in parallel [22], but at 19.8 cycles/byte, his code is even slower than the reference implementation used in OpenSSL.

Finally, Intel has announced a new AES-NI instruction set [17] that will provide dedicated hardware support for AES encryption and thus circumvent cache leaks on future CPUs. However, processors rolled out to the market today do not yet support these instructions, so cache-timing attacks will continue to be a threat to AES for several years until all current processors have been replaced.

This paper presents a constant-time implementation of AES which only needs 7.59 cycles/byte on an Intel Core 2 Q9550, including costs for transformation of input data into bitsliced format and transformation of output back to standard format. On the newer Intel Core i7, we show even faster speeds of 6.92 cycles/byte, while lookup-table-based implementations on the same platform are still behind the 10 cycles/byte barrier. Not only is our software up to 30% faster than any previously presented AES software for 64-bit Intel processors, it also no longer needs input chunks of 2 KB but only of 128 bytes to achieve optimal speed and is thus efficient for packet as well as stream encryption.

Secondly, we propose a fast implementation of Galois/Counter mode (GCM) authentication. Combined with our fast AES encryption, we demonstrate speeds of 10.68 cycles per encrypted and authenticated byte on the Core 2 Q9550. Our fast GCM implementation, however, uses the standard method of lookup tables for multiplication in a finite field. While no cache-timing attacks against GCM have been published, we acknowledge that this implementation might be vulnerable to cache leaks. Thus, we also describe a new method for implementing GCM without lookup tables that still yields a reasonable speed of 21.99 cycles/byte. The machine-level strategies for implementing AES-GCM in constant time might be of independent interest to implementors of cryptographic software.

**Note.** All software presented in this paper is in the public domain and is available online on the authors' websites [19, 31] to maximize reusability of results.

<sup>&</sup>lt;sup>1</sup> From here on, we consider only AES-128. All results extend straightforwardly to other key sizes, with an appropriate downscaling in performance.

**Organization of the paper.** In Section 2, we analyze the applicability of cache-timing attacks to each component of AES-GCM authenticated encryption. Section 3 gives an overview of the target platforms. In Sections 4 and 5, we describe our implementations of AES and GCM, respectively. Finally, Section 6 gives performance benchmarks on three different platforms.

#### 2 Cache Timing Attacks against AES and GCM

Cache-timing attacks are software side-channel attacks exploiting the timing variability of data loads from memory. This variability is due to the fact that all modern microprocessors use a hierarchy of caches to reduce load latency. If a load operation can retrieve data from one of the caches (*cache hit*), the load takes less time than if the data has to be retrieved from RAM (*cache miss*).

Kocher [21] was the first to suggest cache-timing attacks against cryptographic algorithms that load data from positions that are dependent on secret information. Initially, timing attacks were mostly mentioned in the context of public-key algorithms until Kelsey et al. [20] and Page [30] considered timing attacks, including cache-timing attacks, against secret-key algorithms. Tsunoo et al. demonstrated the practical feasibility of cache-timing attacks against symmetric-key ciphers MISTY1 [33] and DES [32], and were the first to mention an attack against AES (without giving further details).

In the rest of this section, we analyze separately the cache-timing vulnerability of three components of AES-GCM: encryption, key schedule, and authentication.

#### 2.1 Attacks against AES Encryption

A typical implementation of AES uses precomputed lookup tables to implement the S-Box, opening up an opportunity for a cache-timing attack. Consider, for example, the first round of AES: the indices of the table lookups are then defined simply by the xor of the plaintext and the first round key. As the attacker knows or even controls the plaintext, information about the lookup indices directly leaks information about the key.

Bernstein [3] was the first to implement a cache-timing key-recovery attack against AES. While his attack relies on the attacker's capability of producing reference timing distributions from known-key encryptions on a platform identical to the target platform and has thus been deemed difficult to mount [29,9], several improved attack strategies have subsequently been described by Bertoni et al. [6], Osvik et al. [29], Actiçmez et al. [18], Bonneau and Mironov [9], and Neve et al. [28,27].

In particular, Osvik et. al. [29] propose an attack model where the attacker obtains information about cache access patterns by manipulating the cache between encryptions via user-level processes. Bonneau and Mironov [9] further demonstrate an attack detecting cache hits in the encryption algorithm itself, as opposed to timing a process controlled by the attacker. Their attack requires no active cache manipulation, only that the tables are (partially) evicted from cache prior to the encryption. Finally, Aciçmez et. al. [18] note that if the encrypting machine is running multiple processes, workload on the target machine achieves the desired cache-cleaning effect, and provide simulation results suggesting that it is possible to recover an AES encryption key via a passive remote timing attack.

#### 2.2 Attacks against AES Key Expansion

The expansion of the 128-bit AES key into 11 round keys makes use of the SUB-BYTES operation which is also used for AES encryption and usually implemented through lookup tables. During key schedule, the lookup indices are dependent on the secret key, so in principle, ingredients for a cache-timing attack are available also during key schedule.

However, we argue that mounting a cache-timing attack against AES keyexpansion will be very hard in practice. Common implementations do the key expansion just once and store either the fully expanded 11 round keys or partiallyexpanded keys (see e.g. [2]); in both cases, table lookups based on secret data are performed just once, precluding statistical timing attacks, which require multiple timing samples.

We nevertheless provide a constant-time implementation of key expansion for the sake of completeness. The cycle count of the constant-time implementation is however inferior to the table-based implementation; a performance comparison of the two methods is given in Section 6.

#### 2.3 Attacks against Galois/Counter Mode Authentication

The computationally expensive operations for GCM authentication are multiplications in the finite field  $\mathbb{F}_{2^{128}}$ . More specifically, each block of input requires multiplication with a secret constant factor H derived from the master encryption key. As all common general-purpose CPUs lack support for multiplication of polynomials over  $\mathbb{F}_2$ , the standard way of implementing GCM is through lookup tables containing precomputed multiples of H.

The specification of GCM describes different multiplication algorithms involving tables of different sizes allowing to trade memory for computation speed [25]. The basic idea of all of these algorithms is the same: split the non-constant factor of the multiplication into bytes or half-bytes and use these as indices for table lookups.

For the first block of input  $P_1$ , this non-constant factor is  $C_1$ , the first block of ciphertext. Assuming the ciphertext is available to the attacker anyway, the indices of the first block lookups do not leak any secret information. However, for the second ciphertext block  $C_2$ , the non-constant input to the multiplication is  $(C_1 \cdot H) \oplus C_2$ . An attacker gaining information about this value can easily deduce the secret value H necessary for a forgery attack.<sup>2</sup>

$<sup>^2</sup>$  The authentication key H is derived from the master key via encrypting a known constant. Thus, learning H is equivalent to obtaining a known plaintext-ciphertext pair and should pose no threat to the master encryption key itself.

The lookup tables used for GCM are usually at least as large as AES lookup tables; common sizes include 4 KB, 8 KB and 64 KB. The values retrieved from these tables are 16 bytes long; knowledge of the (64-byte) cache line thus leaves only 4 possibilities for each lookup index. For example, the 64-KB implementation uses 16 tables, each corresponding to a different byte of the 128-bit input. Provided that cache hits leak the maximum 6 bits in each byte, a  $2^{32}$  exhaustive search over the remaining unknown bits is sufficient to recover the authentication key.

We conclude that common implementations of GCM are potentially vulnerable to authentication key recovery via cache timing attacks. Our software thus includes two different versions of GCM authentication: a fast implementation based on 8-KB lookup tables for settings where timing attacks are not considered a threat; and a slower, constant-time implementation offering full protection against timing attacks. For a performance comparison of these two implementations, see Section 6.

## 3 The Intel Core 2 and Core i7 Processors

We have benchmarked our implementations on three different Intel microarchitectures: the 65-nm Core 2 (Q6600), the 45-nm Core 2 (Q9550) and the Core i7 (920). These microarchitectures belong to the amd64 family, they have 16 128-bit SIMD registers, called XMM registers.

The 128-bit XMM registers were introduced to Intel processors with the "Streaming SIMD Extensions" (SSE) on the Pentium III processor. The instruction set was extended (SSE2) on the Pentium IV processor, other extensions SSE3, SSSE3 and SSE4 followed. Starting with the Core 2, the processors have full 128-bit wide execution units, offering increased throughput for SSE instructions.

Our implementation mostly uses bit-logical instructions on XMM registers. Intel's amd64 processors are all able to dispatch up to 3 arithmetic instructions (including bit-logical instructions) per cycle; at the same time, the number of simultaneous loads and stores is limited to one.

Virtually all instructions on the amd64 operate on two registers; that is, a twooperand instruction, such as an XOR, overwrites one of the inputs with the output. This introduces an overhead in register-to-register moves whenever both inputs need to be preserved for later reuse.

Aside from these obvious performance bottlenecks, different CPUs have specific limitations:

The pshufb instruction: This instruction is part of the SSSE3 instruction-set extension and allows to shuffle the bytes in an XMM register arbitrarily. On a 65-nm processor, pshufb is implemented through 4  $\mu$ ops; 45-nm Core 2 and Core i7 CPUs need just 1  $\mu$ op (see [15]). This reduction was achieved by the introduction of a dedicated shuffle-unit [12]. The Core i7 has two of these shuffle units, improving throughput by a factor of two.

**Choosing between equivalent instructions:** The SSE instruction set includes three different logically equivalent instructions to compute the xor of two 128-bit registers: xorps, xorpd and pxor; similar equivalences hold for other bit-logical instructions: andps/andpd/pand, orps/orpd/por.

While xorps/xorpd consider their inputs as floating point values, pxor works on integer inputs. On Core 2 processors, all three instructions yield the same performance. On the Core i7, on the other hand, it is crucial to use integer instructions: changing all integer bit-logical instructions to their floating-point equivalents results in a performance penalty of about 50% on our benchmark Core i7 920.

What about AMD processors? Current AMD processors do not support the SSSE3 pshufb instruction, but an even more powerful SSE5 instruction pperm will be available for future AMDs. It is also possible to adapt the software to support current 64-bit AMD processors. The performance of the most expensive part of the computation—the AES S-box—will not be affected by this modification, though the linear layer will require more instructions.

## 4 Bitsliced Implementation of AES in Counter Mode

Bitslicing as a technique for implementing cryptographic algorithms was proposed by Biham to improve the software performance of DES [7]. Essentially, bitslicing simulates a hardware implementation in software: the entire algorithm is represented as a sequence of atomic Boolean operations. Applied to AES, this means that rather than using precomputed lookup tables, the  $8 \times 8$ -bit S-Box as well as the linear layer are computed on-the-fly using bit-logical instructions. Since the execution time of these instructions is independent of the input values, the bitsliced implementation is inherently immune to timing attacks.

Obviously, representing a single AES byte by 8 Boolean variables and evaluating the S-Box is much slower than a single table lookup. However, collecting equivalent bits from multiple bytes into a single variable (register) allows to compute multiple S-Boxes at the cost of one. More specifically, the 16 XMM registers of the Core 2 processors allow to perform packed Boolean operations on 128 bits. In order to fully utilize the width of these registers, we thus process 8 16-byte AES blocks in parallel. While our implementation considers 8 consecutive blocks of AES in counter mode, the same technique could be applied equally efficiently

|             | xor/and/or | pshufd/pshufb | xor (mem-reg) | mov (reg-reg) | TOTAL |

|-------------|------------|---------------|---------------|---------------|-------|

| SubBytes    | 128        | -             | -             | 35            | 163   |

| ShiftRows   | _          | 8             | -             | -             | 8     |

| MixColumns  | 27         | 16            | -             | _             | 43    |

| AddRoundKey | -          | -             | 8             | -             | 8     |

| TOTAL       | 155        | 24            | 8             | 35            | 222   |

Table 1. Instruction count for one AES round

to other modes, as long as there is sufficient parallelism. For example, while the CBC mode is inherently sequential, one could consider 8 parallel independent CBC encryptions to achieve the same effect.

Table 1 summarizes the instruction count for each component of AES. In total, one full round of AES requires 222 instructions to process 8 blocks, or 1.73 instructions/byte. In comparison, a typical lookup-table-based implementation performs 1 lookup per byte per round. As the Core 2 can issue up to 3 arithmetic instructions per clock cycle, we are able to break the fundamental 1 cycle/byte barrier of lookup-table-based implementations.

Several AES implementations following a similar bitslicing approach have been reported previously [22, 23, 24]. However, compared to previous results, we have managed to further optimize every step of the round function. Our implementation of SUBBYTES uses 15% fewer instructions than previously reported software implementations. Also, replacing rotates with the more general byte shuffling instructions has allowed us to design an extremely efficient linear layer (see Section 4.3 and 4.4). In the rest of this section, we describe implementation aspects of each step of the AES round function, as well as the format conversion algorithm.

#### 4.1 Bitsliced Representation of the AES State

The key to a fast bitsliced implementation is finding an efficient bitsliced representation of the cipher state. Denote the bitsliced AES state by  $a[0], \ldots, a[7]$ , where each a[i] is a 128-bit vector fitting in one XMM register. We take 8 16-byte AES blocks and "slice" them bitwise, with the least significant bits of each byte in a[0] and the most significant bits in the corresponding positions of a[7]. Now, the AES S-Box can be implemented equally efficiently whatever the order of bits within the bitsliced state. The efficiency of the linear layer, on the other hand, depends crucially on this order.

In our implementation, we collect in each byte of the bitsliced state 8 bits from identical positions of 8 different AES blocks, assuring that bits within each byte are independent and all instructions can be kept byte-level. Furthermore, in order to simplify the MIXCOLUMNS step, the 16 bytes of an AES state are collected in the state row by row. Figure 1 illustrates the bit ordering in each 128-bit state vector a[i].

Several solutions are known for converting the data to a bitsliced format and back [22,24]. Our version of the conversion algorithm requires 84 instructions to bitslice the input, and 8 byte shuffles to reorder the state row by row.

|                                                               | rc                                      | w 0                     |              |                           |                   |                                           | row 3             |                                                  |

|---------------------------------------------------------------|-----------------------------------------|-------------------------|--------------|---------------------------|-------------------|-------------------------------------------|-------------------|--------------------------------------------------|

| ${\rm column}~0$                                              | column 1                                | colum                   | nn2          | colu                      | mn 3              | <br>column                                | 0                 | $\operatorname{column} 3$                        |

| <u>block 0</u><br><u> </u><br> -<br> <br> <br> <br> <br> <br> | block 0<br>block 1<br>:<br>:<br>block 7 | block 0<br>block 1<br>: | :<br>block 7 | <u>block 0</u><br>block 1 | :<br>:<br>block 7 | <br><u>block 0</u><br><u>block 1</u><br>: | block 7<br>:<br>: | <u>block 0</u><br><u>block 1</u><br>:<br>block 7 |

Fig. 1. Bit ordering in one 128-bit vector of the bitsliced state

|          | xor | and/or | mov | TOTAL |

|----------|-----|--------|-----|-------|

| Hardware | 82  | 35     | -   | 117   |

| Software | 93  | 35     | 35  | 163   |

Table 2. Instruction count for the AES S-Box

#### 4.2 The SUBBYTES Step

The SUBBYTES step of AES transforms each byte of the 16-byte AES state according to an  $8 \times 8$ -bit S-Box S based on inversion in the finite field  $\mathbb{F}_{2^8}$ . We use well-known hardware implementation strategies for decomposing the S-Box into Boolean instructions. The starting point of our implementation is the compact hardware S-Box proposed by Canright [11], requiring 120 logic gates, and its recent improvements by Boyar and Peralta [10], which further reduce the gate count to 117. Our implementation of the SUBBYTES step is obtained by converting each logic gate (xor, and, or) in this implementation to its equivalent CPU instruction. All previous bitsliced implementations use a similar approach, nevertheless, by closely following hardware optimizations, we have improved the software instruction count by 15%, from 199 instructions [24] to 163.

We omit here the lengthy description of obtaining the Boolean decomposition; full details can be found in the original paper [11]. Instead, we highlight differences between the hardware approach and our software "simulation", as the exchange rate between hardware gates and instructions on the Core 2 is not one-to-one.

First, the packed Boolean instructions of the Core 2 processors have one source and one destination; that is, one of the inputs is always overwritten by the result. Thus, we need extra move instructions whenever we need to reuse both inputs. Also, while the compact hardware implementation computes recurring Boolean subexpressions only once, we are not able to fit all intermediate values in the available 16 XMM registers. Instead, we have a choice between recomputing some values, or using extra load/store instructions to keep computed values on the stack. We chose to do away without the stack: our implementation fits entirely in the 16 registers and uses 128 packed Boolean instructions and 35 registerto-register move instructions. Table 2 lists the instruction/gate counts for the S-Box in software and hardware.

#### 4.3 The ShiftRows Step

Denote the  $4 \times 4$ -byte AES state matrix by  $[a_{ij}]$ . SHIFTROWS rotates each row of the matrix left by 0, 1, 2 and 3 bytes, respectively:

| $\begin{bmatrix} a_{00} \ a_{01} \ a_{02} \ a_{03} \end{bmatrix}$ | $\begin{bmatrix} a_{00} \ a_{01} \ a_{02} \ a_{03} \end{bmatrix}$                                         |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| $a_{10} a_{11} a_{12} a_{13}$                                     |                                                                                                           |

| $a_{20} a_{21} a_{22} a_{23}$                                     | <br>$\begin{array}{c} a_{11} \ a_{12} \ a_{13} \ a_{10} \\ a_{22} \ a_{23} \ a_{20} \ a_{21} \end{array}$ |

| $\begin{bmatrix} a_{30} \ a_{31} \ a_{32} \ a_{33} \end{bmatrix}$ | $a_{33} a_{30} a_{31} a_{32}$                                                                             |

Since each byte of the bitsliced state contains 8 bits from identical positions of 8 AES blocks, SHIFTROWS requires us to permute the 16 bytes in each 128-bit vector according to the following permutation pattern:

$\begin{bmatrix} a_{00} | a_{01} | a_{02} | a_{03} | a_{10} | a_{11} | a_{12} | a_{13} | a_{20} | a_{21} | a_{22} | a_{23} | a_{30} | a_{31} | a_{32} | a_{33} \end{bmatrix} \mapsto \\ \begin{bmatrix} a_{00} | a_{01} | a_{02} | a_{03} | a_{11} | a_{12} | a_{13} | a_{10} | a_{22} | a_{23} | a_{20} | a_{21} | a_{33} | a_{30} | a_{31} | a_{32} \end{bmatrix} \mapsto \\ \begin{bmatrix} a_{00} | a_{01} | a_{02} | a_{03} | a_{11} | a_{12} | a_{13} | a_{10} | a_{22} | a_{23} | a_{20} | a_{21} | a_{33} | a_{30} | a_{31} | a_{32} \end{bmatrix} \mapsto \\ \begin{bmatrix} a_{00} | a_{01} | a_{02} | a_{03} | a_{11} | a_{12} | a_{13} | a_{10} | a_{22} | a_{23} | a_{20} | a_{21} | a_{33} | a_{30} | a_{31} | a_{32} \end{bmatrix} .$

Using the dedicated SSSE3 byte shuffle instruction pshufb, the whole SHIFTROWS step can be done in 8 XMM instructions.

#### 4.4 The MIXCOLUMNS Step

MIXCOLUMNS multiplies the state matrix  $[a_{ij}]$  by a fixed  $4 \times 4$  matrix to obtain a new state  $[b_{ij}]$ :

| $\begin{bmatrix} b_{00} \ b_{01} \ b_{02} \ b_{03} \end{bmatrix}$ |   | $\begin{bmatrix} 02_x & 03_x & 01_x & 01_x \end{bmatrix}$ |   | $\begin{bmatrix} a_{00} \ a_{01} \ a_{02} \ a_{03} \end{bmatrix}$ |   |

|-------------------------------------------------------------------|---|-----------------------------------------------------------|---|-------------------------------------------------------------------|---|

| $b_{10} b_{11} b_{12} b_{13}$                                     | _ | $01_x 02_x 03_x 01_x$                                     |   | $a_{11} a_{12} a_{13} a_{10}$                                     |   |

| $b_{20} b_{21} b_{22} b_{23}$                                     | _ | $01_x 01_x 02_x 03_x$                                     | • | $a_{22} a_{23} a_{20} a_{21}$                                     | • |

| $\begin{bmatrix} b_{30} \ b_{31} \ b_{32} \ b_{33} \end{bmatrix}$ |   | $\begin{bmatrix} 03_x & 01_x & 01_x & 02_x \end{bmatrix}$ |   | $\begin{bmatrix} a_{33} \ a_{30} \ a_{31} \ a_{32} \end{bmatrix}$ |   |

Owing to the circularity of the multiplication matrix, each resulting byte  $b_{ij}$  can be calculated using an identical formula:

$$b_{ij} = 02_x \cdot a_{ij} \oplus 03_x \cdot a_{i+1,j} \oplus a_{i+2,j} \oplus a_{i+3,j},$$

where indices are reduced modulo 4.

Recall that each byte  $a_{ij}$  is an element of  $\mathbb{F}_{2^8} = \mathbb{F}_2[X]/X^8 + X^4 + X^3 + X + 1$ , so multiplication by  $02_x$  corresponds to a left shift and a conditional masking with  $00011011_b$  whenever the most significant bit  $a_{ij}[7] = 1$ . For example, the least significant bit  $b_{ij}[0]$  of each byte is obtained as

$$b_{ij}[0] = a_{ij}[7] \oplus a_{i+1,j}[0] \oplus a_{i+1,j}[7] \oplus a_{i+2,j}[0] \oplus a_{i+3,j}[0].$$

As the bitsliced state collects the bits of an AES state row by row, computing  $a_{i+1,j}[0]$  from  $a_{ij}[0]$  for all 128 least significant bits in parallel is equivalent to rotating a[0] left by 32 bits:

$$\begin{split} & [a_{00}|a_{01}|a_{02}|a_{03}|a_{10}|a_{11}|a_{12}|a_{13}|a_{20}|a_{21}|a_{22}|a_{23}|a_{30}|a_{31}|a_{32}|a_{33}] \mapsto \\ & [a_{10}|a_{11}|a_{12}|a_{13}|a_{20}|a_{21}|a_{22}|a_{23}|a_{30}|a_{31}|a_{32}|a_{33}|a_{00}|a_{01}|a_{02}|a_{03}]. \end{split}$$

Similarly, computing  $a_{i+2,j}$   $(a_{i+3,j})$  requires rotation by 64 (resp. 96) bits. To obtain the new bitsliced state vector b[0], we can now rewrite the above equation as

$$b[0] = (a[7] \oplus (rl^{32}a[7])) \oplus (rl^{32}a[0]) \oplus rl^{64}(a[0] \oplus (rl^{32}a[0]))$$

Similar equations can be obtained for all state vectors b[i] (see App. A for a complete listing). By observing that  $rl^{64}a[i] \oplus rl^{96}a[i] = rl^{64}(a[i] \oplus rl^{32}a[i])$ , we

are able to save a rotation and we thus only need to compute two rotations per register, or 16 in total. There is no dedicated rotate instruction for XMM registers; however, as all our rotations are in full bytes, we can use the pshufd 32-bit-doubleword permutation instruction. This instruction allows to write the result in a destination register different from the source register, saving registerto-register moves. In total, our implementation of MIXCOLUMNS requires 43 instructions: 16 pshufd instructions and 27 xors.

## 4.5 The AddRoundKey Step

The round keys are converted to bitsliced representation during key schedule. Each key is expanded to 8 128-bit values, and a round of ADDROUNDKEY requires 8 xors from memory to the registers holding the bitsliced state. The performance of the ADDROUNDKEY step can further be slightly optimized by interleaving these instructions with the byte shuffle instructions of the SHIFTROWS step.

## 4.6 AES Key Schedule

The AES key expansion algorithm computes 10 additional round keys from the initial key, using a sequence of SUBBYTES operations and xors. With the input/output transform, and our implementation of SUBBYTES, we have all the necessary components to implement the key schedule in constant time. The key schedule performs 10 unavoidably sequential SUBBYTES calls; its cost in constant time is thus roughly equivalent to the cost of one 8-block AES encryption. The performance results in Section 6 include an exact cycle count.

## 5 Implementations of GCM Authentication

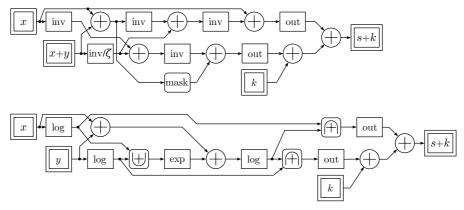

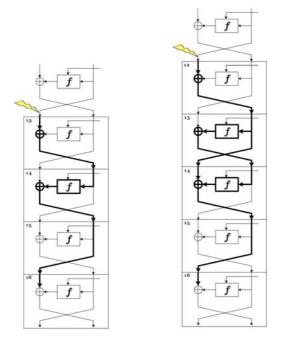

Galois/Counter mode is a NIST-standardized block cipher mode of operation for authenticated encryption [25]. The 128-bit authentication key H is derived from the master encryption key K during key setup as the encryption of an all-zero input block. The computation of the authentication tag then requires, for each 16-byte data block, a 128-bit multiplication by H in the finite field  $\mathbb{F}_{2^{128}} = \mathbb{F}_2[X]/(X^{128} + X^7 + X^2 + X + 1)$ . Figure 2 illustrates the mode of operation; full details can be found in the specification [25].

The core operation required for GCM authentication is thus Galois field multiplication with a secret constant element H. This section describes two different implementations of the multiplication—first, a standard table-based approach, and second, a constant-time solution. Both implementations consist of a onetime key schedule computing H and tables containing multiples of H; and an online phase which performs the actual authentication. Both implementations accept standard (non-bitsliced) input.

Fig. 2. Galois/Counter Mode Authenticated Encryption

#### 5.1 Table-Based Implementation

Several flavors of Galois field multiplication involving lookup tables of different sizes have been proposed for GCM software implementation [25]. We chose the "simple, 4-bit tables method", which uses 32 tables with 16 precomputed multiples of H each, corresponding to a memory requirement of 8 KB.

Following the ideas from [13], we can do one multiplication using 84 arithmetic instructions and 32 loads.

The computation is free of long chains of dependent instructions and the computation is thus mainly bottlenecked by the number of 32 loads per multiplication yielding a performance of 10.68 cycles/byte for full AES-GCM on a Core 2 Q9550.

#### 5.2 Constant-Time Implementation

Our alternative implementation of GCM authentication does not use any table lookups or data-dependent branches and is thus immune to timing attacks. While slower than the implementation described in Section 5.1, the constanttime implementation achieves a reasonable speed of 21.99 cycles per encrypted and authenticated byte and, in addition, requires only 2 KB of memory for precomputed values, comparing favorably to lookup-table-based implementations.

During the offline phase, we precompute values  $H, X \cdot H, X^2 \cdot H, \ldots, X^{127} \cdot H$ . Based on this precomputation, multiplication of an element D with H can be computed using a series of xors conditioned on the bits of D, as shown in Algorithm 1.

For a constant-time version of this algorithm we have to replace the conditional statements by a sequence of deterministic instructions. Suppose that we want to xor register %xmm3 into register %xmm4 if and only if bit  $b_0$  of register **Algorithm 1.** Multiplication in  $\mathbb{F}_{2^{128}}$  of *D* with a constant element *H*.

**Require:** Input *D*, precomputed values  $H, X \cdot H, X^2 \cdot H, \dots, X^{127} \cdot H$  **Ensure:** Output product  $DH = D \cdot H$  DH = 0 **for** i = 0 to 127 **do if**  $d_i == 1$  **then**   $DH = DH \oplus X^i \cdot H$  **end if end for**

| Listing 1. A constant-time implementation of conditional xor |                                                                            |                                   |       |   |               |  |   |      |    |        |  |

|--------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------|-------|---|---------------|--|---|------|----|--------|--|

| 2: pan<br>3: pcm<br>4: psh<br>5: pan                         | dqa %xmm0,<br>d BIT0,<br>peqd BIT0,<br>ufd \$0xff,<br>d %xmm3,<br>r %xmm1, | %xmm1<br>%xmm1<br>%xmm1,<br>%xmm1 | %xmm1 | # | %xmm1<br>BITO |  | - | mask | in | memory |  |

%xmm0 is set. Listing 1 shows a sequence of six assembly instructions that implements this conditional xor in constant time. Lines 1–4 produce an all-zero mask in register %xmm1 if  $b_0 = 0$  and an all-one mask otherwise. Lines 5–6 mask %xmm3 with this value and xor the result. We note that the precomputation described above is also implemented in constant time, using the same conditional-xor technique.

In each 128-bit multiplication in the online phase, we need to loop through all 128 bits of the intermediate value D. Each loop requires  $6 \cdot 128$  instructions, or 48 instructions per byte. We managed to further optimize the code in Listing 1 by considering four bitmasks in parallel and only repeating lines 1–3 of the code once every four bits, yielding a final complexity of 3.75 instructions per bit, or 30 instructions/byte. As the Core 2 processor can issue at most 3 arithmetic instructions per cycle, a theoretical lower bound for a single Galois field multiplication, using our implementation of the conditional xor, is 10 cycles/byte. The actual performance comes rather close at around 14 cycles/byte for the complete authentication.

#### 6 Performance

We give benchmarking results for our software on three different Intel processors. A description of the computers we used for benchmarking is given in Table 3; all benchmarks used just one core.

To ensure verifiability of our results, we used the open eSTREAM benchmarking suite [14], which reports separate cycle counts for key setup, IV setup, and for encryption.

|               | latour                  | berlekamp               | dragon                |

|---------------|-------------------------|-------------------------|-----------------------|

| CPU           | Intel Core 2 Quad Q6600 | Intel Core 2 Quad Q9550 | Intel Core i7 920     |

| CPU frequency | 2404.102 MHz            | 2833 MHz                | 2668 MHz              |

| RAM           | 8 GB                    | 8 GB                    | 3  GB                 |

| OS            | Linux 2.6.27.11 x86_64  | Linux 2.6.27.19 x86_64  | Linux 2.6.27.9 x86_64 |

| Affiliation   | Eindhoven University    | National Taiwan         | National Taiwan       |

|               | of Technology           | University              | University            |

Table 3. Computers used for benchmarking

Table 4. Performance of AES-CTR encryption in cycles/byte

| Packet size                                               | 4096                                                   | bytes   | 1500   | bytes | <b>576</b> | bytes | 40    | bytes | Simple | Imix  |

|-----------------------------------------------------------|--------------------------------------------------------|---------|--------|-------|------------|-------|-------|-------|--------|-------|

| latour                                                    |                                                        |         |        |       |            |       |       |       |        |       |

| This paper                                                |                                                        | 9.32    |        | 9.76  |            | 10.77 |       | 34.36 |        | 12.02 |

| [5]                                                       |                                                        | 10.58   |        | 10.77 |            | 10.77 |       | 19.44 |        | 11.37 |

| Cycles for l                                              | Cycles for key setup (this paper), table-based: 796.77 |         |        |       |            |       |       |       |        |       |

| Cycles for key setup (this paper), constant-time: 1410.56 |                                                        |         |        |       |            |       |       |       |        |       |

| Cycles for k                                              | xey set                                                | up [5]: | 163.25 | 5     |            |       |       |       |        |       |

| berlekamp                                                 |                                                        |         |        |       |            |       |       |       |        |       |

| This paper                                                |                                                        | 7.59    |        | 7.98  |            | 8.86  |       | 28.71 |        | 9.89  |

| [5]                                                       | 10.60                                                  |         |        | 10.77 | 10.75      |       | 19.34 |       |        | 11.35 |

| Cycles for key setup (this paper), table-based: 775.14    |                                                        |         |        |       |            |       |       |       |        |       |

| Cycles for key setup (this paper), constant-time: 1179.21 |                                                        |         |        |       |            |       |       |       |        |       |

| Cycles for key setup [5]: 163.21                          |                                                        |         |        |       |            |       |       |       |        |       |

| dragon                                                    |                                                        |         |        |       |            |       |       |       |        |       |

| This paper                                                |                                                        | 6.92    |        | 7.27  |            | 8.08  |       | 26.32 |        | 9.03  |

| [5]                                                       |                                                        | 10.01   |        | 10.24 |            | 10.15 |       | 18.01 |        | 10.72 |

| Cycles for key setup (this paper), table-based: 763.38    |                                                        |         |        |       |            |       |       |       |        |       |

| Cycles for key setup (this paper), constant-time: 1031.11 |                                                        |         |        |       |            |       |       |       |        |       |

| Cycles for key setup [5]: 147.70                          |                                                        |         |        |       |            |       |       |       |        |       |

Benchmarking results for different packet sizes are given in Tables 4 and 5. The "simple Imix" is a weighted average simulating sizes of typical IP packages: it takes into account packets of size 40 bytes (7 parts), 576 bytes (4 parts), and 1500 bytes (1 part).

For AES-GCM authenticated encryption, the eSTREAM benchmarking suite reports cycles per encrypted and authenticated byte without considering final computations (one 16-byte AES encryption and one multiplication) necessary to compute the authentication tag. Cycles required for these final computations are reported as part of IV setup. Table 5 therefore gives performance numbers as reported by the eSTREAM benchmarking suite (cycles/byte and cycles required for IV setup) and "accumulated" cycles/byte, illustrating the "actual" time required for authenticated encryption.

For AES in counter mode, we also give benchmarking results of previously fastest software [5], measured with the same benchmarking suite on the same computers. Note however that this implementation uses lookup tables. The previous fastest

| Packet size                                                                           | 4096 bytes   | 1500 bytes     | 576 bytes     | 40 bytes    | Simple  | Imix  |  |  |

|---------------------------------------------------------------------------------------|--------------|----------------|---------------|-------------|---------|-------|--|--|

| latour                                                                                |              |                |               |             |         |       |  |  |

| Table-based (eSTREAM)                                                                 | 12.22        | 13.73          | 16.12         | 76.82       |         | 19.41 |  |  |

| Table-based (accumulated)                                                             | 12.55        | 14.63          | 18.49         | 110.89      |         | 23.41 |  |  |

| Constant-time (eSTREAM)                                                               | 27.13        | 28.79          | 31.59         | 99.90       |         | 35.25 |  |  |

| Constant-time (accumulated)                                                           | 27.52        | 29.85          | 34.36         | 139.76      |         | 39.93 |  |  |

| Cycles for precomputation an                                                          | d key setup, | table-based:   | 3083.31       |             |         |       |  |  |

| Cycles for precomputation an                                                          |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final                                                         |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final                                                         | computations | s for authenti | ication, cons | stant-time: | 1594.39 |       |  |  |

| berlekamp                                                                             |              |                |               |             |         |       |  |  |

| Table-based (eSTREAM)                                                                 | 10.40        | 11.64          | 13.72         | 65.95       |         | 16.54 |  |  |

| Table-based (accumulated)                                                             | 10.68        | 12.39          | 15.67         | 94.24       |         | 19.85 |  |  |

| Constant-time (eSTREAM)                                                               | 21.67        | 23.05          | 25.34         | 82.79       |         | 28.44 |  |  |

| Constant-time (accumulated)                                                           | 21.99        | 23.92          |               | 115.57      |         | 32.30 |  |  |

| Cycles for precomputation and key setup, table-based: 2786.79                         |              |                |               |             |         |       |  |  |

| Cycles for precomputation and key setup, constant-time: 3614.83                       |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final computations for authentication, table-based: 1131.97   |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final computations for authentication, constant-time: 1311.21 |              |                |               |             |         |       |  |  |

| dragon                                                                                |              |                |               |             |         |       |  |  |

| Table-based (eSTREAM)                                                                 | 9.86         | 10.97          | 12.87         | 59.05       |         | 15.34 |  |  |

| Table-based (accumulated)                                                             | 10.12        | 11.67          | 14.69         | 85.24       |         | 18.42 |  |  |

| Constant-time (eSTREAM)                                                               | 20.00        | 21.25          | 23.04         | 73.95       |         | 25.87 |  |  |

| Constant-time (accumulated)                                                           | 20.29        | 22.04          |               | 103.56      |         | 29.36 |  |  |

| Cycles for precomputation and key setup, table-based: 2424.50                         |              |                |               |             |         |       |  |  |

| Cycles for precomputation and key setup, constant-time: 3429.55                       |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final computations for authentication, table-based: 1047.49   |              |                |               |             |         |       |  |  |

| Cycles for IV setup and final computations for authentication, constant-time: 1184.41 |              |                |               |             |         |       |  |  |

Table 5. Cycles/byte for AES-GCM encryption and authentication

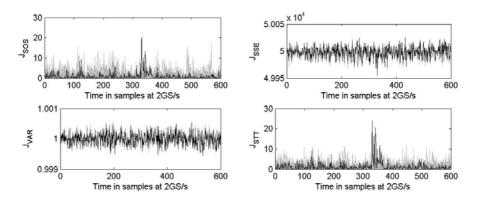

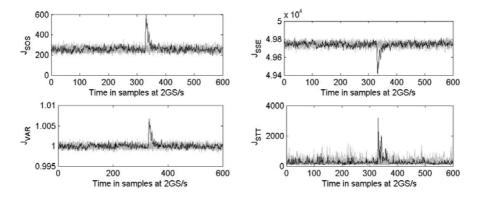

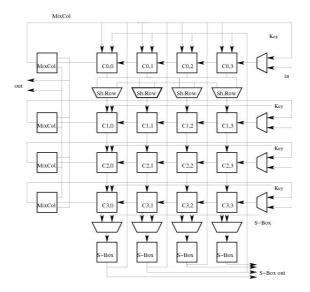

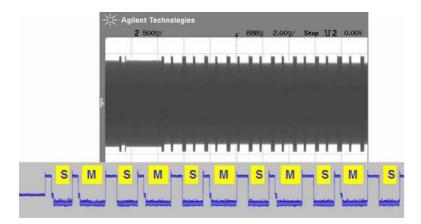

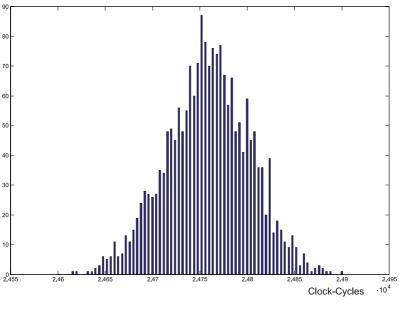

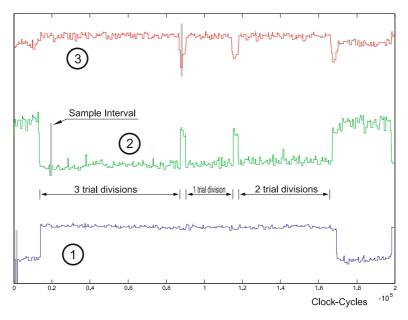

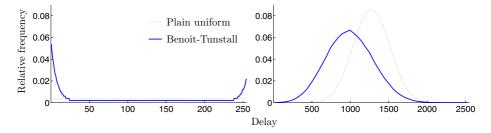

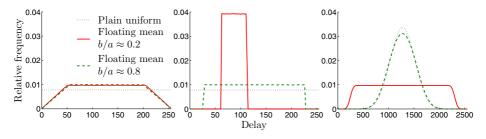

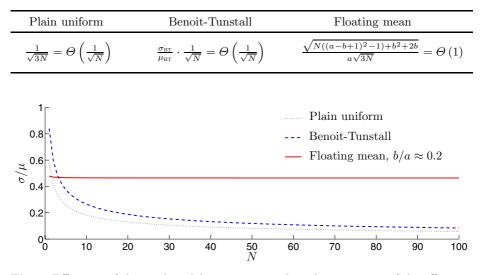

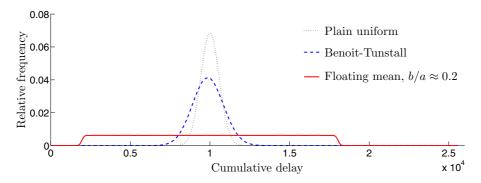

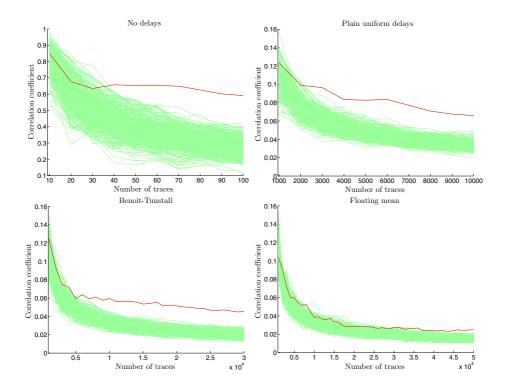

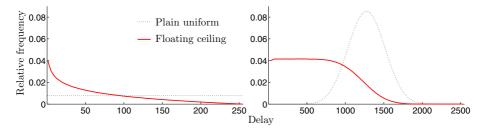

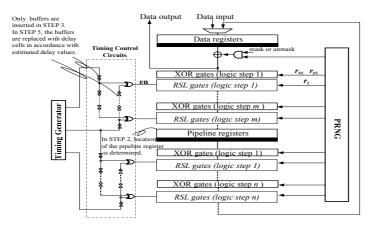

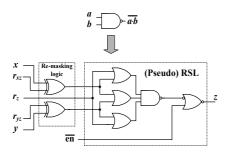

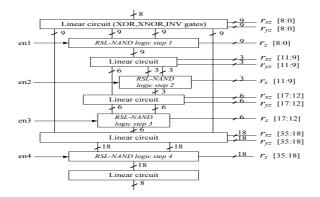

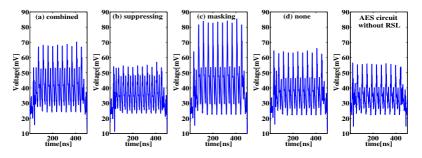

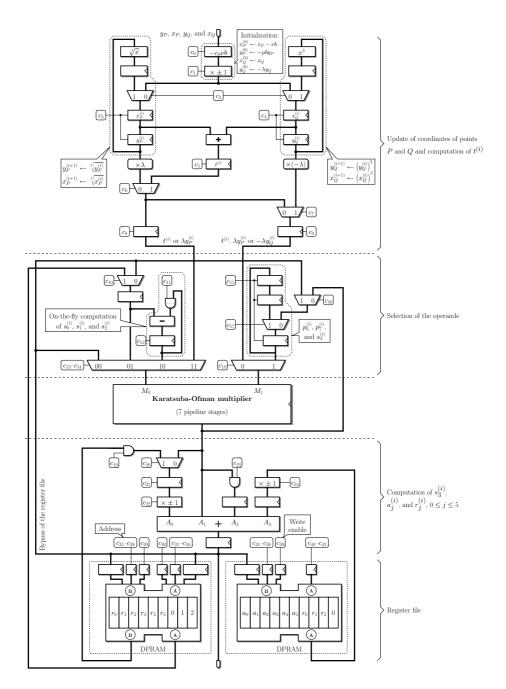

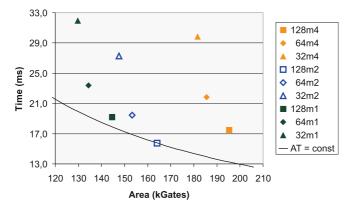

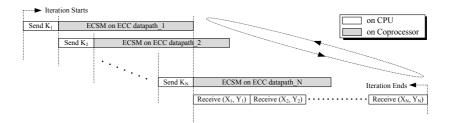

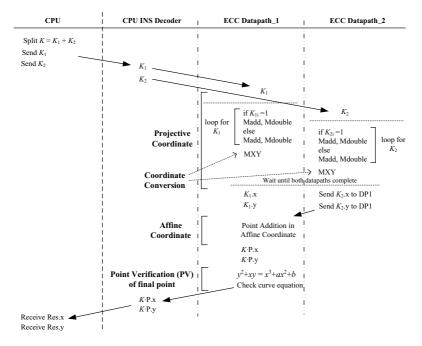

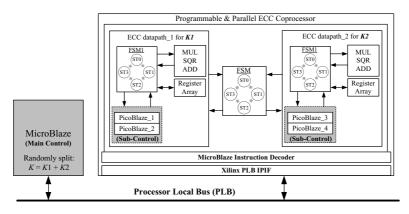

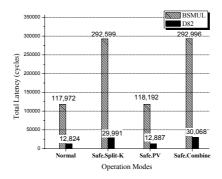

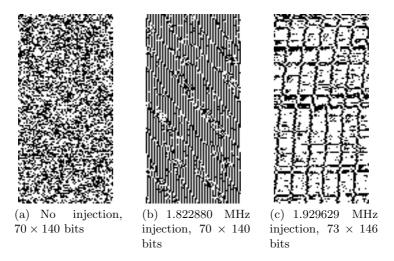

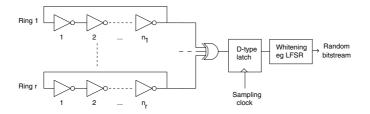

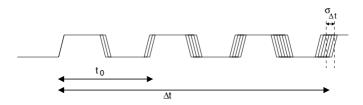

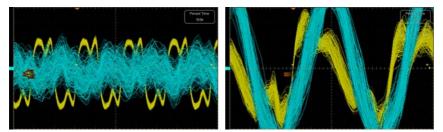

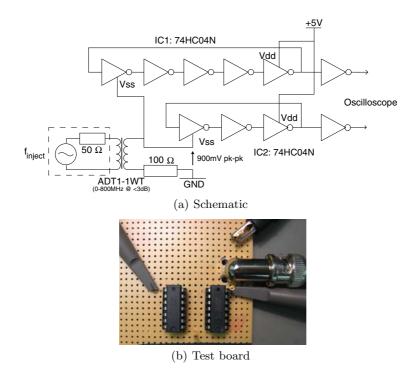

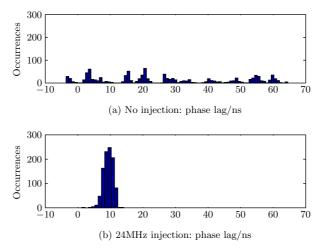

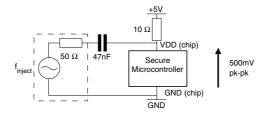

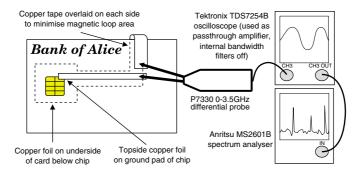

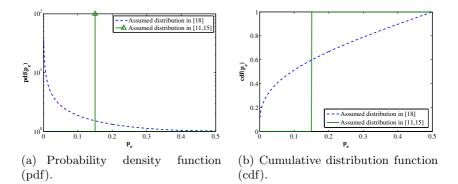

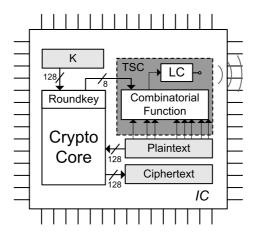

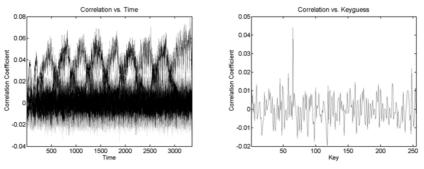

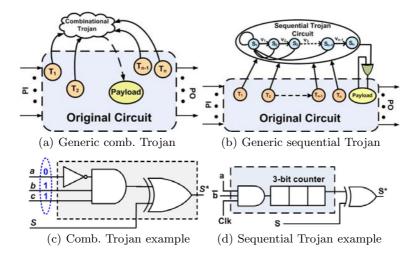

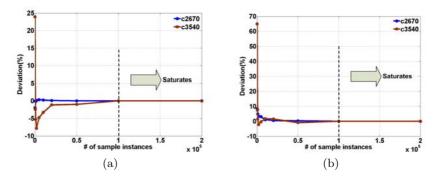

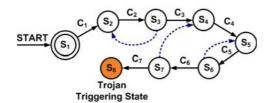

bitsliced implementation [24] is not available for public benchmarking; based on the results in the paper, we expect it to perform at best equivalent for stream encryption; and significantly slower for all packet sizes below 2 KB.