Darren Cofer Alessandro Fantechi (Eds.)

# Formal Methods for Industrial Critical Systems

13th International Workshop, FMICS 2008 L'Aquila, Italy, September 2008 Revised Selected Papers

# Lecture Notes in Computer Science

5596

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Microsoft Research, Cambridge, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Darren Cofer Alessandro Fantechi (Eds.)

# Formal Methods for Industrial Critical Systems

13th International Workshop, FMICS 2008 L'Aquila, Italy, September 15-16, 2008 Revised Selected Papers

#### Volume Editors

Darren Cofer Rockwell Collins 7805 Telegraph Rd. 100, Bloomington, MN 55438, USA E-mail: ddcofer@rockwellcollins.com

Alessandro Fantechi Università di Firenze, Dipartimento di Sistemi e Informatica Via S. Marta 3, 50139 Firenze, Italy E-mail: fantechi@dsi.unifi.it

Library of Congress Control Number: 2009930950

CR Subject Classification (1998): D.2.4, D.2, D.3, C.3, F.3

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-642-03239-7 Springer Berlin Heidelberg New York ISBN-13 978-3-642-03239-4 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12711871 06/3180 5 4 3 2 1 0

#### Preface

The aim of the FMICS workshop series is to provide a forum for researchers who are interested in the development and application of formal methods in industry. In particular, these workshops are intended to bring together scientists and practitioners who are active in the area of formal methods and interested in exchanging their experiences in the industrial usage of these methods. These workshops also strive to promote research and development for the improvement of formal methods and tools for industrial applications.

The topics for which contributions to FMICS 2008 were solicited included, but were not restricted to, the following:

- Design, specification, code generation and testing based on formal methods

- Verification and validation of complex, distributed, real-time systems and embedded systems

- Verification and validation methods that address shortcomings of existing methods with respect to their industrial applicability (e.g., scalability and usability issues)

- Tools for the development of formal design descriptions

- Case studies and experience reports on industrial applications of formal methods, focusing on lessons learned or identification of new research directions

- Impact of the adoption of formal methods on the development process and associated costs

- Application of formal methods in standardization and industrial forums

The workshop included six sessions of regular contributions in the areas of model checking, testing, software verification, real-time performance, and industrial case studies. There were also three invited presentations, given by Steven Miller, Rance Cleaveland, and Werner Damm, covering the application of formal methods in the avionics and automotive industries.

Moreover, a panel was organized on the topic "Formal Methods in Commercial SW Development Tools." The aim of this panel was to promote discussion of current and foreseen applications of formal methods within model-based development frameworks that include formal analysis and generation methods for software design.

Out of the 36 submissions to FMICS 2008, 14 papers were accepted for presentation at the workshop, as well as two short presentations to serve as an introduction to the panel. We wish to thank the members of the Program Committee and the additional reviewers for their careful evaluation of the submitted papers. We also acknowledge the effort of all the members of the Program Committee in constructive discussions during the electronic program selection meeting. Special

#### VI Preface

thanks for the efforts devoted to the organization of the workshop go to the staff of the ASE 2008 conference, with which this workshop was co-located.

September 2008

Darren Cofer Alessandro Fantechi

The FMICS 2008 workshop was hosted by the warm people of L'Aquila, Italy, and by the historic buildings of the city. Workshop participants had the occasion to stroll in the peaceful narrow streets of the old center, and to visit the magnificent monuments and churches that were built in the city several centuries ago.

On Monday, April 6, 2009, a severe earthquake hit the city, followed by more aftershocks in the following days. Hundreds of lives were lost, thousands were injured, and many houses and major historical buildings collapsed or were severely damaged. The vivid images in the memories of the workshop participants have been replaced by pictures of destruction from the media.

It is our hope that the proud, tireless and industrious people of the Abruzzo region will one day be able to bring back the city and the region to what the FMICS guests experienced.

April 2009

Darren Cofer Alessandro Fantechi

# Organization

FMICS 2008 was organized by the ERCIM Working Group on Formal Methods for Industrial Critical Systems.

## **Program Chairs**

Darren Cofer Rockwell Collins, USA

Alessandro Fantechi Università di Firenze and ISTI-CNR, Italy

#### **Program Committee**

Maria Alpuente Universidad Politècnica de Valencia, Spain

Alvaro Arenas STFC RAL, UK

Lubos Brim Masaryk University, Czech Republic

Wan Fokkink Vrije Universiteit Amsterdam, The Netherlands

Patrice Godefroid Microsoft Research, USA

Leszek Holenderski Philips Research, The Netherlands

Roope Kaivola Intel, USA

Stefan Kowalewski RWTH Aachen, Germany

Stefania Gnesi ISTI-CNR. Italy

Mark Lawford McMaster University, Canada Stefan Leue University of Konstanz, Germany Radu Mateescu INRIA Rhone-Alpes, France

Charles Pecheur Universitè Catholique de Louvain, Belgium

Francois Pilarski Airbus, France

Ralf Pinger Siemens, Germany

Murali Rangarajan Honeywell, USA

Marco Roveri IRST, Italy

Ina Schieferdecker Fraunhofer FOKUS, Germany

Wilfried Steiner TTTech, Austria

#### Additional Referees

Jiri Barnat Masaryk University, Czech Republic

Robert Beers Intel, USA

Dragan Bosnacki Eindhoven University of Technology,

The Netherlands

Goetz Botterweck Lero, Ireland

Marco Bozzano Fondazione Bruno Kessler, Italy

Calame Jens CWI, The Netherlands

#### VIII Organization

Alessio Ferrari Jan Friso Groote

Jose Iborra Christophe Joubert Dmitry Korchemny

Alexandre Korobkine

Frédéric Lang Giovanni Lombardi Franco Mazzanti

Stefan Milius

Francisco Javier Oliver

Lucian Patcas Bas Ploeger

Erik Reeber

Viktor Schuppan Wendelin Serwe Andrey Tchaltsev Maurice H. ter Beek

Francesco Tiezzi Stefano Tonetta Alicia Villanueva

Michael Whalen Anton Wijs Università di Firenze, Italy

Eindhoven University of Technology,

The Netherlands

Universidad Politècnica de Valencia, Spain Universidad Politècnica de Valencia, Spain

Intel, USA

McMaster University, Canada INRIA Rhone-Alpes, France)

ISTI-CNR, Italy ISTI-CNR, Italy Siemens, Germany

Universidad Politècnica de Valencia, Spain

McMaster University, Canada

Eindhoven University of Technology,

The Netherlands

Intel, USA

Fondazione Bruno Kessler, Italy INRIA Rhone-Alpes, France Fondazione Bruno Kessler, Italy

ISTI-CNR, Italy

Università di Firenze, Italy Fondazione Bruno Kessler, Italy

Universidad Politècnica de Valencia, Spain

Rockwell Collins, USA INRIA Rhone-Alpes, France

# **Table of Contents**

| Invited Presentations                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------|----|

| Formal Methods for Critical Systems (Invited Speaker)                                                               | 1  |

| Model-Based Verification of Automotive Control Software (Invited Speaker)                                           | 2  |

| Contract-Based Analysis of Automotive and Avionics Applications: The SPEEDS Approach (Invited Speaker)  Werner Damm | 3  |

| Panel                                                                                                               |    |

| Panel Discussion on Formal Methods in Commercial Software Development Tools                                         | 4  |

| Research Papers                                                                                                     |    |

| LETO - A Lustre-Based Test Oracle for Airbus Critical Systems                                                       | 7  |

| Extending Structural Test Coverage Criteria for LUSTRE Programs with Multi-clock Operators                          | 23 |

| Fighting State Space Explosion: Review and Evaluation                                                               | 37 |

| Local Quantitative LTL Model Checking                                                                               | 3  |

| Efficient Symbolic Model Checking for Process Algebras                                                              | 9  |

| Reentrant Readers-Writers: A Case Study Combining Model Checking with Theorem Proving                               | 35 |

# X Table of Contents

| Using CSP  B Components: Application to a Platoon of Vehicles Samuel Colin, Arnaud Lanoix, Olga Kouchnarenko, and Jeanine Souquières       | 103 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Formal Verification of the Implementability of Timing Requirements  Xiayong Hu, Mark Lawford, and Alan Wassyng                             | 119 |

| Dynamic Event-Based Runtime Monitoring of Real-Time and Contextual Properties                                                              | 135 |

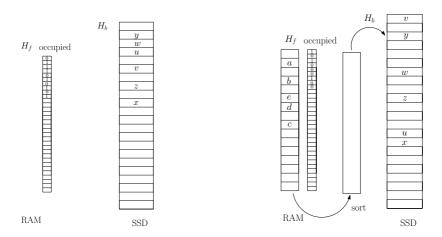

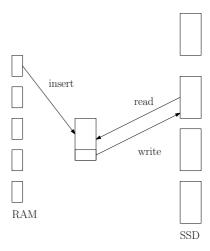

| Can Flash Memory Help in Model Checking?                                                                                                   | 150 |

| From Informal Requirements to Property-Driven Formal Validation Alessandro Cimatti, Marco Roveri, Angelo Susi, and Stefano Tonetta         | 166 |

| Automated Certification of Non-Interference in Rewriting Logic                                                                             | 182 |

| Formal Verification of Safety Functions by Reinterpretation of Functional Block Based Specifications                                       | 199 |

| Using Datalog and Boolean Equation Systems for Program Analysis  María Alpuente, Marco A. Feliú, Christophe Joubert, and Alicia Villanueva | 215 |

| Author Index                                                                                                                               | 233 |

# Formal Methods for Critical Systems

Steven P. Miller

Rockwell Collins, USA

Abstract. Formal methods have traditionally been reserved for systems with requirements for extremely high assurance. However, the growing popularity of model-based development, in which models of system behavior are created early in the development process and used to autogenerate code, are making precise, mathematical specifications much more common in industry. At the same time, formal verification tools such as model checkers continue to grow more powerful. The convergence of these two trends opens the door for the practical application of formal verification techniques early in the life cycle for many systems. This talk will describe how Rockwell Collins has applied both theorem proving and model checking to commercial avionics and security systems to reduce costs and improve quality.

# Model-Based Verification of Automotive Control Software

#### Rance Cleaveland

Department of Computer Science and Fraunhofer USA Center for Experimental Software Engineering, University of Maryland, USA

Abstract. This talk will report on the use of an approach, called Instrumentation Based Verification, for checking the correctness of models of control software given in Simulink<sup>®</sup> and Stateflow<sup>®</sup>. In IBV, engineers formalize requirements as so-called monitor models, whose purpose is to search executions of the main controller model for violations of required behavior. Testing is then performed on the instrumented controller model in order to check for the possibility of deviations between controller and requirements. Tools such as Reactis<sup>®</sup> provide automated support for conducting these activities, and the technique has attracted interest in automotive, aerospace and medical-device settings. The presentation will first review model-based development and IBV and their industrial motivations. It will then report on a project between the Fraunhofer Center for Experimental Software Engineering and a major automotive supplier on using IBV to verify models of an exterior-lighting control system.

# Contract-Based Analysis of Automotive and Avionics Applications: The SPEEDS Approach

Werner Damm

OFFIS, Germany

Abstract. The Speeds project has developed a layered meta-model of heterogeneous rich components and standardized approaches for the integration of commercial industry standard modeling tools to assemble system-level design models with contract-based interface specifications by combining models expressed in any authoring tool compliant to the integration standard, including Matlab-Simulink/Stateflow, Rhapsody, and Scade. It is currently integrating a range of analysis methods supporting interface compliance testing and dominance analysis between contracts expressed in extended automata model, subsuming timed automata. The presentation focuses on real-time analysis methods, and demonstrates a methodology for assessing realizability of end-to-end latencies at system level, exploring the design space of possible system configurations meeting vertical resource assumptions, and assessing compliance to such vertical assumptions based on distributed real-time schedulability analysis for FlexRay and CAN bus based target architectures.

# Panel Discussion on Formal Methods in Commercial Software Development Tools

#### Alessandro Fantechi and Alessio Ferrari

DSI - Università di Firenze, Italy

Research on formal methods for software verification currently has decades of history within academia, and it is a central topic in software engineering. Nevertheless, usage of formal methods in companies is still at its embryonic stage. The reasons of this discrepancy have to be explored and solutions have to be found in order to increase adoption of formalized verification within industry.

A panel discussion was held at the closing of the  $13^{th}$  FMICS Workshop in order to investigate this topic with invited speakers from industry and academy. The panel was introduced by two short presentations on the theme, namely:

Model-driven software development: needs and experiences in rail automation, by Stefan Milius and Uwe Steinke, from Siemens AG.

Simulink Design Verifier vs. SPIN A Comparative Case Study, by Florian Leitner and Stefan Leue from the University of Konstanz, Germany.

The participants to the panel were: Steven Miller of Rockwell Collins, Rance Cleaveland of Reactive Systems Inc., Werner Damm of OFFIS, Mark Lawford from McMaster University and Pedro Merino from the University of Malaga.

The first contribution comes from Mark Lawford. He states that the limited penetration of formal methods within industry is related to the extensive use of design tools which have no formal semantic. Tools like MATLAB are able to ease the specification part of the process, giving the developer a high level of freedom and flexibility; in part because there are no strong formal constraints inherent within these tools. While speeding up the specification and development phase of the process, this approach creates problems in the verification phase: if no formal specification is given, how can formal verification take place? Formal methods are then "bolted onto the side" of existing software development processes, effectively creating two models of the system - the informal one used by the developers and the formal one used by the verifiers. Maintaining consistency of these models becomes an additional burden. The way to achieve a higher rate of adoption of formal methods in the industry is to create integrated methods supported by integrated tools.

Rance Cleaveland has a different opinion: there is no need to disrupt the specification phase, since this is currently well established in companies, and it has a sufficient degree of formalization. The focus has to be raised to the process level, and strategies have to be explored to allow adaptation of the formal verification task into existing processes. A software process is built on the concept of Who will press Which mouse button, When? In industries people live according to the tasks performed by other people, tasks that someone has to undertake, and this chain has to be well defined and strongly consistent. Any

D. Cofer and A. Fantechi (Eds.): FMICS 2008, LNCS 5596, pp. 4–6, 2009.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2009

development tool, whether formally based or not, in order to achieve adoption within a company needs to have the process implications explained: how the process can be more efficient, which activities can be removed, which tasks have to be added in order to accommodate the new tool. The problem is again Who will press Which mouse button When?, and with the new tool new mouse buttons come, and the path to reach the integration has to be explained. Concerning modeling tools the solution to this issue is currently quite stable. Every year there is a large number of publications on Model Based Development processes, and therefore industries interested in MBD have templates for understanding how to include the modeling tools into their development processes. In the case of verification tools this is not so clear. The incorporation of verification into the workflow is an issue that must be solved. In order to have a predictable development flow the company has to understand when the model checking task takes place, who has to be trained, and who will actually press the button verify. Furthermore, the relationship with the existing V&V activities, such as unit testing and integration testing, needs also to be fixed. Solutions to these problems have to be given by the tool vendors, to enable companies understanding when to use the verification tools, and which tool is more suitable for their needs.

Werner Damm enforces the point of view of Rance Cleaveland, stating that technology is nothing from the industrial perspective, and what is required is process integration. He also agrees on the fact that formal verification has to productively deal with industry standard design tools, such as MATLAB. But this does not mean that one single modeling and analysis tool can be enough. The categories of design situations which a company has to work on are so diverse, ranging from system architecture design, requirement capturing, code generation, that there will never be a single formalism expressive enough, adaptable enough, to fit with this many different categories of design situation. Therefore, formal verification has to cope with commercial tools, but one tool will not be enough. This need for diversity is also enforced by the issue of the maintainability of the process chain in an industry. A solution to this, is to get to open-source tools and create a community of researchers supporting them. In order to realize this objective another step is required. The key resides in agreeing on a common suite of standard meta-models, and ensure interoperability according to the meta-models. Given this accepted standard, open-source solutions can be created with the support of the research community. On the other hand it is essential to create a market environment where companies are pushed to merge, in order to build a critical mass and in so doing, create commercial alternatives to monopoly situations. The point of arrival is an environment in which commercial solutions are completed by open-source ones, no monopolist is dominating the market and interoperability is guaranteed by the meta-models standard.

Rance Cleaveland agrees on the necessity of defining a standard meta-model, but he completely disagree with Werner Damm on the role of the open source community. His opinion is that, with open source, nobody's leverage depends on the selling of the software and therefore its quality tends to degrade. Therefore a standard is needed in order to let companies comply this standard with their tool.

On the other side Werner Damm points out that the question of maintenance of open source solutions is generally not so negative as described by Rance Cleaveland, since there are companies providing services around open source tools and therefore these companies would be in charge of providing maintenance. Though Pedro Merino agrees on the part that open source tools can play in disrupting monopoly, he is doubtful on the actual role that the meta-modeling standard can play. Pedro Merino has been also working on proposals for such meta-languages, however, according to the past experience with operating systems and network standards, he believes that defining a common language or infrastructure does not imply that software vendors will produce tools supporting it.

As a final argument for the discussion, Steven Miller shows how the interoperability pointed by Werner Damm can be achieved with the existing tools and technologies, and who are the subjects involved. In the Rockwell Collins Translation Framework, SCADE and MATLAB models are translated into the Lustre formal language, and then verified through different analysis tools, both commercial and open source. In the future this approach could be extended, with multiple modeling tools on one side, multiple analysis tools on the other side, but just one standardized modeling language; it being Lustre, SAL, or AP233. The subjects involved on the modeling tools side will probably be the commercial software vendors, while the subjects developing analysis and verification tools will more likely be academies and researchers.

# LETO - A Lustre-Based Test Oracle for Airbus Critical Systems

Guy Durrieu<sup>1</sup>, Hélène Waeselynck<sup>2</sup>, and Virginie Wiels<sup>1</sup>

<sup>1</sup> ONERA, Centre de Toulouse, 2, Avenue E. Belin, BP 74025, 31077 Toulouse Cedex 4, France {Guy.Durrieu,Virginie.Wiels}@cert.fr http://www.cert.fr

<sup>2</sup> LAAS-CNRS, Université de Toulouse 7, Av du Colonel Roche, 31077 Toulouse Cedex 4, France Helene.Waeselynck@laas.fr http://www.laas.fr

**Abstract.** This paper presents an approach and an associated tool that have been proposed to automate the test oracle procedure of critical systems developed at Airbus. The target tests concern the early validation of the SCADE design and are performed in a simulated environment. The proposed approach and tool have been successfully applied to several Airbus examples.

**Keywords:** Test oracle, automation, formal methods, avionics.

#### 1 Introduction

This paper presents the results of an R&D study conducted for Airbus, that aimed to increase their current level of test automation. The target tests concern the early validation of critical systems and are performed in a simulated environment.

The test oracle procedure was identified as a candidate for automation. A test oracle is a mechanism for determining whether or not a program produced correct outputs during testing. The availability of such a mechanism has been recognized as problematic for a long time [1]. Considering the importance of the problem, there has been comparatively little work in the testing literature to investigate adequate solutions. Still, some approaches have been proposed (see [2] for an overview), ranging from contract-based assertions to model-based test approaches where a behavioral model is used in both the generation of test cases and the determination of outputs. Such approaches are not widespread in industry yet. In practice, the test result analysis is almost always done manually, the tester playing the role of the oracle. Such is currently the case at Airbus.

We report here on the automated solution we have proposed to Airbus. It has been implemented as prototype tool, LETO (LustrE-based Test Oracle) to demonstrate the concept. Lustre [7] is a formal language for reactive systems. In the spirit, LETO is close to other approaches using Lustre-based synchronous

D. Cofer and A. Fantechi (Eds.): FMICS 2008, LNCS 5596, pp. 7–22, 2009.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2009

observers to check the test execution [3] [4]. However, the implementation is different due to the constraints put by the Airbus test environment. In particular, the test traces are analyzed off-line.

The paper starts by a presentation of the industrial context. Section explains which test phase of the Airbus development process is addressed by our work. Section summarizes the insights we gained from the analysis of current practice for this test phase. We identified high-level requirements for an automated oracle. Section presents the oracle approach retained to fulfill these requirements. The approach has been implemented in LETO (Section ) and experimented on real examples supplied by Airbus (Section ). Concluding remarks are provided in Section 7.

#### 2 Development Process and Target Test Phase

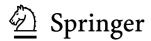

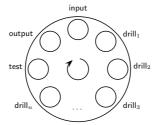

Figure 1 gives an overview of the Airbus development process. Three levels are distinguished: aircraft, system and equipment. The most critical systems, like flight control systems [9], are designed using the formal language SCADE [10]. A qualified code generator automatically generates most of the embedded code. Some validation activities are then shifted from the code to the SCADE design. Overall, the main V&V activities at Airbus are the following:

- Model tests: the considered system is validated using a desktop simulation environment called OCASIME. The environment provides a panel of commands representing possible pilot actions. It links the SCADE design to code simulating the aircraft movement and accounts for the redundancy levels in the fault-tolerant architecture. It thus makes it possible to simulate the complete system (computers, sensors, actuators, aircraft returns).

- Aircraft level simulation: several systems are validated in a simulated environment.

- Formal verification at code level [11]: Airbus uses abstract-interpretation based tools to verify non functional properties of programs (such as absence of run-time errors) and uses proof based tools to verify functional properties on the parts of the programs that are manually coded.

- Software integration tests.

- Lab tests: first tests with real equipments, on a single system or on several systems.

- Ground tests and Flight tests.

This study is focused on the model tests performed in the OCASIME environment, for the validation of the SCADE design of one system (e.g., the flight control system). Based on the detailed requirements, a test specification document (PGE, for *Programme Général des Essais* in the Airbus terminology) gives the functional test objectives to be covered. The testers then define concrete test scenarios to address the objectives, with possibly several scenarios per objective. The scenarios are implemented and run using OCASIME. The simulation API offers much flexibility to inject stimuli on data, and to select the variables to be

Fig. 1. Airbus development process

monitored. The test trace is then manually analyzed to determine whether the system passes or fails the test. To facilitate analysis, the tester can use the visual support of time diagrams showing the evolution of the monitored variables.

During the life cycle of a system, several versions of the design are to be tested. OCASIME offers facilities to automate the execution of regression tests. However, the analysis of the regression test results remains manual for a large part: as soon as the test trace is not strictly identical to the previously recorded one, manual analysis has to determine whether or not the observed discrepancies reveal a fault. In practice, it turns out that a number of discrepancies are observed, and that most of them are unimportant. For example, the bits of a floating point variable may not be identical from one execution to the other (difference in the value domain), but the corresponding values are actually very close within some epsilon tolerance. Or it may be observed that a Boolean variable changes from False to True at a slightly different simulation step (difference in the time domain), but once again this falls within some time tolerance interval. Hence, the analysis of results is time consuming not only for the first execution of the test, but also for all executions with successive design versions. A significant gain could be expected from the automation of the test oracle procedure.

# 3 Requirements for an Automated Test Oracle Procedure

Our analysis of the industrial context allowed us to identify some high-level requirements for an automated oracle approach.

In order to simplify the interfacing with the OCASIME environment, it was decided that the oracle tool would perform off-line analysis of test traces. In this way, the tool can be designed as an independent facility, with the only constraint that it should accept the XML file format of OCASIME traces.

The oracle checks should be defined at a higher level than raw expected values. Rather, the tester should be given the possibility of expressing properties relating the input and output values, in a declarative way. The properties are expected to formalize statements from the documents that are currently used as references for the manual analysis, namely the PGE and the detailed system requirements. In order to gain deeper insights into such properties, we analyzed examples extracted from three different functions of flight control systems: sidesticks, autopilot, and ADIRS (Air Data and Inertial Reference System). Related documentation was made available to us, including detailed functional requirements, PGE and concrete scenarios. We also had meetings and interviews with testers.

Analysis showed that a rich specification language is needed for the formalization of properties, with logical, arithmetic as well as temporal operators. An example, to be developed later in this paper, concerns the acquisition of ADIRS data. Some numerical input parameters are acquired from three independent sources. One of the test objectives is to test whether a single faulty source is correctly identified and locked out. The source is identified as faulty if the delivered value departs from the median of the three values for more than a predefined threshold, and does so during a given period of time. Once declared faulty (a Boolean alarm is set to true), the source is locked out (the alarm remains true forever, and the acquired value is no longer considered). The consolidated value of the acquired parameter is then the mean of the two remaining sources. For this test, it can be seen that the oracle checks involve a mix of numerical (calculation of difference from median, of a mean value), logical (determination of the mode for calculating the consolidated value) and temporal (persistence during a time interval, or forever) concerns.

The latter example is representative of a case where the output values are completely determined: the specified properties are actually formulas to derive outputs from the inputs. In other cases, the oracle checks may involve invariant properties to be satisfied whatever the specific values produced during the scenario. For example, in a test objective for sidesticks, a given output parameter has to remain within a safety range, and the calculation for the bounds of the range has to account for both the current and past inputs (numerical and temporal operators). We thus have two classes of oracle checks:

- Checks for equality. A sequence of expected outputs is computed by the oracle according to a specified formula, and compared to actual outputs. Such checks should explicitly accommodate a tolerance in both the value and time domains, as explained in the discussion of regression testing (Section ≥ last paragraph).

- Assertion checks. Rather than computing expected values, the oracle checks for the validity of more general properties relating inputs and outputs.

The tester should have flexibility in using the logical, numerical and temporal operators for the specification of both classes of checks.

Finally, an important outcome of our analysis was the observation that a number of test objectives are repeatedly found with parameterization variants. This is due to symmetries in the Flight Control system. An obvious example of symmetry arises from redundancy in the fault-tolerant architecture: variants of a same test objective are found for the three primary computers and their COM/MON channels (see for an overview of Airbus architectures). Also, inside a given computer, similar treatments may be attached to different inputs. For example, the test with a single faulty source is applicable to many ADIRS parameters. Moreover, for a target parameter, each of the sources may play the role of the faulty one. In all these examples, the same tests are repeated with some specialization to the current context (e.g., target computer, target input parameter). It would be convenient to define the corresponding oracle checks once and for all, in a generic way, with some mechanism to instantiate the checks with actual parameters.

The next section presents the approach proposed to fulfill these needs.

#### 4 Proposed Approach

In order to automate the oracle procedure, it is necessary to formalize the test objectives described in the PGE. For this, we need to choose an expressive language and to allow for a form of genericity in the description of objectives.

#### 4.1 Overview

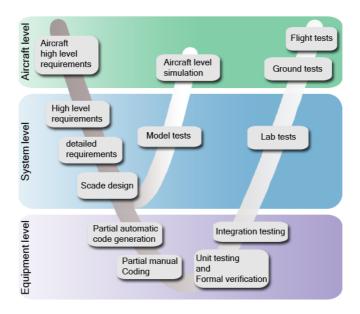

We decided to have two kinds of components to describe test objectives, respectively called *generic test schemas* and *instantiation schemas*. A generic test schema is parameterized and describes a test objective in a generic way. An instantiation schema contains a list of instantiation cases for a generic schema, hence allowing its specialization to different concrete contexts.

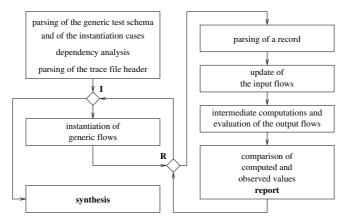

In the approach we propose (see Figure 2), the tester writes the generic schemas and instantiation schemas from the PGE. It is a supplementary task but one that will allow the automation of the oracle and that will also facilitate capitalization and reuse of test schemas. The library represented on the figure contains functions that can be used for the definition of test schemas (examples of such functions will be presented in the following), and existing test schemas that can be reused.

The tester also defines the test scenarios that will be executed on the simulator. The automated oracle will decide on the result of the test from the trace file, the generic and instantiation schemas.

#### 4.2 Test Schemas

In this subsection, we give the syntax of the generic and instantiation schemas. The generic schema has the following form:

Fig. 2. Proposed approach

SCHEMA generic\_schema PARAMETERS : parameters

VARIABLES : internal variables AUXILIARY : auxiliary computation TEST : expected results of test

**ENDSCHEMA**

Parameters are the generic variables that will be instantiated in the instantiation schemas. Variables and auxiliary represent internal variables and computation that may be necessary for the expression of the test part. The test part describes the expected results of the test (the oracle checks to be performed).

The instantiation schema has the following form:

```

SCHEMA inst_schema

FOR A in {a1,a2,a3}

FOR B in {b1,b2,b3}

generic_schema(A,B)

ENDFOR

ENDFOR

```

For each generic parameter, a list of actual variables can be given. The schema above means that the generic schema will be considered 9 times (generic schema(a1,b1), generic schema(a1,b2), generic schema(a1,b3), generic schema(a2,b1), etc).

#### 4.3 Language for the Test Section

**The need.** Concerning the "test" section, we observed that there was a need for logical, arithmetic and temporal operators. Our first intent was to define a

specific language for the test part, but after analysing the test objectives, we realised that existing languages could answer our needs, and proposed to use the Lustre language 7.

Using Lustre as a test oracle language. Using Lustre brings many advantages:

- it has a well defined semantics:

- it is well suited for the targeted type of systems, and widely used for designing critical embedded systems, in particular at Airbus: the SCADE language is actually a graphical language based on Lustre;

- there is an active working community around Lustre and the associated tools;

- it is able to handle all identified needs;

- it is a modular and hierarchical language, which could be useful to ease reuse and composition of schemas, although this aspect was not developed nor implemented in the current version of LETO;

- it is a formal declarative language, which is interesting for several reasons:

- it makes the automation of the oracle easier,

- from a more global perspective, it should be useful for establishing links with formal verification of properties that is experimented also at Airbus.

One possible inconvenience of choosing Lustre is the use of the same language for describing the system and for specifying the test objectives, this could hinder the necessary independence between development and verification. This inconvenience will have to be evaluated during experiments, it is however diminished by the fact that we use the textual version of the language that feels more declarative than the graphical one thanks to the the equational form.

Overview of Lustre – selected subset for the test oracle. As previously said, Lustre is a functional declarative language, the application field of which is the specification of control and signal processing systems. It belongs to the family of synchronous languages for which, different tools oriented towards the design of safety-critical embedded systems have been developed during the last decade [8], the Scade suite among others [10]. Synchrony divides time into discrete instants, and a synchronous program progresses according to successive atomic reactions, which implies a notion of clock defining the instants where reactions occur. Data are represented as infinite flows of typed values, each value corresponding to an instant, and operations on data are specified as flow equations. A Lustre program is thus a set of equations with neither a notion of control nor of sequentiality: the equation set is reevaluated at each instant on a data flow control basis (maybe concurrently). A specific function, called pre, allows us to get the value of a flow at the previous instant; another specific function, ->, allows us to specify, if necessary, the value of a flow at the first instant.

Besides the arithmetic, logic, conditional and temporal operations required for writing equations Lustre includes:

- the notion of *assertion*, allowing us to specify a condition that must hold at all instants of the execution of a Lustre program;

- the notion of *node*, supporting modularity and hierarchy: this notion simply generalizes the notion of operator;

- a set of operations allowing calculus on clocks.

For a first version of our test language, we only needed the basic equation specification part of Lustre, and some additional basic temporal operators, allowing us to easily express temporal properties, such as during, the result of which is true when a given condition holds for a given time interval. The syntax of Lustre equations was embedded in the TEST part of the schemas. The notion of assertion was also included in our test language. Finally, syntactic constructs allowing the specification of value and time tolerances (see Section 5 "Oracle") were added to the basic equation syntax.

The semantics, however, is here slightly different from the semantics of standard Lustre, since we refer to the contents of a trace file instead of the execution of a program; that is, an instant corresponds to a simulation step (associated to a time value), and the value of a tested variable corresponds to the measured value at this time (which must agree with the expected value defined by the corresponding equation); the value returned by the pre function for a tested variable is the value of the tested variable at the previous measure; an assertion allows to verify that a given condition holds for all the measures recorded in the considered trace file.

In a later version, the test language would include the Lustre notion of node, which would be useful for reusing and composing schemas, or for extending the set of basic operators.

#### 4.4 Illustration

We illustrate here the concepts of generic and instantiation schemas on a case study.

Case Study. We present here a case study extracted from the ADIRS PGE. ADIRS deals with the acquisition of several parameters necessary for the flight control system (such as altitude, speed, angle of attack). For each of these parameters, redundant sensors exist and a consolidated value is computed from the set of input values available. The treatment is the same for a certain number of parameters, we will consider the test objectives defined for the nominal case and the case where one of the input is out of range. Thanks to our generic approach, we were able to define a generic schema that was applicable for several parameters.

- Nominal case: the PGE says "Verify that the consolidated value is equal to the median of the three input values".

- Faulty case: the PGE says "Inject a divergence on each of the three input values (one at a time). For each case, verify that the consolidated value is equal to the average of the two remaining values".

The case study presented is of course only part of the real treatment. We have simplified it for the paper but our approach was able to handle the complete treatment and other complex examples (see Section 5).

Generic schemas. The generic schema for the nominal case is the following.

#### SCHEMA Nominal

The schema has two generic parameters *input* which is an array of three inputs and *consolidated* the consolidated value. The consolidated value should be the median of the three input values.

The generic schema for the faulty case is the following.

```

SCHEMA Faulty

-- In this schema, we suppose it is the first input that is faulty --

______

-- the functions:

- median

- half_sum

-- are defined in a standard library

PARAMETERS :

input : real^3 ;

-- the 3 inputs

-- threshold, confirmation delay

s, confirm : real ;

consolidated : real ;

-- consolidated value

VARIABLES :

fault : bool ;

t : bool ;

m : real ;

hs : real ;

AUXILIARY :

m = median(input[0], input[1], input[2]);

t = abs(input[0] - m) > s;

hs = half_sum(input[1], input[2]);

fault = false -> during(confirm, t) or pre fault;

consolidated = if fault then hs else m ;

ENDSCHEMA Faulty

```

For the faulty case, two generic parameters are added that represent the threshold and the confirmation delay. A fault is defined as the fact that the difference between the input value and the median is greater than the threshold during a time that is greater or equal to the confirmation delay.

In this schema, we suppose that it is the first input that is faulty, we will see in the instantiation schema how to apply this generic schema in order to handle the fault for each of the three inputs.

*Tolerances*. If necessary, tolerances can be added on real values or time for the change of boolean value, the syntax is the following:

```

fault = false -> during(confirm, t) or pre fault timetolerance 1;

consolidated = if fault then hs else m realtolerance 0.02;

```

Assertions. It is also possible to define assertions inside test schemas to verify that a given expression is true. In the ADIRS PGE, the test objectives include verification on the value of a certain number of booleans representing alarms in case of faults. The schema above gives an example of an assertion that states that the boolean should becomes true between time 4 and time 8 (between is an operator encoded in the tool).

```

SCHEMA Alarm

PARAMETERS :

bool_alarm : bool ;

VARIABLES :

AUXILIARY :

TEST :

assert between(4.0, 8.0, bool_alarm) ;

ENDSCHEMA Alarm

```

**Instantiation Schemas.** An instantiation schema for the nominal case could be the following.

```

SCHEMA InstantiatedNominal

FOR COMPUTER IN { "1", "2", "3" }

FOR UNIT IN { COM, MON }

FOR consolidated IN { ALPHA },

input IN { [ALPHA1, ALPHA1, ALPHA3] },

TRACEFILE IN

{"${AUT_ORACLE}/ALPHA_P123.ras"}

Nominal(input, consolidated)

ENDFOR

ENDFOR

ENDFOR

ENDFOR ENDSCHEMA InstantiatedNominal

```

The instantiation schema states that the generic schema will be applied for the parameter alpha (angle of attack), for three primary computers and two units of each computer.

An instantiation schema for the faulty case could be the following.

```

SCHEMA InstantiatedFaulty

FOR TRACEFILE IN {"${AUT_ORACLE}/Faulty_ALPHA_P123.ras" }

FOR s IN { 3.6 }

FOR confirm IN { 100 }

FOR consolidated IN { ALPHA }

FOR COMPUTER IN { "1", "2", "3" }

FOR UNIT IN { COM, MON }

FOR input IN { [ALPHA1, ALPHA2, ALPHA3],

[ALPHA2, ALPHA1, ALPHA3],

[ALPHA3, ALPHA1, ALPHA2]

Faulty(input, s, confirm, consolidated)

ENDFOR.

ENDFOR

ENDFOR.

ENDFOR

ENDFOR

ENDFOR

ENDFOR

ENDSCHEMA InstantiatedFaulty

```

In addition to the different computers and units as before, this instantiated schema allows the application of the generic schema to handle the divergence of each of the three inputs, as specified in the PGE.

## 5 Implementation of the Approach

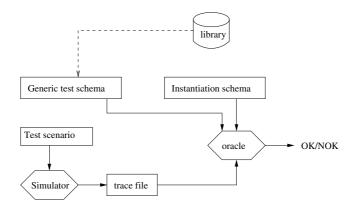

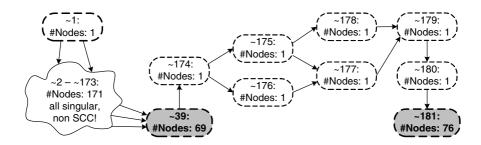

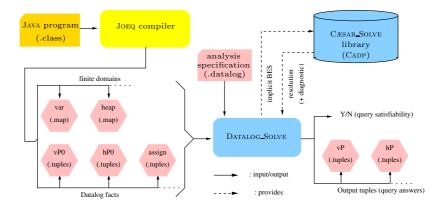

An experimental oracle prototype, based on the principles described in the previous sections, was developed in Java. Figure 3 shows the main features of this prototype, called LETO (LustrE-based Test Oracle). The main components are briefly described below.

**Schema Parsing.** The oracle prototype requires as inputs:

- a file containing the generic test schema, which specifies the expected relations between the measured flows.

- a file containing the instantiation cases, which binds the formal names used within the generic schema to the real names found in the trace files, and allow to iterate the use of a generic schema on different measure sets.

JavaCC  $\square$   $\square$  has been used for the development of a parser accepting the syntax of the generic test schemas and instantiation cases. JavaCC is a parser generator which takes as input a grammar at EBNF (*Extended Backus Naur Form*) format with additional syntactic and semantic predicates, and produces a LL(k) recursive descending parser implemented as a finite state automaton. JavaCC also provides tools for automatic construction of abstract syntax trees (AST).

The schema parser is launched by the oracle, with the name of the schema files to be parsed; the AST obtained after parsing are sent back for processing to the oracle core.

Fig. 3. The experimental oracle prototype

XML Parsing. In addition to test schema and instantiation cases, LETO obviously accesses the trace files to be checked. These trace files adopt an XML format, with a header specifying the registered signals and a sequence of records containing the measured values at given instants.

The XML parser was developed using the SAX2 toolkit. The result is a set of callback methods, activated when encountering the associated XML tags, which in turn call the appropriate processing functions within the oracle. The XML parser is launched by the oracle, with the name of the trace file to be analyzed.

#### **Oracle.** The oracle core performs three functions:

- it analyzes the generic test schema, the instantiation cases, and successively carries out the specified instantiations for the set of generic flows used in the generic test schema. The analysis of the generic test schema implies an analysis of dependencies in order to get an evaluation order for the specified equations.

- for each instantiation it launches the parsing of the specified trace file; for each measure record, it performs the verification specified in the test schema with help of the evaluator, that is, given the current set of measures, it computes the expected value of the tested flows and compares the result to their measured value with some specified tolerance (see below); it is also able to check that a given condition (or assertion) is verified on the whole trace file; if necessary, it issues warning messages. For each measure record, it manages the current and previous values of each flow.

- at the end of each iteration, it produces a report summarizing the results obtained while processing the trace file.

As suggested above, some differences between the expected and measured values may be meaningless from the test validity point of view; this can be taken into account by associating *tolerances* to the relevant equation. Two kinds of tolerance are considered:

- value tolerance: if the difference between the expected and measured values

is less than a given bound, no discrepancy message is issued; this kind of

tolerance is mainly used for floating point measures (e. g. a sensor measure).

- time tolerance: if the duration of the discrepancy between the expected and measured values is less than a given number of clock ticks, no discrepancy message is issued; this kind of tolerance is mainly used for boolean measures (e. g. an alarm signal).

**Evaluator.** Given a set of value for the flows defined in the generic test schema, the evaluator is able to compute, on request of the oracle core, the results of any arithmetic and logical expression specified in the schema.

Graphical User Interface. In order to help in the design and experimentation of generic test schemas and instantiation cases, a graphical user interface has

Fig. 4. Screen shot of the LETO graphical user interface

- I: instantiation loop; for each instantiation case the R loop is processed.

- **R:** record loop; for a given instantiation, the set of test records is processed.

Fig. 5. General algorithm of the oracle prototype

been developed, allowing us to easily specify the names of the involved files, global tolerance, to start the analysis process and to display the results. However, the use of this graphical interface is not mandatory, and the normal mode for exploiting the automated interface is the batch mode.

Figure 4 shows a screen shot of the graphic user interface of the oracle prototype.

The upper part allows us to specify the generic schema and the instantiation cases which are to be used. The middle part contains several buttons for starting the analysis, enter debug modes and save the log pane contents located in the lower part of the GUI. At the end of the analysis, the visual indicator located at the left of the middle part is green if no discrepancy has been detected, and red otherwise.

Figure 5 summarizes the general algorithm of the oracle prototype.

## 6 Experiments and Results

The approach described in this paper was successfully used on several industrial cases coming from the avionic world, specifically from the AIRBUS A380. The checked trace files, for example, were dealing with:

- the Air Data & Inertial Reference System: it was to be verified that in the trace file the right value was correctly selected by the logic managing the redundancy in each operational case (nominal, one or more faulty sources).

- the pilot environment (side sticks): it was to be verified that the electrical signal generated by the command devices always evolved within the expected domain.

The experiments carried out showed a good proximity between the values computed by the oracle and the values found in the trace files. Few discrepancies were detected by the oracle, which all were explained either by a too restrictive tolerance or by a slight time shift between the oracle and the trace file; once these discrepancies explained, it was possible to parameterize the oracle (tolerances on value and on time) in order to avoid irrelevant alerts.

It was also important from the project point of view to evaluate the perception of the tool, and more specifically of the test language, by Airbus people in charge of carrying out the test campaigns. This was done through some "practical exercises" which allowed several of these Airbus test experts to experiment the Lustre specifying style as well as the whole test automation approach on the above practical industrial cases, and to observe the potential effort savings.

#### 7 Conclusion

We have proposed an approach to automate the test oracle procedure for a given industrial context. The approach has been implemented in a tool, applied to a set of representative case studies and has been successful in answering the identified needs. In particular, it is very useful to handle non regression tests in an efficient way: our approach verifies the simulation results against expected I/O properties (which are quite stable) and not against the raw results of the previous simulations. An industrial deployment of the approach would now necessitate further methodological work: choice of the best granularity for the test schemas, definition of the library of functions necessary for the test schemas definition.

The existing industrial context imposed some constraints on the solutions that could be proposed. For example, the automated oracle checks had to be done off-line. They could not be done during test execution, for technical reasons regarding the implementation of the OCASIME simulator. However, the approach and tool we proposed may be used in other industrial contexts. The specific part is the format of the trace files, but given it is provided in an XML format, the necessary changes to the LETO tool are not prohibitive. The principle of the test schemas and the chosen language for these schemas is intended to be well adapted to critical embedded systems in general. The test schemas are generic and can be instantiated for several concrete cases. They also establish a formal traceability between the test specification document (e.g., PGE in the Airbus context) and the corresponding tests. By essence, test schemas are less ambiguous and more informative than informal test specification documents. Their definition requires supplementary work but this work can be capitalized and reused.

Several themes are interesting for future work. Composition operations could be investigated to further facilitate the definition of test schemas from existing ones. We are also studying a similar notion of schemas for the activation part of the test: generic and instantiated schemas could be used to formalize, store and reuse activation functions for test scenarios. Finally and in a more distant perspective, existing lustre-based tools could allow automatic generation of test scenarios.

Acknowledgements. This work was supported by an Airbus contract. We would like to thank Jean-Jacques Aubert and Pierre Virelizier for their constant support during the project and for their comments on this paper.

#### References

- Weyuker, E.: On Testing Non-Testable Programs. The Computer Journal 25(4), 465–470 (1982)

- Baresi, L., Young, M.: Test oracles. Technical Report CIS-TR01-02, Univ. of Oregon (2001)

- 3. Raymond, P., Weber, D., Nicollin, X., Halbwachs, N.: Automatic Testing of Reactive Systems. In: 19th IEEE Real-Time Systems Symposium (RTSS 1998), pp. 200–209. IEEE CS Press, Los Alamitos (1998)

- 4. Parissis, I., Vassy, J.: Strategies for Automated Specification-based Testing of Synchronous Software. In: 16th IEEE Int. Conf. on Automated Software Engineering (ASE 2001), pp. 364–367. IEEE CS Press, Los Alamitos (2001)

- 5. Copeland, T.: Generating Parsers with JavaCC. Centennial Books, Alexandria (2007)

- 6. javacc Project home, <a href="http://javacc.dev.java.net/">http://javacc.dev.java.net/</a>

- Halbwachs, N., Caspi, P., Raymond, P., Pilaud, D.: The synchronous dataflow programming language LUSTRE. Proceedings of the IEEE 79(9), 1305–1320 (1991)

- 8. Benveniste, A., Caspi, P., Edwards, S.A., Halbwachs, N., Le Guernic, P., de Simone, R.: The Synchronous Languages 12 Years Later. Proceedings of the IEEE 91(1) (January 2003)

- 9. Traverse, P., Lacaze, I., Souyris, J.: Airbus Fly-By-Wire: A Total Approach to Dependability. In: Building the Information Society, 18th IFIP World Computer Congress (WCC 2004), pp. 191–212. Kluwer, Dordrecht (2004)

- Esterel Scade Suite,

http://www.esterel-technologies.com/products/scade-suite

- Duprat, S., Souyris, J., Favre-Flix, D.: Formal Verification Workbench for Airbus Avionics Software. In: Embedded Real-Time Software (ERTS 2006). SIA (2006)

# Extending Structural Test Coverage Criteria for LUSTRE Programs with Multi-clock Operators

Virginia Papailiopoulou, Laya Madani, Lydie du Bousquet, and Ioannis Parissis

University of Grenoble - Laboratoire d'Informatique de Grenoble BP 72 - 38402 Saint-Martin d'Hères Cedex France {Virginia.Papailiopoulou,Laya.Madani,Lydie.du-Bousquet, Ioannis.Parissis}@imag.fr

**Abstract.** Lustre is a formal synchronous declarative language widely used for modeling and specifying safety-critical applications in the fields of avionics, transportation or energy production. Testing this kind of applications is an important and demanding task during the development process. It mainly consists in generating test data and measuring the achieved coverage. A hierarchy of structural coverage criteria for Lus-TRE programs have been recently defined to assess the thoroughness of a given test set. They are based on the operator network, which is the graphical representation of a LUSTRE program and depicts the way that input flows are transformed into output flows through their propagation along the program paths. The above criteria definition aimed at demonstrating the opportunity of such a coverage assessment approach but doesn't deal with all the language constructions. In particular, the use of multiple clocks has not been taken into account. In this paper, we extend the criteria to programs that use multiple clocks. Such an extension allows for the application of the existing coverage metrics to industrial software components, which usually operate on multiple clocks, without negatively affecting the complexity of the criteria.

#### 1 Introduction

Synchronous software is normally part of safety-critical applications in such domains as avionics, transportation and energy. Formal specification is usually required to model the system behavior along the different levels of the development process. Such a specification not only describes the correct function of the system but also it defines the conditions under which that correct function is reached. That specification can be further used to automatically generate test data.

Several programming languages have been proposed to specify and implement synchronous applications, such as Esterel [2], Signal [8] or Lustre [5]]. Lustre is a declarative, data-flow language, which is devoted to the specification of real-time applications. It provides formal specification and verification facilities and ensures efficient C code generation. It is based on the synchronous approach which demands that the software reacts to its inputs instantaneously. In practice, that means that the software reaction is sufficiently fast so that every change in the external environment is taken into account. As soon as the

D. Cofer and A. Fantechi (Eds.): FMICS 2008, LNCS 5596, pp. 23–36, 2009.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2009

order of all the events occurring both inside and outside the program is specified, time constraints describing the behavior of a synchronous program can be expressed [6]. These characteristics make it possible to efficiently design and model synchronous systems.

A graphical tool dedicated to the development of critical embedded systems and often used by industries and professionals is SCADE (Safety Critical Application Development Environment). SCADE is a graphical environment used in the development of safety-critical embedded software. It is based on the Lustree language and it allows the hierarchical definition of the system components and the automatic code generation. From the SCADE functional specifications, C code is automatically generated, though this transformation (SCADE to C) is not standardized. This graphical modeling environment is used mainly in the aerospace field (Airbus, DO-178B); however its capabilities serve also transportation, automotive and energy.

In major industrial applications, the testing process usually consists in producing test cases based on the functional requirements of the system under test. Test objectives and test data are constructed with regard to the system requirements and the coverage evaluation is applied on the generated C code. For programs written in sequential languages, several adequacy criteria have been presented in the past, such as path/branch coverage criteria, LCSAJ (Linear Code Sequence And Jump) 10 and MC/DC (Modified Decision Condition Coverage).

These criteria are not conformed with the synchronous paradigm and cannot be applied on Lustre programs to assess how thoroughly the produced test data have tested the corresponding specification. Furthermore, it is difficult to formally relate the coverage measurement results with the system specification and the test objective. To deal with this problem, especially designed structural coverage criteria for LUSTRE programs have been proposed [7]. Although these criteria are comparable to the existing data-flow based criteria [9,3], they are not the same. They aim at defining intermediate coverage objectives and estimating the required test effort towards the final one. These criteria are based on the notion of the activation condition of a path, which informally represents the propagation of the effect of the input edge through the output edge.

However, the above coverage criteria can be applied only on specifications that are defined under a unique global clock. The global clock is a boolean flow that always values true and defines the frequency of the program execution cycles. Other, slower, clocks can be defined through boolean-valued flows. They are mainly used to prevent useless operations of the program and to save computational resources by forcing some program expressions to be evaluated strictly on specific execution cycles. Thus, nested clocks may be used to restrict the operation of certain flows when this is necessary, without affecting at the same time the rest of the program variables. In LUSTRE, using multiple clocks is made through two specific operators, when and current. In this paper, we propose the extension of the existing coverage criteria taking into account the when and current operators. In fact, we define the activation conditions for the paths containing these operators in order that the coverage criteria are applicable on

such paths. The complexity of the criteria, in terms of the cost of computing the paths and their activation conditions, is not increased.

The paper is structured in three main sections. Section 2 provides a brief overview of the essential concepts on LUSTRE language. Section 3 presents the existing coverage criteria for LUSTRE programs while in section 4 we thoroughly demonstrate their extension to the use of multiple clocks. Section 5 concludes and shows some perspectives for future work.

#### 2 Overview of Lustre

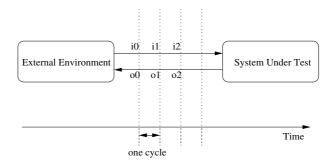

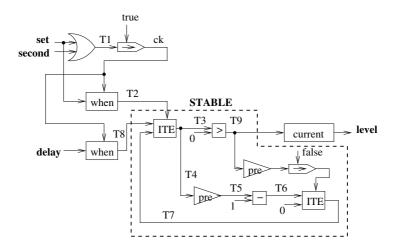

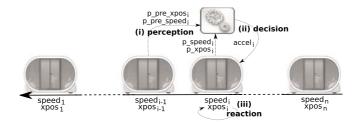

LUSTRE  $\boxed{5}$  is a data-flow language. Contrary to imperative languages which describe the control flow of a program, LUSTRE describes the way that the inputs are turned into the outputs. Any variable or expression is represented by an infinite sequence of values and take the n-th value at the n-th cycle of the program execution, as it is shown in Figure  $\boxed{1}$  At each tick of a global clock, all inputs are read and processed simultaneously and all outputs are emitted, according to the synchrony hypothesis.

A LUSTRE program is structured into nodes. A node is a set of equations which define the node's outputs as a function of its inputs. Each variable can be defined only once within a node and the order of equations is of no matter. Specifically, when an expression E is assigned to a variable X, X=E, that indicates that the respective sequences of values are identical throughout the program execution; at any cycle, X and E have the same value. Once a node is defined, it can be used inside other nodes like any other operator.

The operators supported by LUSTRE are the common arithmetic and logical operators (+, -, \*, /, and, or, not) as well as two specific temporal operators: the precedence (pre) and the initialization (->). The pre operator introduces to the flow a delay of one time unit, while the -> operator -also called followed by (fby)- allows the flow initialization. Let  $X = (x_0, x_1, x_2, x_3, \ldots)$  and  $(e_0, e_1, e_2, e_3, \ldots)$  be two LUSTRE expressions. Then pre(X) denotes the sequence  $(nil, x_0, x_1, x_2, x_3, \ldots)$ , where nil is an undefined value, while  $X \rightarrow E$  denotes the sequence  $(x_0, e_1, e_2, e_3, \ldots)$ .

Fig. 1. Synchronous software operation

Fig. 2. Example of a LUSTRE node

true false false ...

true

never A

LUSTRE does not support loops (operators such for and while) nor recursive calls. Consequently, the execution time of a LUSTRE program can be statically computed and the satisfaction of the synchrony hypothesis can be checked.

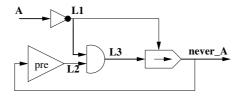

A simple LUSTRE program is given in Figure 2 followed by an instance of its execution. This program has a single input boolean variable and a single boolean output. The output is *true* if and only if the input has never been *true* since the beginning of the program execution.

#### 2.1 Operator Network

The transformation of the inputs into the outputs in a Lustree program is done via a set of operators. Therefore, it can be represented by a directed graph, the so called operator network. An operator network is a graph with a set of N operators which are connected to each other by a set of  $E \subseteq N \times N$  directed edges. Each operator represents a logical or a numerical computation. With regard to the corresponding Lustree program, an operator network has as many input edges (respectively, output edges) as the program input variables (respectively, output variables).

Figure 3 shows the corresponding operator network for the node of Figure 2

Fig. 3. The operator network for the node Never

An operator represents a data transfer from an input edge into an output edge. There are two kinds of operators:

- a) the basic operators which correspond to a basic computation and

- b) the compound operators which correspond to the case where in a program, a node calls another node.

<sup>&</sup>lt;sup>1</sup> For the time being, we only consider basic operators.

A basic operator is denoted as  $\langle e_i, s \rangle$ , where  $e_i$ , i = 1, 2, 3, ..., stands for its inputs edges and s stands for the output edge.

#### 2.2 Clocks in Lustre

In LUSTRE, any variable and expression denotes a flow, i.e. each infinite sequence of values is defined on a clock, which represents a sequence of time. Thus, a flow is the pair of a sequence of values and a clock.

The clock serves to indicate when a value is assigned to the flow. That means that a flow takes the n-th value of its sequence of values at the n-th time of its clock. Any program has a cyclic behavior and that cycle defines a sequence of times, i.e. a clock, which is the  $basic\ clock$  of a program. A flow on the basic clock takes its n-th value at the n-th execution cycle of the program. Slower clocks can be defined through flows of boolean values. The clock defined by a boolean flow is the sequence of times at which the flow takes the value true.

Two operators affect the clock of a flow: when and current.

when is used to **sample** an expression on a slower clock. Let E be an expression and B a boolean expression with the same clock. Then X=E when B is an expression whose clock is defined by B and its values are the same as those of E's only when B is true. That means that the resulting flow X has not the same clock with E or, alternatively, when B is false, X is not defined at all.

current operates on expressions with different clocks and is used to **project** an expression on the immediately faster clock. Let E be an expression with the clock defined by the boolean flow B which is not the basic clock. Then Y=current(E) has the same clock as B and its value is the value of E at the last time that E was E was true. Note that until E is E is true for the first time, the value of E will be E will be E and E and E will be E and E are E are E and E are E and E are E and E are E and E are E are E and E are E are E and E are E and E are E are E are E are E and E are E are E are E and E are E are E and E are E and E are E are E are E and E are E and E are E are E are E and E are E and E are E and E are E are E are E are E are E are E and E are E are E are E are E are E and E are E and E are E are E are E are E are E and E are E are E are E are E and E are E are E are E are E and E are E are E are E are E and E are E are

The sampling and the projection are two complementary operations: a projection changes the clock of a flow to the clock that the flow had before its last sampling operation. Trying to project a flow that was not sampled produces an error. Table provides the use of the two temporal LUSTRE operators in more details.

| Е            | $e_0$       | $e_1$       | $e_2$       | $e_3$       | $ e_4 $     | $e_5$       | $e_6$       | $e_7$       | $e_8$       |  |

|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--|

| В            | false       | false       | true        | false       | true        | false       | false       | true        | true        |  |

| X=E when B   |             |             | $x_0 = e_2$ |             | $x_1 = e_4$ |             |             | $x_2 = e_7$ | $x_3 = e_8$ |  |

| Y=current(E) | $y_0 = nil$ | $y_1 = nil$ | $y_2 = e_2$ | $y_3 = e_2$ | $y_4 = e_4$ | $y_5 = e_4$ | $y_6 = e_4$ | $y_7 = e_7$ | $y_8 = e_8$ |  |

Table 1. The use of the operators when and current

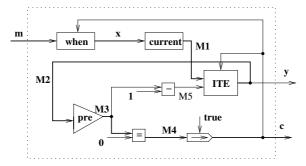

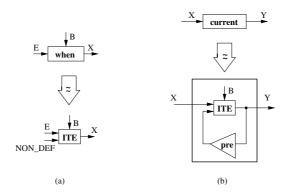

An example 4 of the use of clocks in Lustre is given in Figure 4.

The LUSTRE node  $\max$  receives as input the signal m. Starting from this input value when the clock c is true, the program counts backwards until zero; from this moment, it restarts from the current input value and so on.

```

node mux(m:int) returns (c:bool; y:int);

var (x:int) when c;

let

y = if c then current(x) else pre(y)-1;

c = true -> (pre(y)=0);

x = m when c;

tel;

```

Fig. 4. The mux example and the corresponding operator network

# 3 Coverage Criteria for Lustre Programs

#### 3.1 Activation Conditions

Given an operator network N, paths can be defined in the program. That is, the possible directions of flows from the input through the output. More formally, a path is a finite sequence of edges  $\langle e_0, e_1, \ldots, e_n \rangle$ , such that for  $\forall i \in [0, n-1], e_{i+1}$  is a successor of  $e_i$  in N. A unit path is a path with two successive edges. For instance, in the operator network of Figure  $\square$ , there can be found the following paths.

```

\begin{array}{l} p_1 = \langle A, L_1, never\_A \rangle \\ p_2 = \langle A, L_1, L_3, never\_A \rangle \\ p_3 = \langle A, L_1, never\_A, L_2, L_3, never\_A \rangle \\ p_4 = \langle A, L_1, L_3, never\_A, L_2, L_3, never\_A \rangle \end{array}

```

Obviously, one could discover infinitely many paths in an operator network depending on the number of cycles repeated in the path (i.e. the number of pre operators in the path). However, we only consider paths of finite length by limiting the number of cycles. That is, a path of length n is obtained by concatenating a path of length n-1 with a unit path (of length 2). Thus, beginning from unit paths, longer paths could be built; a path is finite if it contains no cycles or if the number of cycles is limited.

A boolean LUSTRE expression is associated with each pair  $\langle e, s \rangle$ , denoting the condition on which the data flows from the input edge e through the output s.

| Operator                   | Activation condition                     |

|----------------------------|------------------------------------------|

| s = NOT(e)                 | $AC\left( e,s\right) =true$              |

| $s = AND\left(a, b\right)$ | AC(a, s) = not(a)  or  b                 |

|                            | AC(b,s) = not(b) or a                    |

| s = OR(a, b)               | AC(a, s) = a  or  not(b)                 |

|                            | AC(b,s) = b  or  not  (a)                |

| s = ITE(c, a, b)           | $AC\left( c,s\right) =true$              |

|                            | $AC\left( a,s\right) =c$                 |

|                            | AC(b,s) = not(c)                         |

| relational operator        | $AC\left( e,s\right) =true$              |

| s = FBY(a, b)              | $AC(a, s) = true \rightarrow false$      |

|                            | $AC(b,s) = false \rightarrow true$       |

| s = PRE(e)                 | $AC(e, s) = false \rightarrow pre(true)$ |

Table 2. Activation conditions for all Lustre operators

This condition is called *activation condition*. The evaluation of the activation condition depends on what kind of operators the paths is composed of. Informally, the notion of the activation of a path is strongly related to the propagation of the effect of the input edge through the output edge. More precisely, a path activation condition shows the dependencies between the path inputs and outputs. Therefore, the selection of a test set satisfying the paths activation conditions in an operator network leads to a notion for the program coverage. Since covering all the paths in an operator network could be impossible, because of their potentially infinite number and length, in our approach, coverage is defined with regard to a given path length.

Table  $\square$  summarizes the formal expressions of the activation conditions for all LUSTRE operators (except for when and current for the moment). In this table, each operator op, with the input e and the output s, is paired with the respective activation condition  $AC\left(e,s\right)$  for the unit path  $\langle e,s\rangle$ . Noted that some operators may define several paths through their output, so the activation conditions are listed according to the path inputs.

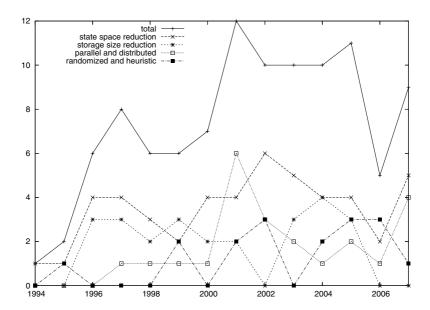

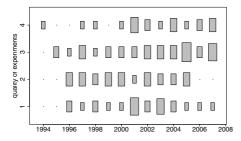

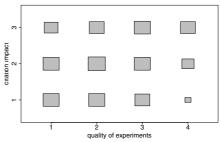

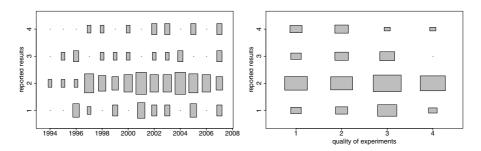

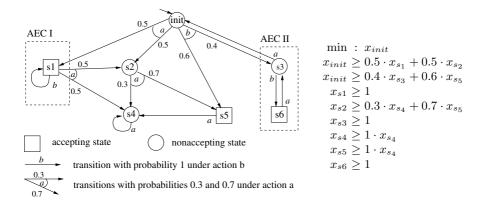

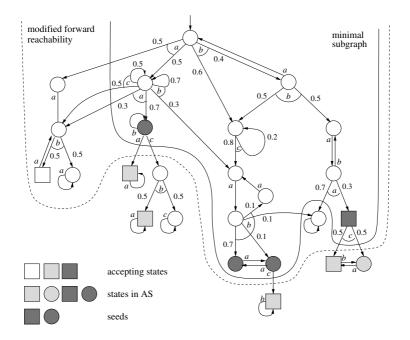

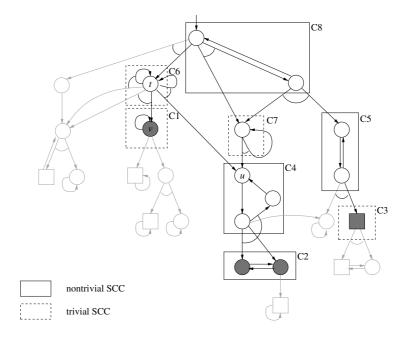

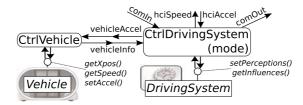

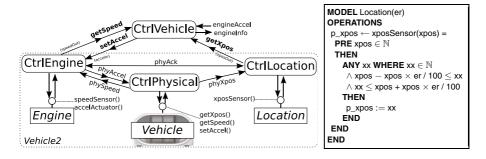

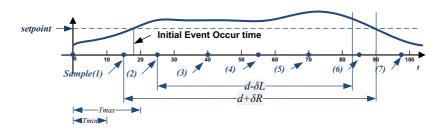

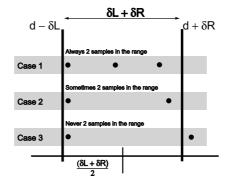

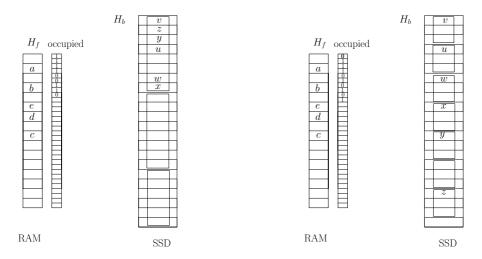

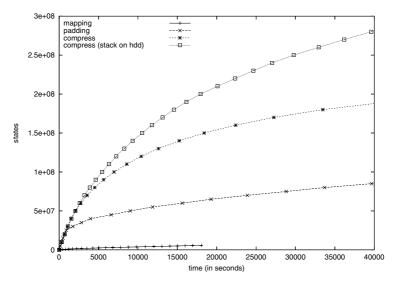

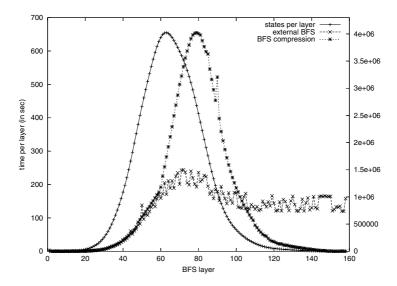

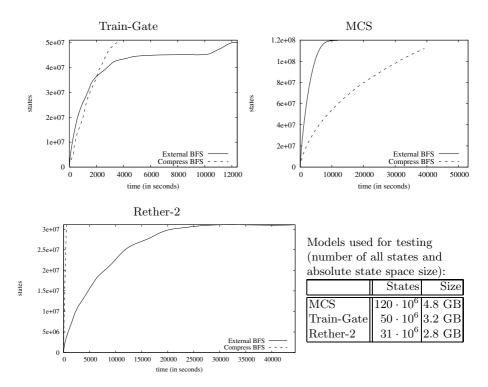

Let us consider the path  $p_2 = \langle A, L_1, L_3, never\_A \rangle$  in the corresponding operator network for the node Never (Figure 3). The condition under which that path is activated is represented by a boolean expression showing the propagation of the input A through the output  $never\_A$ . To calculate its activation condition, we progressively apply the rules for the activation conditions of the corresponding operators according to Table 2. Starting from the end of the path, we reach