Oege de Moor Michael I. Schwartzbach (Eds.)

# **Compiler Construction**

18th International Conference, CC 2009 Held as Part of the Joint European Conferences on Theory and Practice of Software, ETAPS 2009 York, UK, March 2009, Proceedings

#### Lecture Notes in Computer Science

5501

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Oege de Moor Michael I. Schwartzbach (Eds.)

## Compiler Construction

18th International Conference, CC 2009 Held as Part of the Joint European Conferences on Theory and Practice of Software, ETAPS 2009 York, UK, March 22-29, 2009 Proceedings

#### Volume Editors

Oege de Moor Oxford University Computing Laboratory, Wolfson Building Parks Road, Oxford OX1 3QD, UK E-mail: oege@comlab.ox.ac.uk

Michael I. Schwartzbach Aarhus University, Department of Computer Science Aabogade 34, 8200 Aarhus N., Denmark E-mail: mis@cs.au.dk

Library of Congress Control Number: Applied for

CR Subject Classification (1998): D.3.4, D.2.2, D.2.4, D.2.5, D.3.3

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-642-00721-X Springer Berlin Heidelberg New York ISBN-13 978-3-642-00721-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12630653 06/3180 5 4 3 2 1 0

#### Foreword

ETAPS 2009 was the 12th instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference that was established in 1998 by combining a number of existing and new conferences. This year it comprised five conferences (CC, ESOP, FASE, FOSSACS, TACAS), 22 satellite workshops (ACCAT, ARSPA-WITS, Bytecode, COCV, COMPASS, FESCA, FInCo, FORMED, Galop, GT-VMT, HFL, LDTA, MBT, MLQA, OpenCert, PLACES, QAPL, RC, SafeCert, TAASN, TERMGRAPH, and WING), four tutorials, and seven invited lectures (excluding those that were specific to the satellite events). The five main conferences received 532 submissions (including 30 tool demonstration papers), 141 of which were accepted (10 tool demos), giving an overall acceptance rate of about 26%, with most of the conferences at around 25%. Congratulations therefore to all the authors who made it to the final programme! I hope that most of the other authors will still have found a way of participating in this exciting event, and that you will all continue submitting to ETAPS and contributing towards making it the best conference on software science and engineering.

The events that comprise ETAPS address various aspects of the system development process, including specification, design, implementation, analysis and improvement. The languages, methodologies and tools which support these activities are all well within its scope. Different blends of theory and practice are represented, with an inclination towards theory with a practical motivation on the one hand and soundly based practice on the other. Many of the issues involved in software design apply to systems in general, including hardware systems, and the emphasis on software is not intended to be exclusive.

ETAPS is a confederation in which each event retains its own identity, with a separate Programme Committee and proceedings. Its format is open-ended, allowing it to grow and evolve as time goes by. Contributed talks and system demonstrations are in synchronised parallel sessions, with invited lectures in plenary sessions. Two of the invited lectures are reserved for 'unifying' talks on topics of interest to the whole range of ETAPS attendees. The aim of cramming all this activity into a single one-week meeting is to create a strong magnet for academic and industrial researchers working on topics within its scope, giving them the opportunity to learn about research in related areas, and thereby to foster new and existing links between work in areas that were formerly addressed in separate meetings.

ETAPS 2009 was organised by the University of York in cooperation with

- ▶ European Association for Theoretical Computer Science (EATCS)

- ▶ European Association for Programming Languages and Systems (EAPLS)

- ▶ European Association of Software Science and Technology (EASST)

and with support from ERCIM, Microsoft Research, Rolls-Royce, Transitive, and Yorkshire Forward.

The organising team comprised:

Chair Gerald Luettgen

Secretariat Ginny Wilson and Bob French

Finances Alan Wood

Satellite Events Jeremy Jacob and Simon O'Keefe

Publicity Colin Runciman and Richard Paige

Website Fiona Polack and Malihe Tabatabaie.

Overall planning for ETAPS conferences is the responsibility of its Steering Committee, whose current membership is:

Vladimiro Sassone (Southampton, Chair), Luca de Alfaro (Santa Cruz), Roberto Amadio (Paris), Giuseppe Castagna (Paris), Marsha Chechik (Toronto), Sophia Drossopoulou (London), Hartmut Ehrig (Berlin), Javier Esparza (Munich), Jose Fiadeiro (Leicester), Andrew Gordon (MSR Cambridge), Rajiv Gupta (Arizona), Chris Hankin (London), Laurie Hendren (McGill), Mike Hinchey (NASA Goddard), Paola Inverardi (L'Aquila), Joost-Pieter Katoen (Aachen), Paul Klint (Amsterdam), Stefan Kowalewski (Aachen), Shriram Krishnamurthi (Brown), Kim Larsen (Aalborg), Gerald Luettgen (York), Rupak Majumdar (Los Angeles), Tiziana Margaria (Göttingen), Ugo Montanari (Pisa), Oege de Moor (Oxford), Luke Ong (Oxford), Catuscia Palamidessi (Paris), George Papadopoulos (Cyprus), Anna Philippou (Cyprus), David Rosenblum (London), Don Sannella (Edinburgh), João Saraiva (Minho), Michael Schwartzbach (Aarhus), Perdita Stevens (Edinburgh), Gabriel Taentzer (Marburg), Dániel Varró (Budapest), and Martin Wirsing (Munich).

I would like to express my sincere gratitude to all of these people and organisations, the Programme Committee Chairs and PC members of the ETAPS conferences, the organisers of the satellite events, the speakers themselves, the many reviewers, and Springer for agreeing to publish the ETAPS proceedings. Finally, I would like to thank the Organising Chair of ETAPS 2009, Gerald Luettgen, for arranging for us to hold ETAPS in the most beautiful city of York.

January 2009

Vladimiro Sassone, Chair ETAPS Steering Committee

#### Preface

This volume contains the papers presented at CC 2009, the 18th International Conference on Compiler Construction held on March 23-24 in York, UK as part of the Joint European Conference on Theory and Practice of Software (ETAPS 2009). Papers were solicited from a wide range of areas including traditional compiler construction, compiler analyses, runtime systems and tools, programming tools, techniques for specific domains, and the design and implementation of novel language constructs. The submissions and the papers in this volume reflect this variety.

There were 72 submissions. Each submission was reviewed by at least three Programme Committee members and was subjected to several rounds of thorough discussions, and in some cases additional expert reviews were obtained. The PC finally decided to accept 18 research papers.

Many people contributed to the success of this conference. First of all, we would like to thank the authors for submitting papers of high quality. We are also grateful to the members of the Programme Committee and to the external reviewers for their substantive and insightful reviews. Also, thanks go to the developers and supporters of the EasyChair conference management systems for making life so much easier for the authors and the Programme Committee.

CC 2009 was made possible by the ETAPS Steering Committee and the Local Organizing Committee. Finally, we are grateful to Vivek Sarkar for giving the CC 2009 invited talk entitled *Challenges in Code Optimization of Parallel Programs*.

January 2009

Michael Schwartzbach Oege de Moor

#### Conference Organization

#### **Programme Chairs**

Oege de Moor Michael I. Schwartzbach

#### Programme Committee

Silvia Breu University of Cambridge, UK

Manuel Chakravarty University of New South Wales, Australia

Satish Chandra IBM Research, New York

Michael Franz UC Irvine, USA

Jan Heering CWI, The Netherlands Paul Kelly Imperial College, UK Viktor Kuncak EPFL, Switzerland

Sorin Lerner University of California at San Diego, USA

Yanhong Annie Liu SUNY at Stony Brook, USA Ondrej Lhotak University of Waterloo, Canada

Oege de Moor Oxford University, UK Pierre-Etienne Moreau INRIA Nancy, France

Lori Pollock University of Delaware, USA Markus Pueschel Carnegie Mellon University, USA

Mooly Sagiv Tel-Aviv University, Israel

Wolfram Schulte Microsoft Research Redmond, USA Michael I. Schwartzbach University of Aarhus, Denmark University of Oregon, USA

Zhendong Su UC Davis, USA

Don Syme Microsoft Research Cambridge, UK

#### Reviewers

Amaral, J. Nelson

Arnold, Mat

Balland, Emilie

Bird, Christian

Bouchez, Florent

Cintra, Marcelo

Cunei, Antonio

Danvy, Olivier

Ditu, Gabriel

Dor, Nurit

Brauner, Paul Edwards, Stephen A.

Bravenboer, Martin Ernst, Erik

Burckel, Serge Field, John

Chang, Mason Fink, Stephen

Chugh, Ravi Franchetti, Franz

#### X Organization

Gabel, Mark Gal. Andreas Gfeller, Sebastian Gorbovitski, Michael Hu, Zhenjiang Huang, Shan Shan Jackson, Todd Jiang, Lingxiao Keller, Gabriele Klint, Paul Kopetz, Radu Lashari, Ghulam Lee, Sean Leshchinskiy, Roman Lev-Ami, Tal Lindig, Christian Liu, Xuezheng

Liu, Xuezheng Lokhmotov, Anton Manevich, Roman de Mesmay, Frederic Message, Robin Mullins, Robert Naeem, Nomair Parkinson, Matthew Pearce, David Piskac, Ruzica Rabbah, Rodric Reilles, Antoine Rinetzky, Noan Rothamel, Tom Russell, Francis Salamat, Babak Seyster, Justin Sittampalam, Ganesh Sridharan, Manu Suter, Philippe Swierstra, Doaitse Tatlock, Zachary Tekle, Tuncay Theoduloz, Gregory Van Wyk, Eric Vechev, Martin Vinju, Jurgen Voronenko, Yevgen Wagner, Gregor Wang, Liqiang Wies, Thomas Wilhelm, Reinhard Wimmer, Christian Winwood, Simon

Yahav, Eran Yermolovich, Alexander Yohan, Boichut

#### **Table of Contents**

| Challenges in Code Optimization of Parallel Programs (Invited Talk)                   | 1   |

|---------------------------------------------------------------------------------------|-----|

| Extensible Proof-Producing Compilation                                                | 2   |

| From Specification to Optimisation: An Architecture for Optimisation of Java Bytecode | 17  |

| A Framework for Exploring Optimization Properties                                     | 32  |

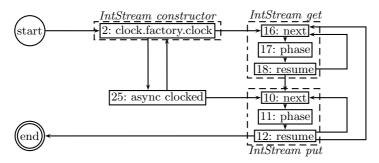

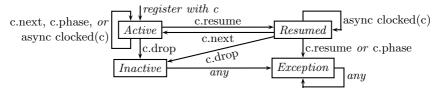

| Compile-Time Analysis and Specialization of Clocks in Concurrent Programs             | 48  |

| Implementation and Use of Transactional Memory with Dynamic Separation                | 63  |

| Exploiting Speculative TLP in Recursive Programs by Dynamic Thread Prediction         | 78  |

| Live Debugging of Distributed Systems                                                 | 94  |

| Parsing C/C++ Code without Pre-processing                                             | 109 |

| Faster Scannerless GLR Parsing                                                        | 126 |

| Decorated Attribute Grammars: Attribute Evaluation Meets Strategic Programming        | 142 |

| SSA Elimination after Register Allocation                                             | 158 |

#### XII Table of Contents

| Register Spilling and Live-Range Splitting for SSA-Form Programs Matthias Braun and Sebastian Hack                                                                                                              | 174 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Loop-Aware Instruction Scheduling with Dynamic Contention Tracking for Tiled Dataflow Architectures                                                                                                             | 190 |

| Scheduling Tasks to Maximize Usage of Aggregate Variables in Place Samah Abu-Mahmeed, Cheryl McCosh, Zoran Budimlić, Ken Kennedy, Kaushik Ravindran, Kevin Hogan, Paul Austin, Steve Rogers, and Jacob Kornerup | 204 |

| Dynamic Look Ahead Compilation: A Technique to Hide JIT Compilation Latencies in Multicore Environment                                                                                                          | 220 |

| Precise Management of Scratchpad Memories for Localising Array Accesses in Scientific Codes                                                                                                                     | 236 |

| Blind Optimization for Exploiting Hardware Features  Dan Knights, Todd Mytkowicz, Peter F. Sweeney,  Michael C. Mozer, and Amer Diwan                                                                           | 251 |

| How to CPS Transform a Monad                                                                                                                                                                                    | 266 |

| Author Index                                                                                                                                                                                                    | 281 |

### Challenges in Code Optimization of Parallel Programs

Vivek Sarkar

Rice University

Abstract. Code optimization has a rich history that dates back over half a century, and includes deep innovations that arose in response to changing trends in hardware and programming languages. These innovations have contributed significantly to programmer productivity by reducing the effort that programmers spend on hand-implementing code optimizations and by enabling code to be more portable. Often these innovations were accompanied by paradigm shifts in the foundations of compilers led by the introduction of new ideas such as interprocedural whole program analysis, coloring-based register allocation, static single assignment form, array dependence analysis, pointer alias analysis, loop transformations, adaptive profile-directed optimizations, and dynamic compilation.

In this talk, we claim that the current multicore trend in the computer industry is forcing a new paradigm shift in compilers to address the challenge of *code optimization of parallel programs*, regardless of whether the parallelism is implicit or explicit in the programming model. All computers — embedded, mainstream, and high-end — are now being built from multicore processors with little or no increase in clock speed per core. This trend poses multiple challenges for compilers for future systems as the number of cores per socket continues to grow, and the cores become more heterogeneous. In addition, compilers have to keep pace with a proliferation of new parallel languages and libraries.

To substantiate our claim, we first highlight some of the anomalies that arise when classical techniques from sequential code optimization are applied to parallel code. We then examine the historical foundations of code optimization including intermediate representations (IR's), abstract execution models, legality and cost analyses of IR transformations and identify paradigm shifts that will be necessary to support optimization of parallel code. We pay special attention to memory consistency models and their impact on code optimization. Finally, we summarize the approach to code optimization of parallel programs being taken in the Habanero Multicore Software Research project at Rice University.

#### **Extensible Proof-Producing Compilation**

Magnus O. Myreen<sup>1</sup>, Konrad Slind<sup>2</sup>, and Michael J.C. Gordon<sup>1</sup>

**Abstract.** This paper presents a compiler which produces machine code from functions defined in the logic of a theorem prover, and at the same time proves that the generated code executes the source functions. Unlike previously published work on proof-producing compilation from a theorem prover, our compiler provides broad support for user-defined extensions, targets multiple carefully modelled commercial machine languages, and does not require termination proofs for input functions. As a case study, the compiler is used to construct verified interpreters for a small LISP-like language. The compiler has been implemented in the HOL4 theorem prover.

#### 1 Introduction

Compilers pose a problem for program verification: if a high-level program is proved correct, then the compiler's transformation must be trusted in order for the proof to carry over to a guarantee about the generated executable code. In practice there is also another problem: most source languages (C, Java, Haskell etc.) do not have a formal semantics, and it is therefore hard to formally state and verify properties of programs written in these languages.

This paper explores an approach to compilation aimed at supporting program verification. We describe a compiler which takes as input functions expressed in the logic of a theorem prover, compiles the functions to machine code (ARM, x86 or PowerPC) and also proves that the generated code executes the supplied functions. For example, given function f as input

$$f(r_1) = \text{if } r_1 < 10 \text{ then } r_1 \text{ else let } r_1 = r_1 - 10 \text{ in } f(r_1)$$

the compiler can generate ARM machine code

E351000A L: cmp r1,#10

2241100A subcs r1,r1,#10

2AFFFFFC bcs L

and automatically prove a theorem which certifies that the generated code executes f. The following theorem states, if register one (r1) initially holds value  $r_1$ , then the code will leave register one holding value  $f(r_1)$ . The theorem is expressed as a machine-code Hoare triple [17] where the separating conjunction '\*' can informally be read as 'and'.

```

\{r1 \ r_1 * pc \ p * s\} \ p : E351000A, 2241100A, 2AFFFFFC \ \{r1 \ f(r_1) * pc \ (p+12) * s\}

```

Computer Laboratory, University of Cambridge, Cambridge, UK

School of Computing, University of Utah, Salt Lake City, USA

O. de Moor and M. Schwartzbach (Eds.): CC 2009, LNCS 5501, pp. 2–16, 2009.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2009

The fact that f is expressed as a function in the native language of a theorem prover means that it has a precise semantics and that one can prove properties about f, e.g. one can prove that  $f(x) = x \mod 10$  (here mod is modulus over unsigned machine words). Properties proved for f carry over to guarantees about the generated machine code via the certificate proved by the compiler. For example, one can rewrite the theorem from above to state that the ARM code calculates  $r_1 \mod 10$ :

```

\{ \mathsf{r1} \; r_1 * \mathsf{pc} \; p * \mathsf{s} \} \; \; p : \mathsf{E351000A}, \mathsf{2241100A}, \mathsf{2AFFFFFC} \; \; \{ \mathsf{r1} \; (r_1 \; \mathsf{mod} \; 10) * \mathsf{pc} \; (p+12) * \mathsf{s} \}

```

Proof-producing compilation from a theorem prover has been explored before by many, as will be discussed in Section . The contributions that distinguish the work presented here are that the compiler:

- 1. targets multiple, carefully modelled, commercial machine languages (namely ARM, PowerPC and x86, as modelled by Fox [7], Leroy [11] and Sarkar [6]);

- 2. does not require the user to prove termination of the input functions (a restriction posed by the theorem prover in similar work by Li et al. [12][13][14]);

- 3. can, without any added complexity to the certification proof, handle a range of optimising transformations (Section ); and

- 4. supports significant user-defined extensions to its input language (Section 3.1); extensions which made it possible to compile interpreters for a small LISP-like language as a case study (Section 5).

The compiler uses a functional input, which is meant to either be extended directly by the user, as discussed in Section 3.1, or used as a back-end in compilers with more general input languages, e.g. 813114.

This paper builds on the authors' work on *post hoc* verification of realistically modelled machine code [16,17,118], and certifying compilation [8,172,173,114].

#### 2 Core Functionality

The compiler presented in this paper accepts tail-recursive functions as input, functions defined as recursive equations 'f(...) = ...' in a format described in Section [2.1] As output the compiler produces machine code together with a correctness certificate, a theorem which states that the generated machine code executes the function given as input.

The overall compilation algorithm can be broken down into three stages:

- 1. code generation: generates, without proof, machine code from input f;

- **2. decompilation:** derives, via proof, a function f' describing themachine code;

- **3. certification:** proves f = f'.

The remaining subsections describe the input language and code generation that make proving f = f' feasible, as well as the mechanism by which f' is derived. Section 3 describes extensions to the core algorithm.

$<sup>^1</sup>$  The HOL4 source is at http://hol.sf.net/ under HOL/examples/machine-code.

#### 2.1 Input Language

The compiler's input language consists of let-expressions, if-statements and tail-recursion. The language restricts variable names to correspond to names of registers or stack locations.

The following grammar describes the input language. Let r range over register names,  $r_0$ ,  $r_1$ ,  $r_2$ , etc., and s over stack locations,  $s_1$ ,  $s_2$ ,  $s_3$  etc., m over memory modelling functions (mappings from aligned 32-bit machine words to 32-bit machine words), f over function names, g over names of already compiled functions, and  $i_5$ ,  $i_7$ ,  $i_8$  and  $i_{32}$  over unsigned words of size 5-, 7-, 8- and 32-bits, respectively. Bit-operators &, ??, !!,  $\ll$ ,  $\gg$  are and, xor, or, left-shift, right-shift. Operators suffixed with '.' are signed-versions of those without the suffix.

```

\begin{array}{l} input ::= f(v,v,...,v) = rhs \\ rhs ::= \operatorname{let} \ r = exp \ \operatorname{in} \ rhs \\ \mid \ \operatorname{let} \ s = r \ \operatorname{in} \ rhs \\ \mid \ \operatorname{let} \ m = m[ \ address \mapsto r ] \ \operatorname{in} \ rhs \\ \mid \ \operatorname{let} \ (v,v,...,v) = g(v,v,...,v) \ \operatorname{in} \ rhs \\ \mid \ \operatorname{if} \ guard \ \operatorname{then} \ rhs \ \operatorname{else} \ rhs \\ \mid \ f(v,v,...,v) \\ \mid \ (v,v,...,v) \\ \mid \ (v,v,...,v) \\ \mid \ (v,v,...,v) \\ \mid \ exp ::= x \mid \neg x \mid s \mid i_{32} \mid x \ binop \ x \mid m \ address \mid x \ll i_5 \mid x \gg i_5 \mid x \gg .i_5 \\ binop ::= + \mid - \mid \times \mid \operatorname{div} \mid \& \mid ?? \mid !!! \\ cmp ::= < \mid \leq \mid > \mid \geq \mid < \cdot \mid \leq \cdot \mid > \cdot \mid \geq \cdot \mid = \\ guard ::= \neg \ guard \mid guard \wedge guard \mid guard \vee guard \mid x \ cmp \ x \mid x \ \& \ x = 0 \\ address ::= r \mid r + i_7 \mid r - i_7 \\ x ::= r \mid i_8 \\ v ::= r \mid s \mid m \end{array}

```

This input language was designed to be machine independent; programs constructed from this grammar can be compiled to any of the target languages: ARM, x86 and PowerPC. However the input language differs for each target in the number of registers available  $(r_0...r_{12} \text{ for ARM}, r_0...r_6 \text{ for x86 and } r_0...r_{31} \text{ for PowerPC})$  and some detailed restrictions on the use of  $\times$  and div.

#### 2.2 Code Generation

The input language was designed to mimic the operations of machine instructions in order to ease code generation. Each let-expression usually produces a single instruction, e.g.

In some cases one let-expression is split into a few instructions, e.g.

```

let r_3=r_0-r_2 in generates x86 code mov ebx,eax sub ebx,edx let r_3=5000 in generates ARM code mov r3,#19 mov r3,r3,lsl 8 add r3,r3,#136

```

The code generator was programmed to use a few assembly tricks, e.g. on x86 certain instances of addition, which would normally require two instructions (mov followed by add), can be implemented as a single load-effective-address lea:

```

let r_3 = r_0 + r_2 in generates x86 code lea ebx,[eax+edx]

```

A combination of compare and branch are used to implement if-statements, e.g.

```

if r_3=45 then ... else ... generates ARM code cmp r3,#45 bne L1

```

Function returns and function calls generate branch instructions.

The compiler generates a list of assembly instructions, which is translated into machine code using off-the-shelf assemblers: Netwide Assembler nasm [I] for x86 and the GNU Assembler gas [2] for ARM and PowerPC. Note that these tools do not need to be trusted. If incorrect code is generated then the certification phase, which is to prove the correctness certificate, will fail.

#### 2.3 Proving Correctness Theorem

The theorem certifying the correctness of the generated machine code is proved by first deriving a function f' describing the effect of the generated code, and then proving that f' is equal to the original function to be compiled. Function f' is derived using proof-producing decompilation [IS]. This section will illustrate how decompilation is used for compilation and then explain decompilation.

**Example.** Given function f, which traverses  $r_0$  steps down a linked-list in m,

```

\begin{split} f(r_0,r_1,m) &= \\ &\text{if } r_0 = 0 \text{ then } (r_0,r_1,m) \text{ else} \\ &\text{let } r_1 = m(r_1) \text{ in} \\ &\text{let } r_0 = r_0 - 1 \text{ in} \\ &f(r_0,r_1,m) \end{split}

```

Code generation produces the following x86 code.

```

0:

85C0

L1:

test eax, eax

2:

7405

jz L2

4:

mov ecx, [ecx]

8B09

6:

48

dec eax

7:

EBF7

jmp L1

L2:

```

Proof-producing decompilation is applied to the generated machine code. The decompiler takes machine code as input and produces a function f' as output,

```

\begin{split} f'(eax,ecx,m) &= \\ \text{if } eax \ \& \ eax = 0 \ \text{then } (eax,ecx,m) \ \text{else} \\ \text{let } ecx &= m(ecx) \ \text{in} \\ \text{let } eax &= eax - 1 \ \text{in} \\ f'(eax,ecx,m) \end{split}

```

together with a theorem (expressed as a machine-code Hoare triple  $\boxed{17 \ 18}$ ) which states that f' accurately records the update executed by the machine code. The decompiler derives f' via proof with respect to a detailed processor model written by Sarkar  $\boxed{6}$ . Here eip asserts the value of the program counter.

```

\begin{split} f'_{pre}(eax, ecx, m) &\Rightarrow \\ \{ (\text{eax}, \text{ecx}, \text{m}) \text{ is } (eax, ecx, m) * \text{eip } p * \text{s} \} \\ p : 85\text{C074058B0948EBF7} \\ \{ (\text{eax}, \text{ecx}, \text{m}) \text{ is } f'(eax, ecx, m) * \text{eip } (p+9) * \text{s} \} \end{split}

```

The decompiler also automatically defines  $f'_{pre}$ , which is a boolean-valued function that keeps track of necessary conditions for the Hoare triple to be valid as well as side-conditions that are needed to avoid raising hardware exceptions. In this case, ecx is required to be part of the memory segment modelled by function m and the underlying model requires ecx to be word-aligned (ecx & 3 = 0), whenever  $eax \& eax \neq 0$ .

```

\begin{split} f'_{pre}(eax,ecx,m) &= \\ &\text{if } eax \ \& \ eax = 0 \ \text{then } true \ \text{else} \\ f'_{pre}(eax-1,m(ecx),m) \ \land \ ecx \in \text{domain } m \ \land \ (ecx \ \& \ 3=0) \end{split}

```

Next the compiler proves f = f'. Both f and f' are recursive functions; thus proving f = f' would normally require an induction. The compiler can avoid an induction since both f and f' are defined as instances of tailrec:

```

tailrec x = if (G x) then tailrec (F x) else (D x)

```

The compiler proves f = f' by showing that the components of the tailrec instantiation are equal, i.e. for f and f', as given above, the compiler only needs to prove the following. ( $f'_{pre}$  is not needed for these proofs.)

```

G: (\lambda(r_0, r_1, m). r_0 \neq 0) = (\lambda(eax, ecx, m). eax \& eax \neq 0)

D: (\lambda(r_0, r_1, m). (r_0, r_1, m)) = (\lambda(eax, ecx, m). (eax, ecx, m))

F: (\lambda(r_0, r_1, m). (r_0 - 1, m(r_1), m)) = (\lambda(eax, ecx, m). (eax - 1, m(ecx), m))

```

The code generation phase is programmed in such a way that the above component proofs will always be proved by an expansion of let-expressions followed by rewriting with a handful of verified rewrite rules that undo assembly tricks, e.g.  $\forall w.\ w\ \&\ w=w.$

The precondition  $f'_{pre}$  is not translated, instead  $f_{pre}$  is defined to be  $f'_{pre}$ . The compiler proves the certificate of correctness by rewriting the output from the decompiler using theorems f' = f and  $f'_{pre} = f_{pre}$ . The example results in:

```

\begin{split} f_{pre}(eax, ecx, m) &\Rightarrow \\ \{ \, (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \; \mathsf{is} \; (eax, ecx, m) * \mathsf{eip} \; p * \mathsf{s} \, \} \\ p : 85\mathsf{C}074\mathsf{O}58\mathsf{B}094\mathsf{8}\mathsf{E}\mathsf{B}\mathsf{F}7 \\ \{ \, (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \; \mathsf{is} \; f(eax, ecx, m) * \mathsf{eip} \; (p+9) * \mathsf{s} \, \} \end{split}

```

**Decompilation.** The proof-producing decompilation, which was used above, is explained in detail in [18]. However, a brief outline will be given here.

Decompilation starts by composing together Hoare triples for machine instructions to produce Hoare triples describing one pass through the code. For the above x86 code, successive compositions collapse Hoare triples of the individual instructions into two triples, one for the case when the conditional branch is taken and one for the case when it is not.

```

\begin{array}{l} eax \& \ eax = 0 \Rightarrow \\ \big\{ (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \ \mathsf{is} \ (eax, ecx, m) * \mathsf{eip} \ p * \mathsf{s} \big\} \\ p : 85\mathsf{C074058B0948EBF7} \\ \big\{ (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \ \mathsf{is} \ (eax, ecx, m) * \mathsf{eip} \ (p+9) * \mathsf{s} \big\} \\ eax \& \ eax \neq 0 \ \land \ ecx \in \mathsf{domain} \ m \ \land \ (ecx \& \ 3 = 0) \Rightarrow \\ \big\{ (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \ \mathsf{is} \ (eax, ecx, m) * \mathsf{eip} \ p * \mathsf{s} \big\} \\ p : 85\mathsf{C074058B0948EBF7} \\ \big\{ (\mathsf{eax}, \mathsf{ecx}, \mathsf{m}) \ \mathsf{is} \ (eax-1, m(ecx), m) * \mathsf{eip} \ p * \mathsf{s} \big\} \end{array}

```

Using these one-pass theorems, the decompiler instantiates the following loop rule to produce function f' and the certificate theorem. If F describes a looping pass, and D is a pass that exits the loop, then tailrec x is the result of the loop:

```

\forall \mathsf{res} \; \mathsf{res'} \; c. \quad (\forall x. \; P \; x \land G \; x \Rightarrow \{\mathsf{res} \; x\} \, c \, \{\mathsf{res} \; (F \; x)\}) \land \\ (\forall x. \; P \; x \land \neg (G \; x) \Rightarrow \{\mathsf{res} \; x\} \, c \, \{\mathsf{res'} \; (D \; x)\}) \Rightarrow \\ (\forall x. \; \mathsf{pre} \; x \Rightarrow \{\mathsf{res} \; x\} \, c \, \{\mathsf{res'} \; (\mathsf{tailrec} \; x)\})

```

Here pre is the recursive function which records the side-conditions that need to be met (e.g. in this case P is used to record that ecx needs to be aligned).

$$\mathsf{pre}\; x = P\; x \wedge (G\; x \Rightarrow \mathsf{pre}\; (F\; x))$$

For the above one-pass Hoare triples to fit the loop rule, the decompiler instantiates G, F, D, P, res and res' as follows:

```

\begin{split} G &= \lambda(eax,ecx,m).\;(eax\;\&\;eax\neq 0)\\ F &= \lambda(eax,ecx,m).\;(eax-1,m(ecx),m)\\ D &= \lambda(eax,ecx,m).\;(eax,ecx,m)\\ P &= \lambda(eax,ecx,m).\;(eax\;\&\;eax\neq 0) \Rightarrow ecx \in \operatorname{domain}\; m \wedge (ecx\;\&\; 3=0)\\ \operatorname{res} &= \lambda(eax,ecx,m).\;(\operatorname{eax},\operatorname{ecx},\operatorname{m})\;\operatorname{is}\;(eax,ecx,m) *\operatorname{eip}\; p *\operatorname{s}\\ \operatorname{res}' &= \lambda(eax,ecx,m).\;(\operatorname{eax},\operatorname{ecx},\operatorname{m})\;\operatorname{is}\;(eax,ecx,m) *\operatorname{eip}\; (p+9) *\operatorname{s} \end{split}

```

#### 3 Extensions, Stacks and Subroutines

The examples above illustrated the algorithm of the compiler based on simple examples involving only registers and direct memory accesses. This section describes how the compiler supports user-defined extensions, stack operations and subroutine calls.

#### 3.1 User-Defined Extensions

The compiler has a restrictive input language. User-defined extensions to this input language are thus vital in order to be able to make use of the features specific to each target language.

User-defined extensions to the input language are made possible by the proof method which derives a function f' describing the effect of the generated code: function f' is constructed by composing together Hoare triples describing parts of the generated code. By default, automatically derived Hoare triples for each individual machine instruction are used. However, the user can instead supply the proof method with alternative Hoare triples in order to build on previously proved theorems.

An example will illustrate how this observation works in practice. Given the following Hoare triple (proved in Section  $\square$ ) which shows that ARM code has been shown to implement " $r_1$  is assigned  $r_1 \mod 10$ ",

$$\{r1 \ r_1 * pc \ p * s\} \ p : E351000A, 2241100A, 2AFFFFFC \ \{r1 \ (r_1 \bmod 10) * pc \ (p+12) * s\}$$

the code generator expands its input language for ARM with the following line:

$$rhs ::= let r_1 = r_1 \mod 10$$

in  $rhs$

Now when a function f is to be compiled which uses this feature,

$$f(r_1,r_2,r_3) = \text{let } r_1 = r_1 + r_2 \text{ in}$$

$$\text{let } r_1 = r_1 + r_3 \text{ in}$$

$$\text{let } r_1 = r_1 \text{ mod } 10 \text{ in}$$

$$r_1$$

the code generator implements "let  $r_1 = r_1 \mod 10$  in" using the machine code (underlined below) found inside the Hoare triple. The other instructions are E0811002 for add r1,r1,r2 and E0811003 for add r1,r1,r3.

#### E0811002 E0811003 E351000A 2241100A 2AFFFFFC

The compiler would now normally derive f' by composing Hoare triples for the individual machine instructions, but in this case the compiler considers the underlined code as a 'single instruction' whose effect is described by the supplied Hoare triple. It composes the following Hoare triples, in order to derive a Hoare triple for the entire code.

$$\{r1 \ r_1 * r2 \ r_2 * pc \ p\} \ p : E0811002 \ \{r1 \ (r_1+r_2) * r2 \ r_2 * pc \ (p+4)\}$$

```

\begin{cases} \mathsf{r1} \ r_1 * \mathsf{r2} \ r_2 * \mathsf{r3} \ r_3 * \mathsf{pc} \ p * \mathsf{s} \rbrace \\ p : \mathsf{E0811002}, \mathsf{E0811003}, \mathsf{E351000A}, \mathsf{2241100A}, \mathsf{2AFFFFFC} \\ \mathsf{r1} \ f(r_1, r_2, r_3) * \mathsf{r2} \ r_2 * \mathsf{r3} \ r_3 * \mathsf{pc} \ (p + 20) * \mathsf{s} \rbrace \end{cases}

```

It is important to note that the Hoare triples supplied to the compiler need not concern registers or memory locations, instead more abstract Hoare triples can be supplied. For example, in Section 5, the compiler is given Hoare triples that show how basic operations over LISP s-expressions can be performed. The LISP operation car is implemented by ARM instruction E5933000. Here s-expressions are defined as a data-type with type-constructors Dot (pairs), Num (numbers) and Sym (symbols). Details are given in Section 5

```

\begin{array}{l} (\exists x \ y. \ v_1 = \mathsf{Dot} \ x \ y) \ \Rightarrow \\ \{ \ \mathsf{lisp} \ (a,l) \ (v_1,v_2,v_3,v_4,v_5,v_6) * \mathsf{pc} \ p \ \} \\ p : \mathsf{E5933000} \\ \{ \ \mathsf{lisp} \ (a,l) \ (\mathsf{car} \ v_1,v_2,v_3,v_4,v_5,v_6) * \mathsf{pc} \ (p+4) \ \} \end{array}

```

The above specification extends the ARM code generator to handle assignments of car  $v_1$  to s-expression variable  $v_1$ .

$$rhs ::= let v_1 = car v_1 in rhs$$

#### 3.2 Stack Usage

The stack can be used by assignments to and from variables  $s_0$ ,  $s_1$ ,  $s_2$  etc., e.g. the following let-expressions correspond to machine code which loads register 1 from stack location 3 (three down from top of stack), adds 78 to register 1 and then stores the result in stack location 2.

$$f(r_1, s_2, s_3) = \text{let } r_1 = s_3 \text{ in}$$

$$\text{let } r_1 = r_1 + 78 \text{ in}$$

$$\text{let } s_2 = r_1 \text{ in}$$

$$(r_1, s_2, s_3)$$

Internally stack accesses are implemented by supplying the decompiler with specifications which specify stack locations using M-assertions (defined formally in [17], informally M x y asserts that memory location x holds value y), e.g. the following is the specification used for reading the value of stack location 3 into register 1. Register 13 is the stack pointer.

The postcondition for the certification theorem proved for the above function f:

```

\{ (r1, M(sp+8), M(sp+12)) \text{ is } f(r_1, s_2, s_3) * r13 sp * pc (p+12) \}

```

#### 3.3 Subroutines and Procedures

Subroutines can be in-lined or called as procedures. Each compilation adds a new let-expression into the input languages of the compiler. The added let-expressions describe the compiled code, i.e. they allow subsequent compilations to use the previously compiled code. For example, when the following function (which uses f from above) is compiled, the code for f will be in-lined as in Section 3.1

$$g(r_1,r_2,s_2,s_3) = \text{let } (r_1,s_2,s_3) = f(r_1,s_2,s_3) \text{ in }$$

$$\text{let } s_2 = r_1 \text{ in }$$

$$(r_1,r_2,s_2,s_3)$$

Note that for simplicity, function calls must match the variable names used when compiling the called function was compiled, e.g. a function compiled as  $k(r_1) = ...$  cannot be called as 'let  $r_2 = k(r_2)$  in' since the input is passed to code implementing k in register 1 not in register 2.

If the compiler had been asked to compile f as a procedure, then the numbering of stack variables needs to be shifted for calls to f. Compiling f as a procedure sandwiches the code for f between a push and pop instruction that keep track of the procedure's return address. When f accesses stack locations 2 and 3 (counting in pop-order), these are for caller g locations 1 and 2.

$$\begin{split} g(r_1,r_2,s_1,s_2) &= \mathsf{let}\ (r_1,s_1,s_2) = f(r_1,s_1,s_2)\ \mathsf{in} \\ &\mathsf{let}\ s_2 = r_1\ \mathsf{in} \\ &(r_1,r_2,s_1,s_2) \end{split}$$

#### 4 Optimising Transformations

Given a function f, the compiler generates code, which it decompiles to produce function f' describing the behaviour of the generated code. The code generation phase can perform any optimisations as long as the certification phase can eventually prove f = f'. In particular, certain instructions can be reordered or removed, and the code's control flow can use special features of the target language.

#### 4.1 Instruction Reordering

Instruction reordering is a standard optimisation applied in order to avoid unnecessary pipeline stalls. The compiler presented here supports instruction reordering as is illustrated by the following example. Given a function f which stores  $r_1$  into stack location  $s_5$ , then loads  $r_2$  from stack location  $s_6$ , and finally adds  $r_1$  and  $r_2$ .

$$f(r_1,r_2,s_5,s_6) = \text{let } s_5 = r_1 \text{ in}$$

$$\text{let } r_2 = s_6 \text{ in}$$

$$\text{let } r_1 = r_1 + r_2 \text{ in}$$

$$(r_1,r_2,s_5,s_6)$$

The code corresponding directly to f might cause a pipeline stall as the result of the load instruction (let  $r_2 = s_6$  in) may not be available on time for the add instruction (let  $r_1 = r_1 + r_2$  in). It is therefore beneficial to schedule the load instructions as early as possible; the generated code reduces the risk of a pipeline stall by placing the load instruction before the store instruction:

$$\begin{split} f'(r_1,r_2,s_5,s_6) = & \text{ let } r_2 = s_6 \text{ in } \\ & \text{ let } s_5 = r_1 \text{ in } \\ & \text{ let } r_1 = r_1 + r_2 \text{ in } \\ & (r_1,r_2,s_5,s_6) \end{split}$$

Valid reorderings of instructions are unnoticeable after expansion of letexpressions, thus the proof of f = f' does not need to be smarter to handle this optimisation.

#### 4.2 Removal of Dead Code

Live-variable analysis can be applied to the code in order to remove unused or  $dead\ code$ . In the following definition of f, the first let-expression is unnecessary.

$$\begin{split} f(r_1,r_2,s_5,s_6) &= \mathsf{let}\ r_1 = s_5 \ \mathsf{in} \\ &\mathsf{let}\ r_2 = s_6 \ \mathsf{in} \\ &\mathsf{let}\ r_1 = r_2 + 8 \ \mathsf{in} \\ &(r_1,r_2,s_5,s_6) \end{split}$$

The generated code ignores the first let-expression and produces a function f' which is, after expansion of let-expressions, identical to f.

#### 4.3 Conditional Execution

ARM machine code allows conditional execution of nearly all instructions in order to allow short forward jumps to be replaced by conditionally executed instructions (this reduces branch overhead). The compiler produces conditionally-executed instruction blocks where short forward jumps would otherwise have been generated. The functions decompiled from conditionally executed instructions are indistinguishable from those decompiled from code with normal jumps (as can be seen in the examples of Section II and I.4.4).

x86 supports conditional assignment using the conditional-move instruction cmov. For x86, the compiler replaces jumps across register-register moves by conditional-move instructions.

#### 4.4 Shared Tails

The compiler's input language supports if-statements that split control, but does not provide direct means for joining control-flow. For example, consider

```

(if r1 = 0 then r2 := 23 else r2 := 56); r1 := 4

```

which can be defined either directly as function f with 'shared tails'

$$f(r_1,r_2)=\text{if }r_1=0 \text{ then let }r_2=23 \text{ in let }r_1=4 \text{ in }(r_1,r_2)$$

else let  $r_2=56$  in let  $r_1=4$  in  $(r_1,r_2)$

or as function g with auxiliary function  $g_2$  compiled to be in-lined:

$$\begin{split} g(r_1,r_2) &= \text{let } (r_1,r_2) = g_2(r_1,r_2) \text{ in let } r_1 = 4 \text{ in } (r_1,r_2) \\ g_2(r_1,r_2) &= \text{if } r_1 = 0 \text{ then let } r_2 = 23 \text{ in } (r_1,r_2) \\ &= \text{else let } r_2 = 56 \text{ in } (r_1,r_2) \end{split}$$

Generating code naively for f would result in two instructions for let  $r_1 = 4$  in, one for each branch. The compiler implements an optimisation which detects 'shared tails' so that the code for f will be identical to that produced for g. The compiler generates the following ARM code for function g (using conditional execution to avoid inserting short jumps).

0: E3510000 cmp r1,#0 4: 03A02017 moveq r2,#23 8: 13A02038 movne r2,#56 12: E3A01004 mov r1,#4

#### 5 Compilation Example: Verified LISP Interpreter

The following example shows how one can utilise extensions to the input language. A verified interpreter for a LISP-like language is constructed using compilation. Details of the following section will be published as a separate paper.

The LISP interpreter constructed here operates over a simple date-type of s-expressions: Dot x y is a pair, Num n is a number n, and Sym s is a symbol s, in HOL4, s has type string. Basic operations are defined as follows:

```

\begin{aligned} &\operatorname{car}\left(\operatorname{Dot}x\,y\right)\,=\,x\\ &\operatorname{cdr}\left(\operatorname{Dot}x\,y\right)\,=\,y\\ &\operatorname{cons}x\,y\,=\,\operatorname{Dot}x\,y\\ &\operatorname{plus}\left(\operatorname{Num}m\right)\,\left(\operatorname{Num}n\right)\,=\,\operatorname{Num}\,\left(m+n\right)\\ &\operatorname{minus}\left(\operatorname{Num}m\right)\,\left(\operatorname{Num}n\right)\,=\,\operatorname{Num}\,\left(m-n\right)\\ &\operatorname{size}\left(\operatorname{Num}w\right)\,=\,0\\ &\operatorname{size}\left(\operatorname{Sym}s\right)\,=\,0\\ &\operatorname{size}\left(\operatorname{Dot}x\,y\right)\,=\,1+\operatorname{size}x+\operatorname{size}y \end{aligned}

```

A new resource assertion lisp is defined which relates LISP objects to concrete memory representations: lisp (a, l)  $(v_1, v_2, v_3, v_4, v_5, v_6)$  states that a heap is located at address a, has capacity l, and that s-expressions  $v_1, v_2, v_3, v_4, v_5, v_6$  are stored in this heap. The definition of lisp is omitted in this presentation.

Machine code for basic operations has been proved (in various ways using decompilation and compilation) to implement basic assertions, e.g. ARM code for storing  $car v_1$  into  $v_1$ :

A memory allocator with a built-in copying garbage collector (a Cheney garbage collector  $\blacksquare$ ) is used to implement creation of a new pair Dot  $v_1$   $v_2$ . The precondition of this operation requires the heap to have enough space to accommodate a new cons-cell.

When the above specifications are supplied to the compiler it knows what machine code to generate for two new commands: one for calculating car of  $v_1$  and one for storing cons  $v_1$   $v_2$  into  $v_1$ :

```

let v_1 = car v_1 in 	 let v_1 = cons v_1 v_2 in

```

Once the compilers language had been extended with sufficiently many such primitive operations, a LISP interpreter was compiled using our proof-producing compiler. The top-level specification function defining a simple LISP interpreter  $lisp\_eval$  is listed in Figure When  $lisp\_eval$  is compiled, code is generated and a theorem is proved which state that this LISP interpreter is implemented by the generated machine code, in this case ARM code.

```

\begin{array}{l} lisp\_eval\_pre(v_1, v_2, v_3, v_4, v_5, v_6, l) \implies \\ \{ \ lisp\ (a, l)\ (v_1, v_2, v_3, v_4, v_5, v_6) * \texttt{s} * \texttt{pc}\ p \ \} \\ p: \dots \text{ the generated code}\ \dots \\ \{ \ lisp\ (a, l)\ (lisp\_eval(v_1, v_2, v_3, v_4, v_5, v_6, l)) * \texttt{s} * \texttt{pc}\ (p+3012) \ \} \end{array}

```

Here  $lisp\_eval\_pre$  has collected the various side-conditions that need to be true for proper execution of the code.

#### 6 Summary and Discussion of Related Work

This paper has described how an extensible proof-producing compiler can be implemented using decompilation into logic [18]. The implementation required only a light-weight certification phase (approximately 100 lines of ML code) to be programmed, but still proves functional equivalence between the source and target programs. In contrast to previous work [8][12][13][14], correctness proofs are here separated from code generation.

```

TASK_EVAL = Sym "nil"

TASK_CONT = Sym "t"

lisp_lookup (v1, v2, v3, v4, v5, v6) = ...

lisp_eval0 (v1, v2, v3, v4, v5, v6, 1) = ...

lisp_eval1 (v1, v2, v3, v4, v5, v6, 1) = ...

lisp_eval(v1,v2,v3,v4,v5,v6,1) =

if v2 = TASK EVAL then

let v2 = TASK_CONT in

if isSym v1 then (* exp is Sym *)

let (v1,v2,v3,v4,v5,v6) = lisp_lookup (v1,v2,v3,v4,v5,v6) in

lisp_eval (v1, v2, v3, v4, v5, v6, 1)

else if isDot v1 then (* exp is Dot *)

let v2 = CAR v1 in

let v1 = CDR v1 in

let (v1,v2,v3,v4,v5,v6,1) = lisp_eval0 (v1,v2,v3,v4,v5,v6,1) in

lisp_eval (v1, v2, v3, v4, v5, v6, 1)

else (* exp is Num *)

lisp_eval (v1, v2, v3, v4, v5, v6, 1)

else (* if v2 = TASK_CONT then *)

if v6 = Sym "nil" then (* evaluation complete *)

(v1, v2, v3, v4, v5, v6)

else (* something is still on the to-do list v6 *)

let (v1, v2, v3, v4, v5, v6, 1) = lisp_eval1 (v1, v2, v3, v4, v5, v6, 1) in

lisp_eval (v1, v2, v3, v4, v5, v6, 1)

```

Fig. 1. The top-level definition of lisp\_eval in HOL4

For each run, the compiler generates code and then proves that the code is correct. This is an idea for which Pnueli et al. [20] coined the term translation validation. There are two basic approaches to translation validation: (1) code generation is instrumented to generate proofs, and (2) code generation proceeds as usual then the certification phase attempts to guess the proofs. Approach 1 is generally considered more feasible [21]. However, Necula [19] showed that approach 2 is feasible even for aggressively optimising compilers such as GNU gcc [2]. Necula built into his certification phase heuristics that attempt to guess which optimisations were performed. The compiler presented here also implements approach 2, but restricts the (initial) input language and the optimisations to such an extent that the certification phase does not need any guesswork.

An alternative to producing a proof for each run is to prove the compiler correct. A recent, particularly impressive, milestone in compiler verification was achieved by Leroy [11], who proved the correctness of an optimising compiler which takes a significant subset of C as input and produces PowerPC assembly code as output. As part of this project Tristan and Leroy [22] verified multiple

$<sup>^{2}</sup>$  The work presented here builds on Leroy's specification of PowerPC assembly code.

translation validators. Other recent work is [10,15,111,315]. We chose not to verify our compiler/translation validator, since our compiler constructs all of its proofs in the HOL4 theorem prover. The trusted computing base (TCB) of our compiler is HOL4 and the specifications of the target machine languages. It seems that the user-defined extensions such as those in the LISP example would have been much harder to implement in a verified compiler, since verifying a compiler involves defining a deep embedding of the input language.

The VLISP project [9], which produced verified on-paper proofs for an implementation of a larger subset of LISP, is related to the example above of constructing a verified LISP interpreter. The fact that the proof presented here is mechanised and goes down to detailed models of commercial machine languages distinguishes this work from the VLISP project which stopped at the level of verified algorithms.

**Acknowledgements.** We thank Anthony Fox, Xavier Leroy and Susmit Sarkar for allowing us to use their processor models for this work. We also thank Thomas Tuerk, Aaron Coble and the anonymous reviewers for comments on earlier drafts. The first author is grateful for funding from EPSRC, UK.

#### References

- 1. The Netwide Assembler, http://www.nasm.us/

- 2. The GNU Project. GCC, the GNU Compiler Collection, http://gcc.gnu.org/

- Benton, N., Zarfaty, U.: Formalizing and verifying semantic type soundness of a simple compiler. In: Leuschel, M., Podelski, A. (eds.) Principles and Practice of Declarative Programming (PPDP), pp. 1–12. ACM, New York (2007)

- 4. Cheney, C.J.: A non-recursive list compacting algorithm. Commun. ACM 13(11), 677-678~(1970)

- Chlipala, A.J.: A certified type-preserving compiler from lambda calculus to assembly language. In: Programming Language Design and Implementation (PLDI), pp. 54–65. ACM, New York (2007)

- Crary, K., Sarkar, S.: Foundational certified code in a metalogical framework. Technical Report CMU-CS-03-108, Carnegie Mellon University (2003)

- 7. Fox, A.: Formal specification and verification of ARM6. In: Basin, D., Wolff, B. (eds.) TPHOLs 2003. LNCS, vol. 2758, pp. 25–40. Springer, Heidelberg (2003)

- 8. Gordon, M., Iyoda, J., Owens, S., Slind, K.: Automatic formal synthesis of hardware from higher order logic. Electr. Notes Theor. Comput. Sci. 145, 27–43 (2006)

- 9. Guttman, J., Ramsdell, J., Wand, M.: VLISP: A verified implementation of scheme. Lisp and Symbolic Computation 8(1/2), 5–32 (1995)

- Klein, G., Nipkow, T.: A machine-checked model for a Java-like language, virtual machine, and compiler. ACM Trans. Program. Lang. Syst. 28(4), 619–695 (2006)

- Leroy, X.: Formal certification of a compiler back-end, or: programming a compiler with a proof assistant. In: Principles of Programming Languages (POPL), pp. 42– 54. ACM Press, New York (2006)

- 12. Li, G.-D., Owens, S., Slind, K.: Structure of a proof-producing compiler for a subset of higher order logic. In: De Nicola, R. (ed.) ESOP 2007. LNCS, vol. 4421, pp. 205–219. Springer, Heidelberg (2007)

- 13. Li, G.-D., Slind, K.: Compilation as rewriting in higher order logic. In: Pfenning, F. (ed.) CADE 2007. LNCS, vol. 4603, pp. 19–34. Springer, Heidelberg (2007)

- Li, G., Slind, K.: Trusted source translation of a total function language. In: Ramakrishnan, C.R., Rehof, J. (eds.) TACAS 2008. LNCS, vol. 4963, pp. 471–485.

Springer, Heidelberg (2008)

- 15. Meyer, T., Wolff, B.: Tactic-based optimized compilation of functional programs. In: Filliâtre, J.-C., Paulin-Mohring, C., Werner, B. (eds.) TYPES 2004. LNCS, vol. 3839, pp. 201–214. Springer, Heidelberg (2006)

- Myreen, M.O., Fox, A.C.J., Gordon, M.J.C.: A Hoare logic for ARM machine code. In: Arbab, F., Sirjani, M. (eds.) FSEN 2007. LNCS, vol. 4767, pp. 272–286. Springer, Heidelberg (2007)

- Myreen, M.O., Gordon, M.J.C.: A Hoare logic for realistically modelled machine code. In: Grumberg, O., Huth, M. (eds.) TACAS 2007. LNCS, vol. 4424, pp. 568– 582. Springer, Heidelberg (2007)

- 18. Myreen, M.O., Slind, K., Gordon, M.J.C.: Machine-code verification for multiple architectures An application of decompilation into logic. In: Formal Methods in Computer Aided Design (FMCAD). IEEE, Los Alamitos (2008)

- 19. Necula, G.C.: Translation validation for an optimizing compiler. In: Programming Language Design and Implementation (PLDI), pp. 83–94. ACM, New York (2000)

- Pnueli, A., Siegel, M., Singerman, E.: Translation validation. In: Steffen, B. (ed.) TACAS 1998. LNCS, vol. 1384, pp. 151–166. Springer, Heidelberg (1998)

- Rinard, M.C.: Credible compilation. In: Jähnichen, S. (ed.) CC 1999. LNCS, vol. 1575. Springer, Heidelberg (1999)

- 22. Tristan, J.-B., Leroy, X.: Formal verification of translation validators: a case study on instruction scheduling optimizations. In: Principles of Programming Languages (POPL), pp. 17–27. ACM, New York (2008)

#### From Specification to Optimisation: An Architecture for Optimisation of Java Bytecode

Richard Warburton<sup>1</sup> and Sara Kalvala<sup>2</sup>

- <sup>1</sup> University of Warwick, Coventry, UK R.L.M.Warburton@warwick.ac.uk

- <sup>2</sup> University of Warwick, Coventry, UK Sara.Kalvala@warwick.ac.uk

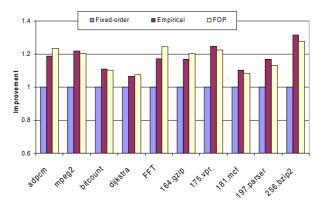

Abstract. We present the architecture of the Rosser toolkit that allows optimisations to be specified in a domain specific language, then compiled and deployed towards optimising object programs. The optimisers generated by Rosser exploit model checking to apply dataflow analysis to programs to find optimising opportunities. The transformational language is derived from a formal basis and consequently can be proved sound. We validate the technique by comparing the application of optimisers generated by our system against hand-written optimisations using the Java based Scimark 2.0 benchmark.

#### 1 Introduction

An optimisation phase is an integral part of most real-world compilers, and significant effort in compiler development is spent in obtaining fast-running code. This effort must be balanced with the need to ensure that optimisations do not introduce errors into programs, and the desire to not worsen compilation time significantly. Several publications, such as Anae have described the use of domain specific languages, based on temporal logic, in order to describe optimisations. Rosser allows the application of specifications of compiler optimisations to Java Bytecode. Optimisations are matched against programs using model-checking, and graph rewriting is used to actually modify the programs.

The contributions from the design of Rosser to the design of compilers include:

- An implementation that automatically generates optimisations from specifications and can be practically used against a real world programming language.

- A novel intermediate representation of Java programs, that uses BDDs to aid in symbolic model checking.

- A method of interactively and visually rewriting the control flow graph (CFG) of Java programs using the Rosser system.

- A case-study backed analysis of the performance ramifications of using model checking for dataflow analysis compared with hand-written analysers.

O. de Moor and M. Schwartzbach (Eds.): CC 2009, LNCS 5501, pp. 17–31, 2009.

The remainder of this paper is structured as follows: we summarize the TRANS language, discuss the design of Rosser, provide a brief explanation of the verification of soundness, discuss some experimental results, compare with related work, and discuss ongoing work.

#### 2 Background and Specification Language

#### 2.1 Specification Language Overview

The design of a specification language for optimisations needs to satisfy many constraints: the optimisations should be expressed in such a way that they are easy to understand and their correctness verified, and it should be possible to clearly express the conditions in which the optimisations apply.

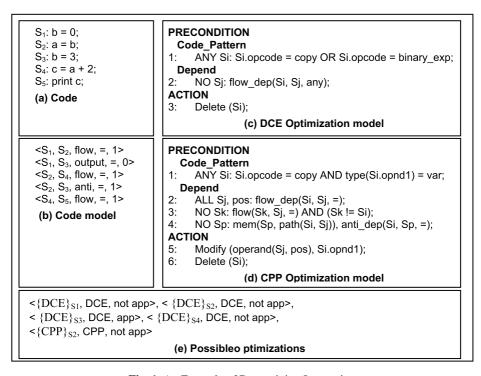

In the TRANS language [7], the optimisations are represented through two components: a rewrite rule and a side condition which indicates the situations in which the rewrite can be applied safely. The specification of dead code elimination is shown in [Fig. 1]. Other optimisations specified in TRANS include lazy code motion, constant propagation, strength reduction, branch elimination, skip elimination, loop fusion, and lazy strength reduction; further details of these can be found in [4].

```

\begin{array}{ll} n: x := e & \Rightarrow & skip \\ \text{if} & \neg \; \texttt{EX} \; \left(\texttt{E} \; \left(\; \neg \; \texttt{def} \left(x\right) \; \texttt{U} \; \texttt{use} \left(x\right) \; \land \; \neg \; \texttt{node} \left(n\right) \; \right)\right) \; @ \; n \end{array}

```

Fig. 1. Dead Code Elimination in TRANS

In order to use this language towards optimisation of Java programs, we replaced the original syntax for program fragments with code in <code>Jimple</code>, one of the intermediate representations used in <code>Soot</code> [18]. As such, the core of the rewrite rules is based on standard programming syntax (assignment statements, go-to and if statements, etc) and will therefore not be explained here. The syntax is expanded with a few constructs to support meta-variables, representing either syntactic fragments of the program or nodes of the CFG.

The side condition language is an extension of first order CTL, where formulae are built up from basic predicates that describe properties of states. There are two types of these basic predicates used to obtain information about a node in the control flow graph; these are the *node* and stmt predicates. The formula node(x) will hold at a node n in a valuation that maps n to x. The formula stmt(s) will hold at a node n where the valuation makes the pattern s match the statement at node n. As well as judgements about states the language can make "global" judgements. For example, the formula  $\phi @ n \wedge conlit(c)$  states that  $\phi$  holds at n and c is a constant literal, throughout the program.

A logical judgement of the form:  $\phi$  @ n states that the formula  $\phi$  is satisfied at node n of the control flow graph. We base our language for expressing conditions on CTL [3], a path-based logic which can express many optimisations while still being efficient to model-check. However, we modify the logic slightly to make

it easier to express properties of programs: we include past temporal operators (E) and E are the extraction operators operators of E and E and E are the expression of E and E are the expression operators operator

It is also possible to make use of user defined predicates via a simple macro system. These can be used in the same way as core language predicates such as *use*. They are defined by an equality between a named binding and the temporal logic condition that the predicate should be 'expanded' into.

Actions. A simple rewrite merely replaces the code at one node with new code; however, most optimisations must actually change the structure of CFGs. These structural changes are supported by four types of action: the replace action which replaces a node with some sequence of nodes, the remove\_edge and add\_edge actions which add and remove edges respectively and the split\_edge action which inserts a node between two other nodes joined by an edge. All the actions maintain the invariant that if the Dimple representation can generate Jimple before the action has been performed, then it must do afterwards. This motivates the choice of several specific actions, rather than unrestricted graph rewriting.

Strategies. The TRANS language contains three strategies, that offer operators for combining different transformation. The MATCH  $\phi$  IN T strategy restricts the domain of information in the transformation T by the condition  $\phi$ . The  $T_1$  THEN  $T_2$  strategy applies the sequential composition of  $T_1$  and  $T_2$ . When actions are applied normally, ambiguity with respect to what node actions and rewrites are applied to are automatically resolved. In other words, if there are several bindings that have the same value for a Node attribute that is being used in a rewrite rule then only one of them is non-deterministically selected. The APPLY\_ALL T strategy uses all of the valuations within transformation T, without this restriction.

#### 2.2 Implementation Background

Since side conditions in TRANS specifications use temporal logic, a model checking based approach is used to obtain the results of the analyses. The use of Binary Decision Diagrams (BDDs), in both model-checking and data-flow analysis applications, has significantly reduced memory consumption [12], and improved runtime performance.

To facilitate the use of a BDD representation of object programs, Rosser generates code in Jedd, an extension to Java that allows a high level representation of BDDs [II]. Relations are introduced as a primitive type within Jedd, and several operations, such as union, intersection, difference and comparison are defined over them. BDDs can be directly coded as relations. Jedd has been used as the basis for implementing inter-procedural data flow analysis [2]. The operators of Jedd are summarised in Table 1.

| Operation             | Comment                                                                     |

|-----------------------|-----------------------------------------------------------------------------|

| x = 0B                | Assigns the empty set to relation $x$                                       |

| x = 1B                | Assigns the set of all possible elements to relation $x$                    |

| (x =>) r              | projects attribute $x$ away from relation $r$                               |

| (x => y) r            | renames attribute $x$ , from relation $r$ to $y$                            |

| (x => x y) r          | copies attribute $x$ , from relation $r$ to $y$                             |

| r1 & r2               | Intersection of relations $r1$ and $r2$                                     |

| $r1 \mid r2$          | Union of relations $r1$ and $r2$                                            |

| r1-r2                 | Set Difference of relations $r1$ and $r2$                                   |

| $r1\{x\} > < r2\{y\}$ | Joins relations $r1$ and $r2$ where $x$ equals $y$ , projecting $y$         |

| $r1\{x\} <> r2\{y\}$  | Joins relations $r1$ and $r2$ where $x$ equals $y$ , projecting $x$ and $y$ |

Table 1. Jedd operations

#### 3 Architecture of Rosser

#### 3.1 Architectural Overview

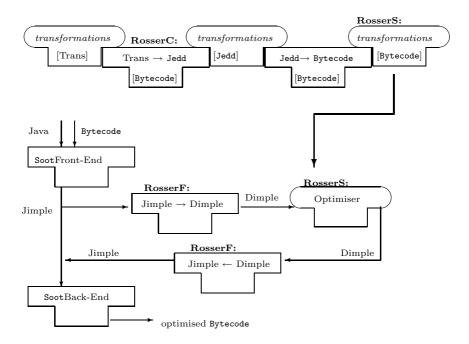

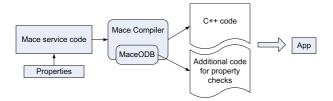

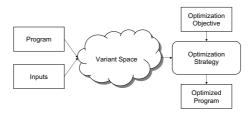

The Rosser compiler framework comprises three components. A meta-compiler, RosserC, translates TRANS specifications to produce the code for the optimising phase. Every optimisation specification is compiled into the general form of finding satisfying valuations for its side condition, by application of its side condition to the intermediate representation. The program generated (referred to as RosserS) is loaded into the runtime framework and applied to a program via the Soot framework.

Soot provides the program already translated into Jimple, where expressions are represented as trees, at a Java-like level, and control flow at a lower level utilising basic conditionals and goto statements [17]. We introduce Dimple—a representation equivalent to Jimple in overall structure, but using BDDs instead of Plain Old Java Objects (POJOs) in order to implement the optimisations. Dimple represents the relations between parents and children as Jimple expression trees. The translation between Jimple and Dimple is done through the RosserF framework. Only parts of the program that are relevant to the optimisations are translated, since only some components of the program need to be pattern-matched. For example since we specify no inter-procedural optimisations there is no representation of the class hierarchy in our implementation.

These interactions are illustrated in Fig. 2.

#### 3.2 Representation of Programs in *Dimple*

The *Dimple* representation introduced in this paper offers a novel approach to the intermediate representation of programs. Whilst BDDs have been used as the basis of representing sets of data during dataflow analysis [2], they haven't been used to represent entire programs before.

The type system of *Dimple* is described through several domains:

**OP** consists of all operators represented in Jimple, for example addition, and negation.

Fig. 2. Architecture of the Rosser framework

**ET** is the edge type domain and contains three possible values: sequential, branch and exception, and is used in pattern matching different edge.

**Node** lists every node in the control flow graph.

Call references every method invocation.

**Value** contains an entry for every possible value in the program, for example the expression x + 1, contains and entry for x, 1 and x + 1.

Table 2 summarises the translation of the syntactic components of programs in Jimple. Recall that use and def are predicates that hold true if their argument (a variable) is read from or written into at a given node. This fragment of the translation presents the MustDef relation, while similar treatment applies to MayDef, MayUse and MustUse relations, which all store information about different use/def chains in the same format. The next section describes these relations in more detail.

#### 3.3 Use/def Analysis

The first phase in translation is the refinement of use and def predicates. These predicates hold true at statements where the variable that they refer to is either read or written to. In Java, as with other programming language, it is possible for several variables to alias the same heap object. This affects use and def predicates because it requires a refinement of the semantics to variables that alias heap objects that are either read or written to. Since assignment may differ

| Name         | Type                                                        | Comment/Example                                                                                                  |

|--------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Nodes        | $\langle \mathtt{Node} \rangle$                             | All nodes in CFG                                                                                                 |

| Skips        | $\langle \mathtt{Node} \rangle$                             | All Noop instructions                                                                                            |

| Edges        | $\langle \mathtt{Node}, \mathtt{Node}, \mathtt{ET} \rangle$ | $x = 1$ ; $y = x \rightarrow \langle x = 1, y = x, SEQ \rangle$                                                  |

| ReturnValues | $\langle \mathtt{Node}, \mathtt{Value}  angle$              | $\texttt{return} \ \ \texttt{x;} \ {\rightarrow} \langle \texttt{return} \ \ \texttt{x,} \ \ \texttt{x} \rangle$ |

| Assign       | $\langle \mathtt{Node}, \mathtt{Value}  \rangle$            | $y = z + 1 \rightarrow \langle y = z + 1, y, z + 1 \rangle$                                                      |

| IfStmt       | $\langle \mathtt{Node}, \mathtt{Value}  angle$              | if (x==3) $\rightarrow$ (if (x==3), x==3)                                                                        |

| Expr         | $\langle {\tt Value, Value, OP} \rangle$                    | $x + y \rightarrow \langle x + y, x, y, + \rangle$                                                               |

| UExpr        | $\langle {	t Value, Value, OP}  angle$                      | $!x \rightarrow \langle !x, x, ! \rangle$                                                                        |

| Conlit       | $\langle \mathtt{Value}  angle$                             | All Constants, eg $\langle 1 \rangle$                                                                            |

| Varlit       | $\langle \mathtt{Value} \rangle$                            | All Variable literals, eg $\langle x \rangle$                                                                    |

| CallSites    | $\langle {	t Value, Call}  angle$                           | Relation between call sites and values                                                                           |

| MustDef      | $\langle \mathtt{Node}, \mathtt{Value} \rangle$             | At $x = 3$ ; $\langle x = 3, x \rangle$                                                                          |

**Table 2.** Representing programs in *Dimple*

depending on what path through the program's control flow graph was taken, the aliasing relationship depends on this path.

As with traditional dataflow analyses  $\Pi$ , the approach taken in Rosser is to divide relationships into 'must' and 'may' forms. For example, MustUse(x) @ n, indicates that for all execution paths at node n, x is used in the computation that occurs at node n. If MayUse(x) @ n, then there exists an execution path such that, at node n, x is used in a computation. The situation is symmetric for MayDef and MustDef. TRANS specifications, however, do not use these conditional variants of the predicates and must be refined accordingly by RosserC.

In order to be a sound refinement of the predicates in TRANS it is necessary for the may/must variants to conservatively approximate their behaviour. That is to say, they must never enable an optimisation that would otherwise be disabled. In order to determine whether the predicate would enable incorrect optimisation we use the concept of *polarity*. The polarity of a predicate is positive if there is an even number of negations preceeding the predicate, and negative otherwise. If a predicate has a positive polarity then nodes where it holds true are being added to the possible points of optimisation. The converse also holds true. Since the must variant of a predicate holds true at a subset of nodes where the predicate holds true we refine predicates with a positive polarity to their must variants. The may variant of a predicate holds true at a superset of nodes where its predicate holds true, so we refine predicates with a negative polarity to the may variant.

This approach to refining use/def predicates means that specifications written in the TRANS language are portable over both languages that allow and disallow aliasing. This has the added advantage of facilitating prototyping of optimisations in simple contexts (for example against Local primitives, which are pass by value) and then be able to apply them in more complicated situations. This underlies one of the design principles of Rosser: to move the burden of compiler development away from the optimisation specification and into the framework.

| Before                                                | After                                                                                                                                       |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| AG p                                                  | ¬E (true U ¬p)                                                                                                                              |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\neg \; (\; \texttt{E} \; (\; \neg \; q \; \texttt{U} \; (\; \neg \; p \; \land \neg \; q)] \; \lor \; \texttt{EG} \; \neg \; q \; ) \; )$ |

| AX D                                                  | ¬ EX ¬ p                                                                                                                                    |

Table 3. Temporal Logic refinements

#### 3.4 Refinement and Type-Checking

The CTL formulae of a specification are initially refined to a smaller set of connectives in order to simplify the output phases.

Rewrite rules are refined to a pattern matching component, which becomes part of the side condition, and a TRANS action. In the case of dead code elimination, this is the *replace* action, which swaps an existing node bound to a meta-variable, inserting an IR element generated from variable bindings in its place.

RosserC also performs type checking. The goal is to statically identify the types of all the meta variables within the TRANS specification. This is beneficial for two reasons. Firstly the output code is statically typed, and so type checking TRANS formulae helps generate object code. Secondly it is helpful in order to reduce the number of accidental or transcription errors within TRANS formulae. If a meta-variable has to bind to a structure of one type in a certain place within the specification and a different type in another part, then it is clearly not a well-formed TRANS specification. Consider the hypothetical specification:

```

n: x := e \Rightarrow \text{skip } if \text{ conlit(n)}

```

This specification fails type checking because the metavariable n has to be a node in its use on the left hand side, and a constant literal if it is an argument to conlit.

Fig. 3 shows the effect of refinement on the specification of dead code elimination shown in Fig. 1. Here the pattern matching has become part of the side condition and the use/def predicates have been refined.

```

\label{eq:replace} \begin{array}{l} \it{replace}\; n \;\; \text{with skip} \\ \it{if} \\ \it{stmt(x := e)} \;\; @ \;\; n \;\land \neg \; EX \;\; (E \;\; (\; \neg \; maydef \; (x) \; U \;\; mustuse \; (x) \;\land \neg \; node(n) \;\; )) \;@ \;\; n \\ \it{optimization} \\ \it{optimiz

```

Fig. 3. Refined specification of dead code elimination

#### 3.5 Code Generation

The RosserC compiler outputs Jedd code, where for each optimisation a corresponding class is generated. The side condition is compiled into a method called condition, whose return type is a relation, with an attribute for each metavariable within the specification, its only parameter being the method to be optimised. A transformation is applied through method transformation, which in

```

1

\langle e, n, x, x1 : N6 \rangle x2 = 1B;

2

x2 = x2\{x1\} >  meth. Nodes\{n\};

3

\langle e, n, x \rangle = meth. Assign;

x2 = x2\{e, n, x\} > x3\{e, n, x\};

4

5

x2 \&= (x1 \Rightarrow x1, x1 \Rightarrow n)((n \Rightarrow )(x2));

6

< e, n, x > x4 = (x1 \Rightarrow )(x2);

Fig. 4. Compilation of stmt(x := e) @ n

1

\langle e, n, x, x6: N7 \rangle x7 = 1B;

2

x7 = x7\{x6, x\} > meth. MustUse\{n, x\};

3

\langle e, n, x, x6 : N8 \rangle x8 = 1B;

4

x8 \&= (x6 \implies x6, x6 \implies n)((n \implies )(x8));

x8 = 1B - x8;

5

6

x8 = x7 \& x8;

```

**Fig. 5.** Compilation of mustuse(x)  $\land \neg$  node(n)

turn calls the condition method and then iterates over all the values within the resulting valuation set. Generating the condition method body proceeds by recursion of the structure of the now refined TRANS side conditions.