Francesca Saglietti Norbert Oster (Eds.)

# Computer Safety, Reliability, and Security

26th International Conference, SAFECOMP 2007 Nuremberg, Germany, September 2007 Proceedings

## Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Francesca Saglietti Norbert Oster (Eds.)

## Computer Safety, Reliability, and Security

26th International Conference, SAFECOMP 2007 Nuremberg, Germany, September 18-21, 2007 Proceedings

#### Volume Editors

Francesca Saglietti Department of Software Engineering University of Erlangen-Nuremberg Germany E-mail: saglietti@informatik.uni-erlangen.de

Norbert Oster Department of Software Engineering University of Erlangen-Nuremberg Germany E-mail: oster@informatik.uni-erlangen.de

#### Library of Congress Control Number: Applied for

#### CR Subject Classification (1998): D.1-4, E.4, C.3, F.3, K.6.5

#### LNCS Sublibrary: SL 2 - Programming and Software Engineering

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-75100-9 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-75100-7 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, IndiaPrinted on acid-free paperSPIN: 1216189806/31805 4 3 2 1 0

## Preface

Since 1979, when it was first established by the Technical Committee on Reliability, Safety and Security of the European Workshop on Industrial Computer Systems (EWICS TC7), the SAFECOMP Conference series has regularly and continuously contributed to improving the state of the art of highly dependable computer-based systems, since then increasingly applied to safety-relevant industrial domains.

In this expanding technical field SAFECOMP offers a platform for knowledge and technology transfer between academia, industry, research and licensing institutions, providing ample opportunities for exchanging insights, experiences and trends in the areas of safety, reliability and security regarding critical computer applications. In accordance with the growing spread of critical infrastructures involving both safety and security threats, this year's SAFECOMP program included a considerable number of contributions addressing technical problems and engineering solutions across the border between safety-related and securityrelated concerns.

The reaction to our call for papers was particularly gratifying and impressive, including 136 full papers submitted by authors representing 29 countries from Europe, Asia, North and South America as well as Australia. The selection of 33 full papers and 16 short papers for presentation and publication was a challenging task requiring a huge amount of reviewing and organizational effort. In view of the particularly high number of articles submitted, obvious practical constraints led – to our regret – to the rejection of a considerable amount of high-quality work. To all authors, invited speakers, members of the International Program Committee and external reviewers go our heartfelt thanks!

The local organization of SAFECOMP 2007, hosted in Nuremberg, is also gratefully acknowledged. The intensive preparatory activities demanded yearlong dedication from the members of the Department of Software Engineering at the University of Erlangen-Nuremberg, which co-organized the event in co-operation with the German Computer Society (Gesellschaft für Informatik). Particular thanks are due to all colleagues and friends from the Organizing Committee, whose support we regard as crucial for the success of this conference.

We are confident that – when reading the present volume of the *Lecture Notes in Computer Science* – you will find its contents interesting enough to consider joining the SAFECOMP community. In the name of EWICS TC7 and of the future organizers we welcome you and invite you to attend future SAFECOMP conferences – among them SAFECOMP 2008 in Newcastle upon Tyne (UK) – and to contribute actively to their technical program.

July 2007

Francesca Saglietti Norbert Oster

## Organization

## Program Chair

Francesca Saglietti (Germany)

## **EWICS** Chair

Udo Voges (Germany)

### International Program Committee

Stuart Anderson (UK) Robin Bloomfield (UK) Sandro Bologna (Italy) Jens Braband (Germany) Inga Bratteby-Ribbing (SE) Bettina Buth (Germany) Peter Daniel (UK) Christian Diedrich (Germany) Jana Dittmann (Germany) Wolfgang Ehrenberger (Germany) Massimo Felici (UK) Robert Genser (Austria) Bjorn Axel Gran (Norway) Karl-Erwin Großpietsch (Germany) Wolfgang Halang (Germany) Monika Heiner (Germany) Maritta Heisel (Germany) Constance Heitmeyer (USA) Janusz Gorski (Poland) Karl-Heinz John (Germany) Karama Kanoun (France)

## **Organizing Committee**

Francesca Saglietti (Co-chair) Wolfgang Ehrenberger (Co-chair) Norbert Oster Jutta Radke Gerd Schober Sven Söhnlein Floor Koornneef (The Netherlands) Peter B. Ladkin (Germany) Søren Lindskov Hansen (Denmark) Bev Littlewood (UK) Vic Maggioli (USA) Odd Nordland (Norway) Gerd Rabe (Germany) Felix Redmill (UK) Martin Rothfelder (Germany) Krzysztof Sacha (Poland) Erwin Schoitsch (Austria) Werner Stephan (Germany) Mark Sujan (UK) Pascal Traverse (France) Jos Trienekens (The Netherlands) Meine Van der Meulen (The Netherlands) Udo Voges (Germany) Albrecht Weinert (Germany) Rune Winther (Norway) Stefan Wittmann (Belgium) Zdzislaw Zurakowski (Poland)

## **External Reviewers**

Myla Archer Lassaad Cheikhrouhou DeJiu Chen Yves Crouzet Håkan Edler Jonas Elmqvist Denis Hatebur **Tobias Hoppe** Ralph D. Jeffords Björn Johansson Johan Karlsson Stefan Kiltz Andreas Lang Bruno Langenstein Tiejun Ma Oliver Meyer M. Oliver Möller Simin Nadjm-Tehrani Vincent Nicomette

Andreas Nonnengart Andrea Oermann Ulf Olsson Norbert Oster Christian Raspotnig Ronny Richter Georg Rock Jan Sanders Thomas Santen **Tobias Scheidat** Holger Schmidt Bernd Schomburg Martin Schwarick Dirk Seifert Sven Söhnlein Marc Spisländer Mirco Tribastone Arno Wacker Dirk Wischermann

## Scientific Sponsor

$\rm EWICS$  – European Workshop on Industrial Computer Systems  $\rm TC7$  – Technical Committee on Reliability, Safety and Security

in collaboration with the following  ${\bf Scientific}\ {\bf Co-sponsors:}$

IFAC International Federation of Automatic Control

IFIP International Federation for Information Processing

ENCRESS European Network of Clubs for Reliability and Safety of Software-Intensive Systems

SCSC The Safety-Critical Systems Club

SRMC The Software Reliability & Metrics Club

OCG Austrian Computer Society

DECOS Dependable Embedded Components and Systems

## X Organization

## SAFECOMP 2007 Organizers

SWE Department of Software Engineering University of Erlangen-Nuremberg

GI Gesellschaft für Informatik e.V.

## Table of Contents

## Safety Cases

| Establishing Evidence for Safety Cases in Automotive Systems – A |    |

|------------------------------------------------------------------|----|

| Case Study                                                       | 1  |

| Willem Ridderhof, Hans-Gerhard Gross, and Heiko Doerr            |    |

| Goal-Based Safety Cases for Medical Devices: Opportunities and   |    |

| Challenges                                                       | 14 |

| Mark-Alexander Sujan, Floor Koornneef, and Udo Voges             |    |

## Impact of Security on Safety

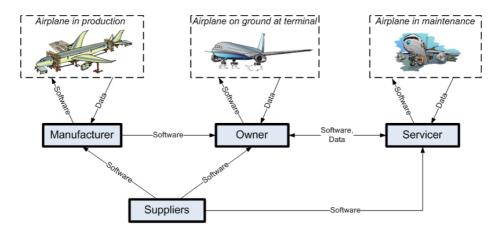

| Electronic Distribution of Airplane Software and the Impact of<br>Information Security on Airplane Safety<br>Richard Robinson, Mingyan Li, Scott Lintelman,<br>Krishna Sampigethaya, Radha Poovendran, David von Oheimb,<br>Jens-Uwe Bußer, and Jorge Cuellar | 28 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

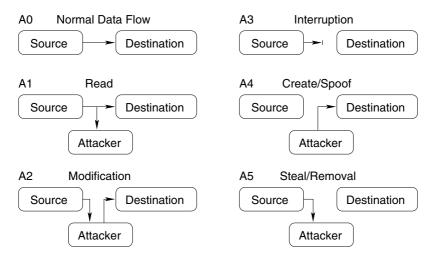

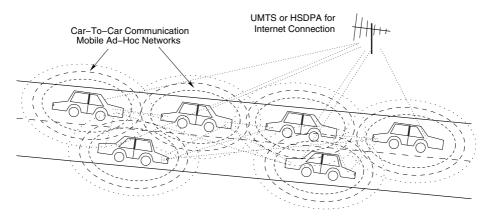

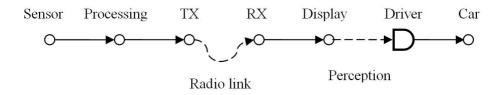

| Future Perspectives: The Car and Its IP-Address – A Potential Safety<br>and Security Risk Assessment<br>Andreas Lang, Jana Dittmann, Stefan Kiltz, and Tobias Hoppe                                                                                           | 40 |

| Modelling Interdependencies Between the Electricity and Information<br>Infrastructures                                                                                                                                                                        | 54 |

| Poster Session 1                                                                                                                                                                                                                                              |    |

| Handling Malicious Code on Control Systems                                                                                                                                                                                                                    | 68 |

| Management of Groups and Group Keys in Multi-level Security<br>Environments                                                                                                                                                                                   | 75 |

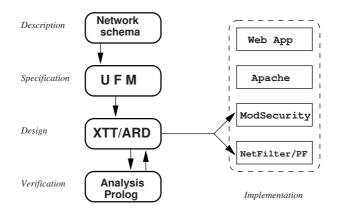

| Application of the XTT Rule-Based Model for Formal Design and<br>Verification of Internet Security Systems                                                                                                                                                    | 81 |

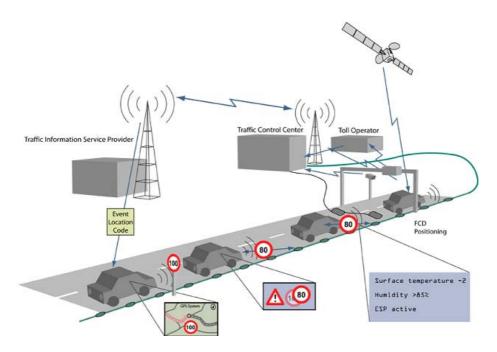

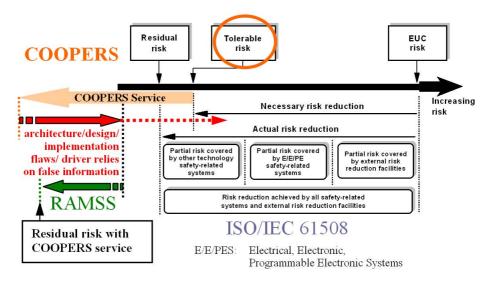

| RAMSS Analysis for a Co-operative Integrated Traffic Management<br>System<br>Armin Selhofer, Thomas Gruber, Michael Putz,<br>Erwin Schoitsch, and Gerald Sonneck                                                                                              | 87 |

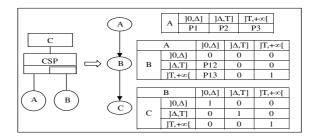

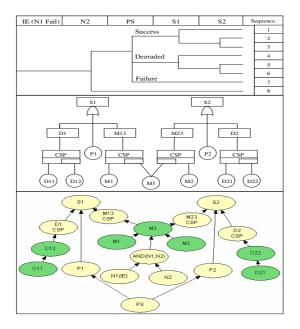

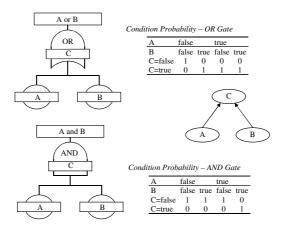

| Combining Static/Dynamic Fault Trees and Event Trees Using<br>Bayesian Networks                                                                                    | 93  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

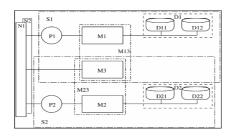

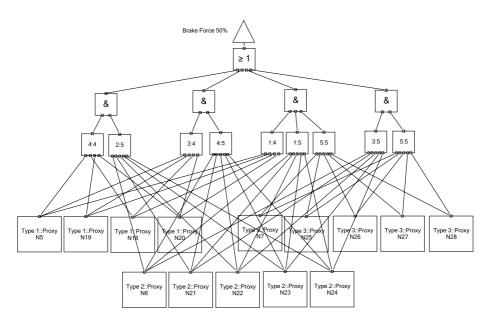

| Component Fault Tree Analysis Resolves Complexity: Dependability<br>Confirmation for a Railway Brake System<br>Reiner Heilmann, Stefan Rothbauer, and Ariane Sutor |     |

| Fault Tree Analysis                                                                                                                                                |     |

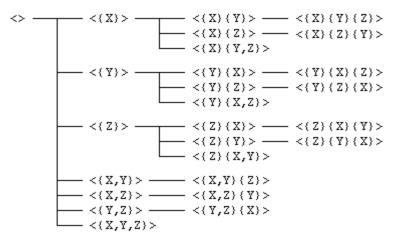

| Compositional Temporal Fault Tree Analysis<br>Martin Walker, Leonardo Bottaci, and Yiannis Papadopoulos                                                            | 106 |

| Representing Parameterised Fault Trees Using Bayesian Networks<br>William Marsh and George Bearfield                                                               | 120 |

| Human Error Analysis Based on a Semantically Defined Cognitive                                                                                                     |     |

| Pilot Model                       | 134 |

|-----------------------------------|-----|

| Andreas Lüdtke and Lothar Pfeifer |     |

## Safety Analysis

| Safety Analysis of Safety-Critical Software for Nuclear Digital<br>Protection System                                                                | 148 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Specification of a Software Common Cause Analysis Method<br>Rainer Faller                                                                           | 162 |

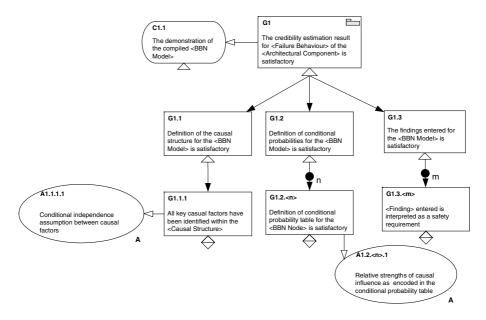

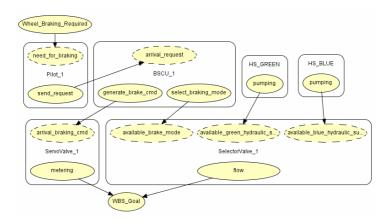

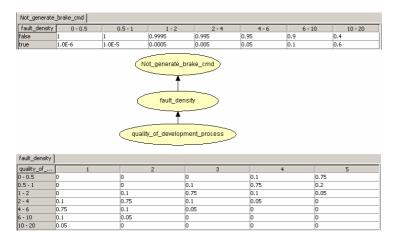

| Combining Bayesian Belief Networks and the Goal Structuring<br>Notation to Support Architectural Reasoning About Safety<br>Weihang Wu and Tim Kelly | 172 |

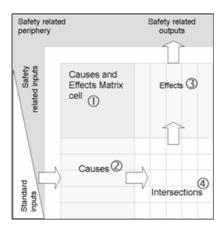

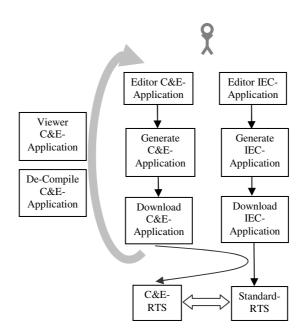

| Application of Interactive Cause and Effect Diagrams to Safety-Related<br>PES in Industrial Automation<br>Hans Russo and Andreas Turk               | 187 |

| Security Aspects                                                                                                                                    |     |

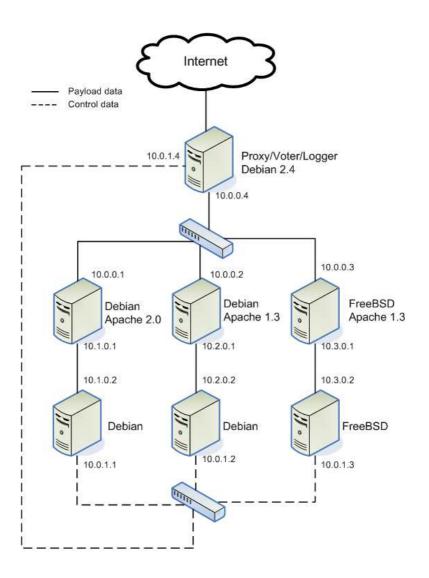

| Survival by Deception                                                                                   | 197 |

|---------------------------------------------------------------------------------------------------------|-----|

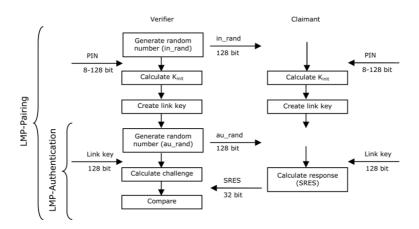

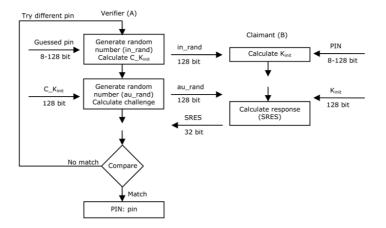

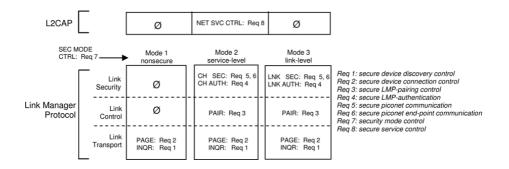

| How to Secure Bluetooth-Based Pico Networks<br>Dennis K. Nilsson, Phillip A. Porras, and Erland Jonsson | 209 |

| Learning from Your Elders: A Shortcut to Information Security     |     |

|-------------------------------------------------------------------|-----|

| Management Success                                                | 224 |

| Finn Olav Sveen, Jose Manuel Torres, and Jose Maria Sarriegi      |     |

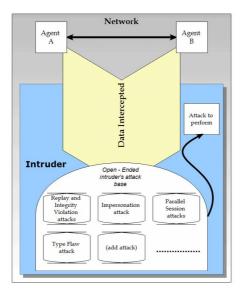

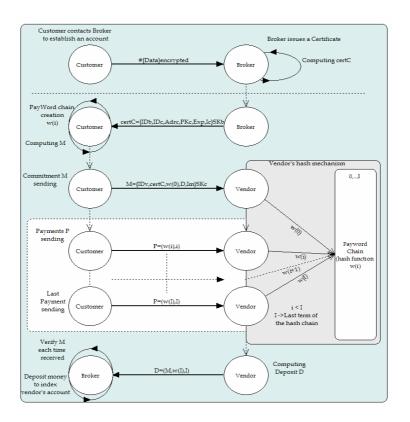

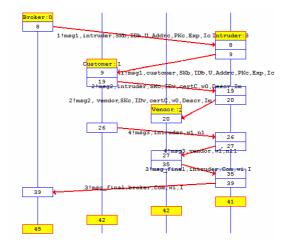

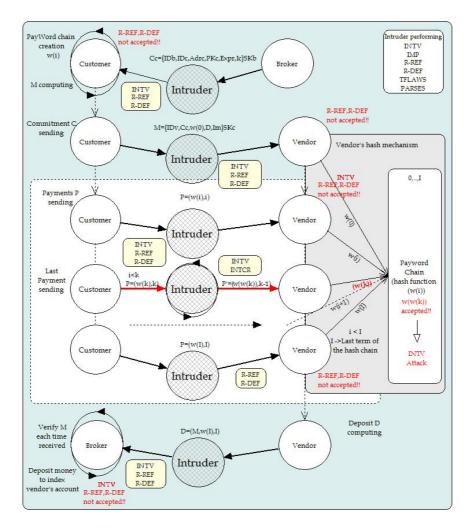

| Intrusion Attack Tactics for the Model Checking of e-Commerce     |     |

| Security Guarantees                                               | 238 |

| Stylianos Basagiannis, Panagiotis Katsaros, and Andrew Pombortsis |     |

## Poster Session 2

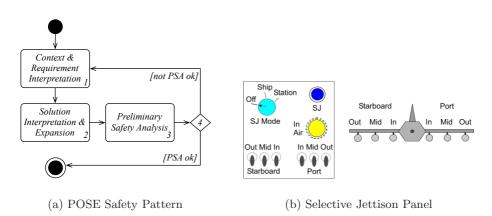

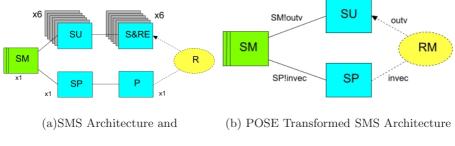

| Safety Process Improvement with POSE and Alloy<br>Derek Mannering, Jon G. Hall, and Lucia Rapanotti                                                                                                                                                                                     | 252 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

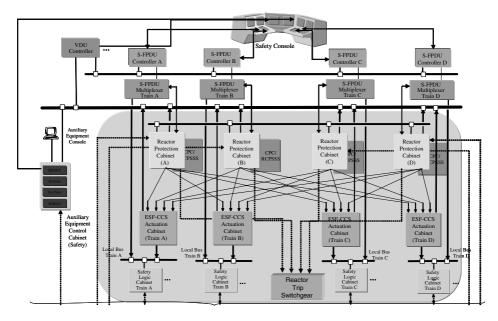

| Defense-in-Depth and Diverse Qualification of Safety-Critical<br>Software<br>Horst Miedl, Jang-Soo Lee, Arndt Lindner, Ernst Ho man,<br>Josef Martz, Young-Jun Lee, Jong-Gyun Choi,<br>Jang-Yeol Kim, Kyoung-Ho Cha, Se-Woo Cheon, Cheol-Kwon Lee,<br>Gee-Yong Park, and Kee-Choon Kwon | 258 |

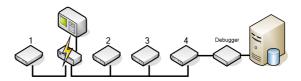

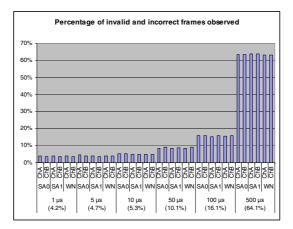

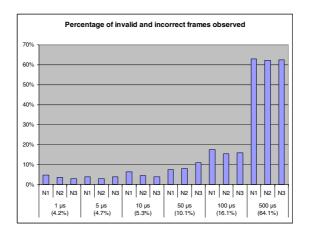

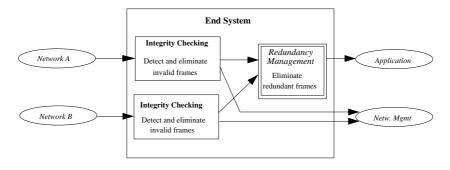

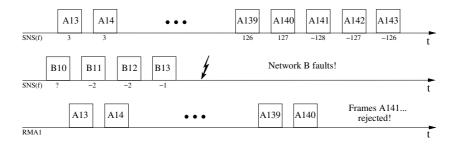

| Experimental Evaluation of the DECOS Fault-Tolerant Communication<br>Layer                                                                                                                                                                                                              | 264 |

| Achieving Highly Reliable Embedded Software: An Empirical<br>Evaluation of Different Approaches<br>Falk Salewski and Stefan Kowalewski                                                                                                                                                  | 270 |

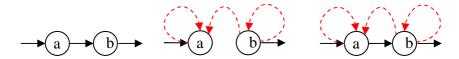

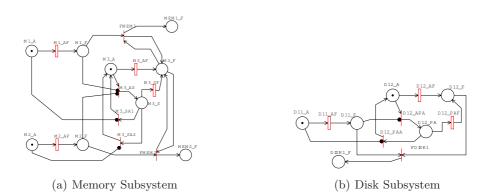

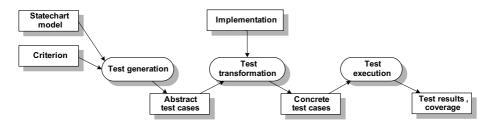

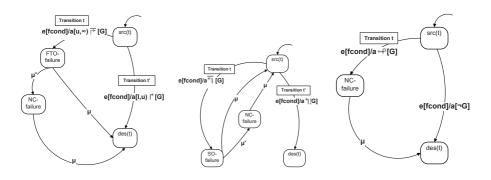

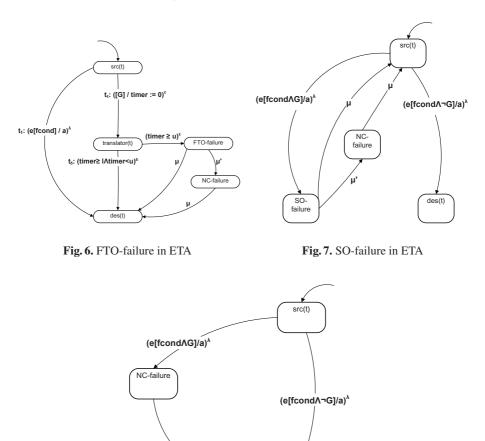

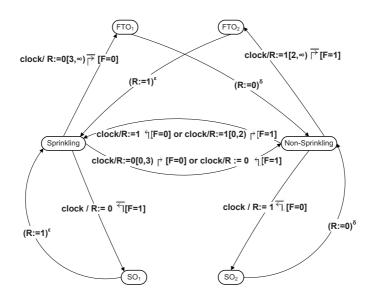

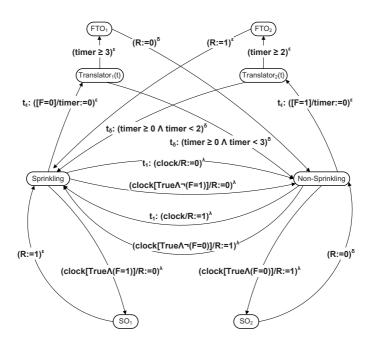

| Modeling, Analysis and Testing of Safety Issues - An Event-Based<br>Approach and Case Study<br><i>Fevzi Belli, Axel Hollmann, and Nimal Nissanke</i>                                                                                                                                    | 276 |

| A Concept for a Safe Realization of a State Machine in Embedded<br>Automotive Applications<br>Jürgen Mottok, Frank Schiller, Thomas Völkl, and Thomas Zeitler                                                                                                                           | 283 |

| Verification and Validation                                                                                                                                                                                                                                                             |     |

| Safety Demonstration and Software Development                                                                                                                                                                                                                                           | 280 |

| Safety Demonstration and Software Development                                                                        | 289 |

|----------------------------------------------------------------------------------------------------------------------|-----|

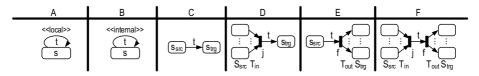

| Improving Test Coverage for UML State Machines Using Transition<br>Instrumentation                                   | 301 |

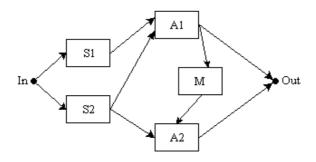

| Verification of Distributed Applications<br>Bruno Langenstein, Andreas Nonnengart, Georg Rock, and<br>Werner Stephan | 315 |

## Platform Reliability

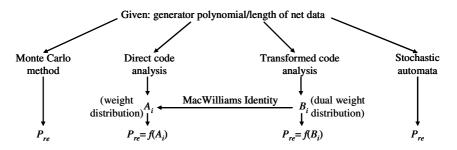

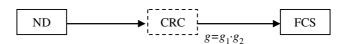

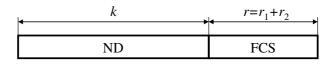

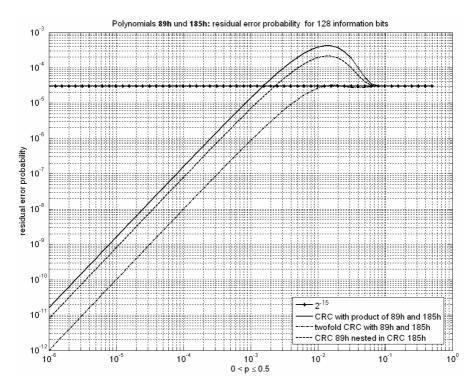

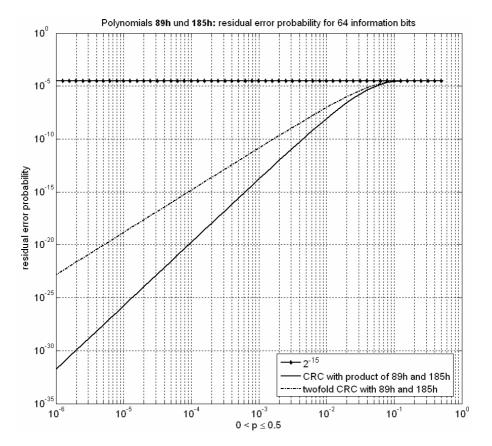

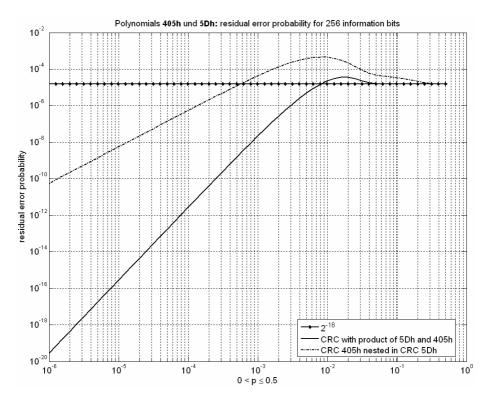

| Analysis of Combinations of CRC in Industrial Communication<br><i>Tina Mattes, Jörg Pfahler, Frank Schiller, and Thomas Honold</i> | 329 |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

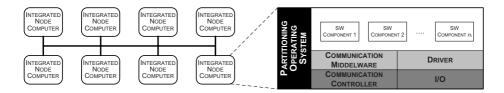

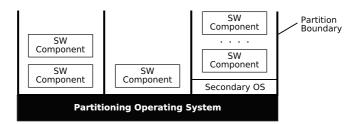

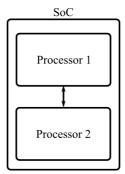

| A Comparison of Partitioning Operating Systems for Integrated<br>Systems                                                           | 342 |

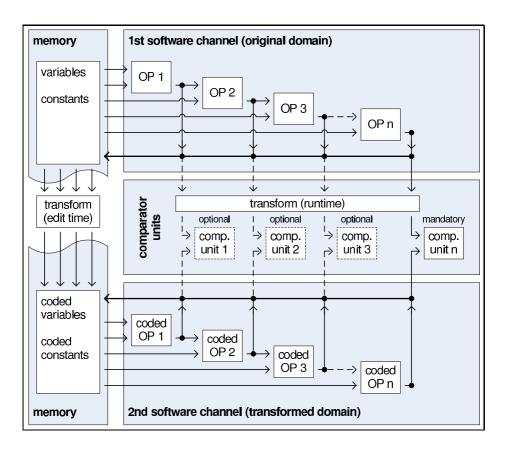

| Software Encoded Processing: Building Dependable Systems with<br>Commodity Hardware<br>Ute Wappler and Christof Fetzer             | 356 |

## **Reliability Evaluation**

| Reliability Modeling for the Advanced Electric Power Grid<br>Ayman Z. Faza, Sahra Sedigh, and Bruce M. McMillin                     | 370 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Case Study on Bayesian Reliability Estimation of Software Design of<br>Motor Protection Relay<br>Atte Helminen                      | 384 |

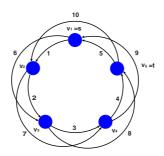

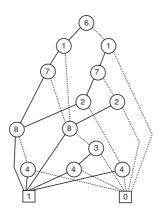

| A Reliability Evaluation of a Group Membership Protocol<br>Valério Rosset, Pedro F. Souto, Paulo Portugal, and<br>Francisco Vasques | 397 |

## Poster Session 3

| Bounds on the Reliability of Fault-Tolerant Software Built by Forcing<br>Diversity                                                             | 411 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

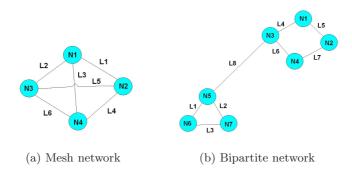

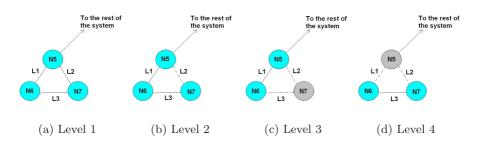

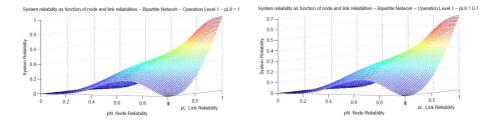

| A Tool for Network Reliability Analysis<br>Andrea Bobbio, Roberta Terruggia, Andrea Boellis,<br>Ester Ciancamerla, and Michele Minichino       | 417 |

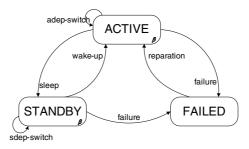

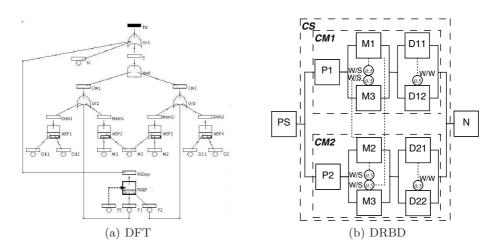

| DFT and DRBD in Computing Systems Dependability Analysis<br>Salvatore Distefano and Antonio Puliafito                                          | 423 |

| Development of Model Based Tools to Support the Design of Railway<br>Control Applications<br>István Majzik, Zoltán Micskei, and Gergely Pintér | 430 |

## Formal Methods

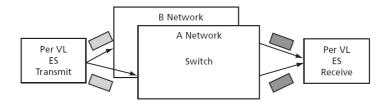

| Formal Specification and Analysis of AFDX Redundancy Management |     |

|-----------------------------------------------------------------|-----|

| Algorithms                                                      | 436 |

| Jan Täubrich and Reinhard von Hanxleden                         |     |

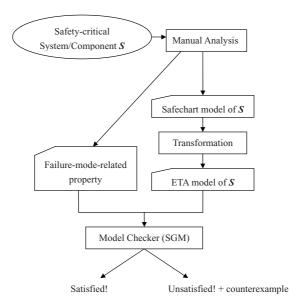

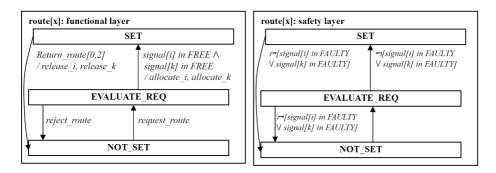

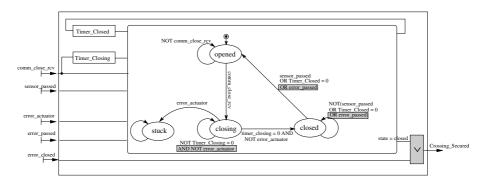

| Modeling and Automatic Failure Analysis of Safety-Critical Systems |     |

|--------------------------------------------------------------------|-----|

| Using Extended Safecharts                                          | 451 |

| Yean-Ru Chen, Pao-Ann Hsiung, and Sao-Jie Chen                     |     |

| Using Deductive Cause-Consequence Analysis (DCCA) with SCADE       | 465 |

| Obling Deductive Cause | Compequence rinaryons ( | Decen with South |

|------------------------|-------------------------|------------------|

| Matthias Güdemann,     | Frank Ortmeier, and V   | Nolfgang Reif    |

## Static Code Analysis

| Experimental Assessment of Astrée on Safety-Critical Avionics |     |

|---------------------------------------------------------------|-----|

| Software                                                      | 479 |

| Jean Souyris and David Delmas                                 |     |

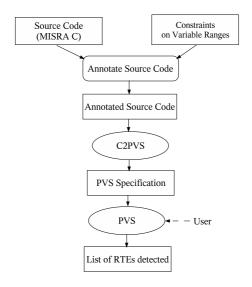

| Detection of Runtime Errors in MISRA C Programs: A Deductive  |     |

| Approach                                                      | 491 |

| Ajith K. John, Babita Sharma, A.K. Bhattacharjee,             |     |

| S.D. Dhodapkar, and S. Ramesh                                 |     |

## Safety-Related Architectures

| A Taxonomy for Modelling Safety Related Architectures in Compliance<br>with Functional Safety Requirements                                                   | 505 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

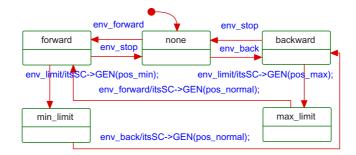

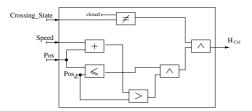

| Controller Architecture for Safe Cognitive Technical Systems<br>Sebastian Kain, Hao Ding, Frank Schiller, and Olaf Stursberg                                 | 518 |

| Improved Availability and Reliability Using Re-configuration Algorithm<br>for Task or Process in a Flight Critical Software<br>Ananda Challaghatta Muniyappa | 532 |

| Author Index                                                                                                                                                 | 547 |

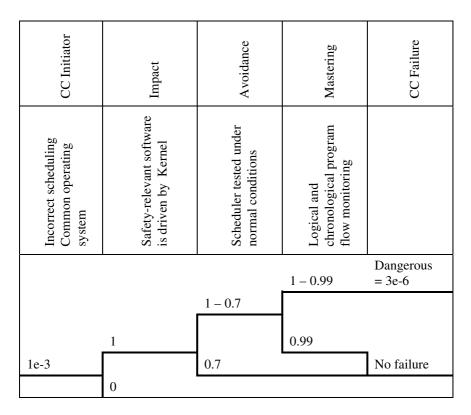

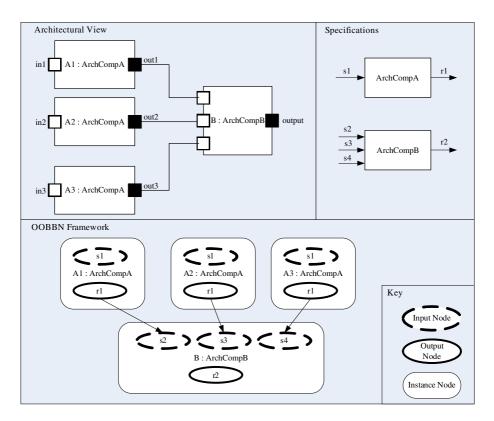

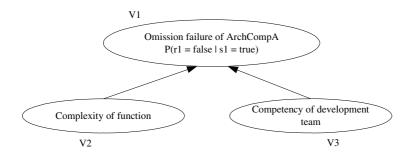

## Establishing Evidence for Safety Cases in Automotive Systems – A Case Study

Willem Ridderhof<sup>1</sup>, Hans-Gerhard Gross<sup>2</sup>, and Heiko Doerr<sup>3</sup>

<sup>1</sup> ISPS Medical Software, Rotterdamseweg 145, 2628 AL Delft willem.ridderhof@isps-medical-software.nl

<sup>2</sup> Embedded Software Laboratory, Delft University of Technology Mekelweg 4, 2628 CD Delft, The Netherlands h.g.gross@tudelft.nl

<sup>3</sup> CARMEQ GmbH, Carnotstr. 4, 10587 Berlin, Germany heiko.doerr@carmeq.com

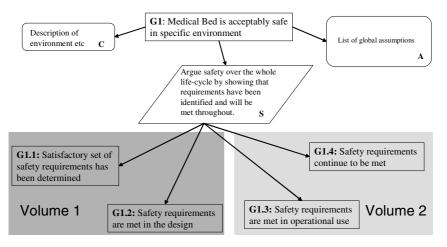

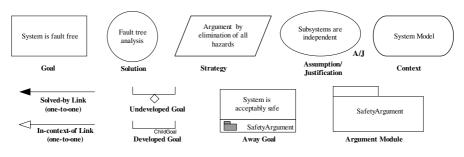

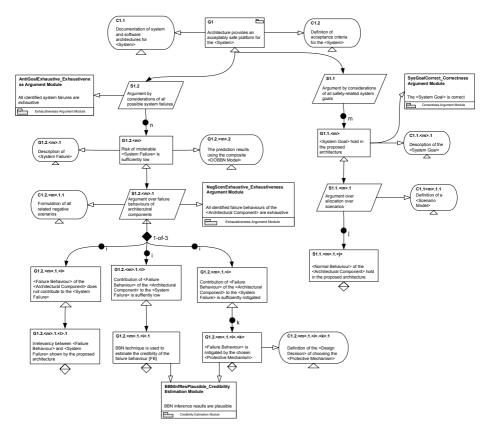

Abstract. The upcoming safety standard ISO/WD 26262 that has been derived from the more general IEC 61508 and adapted for the automotive industry, introduces the concept of a safety case, a scheme that has already been successfully applied in other sectors of industry such as nuclear, defense, aerospace, and railway. A safety case communicates a clear, comprehensive and defensible argument that a system is acceptably safe in its operating context. Although, the standard prescribes that there should be a safety argument, it does not establish detailed guide-lines on how such an argument should be organized and implemented, or which artifacts should be provided.

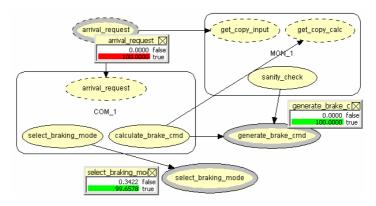

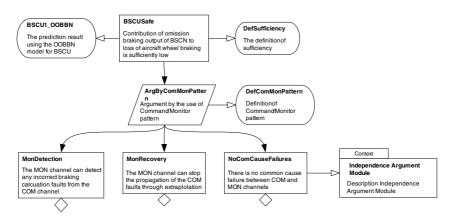

In this paper, we introduce a methodology and a tool chain for establishing a safety argument, plus the evidence to prove the argument, as a concrete reference realization of the ISO/WD 26262 for automotive systems. We use the Goal-Structuring-Notation to decompose and refine safety claims of an emergency braking system (EBS) for trucks into sub-claims until they can be proven by evidence. The evidence comes from tracing the safety requirements of the system into their respective development artifacts in which they are realized.

## 1 Introduction

Safety critical systems have to fulfill safety requirements in addition to functional requirements. Safety requirements describe the characteristics that a system must have in order to be safe [12]. This involves the identification of all hazards that can take place, and that may harm people or the environment. Safety-related issues are often captured in standards describing products and processes to be considered throughout the life-cycle of a safety critical system. The upcoming safety standard ISO/WD 26262 [2] is an implementation of the more general IEC 61508 standard that addresses safety issues in the automotive industry. The objective of the automotive standard is to take the specific constraints of automotive embedded systems and their development processes

F. Saglietti and N. Oster (Eds.): SAFECOMP 2007, LNCS 4680, pp. 1–13, 2007.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2007

into account. Domain-dependent challenges are, for instance, the task distribution of OEMs and suppliers, the degree of iterative development, and the high importance of the application of the embedded system to the target vehicle. The short development cycles and large number of produced units are further specifics which disallow the straight-forward application of safety standards from other domains of transportation. The current working draft is divided into a number of volumes considering e.g. determination of safety integrity levels, and requirements to systems development, software development, and supporting processes. Besides many other requirements the standard prescribes that a safety case should be created for every system that has safety-related features. It states that part of the system documentation should provide evidence for the fulfillment of safety requirements, thus guaranteeing functional safety. However, the standard does not provide any details about which artifacts should be produced in order to prove functional safety, nor does it say how such a proof may be devised.

In this paper, we develop a generic safety case that may act as a reference realization for the automotive industry. In section 2 we describe how a safety case may be constructed based on the Goal-Structuring-Notation (GSN). Section 3 shows that constructing a safety argument is, to a large extent, a traceability effort and dealing with the construction of trace tables. Section 4 presents the case study, a safety critical system, for which we have devised part of a safety argument. Here, we concentrate on the traceability part. Section 5 summarizes and concludes the paper.

#### 2 The Safety Case

Part of the certification process in the automotive domain is the assessment of a system through an inspection agency. To convince inspectors that a system is safe, a safety case should be created. The safety case communicates a clear, comprehensive and defensible argument that a system is acceptably safe in its operating context [7]. The argument should make clear that it is reasonable to assume the system can be operated safely. It is typically based on engineering judgment rather than strict formal logic [12], and it provides evidence that the risks (hazards) associated with the operation of the system have been considered carefully, and that steps have been taken to deal with the hazards appropriately.

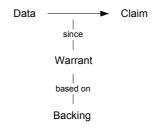

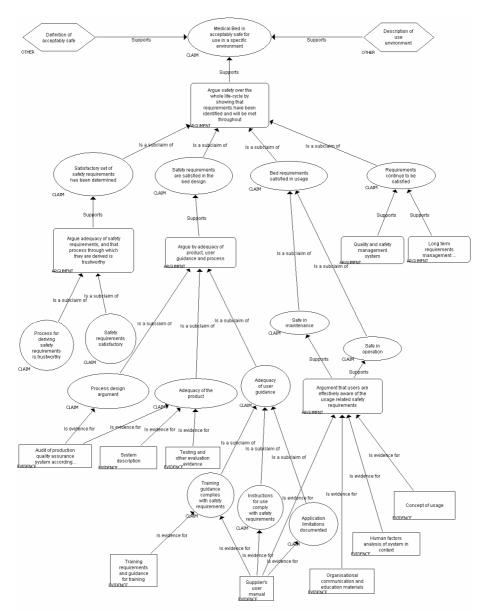

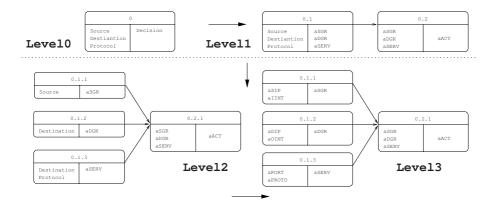

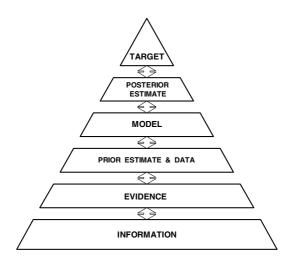

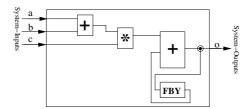

The safety argument (SA) must identify all matters significant to the safety of the system and demonstrate how these issues have been addressed. A convenient way to define a safety argument is through the Goal-Structuring-Notation devised by Kelly [7] which is based on earlier work by Toulmin on the construction of arguments [13]. An argument consists of claims whose truth should be proven. The facts used to prove the claims are referred to as data, and the justification for why data prove a claim is described by warrants. If it is possible to dispute a warrant, backing can be used to show why the warrant is valid. The structure of this argument is depicted in Fig. [1] as far as it is relevant for

Fig. 1. Structure of Toulmin's Argument 13

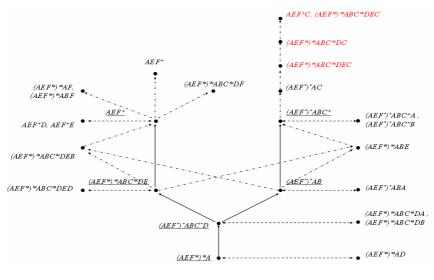

Fig. 2. Example GSN tree, decomposition of the goal "the product is safe"

the safety case. Further concepts being introduced by Toulmin like qualifiers or rebuttals do not contribute to the construction of a safety case. Qualifiers are ordinary language terms like "few", "rarely", or "some" which are used to express the likelihood of a warrant or backing. For safety analysis, formal methods are available to capture this aspect of a safety analysis. Rebuttals deal with the potential counter-arguments arising in an ongoing discussion. However, a safety case is the result of an intense discussion during which all counter-arguments must have been evaluated and resolved such that a safety case can be accepted. So, rebuttals are not relevant for a safety case.

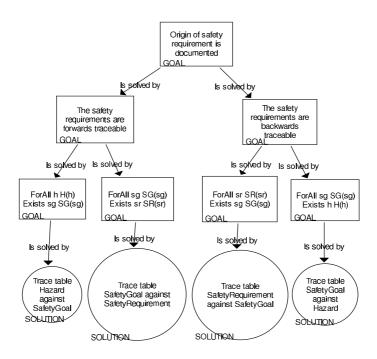

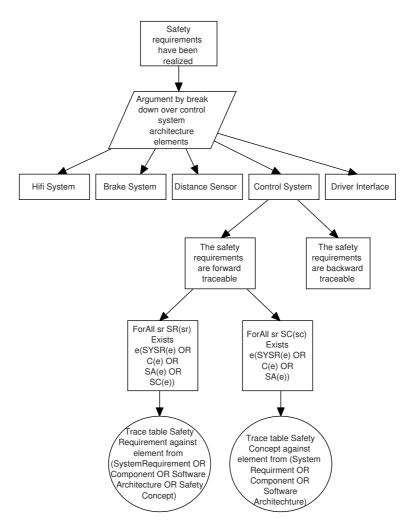

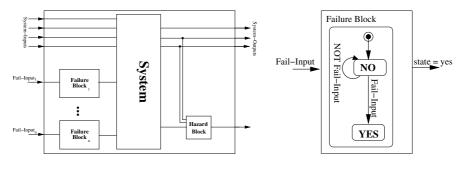

The main elements of the GSN are goals and solutions. Goals correspond to Toulmin's claims whereas solutions relate to Toulmin's data, also termed evidence. For constructing a safety case, we have to determine which evidence is required for a particular safety argument, and why the evidence supports the claim. According to the GSN, the safety case starts with a top-level claim, or a goal, such as "the system is safe" or "safety requirements have been realized." The top-level claim is then decomposed into sub-ordinate claims down to a level that a sub-claim can be proven by evidence. The concepts of the GSN are displayed in the example in Fig. [2] Claims and sub-claims, or goals, are represented as rectangular boxes and evidence, or solutions, as circles. A strategy-node, represented as rhomboid, contains the explanation why a goal has been decomposed. The argument can be constructed by going through the following steps [3].7:

- 1. Identification of the goals to be supported.

- 2. Definition of the basis on which the goals are stated.

- 3. Identification of the strategy to support the goals.

- 4. Definition of the basis on which the strategies are stated.

- 5. Elaboration of the strategy including the identification of new goals and starting from step 1, or moving to step 6.

- 6. Identification of a basic solution that can be proven.

It is difficult to propose a standard safety case structure that may be valid for most systems. However, some of the argumentation will be the same for many systems, such as "all safety requirements have been realized," or the like. Such argumentation structures, or so-called safety case patterns [6][5], may be reused in several safety cases for different systems. By using such patterns, safety cases can be devised much faster. Similarly, safety case anti-pattern can be used to express weak and flawed safety arguments [7][4].

A particular GSN decomposition proposed by the EU project EASIS 3 organizes the argumentation into a product branch and a process branch, claiming that "a system is safe" if "the process is safe" and "the product is safe." The safety of the process can be assured through application of certified development standards, such as the IEC 61508 4 or the V-model 11. Here, questions should be asked about how the product is developed, such as "did we perform hazard analysis?", "do we have a hazard checklist?", "did we perform a preliminary hazard identification?", "did we implement the results of the preliminary hazard identification?", and so on 3.

On the product side, we can decompose the claim "the product is safe" into the sub-goal "the safety requirements are traceable" which turns the satisfaction of our safety case into a traceability problem. We can argue, that if all safety related aspects of our system can be traced to their origin and to their realization, the system is safe, given the process is safe (proof of the process branch). Traceability is a prerequisite for assessment and validation of the safety goals, which we refer to as "proof of safety requirements." We can then decompose the traceability goal further into "proof of safety requirements", "origin of safety requirements documented", and "safety requirements realized." This extended organization of the safety case is depicted in Fig. [2] and, through its general nature, it can be used as a pattern for all systems.

#### **3** Traceability of Safety Requirements

In the previous section, we argued that part of the proof of a safety case can be achieved through tracing all safety requirements to the respective development documents. This is fully in line with the ISO/WD 26262 [2] since it demands that "the origin, realization and proof for a requirement are clearly described in the documentation" of a system. A requirement is a condition or an ability that the system should fulfill. The origin of a requirement is a rationale why this requirement has been elicited for the system. The realization demonstrates how/where the requirement is implemented in the final system. A proof for a requirement means that it should be demonstrated that the requirement has an origin and that it is implemented, in other words, that the requirement is traceable across all development documents in both directions, forwards and backwards. The documents comprise the hazards possible, the safety goals, the safety requirements, design elements, and implementation elements, plus associated review documents.

As shown in Fig. 2. the "product is safe"-branch is decomposed into a traceability sub-goal that is split into various traceability claims, i.e., "origin of safety requirements documented", "safety requirements realized", and "proof of safety requirements." This last goal is decomposed into two sub-goals, "safety requirements validated" and "safety requirements satisfied" which can be traced to the respective documents that deal with those issues.

The origin of a safety requirement can be demonstrated by backward traceability. Safety requirements are derived from hazards and safety goals. Every safety requirement should be linked to at least one safety goal, expressed through  $\forall srSR \longrightarrow \exists sgSG$ , and every safety goal should be linked to a hazard, expressed through  $\forall sgSG \longrightarrow \exists hH$ . But also forward traceability is important, so that for every hazard, there is a safety goal ( $\forall hH \longrightarrow \exists sgSG$ ), and for every safety goal, there should be an associated safety requirement ( $\forall sgSG \longrightarrow \exists srSR$ ). Consequently, we can extend our safety case as depicted in Fig.  $\Box$

For the lowest-level goals, we can then come up with solutions in the form of trace tables. These are now product-specific. Once all trace relations have been established in a development project we can claim that the system is acceptably safe with respect to those safety goals, e.g. with respect to "origin of safety requirements is documented." We have to do this for all safety goals defined, and we demonstrate how this may be done for a specific case using specific tools in the next section.

Fig. 3. Further decomposition of the goal "origin of safety requirement is documented"

#### 4 Case Study

We have devised a partial safety case for an emergency brake system (EBS). This innovative assistance functionality becomes part of modern vehicles and lorries. DaimlerChrysler, for instance, markets that type of application as Active Brake Assist. An emergency brake system warns the driver of a likely crash, and, if the driver does not react upon the warning, initiates and emergency braking. It is a distributed system incorporating the braking system, a distance sensor, the hifi-system, a control system, as well as the driver's interface. The individual subsystems are usually interconnected through a vehicle's CAN bus.

In order to devise the traceability part of the safety case, first, we have to take a look at the development processes and tools deployed. The safety requirements (SR) for this system are coming from a preliminary hazard analysis (PHA), or from a hazards and operability analysis (HAZOP) **[10]**. Once all the potential hazards have been identified, they are associated with safety goals (SG). Safety goals are comparable to top level functional requirements. The requirements are decomposed into sub-system requirements, and eventually, into component requirements. For the execution of the safety analysis the system boundaries have to be determined. This design decision is typically a compromise between controllability and complexity. An emergency brake system is a safety application

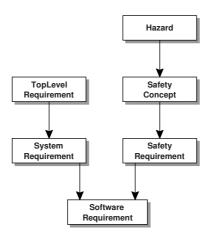

Fig. 4. Classes of development artifacts and their (forward) traceability relations that we implemented for the EBS case study

and an add-on to an already available braking system. The system boundaries of that embedded system therefore are mostly established by electronic signals. Potential hazards due to brake wear for instances will have to be signaled by the brake and these signals must be taken into account by the safety analysis.

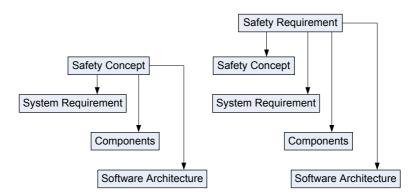

All requirements are managed within Telelogic's DOORS, a widely used requirements management tool (http://www.telelogic.com). They are associated with different levels such as safety requirement, safety concept, system requirement, component specification, etc, and the tool maintains also traces between those levels. These traces are shown in Fig. 4

Apart from DOORS for the requirements management, various other tools should be used throughout the other development phases in order to comply to standard's requirements. A typical tool chain could consist of:

- Matlab's Simulink and Stateflow (http://www.matlab.com) are used for system and component design,

- DSpace's TargetLink (http://www.dspace.com) is used for the implementation and automatic code generation out of the Matlab models.

- Tessy (by Hitex) is used for automated unit testing,

- the Classification Tree Editor (CTE by Hitex) is used to support input domain-based testing,

- Time Partition Testing is employed for generating test cases with continuous input data streams [8,9],

- DSpace's MTest generates test cases automatically based on the Simulink and TargetLink models (http://www.dspace.com),

- QA-C/Misra can be used to analyze the resulting C-code (http://www.qasystems.de),

- PolySpace is a tool that can detect run-time errors during compile time (http://www.polyspace.de), and

- Mercury's Quality Center is a global suite of tools for ensuring software quality (http://www.mercury.com).

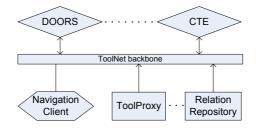

Fig. 5. ToolNet Architecture

Fig. 6. Information model for the requirements engineering phase

#### 4.1 ToolNet

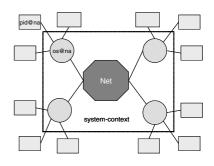

The tools in the previous list are dealing with different types of work products, and the trace tables that we have to devise for the safety case have to refer to the artifacts stored in these various tools. In other words, in order to realize a full tracing between the different work products, we have to gain access to the tools' various data representations. This is done through another tool, called ToolNet which enables us to create traceability links between various development artifacts independent from the type of tool through which they have been created. ToolNet is based on a bus-architecture, the so-called information backbone that connects each tool via an adapter (I) (Fig. 5). Every single development object recognized by ToolNet is assigned a unique ID (object reference) which is based on its data source (a tool or part of a tool). The development objects must be defined unambiguously, according to a product-specific information model **5**. It describes the available and traceable development objects such as hazard, safety concept, safety requirement, etc. An example information model for our project is displayed in Fig. 6 The development object models and the ToolNet structure permit the tools to interact with each other through services implemented in

Fig. 7. Product-specific safety case for the emergency braking control system

Fig. 8. Evaluation of an OCL constraint in ToolNet

their respective adapters. A user can select a specific development object from one tool, e.g., a requirement within DOORS, and associate it with another

| 💶 ToolNet Desktop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |                                                                           | _ D ×         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|---------------|

| File Tools Components Options View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Help                                 |                                                                           |               |

| 🏟 SA 🔌 📣 🚦 💷 🛄 👿 👟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |                                                                           |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |                                                                           |               |

| SafetyAnalyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |                                                                           |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |                                                                           | 🔤 🎛 🗙         |

| $\langle$ Projects $\langle$ Safety Control $\rangle$ Navigation $\langle$ Remote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | View \                               |                                                                           |               |

| Tool Object                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Link(s) of selected object           | Tool Object                                                               | 🖉 Clear       |

| VI SYA:219:Das "Authebungskrite :: SafetyR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |                                                                           | :: SafetyCon  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SR_SC ▶                              | 🎕 SYA:514:Bzgl. der Sicherheit                                            |               |

| 🕥 SYA:451:Eine Notbremsung dar :: Safety –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SR_SC ▶                              | 📬 SYA:515:Eine ausgelöste Not                                             |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GS_C ▶                               | 🧃 Tool Object is not loaded (26                                           |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GS_C ▶                               |                                                                           |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SR_SC ▶                              | 🧃 SYA:515:Eine ausgelöste Not                                             |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GS_C ▶                               |                                                                           |               |

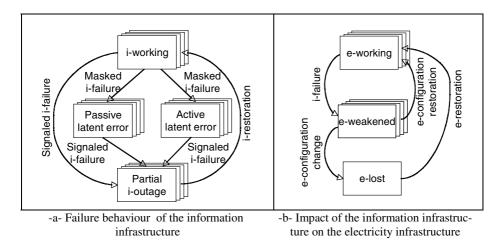

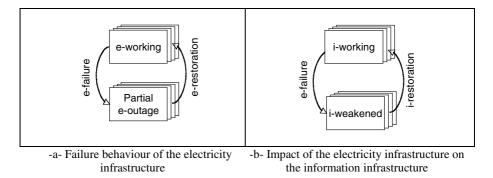

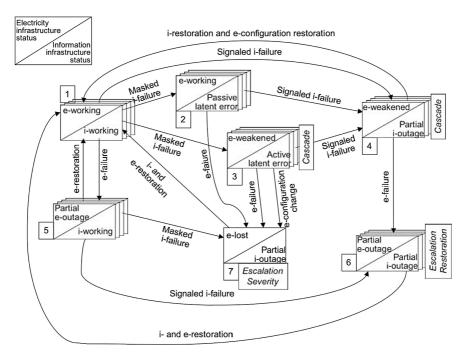

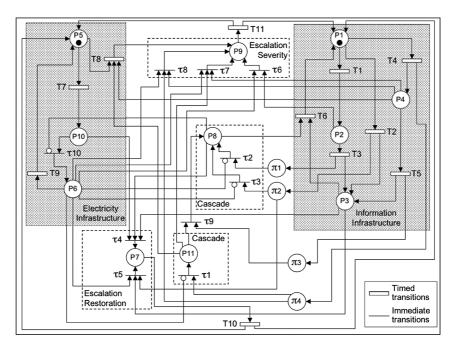

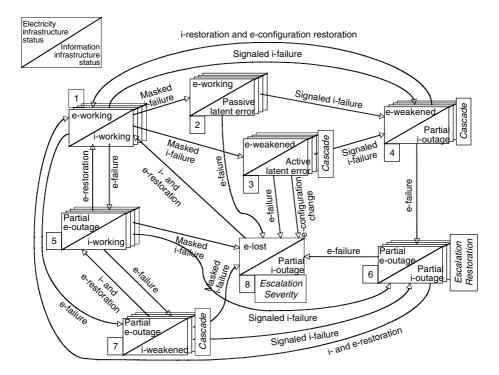

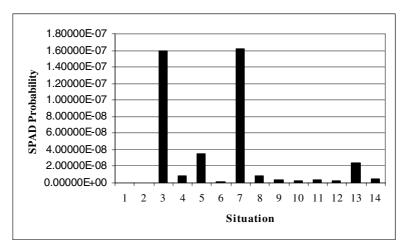

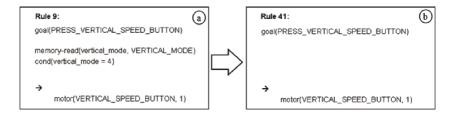

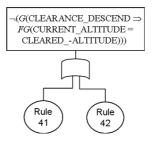

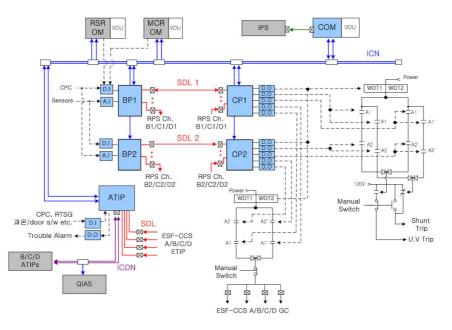

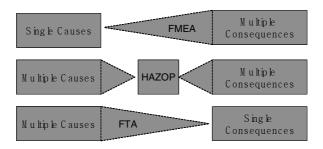

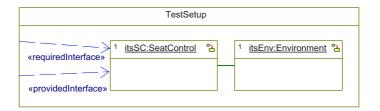

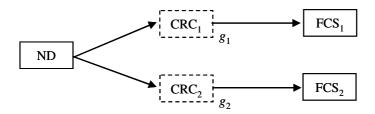

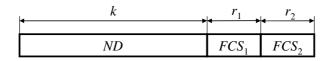

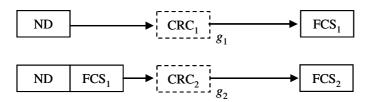

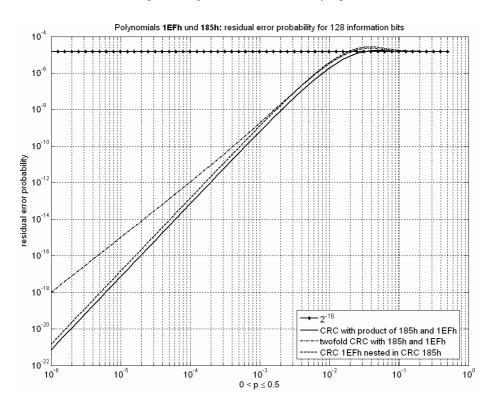

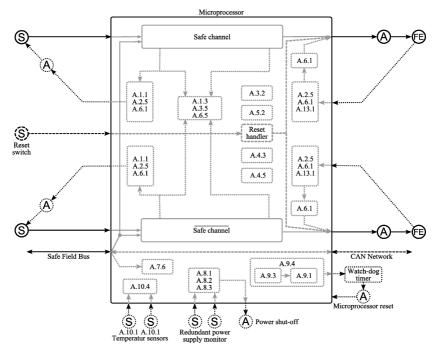

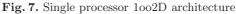

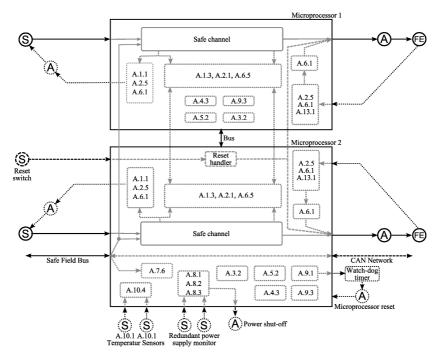

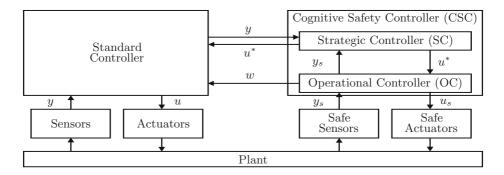

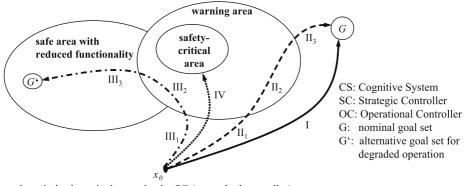

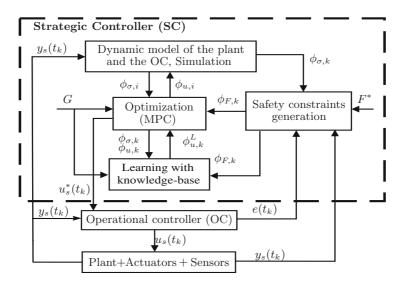

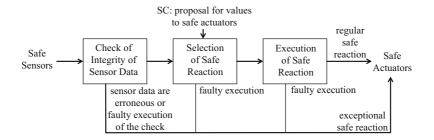

| 🕥 SYA:220:Eine Notbremsung dar :: Safety –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SR_SC ▶                              |                                                                           |               |