Barbara Gallina Amund Skavhaug Friedemann Bitsch (Eds.)

# Computer Safety, Reliability, and Security

37th International Conference, SAFECOMP 2018 Västerås, Sweden, September 19–21, 2018 Proceedings

## **Lecture Notes in Computer Science**

11093

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zurich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology Madras, Chennai, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max Planck Institute for Informatics, Saarbrücken, Germany

More information about this series at http://www.springer.com/series/7408

Barbara Gallina · Amund Skavhaug Friedemann Bitsch (Eds.)

## Computer Safety, Reliability, and Security

37th International Conference, SAFECOMP 2018 Västerås, Sweden, September 19–21, 2018 Proceedings

Editors

Barbara Gallina

Mälardalen University

Västerås

Sweden

Amund Skavhaug Norwegian University of Science and Technology Trondheim Norway Friedemann Bitsch

Thales Deutschland GmbH

Ditzingen

Germany

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-99129-0 ISBN 978-3-319-99130-6 (eBook) https://doi.org/10.1007/978-3-319-99130-6

Library of Congress Control Number: 2018950937

LNCS Sublibrary: SL2 – Programming and Software Engineering

#### © Springer Nature Switzerland AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Preface**

This volume contains the proceedings of the 37th International Conference on Computer Safety, Reliability and Security (SAFECOMP 2018) held during September 19–21, 2018, in Västerås, Sweden. Since 1979, when the conference was established by the European Workshop on Industrial Computer Systems, Technical Committee 7 on Reliability, Safety and Security (EWICS TC7), it has contributed to the state of the art through knowledge dissemination and discussions of important aspects of computer systems of our everyday life. With the proliferation of embedded systems, the omnipresence of the Internet of Things, and the commodity of advanced real-time control systems, our dependence on safe and correct behavior is increasing. Currently, we are witnessing the beginning of the area of truly autonomous systems, perhaps with driverless cars as the most well-known example to the non-specialist, where the safety and correctness of their computer systems are already being discussed in the mainstream media. In this context, it is clear that the relevance of the SAFECOMP conference series is increasing.

The international Program Committee (PC), consisting of 56 members from 15 countries, received 63 papers from 24 nations. Of these, 20 papers were selected to be presented at the conference resulting in an acceptance rate of 31.7%. The review process was thorough with at least three reviewers, which ensured independency, and 20 of these reviewers met in person in Munich, Germany in April 2018 for the final discussion and selection. Our warm thanks go to reviewers who offered their time and competence in the PC work. We are grateful for the support we received from the PC member Mario Trapp, Fraunhofer ESK, who generously hosted the PC meeting.

The conference featured three keynotes: "Software Engineering for Safety in Molecular Programmed Systems" by Robyn Lutz, Professor of Computer Science at Iowa State University; "Reviews?! We Do That! Cross-Domain Reuse of Engineering Knowledge and Evidence" by Uma Ferrell, Software and Airborne Electronic Hardware Designated Engineering Representative for the US Federal Aviation Administration; "Experiences from the Industry, Design and Application of a Control System Platform for Safety of Machinery" by Richard Hendeberg, Specialist in Functional Safety at Epiroc Rock Drills AB.

As in the previous years, the conference was organized as a single-track conference, allowing intensive networking during breaks and social events, and participation in all presentations and discussions. The conference also included a fast abstracts session, giving the opportunity for new ideas and work in progress to bloom in a fertile soil. The Fast Abstracts proceedings are published in the HAL repository.

Finally, the conference also included a panel session, focusing on stimulating an interactive discussion with the audience around the main theme of SAFECOMP 2018, i.e., "Cross- and Intra-Domain Reuse of Engineering and Certification Artefacts: Challenges and Opportunities."

#### VI Preface

As has been the tradition for many years, the day before the main track of the conference was dedicated to five regular workshops: DECSoS, ASSURE, SASSUR, STRIVE, WAISE. Papers from these workshops are published in a separate LNCS volume (11094).

We would like to express our gratitude to the many people who helped with the preparations and running of the conference, especially Friedemann Bitsch as publication chair, Erwin Schoitsch as workshop chair, Jérémie Guiochet as fast abstracts chair, Alexander Romanovsky as publicity chair, and not to be forgotten the local organization and support staff, Irfan Sljivo, Lena Jonsson, Martina Pettersson, Elena Rivani, Linda Claesson, and Gunnar Widforss.

For its support, we wish to thank Mälardalen University, represented by the School of Innovation, Design, and Engineering and, more specifically, by the research group Certifiable Evidences and Justification Engineering. We also wish to thank all other supporting institutions.

Without the support from the EWICS TC7 headed by Francesca Saglietti, this event could not have happened. We wish the EWICS TC7 organization continued success, and we are looking forward to being part of this in the future.

Finally, the most important people to whom we want to express our gratitude are the authors and participants. Your dedication, effort, and knowledge are the foundation of the scientific progress. We hope you had fruitful discussions, gained new insights, and had a memorable time in Västerås.

September 2018

Barbara Gallina Amund Skavhaug

#### **Organization**

**EWICS TC7 Chair**

Francesca Saglietti University of Erlangen-Nuremberg, Germany

**General Chair**

Barbara Gallina Mälardalen University, Sweden

**Program Co-chairs**

Barbara Gallina Mälardalen University, Sweden

Amund Skavhaug The Norwegian University of Science and Technology,

Norway

Workshop Chair

Erwin Schoitsch AIT Austrian Institute of Technology, Austria

**Publication Chair**

Friedemann Bitsch Thales Deutschland GmbH, Germany

**Organizing Committee**

Irfan Sljivo Mälardalen University, Sweden

Lena Jonsson Mälardalen University, Sweden

Martina Pettersson Mälardalen University, Sweden

Elena Rivani Mälardalen University, Sweden

Linda Claesson Mälardalen University, Sweden

Gunnar Widforss Mälardalen University, Sweden

**Publicity Chair**

Alexander Romanovsky Newcastle University, UK

**Fast Abstracts Chair**

Jérémie Guiochet LAAS-CNRS, University of Toulouse, France

#### **Program Committee**

Uwe Becker Draeger Medical GmbH, Germany

Peter G. Bishop Adelard, UK

Friedemann Bitsch Thales Deutschland GmbH, Germany

Robin Bloomfield City University London, UK

Sandro Bologna Associazione Italiana Esperti Infrastrutture Critiche,

Italy

Andrea Bondavalli University of Florence, Italy Jens Braband Siemens AG, Germany Anna Carlsson OHB Sweden, Sweden

António Casimiro University of Lisbon, Portugal

Peter Daniel EWICS TC7, UK

Ewen Denney SGT/NASA Ames Research Center, USA

Felicita Di Giandomenico ISTI-CNR, Italy

Wolfgang Ehrenberger Hochschule Fulda, Germany

Massimo Felici Deloitte Consulting & Advisory, Belgium

Uma Ferrell MITRE Corporation, USA

Francesco Flammini Linnaeus University, Sweden

Barbara Gallina Mälardalen University, Sweden

Ilir Gashi CSR, City University London, UK

Janusz Górski Gdańsk University of Technology, Poland

Jérémie Guiochet LAAS-CNRS, France

Maritta Heisel University of Duisburg-Essen, Germany

Chris Johnson University of Glasgow, UK

Bernhard Kaiser Assystem Germany GmbH, Germany

Karama Kanoun LAAS-CNRS, France

Johan Karlsson Chalmers University of Technology, Sweden

Phil Koopman Carnegie Mellon University, USA

Floor Koornneef Delft University of Technology, The Netherlands

Timo Latvala Space Systems Finland Ltd., Finland

Bev Littlewood City University London, UK

Silvia Mazzini Intecs, Italy

John McDermid University of York, UK

Frank Ortmeier Otto-von-Guericke Universität Magdeburg, Germany

Michael Paulitsch Intel, Austria

Holger Pfeifer Technical University of Munich, Germany

Thomas Pfeiffenberger Salzburg Research Forschungsgesellschaft m.b.H,

Austria

Peter Popov City University London, UK

Laurent Rioux Thales R&T, France

Alexander Romanovsky

John Rushby

Newcastle University, UK

SRI International, USA

Francesca Saglietti University of Erlangen-Nuremberg, Germany

Christoph Schmitz Zühlke Engineering AG, Switzerland

Erwin Schoitsch AIT Austrian Institute of Technology, Austria

Christel Seguin Office National d'Etudes et Recherches Aérospatiales,

France

Amund Skavhaug The Norwegian University of Science and Technology,

Norway

Mark-Alexander Sujan University of Warwick, UK

Kenji Taguchi CAV Technologies Co., Ltd., Japan Stefano Tonetta Fondazione Bruno Kessler, Italy

Mario Trapp Fraunhofer Institute for Experimental Software

Engineering, Germany

Elena Troubitsyna Åbo Akademi University, Finland Fredrik Törner Volvo Car Corporation, Sweden

Martin Törngren KTH Royal Institute of Technology, Sweden

Pieter van Gelder Delft University of Technology, The Netherlands

Marcel Verhoef European Space Agency, The Netherlands

Jonny Vinter RISE Research Institutes of Sweden

Helene Waeselynck LAAS-CNRS, France

#### **Additional Reviewers**

Matthieu Amy LAAS-CNRS, France Milan Battelino OHB Sweden, Sweden

Victor Bos Space Systems Finland Ltd., Finland Bill Drozd Carnegie Mellon University, USA

Sam George Adelard, UK

Didem Gürdür KTH Royal Institute of Technology, Sweden

Denis Hatebur University of Duisburg-Essen, Germany

Dubravka Ilic Space Systems Finland Ltd., Finland

Lola Masson LAAS-CNRS, France

Viorel Preoteasa Space Systems Finland Ltd., Finland Irum Rauf Åbo Akademi University, Finland RISE Research Institutes of Sweden

Paulius Stankaitis Newcastle University, UK

Kimmo Varpaaniemi Space Systems Finland Ltd., Finland Inna Vistbakka Åbo Akademi University, Finland

Andrzej Wardziński Gdańsk University of Technology, Poland Xinhai Zhang KTH Royal Institute of Technology, Sweden

#### **Supporting Institutions**

European Workshop on Industrial Computer Systems Reliability, Safety and Security

Mälardalen University, Sweden

Norwegian University of Science and Technology

Austrian Institute of Technology

Thales Deutschland GmbH

Lecture Notes in Computer Science (LNCS), Springer Science + Business Media

Austrian Computer Society

#### ARTEMIS Industry Association

European Network of Clubs for Reliability and Safety of Software-Intensive Systems European

Network of

Clubs for

REliability and

Safety of

Software

German Computer Society

Electronic Components and Systems for European Leadership - Austria

Verband österreichischer Software Industrie

#### XII Organization

European Research Consortium for Informatics and Mathematics

IEEE SMC Technical Committee on Homeland Security (TCHS)

# Software Engineering for Safety in Programmed Molecular Systems

Robyn R. Lutz

Iowa State University, Ames, IA 50011, USA

**Abstract.** Molecular programming uses the computational power of DNA and other biomolecules to create nanoscale systems. Many of these envisioned nano-systems are safety-critical, such as diagnostic biosensors that detect contaminants, drug capsules that dispense medicine when they encounter diseased cells, and configurable nano-robots. Challenges to the safety engineering of the nano-systems include their probabilistic behavior, their very small size, the very large number of them that execute at once, and the dynamic environment in which they operate. Designs need to assure safe outcomes from highly fault-prone devices, hampered by the difficulty of defining the limits of their safe operation.

I organize the talk around our interdisciplinary team's development of an essential safety building block for programmed molecular systems – an embeddable, reusable, molecular Runtime Fault Detector. I describe how we harnessed goal-oriented requirements and risk analyses, reaction network modeling, and probabilistic model checking to specify, analyze, and verify the safety requirements and design for this new nano-system. Finally, I suggest that a similar approach also may be helpful in the safety engineering of non-molecular systems composed of highly distributed, autonomous, fault-prone components operating in dynamic environments.

**Keywords:** Software safety · Molecular programming · Software engineering Chemical reaction networks

**Acknowledgments.** This research was supported in part by National Science Foundation Grant 1545028.

# Reviews?! We do that! Cross-Domain Reuse of Engineering Knowledge and Evidence

#### Uma Ferrell

MITRE Corporation, 7515 Colshire Drive, McLean VA 22102, USA

Abstract. Both industry and certification authorities have reason to be excited about the benefits and opportunities of reusing and building products for more than one domain such as aviation and automobiles. Cross-domain reuse in an increasingly complex world can inject novel technologies to conventional domains to increase safety. Such opportunities come with social and ethical responsibilities for the safe use of a product in the target environment, not just whether the product and evidence are acceptable to certification authorities. The evidence may be wrongly presented based only on the equivalency in the use of expected language in pertinent standards. The evidence should be based on the actual accomplishments met and whether those accomplishments are applicable towards design assurance and safety in the target domain and environment. Cross-domain reuse has many considerations. This talk is focused only on safety and security. Obviously, consideration of reuse must include functionality, use of standards in that domain, and certification concerns. All these considerations have undercurrents of safety as well as security. Let us focus further on three topics:

- **Derivation of risk:** Derivation of risk depends on the target domain and the human/system use of the product. Also, the acceptable level of risk tolerance is inherently different in different domains. Aviation is one of the few domains where safety risk tolerance is codified. As stewards of safety in this society, we need to be aware of the real idea behind certification, and promulgate a safety culture to take responsibility for safe cross-domain use of the product throughout the product life.

- Appropriate use of evidence: While acceptability for certification is important, the knowledge and evidence for why a product is acceptable is even more important. Evidence may have been produced in a previous domain that appears to be usable in a target domain. Only the basis for that evidence may have a different interpretation and implication in the target domain because the terminology for even simple terms such as "reviews" may not have the same meaning in different domains. Further, the same functionality may be used in diverse ways in the two domains.

- Importance of systems engineering: There are certainly considerations that may be codified and delegated to checklists. But blind use of checklists makes a poor substitute for domain knowledge and engineering. Cross-domain use does not just mean that one could deploy a product. Continued safe use of the product in the target domain has specific implications for maintenance of the product as well as maintenance of the system of which the product is just one component. For example, an electro-mechanical system may need adjustments

to maintenance cycles depending on the characteristics of the component commanding the mechanical actions. In general, we must make sure that component engineering is within the context of system safety and security.

Opportunities of cross-domain reuse indeed come with responsibilities to understand, analyze, and engineer the product. Appropriate reuse considered in the system context can be a powerful tool to introduce newer technologies to solve complex problems.

# Experiences from the Industry, Design and Application of a Control System Platform for Safety of Machinery

#### Richard Hendeberg

Epiroc Rock Drills AB, Örebro, Sweden richard.hendeberg@epiroc.com

**Abstract.** Epiroc Rock Drills AB is a global manufacturer of mining and construction machinery. These highly automated machines operates in an incredibly harsh environment where reliability and availability is paramount. In this talk, the focus is on Epiroc's control systems platform and work with safety of machinery. How a modular design, componentization of software and standardization on hardware modules has led to an efficient reuse of engineering efforts and an automation platform, which is used throughout Epiroc's entire range of machinery. In this talk, it is also given an overview of Epiroc's journey with safety of control systems, leading up to the integration of safety functions into the existing control system platform. The challenges of designing safety functions for a harsh environment and why availability of the machine might be as important for the safety of the operator as the reliability of the safety function.

**Keywords:** Mining machinery  $\cdot$  Construction machinery  $\cdot$  Safety of machinery Hardware component reuse

### **Contents**

| Automotive Safety Standards and Cross-Domain Reuse Potential                                                                                |     |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Practical Experience Report: Automotive Safety Practices vs. Accepted Principles                                                            | 3   |

| A Generic Method for a Bottom-Up ASIL Decomposition                                                                                         | 12  |

| Assurance Benefits of ISO 26262 Compliant Microcontrollers for Safety-Critical Avionics                                                     | 27  |

| Autonomous Driving and Safety Analysis                                                                                                      |     |

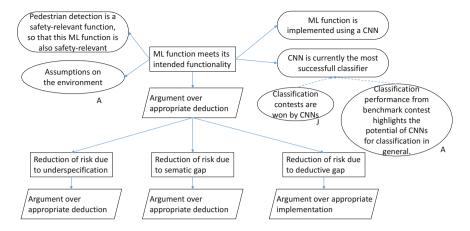

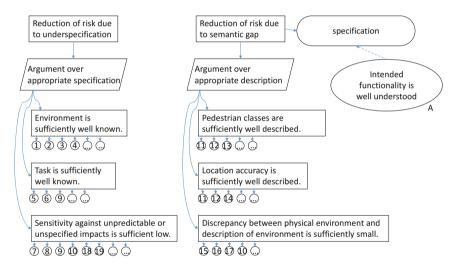

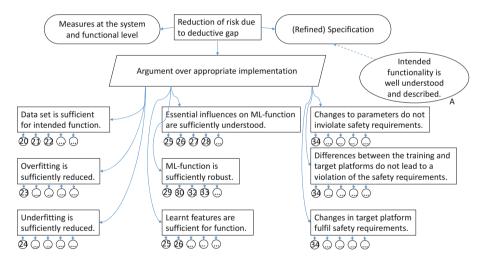

| Structuring Validation Targets of a Machine Learning Function  Applied to Automated Driving                                                 | 45  |

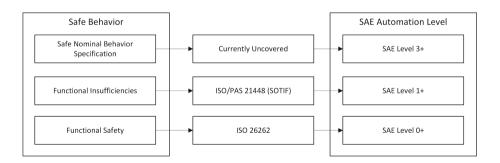

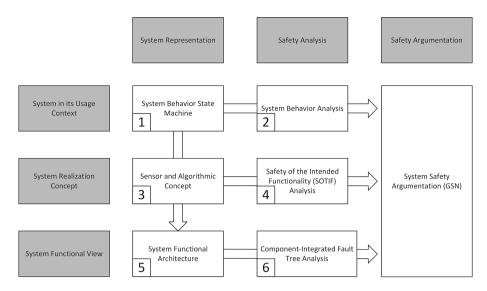

| Multi-aspect Safety Engineering for Highly Automated Driving:  Looking Beyond Functional Safety and Established Standards and Methodologies | 59  |

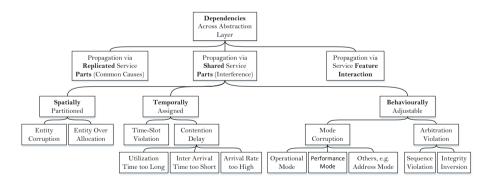

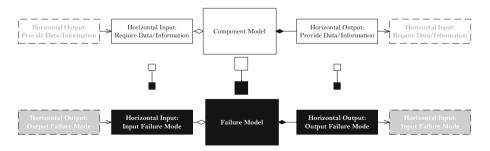

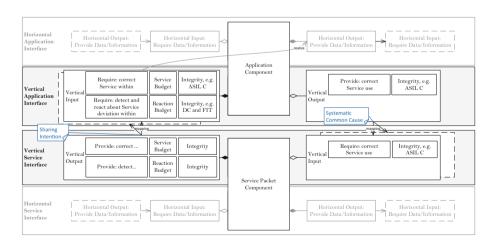

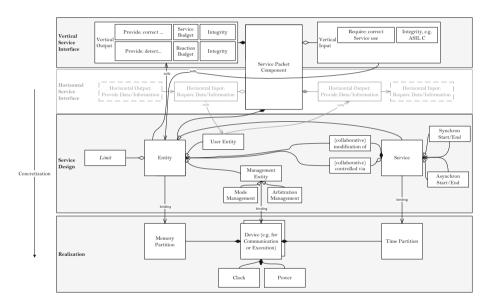

| A Model-Based Safety Analysis of Dependencies Across Abstraction Layers                                                                     | 73  |

| Verification                                                                                                                                |     |

| Formal Verification of Signalling Programs with SafeCap                                                                                     | 91  |

| Deriving and Formalising Safety and Security Requirements for Control Systems.                                                              | 107 |

| Elena Troubitsyna and Inna Vistbakka                                                                                                        | 107 |

| Optimal Test Suite Generation for Modified Condition Decision Coverage Using SAT Solving                                                                                                                               | 123 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Takashi Kitamura, Quentin Maissonneuve, Eun-Hye Choi, Cyrille Artho, and Angelo Gargantini                                                                                                                             |     |

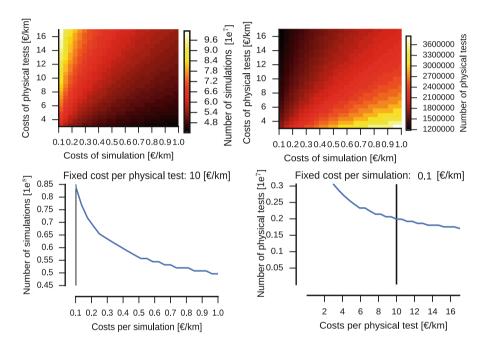

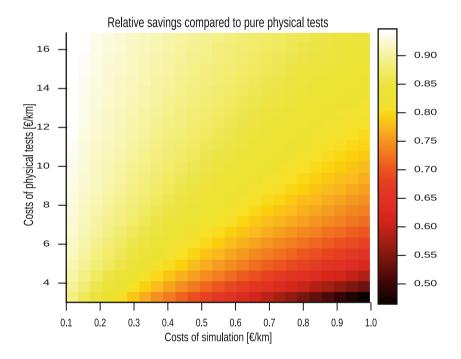

| Efficient Splitting of Test and Simulation Cases for the Verification of Highly Automated Driving Functions                                                                                                            | 139 |

| Multi-Concern Assurance                                                                                                                                                                                                |     |

| Roadblocks on the Highway to Secure Cars: An Exploratory Survey on the Current Safety and Security Practice of the Automotive Industry Michael Huber, Michael Brunner, Clemens Sauerwein, Carmen Carlan, and Ruth Breu | 157 |

| Safe and Secure Automotive Over-the-Air Updates                                                                                                                                                                        | 172 |

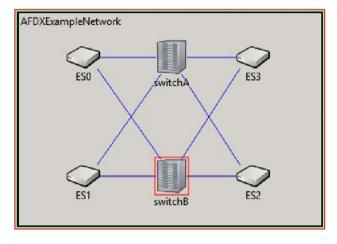

| Dependability Analysis of the AFDX Frame Management Design  Venesa Watson and Mahlet Bejiga                                                                                                                            | 188 |

| Fault Tolerance                                                                                                                                                                                                        |     |

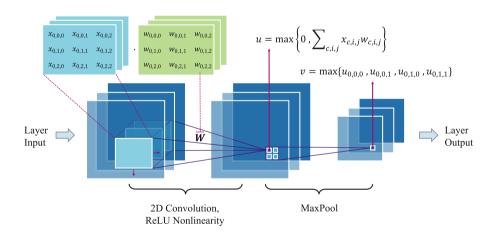

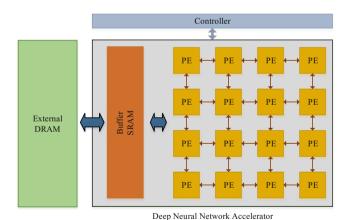

| Efficient On-Line Error Detection and Mitigation for Deep Neural Network Accelerators                                                                                                                                  | 205 |

| Random Additive Control Flow Error Detection                                                                                                                                                                           | 220 |

| Fault-Tolerant Clock Synchronization with Only Two Redundant Paths Zoha Moztarzadeh                                                                                                                                    | 235 |

| MORE: MOdel-based REdundancy for Simulink                                                                                                                                                                              | 250 |

| Safety and Security Risk                                                                                                                                                                                               |     |

| Diversity in Open Source Intrusion Detection Systems                                                                                                                                                                   | 267 |

|                                                                                    | Contents | XXI |

|------------------------------------------------------------------------------------|----------|-----|

| Inter-device Sensor-Fusion for Action Authorization on Industry Mobile Robots      |          | 282 |

| Towards a Common Ontology of Safety Risk Concepts for Ra<br>Vehicles and Signaling |          | 297 |

| Author Index                                                                       |          | 311 |

## **Automotive Safety Standards and Cross-Domain Reuse Potential**

# Practical Experience Report: Automotive Safety Practices vs. Accepted Principles

Philip Koopman<sup>(⊠)</sup>

Carnegie Mellon University, Pittsburgh, PA 15217, USA koopman@cmu.edu

**Abstract.** This paper documents the state of automotive computer-based system safety practices based on experiences with unintended acceleration litigation spanning multiple vehicle makers. There is a wide gulf between some observed automotive practices and established principles for safety critical system engineering. While some companies strive to do better, at least some car makers in the 2002–2010 era took a test-centric approach to safety that discounted non-reproducible and "unrealistic" faults, instead blaming driver error for mishaps. Regulators still follow policies from the pre-software safety assurance era. Eight general areas of contrast between accepted safety principles and observed automotive safety practices are identified. While the advent of ISO 26262 promises some progress, deployment of highly autonomous vehicles in a non-regulatory environment threatens to undermine safety engineering rigor.

**Keywords:** Software safety · Automotive · Unintended acceleration

#### 1 Introduction

Innocent people have died, been severely injured, or gone to jail because of defects or potential defects in computer-based automotive systems. With the deployment of self-driving cars, it is more important than ever to understand the gaps between theory and practice in automotive computer-based system safety.

This paper is based on the author's personal experiences with unintended acceleration (UA) litigation against car makers (Original Equipment Manufacturers, or OEMs) for 2000–2010 model year vehicles, and additional experiences with multiple recent military and commercial self-driving car (Autonomous Vehicle, or AV) safety assurance projects. These experiences include access to extensive sets of engineering documents, analysis of Electronic Throttle Control (ETC) source code, and vehicle testing to confirm identified safety vulnerabilities. These experiences have revealed common threads that encompass technical, business, regulatory, and litigation aspects of safety. While regulatory environments vary in other countries, the significant role that the United States (US) car industry and US legal system play in the automotive domain ensure that these factors will influence many cars produced worldwide.

Unlike other domains, conformance to international computer-based system safety standards is voluntary for US-sold vehicle OEMs and suppliers. Moreover, some OEMs have not followed industry-specific guidelines such as the MISRA Software Guidelines [1], including vehicles that are the subject of two class action lawsuits. [2] at

<sup>©</sup> Springer Nature Switzerland AG 2018

B. Gallina et al. (Eds.): SAFECOMP 2018, LNCS 11093, pp. 3–11, 2018.

30:21–25 and [3] at 78:15–79:15. (Note that [2] is a transcript from a death and injury case involving a vehicle of a type included in the corresponding class action lawsuit).

The US permits OEMs to deploy vehicles that are self-certified to meet provisions of the US Federal Motor Vehicle Safety Standards (FMVSS). FMVSS regulations take the form of a test procedure approach originally intended to ensure that the normal safety-relevant functionality of pre-computer vehicles, such as braking capability, was adequate. While some simplistic failure modes such as detecting the complete loss of a functional subsystem are included, the test procedures are not intended to achieve any defined amount of software testing coverage, are not designed to detect non-deterministic faults, and do not demonstrate fault recovery from non-trivial computational faults. While vehicles commonly use some basic fault tolerance patterns such redundant CPUs for life-critical functions, it can be the case that redundancy and other fault tolerant computing techniques not used in accordance with accepted practices, such as dual-CPU designs with a single point of failure [4].

At least one death has been officially declared to be due to automotive computer system malfunction [4], and there have been approximately 500 settlements for death and injury alleged to also be due to defective vehicle designs by the same OEM [5]. Another class action against a second OEM alleges similar issues [3]. Additionally, there are instances in which individuals have faced civil or criminal penalties for mishaps they claim were caused by vehicle malfunctions (e.g., [6]). Now that computers have life critical control authority, they must be considered as a credible potential cause of severe mishaps.

Electrified vehicles present additional risks because regenerative braking tends to disable the direct hydraulic connection between the brake pedal and friction-based brake pads [7]. (If this weren't the case, energy could be lost due to friction instead of being used to recharge the battery.) Some drivers have reported loss of brake effectiveness with these vehicles (e.g., [8]) which could potentially be caused by a software defect. Some litigation has involved reported symptoms consistent with such a defect. Increasing levels of autonomy raise the stakes further.

| Accepted safety principle             | Observed automotive safety practice      |  |  |

|---------------------------------------|------------------------------------------|--|--|

| Evidence required to show safety      | Evidence required to show defect         |  |  |

| Safety argument                       | System-level functional test             |  |  |

| Arbitrary failures                    | "Realistic" failures                     |  |  |

| Random failures expected              | Non-reproducible failures are discounted |  |  |

| Blaming humans is a last resort       | Driver error presumed                    |  |  |

| Engineering rigor and integrity level | All unsafe defects identified and fixed  |  |  |

| Independent assessment                | Self-certification                       |  |  |

| ALARP, etc.                           | Cost effective regulation                |  |  |

|                                       |                                          |  |  |

Table 1. Contrasting areas of safety principles and observed automotive practices.

Table 1 identifies areas in which some observed OEM practices do not necessarily correspond with accepted safety principles. The scope of this table deals with vehicles produced with ETC in the 2002–2010 era from some Asia, US and European OEMs

selling into the US market. It should be emphasized that some OEMs claim to follow accepted safety practices. And to be clear, the listed OEM practices should not be considered industry-accepted practices for making safe vehicles, but rather should be seen as areas in which some OEMs' observed practices fell short of meeting accepted safety practices. Based on personal experience in a variety of venues, it is clear that portions of the OEM and supplier ecosystem were still stuck in the pre-software safety engineering era at least up until the creation of ISO 26262 [9], and that adoption of that new standard is taking time.

#### 2 Safety Principles vs. Automotive Safety Practices

#### 2.1 Safety Arguments Aren't Specifically Required by Regulators

A general safety principle is that a system is not presumed to be safe until a mishap occurs, but rather must be demonstrated to be safe before deployment. Approaches to demonstrating safety are typically based on some sort of safety argument. That argument might be explicit (e.g., a GSN argumentation structure [10]), implicit in the form of having followed a suitable set of safety practices (e.g., [1]), or some mixture of the two. Common codified safety practices include the generic notions of a Safety Integrity Level (SIL), Design Assurance Level (DAL), or other risk-based approach to identifying and requiring a defined level of engineering rigor.

The US legal system, on the other hand, tends to emphasize the identification of defects. OEMs can attempt to defend themselves simply by asserting that their vehicle is safe because no bugs have been identified that lead to UA [11] at 47:3–10. Injured parties and their experts typically must search for relevant bugs or other design defects such as single points of failure to support a vehicle defect argument.

US regulations do not require vehicles to have a safety argument beyond FMVSS compliance, although using one is not precluded. However, lack of following accepted engineering practices can be a contributing factor to legal outcomes, especially when considering negligence. Additionally, a pattern of mishaps can lead to a mandatory vehicle recall in some cases.

Some European vehicles in the 2000s adopted the E-Gas approach for electronic throttle control ([12] is a newer, publicly available description). In general, the approach involves a primary functional unit that performs control, and monitoring/checking units that disable engine power if a fault is detected. The suitability of this approach for life-critical applications depends upon adequate isolation between doer/checker levels and appropriate fault coverage. In some cases, independent UA mitigation is required, such as a vacuum pump to boost braking force independent of throttle position. The specification also describes required fault handling functionality.

#### 2.2 Argumentation vs. Testing

While general safety principles require some sort of argument based in part on engineering analysis and rigor, the US regulatory system and much common practice is heavily based on vehicle-level testing. It is common for OEMs to practice

non-software-specific techniques for fault analysis such as DFMEAs [13]. However, use of more advanced computer-based system safety techniques is uneven.

As previously discussed, the centerpiece of US automotive safety regulation is the suite of Federal Motor Vehicle Safety Standards (FMVSS). While some testing contemplates simplistic component fault models, FMVSS criteria generally do not involve design processes, code quality, or other accepted computer-based system safety considerations. For example, FMVSS 138 [14] fault injection covers a silent malfunction due to loss of component power in a tire pressure monitoring system. Similarly, US National Highway Traffic Safety Administration (NHTSA) investigations involve vehicle level testing and discussions with the OEM, but emphasize driver error as a cause of UA. For example, [15] blames the driver rather than the ETC for data samples showing a doubling of engine RPM and vehicle speed with unchanged accelerator pedal input.

#### 2.3 Arbitrary vs. "Realistic" Faults and Failures

For safety critical systems, even a single bit flip or other small fault has the potential to cause a catastrophic mishap if not sufficiently mitigated. Well defined and expansive fault models such as transient faults and single event upsets are well known in the areas of safety and fault tolerant computing research. Arbitrary failures of computer-based system components must be considered when designing life-critical systems [16]. Moreover, there is an increasing body of confirmed reports of Byzantine (e.g., two-faced) faults occurring in real systems [17]. However, some OEMs do not embrace these accepted fault and failure models.

Automotive OEM safety analysis is often concerned with simplistic fault models such as electrical wires shorted to power supply voltages, open circuits, or computer crashes. Faults that are subjectively judged not to be "realistic" by designers are often dismissed. However, research has documented subtle real world faults and failures that defy designer intuition about fault realism [18].

Any redundancy often relies upon self-diagnosis and simplistic fault detection mechanisms such as watchdog timers, heartbeats, and input port sanity checks [4]. Such simplistic redundancy management approaches offer only partial fault coverage, and permit dangerous fail-active behaviors [19].

#### 2.4 Failure Reproducibility

Transient faults and resulting failures are generally not reproducible upon demand in ordinary system operation, because the underlying causes can be comparatively infrequent, randomly occurring events. Fault injection experiments reveal vulnerabilities, but are routinely criticized in litigation for involving minor instrumentation modifications to vehicle software such as inclusion of a subroutine to flip memory bits upon command. Such modifications are then claimed to render fault injection results invalid due to involving a variation from the exact software image that would be in a production vehicle, or otherwise not being "realistic" [11] at 84:14–24.

Diagnostic gaps and undiagnosed failures are common. In some – but not all – cases, Trouble Not Identified (TNI) incidents can eventually be traced to systematic

causes with sufficient detective work [20]. Despite less than complete diagnostic coverage, and substantial TNI rates, ETC malfunction is often inappropriately ruled out by OEMs or investigators when no Diagnostic Trouble Code (DTC) has been recorded. This is especially true when problems cannot be reproduced with the subject vehicle – even when a report is made by a source that many would consider credible, such as a dealership employee or police officer [3] at 86:10–87:24.

Automotive safety struggles with non-reproducible faults. NHTSA tends to close investigations of non-reproducible faults rather than investigating potential software defects as root causes of mishaps. Similarly, OEMs can emphasize reproducible faults and undeniable trends of field data, rather than perceived "one-off" events, in part to avoid putting "the company out of business" [21].

#### 2.5 The Driver Error Narrative

It is well known that humans are imperfect. It follows that the heart and soul of a typical UA legal defense is a claim of driver error, typically in the form of pressing the accelerator pedal instead of the brake pedal. Many publications, including those from NHTSA, repeat the refrain of driver error causing UA events [22]. However, these reports fail to consider computer system defects. Rather, reports conclude that in the absence of mechanical defects or concrete physical evidence of a vehicle malfunction the cause of a mishap must be drive error. Situations that provide truly compelling evidence to rule out drive error tend to be attributed to "unknown" causes.

While OEMs and NHTSA typically cite various reports in support of the pedal misapplication narrative, what data can be found on that specific failure mode tends to tell a different story. A pre-ETC analysis of 997 "reasons/excuses" for crashes found only one instance of "hit gas pedal instead of brake" – but 29 instances of "vehicle failure" [23] pp. 293, 296. Thus, contrary to the typical human error narrative, available data provides support for a finding that vehicles malfunction more often than humans press the wrong pedal.

Revisiting the Audi 5000 investigation report reveals that even the veritable poster child of human error producing UA provides incomplete support for the pedal misapplication narrative. Audi vehicle malfunctions produced up to 0.3 g of un-commanded acceleration, having nothing to do with driver error. However, when such a UA event startled the driver, sometimes the driver would press the wrong pedal, resulting in a collision before there was time to self-correct in a tight-quarters situation [24].

Pedal misapplication issues are complicated by problems with data recording strategies, such as potentially missing driver actions due to under-sampling [15]. Moreover, data recordings can be untrustworthy to the extent they rely upon suspect data being provided by the same computer that is potentially causing the UA.

#### 2.6 Engineering Rigor

Developing naked, undocumented code with no substantive safety process can reasonably be expected to result in defects that could cause a catastrophic loss event for life critical systems. This can create a fear that developers will be criticized for the smallest of imperfections. However, the remedy for this fear is well understood: use an

accepted safety approach. If nothing else, a successful independent assessment provides an argument in defense of allegations of negligence. However, a negative assessor report can appear to be adverse in litigation [3] at 78:15–78:21.

Some automotive designers adopted model-based design during the 2000–2010 timeframe. This type of approach can provide tool support for certified code generation and formal proofs of correctness for some aspects of system operation. However, more than this is required for safety, and use of this type of tooling does not by itself ensure good design quality. The two class action cases discussed in this paper did not make any apparent use model based design for the code in question.

#### 2.7 Certification and Deployment of Autonomous Vehicles

Independent assessment of safety standard conformance has been possible for many years in the automotive industry. However, current automotive regulations only require assessment against FMVSS test regimes. The future of AVs currently promises more of the same. A first draft AV policy [25] encouraged some level of accountability for safety arguments via a self-certification signature sheet. However, a later version takes a "non-regulatory" approach to safety, making even self-certification entirely optional for AVs [26]. Current US federal regulatory efforts emphasize modifications or waivers of FMVSS test regimes to accommodate AVs.

Of significant concern in AV deployment is the usual argument for doing so: human drivers make avoidable mistakes; computers won't make those mistakes; therefore computers will be safer drivers than humans. There is insufficient field data and no robust technical public safety argument upon which to base an assertion that AVs have even achieved safety parity with an "average" human driver (whatever that might actually mean, noting that impaired drivers are part of the human driver population). Perhaps AVs will simply make *different* mistakes. Ensuring AV safety is complicated by the use of novel technologies such as machine learning [27].

Two vendors have commendably published safety brochures [28, 29]. No vendors currently claim rigorous, independently assessed safety arguments.

#### 3 Regulatory and Litigation Considerations

#### 3.1 Cost Effectiveness of Safety Assessment

Accepted safety practices require reducing risk to an acceptably low level, e.g., As Low as Reasonably Practicable (ALARP). However, US government agencies are required to justify that all new regulations, including safety regulations, are cost effective. The existing pedal misapplication narrative surrounding UA makes it difficult to introduce new software safety regulations to avoid software defects, because such defects have not been officially blamed for many mishaps. If there is no apparent carnage from unsafe software, it is difficult to cost-justify improving software safety. However, new laws can create stronger safety requirements without cost justification.

The litigation aspect of cost effectiveness is a bit different. Generally, the questions asked are whether accepted engineering practices were followed, and whether a

reasonable alternative design approach would have prevented a mishap from occurring. However, a defect must first be identified before those questions are asked, and generally some sort of loss or legal violation must occur before legal action can be taken.

#### 3.2 Source Code Availability

Source code is generally unavailable for inspection unless a very large litigation effort is mounted. Government regulators do not have access to source code, nor do any outside assessors unless the OEM decides to voluntarily grant access. Even if litigation source code access is granted, it is often done under onerous conditions such as via a dedicated non-networked secure room with a metal detector wanding procedure before entrance. In one case, a judge found that OEM "misrepresentations caused Plaintiffs to incur unnecessary costs" due to requiring overly burdensome source code security measures [30]. All things considered, source code analysis can easily turn into a million-dollar-plus effort including the cost of litigating to gain access, the cost of operating a secure room, and expert witness costs. This makes source code analysis impractical for most litigation, especially criminal defense, unless it can piggy-back on a class action lawsuit that has deep pockets financial backing.

The expense and difficulty of source code analysis provides a perverse incentive for poor code quality, skimpy design information, and opaque configuration management practices. The more difficult to understand the software system is, the more difficult and expensive it will be for experts to access it and identify specific defects that could have caused UA or other dangerous vehicle behaviors.

#### 3.3 The Importance of Academic Rigor in Publication

Academics need to be aware that litigation uses peer-reviewed academic papers as evidence to support expert testimony. Even a well-intentioned paper that reaches a flawed or poorly stated conclusion can do significant damage to practical safety if a lawyer can find a way to interpret it as providing protective cover for an unsafe system. Researchers and reviewers should be mindful of ways in which a paper might be used to support an opinion that accepted safety practices are deficient unless that is truly the finding of the research data. A particularly important point is that old techniques should not be identified as defective simply because new techniques are better. Studies should disclose threats to validity so that conclusions are not applied in inappropriate situations. Finally, reviewers and editors should ensure that authors who attempt to discredit previous publications fully disclose potential conflicts of interest that might potentially result in bias, such as involvement in pending litigation adverse to the previous publication's findings or authors [31].

#### 4 Conclusions

Automotive-specific safety guidelines and standards have existed for more than two decades. Yet adoption is not required, and not is universal. Recent findings of industry cover-ups regarding sticky gas pedals, floor mats, ignition switches, air bags, and

emission defeat devices do not inspire confidence. One can hope that the significant costs paid by OEMs for these transgressions will motivate better behavior in the future. Litigation historical outcomes notwithstanding, it remains to be seen whether AV designers will adopt robust safety engineering practices, or will succumb to pressure and take shortcuts in the rush to market.

While it would be best if all OEMs actually adopted well understood accepted safety practices, a more pragmatic approach is to perform research that will meet the automotive industry where it is instead of where it should be. To that end, additional work on the following topics could help improve practical automotive safety (this list should not be interpreted as criticism of currently accepted safety practices):

- Studies that explicitly differentiate between driver error and computer faults

- Studies that measure how well specific safety techniques reduce mishap risk

- Fault injection techniques tailored to production vehicle deployment

- System-level testing approaches that validate safety

- Safety measurement approaches suitable for FMVSS test procedure codification

- Forensically valid automotive data recorders

- AV-specific safety validation (e.g., machine learning safety validation)

- Better understanding of the factors that support a robust safety culture.

More generally, anything that the safety community can do help educate regulators, lawmakers, and non-specialist automotive practitioners appreciate the importance of adopting safety techniques proven in other domains can also help.

Threats to Validity: Reported experiences are based on previous-generation vehicle designs due to the retrospective nature of the litigation and regulatory system. There is a significant variation in OEM attitudes and practice of safety, and certainly some OEMs try hard to adopt and even go beyond basic accepted safety practices.

*Disclosure:* The author is involved in ongoing litigation concerning multiple OEMs, including Toyota and Ford, and is a principle in an autonomous vehicle safety company. He is not a lawyer. No external support funded this research.

#### References

- 1. MISRA: Development Guidelines for Vehicle Based Software, November 1994

- 2. Bookout v. Toyota Trial Transcript, 11 October 2013. https://goo.gl/MP8w3w

- 3. Charles Johnson et al. v. Ford Motor Company, US Dist. S. WV, Huntington, 3:13-CV-06529, 1 Feb 2018 PM. (Lawyer summaries of expert testimony and evidence)

- Koopman, P.: A case study of toyota unintended acceleration and software safety. Carnegie Mellon University, 18 September 2014. Presentation slides

- Kennedy, J.: Toyota has reached deals in 496 cases in acceleration MDL. Law360, 15 November 2017. https://goo.gl/T4TaLs

- 6. Manganis, J.: Cop's fatal-crash trial underway; defense appears to abandon long-touted 'sudden acceleration' theory. Salem News, 17 March 2008. https://goo.gl/jiZ9rN

- 7. Toyota, 2005 Prius Repair Manual (RM1130U), pp. 05-951

- 8. Marosi, R., Olivarez-Giles, N.: Runaway prius driver: I was laying on the brakes but it wasn't slowing down, 10 March 2010. https://goo.gl/aZK7BM

- 9. ISO: Road vehicles-Functional Safety-Management of functional safety, ISO 26262 (2011)

- 10. GSN Community Standard Version 1, November 2011

- 11. Bookout v. Toyota Trial Transcript, 22 October 2013. https://goo.gl/hh47vg

- 12. EGAS Working Group, Standardized E-Gas Monitoring Concept for Gasoline and Diesel Engine Control Units, Version 5.5 (2013)

- SAE: Potential Failure Mode and Effects Analysis in Design (Design FMEA), J1739\_200901, 15 January 2009

- GPO: Section 571.138, Standard No. 138; Tire pressure monitoring systems. 49 CFR Ch. V (10-1-11 Edition)

- 15. NHTSA: Denial of a petition for a defect investigation. Federal register vol. 80, no. 93, pp. 27835–27844, 14 May 2015

- Lala, J., Harper, R.: Architectural principles for safety-critical real-time applications. Proc. IEEE 82(1), 25–40 (1994)

- Driscoll, K., Hall, B., Sivencrona, H., Zumsteg, P.: Byzantine fault tolerance, from theory to reality. In: Anderson, S., Felici, M., Littlewood, B. (eds.) SAFECOMP 2003. LNCS, vol. 2788, pp. 235–248. Springer, Heidelberg (2003). https://doi.org/10.1007/978-3-540-39878-3\_19

- 18. Driscoll, K.: Real system failures (2012), https://c3.nasa.gov/dashlink/resources/624/

- 19. Hammett, R.: Design by extrapolation: an evaluation of fault-tolerant avionics. In: 20th Conference on Digital Avionics Systems. IEEE (2001)

- 20. Thomas, D., et al.: The 'trouble not identified' phenomenon in automotive electronics. Microelectron. Reliab. **42**, 641–651 (2002)

- Gladwell, M.: The engineer's lament: two ways of thinking about automotive safety. The New Yorker, 4 May 2015

- 22. Lococo, K., et al.: Pedal Application Errors, DOT HS 811 597, March 2012

- Wierwille, W., et al.: Identification and evaluation of driver errors: overview and recommendations. Federal Highway Administration; McLean, VA, FHWARD-02-003 (2002)

- Walter, R., et al.: Study of mechanical and driver-related systems of the Audi 5000 capable of producing uncontrolled sudden acceleration incidents, DOT-TSC-NHTSA-88-4, December 1988

- US DoT: Federal Automated Vehicles Policy: Accelerating the next revolution in roadway safety, September 2016

- 26. US DoT: Automated Driving Systems 2.0: a vision for safety, September 2017

- 27. Koopman, P., Wagner, M.: Autonomous vehicle safety: an interdisciplinary challenge. IEEE Intell. Transp. Syst. Mag. **9**, 90–96 (2017)

- 28. Waymo: On the Road to Fully Self-Driving (2018). https://goo.gl/3GwP2T

- 29. GM: 2018 Self-Driving Safety Report. https://goo.gl/2d5PTM

- 30. Johnson, C., et al. v. Ford Motor Company, US Dist. S. WV, Huntington, 3:13-CV-06529, order granting sanctions, 27 December 2017

- 31. Koopman, P.: Letter to editor. IEEE Consum. Electron. Mag. 7(1), 6 (2018)

## A Generic Method for a Bottom-Up ASIL Decomposition

Alessandro Frigerio<sup>1(⊠)</sup>, Bart Vermeulen<sup>2</sup>, and Kees Goossens<sup>1</sup>

<sup>1</sup> Eindhoven University of Technology, Eindhoven, The Netherlands a.frigerio@tue.nl

Abstract. Automotive Safety Integrity Level (ASIL) decomposition is a technique presented in the ISO 26262: Road Vehicles - Functional Safety standard. Its purpose is to satisfy safety-critical requirements by decomposing them into less critical ones. This procedure requires a system-level validation, and the elements of the architecture to which the decomposed requirements are allocated must be analyzed in terms of Common-Cause Faults (CCF). In this work, we present a generic method for a bottom-up ASIL decomposition, which can be used during the development of a new product. The system architecture is described in a three-layer model, from which fault trees are generated, formed by the application, resource, and physical layers and their mappings. A CCF analysis is performed on the fault trees to verify the absence of possible common faults between the redundant elements and to validate the ASIL decomposition.

**Keywords:** ADAS · ASIL decomposition · Automotive architecture Common-Cause fault analysis · Fault trees · Functional safety ISO 26262

#### 1 Introduction

Automotive Safety Integrity Level (ASIL) decomposition is a standardized practice presented in ISO 26262: Road Vehicles - Functional Safety [8]. This technique is used to reduce the criticality of safety requirements. It is generally applied during the allocation of the ASIL values to the safety requirements. The ASIL value of a requirement corresponds to a minimum ASIL that the system, which consists of a given mapping of applications, resources, and locations, must be able to achieve. When sufficiently independent architectural elements are present, the safety requirements can be split into less critical ones and mapped to the independent elements.

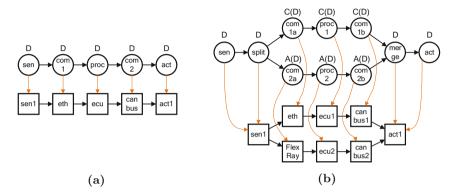

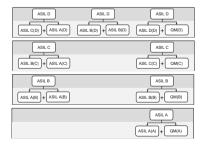

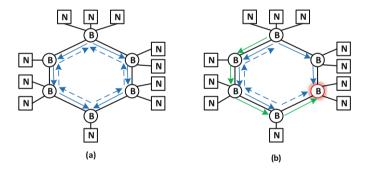

Figure 1 shows an example of a simple application and its mapping to the resources (Fig. 1a) and a corresponding version in which the processing part *proc* is implemented by two different functional nodes, *proc1* and *proc2*, and executed by different processors, *ecu1* and *ecu2* (Fig. 1b). The *split* and *merge* nodes provide the safety mechanisms to obtain the correct application functionality

© Springer Nature Switzerland AG 2018

B. Gallina et al. (Eds.): SAFECOMP 2018, LNCS 11093, pp. 12–26, 2018.

<sup>&</sup>lt;sup>2</sup> NXP Semiconductors, Eindhoven, The Netherlands

with high reliability. They are implemented in this example by the sensor and the actuator respectively. The application layer contains the ASIL related to a safety requirement, while the resource layer has ASIL specifications that must satisfy the application requirements. The implementation resources are then mapped to the physical layer.

**Fig. 1.** Example application mapped on a resource graph (1a) with redundancy (1b). The ASIL requirements for the application are shown above the application nodes. The notation X(Y) refers to a decomposed requirement in which X is the new value and Y the original.

To validate the ASIL decomposition shown in Fig. 1, according to the ISO 26262 standard, the redundant elements must be independent, meaning that they cannot have Common-Cause Faults (CCFs) that could result in a system failure [8]. The independence must be analyzed in terms of software and hardware design and implementation, failures of adjacent elements, environmental factors, failure of common external resources, etc. The ASIL decomposition can be approved only after the analysis of the CCFs.

In this paper we approach the ASIL decomposition in a bottom-up fashion. Compared to a top-down approach, where the ASIL requirements are allocated to an existing architecture, we modify the architecture introducing independent elements on which the redundant requirements can be allocated.

To this end, we present a three-layer model of automotive Electrical and Electronic (E/E) architectures. It is used to analyze the system with automated tools, validate the ASIL requirements from the mapping of the applications, and introduce system redundancy by modifying the structure of the architecture. From the architecture model we generate fault trees for each application that is executed in the vehicle. We use application, resource, and physical space model to analyze the independence of the redundant parts of the system. A model implemented since the early stages of the development phase helps the system architects to maintain proper documentation and to trace the requirements on the implementation. When comparing different solutions, a model-based approach

helps in making the trade-offs between safety, availability of the products, costs, and performance of the implementation.

An inspection of the fault trees allows the detection of a CCF that will cause breaks in the modules's independence assumptions, exposing the situations in which the ASIL decomposition would not be valid.

The novel contribution of this work is:

- A three-layer model that consists of application, resource, physical layers, and their mappings, that explicitly expresses redundancy with specific application and resources elements, to perform the ASIL tailoring process on the implementation level;

- Automated fault trees generation from the model, which are used in the CCF analysis. This validates the independence of redundant elements, as required by the ASIL decomposition process described in the ISO 26262 standard;

- Model transformations to modify the degree of redundancy of the system and lower the ASIL requirements for single elements, while maintaining the ASIL of the system as a whole.

The rest of the paper is organized as follows: Sect. 2 provides an overview of the ISO 26262 safety standard. Section 3 describes the architecture model that is used in this work, and Sect. 4 discusses redundancy in terms of model transformations. Section 5 introduces fault trees and the generation algorithm to synthesize them from the architecture model. Section 6 presents the related work and Sect. 7 concludes the paper by summarizing our results.

#### 2 ISO 26262: Road Vehicles - Functional Safety

The ISO 26262: Road Vehicles - Functional Safety standard, published in 2011, addresses the safety aspects of automotive E/E architectures, considering both random and systematic system failures. It is an automotive-specific adaptation of the IEC 61508 standard [7], which focuses on functional safety of general electronic systems.

The ISO 26262 standard is divided into 10 parts, analyzing safety requirements during all the product life-cycle. It provides guidelines on the management of safety requirements, as well as which safety requirements are necessary for the concept phase of the product, its hardware and software development, the production and the validation of the system. Moreover, it provides guidance on ASIL-oriented requirements and decomposition. A second edition of the standard will be published in 2018 focusing on motorbikes and providing guidance on the application of the standard and ASIL definition to hardware components.

#### 2.1 Automotive Safety and Integrity Level

Safety can be measured with the Automotive Safety Integrity Level (ASIL) concept, which is similar to the Safety Integrity Level (SIL) of IEC 61508.

The ASIL system uses a risk-based approach that takes into account the Severity, Exposure, and Controllability of a potential harm. There are five possible levels: from the most critical ASIL D to the least critical ASIL A and a QM (quality management) level that refers to non-safety-critical items. Figure 2 shows how the ASIL values are calculated based on the three risk parameters. The highest level D corresponds to all the risk parameters being at their maximum: S3 corresponds to life-threatening or fatal injuries, E4 to a high probability of exposure and C3 to a difficult to control or uncontrollable risk.

#### 2.2 Requirement Decomposition

The ISO 26262 standard "provide(s) rules and guidance for decomposing the safety requirements into redundant safety requirements to allow ASIL tailoring at the next level of detail" [8]. Lower ASIL requirements for the implementation resources on which the application nodes are mapped on could be necessary for three main reasons during the product development:

- 1. Elements with the maximum criticality level are not available. Creating ASIL D compliant devices is a difficult task, and often the highest safety level can be achieved only by exploiting the knowledge of the application that the device will support. This is not possible for general purpose elements or resources that are shared by many applications.

- 2. High-ASIL software is difficult and expensive to develop and test. The same holds for the software development tools used;

- 3. The production process used to create a safety-critical component is expensive. Decomposing the system into less-critical elements may be the most cost-efficient solution.

|            |    | C1 | C2 | C3 |

|------------|----|----|----|----|

| S1         | E1 | QM | QM | QM |

|            | E2 | QM | QM | QM |

|            | E3 | QM | QM | Α  |

|            | E4 | QM | Α  | В  |

| <b>S</b> 2 | E1 | QM | QM | QM |

|            | E2 | QM | QM | Α  |

|            | E3 | QM | Α  | В  |

|            | E4 | Α  | В  | С  |

| S3         | E1 | QM | QM | Α  |

|            | E2 | QM | Α  | В  |

|            | E3 | Α  | В  | С  |

|            | E4 | В  | С  | D  |

Fig. 3. Possible decomposition schemes

Figure 3 shows the acceptable ASIL decomposition schemes defined by the standard, which follow the rule of Eq. 1. To the ASIL values, QM to D, we assign a number from 0 to 4, and the following relation must be satisfied:

$$ASIL_{orig} \le \sum ASIL_{decomp}$$

(1)

The standard uses the notation  $ASIL_{decomp}(ASIL_{orig})$  to mark which elements have been decomposed and trace the original requirement. Additional procedures must be carried out when decomposing ASIL D requirements, for example, the test and the integration of each decomposed element shall be implemented in compliance with ASIL C. In particular, when a requirement is decomposed into redundant elements, it is necessary to establish independence between them for the original safety requirement to be correctly satisfied. For example, the redundant elements should not depend on a common resource, such as a shared battery, that could cause them to fail simultaneously, i.e. a CCF.

#### 3 Three-Layer Architecture Model

When describing Advanced Driving Assistance Sytems (ADAS) or Autonomous Driving (AD) related applications, the *sense-think-act* paradigm is generally used. It is a common concept used in Robotics, which separates an application into three main domains:

- (a) Sense: an application will always start by collecting information about the surrounding environment or the vehicle status from one or more sensors.

- (b) Think: the collected data is then processed. Different design approaches can be used to determine if it will happen, for example, in a centralized architecture, where a single module will analyze the data, or in a distributed fashion, in which multiple modules will analyze the different sensor data.

- (c) Act: the final part of an application involves the actuators, which modify the status of the vehicle.

In this work we assume that all applications follow this paradigm, and in the application graph a path from each actuator to at least one sensor always exists.

#### 3.1 Model Description

Modeling the automotive E/E architecture is necessary to analyze the system. To validate ASIL decomposition it is necessary to include both the descriptions of the applications, the implementation resources used, and the physical space of the vehicle.

A three-layer approach is used: the architecture is described in terms of application, resource, and physical layers. The application layer contains disjoint application graphs, while the resource and physical layers contain one graph.

The application layer can contain multiple graphs, each describing a different application. Each application is related to a specific safety requirement, for example availability of the system for a certain task, derived from the safety goals, analyzed during the Hazard Assessment and Risk Analysis (HARA) phase. The application layer describes the functional architecture of the vehicle by defining the relationships between the software nodes via a directed cyclic graph

G = (N, E) for each application, where N is the set of software nodes and E is the set of edges that connect the nodes. Each node has an ASIL requirement, which is originally inherited from the initial safety requirement, but can be lowered by the ASIL decomposition procedure. The edges indicate information flow between the nodes, but do not have any capacity or timing properties, which are expressed by explicit communication nodes. Each node has a specific type:

- (a) Functional: the computational aspects of an application;

- (b) Communication: the communication aspects of an application;

- (c) Sensor: the data source of an application;

- (d) Actuator: the data sink of an application;

- (e) Splitter: node that replicates the input data to its output ports;

- (f) Merger: node that compares the redundant inputs and ensures only correct outputs are forwarded.

Note that the *splitter* and *merger* nodes are necessary to describe the redundant elements of the system, and will be discussed in the following sections.

The resource layer describes the implementation architecture of the vehicle, comprising of hardware and software elements. The resources are expressed with a directed cyclic graph H=(R,L), in which R is the set of resources and L is the set of links that connect them. Each resource can provide multiple types e.g.:

- (a) Functional: a resource on which the application functional nodes can be mapped on, like a processor or a controller;

- (b) Communication: resources that represent the different types of automotive networks (LIN, CAN, FlexRay, MOST, Ethernet) or direct connections;

- (c) Sensor: a resource that collects data, like a camera or a wireless receiver;

- (d) Actuator: a resource that interacts with the physical environment by executing the desired operations, for example the braking actuator;

- (e) Splitter: a resource capable of forwarding the data received on an input ports to multiple output ports;

- (f) Merger: a resource capable of deciding which input data is correct and forwards it to its output ports.

We model generic resource-resource dependencies in the *resource* layer. To show one example, we use the power supply, but any other shared resource can be modeled in the same way and included in the CCF analysis.

- (g) Power Source: a resource that provides the power supply for other resources, for example a battery;

- (h) Power Line: a resource that distributes the power supply to other resources.

Each resource has a set of types, and the application nodes with that type can be mapped on that resource. Hybrid resources can be described properly by the model, for example a gateway would be both a *Functional* and a *Communication* resource, and might have *Splitter* or *Merger* capabilities too. Each resource has

an ASIL value, representing the maximum ASIL value that it can satisfy for a specific safety requirement, usually referred to as a ASIL-X ready resource.

The physical layer is described similarly by a cyclic graph F = (P, C), where P is the set of physical locations and C the set of connections. The description of the physical space is inspired by [10], in which the authors focus on the study of the wiring costs in an E/E architecture and they model the system to analyze wire routing and splice allocations. In our proposed approach, the physical locations can describe: the areas of the vehicle in which the ECUs and hardware components can be placed, which have a limited available space, and the paths in which the communication wires can be positioned and their length.

The interconnections between the different graphs show the mapping of the applications to the hardware resources, and of the hardware resources to the physical locations of the vehicle. Figure 1 is an example of the first two graphs and the relationships between them; it does not show the physical graph to which the resources would be mapped.

### 4 Model Transformations

Reducing the criticality of each module as much as possible apparently lowers the cost of the product while maintaining high safety. In practice more complications are introduced in the design: safety mechanisms must ensure that the proper functionality is preserved, new communication interfaces are added to the architecture, and a system-level analysis must be performed to ensure that the redundant elements are sufficiently independent.

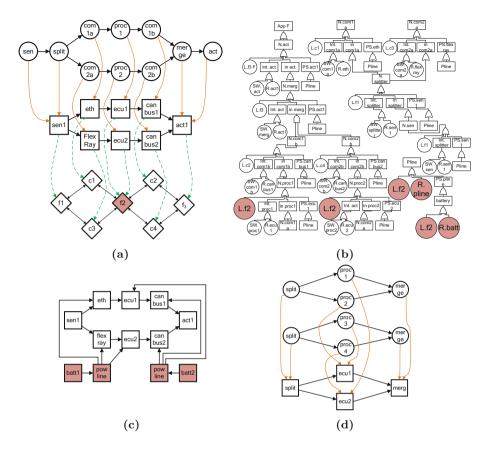

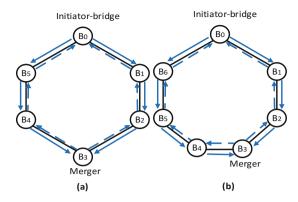

As a base example, Fig. 4 shows the new elements that are introduced in the architecture after the duplication of a single node n, which has only one input and one output for simplicity's sake:

- $-n_s$  has a *splitter* type, it collects the inputs and redirects them to the redundant paths;

- $-c_{1a}$  and  $c_{1b}$  are the new communication nodes that describe the channels between the splitter and the functional nodes;

- $n_1$  and  $n_2$  are the redundant functional nodes;

- $-c_{2a}$  and  $c_{2b}$  are the new communication nodes that describe the channels between the two functional nodes and the merger;

- $-n_m$  has a merger type, it checks the input correctness of the data from the redundant paths and forwards only correct data.

Both the *splitter* and the *merger* nodes are single points of failure for the applications, which means that they will be safety-critical elements that must have at least the same ASIL requirements as the original node n. They perform generic operations on the inputs and outputs of the redundant blocks, for example a merger could be a comparator of a classic k-out-of-n model [1] or part of an health monitoring system which decides which output to use. The other elements of the two branches instead follow the rule presented in Eq. 1.

Fig. 4. Node duplication

A transformation of the resources can be applied in a similar way. High reliable *splitter* and a *merger* resources will manage the redundant independent resources. The replicated application nodes do not always have a one-to-one relationship with the transformed resources. In a bottom-up approach, the designer will make this kind of transformations to the applications and resources layers to create redundant architectures.

Even from a simple transformation, it is clear that replication will introduce a lot of complexity in the system. From a single safety-critical node we introduce at least two nodes, the *splitter* and the *merger*, with the same ASIL value as the original one. In this case, since their functionality is very specific, it is possible to obtain these elements with contained costs compared to a more generic safety-critical one. Moreover, new connections are created and additional latency is introduced by the extra communication and the splitter and merger functionality. New constraints for the design are introduced to meet the independence requirements: redundant application nodes must be mapped on independent resources, and independent resources must be positioned in independent locations. In this work we consider only the safety aspect of these modifications.

## 5 Common-Cause Fault Analysis for ASIL Validation

The information provided by the *application*, resource, and physical layers allows us to compute the ASIL value obtained with the implementation of each application. If the obtained value is lower than the requirements, it means that the resources cannot satisfy them, and either a different mapping or a different implementation must be used.

The computed ASIL value requires a Common-Cause Fault analysis performed on the three layers of the model to be valid. This analysis can either be manual or automated.

In this work, we generate a fault tree for each application, which is used for an automatic CCF analysis. This analysis recognizes redundancy in the model by searching for *splitter-merger* combinations, and uses the nodes and resources dependencies to determine any possible CCF.

This analysis can also be used to validate a new model after a transformation.

### 5.1 Fault Trees in Automotive Systems

Fault Tree Analysis (FTA) is a common top-down Safety Analysis, in which an undesired top-level event is identified and then its causes are considered.

In this work we consider as the top-level event the failure of an application for a specific safety goal, for example the system availability, that manifests itself through the failure of at least one of the actuators. Each node, starting from the actuators, can fail because of different reasons:

- Internal failure of the hardware resource on which the application node is mapped or of the software component that implements the functionality;

- Failure of the location on which the used resource is mapped;

- Dependent resource failure. The resource on which the application node is mapped may depend on other resources, such as the power supply;

- Input Failure. Failure of node A that provides data to node B leads to the failure of the node B.

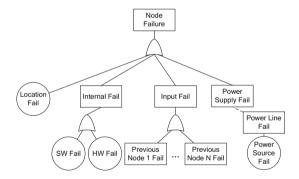

Figure 5 shows the fault tree generated for each node. The same structure is generated for each input application node, until the final sensors are reached, according to the assumption of *sense-think-act* applications. This type of fault tree is based on [6], in which the authors use Dynamic Fault Trees to describe ADAS related applications and perform a FTA.

Fig. 5. Subtree for each application node

The internal failure base event could be further developed as in [6], where the hardware and the safety mechanisms implemented in the resources are considered.

### 5.2 Fault Tree Generation

The fault tree generation algorithm is based on [11]. We assume that the failure of a safety requirement corresponds to the failure of at least one of the related

application's actuators. All the actuators are assumed to have the same importance for the success of each application. Assuming a *sense-think-act* paradigm, we can always expect to find a path from an actuator to a sensor.

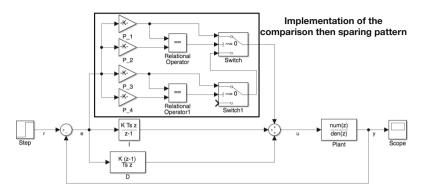

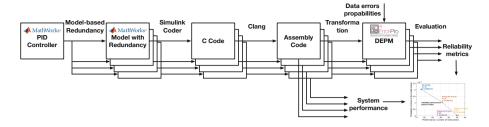

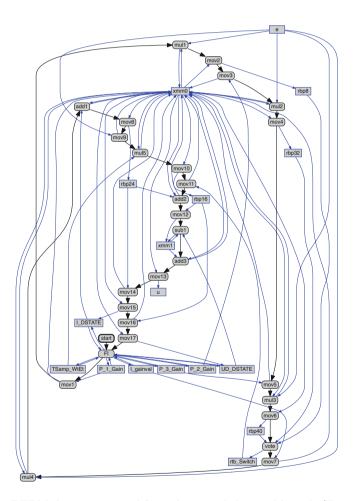

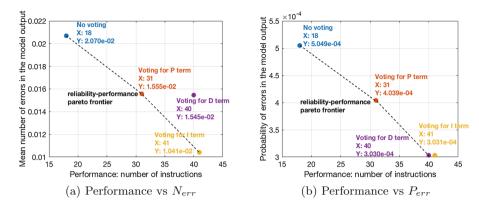

Algorithm 1 accepts an application graph G and the top-level event  $e_T$  as inputs, and then calls the recursive procedure DevelopSubTree for each of the application actuators. The function MappedResource returns the resource on which an application node is mapped, while the function MappedLocation returns the physical location on which the resource is positioned.