# Kofi A. A. Makinwa · Andrea Baschirotto Pieter Harpe *Editors*

# Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers

Advances in Analog Circuit Design 2018

Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers Kofi A. A. Makinwa • Andrea Baschirotto Pieter Harpe Editors

# Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers

Advances in Analog Circuit Design 2018

*Editors* Kofi A. A. Makinwa Delft University of Technology Delft, Zuid-Holland The Netherlands

Pieter Harpe Eindhoven University of Technology Eindhoven, Noord-Brabant The Netherlands Andrea Baschirotto University of Milano-Bicocca Milan, Italy

#### ISBN 978-3-319-97869-7 ISBN 978-3-319-97870-3 (eBook) https://doi.org/10.1007/978-3-319-97870-3

Library of Congress Control Number: 2018959116

#### © Springer Nature Switzerland AG 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### Preface

This book is part of the Analog Circuit Design series and contains contributions by all the speakers at the 27th workshop on Advances in Analog Circuit Design (AACD). The aim of the workshop was to bring together a group of expert designers to discuss new developments and future options.

The 27th workshop was held in Edinburgh, Scotland, from May 14 to 16, 2018. The local organizers were Jed Hurwitz (ADI), Paul Lesso (Cirrus Logic), Jim Brown (Dialog Semiconductor), Emma Dixon (Technology Scotland), and Stephen Taylor (Technology Scotland). Analog Devices, Cirrus Logic, and Dialog Semiconductor were the platinum sponsors of the event.

Each AACD workshop is followed by the publication of a book by Springer, which then becomes part of their successful series on Analog Circuit Design. A full list of the previous books and topics covered in this series can be found on subsequent pages. Each book can be seen as a reference work for students and designers interested in advanced analog and mixed-signal circuit design.

This book is the 27th in this series. It consists of three parts, each with six chapters, that cover the following topics that are currently considered of high importance by the analog and mixed-signal circuit design community:

- · Analog Techniques for Power Constrained Applications

- Sensors for Mobile Devices

- · Energy Efficient Amplifiers and Drivers

We are confident that this book, like its predecessors, will prove to be a valuable contribution to our analog and mixed-signal circuit design community.

Delft, The Netherlands Milan, Italy Eindhoven, The Netherlands Kofi A. A. Makinwa Andrea Baschirotto Pieter Harpe

# **Topics Previously Covered in the Springer Series on Analog Circuit Design**

| 2017 | Eindhoven (The<br>Netherlands) | Hybrid ADCs<br>Smart Sensors for the IoT                    |

|------|--------------------------------|-------------------------------------------------------------|

|      | Netherlands)                   | Sub-1V & Advanced-node Analog Circuit Design                |

| 2016 | Villach (Austria)              | Continuous-time $\Sigma \Delta$ Modulators for Transceivers |

|      |                                | Automotive Electronics                                      |

|      |                                | Power Management                                            |

| 2015 | Neuchâtel                      | Efficient Sensor Interfaces                                 |

|      | (Switzerland)                  | Advanced Amplifiers                                         |

|      |                                | Low Power RF Systems                                        |

| 2014 | Lisbon (Portugal)              | High-Performance AD and DA Converters                       |

|      |                                | IC Design in Scaled Technologies                            |

|      |                                | Time-Domain Signal Processing                               |

| 2013 | Grenoble (France)              | Frequency References                                        |

|      |                                | Power Management for SoC                                    |

|      |                                | Smart Wireless Interfaces                                   |

| 2012 | Valkenburg (The                | Nyquist A/D Converters                                      |

|      | Netherlands)                   | Capacitive Sensor Interfaces                                |

|      |                                | Beyond Analog Circuit Design                                |

| 2011 | Leuven (Belgium)               | Low-Voltage Low-Power Data Converters                       |

|      |                                | Short-Range Wireless Front-Ends                             |

|      |                                | Power Management and DC-DC                                  |

| 2010 | Graz (Austria)                 | Robust Design                                               |

|      |                                | Sigma Delta Converters                                      |

|      |                                | RFID                                                        |

| 2009 | Lund (Sweden)                  | Smart Data Converters                                       |

|      |                                | Filters on Chip                                             |

|      |                                | Multimode Transmitters                                      |

|      |                                |                                                             |

| 2008 | Pavia (Italy)                   | High-Speed Clock and Data Recovery<br>High-Performance Amplifiers<br>Power Management                                                                         |

|------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2007 | Oostende (Belgium)              | Sensors, Actuators and Power Drivers for the<br>Automotive and Industrial Environment<br>Integrated PAs from Wireline to RF<br>Very High Frequency Front Ends |

| 2006 | Maastricht (The<br>Netherlands) | High-Speed AD Converters<br>Automotive Electronics: EMC issues<br>Ultra Low Power Wireless                                                                    |

| 2005 | Limerick (Ireland)              | RF Circuits: Wide Band, Front-Ends, DACs<br>Design Methodology and Verification of RF and<br>Mixed-Signal Systems<br>Low Power and Low Voltage                |

| 2004 | Montreux (Swiss)                | Sensor and Actuator Interface Electronics<br>Integrated High-Voltage Electronics and Power<br>Management<br>Low-Power and High-Resolution ADCs                |

| 2003 | Graz (Austria)                  | Fractional-N Synthesizers<br>Design for Robustness<br>Line and Bus Drivers                                                                                    |

| 2002 | Spa (Belgium)                   | Structured Mixed-Mode Design<br>Multi-bit Sigma-Delta Converters<br>Short-Range RF Circuits                                                                   |

| 2001 | Noordwijk (The<br>Netherlands)  | Scalable Analog Circuits<br>High-Speed D/A Converters<br>RF Power Amplifiers                                                                                  |

| 2000 | Munich (Germany)                | High-Speed A/D Converters<br>Mixed-Signal Design<br>PLLs and Synthesizers                                                                                     |

| 1999 | Nice (France)                   | XDSL and Other Communication Systems<br>RF-MOST Models and Behavioural Modelling<br>Integrated Filters and Oscillators                                        |

| 1998 | Copenhagen (Denmark)            | 1-Volt Electronics<br>Mixed-Mode Systems<br>LNAs and RF Power Amps for Telecom                                                                                |

| 1997 | Como (Italy)                    | RF A/D Converters<br>Sensor and Actuator Interfaces                                                                                                           |

| 1996 | Lausanne (Swiss)                | Low-Noise Oscillators, PLLs and Synthesizers<br>RF CMOS Circuit Design<br>Bandpass Sigma Delta and Other Data Converters<br>Translinear Circuits              |

| 1995 | Villach (Austria)              | Low-Noise/Power/Voltage              |

|------|--------------------------------|--------------------------------------|

|      |                                | Mixed-Mode with CAD Tools            |

|      |                                | Voltage, Current and Time References |

| 1994 | Eindhoven (The Netherlands)    | Low-Power Low-Voltage                |

|      |                                | Integrated Filters                   |

|      |                                | Smart Power                          |

| 1993 | Leuven (Belgium)               | Mixed-Mode A/D Design                |

|      | -                              | Sensor Interfaces                    |

|      |                                | Communication Circuits               |

| 1992 | Scheveningen (The Netherlands) | OpAmps                               |

|      | -                              | ADCs                                 |

|      |                                | Analog CAD                           |

# Contents

| Part I Analog Techniques for Power Constrained Applications                                                                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction to Energy Harvesting Transducers and Their Power<br>Conditioning Circuits<br>Baoxing Chen                                                                                                                          | 3   |

| From Bluetooth Low-Energy to Bluetooth No-Energy: System<br>and Circuit Aspects of Energy Harvesting for IoT Applications<br>Wim Kruiskamp                                                                                      | 13  |

| <b>Design of Powerful DCDC Converters with Nanopower Consumption</b><br>Vadim Ivanov                                                                                                                                            | 31  |

| Nanopower SAR ADCs with Reference Voltage Generation<br>Maoqiang Liu, Kevin Pelzers, Rainier van Dommele,<br>Arthur van Roermund, and Pieter Harpe                                                                              | 59  |

| <b>Ultra-Low-Power Clock Generation for IoT Radios</b><br>Ming Ding, Pieter Harpe, Zhihao Zhou, Yao-Hong Liu, Christian<br>Bachmann, Kathleen Philips, Fabio Sebastiano, and Arthur van Roermund                                | 83  |

| Low-Power Resistive Bridge Readout Circuit Integrated in Two<br>Millimeter-Scale Pressure-Sensing Systems<br>Sechang Oh, Yao Shi, Gyouho Kim, Yejoong Kim, Taewook Kang,<br>Seokhyeon Jeong, Dennis Sylvester, and David Blaauw | 111 |

| Part II Sensors for Mobile Devices                                                                                                                                                                                              |     |

| Advanced Capacitive Sensing for Mobile Devices                                                                                                                                                                                  | 131 |

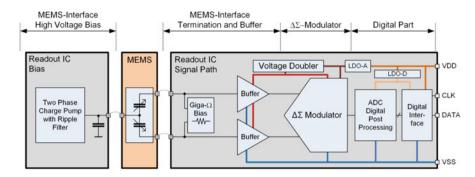

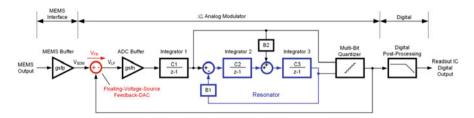

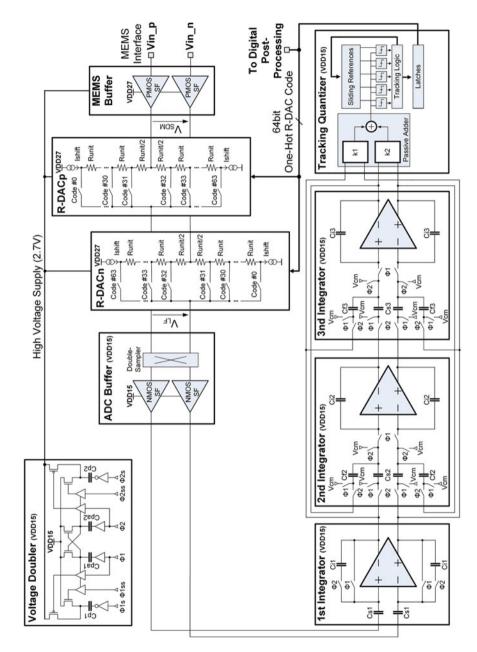

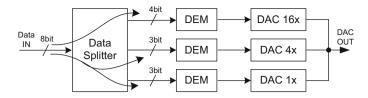

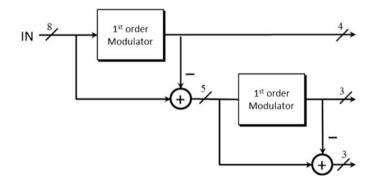

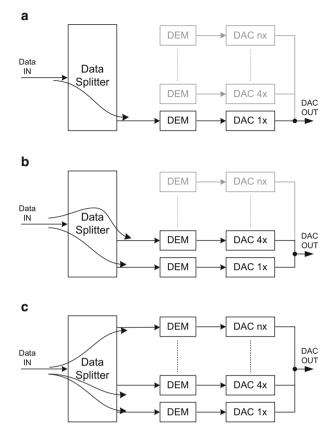

| <b>MEMS Microphones: Concept and Design for Mobile Applications</b><br>Luca Sant, Richard Gaggl, Elmar Bach, Cesare Buffa, Niccolo' De Milleri,<br>Dietmar Sträussnigg, and Andreas Wiesbauer                                   | 155 |

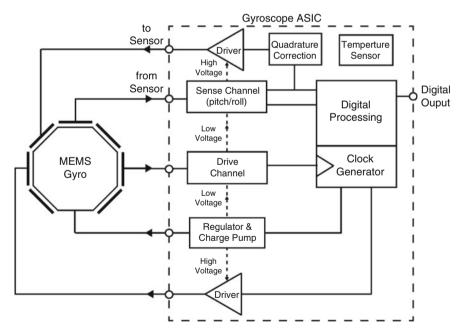

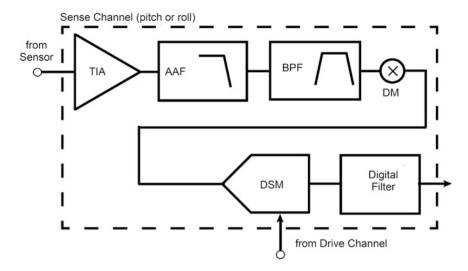

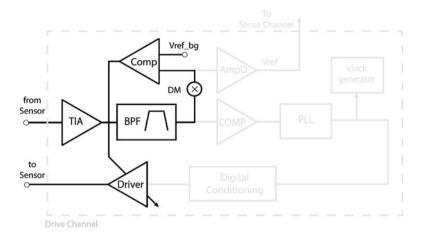

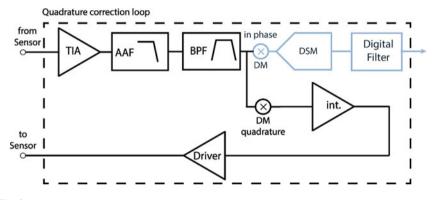

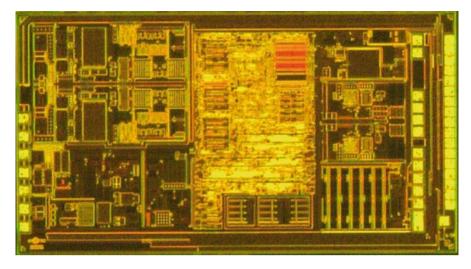

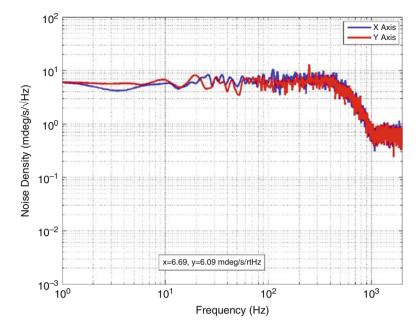

| High-Performance Dual-Axis Gyroscope ASIC Design<br>Zhichao Tan, Khiem Nguyen, and Bill Clark                                                                                                       | 175 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

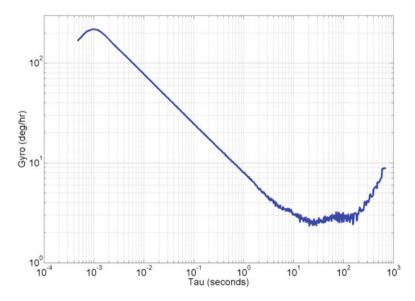

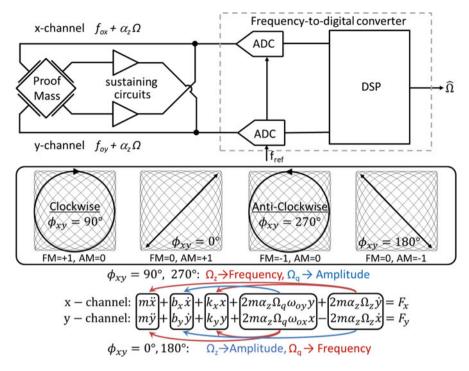

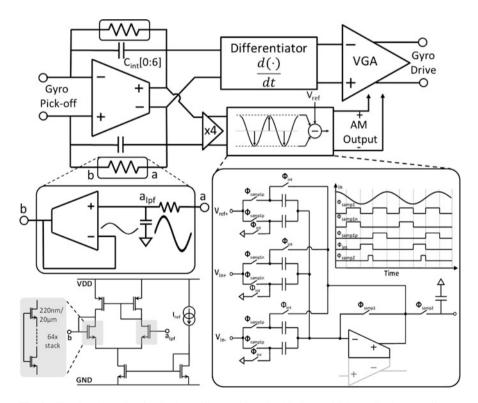

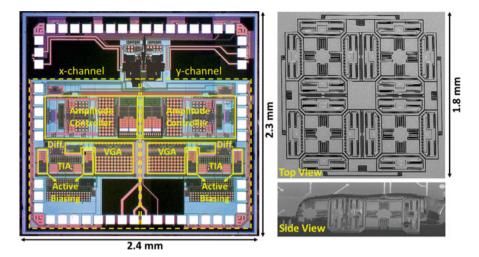

| Direct Frequency-To-Digital Gyroscopes with Low Drift and High<br>Accuracy<br>Burak Eminoglu and Bernhard E. Boser                                                                                  | 191 |

| <b>CMOS-Compatible Carbon Dioxide Sensors</b><br>Zeyu Cai, Robert van Veldhoven, Hilco Suy, Ger de Graaf,<br>Kofi A. A. Makinwa, and Michiel Pertijs                                                | 199 |

| <b>Time of Flight Imaging and Sensing for Mobile Applications</b><br>Neale A. W. Dutton, Tarek Al Abbas, Francescopaulo Mattioli<br>Della Rocca, Neil Finlayson, Bruce Rae, and Robert K. Henderson | 221 |

| Part III Energy Efficient Amplifiers and Drivers                                                                                                                                                    |     |

| High-Efficiency Residue Amplifiers<br>Klaas Bult, Md. Shakil Akter, and Rohan Sehgal                                                                                                                | 253 |

| Energy-Efficient Inverter-Based Amplifiers<br>Youngcheol Chae                                                                                                                                       | 297 |

| Balancing Efficiency, EMI, and Application Cost in Class-D Audio<br>Amplifiers<br>Marco Berkhout                                                                                                    | 315 |

| A Deep Sub-micron Class D Amplifier<br>Mark McCloy-Stevens, Toru Ido, Hamed Sadati, Yu Tamura,<br>and Paul Lesso                                                                                    | 339 |

| Low Power Microphone Front-Ends<br>Lorenzo Crespi, Claudio De Berti, Brian Friend, Piero Malcovati,<br>and Andrea Baschirotto                                                                       | 353 |

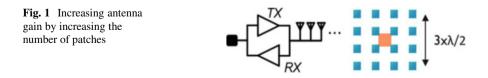

| <b>Challenges of Digitally Modulated Transmitter Implementation</b><br><b>at Millimeter Waves</b>                                                                                                   | 381 |

# Part I Analog Techniques for Power Constrained Applications

The first part of this book is dedicated to recent developments in the field of extremely low power circuits and systems. The first papers discuss energy harvesting and power management circuits, followed by chapters on analog and mixed-signal circuits and systems.

The first chapter from Baoxing Chen (Analog Devices International) describes various kinds of energy sources that can be used for energy harvesting and gives an overview of possible energy harvesting transducers, combined with their required power conditioning circuits.

In the second chapter, Wim Kruiskamp (Dialog Semiconductor) presents an example of an energy harvesting system that allows these IoT devices to be powered by alternative energy sources like light, heat, or RF energy. Some circuits and algorithms that are specifically important for energy harvesting are discussed in more detail.

The third chapter by Vadim Ivanov (Texas Instruments) describes how to design analog building blocks and DC/DC converters in a good way with a nanowatt level of power consumption. Starting with a structured design approach, the author further continues with practical design implementations and examples.

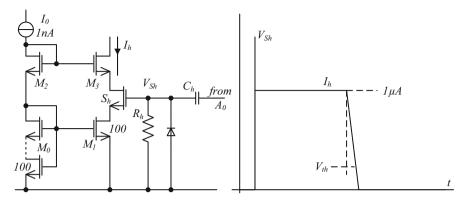

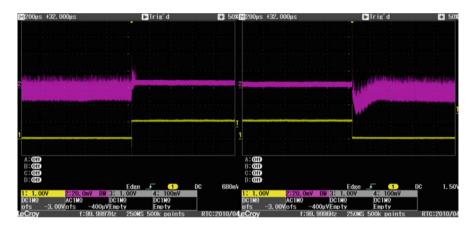

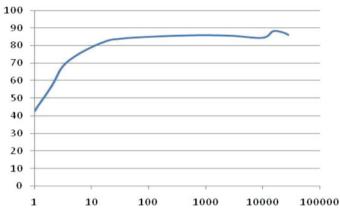

Maoqiang Liu (Eindhoven University of Technology) presents various lowpower Analog-to-Digital Converters in chapter four. In particular, the combination of low-power references and ADCs is investigated. Various implemented examples are discussed where the reference is co-designed, relaxed, or compensated by means of the ADC.

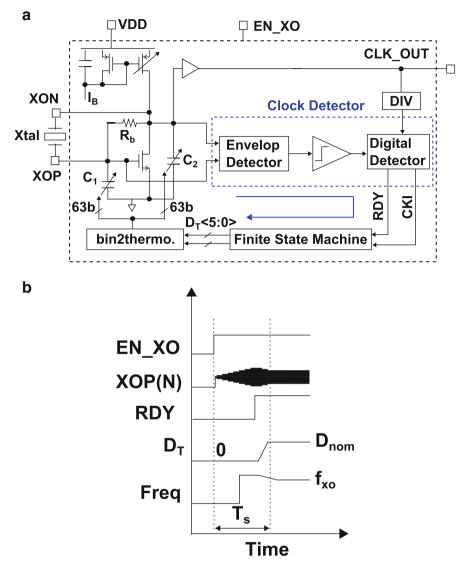

In chapter five, Ming Ding (Holst Centre/imec) discusses the challenges of low-power clock generation for duty-cycled Internet-of-Things radios. Two design examples are discussed in detail: a nanopower sleep timer and a fast start-up crystal oscillator.

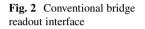

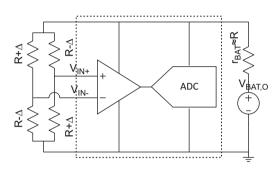

The sixth chapter from David Blaauw (University of Michigan) presents circuits for extremely low power sensor systems. A duty-cycled bridge-to-digital converter for small battery operated pressure sensing systems is presented. Besides presenting the circuit techniques and implementations, the circuit is also demonstrated inside two complete microsystems.

## Introduction to Energy Harvesting Transducers and Their Power Conditioning Circuits

**Baoxing Chen**

#### 1 Introduction

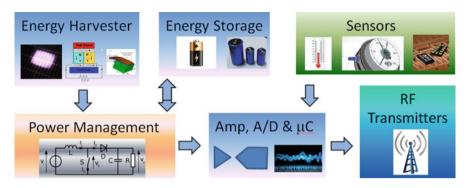

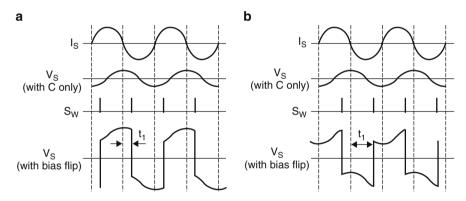

Wireless sensor nodes are usually powered by batteries; however, maintenance for them can become a significant hassle. Batteries have limited life span and they need to be replaced. In some applications, the wireless sensor nodes can be installed in a remote and tough-to-reach area. Maintenance-free wireless sensor nodes are essential to drive the continuous adoption of wireless sensor network for wide range of IoT applications, from machine health monitoring, building automation, to smart wearables. Energy harvesting, i.e., harvesting energy from the ambient environment, is an ideal solution to enable maintenance-free wireless sensor network. An energy harvesting system for wireless sensors consists of the following as shown in Fig. 1.: (1) one or multiple energy harvesters; (2) some kind of energy storage device; (3) power management device to ensure efficient energy extraction from the harvesters, to produce the output voltages suitable for use by other devices, and to manage the storage device; (4) various sensors to sense a variety of environmental data such as temperature, pressure, or gas; (5) the signal conditioning circuits and microcontrollers to interface with the sensors,; and (6) the wireless transceivers. In this chapter, we will mainly focus on 1, 2, and 3.

B. Chen (⊠)

Analog Devices, Inc., Wilmington, MA, USA e-mail: Baoxing.Chen@analog.com

<sup>©</sup> Springer Nature Switzerland AG 2019

K. A. A. Makinwa et al. (eds.), *Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers,* https://doi.org/10.1007/978-3-319-97870-3\_1

Fig. 1 Typical energy harvesting system

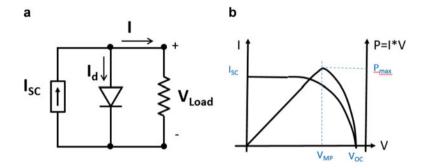

Fig. 2 (a) Circuit model and (b) I-V curve for photovoltaic cell

#### 2 Photovoltaic Harvesting

PV panels can usually generate around 100  $W/m^2$  or 10 mW/cm<sup>2</sup> outdoors with 10% solar cell efficiency, but this number can drop 2–3 orders of magnitude indoors dependent on lighting condition. For area-constraint application, the solar cell efficiency is key. Low solar cell efficiency is due to low quantum efficiency where only the photons with energy bigger than the bandgap can be absorbed and excessive photon energy above the bandgap is also lost to heat. The solar cell efficiency can be improved with multi-junction device, where junctions with different bandgaps are stacked so that photons with different energy are absorbed more efficiently by different junctions.

Figure 2a shows the circuit model for a PV cell where the current through the load is the short circuit current minus the diode current. Figure 2b shows typical I-V curve where  $V_{OC}$  is the open circuit voltage and  $I_{SC}$  is the short circuit current. The power it generates has a peak at certainly voltage  $V_{MP}$ , fraction of the  $V_{OC}$ , and this is the maximum power point with  $P_{max}$ . For the PV power conditioning circuit, it is important that solar cell operates at this point. With low power application, we need to balance the power gain from the additional efficiency gain from accurate

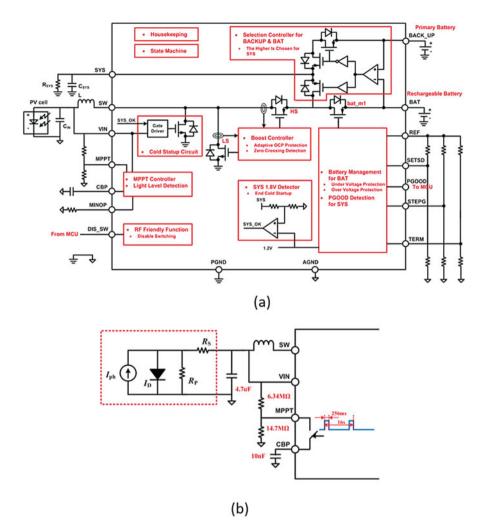

Fig. 3 (a) Boost converter architecture (ADP5090) and (b) VOC sense implementation

maximum power point tracking and the power loss for implementing the MPPT algorithms. One common approach is to approximate the point using some fraction of the open circuit voltage (FOV). While the  $V_{OC}$  changes with different lighting conditions, FOV stays relatively constant. This can be easily implemented with a comparator and voltage divider. The load can be either disrupted to get  $V_{OC}$  or a dummy reference cell is used to get  $V_{OC}$ .

An example implementation for how  $V_{OC}$  is sampled is shown in Fig. 3 [1]. Figure 3a is the overall circuit architecture for an ultralow power boost converter, and Fig. 3b shows the  $V_{OC}$  sampling method. In every 16 s, the converter is interrupted for 256 mS to allow FOV to be sampled and stored in  $C_{BP}$  through a

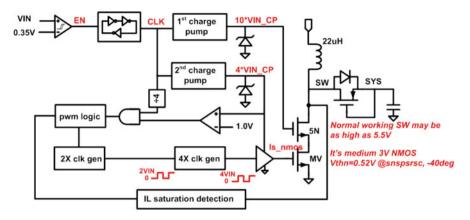

Fig. 4 Cold startup circuit implementation

| Supplier                                 | ADI                         | TI                          | Linear Tech                 | Maxim         |

|------------------------------------------|-----------------------------|-----------------------------|-----------------------------|---------------|

| features                                 | ADP5090                     | bq25504                     | LTC3105                     | Max17710      |

| Start-up input voltage                   | 380 mV                      | 330 mV                      | ZSOmV                       | 750 mV        |

| Efficiency<br>(Vin@0.5 V;<br>Vout@3.0 V) | 58% (10 uA)<br>79% (100 uA) | 35% (10 uA)<br>75% (100 uA) | 30% (10 uA)<br>50% (100 uA) | Not supported |

| lq                                       | ≈350 nA                     | 570 nA                      | 10 uA                       | 625 nA        |

Table 1 Comparison for startup voltage and low load efficiency

voltage divider of  $V_{OC}$ . Since a single cell output voltage can be low, an important piece of the PV harvesting is the cold startup circuit. An example implementation is shown in Fig. 4 [2].

The first charge pump 10\*VIN\_CP is used to control a cascade device to protect the 3 V medium VT startup switch MV from the switching node voltages, and a comparator is used to make sure the second charge pump output voltage 4\*VIN\_CP is good. Inductor current saturation is detected to minimize startup current as long startup period from a regular oscillator can easily make inductor current saturated. Table 1 is the summary of startup voltage and efficiencies for a few ultralow power boost converters on the market. As much as 58% efficiency can be achieved with only 10uA load, and the quiescent current is only about 350 nA.

#### **3** Thermoelectric Harvesting

Thermoelectric harvesters rely on a temperature gradient to generate power based on one of the thermoelectric effects, the Seeback effect, which is the direct conversion of temperature differences to electric voltages. The efficiency for a thermoelectric generator depends not only on the temperatures at the hot side and cold side but also on the figure of merit ZT for the thermoelectric material used, where  $ZT = \frac{S^2 \sigma T}{\kappa}$ . S is the Seeback coefficient or the thermopower,  $\sigma$  is the electrical conductivity, and  $\kappa$  is the thermal conductivity. The best bulk thermoelectric material at room temperature is Bi<sub>2</sub>Te<sub>3</sub>, which has a ZT ~1. Besides materials, there has been progress in enhancing ZT using low-dimensional structures such as quantum wells or nano-wires where larger S and/or lower thermal conductivity can be achieved.

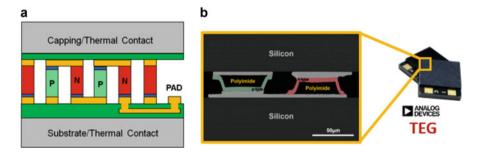

Thermoelectric harvesters are scalable and are suitable for integration. The efficiency of a thermoelectric element does not depend on the size, and the heat that can conduct through a certain cross-section area for a given thermoelectric element increases with the reduction in its length. However, the reduction in length will lead to reduction in thermal resistance which can pose challenges in applications with high external thermal resistances where the available temperature gradient is divided between external and internal thermal resistances and only the gradient across the thermoelectric element contributes to the power generation. A thermoelectric harvester usually consists of multiple thermoelectric legs with positive thermoelectric power (p-type) and negative thermoelectric power (n-type) connected in series electrically, but in parallel thermally, to build enough voltage that can be used. The voltage across a single element can be quite small, and in many cases, a booster converter is used to further raise the voltage and ensures impedance matching to extract the maximum power from the harvester. To reduce the thermal shunt by the ambient air surrounding the P and N legs, wafer capping can be used to seal the thermoelectric legs in a vacuum as shown in Fig. 5a [3]. To improve device thermal resistance without the need for thick films, the thermoelectric films can be deposited along a thick polyimide island as shown in Fig. 5b.

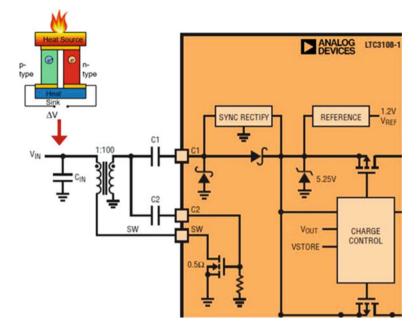

A thermoelectric harvester delivers the maximum power to the load when the load resistance matches the internal device resistance. Similar circuit can be adapted from FOV for the PV cell harvesting but setting FOV equal to 0.5. Besides load matching for maximum power, another common need is the startup circuit due to the low voltage output from the thermoelectric harvester with limited DT. Depleted NMOS together with a step-up transformer can form self-oscillation to build up

Fig. 5 (a) Structure for a vertical thermoelectric harvester with vacuum capping (b) pyramidshaped thermoelectric harvester

Fig. 6 Low voltage startup using step-up transformers

startup voltage as shown in Fig. 6 [4]. With 1:100 step-up transformers, the converter can startup from input as low as 20 mV. In some applications, the harvester also needs to harvest energy from both positive input voltages and negative input voltages. For example, a ground spike can be used to harvest energy from the temperature differences between the surface and the soil under, and the polarity can change depending on the day or night. A full bridge circuit with parallel diodes and switches can be used, and the switches are turned on or off by looking at the voltage polarities at the input. For bipolar startup, two startup transformers can be used [5].

#### 4 Vibrational Harvesting

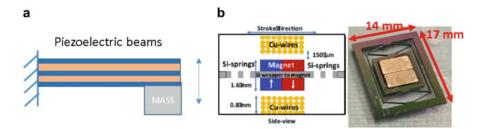

Vibrational harvesters usually rely on certain mechanical structures to convert external vibration to the kinetic energy, and the mechanical structures are coupled to energy transducers, such as piezoelectric transducers or electromagnetic transducers, to convert kinetic energy to electricity. Figure 7a shows a typical cantilever-based piezoelectric harvester. The beam operates in a bending mode, strains the piezoelectric films, and generates charges from the piezoelectric effect. While a cantilever provides low resonant frequency, a proof mass at the end further reduces the resonant frequency, more suitable for low-frequency vibrational

Fig. 7 (a) Piezoelectric harvester (b) electromagnetic harvester

Fig. 8 (a) Piezoelectric harvester model (b) full bridge rectifier for the harvester

harvesting. Figure 7b shows an example MEMS electromagnetic harvester [6]. The magnets mount on a silicon spring, and the magnetic field will cut across the coils mount above and below the magnet once the spring oscillates. Vibrational harvesters can be analyzed using damped mass-spring systems [7]. It is desired to maximize the mass displacement with the power increasing with the square of the amplitude but the mass displacement is limited by the size of the system.

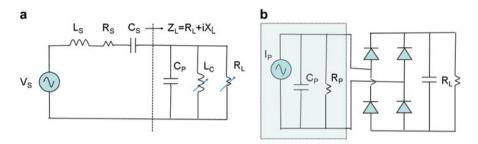

Equivalent circuit model for a piezoelectric harvester is shown in Fig. 8a. Its source impedance is equivalently a serial RLC network [8], where RS =  $\eta/\Theta^2$ , LS = M/ $\Theta^2$ , CS =  $\Theta^2/K$ .  $\eta$  is the mechanical damping coefficient,  $\Theta$  is the piezoelectric coefficient, M is the mass, and K is the effective stiffness. This can be derived from the vibration and transducing equations. The dotted line represents electromechanical interface. To extract maximum power into the electrical domain, it is desired that the loading impedance  $Z_L = R_L + jX_L$  be the complex conjugate of the source impedance,  $Z_{\rm S}^* = R_{\rm S} - jX_{\rm S}$ , where  $X_{\rm S} = \omega L_{\rm S} - 1/(\omega C_{\rm S})$ . With conjugate matching, the source basically sees source impedance  $R_{\rm S}$  and  $R_{\rm L}$ , and current and voltage waveforms are synchronized. In principle,  $Z_{\rm L}$  can be adjusted with variable L<sub>C</sub> and R<sub>L</sub> but L<sub>C</sub> can be large, tens to hundreds of Henry. In many practical systems, simple full bridge rectifier is used without conjugate matching as shown in Fig. 8b; however, the efficiency can be low as its ideal efficiency is only  $4/\pi Q_{\rm P}$ , where  $Q_{\rm P} = \omega_{\rm P} C_{\rm P} R_{\rm P}$  and  $Q_{\rm P}$  is usually bigger than 10. Its efficiency can be improved to  $8/\pi Q_P$  with a bias flip switch without inductors, and the harvesting efficiency can be dramatically boosted with synchronized switching harvesting on

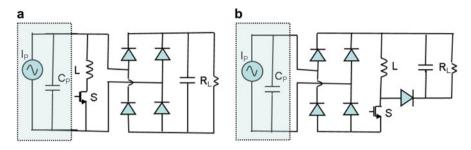

Fig. 9 (a) SSHI diagram (b) SECE diagram

inductors (SSHI) [9, 10] or synchronous electrical charge extraction (SECE) [11] as shown in Fig. 9.

SSHI adds an inductive switch path, L and S, to avoid the energy wasted for charging and discharging internal capacitance  $C_P$ . SECE has a switch S that will turn on each time the rectified voltage reaches maximum and turn off each time it reaches 0. This allows the stored charge to be removed completely and for the transducer to deliver the power to the load through L. Full wave rectified diodes, as shown in Fig. 9, can lead to significant rectification loss with the finite diode drop. Active NMOS with cross-coupled PMOS or active PMOS with cross-coupled NMOS can be used to reduce rectification loss considerably. With limited harvested energy, the comparators used to control the active switches need to be designed with low quiescent power.

While synchronized switching can boost harvester efficiency, it relies on the harvesters operating at resonant frequencies. However, the manufactured harvesters can have certain percentage of variations in their resonant frequencies because of manufacturing tolerances, and extracted power can be significantly lower if these resonant frequencies do not match those of the vibrational sources. Off-resonance efficiency can be improved by introducing switching delays for synchronized switching techniques based on the conjugate impedance matching principle [12].

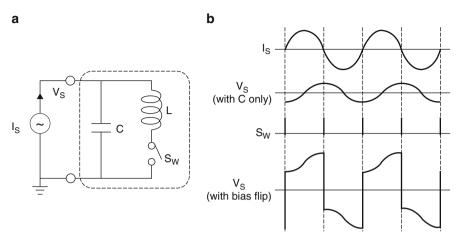

As shown in Fig. 10a, synchronized switching can be analyzed with a simple current source with parallel capacitance in parallel with a serial-connected inductor and switches. At zero crossing of the source current, the switch turns on for half of the period of the LC resonance to allow  $V_S$  to be flipped.  $V_S$  is not an ideal square waveform with the loss in switches and inductors. Similarly, the synchronized switching waveforms with delays can be shown in Fig. 11. If the delay is positive, the load appears capacitive as shown in Fig. 11a, and if the delay is negative, the load appears inductive as shown in Fig. 11b. A delay to the voltage waveform basically introduces a quadrature term besides the fundamental term. The equivalent impedance seen at the electromechanical interface becomes complex. By adjusting the delay, the equivalent complex impedance can be tuned to match the conjugate source impedance for maximum power transfer.

Fig. 10 (a) Synchronized switching schematic (b) waveforms

Fig. 11 Synchronized switching with (a) positive delay (b) negative delay

#### 5 Conclusions

Various energy harvesting transducers and their power conditioning circuits have been reviewed and discussed. Both the transducers and power conditioning circuits need to be optimized to maximize the power delivered to the load. While nonlinear harvesting circuits such as SSHI and SECE can significantly boost the output available to the load, it is important to minimize the circuit overhead for implementing these techniques. To accommodate manufacturing tolerances of the resonant frequencies for the vibrational harvester, off resonance output power can be improved through conjugate impedance matching or through introducing delays in synchronized switching. Acknowledgment The author would like to acknowledge contributions from members of the energy harvesting team at Analog Devices, Inc. and our university collaborators.

#### References

- 1. ADP5090 datasheet. http://www.analog.com/media/en/technical-documentation/data-sheets/ ADP5090.pdf.

- Lu Y, Yao S, Shao B, Brokaw P. A 200nA single inductor dual-input-triple-output (DITO) converter with two-stage charging and process-limit cold-start voltage for photovoltaic and thermoelectric energy harvesting. ISSCC Dig. Tech. Papers, Feb. 2016, pp 368–70.

- Cornett J, Lane B, Dunham M, Asheghi M, Goodson K, Gao Y, Sun N, Chen B. Chip-scale thermal energy harvester using Bi<sub>2</sub>Te<sub>3</sub>. IECON 2015-Yokahama, 41st Annual Conference of the IEEE Industrial Electronics Society, 2015, pp. 3326–9.

- 4. LTC3108 datasheet. http://www.linear.com/product/LTC3108.

- 5. LTC3109 datasheet. http://www.linear.com/product/LTC3109.

- Shin A, Radhakrishna U, Yang Y, Zhang Q, Gu L, Riehl P, Chandrakasan AP, Lang JH. A MEMS magnetic-based vibration energy harvester. Power MEMS Proceedings, 2017, pp. 363– 6.

- Beeby S, Tudor M, White N. Energy harvesting vibration sources for microsystems applications. Meas Sci Technol. 2006;17:175–95.

- Lien IC, Shu YC, Wu WJ, Shiu SM, Lin HC. Revisit of series-SSHI with comparison to other interface circuits in piezoelectric energy harvesting. Smart Mater Struct. 2010;19:125009–20.

- Guyomar D, Badel A, Lefeuvre E, Richard C. Toward energy harvesting using active materials and conversion improvement by nonlinear processing. IEEE Trans Ultrason Ferroelectr Freq Control. 2005;52(4):584–95.

- Ramadass Y, Chandraksan A. An efficient piezoelectric energy harvesting interface circuit using a bias-flip rectifier and shared inductor. IEEE J Solid State Circuits. 2010;45(1):189– 204.

- Lefeuvre E, Badel A, Richard C, Guyomar D. Piezoelectric energy harvesting device optimization by synchronous electric charge extraction. J Intell Mater Syst Struct. 2005;16(10):865–76.

- Hsieh P-H, Chen C-H, Chen H-C. Improving the scavenged power of nonlinear piezoelectric energy harvesting interface at off-resonance by introducing switching delay. IEEE Trans Power Electron. 2015;30(6):3142–55.

## From Bluetooth Low-Energy to Bluetooth No-Energy: System and Circuit Aspects of Energy Harvesting for IoT Applications

Wim Kruiskamp

#### 1 Introduction

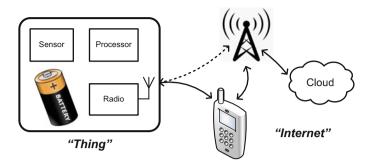

The Internet of Things (IoT) is the network of physical devices, vehicles, home appliances, and other items embedded with electronics, software, sensors, actuators, and network connectivity which enables these objects to connect and exchange data [1]. The "Things" in IoT can be anything and the variety in implementations is enormous, but many of them can be simplified to the system as depicted in Fig. 1. On the left side, there is the "Thing," which often is a small battery-powered device that includes a transceiver to connect wirelessly to the internet. It also often includes a sensor and some processing power.

The radio connection can be Bluetooth low-energy (BLE), Wi-Fi, cellular, or any other wireless standard. The main topic of this chapter is the energy supply of the IoT devices. The majority of today's devices are powered by a battery, either a 3 V coin-cell or a rechargeable battery. These batteries usually do not contain enough energy to supply the IoT devices for their entire lifetime, so they must be replaced or recharged on a regular basis. That might be acceptable today with only a few devices per person, but with the expected fast growth of the IoT, this will not be rational anymore in the near future. Either the power consumption of IoT devices needs to be reduced in orders of magnitude or they need to be powered by alternative sources. This is where energy harvesting will come into play. The only realistic scenario for everyone having tens of IoT devices will be that these devices are self-sustainable. This can be done by making use of available ambient energy

W. Kruiskamp (🖂)

Dialog Semiconductor, 's-Hertogenbosch, The Netherlands e-mail: wim.kruiskamp@diasemi.com

<sup>©</sup> Springer Nature Switzerland AG 2019

K. A. A. Makinwa et al. (eds.), *Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers*, https://doi.org/10.1007/978-3-319-97870-3\_2

Fig. 1 Internet of Things device

like light, heat, movement, or RF energy. Thus the main driver for energy harvesting will not be cost or an environmental reason, it will be ease-of-use and install-and-forget.

The remainder of this chapter is structured as follows: In Sect. 2, we will look into the average power consumption of a typical BLE IoT device. In Sect. 3, we will briefly discuss alternative energy sources that can deliver this power. In Sect. 4, we will propose a power management unit (PMU) to connect these sources to an IoT device.

#### 2 Average Power Consumption

A popular battery for IoT devices is a 3 V CR2032 coin-cell battery containing about 225mAh of charge. For applications that consume in the order of  $5\mu$ W, this results in a battery lifetime of well over 10 years:

lifetime =

$$\frac{225mAh \times 3V}{5\mu W \times 24 \text{ hours} \times 365 \text{ days} \mu W d} = 15 \text{ years}$$

This kind of battery lifetime is long enough for an acceptable product lifetime without the need to replace the battery. For such applications, there is hardly any reason not to use a coin-cell primary battery; they are reliable, cheap, and relatively small.

However, the majority of today's IoT devices consume at least an order of magnitude more power. This power consumption of an IoT device is due to the following actions:

- Sensor data acquisition and processing.

- Wireless communication to a host.

- Timekeeping during sleep.

Each of these components will be discussed in the next sections, followed by two application examples.

#### 2.1 Sensor Data Acquisition and Processing

The power consumed to acquire and process information is very application dependent. For functions like temperature measurement, sensors are available which consume less than 1  $\mu$ W [2–4], and more power-hungry temperature sensors can be operated at a low duty-cycle to achieve similar power consumptions. For applications that only perform these kinds of measurements, the power consumption for data acquisition and data processing will not be the limiting factor for a 10-year battery lifetime. For BLE beacons and tags, there is no sensor available hence no power consumption associated with it.

There are, however, also measurements that consume significantly more power. A well-known example is location via GPS which typically consumes in the mW range. Also optical heart-rate monitoring typically consumes a significant amount of power; today ranging from more than 100  $\mu$ W [5, 6] to several mWs. These kinds of measurement functions dominate the total power consumption of fitness trackers for example.

#### 2.2 Wireless Communication (BLE)

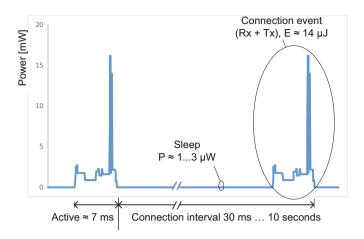

Wireless communication from an IoT device to a host (i.e., a smartphone) via BLE consumes a significant amount of energy. A typical power profile, measured on a DA14580 chip [9], known to be best in class for power consumption, is depicted in Fig. 2. A connection event consists of a receive action and transmit action plus some overhead for processing and startup of the crystal oscillator. The total energy associated with a connection event is about 14  $\mu$ J measured at the battery. With a connection interval of 1 second, that would correspond to an average power consumption of 14  $\mu$ W, plus 1–3  $\mu$ W associated with the power consumption during sleep between the connection events.

#### 2.3 Timekeeping During Sleep

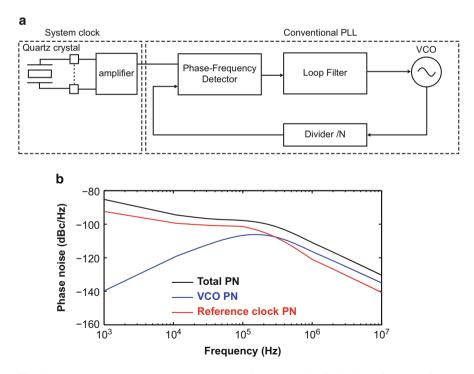

BLE devices are usually asleep most of the time, counting to the next communication event. In order to maintain a synchronous BLE link, the timing accuracy needs to be better than 500 ppm. Traditionally, this timekeeping is done with a 32.768 kHz Quartz oscillator. Such an oscillator plus counter can easily be achieved with a power consumption below 1  $\mu$ W and can have an accuracy in the single-digit

Fig. 2 Typical BLE power consumption

ppm range. Academic research has even reported a power consumption of only 2 nW for a Quartz oscillator [7]. Apart from this low-frequency reference, a BLE chip also needs a reference for the 2.4 GHz RF signal. This is typically done with another Quartz oscillator, operating at a higher frequency, usually 16 MHz or 32 MHz. The power consumption of this higher frequency oscillator is in the order of 100  $\mu$ W and is therefore only enabled when the radio is active and can therefore unfortunately not be used for timekeeping. For that reason, BLE devices traditionally used to have two Quartz oscillators.

Despite their very good accuracy, very good stability and low power consumption, there is a clear trend in BLE to replace the low-frequency Quartz oscillator by an on-chip relaxation oscillator. These oscillators can also be designed with a power consumption of less than 1  $\mu$ W [8] and reasonably good accuracy. The accuracy over temperature of such oscillators is usually not sufficient for the 500 ppm BLE requirements, but by calibrating against the high-frequency Quartz oscillator each time the radio is active, a timing accuracy of better than 500 ppm can be achieved. The benefit of this configuration over the traditional two-crystal configuration is lower cost and smaller size.

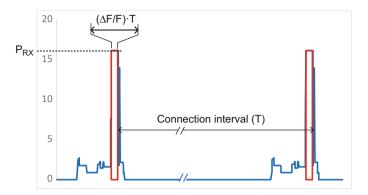

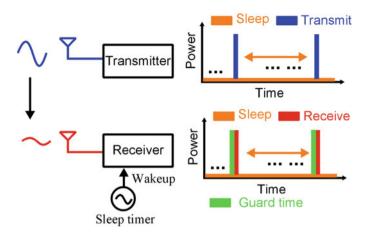

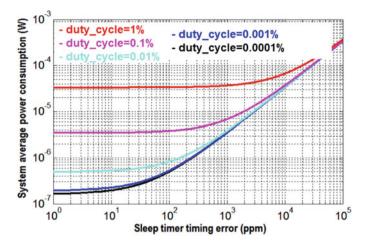

Although the power consumption of a 32 kHz relaxation oscillator in itself is comparable to a 32 kHz Quartz oscillator, the limited accuracy of relaxation oscillators comes with a power consumption penalty at a system level. If the BLE device is synchronized with a smartphone, the receiver must be enabled at the moment the smartphone is transmitting its data. With a very accurate Quartz oscillator, this is not a problem and can be done just in time. In case of a relaxation oscillator, this might vary by 500 ppm, the receiver must be enabled early enough not to miss the smartphone signal. This is depicted in Fig. 3. The power penalty will be equal to:

Fig. 3 Effect of timer inaccuracy on average power consumption

$$P_{\text{extra}} = \frac{(\Delta F)_{\text{max}}}{F} \cdot P_{RX}$$

This extra power consumption is independent of the connection interval: If the connection interval is larger, the absolute time the receiver has to be enabled is larger, but it happens less often.

When we consider a typical receiver power consumption of 10 mW and a relaxation oscillator with a maximum inaccuracy of 500 ppm, the power consumption penalty is:

$$P_{\text{extra}} = 500 \, ppm \cdot 10m W = 5\mu W$$

This 5  $\mu$ W is about equal to the maximum allowed power consumption if we want to operate for more than 10 years on a coin-cell battery and is therefore a very significant contribution.

#### 2.4 Application Example: BLE Beacon

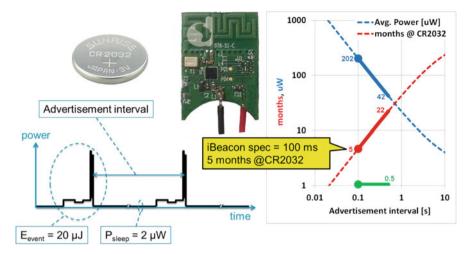

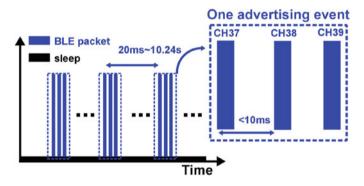

A BLE beacon is like a lighthouse. It repeatedly transmits the same signal to surrounding BLE-enabled devices such as smartphones and tablets. The transmitted data includes a unique identifier of the beacon and might also include a small amount of other data like a link to a website. The signal is transmitted multiple times a second on each of the three advertisement channels of BLE. For a beacon, there is no power required for sensor or data-processing, and inaccuracy of the sleep-timer is irrelevant since a beacon is only one-way communication and therefore not synchronized to a smartphone. The power consumption is therefore dominated by the advertisement event (today, typically 20  $\mu$ J for advertising in

Fig. 4 BLE beacon: Typical power-consumption and battery-lifetime

all three advertisement channels [9, 10]) with a power consumption between the advertisement events in the order of 2  $\mu$ W. Due to this, the battery lifetime is proportional to the advertisement interval as depicted in Fig. 3. In its iBeacon specification, Apple recommends an advertisement interval of 100 ms in order to have high chances that a passing smartphone will catch the beacon signal. This performance might not be needed in all applications and often beacons have longer advertisement intervals, in the order of 300 ms, to save power.

As can be seen in the Fig. 4, the battery lifetime of beacons with the recommended 100 ms advertisement interval is currently well below 1 year. Even if the advertisement interval is stretched to a questionably long interval of 500 ms, the batteries will have to be replaced every 2 years. This power consumption will decrease in next generation BLE devices but is still far away from the 5  $\mu$ W power consumption target to run for more than 10 years on a coin-cell battery.

#### 2.5 Application Example: Fitness Band

Fitness bands and activity trackers are often powered by a rechargeable Li-ion battery with a battery lifetime ranging from less than a week to more than a month. If we assume a battery lifetime of 1 month from a 60 mAh Li-ion battery, we can calculate that the average power consumption has to be in the order of  $300 \,\mu$ W.

These activity trackers are synchronized with the smartphone with one up to a few connections per second. With an energy consumption of 15  $\mu$ J per connection event [9], the radio connection only explains about 10% of the total energy consumption. Power consumption due to inaccuracy of the timer is in the order of 5

$\mu$ W and is therefore negligible compared to the 300  $\mu$ W total power consumption. We can therefore conclude that the power consumption is dominated by the sensors, the data-processing, and notifications to the user via a display and/or buzzer. This power consumption per function is expected to decrease in next-generation devices, but most likely new features will be added to bring the power consumption back up again. Today, we are still far away from the 5  $\mu$ W target to run many years on a small primary battery, and this is not expected to change in the near future.

#### **3** Alternative Energy Sources

In the previous paragraphs, we learned that there is a need for alternative energy sources with an average power in the order of several 10s to several 100 s of  $\mu$ W. The possible options are light, movement, heat, RF-energy, and bio-fuel.

One of the easiest sources to use is light. Photovoltaic (PV) cells are cheap and thin and the available power ranges from 15  $\mu$ W/cm<sup>2</sup> indoors to 15 mW/cm<sup>2</sup> in full sunlight. Even indoors, a few cm<sup>2</sup> could already be sufficient to power an IoT device.

Another option is human body heat. An average human consumes in the order of 2000 kcal per day, which is equal to an average power consumption of 100 W. This power is eventually transformed into heat, and with a typical skin area of about  $2 \text{ m}^2$ , this results in an average thermal power of  $5 \text{ mW/cm}^2$ . With a Thermo Electric Generator (TEG), this thermal power can be converted into electrical power. The efficiency of this power transfer has a theoretical upper limit equal to the Carnot efficiency:

$$\eta_{\text{Carnot}} = 1 - \frac{T_{\text{cold}} [K]}{T_{\text{hot}} [K]}$$

This means we can only achieve 0.3% efficiency per degree Celsius temperature difference over the TEG. Practical TEGs are often made from the material Bismuth Telluride and can achieve an efficiency up to 18% of the theoretical limit. This results in an average electrical power from human heat in the order of  $3\mu$ W/cm<sup>2</sup> per degrees Celsius temperature difference. Another option might be ambient RF energy. However, this is only useful in the near vicinity of an RF source (Table 1).

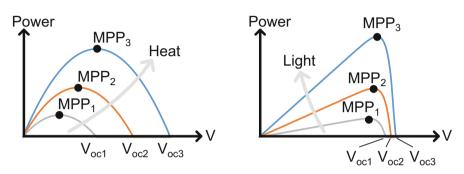

#### 3.1 Maximum Power Point

In order to harvest as much power as possible from an alternative energy source, the voltage across the source must be kept at the value corresponding to the maximum power point (MPP). For a TEG that is half the open-clamp voltage ( $V_{OC}$ ), for a PV-cell it is somewhere between 70% and 80% of its open-clamp voltage.

| Source      | Conditions                                            | Harvested power                               | Open-clamp voltage |

|-------------|-------------------------------------------------------|-----------------------------------------------|--------------------|

| Light       | Outdoors, sunny                                       | 15 mW/cm <sup>2</sup>                         | 0.6 V              |

|             | Outdoors, shade                                       | 500 μW/cm <sup>2</sup>                        | 0.5 V              |

|             | Indoors                                               | 15 μW/cm <sup>2</sup>                         | 0.4 V              |

| Human heat  | $\Delta T = 5 \ ^{\circ}C$ $\Delta T = 1 \ ^{\circ}C$ | 15 μW/cm <sup>2</sup><br>3 μW/cm <sup>2</sup> | 0.4 V<br>80 mV     |

| RF (20 dBm) | Distance = $0.3 \text{ m}$                            | 9 μW/cm <sup>2</sup>                          |                    |

| (=100 mW)   | Distance = $1 \text{ m}$                              | 0.8 μW/cm <sup>2</sup>                        |                    |

Table 1 Typical characteristics of alternative energy sources

Fig. 5 Maximum power point of TEG (left) and PV-cell (right)

A practical challenge for an energy-harvesting system is the fact that the power density of alternative energy sources depends on environmental conditions such as illumination density and temperature. Therefore, a maximum power point tracking (MPPT) system is needed to constantly harvest the maximum amount of energy (Fig. 5).

A popular way to do MPPT is to periodically sample the open-clamp voltage and regulate to a fixed fraction of that voltage [13, 14]. The main drawback of this approach is that the energy harvesting must be interrupted periodically to measure the open-clamp voltage.

Another option is to measure the harvested power and apply a search algorithm (perturb and observe) to stay close to the MPP [15, 16]. This approach does not require the harvesting to be interrupted but does require additional circuitry to measure the harvested power.

#### 4 Proposed Architecture

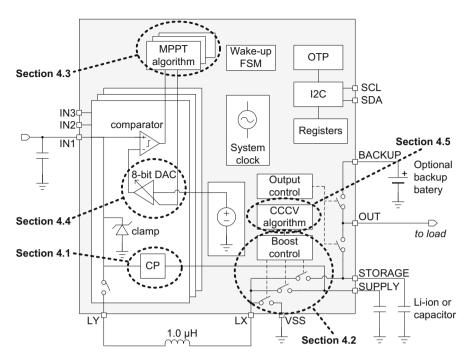

To supply an IoT device from alternative energy sources, the architecture as depicted in Fig. 6 is proposed. The main task of this circuit is to transfer energy from the sources to a storage capacitor or rechargeable battery connected to pin STORAGE. Like many other harvesting circuits [12, 13, 15, 16], this is done by an inductive

Fig. 6 Proposed architecture

boost converter. The control circuits for this boost converter are supplied by the other output of the boost converter: pin SUPPLY. This voltage at the output of the boost converter is not yet available during startup. Therefore, a charge pump is added to allow cold-start at voltages as low as 230 mV.

The system includes a digitally implemented MPPT at each of the three inputs as well as a digitally implemented Constant-Current Constant-Voltage (CCCV) charging algorithm at the output.

In the next sub-sections, the circuits and aspects which are typical for energy harvesting systems are discussed in more detail.

#### 4.1 Startup Circuit

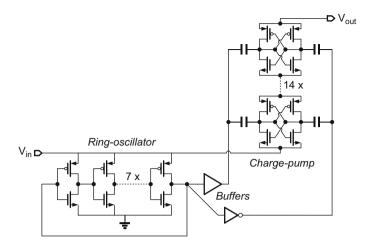

The startup circuit consists of a 7-stage ring-oscillator, clock-buffers, and a 14-stage charge-pump. The charge-pump stage is a modified version of the two-phase voltage doubler, presented in [11] and shown in the right-hand side of Fig. 7.

The chip is processed in standard TSMC 55 nm technology, without using low threshold voltage transistors. This process choice was made for easy integration in a BLE chip but is not the ideal choice for extremely low-voltage operation. In order

Fig. 7 Startup circuit principle

Fig. 8 Bootstrapped transistors (gray) added to original transistors

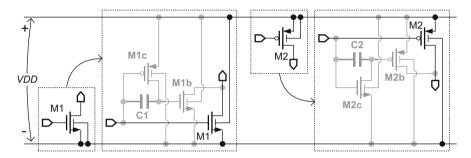

to use the circuit of Fig. 5 at input voltages as low as 230 mV, reverse body biasing was applied to lower the threshold voltage. Furthermore, each transistor is assisted by a transistor with a bootstrapped gate voltage. This is depicted in Fig. 8.

Each nMOS transistor (M1 in Fig. 8) gets a parallel connected transistor M1b, of which the gate is connected via a capacitor C1. Capacitor C1 is charged via transistor M1c and acts like a floating voltage source, increasing the value of Vgs. While the gate of M1 is switching between 0 V and VDD, the gate of M1b is switching between VDD and 2xVDD. The same is done for each pMOS transistor (M2 in Fig. 8). Furthermore, the bulks of all nMOS transistors are connected to the higher rail and the bulks of all pMOS transistors are connected to the lower rail. These techniques are applied in the ring-oscillator, the buffers, and in the charge-pump stages.

Initially the bootstrap capacitors are uncharged and the circuit will operate at a very low frequency with very low drive capability. This slow oscillation will however be sufficient to charge the capacitors in the bootstrapped transistors, which will give these transistors an increased conductivity. This will cause the frequency of the oscillator to rise significantly and will also lower the on-resistance in the switches of the charge-pump stages significantly.

The drawback of this modification, apart from increased complexity, is increased leakage in the off-state and the need to limit the input voltage of the charge pump. This is overcome by disabling the circuit when cold-start is completed and by adding a voltage limiter in front of the startup circuit.

#### 4.2 Boost Converter

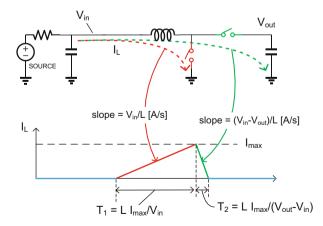

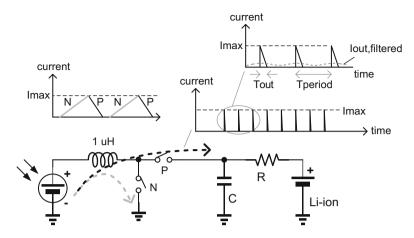

The boost converter is operating in discontinuous conduction mode (DCM) as depicted in Fig. 9. In order to reduce pcb space, a small inductor of 1  $\mu$ H is used, which is an order of magnitude smaller than most other energy-harvesting chips [13, 15, 16].

The control of the boost converter is done by comparators: The input and output voltages are monitored by dynamic (clocked) comparators, which does not consume static power. If both the input voltage is available and the output voltage is below its maximum, a DCM-pulse is started. The inductor is connected to ground and the inductor current will rise linearly, storing energy in the inductor. When a continuous comparator detects that the current has reached a certain value  $I_{max}$ , the inductor is connected to the output and the inductor current drops linearly, releasing its energy to the output. When another continuous comparator detects that the current is zero, the output switch is opened and the procedure starts all over again. The DCM-mode is very suitable for multiple-input operation, since after each DCM-pulse, the boost converter returns to its idle state with zero current in the inductor, which is an ideal situation to change to another input.

Fig. 9 DCM-mode operation of boost converter

For cost and size reasons, the used inductor is a small  $1\mu$ H inductor. The consequence of this small inductor value is short ON-times of the switches: With the used  $I_{max}$  of 280 mA, the ON-time (T<sub>2</sub>) of the output switch can be as low as 70 ns. The two comparators (peak-current detection and zero-cross detection) need to react significantly faster than the ON-time and yet be accurate. To keep the quiescent power of these comparators within acceptable levels, automatic calibration is applied as described in [9], and the comparators are only enabled when needed.

#### 4.3 MPPT Algorithm

The applied MPPT algorithm is "perturb-and-observe": The input DAC is set to a certain value and the harvested energy is measured for a fixed amount of time. Then the DAC is changed by a small amount and the harvested energy is again measured for a same amount of time. If the harvested energy has increased, the DAC is again changed in the same direction, otherwise, the DAC is changed in the opposite direction.

The measuring of the harvested energy is done by counting the DCM pulses to the output and digitally scaling that number by a factor  $E_{\text{DCM}}$ , which is an estimate of the energy per DCM pulse. The factor  $E_{\text{DCM}}$  can be estimated from Fig. 8 as given below:

$$E_{\text{DCM}} = V \cdot I \cdot T \approx \frac{L \cdot (I_{\text{max}})^2}{2} \cdot \frac{V_{\text{STORAGE}}}{(V_{\text{STORAGE}} - V_{\text{in}})}$$

In which *L* and  $I_{\text{max}}$  are known constants,  $V_{\text{in}}$  is set by the DAC and therefore available in a digital form, and  $V_{\text{STORAGE}}$  is a slowly changing voltage that is measured by a SAR ADC each time the DAC is updated. Therefore, this algorithm can be implemented with little analog overhead; mainly a slow and low-resolution ADC.

This MPPT algorithm has several advantages over the more commonly used *fractional open-clamp-voltage* approach, mentioned in Sect. 3.1:

- 1. The harvesting process does not have to be interrupted to measure the openclamp voltage. This interruption would typically be in the order of 2% of the time, reducing the harvested energy by the same amount.

- 2. This MPPT algorithm searches for the maximum energy transferred to the storage and therefore automatically takes into account voltage-dependent efficiency of the boost-converter. The boost-converter is less efficient at very low input voltages, so the overall optimal voltage from an output power perspective might be higher than the optimal voltage for maximum power delivered by the source.

3. The MPP voltage is by definition lower than the open-clamp voltage. The fact that this algorithm does not need to measure the open-clamp voltage therefore allows the use of better transistors (with lower voltage rating) or to accept sources with higher open-clamp voltages.

#### 4.4 Low-Power DAC

The boost-converter is only enabled when there is energy to be harvested and therefore does not have to be designed for very low quiescent power while active. The DACs which set the MPP threshold for the input voltages are always on and therefore has to be very low power, especially since there are three of them, one for each input.

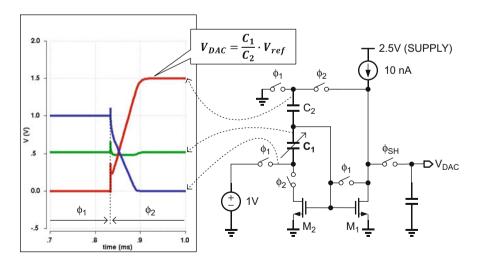

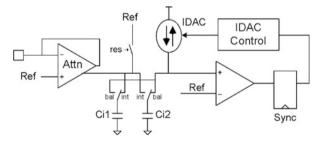

The DACs are realized as switched capacitor circuits, with a single transistor  $(M_1)$  as gain-stage, biased with 10 nA as depicted in Fig. 10. The capacitors  $C_1$  and  $C_2$  are made of 0.6 fF units,  $C_1$  being 100 units and  $C_2$  scalable from 0 to 255 units. During the beginning of phase 2, voltage over  $C_1$  makes a step equal to the reference voltage (1 V). The current to charge  $C_1$  flows through  $C_2$ , therefore increasing the voltage over  $C_2$  with a voltage equal to the reference, multiplied by the capacitor ratio. This voltage is sampled on a capacitor and used as reference for the input comparators.

The bias current can be as low as 10 nA since the speed of the DAC can be low. The MPPT algorithm updates the DAC value at a rate of several 10s of Hz, so a clock speed for the DAC of 1 kHz is more than sufficient.

Fig. 10 Low-Iq DAC

Fig. 11 CCCV charging profile

#### 4.5 CCCV Charging

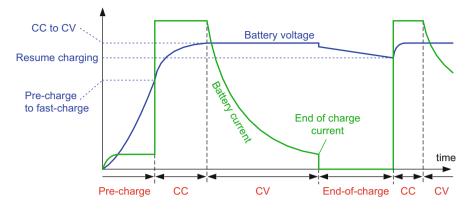

In case a Li-ion battery is used for energy storage, charging should be done according to the well-known Constant-Current, Constant-Voltage (CCCV) profile as depicted in Fig. 11. Four different phases of the charging profile can be recognized: "pre-charge," "constant-current (CC)," "constant-voltage (CV)," and "end-of-charge."

When the battery is almost empty, it is pre-charged by a small current until its voltage reaches a certain level. As soon as the battery voltage has reached that level, the charge current limit is increased to a maximum value and charging continues in CC-mode. The battery voltage will rise further and eventually reach its maximum allowed level. The charging will then be done with a current at which the battery voltage does not exceed the maximum voltage (CV mode). The charging current will drop and eventually falls below the end-of-charge limit. Charging will be stopped completely until the battery voltage has dropped below a certain threshold.

In order to charge a battery according to a CCCV charging profile, the charge current must be controlled and measured. In this proposal, it is done in a digital way. The charge current can be limited by setting a minimum time between each boost-converter DCM pulse relative to the time the inductor is connected to the output (P-switch closed). This is depicted in Fig. 12.

By measuring the on-time  $T_{out}$  of the output switch with an oscillator and a counter, the minimum period  $T_{CC}$  to meet the maximum constant-current limit  $I_{CC}$  can be calculated as follows:

$$T_{CC} = T_{\text{out}} \cdot \frac{I_{\text{max}}}{2 \cdot I_{CC}}$$

In the same way, the period  $T_{end}$  corresponding to an end-of-charge current  $I_{end}$  can be calculated:

Fig. 12 Boost converter current limit

$$T_{\rm end} = T_{\rm out} \cdot \frac{I_{\rm max}}{2 \cdot I_{\rm end}}$$

The procedure to meet the CCCV charging curve is now as follows: If the output voltage is below its maximum allowed level and the time from the previous DCM pulse has exceeded the time  $T_{CC}$ , a next DCM pulse is allowed. When a DCM pulse is blocked by the condition that the output voltage is above the maximum allowed level for more than  $T_{end}$ , the end-of-charge condition has been reached and charging is stopped completely. In order to reduce large ripple currents into the Li-ion battery, an external RC filter with typical values of 1  $\Omega$  and 10  $\mu$ F is added as depicted in Fig. 12.

#### **5** Measurement Results

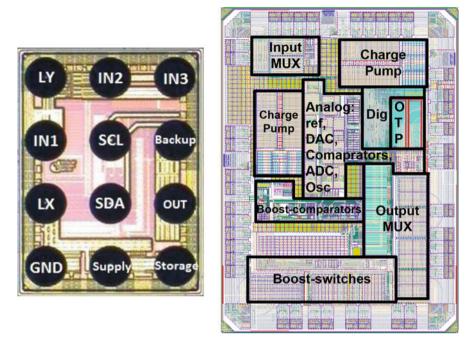

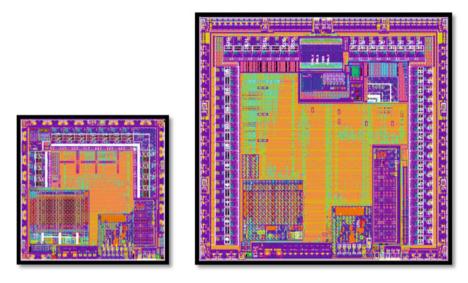

The chip was fabricated in TSMC 55 nm. The output multiplexer and the boostconverter switches consume a large part of the area due to their relatively high voltage tolerance to allow the use of Li-ion batteries. The charge pumps also consume a significant amount of area due to the many stages and on-chip capacitors. The input multiplexer and the digital control are relatively small (Fig. 13).

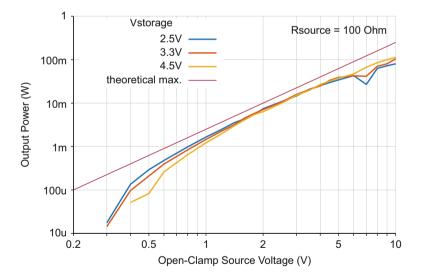

The chip was tested with a voltage source with fixed source resistance. Even though the input circuits cannot withstand more than 2.5 V, the chip can be used with sources with a much higher open-clamp voltage as depicted in Fig. 14. The MPPT algorithm will set the input threshold at a value between 0 V and 2.5 V, which makes the boost converter under normal conditions to prevent the inputs to rise too high. Internal clamp circuits are added to prevent over-voltage at the input when the boost converter pulses are blocked by the CCCV algorithm.

**Fig. 13** Die photo and floorplan  $(1.5 \times 2 \text{ mm})$

Fig. 14 Measured output power versus open-clamp voltage

# 6 Conclusions

Many of today's IoT devices consume too much power to run on the same nonrechargeable battery for the entire product lifetime. It is not to be expected that this will change in the near future. With the anticipated growth in number of IoT devices per person, changing batteries or charging batteries regularly is not a practical situation. Alternative energy sources are available that can deliver the required amount of power. Since these sources are not present continuously, it might be needed to use more than one of these sources and to add a rechargeable battery to the system to bridge longer periods without available energy from the sources.

This chapter shows an example of a power management system that is required for such an energy-harvesting IoT device. It includes circuits that can operate at low voltages, circuits that operate with very low quiescent power, and control algorithms to maximize the harvested power and to guarantee safe charging of batteries.

#### References

- 1. Wikipedia. https://en.wikipedia.org/wiki/Internet\_of\_things.

- 2. Makinwa KAA. Temperature Sensor Performance Survey. [Online]. Available: http://ei.ewi.tudelft.nl/docs/TSensor\_survey.xls.

- Lin Y-S, Sylvester D, Blaauw D.An ultra low power 1V, 220nW temperature sensor for passive wireless applications. 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, 2008, pp. 507–10.

- 4. Souri K, Chae Y, Thus F, Makinwa K. 12.7 A 0.85V 600nW all-CMOS temperature sensor with an inaccuracy of  $\pm 0.4^{\circ}$ C (3 $\sigma$ ) from -40 to 125 $^{\circ}$ C. In 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, 2014, pp. 222–3.

- Konijnenburg M, et al. A multi(BIO)sensor acquisition system with integrated processor, power management, 8 times 8 LED drivers, and simultaneously synchronized ECG, BIO-Z, GSR, and two PPG readouts. IEEE J Solid-State Circuits. 2016;51(11):2584–95.

- Rajesh PV, et al.. 22.4 A 172μW compressive sampling photoplethysmographic readout with embedded direct heart-rate and variability extraction from compressively sampled data. In 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2016, pp. 386–7.

- Hsiao KJ. 17.7 A 1.89nW/0.15V self-charged XO for real-time clock generation. In 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, 2014, pp. 298–9.

- Griffith D, Røine PT, Murdock J, Smith R. 17.8 A 190nW 33kHz RC oscillator with ±0.21% temperature stability and 4ppm long-term stability. In 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, 2014, pp. 300–1.

- Prummel J, et al. A 10 mW Bluetooth low-energy transceiver with on-chip matching. IEEE J Solid-State Circuits. 2015;50(12):3077–88.

- Intaschi L, Bruschi P, Iannaccone G, Dalena F. A 220-mV input, 8.6 step-up voltage conversion ratio, 10.45-μW output power, fully integrated switched-capacitor converter for energy harvesting. In 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, 2017, pp. 1–4.

- 11. Nakagome Y, Tanaka H, et al. An experimental 1.5V 64Mb DRAM. IEEE J Solid-State Circuits. 1991;26(4):465–72.

- 12. Wu HH, Chen LY, Wei CL. Wide-input-voltage-range and high-efficiency energy harvester with a 155-mV startup voltage for solar power. In ESSCIRC 2017 43rd IEEE European Solid State Circuits Conference, Leuven, 2017, pp. 295–8.

- Lu Y, Yao S, Shao B, Brokaw P. 21.3 A 200nA single-inductor dual-input-triple-output (DITO) converter with two-stage charging and process-limit cold-start voltage for photovoltaic and thermoelectric energy harvesting. In 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2016, pp. 368–9.

- Simjee FI, Chou PH. Efficient charging of supercapacitors for extended lifetime of wireless sensor nodes. IEEE Trans Power Electron. 2008;23(3):1526–36.

- 15. Bandyopadhyay S, Chandrakasan AP. Platform architecture for solar, thermal, and vibration energy combining with MPPT and single inductor. IEEE J Solid-State Circuits. 2012;47(9):2199–215.

- 16. Yu G, Chew KWR, Sun ZC, Tang H, Siek L. A 400 nW single-inductor dual-input-tri-output DC–DC buck-boost converter with maximum power point tracking for indoor photovoltaic energy harvesting. IEEE J Solid-State Circuits. 2015;50(11):2758–72.

# **Design of Powerful DCDC Converters** with Nanopower Consumption

Vadim Ivanov

# 1 Introduction

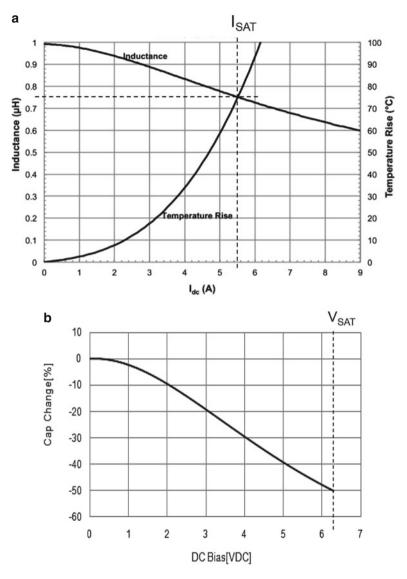

Design of the integrated systems with nanopower consumption is quite different from the standard practice and by no means is business as usual. It starts with process selection that often require unusual options; use of altered system structure and operation manner; meticulous attention to the secondary procedures like startup, power sequencing, etc.; transistor sizing and new nano-specific circuit cells. Power management of such systems should be equally efficient when it is sleeping and when it is operating at full throttle and with instant switching from one mode to another at unpredictable timing. Common concept of operation mode switching is very inefficient: every additional operation mode triples design labor, as we have to create two systems instead of one along with transition procedure; production testing becomes a nightmare; operation and behavior of such systems is almost impossible to explain to customer or somebody without years of deep dive in the subject. Hence, choice of operating mode is narrow. We have to move away from digital options with high-frequency clocks from fixed-frequency DCDC converters and instead concentrate on variable-frequency operation modes with new techniques of the adaptive error- and load-dependent biasing. Another limitation specific to industrial design is selection of external components-such DCDC converter should be operational with cheapest monolithic inductors and ceramic capacitors, which vary 70–90% in current and voltage range [1], as well as operation temperature range from -40 to 85, 125, or even 150C, and robustness to process variation of component parameters.

V. Ivanov (🖂)

Texas Instruments Inc., Tucson, AZ, USA e-mail: ivanov\_vadim@ti.com

<sup>©</sup> Springer Nature Switzerland AG 2019

K. A. A. Makinwa et al. (eds.), *Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers,* https://doi.org/10.1007/978-3-319-97870-3\_3

New applications and requirements demand new, nano-specific circuit techniques and cells. Cells shown below are created with structural design methodology [2] powerful tool in any design. Viability of methodology, cells, and structures has been proven by multiple ICs in mass production.

#### 2 Structural Design Methodology of Analog Circuits

There are 18,000 different amplifiers that can be created from just two transistors. This number is derived from a multiple of options: NMOS/PMOS, common gate/source/drain, four kinds of feedback for each transistor, and for the amplifier as a whole. With the typical analog circuit containing more than a 100 transistors, the number of variants is greater than the number of atoms in the galaxy—and only a few can solve a designer's problem. As a result, most of analog designers are using a cookbook approach, creating a new circuit from the existing one with the fewest changes possible. Radically new solutions are rare, and they are considered to be the major intellectual property by designers and their employers. A method to invent circuit solutions is needed. The structural methodology is one such technique that can be deployed to find a set of acceptable application solutions to weed out bad or inferior circuits instantly. It has a long success record in the design of operational amplifiers, references, power amplifiers, and DCDC converters. By following the steps described below, a designer can find a set of satisfactory solutions, some of which are known and some are new. Then designer can finally choose the one based on personal preference and secondary parameters of importance.

#### 2.1 Graphic Presentation of the System

The first step in the circuit design should be a presentation of the problem to be solved in a graphic form. The graphical representation is much more informative and easier for comprehension then text description or set of equations. The most common language for such presentation is a structural diagram. Another option is the signal flow graph, which has the advantages of existing formal rules for equivalent transformations [3] and drawing simplicity. Almost forgotten, but preferred by founders of the control theory, like Mason or Bode, the signal flow graphs have recently started to gain popularity [4].

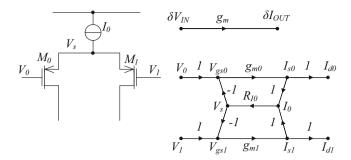

An example of signal flow graphs of the differential pair is given in Fig. 1. The differential stage can be presented in the simple form of a single  $g_m$  link or in more details as illustrated in Fig. 1. Graph in Fig. 1 includes the transconductance of each transistor and a common-mode feedback. The graph in Fig. 1 is called the "general structure with common-mode feedback." Properties of this graph can be extrapolated to any multiloop, multidimensional structure (or multidimensional

Fig. 1 Signal flow graph of differential stage

structure can be equivalently transformed to this graph), just as complex numbers represent properties of the n-dimensional space.

An analysis of the differential structure with common-mode feedback [2, supplement A] is instrumental in the design of circuits with multiple input/output variables, such as class AB stages or multiple output DCDC converters. It also helps in the single-glance estimation and selection of the circuit within the set of possible options.

## 2.2 Dedicated Feedback Control for Each Important Parameter

The next step in the circuit design is a transformation of system structure to the form where every important variable is controlled by a dedicated feedback loop. Circuits without such feedbacks should be weeded out without any further consideration. The advantage of the system where all significant parameters are controlled is obvious; however, the main obstacle to the universal application of this rule is the problem of stability in the resulting multiloop structure.

Although not necessary, but sufficient, the condition for the whole system's stability is the stability in each and every loop within this system [5]. A feedback loop can be unconditionally stable (with any load and signal source impedance) if its open-loop transfer function has only one pole. Consequently, the easy way to ensure system stability is designing each loop with the single-stage (single-pole) amplifiers only.

This approach to stability immensely simplifies the design process. Although in some cases the exclusive use of the single-stage amplifiers is not possible; here, conventional compensation techniques need to be applied and stability has to be carefully verified.

Standard verification of the stability using the merit of phase margin requires a break in the feedback loop and is not suitable for the multiloop system (which one of the loops to break?). Method of the multiloop system small-signal stability verification by using AC simulations has been described in [6]. Due to the

Fig. 2 Elementary cells library

unavoidable presence of the nonlinear effects in the circuit, the small-signal only stability verification is not sufficient. The small- and large-step response transient simulations followed by extraction of the overshoot and damping factor could be used instead.

## 2.3 Library of Elementary Cells

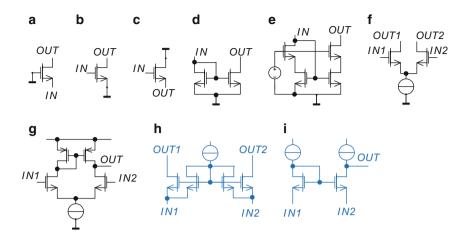

The next design step is implementation of the system structure with elementary cells. The library of these cells includes circuits described in every textbook on analog design, as shown in Fig. 2.

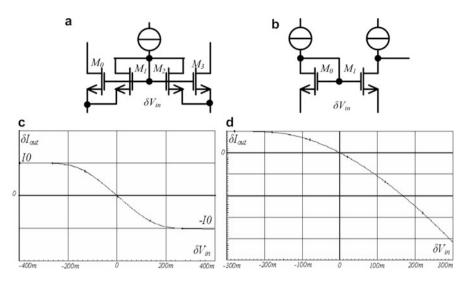

It also includes lesser known cells of the current-input amplifiers shown in Fig. 2h, i, which should be a part of every designer's arsenal. In the circuit of Fig. 3a, MO and MI currents are matched, as well as the currents of M2/M3. Consequently, input currents do not depend on the common-mode input voltage, so the common-mode input impedance is high. The differential input impedance is small and equals to  $1/g_m$ . Dependence of the output current vs. input voltage (Fig. 3c) is similar to the standard differential stage of Fig. 2f.

The single-output version of this amplifier is shown in Fig. 3b. In this cell, the current sinking from output is unlimited and output current vs. input voltage curve (Fig. 3d) is nonsymmetrical.

Use of the current-input amplifier cell inside the local feedback loops improves the speed of these loops at least five times for any given current budget. It simplifies the frequency compensation, allowing replacement of the common-source gain stages in the signal path with the common-gate ones, which have much smaller delay.

Fig. 3 The current-input amplifier cells

The elimination of all or most compensation capacitors becomes possible. For example, an operational amplifier described in [7] comprises more than 25 feedback loops, but the only compensation capacitors on its chip are the two Miller capacitors in the main signal path.

# 2.4 Features of a Good Circuit

With structural methodology, we restrict a set of circuits to be considered "good" circuits only.

#### **Features of the Good Circuit**

- 1. Good circuit has a dedicated feedback loop controlling each parameter which is important for the reaching of system goals.

- 2. Dynamically each local loop and system as a whole are stable and their step response looks like the response of the system with first- or second-order transfer function.

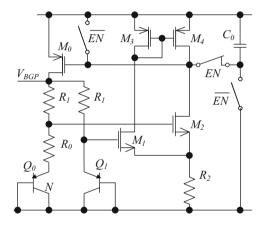

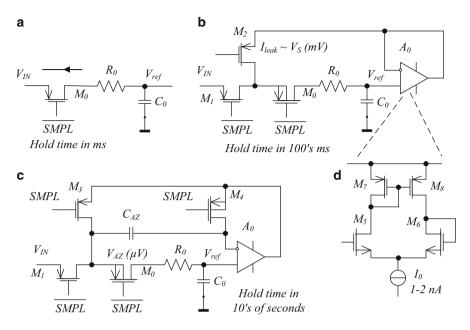

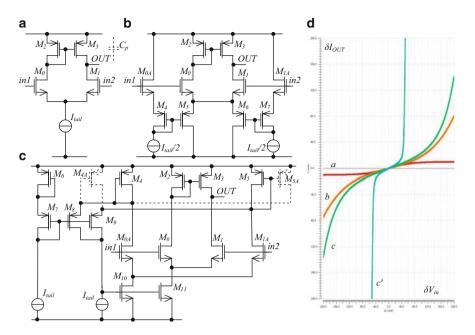

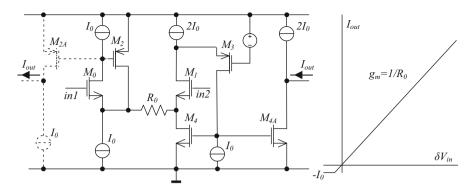

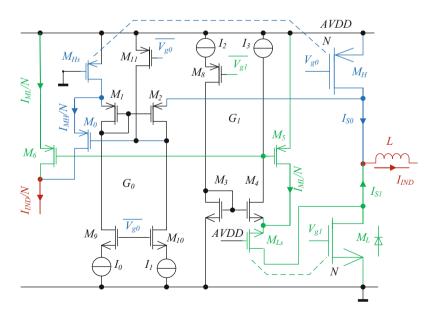

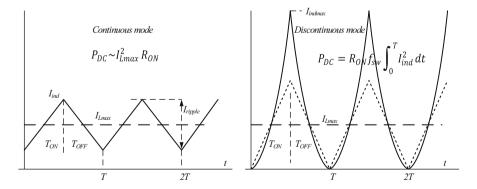

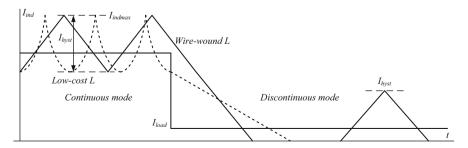

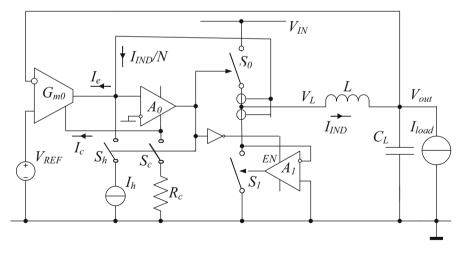

- 3. Good circuit is robust to the variation of the component parameters, process, and temperature.