# Chapter 181 Analytical Modeling and Simulation Study of Homo and Hetero III-V Semiconductor Based Tunnel Field Effect Transistor (TFET)

# M. Lakshmi Varshika, Rakhi Narang, Mridula Gupta and Manoj Saxena

**Abstract** High staggered, Moderate staggered and homo junction III–V semiconductor-based heterojunction TFETs are of interest as they allow a high on– off current ratio and high on current through reduction in the tunneling barrier height. GaAsSb/InGaAs based heterojunction p-n-i-n TFET has shown an increase in the drive current when compared to homojunction due to band engineering. Further engineering can be performed by varying tunneling barrier height ( $E_{beff}$ ) from 0.5 to 0.25 eV using differently staggered heterojunction. Thus, the concept of halo doped heterojunction pocket TFET is presented by analytical and simulation study with varying staggered junctions.

M. L. Varshika

R. Narang

M. Saxena (⊠) Department of Electronics, Deen Dayal Upadhyay College, University of Delhi, Sector-3 Dwarka, New Delhi 110078, India e-mail: saxena\_manoj77@yahoo.co.in

Department of Electrical and Electronics, Birla Institute of Technology and Science, Pilani 500078, Hyderabad, India e-mail: varshikaecono@gmail.com

Department of Electronics, Sri Venkateswara College, University of Delhi, Dhaula Kuan, New Delhi 110021, India e-mail: rakhinarang@gmail.com

M. Gupta Department of Electronic Science, University of Delhi, South Campus, Benito Juarez Road, New Delhi 110021, India e-mail: mridula@south.du.ac.in

<sup>©</sup> Springer Nature Switzerland AG 2019 R. K. Sharma and D. S. Rawal (eds.), *The Physics of Semiconductor Devices*, Springer Proceedings in Physics 215, https://doi.org/10.1007/978-3-319-97604-4\_181

#### 181.1 Introduction

In recent years, prolific research has accounted in incrementing the drain current of TFET and consequently designing a device providing sub threshold slope below the limits with similar performance as that of CMOS technology [1]. Introducing pocket layer in TFET or using hetero materials have shown a considerate improvement in performance than the conventional design. This paper aims at combining some of those techniques.

A p-n junction can be classified on the basis of bandgap, as High staggered hetero, Moderate staggered hetero and Homo junction. The use of these junctions in a TFET as source and channel materials exponents in reducing the tunneling barrier and subsequently increasing drain current [2, 3]. The halo doped pocket hetero junction TFET is the acme of possibility to include in band gap engineering without being utilitarian with materials. Introducing a pocket at the source end and to be able to further reduce the bandgap at the junction using barrier height variation would increment the drain current meteorically. The bandgap engineering performed using tunneling barrier height ( $E_{beff}$ ) variation from 0.5 to 0.25 eV is realized by varying the mole fraction of the materials in GaAsSb and InGaAs as source and drain respectively.

An analytical model that would be applicable to all the three structures as mentioned earlier, with halo doped pocket layer is developed and evaluated. The general approach developed objectively is utilized to generate potential, electric field and energy band profile respectively. The results are then compared with simulation [4–6] output and analyzed. The material parameters are given in Table 181.1.

|                              | Homo<br>junction                       | Moderate hetero<br>junction              | High hetero junction                    |

|------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|

| Source                       | In <sub>0.7</sub> Ga <sub>0.3</sub> As | GaAs <sub>0.4</sub> Sb <sub>0.6</sub>    | GaAs <sub>0.35</sub> Sb <sub>0.65</sub> |

| Pocket                       | In <sub>0.7</sub> Ga <sub>0.3</sub> As | In <sub>0.65</sub> Ga <sub>0.35</sub> As | In <sub>0.7</sub> Ga <sub>0.3</sub> As  |

| Channel and drain            | In <sub>0.7</sub> Ga <sub>0.3</sub> As | In <sub>0.65</sub> Ga <sub>0.35</sub> As | In <sub>0.7</sub> Ga <sub>0.3</sub> As  |

| Source doping concentration  | $5e+19 \text{ cm}^{-3}$                | $5e+19 \text{ cm}^{-3}$                  | $5e+19 \text{ cm}^{-3}$                 |

| Pocket doping concentration  | $1e+19 \text{ cm}^{-3}$                | $1e+19 \text{ cm}^{-3}$                  | $1e+19 \text{ cm}^{-3}$                 |

| Drain doping concentration   | $5e+19 \text{ cm}^{-3}$                | $5e+19 \text{ cm}^{-3}$                  | $5e+19 \text{ cm}^{-3}$                 |

| Electron affinity of channel | 4.63 eV                                | 4.63 eV                                  | 4.63 eV                                 |

| E <sub>beff</sub>            | 0                                      | 0.31 eV                                  | 0.25 eV                                 |

| $E_{\rm g}$ of source        | 0.58 eV                                | 0.69 eV                                  | 0.68 eV                                 |

| $E_{\rm g}$ of drain         | 0.58 eV                                | 0.74 eV                                  | 0.58 eV                                 |

Table 181.1 Device parameters of the architectures under study [3, 10, 11]

## 181.2 Analytical Model of 2D Halo Doped TFET

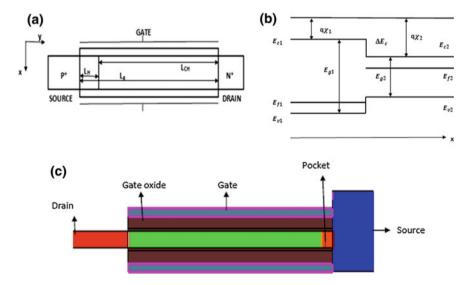

The two dimensional Poisson's Equation for the device shown in Fig. 181.1a, can be expressed as [7]

$$\frac{\partial^2 \varphi(x, y)}{\partial x^2} + \frac{\partial^2 \varphi(x, y)}{\partial y^2} = -\frac{qN}{\varepsilon_{\rm Si}}$$

(181.1)

where  $0 \le x \le t_{Si}$  and  $0 \le y \le L_g$ . The 2D potential,  $\varphi(x, y)$  can be denoted as  $\varphi_H$  and  $\varphi_{CH}$  in  $R_H$  and  $R_{CH}$  regions. *N* is the effective doping which is equal to  $-N_H$  and  $\pm N_{CH}$  respectively. With a parabolic distribution of potential along the *x* direction, [8]

$$\varphi_{\rm H}(x,y) = a_{\rm H}(y) + a_{\rm H1}(y)x + a_{\rm H2}(y)x^2 \tag{181.2}$$

$$\varphi_{\rm CH}(x, y) = a_{\rm CH}(y) + a_{\rm CH1}(y)x + a_{\rm CH2}(y)x^2$$

(181.3)

To ensure the continuity of potential and electric field, boundary conditions [12] are

$$\varphi_{\rm H}(0, y) = \varphi_{\rm H}(t_{\rm Si}, y) = \varphi_{\rm SH}(y)$$

(181.4)

**Fig. 181.1 a** Schematic cross sectional view of p-n-i-n TFET;  $L_g$  is the gate length,  $L_H$  pocket length = 6 nm,  $L_{ch}$  channel length = 150 nm,  $t_{si}$  is the channel thickness = 30 nm, **b** band diagram of hetero interface [9], **c** simulated structure of p-n-i-n TFET

$$E_{x-H}(0,y) = -\frac{d\varphi_{H}(x,y)}{dx}|_{x=0} = -\frac{(V_{g} - V_{fb}) - \varphi_{SH}(y)}{\frac{t_{Si}}{\eta}}$$

(181.5)

$$\frac{\mathrm{d}\varphi_{\mathrm{H}}(x,y)}{\mathrm{d}x}\Big|_{x=\frac{'\mathrm{Si}}{2}} = 0 \tag{181.6}$$

$$\varphi_{\rm CH}(0, y) = \varphi_{\rm CH}(t_{\rm Si}, y) = \varphi_{\rm SCH}(y)$$

(181.7)

$$E_{x-CH}(0,y) = -\frac{d\varphi_{CH}(x,y)}{dx}\Big|_{x=0} = -\frac{(V_g - V_{fb}) - \varphi_{SCH}(y)}{\frac{t_{Si}}{\eta}}$$

(181.8)

$$\frac{\mathrm{d}\varphi_{\mathrm{CH}}(x,y)}{\mathrm{d}x}|_{x=\frac{'\mathrm{Si}}{2}} = 0 \tag{181.9}$$

In the above equations  $\varphi_{\text{SH}}$  and  $\varphi_{\text{SCH}}$  are the surface potentials in pocket region  $R_{\text{H}}$  and channel region  $R_{\text{CH}}$  respectively [8].  $V_{\text{fb}}$  denotes the flat band voltage and  $\eta$  is the ratio of gate oxide capacitance and thin film capacitance. Solving for the parameters using the above boundary conditions yields

$$a_{\rm H/CH}(y) = \varphi_{\rm SH/SCH}(y) \tag{181.10}$$

$$a_{\rm H1/CH1}(y) = -\frac{\eta}{t_{\rm Si}} \left( V_{\rm g} - V_{\rm fb} - \varphi_{\rm SH/SCH}(y) \right)$$

(181.11)

$$a_{\rm H2/CH2}(y) = -\frac{\eta}{t_{\rm Si}^2} \left( V_{\rm g} - V_{\rm fb} - \varphi_{\rm SH/SCH}(y) \right)$$

(181.12)

$$\varphi_{\rm H}(x, L_{\rm H}) = \varphi_{\rm CH}(x, L_{\rm H}) \tag{181.13}$$

$$\frac{d\varphi_H(x,y)}{dy}|_{y=L_H} = \frac{d\varphi_{CH}(x,y)}{dy}|_{y=L_H}$$

(181.14)

By substituting  $\varphi_{\rm H}$  in the 2D Poisson's equation,

$$\ddot{\varphi}_{\rm SH}(y) - \alpha^2 \varphi_{\rm SH}(y) = \beta_{\rm H} \tag{181.15}$$

$$\ddot{\varphi}_{\rm SCH}(y) - \alpha^2 \varphi_{\rm SCH}(y) = \beta_{\rm CH}$$

(181.16)

where,  $\alpha = \sqrt{\frac{2\eta}{t_{Si}^2}}$ ,  $\beta_{CH} = -\frac{2\eta (V_g - V_{fb})}{t_{Si}^2} + \frac{qN_{CH}}{\epsilon_{Si}}$  Solving the above equations gives,

$$\varphi_{\rm SH}(y) = C_{\rm H1} e^{\alpha y} + C_{\rm H2} e^{-\alpha y} - \beta_{\rm H}/\alpha^2$$

(181.17)

$$\varphi_{\rm SCH}(y) = C_{\rm CH1} e^{\alpha y} + C_{\rm CH2} e^{-\alpha y} - \beta_{\rm CH} / \alpha^2$$

(181.18)

Boundary conditions for surface potential at source end,  $\varphi_{\rm SH}(0)$  and drain end,  $\varphi_{\rm SCH}(L_{\rm g})$  are

$$\varphi_{\rm SH}(0) = \frac{kT}{q} \ln\left(\frac{N_{\rm source}}{N_{\rm i}}\right) \tag{181.19}$$

$$\varphi_{\rm SCH}(L_{\rm g}) = \frac{kT}{q} \ln\left(\frac{N_{\rm dr}}{N_{\rm i}}\right) + V_{\rm ds}$$

(181.20)

$N_{\text{source}}$ ,  $N_{\text{dr}}$  and  $N_{\text{i}}$  are the doping concentrations of source, drain and the intrinsic concentration of the channel respectively.

Solving the above equations with given boundary conditions, parameters  $C_{\rm H1}, C_{\rm H2}, C_{\rm CH1}, C_{\rm CH2}$  are evaluated. Further

$$E_{x-H} = a_{H1}(y) + 2xa_{H2}(y)$$

(181.21)

$$E_{\rm y-H} = C_{\rm H1} \alpha e^{\alpha y} - C_{\rm H2} \alpha e^{-\alpha y}$$

(181.22)

$$E_{x-CH} = a_{CH1}(y) + 2xa_{CH2}(y)$$

(181.23)

$$E_{y-CH} = C_{CH1} \alpha e^{\alpha y} - C_{CH2} \alpha e^{-\alpha y}$$

(181.24)

would be the electric field expressions in the pocket and channel region respectively.

The effective bandgap for tunnelling can be decreased even further by using heterostructures [2]. Consider (semiconductor 1) p-n (semiconductor 2) junction with two different bandgap materials. Depending upon the difference between their electron affinities, the junction can be classified as in Fig. 181.2.

The drive current enhances on replacing an InGaAs homojunction TFET by a heterojunction InGaAs/GaAsSb. Further enhancement can be attained by engineering the effective tunneling barrier height  $E_{\text{beff}}$  from 0.58 to 0.25 eV. Moderate-stagger GaAs<sub>0.4</sub>Sb<sub>0.6</sub>/In<sub>0.65</sub>Ga<sub>0.35</sub>As and high stagger GaAs<sub>0.35</sub>Sb<sub>0.65</sub>/In<sub>0.7</sub>Ga<sub>0.3</sub>As hetero junction TFETs are considered, and their electrical results are compared with the In<sub>0.7</sub>Ga<sub>0.3</sub>As homojunction TFET ( $E_{\text{beff}} = 0.58 \text{ eV}$ ).

Also, boundary conditions for surface potential at source end,  $\varphi_{\rm SH}(0)$  and drain end,  $\varphi_{\rm SCH}(L_{\rm g})$  can be evaluated from the band diagram across the hetero junction at the source end as shown in Fig. 181.1b.

$$\varphi_{\rm SH}(0) = V_{\rm bi} = E_{\rm f2} - E_{\rm f1} \tag{181.25}$$

$$E_{\rm f2} - E_{\rm c2} = \frac{kT}{q} \ln\left(\frac{N_{\rm d}}{N_{\rm c2}}\right)$$

(181.26)

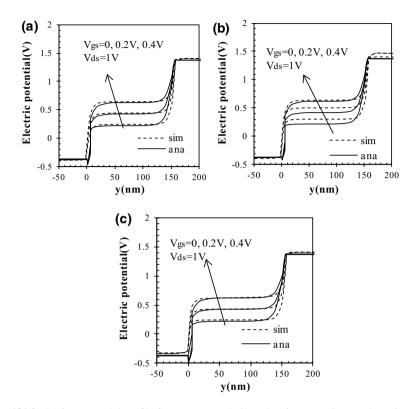

Fig. 181.2 Surface potential profile from source to drain region for **a**  $In_{0.7}Ga_{0.3}As$  homojunction TFET, **b** moderately staggered  $GaAs_{0.4}Sb_{0.6}/In_{0.65}Ga_{0.35}As$  hetero junction TFET, **c** high staggered  $GaAs_{0.35}Sb_{0.65}/In_{0.7}Ga_{0.3}As$

$$E_{\rm v1} - E_{\rm f1} = \frac{kT}{q} \ln\left(\frac{N_{\rm a}}{N_{\rm v1}}\right)$$

(181.27)

$$\Delta E_{\rm c} = \chi_2 - \chi_1 \tag{181.28}$$

$$\Delta E_{\rm c} + \Delta E_{\rm v} = \Delta E_{\rm g} \tag{181.29}$$

Thus,

$$\varphi_{\rm SH}(0) = E_{\rm g1} - \Delta E_{\rm c} + \frac{kT}{q} \ln\left(\frac{N_{\rm a}N_{\rm d}}{N_{\rm c2}N_{\rm v1}}\right) \tag{181.30}$$

$$\varphi_{\rm SCH}(L_{\rm g}) = \frac{kT}{q} \ln\left(\frac{N_{\rm dr}}{n_{\rm i}}\right) + V_{\rm ds} \tag{181.31}$$

where  $\chi_2, \chi_1$  are the electron affinity values of the source and the pocket,  $N_a$ ,  $N_d$ ,  $N_{c2}$ ,  $N_{v1}$  are the doping concentration in source, pocket and intrinsic concentration in source, pocket respectively. $N_{dr}$  is the doping concentration of the drain,  $E_{g1}$  the band energy of source and  $\Delta E_c$  is the conduction band offset. Thus, the parameters are

$$\begin{split} C_{\text{CH2}} &= \frac{1}{\left(e^{\alpha L_{\text{g}}} - e^{-\alpha L_{\text{g}}}\right)} \left[ \left(E_{\text{g1}} - \Delta E_{\text{c}} + \frac{kT}{q} \ln\left(\frac{N_{\text{a}}N_{\text{d}}}{N_{\text{c2}}N_{\text{v1}}}\right)\right) e^{\alpha L_{\text{g}}} - \frac{kT}{q} \ln\left(\frac{N_{\text{dr}}}{n_{\text{i}}}\right) \right. \\ &\left. - V_{\text{ds}} + \left(k1e^{\alpha L_{\text{g}}} - 1\right) \frac{\beta_{\text{CH}}}{\alpha^2} + (1 - k1)e^{\alpha L_{\text{g}}} \frac{\beta_{\text{H}}}{\alpha^2} \right] \\ C_{\text{CH1}} &= \frac{1}{\left(e^{\alpha L_{\text{g}}} - e^{-\alpha L_{\text{g}}}\right)} \left[ \left(E_{\text{g1}} - \Delta E_{\text{c}} + \frac{kT}{q} \ln\left(\frac{N_{\text{a}}N_{\text{d}}}{N_{\text{c2}}N_{\text{v1}}}\right)\right) e^{-\alpha L_{\text{g}}} + \frac{kT}{q} \ln\left(\frac{N_{\text{dr}}}{n_{\text{i}}}\right) \right. \\ &\left. + V_{\text{ds}} + \left(1 - k1e^{-\alpha L_{\text{g}}}\right) \frac{\beta_{\text{CH}}}{\alpha^2} - (1 - k1)e^{-\alpha L_{\text{g}}} \frac{\beta_{\text{H}}}{\alpha^2} \right] \end{split}$$

where,  $k1 = \frac{e^{\alpha L_{\rm H}} + e^{-\alpha L_{\rm H}}}{2}$

### 181.3 Results

A keen assay over the potential plots in Fig. 181.2 at three different  $V_{GS}$  in the pocket region of 0–6 nm the potential increase is essentially identical. The major point of concern is the tunnel region. Pocket purpose was to reduce the tunneling barrier [10], [13]. Further engineering of it is facilitated by hetero junction. However, it is desired that the engineering doesn't affect other parameters.

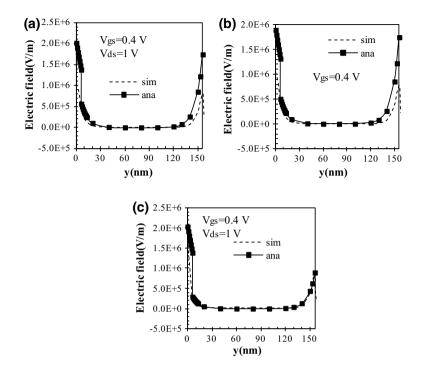

As it could be seen, irrespective of the band energies, the electric potential variation is similar. Also is the case for electric field for a value of  $V_{\rm gs}$  and  $V_{\rm ds}$  (Fig. 181.3). This proves to be advantageous for its application as supplant in conventional field.

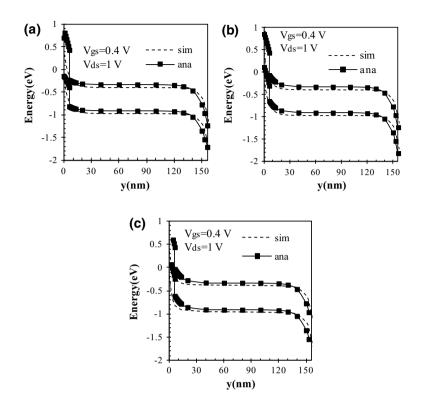

Similarly, supporting are the band energy plots in Fig. 181.4. The band bending in pocket region is higher in highly staggered and in homo junction has least. Band bending is observed at the pocket region. The transition from source to pocket and to the intrinsic channel region has a dip in band energy as in the figures above, near to the 0 nm.

More the band bending, narrower the junction and higher is the possibility of tunneling. High and moderate staggered hetero junction possesses greater steeper transition than that of homo junction. Thus, hetero junction would produce a better on-off current ratio. At commensurate potential hence, a hetero modeled device has promising performance characteristics.

**Fig. 181.3** Electric field profile for **a**  $In_{0.7}Ga_{0.3}As$  homojunction TFET, **b** moderately staggered GaAs<sub>0.4</sub>Sb<sub>0.6</sub>/In<sub>0.65</sub>Ga<sub>0.35</sub>As hetero junction TFET, **c** high staggered GaAs<sub>0.35</sub>Sb<sub>0.65</sub>/In<sub>0.7</sub>Ga<sub>0.3</sub>As

# 181.4 Conclusion

Due to the reduction in tunnel barrier height,  $E_{\text{beff}}$ , the GaAs<sub>0.35</sub>Sb<sub>0.65</sub>/In<sub>0.7</sub>Ga<sub>0.3</sub>As HTFET achieves enhancement in on current over the In<sub>0.7</sub>Ga<sub>0.3</sub>As homojunction TFET at  $V_{\text{DS}} = 1$  V. Mixed lattice-matched heterojunctions (GaAs<sub>1-x</sub>Sb<sub>x</sub>/In<sub>y</sub>Ga<sub>1-y</sub>As) provide a wide range of compositionally tunable  $E_{\text{beff}}$ . With increasing Sb and In compositions,  $E_{\text{beff}}$  can be reduced from 0.5 eV (x = 0.5, y = 0.53) to 0 eV (x = 0.1, y = 1), and hence, the TFET on current can approach the MOSFET level without compromising the steep switching and high on/off current property desirable in a low power logic switch.

**Fig. 181.4** Energy band profile for **a**  $In_{0.7}Ga_{0.3}As$  homojunction TFET, **b** moderately staggered  $GaAs_{0.4}Sb_{0.6}/In_{0.65}Ga_{0.35}As$  hetero junction TFET, **c** high staggered  $GaAs_{0.35}Sb_{0.65}/In_{0.7}Ga_{0.3}As$

Acknowledgements Authors would like to thank Council of Scientific & Industrial Research (CSIR), India (File No. 22(0724)/17/EMR-II).

M. L. Varshika (ENGS3150) would like to thank the Indian Academy of Sciences for providing the opportunity to be a part of SRFP-2017.

#### References

- U.E. Avci, D.H. Morris, I.A. Young, Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Devices Soc. 3(3), 88–95 (2015)

- D. Mohata, B. Rajamohanan, T. Mayer, M. Hudait, J. Fastenau, D. Lubyshev, A.W. Liu, S. Datta, Barrier-engineered arsenide-antimonide heterojunction tunnel FETs with enhanced drive current. IEEE Electron Device Lett. 33(11), 1568–1570 (2012)

- Y.C. Wu, J.H. Tsai, T.K. Chiang, C.C. Chiang, F.M. Wang, Comparative investigation of GaAsSb/InGaAs type-II and InP/InGaAs type-I doped–channel field–effect transistors. Semiconductors 49(2) (2015)

- 4. Sentaurus Users Manual (Synopsis, Inc., 2012)

- A. Biswas, S.S. Dan, C. LeRoyer, W. Grabinski, A.M. Ionescu, TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron. Eng. 98, 334–337 (2012)

- C. Kampen, A. Burenkov, J. Lorenz, Challenges in TCAD simulations of tunneling field effect transistors, in *Proceedings of Solid-State Device Research Conference (ESSDERC)*, pp. 139–142 (2011)

- 7. Y. Taur, J. Wu, J. Min, An analytic model for heterojunction tunnel FETs with exponential barrier. IEEE Trans. Electron Devices **62**(5), 1399–1404 (2015)

- B. Syamal, C. Bose, C.K. Sarkar, N. Mohankumar, Effect of single halo doped channel in tunnel FETs: a 2-D modeling study, in *Proceedings of IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC)*, pp. 1–4 (2010)

- D.K. Mohata, R. Bijesh, Y. Zhu, M.K. Hudait, R. Southwick, Z. Chbili, D. Gundlach, J. Suehle, J.M. Fastenau, D. Loubychev, A.K. Liu, Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction tunnel FETs with high drive current and high on-off ratio, in *VLSI Technology (VLSIT)*, pp. 53–54 (2012)

- D. Mohata, S. Mookerjea, A. Agrawal, Y. Li, T. Mayer, V. Narayanan, A. Liu, D. Loubychev, J. Fastenau, S. Datta, Experimental staggered-source and N+ pocket-doped channel III–V tunnel field-effect transistors and their scalabilities. Appl. Phys. Express 4(2) (2011)

- 11. D.K. Mohata, Arsenide-antimonide hetero-junction tunnel transistors for low power logic applications. Ph.D. Dissertation, The Pennsylvania State University (2013)

- 12. R. Narang, M. Saxena, R.S. Gupta, M. Gupta, Dielectric modulated tunnel field-effect transistor—a biomolecule sensor. IEEE Electron Device Lett. **33**(2), 266–268 (2012)

- 13. T.Y. Yu, L.S. Peng, C.W. Lin, Y.M. Hsin, GaAsSb/InGaAs tunnel field effect transistor with a pocket layer. Microelectr. Reliab. (2017)