María del Mar Gallardo Pedro Merino (Eds.)

# Model Checking Software

25th International Symposium, SPIN 2018 Malaga, Spain, June 20–22, 2018 Proceedings

## Lecture Notes in Computer Science

## 10869

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology Madras, Chennai, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7407

María del Mar Gallardo · Pedro Merino (Eds.)

## Model Checking Software

25th International Symposium, SPIN 2018 Malaga, Spain, June 20–22, 2018 Proceedings

*Editors* María del Mar Gallardo University of Málaga Málaga Spain

Pedro Merino University of Málaga Málaga Spain

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-94110-3 ISBN 978-3-319-94111-0 (eBook) https://doi.org/10.1007/978-3-319-94111-0

Library of Congress Control Number: 2018947326

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

© Springer International Publishing AG, part of Springer Nature 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### Preface

This volume contains the proceedings of the 25th International Symposium on Model Checking Software, SPIN 2018, held in Málaga, Spain, June 20–22, 2018. SPIN is a well-recognized periodic event started in 1995 around the model checking tool SPIN. Since 1995, the event has evolved and has been consolidated as a reference symposium in the area of formal methods related to model checking. The previous edition of the SPIN symposium took place in Santa Barbara (USA) with a record number of submissions and participants.

The SPIN 2018 edition requested regular papers, short papers, and tool demos in the following areas: formal verification techniques for automated analysis of software; formal analysis for modeling languages, such as UML/state charts; formal specification languages, temporal logic, design-by-contract; model checking, automated theorem proving, including SAT and SMT; verifying compilers; abstraction and symbolic execution techniques; static analysis and abstract interpretation; combination of verification techniques; modular and compositional verification techniques; verification of timed and probabilistic systems; automated testing using advanced analysis techniques; combination of static and dynamic analyses; derivation of specifications, test cases, or other useful material via formal analysis; case studies of interesting systems or with interesting results; engineering and implementation of software verification and analysis tools; formal methods education and training; and insightful surveys or historical accounts on topics of relevance to the symposium.

The symposium attracted 28 submissions, although two of them were rejected by the chairs because they were not within the scope of the symposium. Each of the remaining submissions was carefully reviewed by three Program Committee (PC) members. The selection process included further online discussion open to all PC members. Only the papers with positive global score were considered for acceptance. In addition, within these papers, only those with no objections from the PC members were accepted. As a result, 16 papers were selected for presentation at the symposium and publication in Springer's proceedings. The program consisted of 14 regular papers, one short paper, and a demo-tool paper.

In addition to the accepted papers, the symposium included one invited tutorial by Irina Mariuca Asavoae and Markus Roggenbach entitled "Software Model Checking for Mobile Security, Collusion Detection in K," and three invited talks: "Efficient Runtime Verification of First-Order Temporal Properties" by Klaus Havelund and Doron Peled, "Applying Formal Methods to Advanced Embedded Controllers" by Rémi Delmas, and "Program Verification with Separation Logic" by Radu Iosif.

We would like to thank all the authors that submitted papers, the Steering Committee, the PC, the additional reviewers, the invited speakers, the participants, and the

### VI Preface

local organizers for making SPIN 2018 a successful event. We also thank all the sponsors that provided logistics and financial support to make the symposium possible.

May 2018

María del Mar Gallardo Pedro Merino

## Organization

## **Steering Committee**

| Dragan Bosnacki (Chair) | Eindhoven University of Technology, The Netherlands |

|-------------------------|-----------------------------------------------------|

| Susanne Graf            | Verimag, France                                     |

| Gerard Holzmann         | Nimble Research, USA                                |

| Stefan Leue             | University of Konstanz, Germany                     |

| Neha Rungta             | Amazon Web Services, USA                            |

| Jaco Van de Pol         | University of Twente, The Netherlands               |

| Willem Visser           | Stellenbosch University, South Africa               |

|                         |                                                     |

## **Program Committee**

| María Alpuente         | Technical University of Valencia, Spain             |

|------------------------|-----------------------------------------------------|

| Irina Mariuca Asavoae  | Inria, France                                       |

| Dragan Bosnacki        | Eindhoven University of Technology, The Netherlands |

| Rance Cleaveland       | University of Maryland, USA                         |

| Stefan Edelkamp        | King's College London, UK                           |

| Hakan Erdogmus         | Carnegie Mellon, USA                                |

| María del Mar Gallardo | University of Málaga, Spain                         |

| (Chair)                |                                                     |

| Stefania Gnesi         | CNR, Italy                                          |

| Patrice Godefroid      | Microsoft Research, USA                             |

| Klaus Havelund         | NASA/Caltech Jet Propulsion Laboratory, USA         |

| Gerard Holzmann        | Nimble Research, USA                                |

| Radu Iosif             | Verimag, France                                     |

| Frédéric Lang          | Inria, France                                       |

| Kim Larsen             | Aalborg University, Denmark                         |

| Stefan Leue            | University of Konstanz, Germany                     |

| Alberto Lluch Lafuente | Technical University of Denmark, Denmark            |

| Pedro Merino (Chair)   | University of Málaga, Spain                         |

| Alice Miller           | University of Glasgow, UK                           |

| Corina Pasareanu       | CMU/NASA Ames, USA                                  |

| Charles Pecheur        | Université catholique de Louvain, Belgium           |

| Doron Peled            | Bar-Ilan University, Israel                         |

| Neha Rungta            | Amazon Web Services, USA                            |

| Antti Valmari          | University of Jyvskyl, Finland                      |

| Jaco Van de Pol        | University of Twente, The Netherlands               |

| Willem Visser          | Stellenbosch University, South Africa               |

| Farn Wang              | National Taiwan University, Taiwan                  |

|                        |                                                     |

### **Additional Reviewers**

Peter Aldous Mihail Asavoae Giovanni Bacci Georgiana Caltais Laura Carnevali Alessandro Fantechi Grigory Fedyukovich Martin Koelbl Florian Lorber Eric Mercer Marco Muniz Julia Sapiña Andrea Vandin

### **Organizing Committee**

| Carlos Canal           | University of Málaga, Spain |

|------------------------|-----------------------------|

| María del Mar Gallardo | University of Málaga, Spain |

| Pedro Merino           | University of Málaga, Spain |

| Laura Panizo           | University of Málaga, Spain |

### **Sponsors**

## **Abstracts of Invited Papers**

## Software Model Checking for Mobile Security – Collusion Detection in $\ensuremath{\mathbb{K}}$

Irina Măriuca Asăvoae<sup>1</sup>, Hoang Nga Nguyen<sup>2</sup>, and Markus Roggenbach<sup>1</sup>

<sup>1</sup> Swansea University, UK {I.M.Asavoae, M.Roggenbach}@swansea.ac.uk <sup>2</sup> Coventry University, UK Hoang.Nguyen@coventry.ac.uk

Abstract. Mobile devices pose a particular security risk because they hold personal details and have capabilities potentially exploitable for eavesdropping. The Android operating system is designed with a number of built-in security features such as application sandboxing and permission-based access control. Unfortunately, these restrictions can be bypassed, without the user noticing, by colluding apps whose combined permissions allow them to carry out attacks that neither app is able to execute by itself. In this paper, we develop a software model-checking approach within the  $\mathbb{K}$ -framework that is capable to detect collusion. This involves giving an abstract, formal semantics to Android applications and proving that the applied abstraction principles lead to a finite state space.

## Efficient Runtime Verification of First-Order Temporal Properties

Klaus Havelund<sup>1</sup> and Doron Peled<sup>2</sup>

<sup>1</sup> Jet Propulsion Laboratory, California Institute of Technology, USA <sup>2</sup> Department of Computer Science, Bar Ilan University, Israel

Abstract. Runtime verification allows monitoring the execution of a system against a temporal property, raising an alarm if the property is violated. In this paper we present a theory and system for runtime verification of a first-order past time linear temporal logic. The first-order nature of the logic allows a monitor to reason about events with data elements. While runtime verification of propositional temporal logic requires only a fixed amount of memory, the first-order variant has to deal with a number of data values potentially growing unbounded in the length of the execution trace. This requires special compactness considerations in order to allow checking very long executions. In previous work we presented an efficient use of BDDs for such first-order runtime verification, implemented in the tool DEJAVU. We first summarize this previous work. Subsequently, we look at the new problem of dynamically identifying when data observed in the past are no longer needed, allowing to reclaim the data elements used to represent them. We also study the problem of adding relations over data values. Finally, we present parts of the implementation, including a new concept of user defined property macros.

The research performed by the first author was carried out at Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. The research performed by the second author was partially funded by Israeli Science Foundation grant 2239/15: "Runtime Measuring and Checking of Cyber Physical Systems".

## A Sample of Formal Verification Research for Embedded Control Software at ONERA

Rémi Delmas, Thomas Loquen, and Pierre Roux

ONERA Centre de Toulouse, 2 av. Édouard Belin, 31055 Toulouse, France {Rémi Delmas, Thomas Loquen, Pierre Roux}@onera.fr

**Abstract.** This talk presents a sample of research work conducted by the French Aerospace Lab (ONERA) on tailoring and applying formal methods to advanced embedded controllers, at various phases of the development and verification process, illustrated by industrial projects and collaborations. A first line of work<sup>1</sup>, carried out in partnership with Airbus, Dassault and LAAS-CNRS, aims at going beyond simulation for validating advanced hybrid control laws, by leveraging bounded reachability analysis and robustness analysis from the early design phases. This requires to bridge the representation gap existing between hybrid dataflow formalisms used to model control laws (e.g. Simulink, Scade-Hybrid,...), and the automata-based formalisms used by most hybrid model-checkers (e.g. SpaceEx, Flow\*, dReach,...) and robustness analysis frameworks. We discuss the steps taken to handle the complexity and size of typical industrial models. A second line of work<sup>1</sup>, carried out jointly with academic lab LRI (Paris-Sud, INRIA) and technology provider OcamlPro, addresses the sound combination of SMT-solvers and potentially unsound convex optimization engines to allow proving complex polynomial invariants on advanced control laws implementations. Such implementations are usually obtained by automatic time-discretization and code generation from a hybrid dataflow model. The proposed approach shows a notable performance improvement on controllers of interest with respect to earlier approaches based on interval arithmetic or purely symbolic methods such as cylindrical algebraic decomposition or virtual substitutions. Last, we present research conducted<sup>2</sup> in partnership with Liebherr Aerospace Toulouse and technology provider Systerel on leveraging model-checking techniques for unit-level test case generation for an air management system, taking into account the industrial setting and qualification constraints, following DO-178C and DO-333 guidelines.

**Keywords:** Hybrid dataflow models • Hybrid automata • Reachability analysis SMT solvers • Convex optimization • SAT solvers • Test case generation

<sup>&</sup>lt;sup>1</sup> with funding from the French Civil Aviation Authority (DGAC) through the SEFA-IKKY program.

<sup>&</sup>lt;sup>2</sup> with funding from the CIFRE program of the National Technological Research Agency (ANRT) and the RAPID program of the French Government Defense Procurement and Technology Agency (DGA) (project SATRUCT).

### **Program Verification with Separation Logic**

#### Radu Iosif

CNRS/VERIMAG/Université Grenoble Alpes, Grenoble, France Radu.Iosif@univ-grenoble-alpes.fr

**Abstract.** Separation Logic is a framework for the development of modular program analyses for sequential, inter-procedural and concurrent programs. The first part of the paper introduces Separation Logic first from a historical, then from a program verification perspective. Because program verification eventually boils down to deciding logical queries such as the validity of verification conditions, the second part is dedicated to a survey of decision procedures for Separation Logic, that stem from either SMT, proof theory or automata theory. Incidentally we address issues related to decidability and computational complexity of such problems, in order to expose certain sources of intractability.

## Contents

### **Tutorial and Invited Papers**

| Software Model Checking for Mobile Security – Collusion Detection in $\mathbb{K}$<br><i>Irina Măriuca Asăvoae, Hoang Nga Nguyen, and Markus Roggenbach</i> | 3   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Efficient Runtime Verification of First-Order Temporal Properties                                                                                          | 26  |

| Program Verification with Separation Logic                                                                                                                 | 48  |

| Regular Papers                                                                                                                                             |     |

| Petri Net Reductions for Counting Markings<br>Bernard Berthomieu, Didier Le Botlan, and Silvano Dal Zilio                                                  | 65  |

| Improving Generalization in Software IC3<br>Tim Lange, Frederick Prinz, Martin R. Neuhäußer, Thomas Noll,<br>and Joost-Pieter Katoen                       | 85  |

| Star-Topology Decoupling in SPIN                                                                                                                           | 103 |

| Joint Forces for Memory Safety Checking                                                                                                                    | 115 |

| Model-Checking HyperLTL for Pushdown Systems                                                                                                               | 133 |

| A Branching Time Variant of CaRet<br>Jens Oliver Gutsfeld, Markus Müller-Olm, and Benedikt Nordhoff                                                        | 153 |

| Control Strategies for Off-Line Testing of Timed Systems<br>Léo Henry, Thierry Jéron, and Nicolas Markey                                                   | 171 |

| An Extension of TRIANGLE Testbed with Model-Based Testing<br>Laura Panizo, Almudena Díaz, and Bruno García                                                 | 190 |

| Local Data Race Freedom with Non-multi-copy Atomicity                                                                                                      | 196 |

| A Comparative Study of Decision Diagrams for Real-Time<br>Model Checking                                                                          | 216 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Omar Al-Bataineh, Mark Reynolds, and David Rosenblum                                                                                              | 210 |

| Lazy Reachability Checking for Timed Automata with Discrete Variables<br>Tamás Tóth and István Majzik                                             | 235 |

| From SysML to Model Checkers via Model Transformation<br>Martin Kölbl, Stefan Leue, and Hargurbir Singh                                           | 255 |

| Genetic Synthesis of Concurrent Code Using Model Checking<br>and Statistical Model Checking<br>Lei Bu, Doron Peled, Dachuan Shen, and Yuan Zhuang | 275 |

| Quantitative Model Checking for a Controller Design<br>YoungMin Kwon and Eunhee Kim                                                               | 292 |

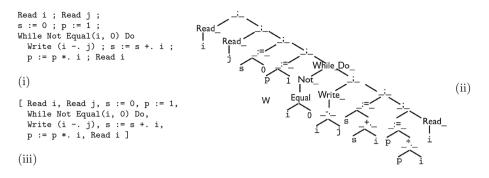

| Modelling Without a Modelling Language Antti Valmari and Vesa Lappalainen                                                                         | 308 |

| Context-Updates Analysis and Refinement in Chisel                                                                                                 | 328 |

| Author Index                                                                                                                                      | 347 |

## **Tutorial and Invited Papers**

## Software Model Checking for Mobile Security – Collusion Detection in $\mathbb{K}$

Irina Măriuca Asăvoae<sup>1</sup>, Hoang Nga Nguyen<sup>2</sup>, and Markus Roggenbach<sup>1(⊠)</sup>

Swansea University, Swansea, UK {I.M.Asavoae, M.Roggenbach}@swansea.ac.uk

<sup>2</sup> Coventry University, Coventry, UK Hoang.Nguyen@coventry.ac.uk

Abstract. Mobile devices pose a particular security risk because they hold personal details and have capabilities potentially exploitable for eavesdropping. The Android operating system is designed with a number of built-in security features such as application sandboxing and permission-based access control. Unfortunately, these restrictions can be bypassed, without the user noticing, by colluding apps whose combined permissions allow them to carry out attacks that neither app is able to execute by itself. In this paper, we develop a software model-checking approach within the K framework that is capable to detect collusion. This involves giving an abstract, formal semantics to Android applications and proving that the applied abstraction principles lead to a finite state space.

Keywords: Mobile-security  $\cdot$  Android  $\cdot$  Model-checking  $\cdot$  K-framework

### 1 Introduction

Mobile devices, such as smartphones and tablets are pervasive in modern everyday life. The number of smartphones in use is predicted to grow from 2.6 billion in 2016 to 6.1 billion in 2020 [24]. One reason for this fast adoption is the extensive ecosystem of apps which enable a wide range of functions. Consequently, smartphones hold a great deal of personal information (e.g., photos, financial data, credentials, messages, location history, health data) making them appealing targets for criminals who often employ malicious apps to steal sensitive information [23], extort users [20], or misuse the device services for their own purposes [29].

The Android operating system is designed with a number of built-in security features such as application sandboxing and permission-based access control. Unfortunately, these restrictions can be bypassed, without the user noticing, by colluding apps whose combined permissions allow them to carry out attacks that neither app is able to execute by itself. The possibility of app collusion was first described by Schlegel et al. in 2011 [34]. In 2016, Blasco et al. were the first to report on a discovery of collusion in the wild [11,12].

M. M. Gallardo and P. Merino (Eds.): SPIN 2018, LNCS 10869, pp. 3–25, 2018.

$https://doi.org/10.1007/978\text{-}3\text{-}319\text{-}94111\text{-}0\_1$

Attackers have a better chance of evading detection in both pre-deployment and after-deployment scenarios by using app collusion where the malicious activity is split across multiple apps and coordinated through inter-app communications. This kind of attack is possible because sandboxed systems, such as Android, are designed to prevent threats from individual apps. However, they do not restrict or monitor inter-app communications, and therefore they would fail to protect from multiple apps cooperating in order to achieve a malicious goal. Most malware analysis systems, such as antivirus software for smartphones, also check apps individually only.

Within the ACID project<sup>1</sup>, we have investigated the phenomenon of collusion with different approaches, including static analysis, machine learning, and software model-checking [5]. It soon became clear that an effective collusiondiscovery tool must include methods to isolate potential sets which require further examination. Here, we developed two different filtering methods: a rule based one [11], and one based on machine learning [19]. These filters, however, developed for a first, fast screening, report many false positives. In this paper, we report on a means for further investigation of sets identified by these filters. Objectives included (1) to reduce the number of false positives and (2) to provide evidence of collusion. In particular the second objective was important. Professional malware systems such as the one from our industrial partner McAfee are under permanent scrutiny: they are in constant legal battle to prove their claims that certain software is actually malware.

To perform such program reasoning, we could choose between methods like model checking, static analysis and dynamic analysis: all of these can be used to find program bugs, however are complementary in the way they handle the program(s) under investigation and the properties to verify. On the one hand, model checking and static analysis work with abstract models, without executing the program, while dynamic analysis directly executes the original program. In this sense, dynamic analysis discovers only real bugs, whereas both model checking and static analysis are sensitive to false bug reports. On the other hand, model checking and static analysis are more general techniques than dynamic analysis (which handles one path at a time) as they use abstract program models to (potentially) represent all the program executions. Model checking and static analysis mitigate precision and computation time using different strategies to handle abstractions. Model checking computes the run-time states of the program and could use, for example, local abstractions to verify its properties. Static analysis works on abstract programs which approximate the original program behaviors (i.e., using convenient abstract domains and abstract semantics). In general, model checking is more precise than static analysis, while being the more expensive approach.

In this paper, we use the  $\mathbb{K}$  framework [33] to give an abstract semantics to Android applications and demonstrate for the subset of non-recursive Android programs that our abstraction works and can effectively distinguish between

<sup>&</sup>lt;sup>1</sup> http://acidproject.org.uk.

collusion/non-collusion using a model-checking approach. Our discussion of collusion and model checking for collusion builds upon our prior publications [5,7,8].

**Related Work.** As detecting malware in single apps is well developed, it suggests itself to tackle collusion by merging apps into a single one [22]. There are also dynamic approaches. For instance, TrustDroid [14] classifies apps into logical domains (w.r.t. their data). Later, at run-time, any app communication between different domains is forbidden. In contrast, we analyse sets of apps by exhaustively unfolding their executions while looking for colluding patterns.

Static approaches to detecting collusion are closest to our work. The tool Epicc [28] reduces the collusion detection to an interprocedural data-flow environment problem that connects sources to sinks (e.g., sensitive data reads and message passing) but does not address app communication. The app communication pattern is analysed by a subsequent tool, IC3 [26], which employs a multi-valued constant propagation solver to produce an accurate string analysis for Intent evaluation (an intent is a special Android data structure that can be shared between different apps). The FUSE tool [30] integrates state-of-the-art pointer analysis of individual apps into building a multi-app information flow graph on which collusion can be detected. The tool FlowDroid [4] uses taint analysis to find connections between source and sink. The app inter-component communication pattern is subsequently analysed using a composite constant propagation technique [27]. We propose a similar approach, namely to track (sensitive) information flow and to detect app communication, but using model checking that gives a witness trace in case of collusion detection. From the proof effort perspective, we mention CompCert [21] that uses the Coq theorem prover to validate a C compiler.

The K framework was proposed in [33] as a formalism to facilitate the design and analysis of programming languages. A number of languages have already been defined in K, including C [18] and Java [13], facilitating their program analysis. We contribute to the pool of K-defined real languages by giving formal semantics to Android byte code. The K framework facilitates program analysis and verification from two angles: (1) using a Maude back-end [16] to access the existing infrastructure of the Maude system [15] and (2) building specialized tools over formal language definitions, e.g., a deductive verifier, which is generic in the language definition, based on matching logic [32]. Security properties in the K framework are explored by K-taint [3] with taint analysis. We use the Maude back-end for model checking the K specification of Android apps. To avoid the scalability issues of model checking, we specify in K an abstract semantics for Android apps and employ K to perform *abstract model checking* on Android apps for collusion.

### 2 Android Application and Smali

Android applications are packaged in apk files. Each consists of resources (e.g., image and sound files), binary code in dex files and a manifest (named Android-Manifest.xml) for essential information. The binary code is machine-readable

and can be executed by Dalvik Virtual Machine (DVM) prior to Android 5.0 or Android Runtime (ART) since Android 4.4. They can be converted into humanreadable format, *Smali*, by disassemblers such as *baksmali*. Note, that Smali code has a different semantics than Java bytecode, as Smali is executed on a register based machine, while Java bytecode operates on a stack based architecture. For the rest of this paper, we shall refer to the binary code as Smali code. Smali, similar to Java, is an Object-Oriented Programming (OOP) language. Here, we assume Smali programs to be correctly typed, as they are in general produced by a compiler rather than written manually.

The Smali code of an Android application consists of a set of classes. Essentially, each class is defined as a collection of fields and methods. A field is a variable defined by a name, a type and optionally an initial value. A method is a sequence of *bytecodes*, which will be referred to as Smali instructions hereinafter. Fields and methods can either be static or not. Static fields and methods belong to the class. In other words, all instances of the class share the same copy. Conversely, each instance has a distinct copy of non-static fields and methods.

Fields are identified by names and types. Types in Smali code are either primitive and reference. Primitive types are: V (void, only for return types), Z (boolean), B (byte), S (short), C (char), I (int, 32-bit), J (long, 64-bit), F (float, 32-bit) and D (double, 64-bit). References types are classes and arrays. Class types start with "L" while array types with "[". For example, the class *java.lang.Object* is written in Smali code as "Ljava/lang/Object"; an onedimensional array of 32-bit integers as "[I".

Methods are identified by names, parameter types and a return type. In contrast to Java, methods in Smali are register-based. Each method is associated with a number of registers which also serve as temporal variables when executed. The number of registers is declared first in the method body by a directive .register n or .local n where n is an integer. If the former is used, then the method has n registers in total; otherwise, it has n + m where m is the number of parameters. If a method has n registers, they are named  $v0, \ldots, v(n-1)$ . If it has m parameters  $(m \le n)$ , the last m registers, i.e.  $v(n-m), \ldots, v(n-m)$ 1), can also be referred to as  $p0, \ldots, p(m-1)$ . When calling a method, values of its parameters are copied into these last registers. The method body is a sequence of Smali instructions. They can be grouped into four categories: *invoke*return for calling and ending methods; control for un/conditional jumps; readwrite for accessing/modifying values stored in registers and memory (fields of instances); and *arithmetic* for arithmetic calculation. Further detail of these instructions can be found on [2]. Android comes with a Platform API which provides a set of predefined classes. Calls to API [1] can be made by invoke instructions. For example, to broadcast an intent (an abstract data structure holding descriptions, usually, of actions to be performed; hence, it can be used to exchange data between applications), an application invokes the API method sendBroadCast(Intent) defined in the class Context.

The potential entry points of an Android Application are defined by classes inheriting from the following ones: *Activity, Service, BroadcastReceiver* and ContentProvider from Android API. To become actual entry points, they must be explicitly declared in the manifest so that they can be instantiated and executed by either DVM or ART. Once instantiated, they are called App components. An activity component is an entry point that provides an interface between the application and users. For example, when a user clicks on the application icon, an activity component corresponding to the declaration in the manifest will be activated. A service component is an entry point to execute the application in the background. A broadcast receiver component is for processing events that are broadcast system-wide. Finally, a content provider component of an application serves requests for accessing and modifying its data from the applications it belongs to as well as other applications.

### 3 Collusion

ISO 27005 defines a threat as "A potential cause of an incident, that may result in harm of systems and organisations." For mobile devices, the range of such threats includes [35]:

- Information theft: without user consent information is sent outside the device boundaries;

- Money theft: e.g., when without user consent an app makes money through sensitive API calls (e.g. SMS); and

- Service or resource misuse: for example without user consent a device is remotely controlled.

The Android OS runs apps in sandboxes, trying to keep them separate from each other. However, at the same time Android provides communication channels between apps. These can be documented ones (overt channels), or undocumented ones (covert channels). An example of an overt channel would be a broadcast intent; an example of a covert channel would be volume manipulation (the volume is readable by all apps) in order to pass a message in a special code.

Broadly speaking, app collusion is when, in performing a threat, several apps are working together, i.e., they exchange information which they could not obtain on their own. Technically, we consider a threat to be a sequence of actions. Here, actions are operations provided by the Android API (such as record audio, access file, write file, send data, etc.).

**Definition 1 (Collusion).** A threat is realised by collusion if it is distributed over several apps, i.e., there is a set S consisting of at least two apps such that:

- each app in S contributes to the execution of at least one action of the threat,

- and each app in S communicates with at least one other app in S.

*Example 1 (Information theft collusion).* This can be illustrated with a contact app (having no Internet access) that reads the contacts database, passes the data to a weather app (having no access to the contact database), which then sends the data outside the device boundaries. For stealth purposes, the communication

between the apps is performed without any visibility to the user, e.g., through a broadcast intent. Such examples can easily be realised, see, e.g., the B.Sc. dissertation by Dicker [17].

*Example 2 (App Collaboration).* A similar situation to Example 1 is given by a picture app (having no Internet access), the user chooses a picture to be sent via email, the picture is passed over an overt Android channel to an email app, the email app (having no access to the picture database) sends the picture outside the device boundaries. For user-friendliness, the communication between the apps is performed without visibility to the user, e.g., through a shared file. This would be considered as collaboration, and not as collusion.

These two examples show that the distinction between collusion and collaboration actually lies in the notion of intention. The pattern in the sequence of actions is the same: one app reads information that Android protects with a permission, this information is passed to a different app, which then sends it outside the device boundaries (note that sending information off the device requires a permission in Android). In the case of the weather app, one can argue that the intent is malicious (as one might expect a weather app to have no need to deal with contact data in the first place); in the case of sending the email, one would expect the intent to be documented and visible to the user.

In this paper, we aim to analyse sequences of actions for patterns, thus leave out of our definition all aspects relating to psychology, sociology, documentation etc. Consequently, we speak about collusion potential.

For the rest of the paper, we will focus on the threat of information theft only. In this context, it is useful to introduce the concept of 'secret information'. Here, we take the pragmatic view that a secret is any information that Android protects with a permission.

**Definition 2** (Collusion potential for information theft). A set consisting of at least two apps has collusion potential for information theft, if

- there is an app reading a secret,

- there is communication among the apps on this secret such that

- another app sends data on this secret outside the device boundaries.

An app set with collusion potential would then require further, possibly manual analysis, involving taking into account further information such as the distribution methods, documentation, transparency to the user, in order to distinguish between collusion and collaboration. The possible automation of such analysis with the help of machine learning techniques is discussed in [6].

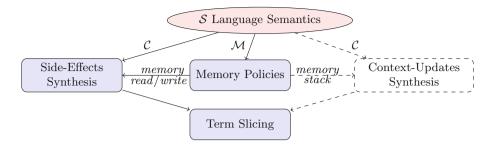

### 4 K Framework

The  $\mathbb{K}$  framework [31,33] proposes a methodology for the design and analysis of programming languages; the framework comes with a rewriting-based specification language and tool support for parsing, interpreting, model-checking and

deductive formal verification. The  $\mathbb{K}$  framework adheres to the principle that programming languages ought to have a formal syntax and semantics definition; and that all their execution and verification tools should be derived from a single, formal definition of this language. Consequently, the ideal work-flow in the  $\mathbb{K}$ framework starts with a formal and executable language syntax and semantics, given as a  $\mathbb{K}$  specification, which then is tested on program examples in order to gain confidence in the language definition. Here, the  $\mathbb{K}$  framework proposes model checking, via its compilation into Maude programs (i.e., using the existing reachability tool and LTL Maude model checker) or deductive verification using the matching logic prover - a first-order logic for reasoning with patterns and pattern matching on program structures.

A K specification consists of configurations, computations, and rules, using a specialised notation to write semantic entities, i.e., K-cells. For example, the K-cell representing the set of program variables as a mapping from identifiers Id to values Val is given by  $\langle Id \mapsto Val \rangle_{vars}$ . In the case of Android apps in their Smali format, the program states essentially consist of the instructions of the current method, method registers mapped to values, and the methods' call-stack. The configurations in K are labeled and nested K-cells, used to represent the program state structure. In other words, a programming language configuration is the set of all semantic entities which are necessary to represent the program states.

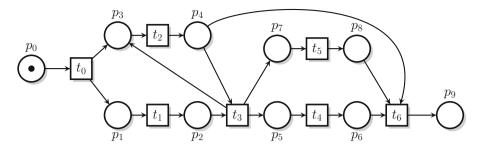

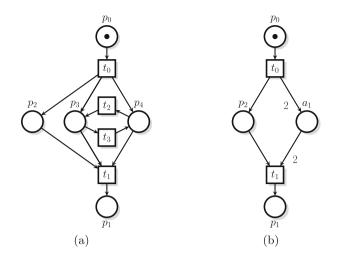

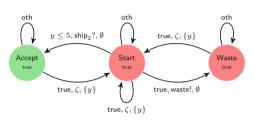

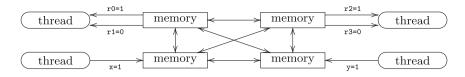

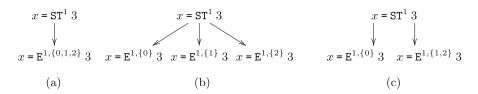

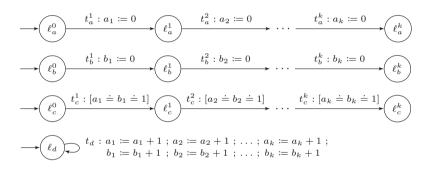

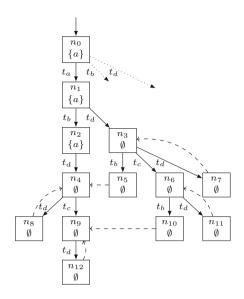

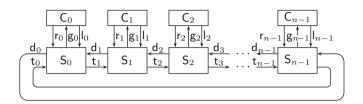

The rules in  $\mathbb{K}$  are of two types: computational and structural. Computational rules represent transitions in a program execution and are specified as configuration updates. Structural rules provide internal changes of the program state such that the configuration form can enable the application of computational rules. The computations in  $\mathbb{K}$  are configuration updates based on the  $\mathbb{K}$  rules; hence a computation represents an execution of the  $\mathbb{K}$  specification. Figure 1 depicts all the executions of a  $\mathbb{K}$  specification, i.e., its associated transition system. Note that inside the blue boxes we have various forms of the program configuration (cfg[pgm]), potentially transformed by the blue arrows depicting structural rules. The red arrows represent transitions between two boxes, which are achieved by the computational rules applied on the normal forms, e.g.,  $t_1 \ldots t_n$ , of the configuration in the box of origin. For example, the computational rule may be regarded as triggering the execution of an instruction while the structural rules prepare the configuration for the execution of the next instruction. More specifically, a computational rule triggers the execution of an instruction that adds the values of two registers/variables and deposits the result into a third one while a structural rule computes the addition of the two

**Fig. 1.** Transition system produced by a  $\mathbb{K}$  specification. (Color figure online)

values. In the rest of the paper we present the configuration, computations, and rules related to our Android  $\mathbb{K}$  specification.

### 5 Concrete Semantics

In this Section, we sketch a first model, a 'concrete semantics', of Android in  $\mathbb{K}$ . Based upon this concrete semantics, we will then, in Sects. 6 and 7, develop our abstract semantics, which will be suitable for model checking for security.

### 5.1 Instrumentation Principles

In order to enable the concrete semantics to discover information theft, we apply a number of instrumentation principles:

| Instrumentation Principle 1                                            |

|------------------------------------------------------------------------|

| We mark registers and objects by a Boolean flag that indicates if they |

| are holding sensitive information.                                     |

### Instrumentation Principle 2

We keep track of the names of those apps which contribute to the generation of the data held in a register or in an object.

For selected instructions, Examples 8 and 9 in Sect. 6 will demonstrate of how we realise these principles.

The Instrumentation Principles 1 and 2 allow us to discover collusion potential for information theft in an easy way. Whenever data is sent outside the device boundaries, we check if this data

- is sensitive and

- was produced with help from an app with a name different from the name of the app which is sending the data;

whenever both of these conditions are true, we have discovered an execution of several apps which leads to potential information theft.

In order to enable the concrete semantics to provide counter example traces leading to information theft, we apply a further instrumentation principles:

| Instrumentation Principle 3                                             |

|-------------------------------------------------------------------------|

| For each app, keep track of the instructions that have been carried out |

Section 8 will present an example of such a trace.

### 5.2 Configurations

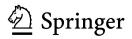

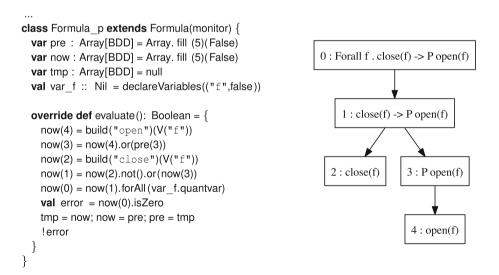

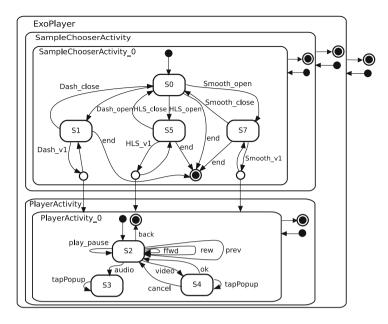

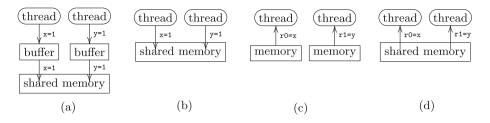

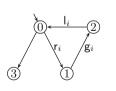

Applying the above three instrumentation principles, we capture Android concrete configurations using the cell mechanism of  $\mathbb{K}$  as depicted in Fig. 2 in the  $\mathbb{K}$  typical notation.

Each configuration contains a number of sandbox cells – one cell for each app belonging to a set of apps which one suspects of collusion. Each sandbox specifies the state of one app. It has a number of sub-cells: appname (string), activities (a list of *activity* class names declared in the manifest) and memory. Additionally, it also hosts zero or more class and thread cells.

A class cell specifies a class by the following sub-cells: classname, super (the name of the super class), interfaces (a list of interfaces that this class implements), fields (a list of fields optionally with initialised values) and zero or more method cells. Each method models a method of the class by three more sub-cells:

Fig. 2. Cell structure of Android concrete configurations in  $\mathbb{K}$ .

methodname (the signature of the method including name and parameter types), returntype and methodbody (list of instructions of the method).

A thread cell models a currently running thread by the following sub-cells: k (the remaining instructions to be executed), regs (content of registers), currentmethod (the complete instructions of the method that is currently executed in this thread; i.e., the instructions in k are a suffix of this instructions), result (holding the return value of a method running within this thread), callbacks (a queue of callback function to be called within this thread), stack (for saving the context of currently pending methods), and labeltrace (a record of which labels have been passed during the running of this thread, implementing Instrumentation Principle 3). The regs cell maps registers to a values.

A memory cell contains class objects that have been instantiated so far. It has an auxiliary cell, newref, to hold the reference for an object to be created next, and a number of object cells. Each contains five sub-cells: objectref, objecttype (its class name), objectfields (mapping from non-static fields to their values), sensitive (to indicate if any value stored in objectfields is sensitive) and created (a set of application names that contribute to the creation of any value objectfields).

Furthermore, a concrete configuration contains a single broadcasts cell. It is used to model Android API methods regarding broadcasting intents across applications. The broadcasts cell holds the intents that have been broadcast by the apps. Each broadcast intent is held in a separate cell comprised of action (action name), extra (a mapping from extra data names (strings) to extra data (strings)), isensitive (a flag indicating if the extra data are sensitive), icreated (a set of application names who contribute to the creation of any extra data), and recipients (a set of application names who have already received this intent).

### 6 Abstraction Principles Concerning Memory

Given a concrete configuration as described in Sect. 5, we capture its pointer structure in a so-called *memory graph*. In a second step, we enrich this memory graph with additional edges that capture data dependencies that could arise from code execution. We call this enrichment the *data dependency graph*. Our abstract semantics will then perform its computations on equivalence classes of the nodes of the data dependency graph.

As strings play an important role in Android inter app communications, we additionally define a *history projection* that allows us to keep track of the strings 'seen' by a register during program execution.

### 6.1 Memory Graph

#### Abstraction Principle 1

We abstract from the data held in the memory cell or in register cells by considering memory regions rather than values and/or pointers.

**Definition 3 (Memory graph, memory region).** Given the memory cell and all thread cells that belong to one sandbox S of a concrete configuration represented in  $\mathbb{K}$ , we define its memory graph to be the directed graph  $G_S = (V, E)$ , where

- the set of nodes V comprises of

- all object references to be found in the memory cell, and of

- all registers in the regs cell, the result cell, and all registers of the methods in the stack cell from each of the thread cells; and where

- there is an edge from a node v to a node w

- if v is a register and w is an object reference with v = (w, ..., ...), i.e., register cell v points to the object with reference w, or

- if v and w are both object references, and the object cell whose cell objectref is v has a cell objectfields with ⟨...,... → w,...⟩<sub>objectfields</sub>, i.e., the object with reference v contains an object field that points to the object with reference w.

A memory region is a connected component in the un-directed graph underlying the memory graph.

Memory regions form a partition of the set of nodes of the memory graph. Note that our definition of a memory region provides an over-approximation of the actual pointer structure, as we are ignoring the direction of the edges.

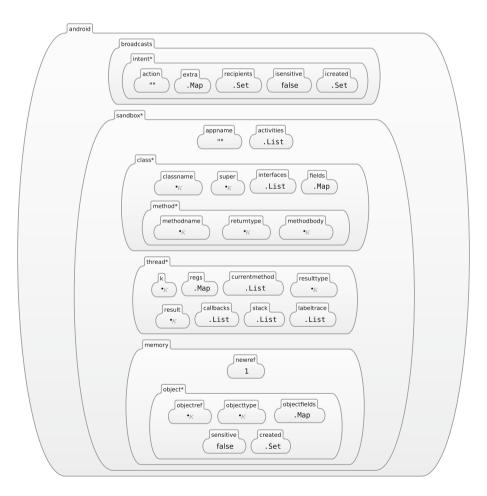

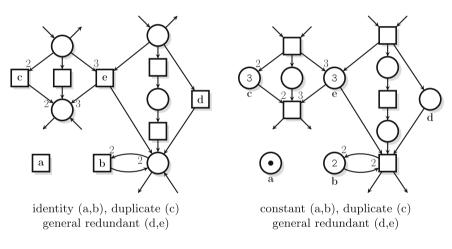

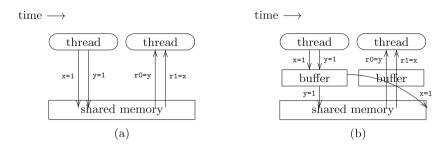

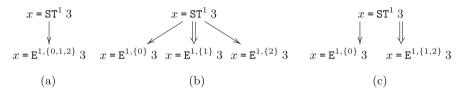

Fig. 3. A sample program in Smali and some of its memory graphs.

Example 3. Consider the Smali method onChange in Fig.3. The same Figure shows possible memory graphs concerning it. There is one *result* cell in the thread that executes it. The method has three registers  $r_1$ ,  $r_2$ , and  $r_3$ . After executing line 1 and 2 of the code, register  $r_1$  contains a pointer to a string object containing the string "GPS" and register  $r_3$  contains a pointer to an object containing a

secret "X", i.e., we have four memory regions, where we can choose, e.g., result,  $r_1$ ,  $r_2$ , and  $r_3$  as representatives. In the graph, we depict the sensitivity of data with "n" for non-sensitive and "s" for sensitive. Execution of line 3 leads to an edge from the object on the right to the object on the left, as myF is set to point to this object (iput assigns to the field myF in the object referenced in register r3 the reference found in register r1), i.e., we have now three memory regions, where we can choose, e.g., result,  $r_1$ , and  $r_2$  as representatives.

### 6.2 Data Dependency Graph

### Abstraction Principle 2

We abstract from computations by considering data dependencies rather than concrete values.

In order to undertake a further abstraction, for each instruction we perform a *data dependency* analysis among the arguments and result involved. We illustrate such an analysis first on the example of arithmetic binary operators *binop* in Smali, these include, e.g., the commands add, sub, mul.

Example 4 (Data dependency analysis of "binop  $r_1, r_2, r_3$ "). The meaning of these instructions is given by  $r_1 := r_2 binop r_3$ . After a binop instruction, the value of register  $r_1$  depends on the values of the registers  $r_2$  and  $r_3$ .

A slightly more involved situation is given when we move the result of a method call, which in Smali is stored in the special result register, into a normal register r.

Example 5 (Data dependency analysis of "move-result r"). The meaning of this instruction is given by r := result. After a move-result instruction, the value of register r depends on the values in the registers of the last method invocation. Assuming that this call was  $invoke\{r_1, r_2, ..., r_n\}m$  for an unimplemented method m, the value of r depends on the values of the registers  $r_1, r_2, ..., r_n - i.e.$ , we make a worst case assumption in order to be on the 'safe' side. The term 'unimplemented' means that we have no representation of this method in our K framework for Android. This can happen, e.g., when an app calls a method from a library for which we decide to leave it our from our analysis.

**Definition 4 (Data dependency graph, data dependency region).** A data dependency graph is a memory graph enriched by data dependency edges. A data dependency region is a connected component in the un-directed graph underlying the data dependency graph.

Data dependency regions form a partition of the set of nodes of the data dependency graph. Like in the definition of memory regions, in our definition of data dependency regions we over-approximate the actual information. For instance, in the case of the method invocation, we make a worst case assumption. Another reason of over-approximation is that, again, when forming the equivalence classes we ignore the direction of the edges.

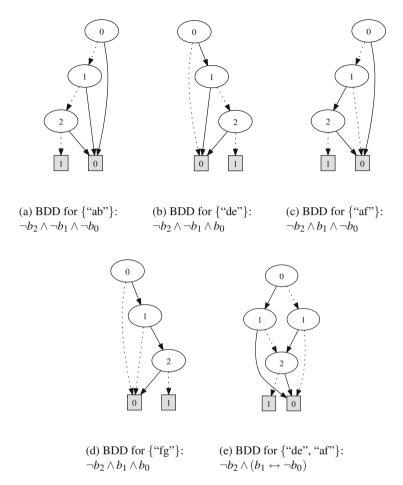

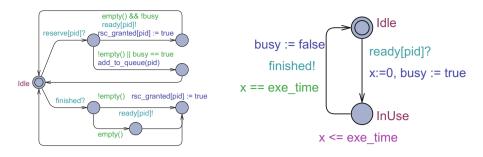

Fig. 4. Some data dependency graphs for the program in Fig. 3.

Example 6. Continuing Example 5, we consider some data dependency graphs for the Smali program of Fig. 3. After invoking the method getInfoSecret in line 5, the result cell depends on register  $r_3$  – indicated by the dashed arrow. On the implementation level, we realise such dependencies as edges in the memory graph, thus, the edge from result to the object that is referenced by  $r_3$ . I.e., we have three data dependency regions, where we can choose, e.g., result,  $r_1$ , and  $r_2$  as representatives. After moving the result into register  $r_2$ ,  $r_2$  inherits the data dependency of the result cell and the result cell is cleared of all data dependencies, i.e., we have three data dependency regions, where we can choose, e.g., result,  $r_1$  and  $r_2$  as representatives.

#### 6.3 History Projection

| Projection Principle                                                   |

|------------------------------------------------------------------------|

| We enrich data dependency regions by a set of strings in order to keep |

| track of 'values of interest'.                                         |

We add a history projection component to the data dependency regions so that we can detect Android communication channels for intents. For example, when sending the broadcast intent in the method **OnChange**, see Fig. 3, the communication channel carries the name "steal", given through the string object to which register  $r_1$  points – see the data dependency graph after executing line 6 in Fig. 4. An app that wants to receive this information, needs to 'listen' on broadcast channel "steal", i.e., in collusion analysis we need to have these strings available in order to see which senders and receivers match. For space reasons, we simplified the parameters of the broadcast method invocation in line 7.

**Definition 5 (History projection).** We annotate each data dependency region of a data dependency graph with a set of strings, which we call the history projection of this region.

The history projection of a region adds further information and thus makes the two previous abstractions finer grained. Like with data dependencies, each Smali instruction needs to be analysed in order to obtain the rules for history projection. The guiding principle is that the history projection collects all strings that have 'appeared' in the history of a region. Example 7 (History projection of "const-string r, s"). This instruction creates a new object containing the string s, and lets register r point to this object. In the data dependency graph, this instruction creates a new region consisting of the register r and the string object only. We annotate this region with the one element set  $\{s\}$  as its history projection.

We use the values collected in the history projection to perform an overapproximation of app communication. In our example program in Fig. 3, we say that the broadcast intent can use any of the strings that register  $r_1$  has in its history projection. We treat receiving a broadcast in a similar way. I.e., we form the intersection between the history projections of the registers involved: if the intersection is empty, the apps do not communicate, otherwise they do. For better results, one could utilize a composite constant propagation technique as discussed in, e.g., [27].

### 6.4 Sample Instructions in Abstract Semantics

With the two above abstraction principles, history projection, and the first two instrumentation principles of sensitivity updates and app-name updates as discussed in Sect. 5 on concrete semantics, we can give an abstract semantics in  $\mathbb{K}$  for nearly all Smali instructions. However, instructions that deal with the control flow that enable loops and recursive procedure calls, will require the application of further abstraction principles – see Sect. 7, which discusses loops.

Here, we give two concrete semantic rules. Registers in the abstract semantics hold enriched data dependency regions ddr, i.e., a symbolic name of the region, a boolean flag *sen* which is true if the region might contain sensitive information, a history projection h, and a set *apps* containing the names of applications that might have influenced the region.

Example 8 (Abstract semantics of of "binop A, B, C"). Let  $(ddr_x, h_x, sen_x, apps_x)$  be the contents of registers  $x, x \in \{A, B, C\}$  before execution of binop. Execution of binop creates a new region name new and updates all three registers A, B and C to the same values, namely to

- $ddr'_x = new,$

- $-h'_x = h_B \cup h_C,$

- $sen'_x = sen_B \lor sen_C$ , and

- $apps'_x = apps_B \cup apps_C$

for  $x \in \{A, B, C\}$ , i.e., *binop* creates a new region subsuming the regions to which the operands B and C were belonging. The new region considers again a worst case scenario by taking the union of the history projects and the app sets, and the logical or for sensitivity. Furthermore, all registers belonging to regions  $ddr_B$  and  $ddr_C$  need to be updated to the new region.

Note that the instruction  $invoke\{r_1, r_2, ..., r_n\}m$  in the abstract semantics behaves in a similar manner to Example 8, namely, the result cell is treated similarly to register A, while the method parameters  $r_1, r_2, ..., r_n$  are treated in a similar way to registers B and C.

Example 9 (Abstract semantics of "move-result r"). Assume that this instruction is executed by an app with name n. Let  $(ddr_{res}, h_{res}, sen_{res}, apps_{res})$  be the contents of the result cell before execution of move-result. Execution of moveresult updates the result cell and register r as follows:

$$- ddr'_{res} = .K \qquad - ddr'_{res} = ddr_{res} - h'_{r} = h_{res}, - sen'_{r} = sen_{res}, \text{ and} - apps'_{r} = apps_{res};$$

i.e., the result cell is marked as empty with the special value K and register r simply holds all values that were held before in the result cell.

#### 6.5 A Theoretical Result on These Abstractions

We conclude by giving an upper bound to the abstract state space:

**Theorem 1 (Abstract state space).** When applying these two abstractions as well as instrumentation for sensitivity and app names, the upper bound for the size of the abstract state space is double exponential in the number of registers of methods either active or on the stacks in the thread cells.

**Proof** (Sketch): History projection picks up constants from the program during execution, there are only finitely many constants in the program. Sensitivity is a Boolean value. The data dependency graph forms a partition of the finitely many available registers. There are double exponentially many partitions possible.

Note that the abstract state space grows and shrinks during the execution of an app, depending on how many threads it has, the number of active registers, and the size of the stacks in these threads.

### 7 Selected Abstraction Principles Concerning Execution

In this Section we focus on guiding abstract execution by model checking principles. In  $\mathbb{K}$  we use the search engine, which exhaustively executes the semantics until it either reaches a colluding state or all executions were unfolded without a collusion found. However, during the process of unfolding all possible executions of the semantics, the search engine does not use any model checking techniques. Hence, we have to insert model checking principles into the abstract semantics that, in the context of a finite state space, make program executions finite.

We apply these abstraction principles when defining the abstract semantics of backward jumps, in the case of loops, and method invocation, in the case of recursive calls. Here we present the case of backward jumps only. To recursive calls, one can apply similar principles through utilising a call stack.

```

method onReceive (Context, Intent)

registers 3

code

1:

invoke {r3} getExtras

move-result r1

2:

3:

whileloop

if-eqz r1, exitloop

4:

iget r3, r2, next

5:

iget r2, r1, next

6:

7:

iget r1, r3, next

jump whileloop

8:

9:

exitloop

10: invoke {r3} publish

11: return void

endmethod

```

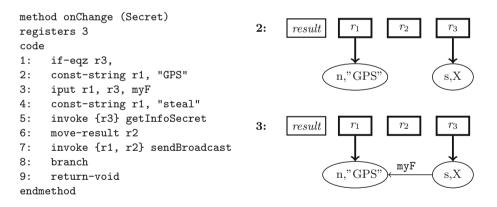

Fig. 5. A Smali method with a while loop.

Example 10 (Execution of loops). Consider the onReceive method shown in Fig. 5. The method onReceive is activated whenever a message fitting the Intent parameter of the method arrives in the system. The onReceive method extracts the details of the received message (by invocation of the getExtras API method in line 1) and deposits these details in the local register r1. Lines 3–8 describe a loop, where line 3 is the label whileloop marking the beginning of the loop. Line 4 contains the loop condition, i.e., when the register r1 contains the null reference, the loop execution stops and the computation continues from the exitloop label in line 9. The loop body passes information in a round-robin from r2 to r3 (in line 5), from r1 to r2 (in line 6), and r3 to r1 (in line 7). Note that we assume that the information passed is available via the field next of the objects referenced by the register r1 r3 is sent outside the device via the invocation of the publish method.

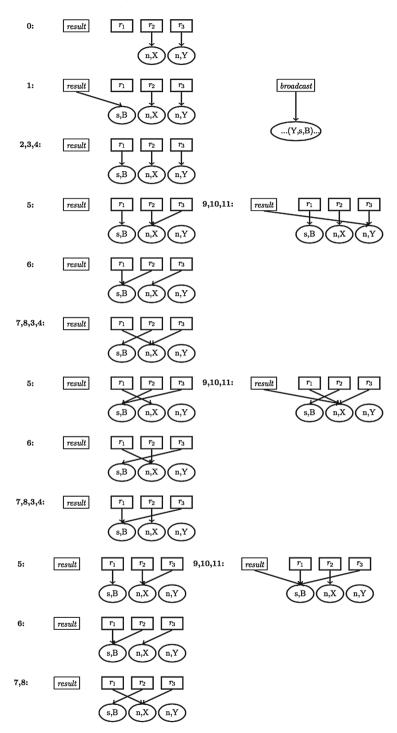

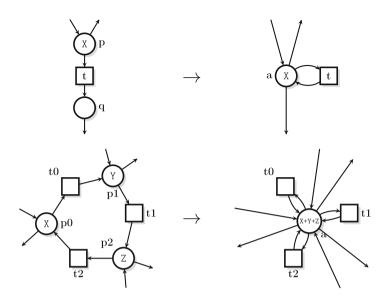

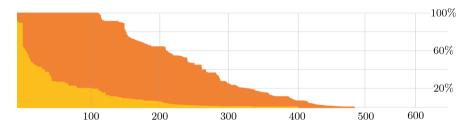

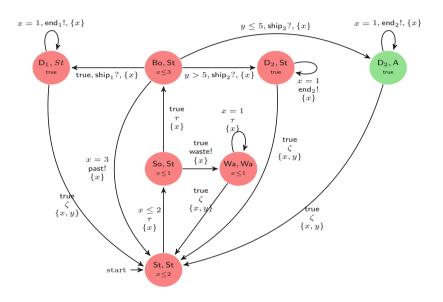

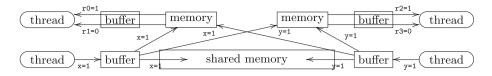

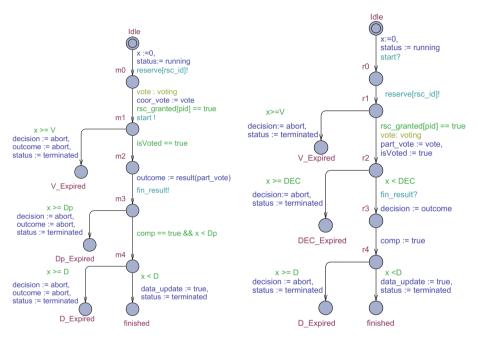

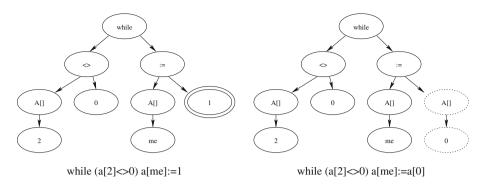

Figure 6 depicts the data dependency graphs of some of its executions and a representation of the broadcast cell. The condition in line 4 of onReceive can evaluate either to true or false: in case it is false, we enter the loop, i.e., we continue execution in line 5; in case it is true, we leave the loop, i.e., we continue execution in line 9. The left column of Fig. 6 shows the data dependency graphs when in the execution of onReceive the condition is always false. The right column shows the data dependency graphs for never entering the loop, for exiting the loop after one iteration, and for exiting the loop after two iterations.

Our example is artificial in the sense that 'normally' one would not expect a field next in the objects in the API classes Context and Intent (referenced in the beginning of the method by the registers r2 and r3, respectively). However, it is 'typical' in the sense that intents are usually read using loop constructs. For brevity, we decided to skip the 'typical' lines before the loop that prepare registers r2 and r3 to contain objects with a next field, i.e., lists.

Fig. 6. Abstract loop execution using onReceive code.

Our Abstraction Principle for Loops is based on the lasso principle in model checking [10]:

| Abstraction Principle for Loops                                       |

|-----------------------------------------------------------------------|

| Stop loop execution at a backward jump point when abstract states are |

| repeated.                                                             |

*Example 11 (Repetition of abstract states).* We observe the register contents when executing the backward jump in line 8 of the method onReceive, c.f. Fig. 5. The relevant data dependency graphs are shown in Fig. 6. Here we obtain the sequence

$$13_n \mid 2_s \longrightarrow 13_s \mid 2_n \longrightarrow 13_n \mid 2_s,$$

where the numbers stand for registers, the vertical bar divides partitions, and the indices n and s stands of non-sensitive and sensitive, resp, i.e.,  $13_n \mid 2_s$  says that  $r_1$  and  $r_3$  belong to the same partition of the data dependency graph which holds non-sensitive information, while register  $r_2$  forms a partition of its own which holds sensitive information. Applying the above Abstraction Principle for Loops means that execution is stopped at the third loop iteration since all abstract states that can occur within this loop have already been passed through during the first two iterations.

We have analysed our loop example applying a standard approach of static analysis [25]:

Example 12 (Comparison with static analysis). By comparison, an execution using static analysis principles is bound to join the abstract states collected at the level of backward jumps. In our example, where we start the the loop in the abstract state  $1_s \mid 2_n \mid 3_n$ , we have the following sequence at the level of the backward jump:  $13_s \mid 2_s \longrightarrow 13_s \mid 2_s$ .

We observe that in this example static analysis performs a smaller number of loop iterations than our model checking approach. However, this comes at the price of less precision. For example, as seen in Fig. 6, registers 1 and 2 are never sensitive at the same time. If later in the computation this fact becomes important (e.g., for passing sensitive data that leads to collusion) then static analysis reports a false positive for collusion while our model checking approach safely reports no-collusion. Further discussion on this topic can be found in [9].

We conclude this Section by some theoretical results that demonstrate that our abstractions provide us with a finite state space that – at least from a theoretical point of view – can be explored by model-checking.

**Theorem 2** (Methods have a finite state space in abstract). The number of partitions of the registers of a method enriched with sensitivity information, app information, and history information, is always finite. **Proof:** This result holds as a method always has only finitely many registers, sensitivity is a Boolean value, the app sets considered are always finite, and the number of string constants in a program is finite as well.

**Corollary 1 (Loops are finite in abstract).** Application of the Abstraction Principle for Loops leads to finite loop executions.

**Corollary 2** (Abstract state space is finite). The abstractions together result in a finite state space for the abstract semantics, which can be investigated via model-checking.

**Proof** (Sketch): We are considering non-recursive apps only. Thanks to Corollary 1, we have only executions of finite length in abstract. A finite execution has only finitely many branches, can start only finitely many threads, and leads to finite stacks only. Thus, by Theorem 1, the abstract state space is finite.

### 8 First Experimental Results

We demonstrate how collusion is detected using our concrete and our abstract semantics on two Android applications, called LocSender and LocReceiver. Together, these two apps jointly carry out an "information theft". They consist of about 100 lines of Java code/3000 lines of Smali code each. Originally written to explore if collusion was actually possible (there is no APK of the Soundcomber example), here they serve as a first test if our model checking approach works.

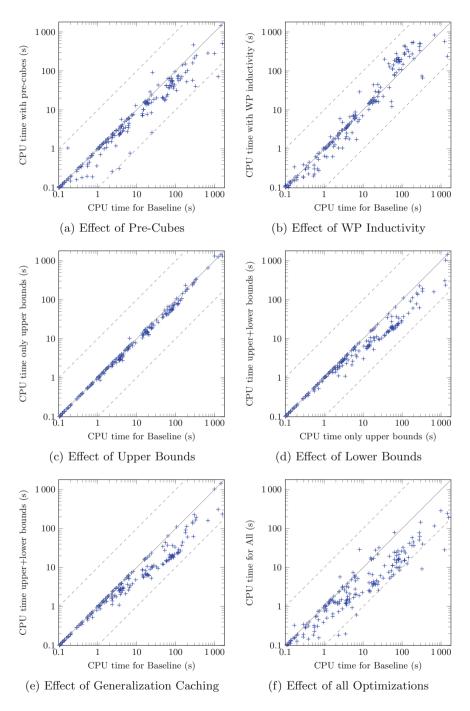

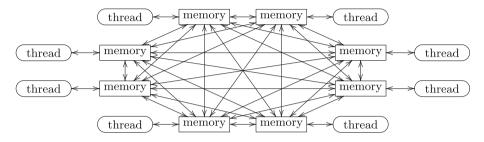

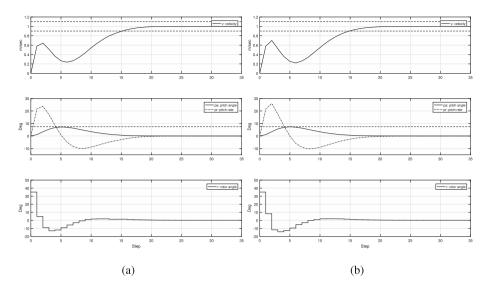

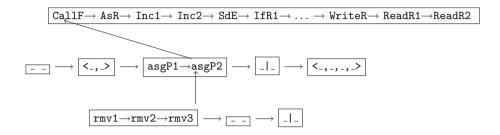

LocSender obtains the location of the Android device and communicates it using a broadcast intent. LocReceiver constantly waits for such a broadcast. On receiving such message, it extracts the location information and finally sends it to the Internet as an HTTP request. We have two variants of LocReceiver: one contains a while loop pre-processing the HTTP request while the other does not. Additionally, we create two further versions of each LocReceiver variant where collusion is broken by (1) not sending the HTTP request at the end, (2) altering the name of the intent that it waits for – named LocReceiver1 and LocReceiver2, respectively. Furthermore, we (3) create a LocSender1 which sends a non-sensitive piece of information rather than the location. In total, we will have eight experiments where the two firsts have a collusion while the six lasts do not<sup>2</sup>. Figure 7 summarises the experimental results. When collusion is detected, our implementation provides an output to trace the execution of both colluding apps. For example, the abstract implementation yields the following traces for the first experiment from Fig. 7:

LocSender: "0" -> "68" -> "70" -> "71" -> "73" -> "75" -> "77" -> "79" -> "81" -> "83" -> "85" -> "86" -> "88" -> "cond\_54".

<sup>&</sup>lt;sup>2</sup> All experiments are carried out on a Macbook Pro with an Intel i7 2.2 GHz quad-core processor and 16 GB of memory.

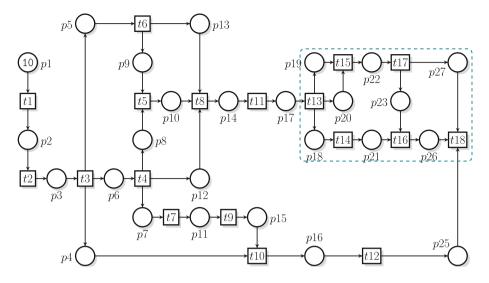

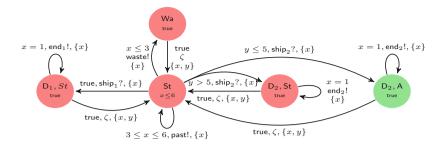

| App1       | App2         | Loop         | Collusion    | Concrete |          | Abstract |              |

|------------|--------------|--------------|--------------|----------|----------|----------|--------------|

|            |              |              |              | Runtime  | Detected | Runtime  | Detected     |

| LocSender  | LocReceiver  |              | $\checkmark$ | 55s      |          | 30s      |              |

| LocSender  | LocReceiver  | $\checkmark$ | $\checkmark$ | time-out |          | 33s      | $\checkmark$ |

| LocSender  | LocReceiver1 |              |              | 1m13s    |          | 31.984s  |              |

| LocSender  | LocReceiver1 | $\checkmark$ |              | time-out |          | 34s      |              |

| LocSender  | LocReceiver2 |              |              | 53s      |          | 32s      |              |

| LocSender  | LocReceiver2 | $\checkmark$ |              | time-out |          | 33s      |              |

| LocSender1 | LocReceiver  |              |              | 1m11s    |          | 32s      |              |

| LocSender1 | LocReceiver  | $\checkmark$ |              | time-out |          | 34s      |              |

Fig. 7. Experimental result.

```

LocReceiver: "0" -> "44" -> "46" -> "48" -> "0" -> "69" -> "71"

-> "72" -> "74" -> "75" -> "77" -> "goto_14" -> "78" -> "79"

-> "goto_14" -> "cond_23" -> "84" -> "85" -> "86" -> "87" ->

"89" -> "try_start_44" -> "90" -> "91" -> "92" -> "93" ->

"try_end_69" -> "100" -> "goto_69" -> "49" -> "52" -> "53"

-> "56" -> "57" -> "58".

```

In these traces, labels in Smali code are recorded as they were traversed during the colluded execution. Therefore, it can be used to evidence collusion in the Smali code.

**Evaluation:** Our experiments indicate that our approach works correctly: if there is collusion it is either detected or has a timeout, if there is no collusion then none is detected. In case of detection, we obtain a trace providing evidence of a run leading to information theft. The experiments further demonstrate the need for an abstract semantics, beyond the obvious argument of speed: e.g., in case of a loop where the number of iterations depends on an environmental parameter that can't be determined, the concrete semantics yields a time out, while the abstract semantics still is able to produce a result. Model checking with the abstract semantics is about twice as fast as with the concrete semantics. At least for such small examples, our approach appears to be feasible.

## 9 Summary and Future Work

In this paper, we have presented a model-checking approach that is capable to discover the threat of app-collusion. To this end, we gave a formal definition of collusion and briefly discussed that it is often a challenge to distinguish between benign and malicious behavior. Formal methods alone are not capable to distinguish between malign collusion and benign collaboration as they need a reference point, a definition of what a program's behavior should be. As such reference points are lacking in the context of mobile apps, the classification that a certain behavior is malicious remains in the end a decision to be made by humans. Towards model-checking for collusion potential, we presented an abstract semantics of Smali within the  $\mathbb{K}$  framework. As a theoretical result we proved that our abstractions lead to a finite state space (for non-recursive apps). On the practical side, we demonstrated that our abstract semantics can effectively detect collusion potential for information theft. Together with our other work within the ACID project, this results in a tool chain for dealing with app collusion:

- First, one isolates sets of apps with high collusion risk this can be done with some filter mechanism, e.g., the rule based one [11] or the machine learning based one [19].

- These app sets then need to be investigated further, where it is essential to provide evidence for collusion potential – this is, where our model-checking approach from this paper comes into play.

- Finally, there needs to be a decision if the combined effort of the apps is collusion or collaboration – as discussed above, this needs to be carried out manually, in the future possibly supported by machine learning [6].

In terms of future work for our approach, we plan to work out the formal details of how to treat recursion and, in particular, expand our work on information theft to other forms of collusion by developing further instrumentation principles. Furthermore, we want to address the question of scalability, in particular of how to solve the combinatorial explosion of n colluding apps with BigData search methods.

For the topic in general, one should note that app collusion is not restricted to Android OS. In principle, it is also a vulnerability of other mobile platforms as well as cloud environments. In the context of the Internet of Things (IoT), malware experts see collusion between devices as 'threat of the future': with increasingly more powerful analysis methods to protect devices against attacks performed by a single program only, criminals might be forced to move to collusion attacks, though these are technically more involved.

Yet another perspective is that model-checking might develop into a third, established technique for malware discovery and analysis, besides static analysis and dynamic analysis.

Acknowledgments. We would like to thank our colleagues and friends Magne Haveraaen, Alexander Knapp, and Bernd-Holger Schlingloff who commented on early drafts and helped us shape this paper; a special thanks goes to Erwin R. Catesbeijana (Jr.) for pointing out that not all inter app communication leads to collusion.

### References

- Android API reference. https://developer.android.com/reference/classes. Accessed 01 May 2018

- Android bytecode. https://source.android.com/devices/tech/dalvik/dalvikbytecode. Accessed 01 May 2018

- Alam, M.I., Halder, R., Goswami, H., Pinto, J.S.: K-taint: an executable rewriting logic semantics for taint analysis in the k-framework. In: ENASE, pp. 359–366. SciTePress (2018)

- Arzt, S., Rasthofer, S., Fritz, C., Bodden, E., Bartel, A., Klein, J., Traon, Y.L., Octeau, D., McDaniel, P.: FlowDroid: precise context, flow, field, object-sensitive and lifecycle-aware taint analysis for android apps. In: PLDI 2014, p. 29. ACM (2014)

- Asavoae, I.M., Blasco, J., Chen, T.M., Kalutarage, H.K., Muttik, I., Nguyen, H.N., Roggenbach, M., Shaikh, S.A.: Detecting malicious collusion between mobile software applications: the Android<sup>TM</sup> case. In: Carrascosa, I.P., Kalutarage, H.K., Huang, Y. (eds.) Data Analytics and Decision Support for Cybersecurity. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-59439-2\_3

- Asavoae, I.M., Blasco, J., Chen, T.M., Kalutarage, H.K., Muttik, I., Nguyen, H.N., Roggenbach, M., Shaikh, S.A.: Distinguishing between malicious app collusion and benign app collaboration: a machine learning approach. Virus Bulletin (2018)

- Asavoae, I.M., Nguyen, H.N., Roggenbach, M., Shaikh, S.A.: Utilising K semantics for collusion detection in Android applications. In: ter Beek, M.H., Gnesi, S., Knapp, A. (eds.) FMICS-AVoCS 2016, pp. 142–149 (2016)

- Asavoae, I.M., Nguyen, H.N., Roggenbach, M., Shaikh, S.A.: Software model checking: a promising approach to verify mobile app security. CoRR abs/1706.04741 (2017). http://arxiv.org/abs/1706.04741

- Beyer, D., Gulwani, S., Schmidt, D.: Combining model checking and data-flow analysis. In: Clarke, E.M., Henzinger, T.A., Veith, H. (eds.) Handbook on Model Checking. Springer, Cham (2018). https://doi.org/10.1007/978-3-319-10575-8\_16

- Biere, A., Cimatti, A., Clarke, E., Zhu, Y.: Symbolic model checking without BDDs. In: Cleaveland, W.R. (ed.) TACAS 1999. LNCS, vol. 1579, pp. 193–207. Springer, Heidelberg (1999). https://doi.org/10.1007/3-540-49059-0\_14

- Blasco, J., Chen, T.M., Muttik, I., Roggenbach, M.: Detection of app collusion potential using logic programming. J. Netw. Comput. Appl. 105, 88–104 (2018). https://doi.org/10.1016/j.jnca.2017.12.008

- Blasco, J., Muttik, I., Roggenbach, M.: Wild android collusions (2016). https:// www.virusbulletin.com/conference/vb2016/

- Bogdănaş, D., Roşu, G.: K-Java: a complete semantics of Java. In: POPL 2015. ACM (2015)

- 14. Bugiel, S., Davi, L., Dmitrienko, A., Heuser, S., Sadeghi, A.R., Shastry, B.: Practical and lightweight domain isolation on Android. In: SPSM 2011. ACM (2011)

- Clavel, M., Durán, F., Eker, S., Lincoln, P., Martí-Oliet, N., Meseguer, J., Talcott, C.: All About Maude - A High-Performance Logical Framework. LNCS, vol. 4350. Springer, Heidelberg (2007). https://doi.org/10.1007/978-3-540-71999-1

- Şerbănuţă, T.F., Roşu, G.: K-Maude: a rewriting based tool for semantics of programming languages. In: Ölveczky, P.C. (ed.) WRLA 2010. LNCS, vol. 6381, pp. 104–122. Springer, Heidelberg (2010). https://doi.org/10.1007/978-3-642-16310-4\_8

- 17. Dicker, C.: Android security: delusion to collusion. B.Sc. dissertation, Swansea University (2015)

- Hathhorn, C., Ellison, C., Roşu, G.: Defining the undefinedness of C. In: PLDI 2015. ACM (2015)

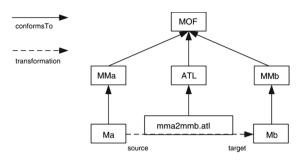

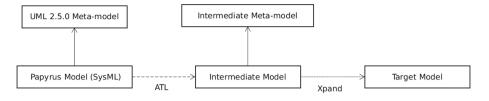

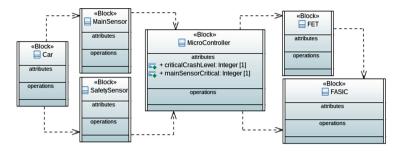

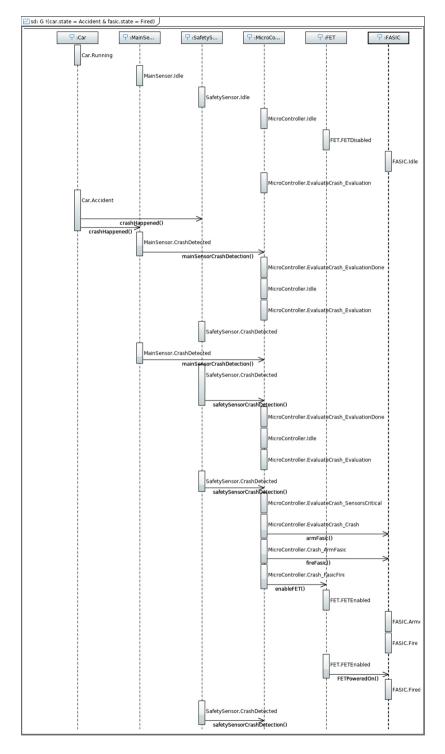

- Kalutarage, H.K., Nguyen, H.N., Shaikh, S.A.: Towards a threat assessment framework for apps collusion. Telecommun. Syst. 66(3), 417–430 (2017). https://doi.org/ 10.1007/s11235-017-0296-1