António Casimiro Pedro M. Ferreira (Eds.)

# Reliable Software Technologies – Ada-Europe 2018

23rd Ada-Europe International Conference on Reliable Software Technologies Lisbon, Portugal, June 18–22, 2018, Proceedings

## Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology Madras, Chennai, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7408

António Casimiro · Pedro M. Ferreira (Eds.)

## Reliable Software Technologies – Ada-Europe 2018

23rd Ada-Europe International Conference on Reliable Software Technologies Lisbon, Portugal, June 18–22, 2018 Proceedings

Editors António Casimiro D University of Lisbon Lisbon Portugal

Pedro M. Ferreira D University of Lisbon Lisbon Portugal

ISSN 0302-9743

ISSN 1611-3349

(electronic)

Lecture Notes in Computer Science

ISBN 978-3-319-92431-1

ISBN 978-3-319-92432-8

(eBook)

https://doi.org/10.1007/978-3-319-92432-8

Library of Congress Control Number: 2018944394

LNCS Sublibrary: SL2 - Programming and Software Engineering

© Springer International Publishing AG, part of Springer Nature 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

The 23rd edition of the International Conference on Reliable Software Technologies (Ada-Europe 2018) took place in Lisbon, returning to Portugal 12 years after Porto in 2006. The previous editions of the conference were held in Spain (Santander, 1999, Palma de Mallorca, 2004, Valencia, 2010, Madrid, 2015), France (Toulouse, 2003, Brest, 2009, Paris, 2014), the UK (London, 1997, York, 2005, Edinburgh, 2011), Austria (Vienna, 2017 and 2002), Switzerland (Montreux, 1996, Geneva, 2007), Sweden (Uppsala, 1998, Stockholm, 2012), Germany (Potsdam, 2000, Berlin, 2013), Italy (Venice, 2008, Pisa, 2016), and Belgium (Leuven, 2001).

The Faculty of Sciences of the University of Lisbon was the lead organizer for this edition, with aid from an international core team that included members of Ada-Europe, the organization that oversees and sponsors the conference series.

The conference took place in the week of June 18–22, 2018, with a rich program for both technical content and social opportunities. The scientific program featured 10 papers selected among 27 peer-reviewed submissions, grouped into five presentation sessions scheduled in the central days of the conference week, to address the following topics: safety and security, Ada 202X, handling implicit overhead, real-time scheduling, and new application domains. The proceedings contained in this volume reflect these contributions (see the Table of Contents for details).

The conference program also included 12 industrial contributions arranged in four industrial presentation sessions. The regular sessions were complemented by four more presentations selected among the regular submitted papers, as well as by vendor presentations. Vendor exhibitions completed the core program.

The first and the last day of the conference were dedicated to tutorials and workshops. A total of ten tutorials took place, eight of which were half-day tutorials and 2 full-day ones. On Monday the program included the workshop on Runtime Verification and Monitoring Technologies for Embedded Systems (RUME), and on Friday the fifth edition of the Workshop on Challenges and New Approaches for Dependable and Cyber-Physical Systems Engineering (DeCPS) took place. The proceedings from this part of the conference program will be published, in successive instalments, in the *Ada User Journal*, the quarterly magazine of Ada-Europe.

The scientific and industrial submissions originated from 19 countries from Europe, Asia, North and South America and Africa. Thanks to that wealth, the final program was an international digest of contributions from Austria, France, Germany, Italy, Norway, Poland, Portugal, South Korea, Spain, Sweden, Switzerland, the UK, and the USA.

Each of the three days of the technical program opened with a keynote talk focusing on topics of interest to the conference scope. The three keynote talks were:

"Security and Dependability Challenges of IT/OT Integration" by Paulo Esteves-Veríssimo, from the University of Luxembourg, Luxembourg, who argued about the need for paradigms and techniques to endow systems with the capacity of

#### VI Preface

defeating incremental adversary power and sustaining perpetual and unattended operation, in a systematic and automatic way.

- "From Physicist to Rocket Scientist, and How to Make a CubeSat That Works" by Carl Brandon, from the Vermont Technical College, USA, who explained how to have a successful CubeSat, where many others have failed, in which the reliability of SPARK/Ada software plays a big part.

- "Vulnerabilities in Safety, Security, and Privacy" by Erhard Plödereder, from the University of Stuttgart, Germany, who discussed the differences and commonalities in threats that affect safety, security, or privacy in today's systems, also arguing that vulnerabilities made possible by programming language features form a common base for violating safety, security, or privacy.

The tutorial program covered the following topics:

- "Recent Developments in SPARK 2014," Peter Chapin, Vermont Technical College, USA

- "Access Types and Memory Management in Ada 2012," Jean-Pierre Rosen, Adalog, France

- "Design and Architecture Guidelines for Trustworthy Systems," William Bail, The MITRE Corporation, USA

- "Numerics for the Non-Numerical Analyst," Jean-Pierre Rosen, Adalog, France

- "Requirements Development for Safety- and Security-Critical Systems," William Bail, The MITRE Corporation, USA

- "Scheduling Analysis of AADL Architecture Models," Frank Singhoff, Lab-STICC/UBO, France and Pierre Dissaux, Ellidiss Technologies, France

- "Writing Contracts in Ada," Jacob Sparre Andersen, JSA Research & Innovation, Denmark

- "Introduction to Libadalang," Raphaël Amiard and Pierre-Marie de Rodat, Ada-Core, France

- "Unit-Testing with Ahven," Jacob Sparre Andersen, JSA Research & Innovation, Denmark

- "Frama-C, a Framework for Analyzing C Code," Julien Signoles, France

The industrial program featured the following presentations:

- "Managing the Endianness of Software Building Blocks with GNAT Ada Pragmas: A Case Study," Patricia Lopez Cueva and Marco Panunzio

- "Using Ada in Non-Ada Systems," Ahlan Marriott

- "Easy Ada Tooling with Libadalang," Pierre-Marie de Rodat and Raphaël Amiard

- "Ariane 6 Flight Software Designed for a Simpler Validation," Philippe Gast and Cyrille Pierre

- "I3DS A Modular Sensor Suite for Space Robotics," Kristoffer Nyborg Gregertsen

- "Multi-Concern Dependability-Centered Assurance for Space Systems via ConcertoFLA," Barbara Gallina, Zulqarnain Haider, Anna Carlsson, Silvia Mazzini, and Stefano Puri

- "Applying Formal Timing Analysis to Satellite Software," Andreas Wortmann

- "Multicore Timing Analysis for Safety-Critical Software," Ian Broster, Guillem Bernat, Francisco Cazorla, Christos Evripidou, and Suzana Milutinovic

- "KhronoSim: Simulation and Testing of Real-Time Critical Cyber-Physical Systems," Gonçalo Gouveia, João Esteves, Cláudio Maia, and Luis Miguel Pinho

- "C Guidelines Compliance and Deviations (the MISRA and CERT Cases)," Maurizio Martignano

- "Agile in Safety Critical Projects," Pawel Zakrzewski

- "AGILE-R: Agile Software Development for Railways," Silvia Mazzini, John Favaro, Guido Ioele, Paolo Panaroni, Giancarlo Gennaro, and Umile Paone

Complementing the regular sessions, the program of the conference included the following technical presentations:

- "The IRONSIDES Project: Final Report," Barry Fagin and Martin Carlisle

- "Concurrent Reactive Objects in Rust—Secure by Construction," Marcus Lindner, Jorge Aparicio, and Per Lindgren

- "Alire: A Library Repository Manager for the Open Source Ada Ecosystem," Alejandro R. Mosteo

- "Real-Time Ada Applications on Android," Alejandro Pérez Ruiz, Mario Aldea Rivas, and Michael González Harbour

We would like to acknowledge the work of all the people who contributed, with various responsibilities and official functions, to the making of the conference program overall. The success of the conference depends in large part on the quality of the program contents. The authors of the selected contributions are to be thanked first and foremost for that. The members of the Program and Industrial Committees had the difficult task of screening the submissions and selecting the contributions to include in this proceedings volume and in the *Ada User Journal*.

The Organizing Committee put it all together: Nuno Neves (Conference Chair); Marcus Völp (Special Session Chair); José Rufino and Marco Panunzio (Industrial Co-chairs); David Pereira (Tutorial and Workshop Chair); Dirk Craeynest (Publicity Chair); Ahlan Marriott and José Neves (Exhibition Co-chairs). All of them deserve our gratitude for their effort.

We hope that the attendees enjoyed every element of the conference program as much as we did in organizing it.

June 2018

António Casimiro Pedro Ferreira

## Organization

## **General Chair**

| Nuno Neves                    | LASIGE/University of Lisbon, Portugal                        |  |  |  |  |

|-------------------------------|--------------------------------------------------------------|--|--|--|--|

| Program Chair                 |                                                              |  |  |  |  |

| António Casimiro              | LASIGE/University of Lisbon, Portugal                        |  |  |  |  |

| Special Session Chain         |                                                              |  |  |  |  |

| Marcus Völp                   | University of Luxembourg, Luxembourg                         |  |  |  |  |

| Tutorial and Worksh           | op Chair                                                     |  |  |  |  |

| David Pereira                 | CISTER/ISEP, Portugal                                        |  |  |  |  |

| Industrial Co-chairs          |                                                              |  |  |  |  |

| Marco Panunzio<br>José Rufino | Thales A.S., France<br>LASIGE/University of Lisbon, Portugal |  |  |  |  |

| Publication Chair             |                                                              |  |  |  |  |

| Pedro Ferreira                | LASIGE/University of Lisbon, Portugal                        |  |  |  |  |

| Exhibition Co-chairs          |                                                              |  |  |  |  |

| José Neves<br>Ahlan Marriott  | GMV Skysoft, Portugal<br>White Elephant GmbH, Switzerland    |  |  |  |  |

| Publicity Chair               |                                                              |  |  |  |  |

| Dirk Craeynest                | Ada-Belgium and KU Leuven, Belgium                           |  |  |  |  |

| Local Secretariat             |                                                              |  |  |  |  |

| Madalena Almeida              | Viagens Abreu, Portugal                                      |  |  |  |  |

## **Sponsoring Institutions**

AdaCore PTC RAPITA Systems Ellidiss Software CRITICAL Software LASIGE/FCT

#### **Program Committee**

Mario Aldea Universidad de Cantabria, Spain Vienna University of Technology, Austria Ezio Bartocci Vienna University of Technology, Austria Johann Blieberger Rakesh Bobba Oregon State University, USA Bernd Burgstaller Yonsei University, South Korea LASIGE/University of Lisbon, Portugal António Casimiro Juan A. de la Puente Universidad Politécnica de Madrid, Spain Virgil Gligor Carnegie Mellon University, USA Michael González Universidad de Cantabria, Spain Harbour J. Javier Gutiérrez Universidad de Cantabria, Spain Jérôme Hugues ISAE, France Ruediger Kapitza Technische Universität Braunschweig, Germany Hubert Keller Karlsruhe Institute of Technology, Germany Raimund Kirner University of Hertfordshire, UK Adam Lackorzynski TU Dresden and Kernkonzept GmbH, Germany Kristina Lundkvist Mälardalen University, Sweden Franco Mazzanti ISTI-CNR, Italy Laurent Pautet Telecom ParisTech, France CISTER/ISEP, Portugal Luís Miguel Pinho Erhard Plödereder Universität Stuttgart, Germany Jorge Real Universitat Politècnica de València, Spain AdaCore, France José Ruiz Sergio Sáez Universitat Politècnica de València, Spain Elad Schiller Chalmers University of Technology, Sweden Université de Bretagne Occidentale, France Frank Singhoff Jorge Sousa Pinto University of Minho, Portugal Tucker Taft AdaCore, USA Elena Troubitsyna Åbo Akademi University, Finland Santiago Urueña GMV, Spain Tullio Vardanega Università di Padova, Italy Marcus Völp University of Luxembourg, Luxembourg

## **Industrial Committee**

| Ian Broster<br>Luís Correia | Rapita Systems, UK<br>EMPORDEF-TI, Portugal     |

|-----------------------------|-------------------------------------------------|

| Dirk Craeynest              | Ada-Belgium and KU Leuven, Belgium              |

| Thomas Gruber               | Austrian Institute of Technology (AIT), Austria |

| Andreas Jung                | European Space Agency, The Netherlands          |

| Ismael Lafoz                | Airbus Defence and Space, Spain                 |

| Ahlan Marriott              | White Elephant, Switzerland                     |

| Maurizio Martignano         | Spazio IT, Italy                                |

| Marco Panunzio              | Thales Alenia Space, France                     |

| Paul Parkinson              | Wind River, UK                                  |

| Jean-Pierre Rosen           | Adalog, France                                  |

| José Rufino                 | LASIGE/University of Lisbon, Portugal           |

| Emilio Salazar              | GMV, Spain                                      |

| Helder Silva                | EDISOFT, Portugal                               |

| Jacob Sparre Andersen       | JSA Consulting, Denmark                         |

| Andreas Wortmann            | OHB System, Germany                             |

## **Additional Reviewers**

Akshith Gunasekaran Rahma Bouaziz Hai Nam Tran Hector Perez Wenbo Xu

## Contents

#### Safety and Security

| Using Safety Contracts to Verify Design Assumptions During Runtime<br>Omar Jaradat and Sasikumar Punnekkat                                                              | 3   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tool-Supported Safety-Relevant Component Reuse: From<br>Specification to Argumentation                                                                                  | 19  |

| Ada 202X                                                                                                                                                                |     |

| Safe Dynamic Memory Management in Ada and SPARK                                                                                                                         | 37  |

| Safe Non-blocking Synchronization in Ada2x                                                                                                                              | 53  |

| Handling Implicit Overhead                                                                                                                                              |     |

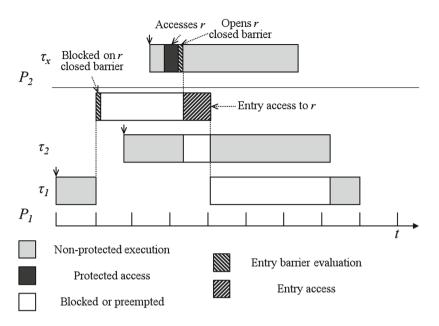

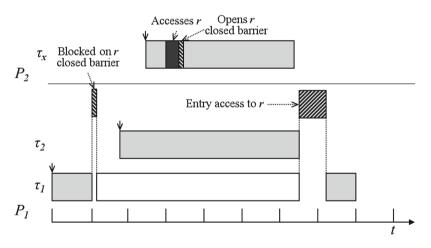

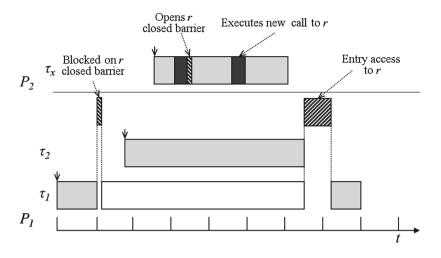

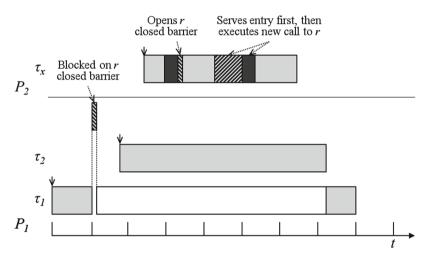

| On the Effect of Protected Entry Servicing Policies on the<br>Response Time of Ada Tasks<br>Jorge Garrido, Juan Zamorano, Alejandro Alonso,<br>and Juan A. de la Puente | 73  |

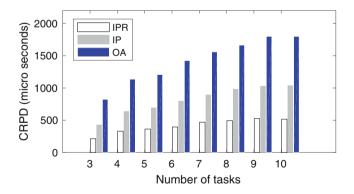

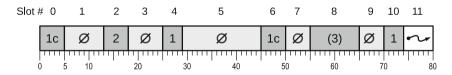

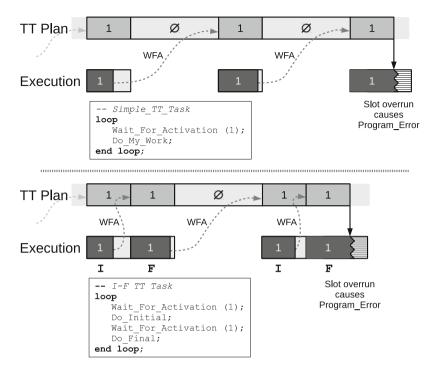

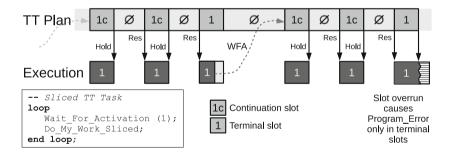

| Improved Cache-Related Preemption Delay Estimation for Fixed<br>Preemption Point Scheduling<br><i>Filip Marković, Jan Carlson, and Radu Dobrin</i>                      | 87  |

| Real-Time Scheduling                                                                                                                                                    |     |

| Combined Scheduling of Time-Triggered and Priority-Based Task<br>Sets in Ravenscar<br>Jorge Real, Sergio Sáez, and Alfons Crespo                                        | 105 |

| Theory and Practice of EDF Scheduling in Distributed<br>Real-Time Systems                                                                                               | 123 |

| J. JUVIET GUILETTEL UNU MECTOT I ETEL                                                                                                                                   |     |

XIV Contents

## **New Application Domains**

| Safe Parallelism: Compiler Analysis Techniques for Ada and OpenMP      |     |  |  |  |

|------------------------------------------------------------------------|-----|--|--|--|

| Sara Royuela, Xavier Martorell, Eduardo Quiñones,                      |     |  |  |  |

| and Luis Miguel Pinho                                                  |     |  |  |  |

| Microservice-Based Agile Architectures: An Opportunity for Specialized |     |  |  |  |

| Niche Technologies.                                                    | 158 |  |  |  |

| Stefano Munari, Sebastiano Valle, and Tullio Vardanega                 |     |  |  |  |

| Author Index                                                           | 175 |  |  |  |

## Safety and Security

## Using Safety Contracts to Verify Design Assumptions During Runtime

Omar $\operatorname{Jaradat}^{(\boxtimes)}$  and Sasikumar Punnekkat

School of Innovation, Design and Engineering, Mälardalen University, Västerås, Sweden {omar.jaradat,sasikumar.punnekkat}@mdh.se

Abstract. A safety case comprises evidence and argument justifying how each item of evidence supports claims about safety assurance. Supporting claims by untrustworthy or inappropriate evidence can lead to a false assurance regarding the safe performance of a system. Having sufficient confidence in safety evidence is essential to avoid any unanticipated surprise during operational phase. Sometimes, however, it is impractical to wait for high quality evidence from a system's operational life, where developers have no choice but to rely on evidence with some uncertainty (e.g., using a generic failure rate measure from a handbook to support a claim about the reliability of a component). Runtime monitoring can reveal insightful information, which can help to verify whether the preliminary confidence was over- or underestimated. In this paper, we propose a technique which uses runtime monitoring in a novel way to detect the divergence between the failure rates (which were used in the safety analyses) and the observed failure rates in the operational life. The technique utilises safety contracts to provide prescriptive data for what should be monitored, and what parts of the safety argument should be revisited to maintain system safety when a divergence is detected. We demonstrate the technique in the context of Automated Guided Vehicles (AGVs).

**Keywords:** Confidence · Safety contracts · Safety case Safety argument · Monitoring · Runtime · Failure rate Probability of failure · Through-life safety assurance

## 1 Introduction

Safety critical systems are those systems whose failure could result in loss of life, significant property damage or damage to the environment [1]. Factories are often categorised as safety critical systems since failures of these systems, under certain conditions, can lead to severe consequences [2]. Assuring safety for such systems should provide justified confidence that all potential risks due to system failures are either eliminated or acceptably mitigated. Hence, all failures which might expose the manufacturing processes to hazards shall be analysed

© Springer International Publishing AG, part of Springer Nature 2018

A. Casimiro and P. M. Ferreira (Eds.): Ada-Europe 2018, LNCS 10873, pp. 3–18, 2018. https://doi.org/10.1007/978-3-319-92432-8\_1 and controlled as part of pre-deployment safety assurance and monitored and controlled as part of operational phase.

Developers of some safety critical systems build a safety case to demonstrate the safety aspect of their system by identifying all unreasonable risks and describing, in the light of the available evidence, how these risks have been eliminated or adequately mitigated. Typically, a safety case comprises both safety evidence (e.g. safety analyses, software and hardware inspection reports, or functional test results) and a safety argument (i.e., reasoning) explaining that evidence. The safety argument shows which claims the developer uses each item of evidence to support and how those claims, in turn, support broader claims about system behaviour, hazards addressed, and, ultimately, acceptable safety [3].

An organisation building a safety case should be accountable for the ownership of the risks to be controlled by adopting an appropriate safety management system, performing a hazard assessment, selecting appropriate controls, and implementing them [4]. In order to help building a sufficient and credible (i.e., on a scientific basis) confidence in the safe performance of a system, its safety case shall always communicate the actual safe performance of the system, and shall always contain only acceptable items of evidence that this system meets its safety requirements. However, an item of evidence is valid only in the operational and environmental context in which it is obtained or to which it applies. More clearly, as the system evolves after deployment, there could be a mismatch between our communicated understanding of the system safety by the safety case and the safety performance of the system in actual operation, which might invalidate many of the prior assumptions made, undermine the collected items of evidence and thus defeat safety claims [5]. Despite the improvements in operational safety monitoring, there is insufficient clarity on how to utilise the analysis results of the monitored data on the documented confidence in safety cases.

In safety critical systems, failure rates are sometimes used as quantitative criteria while performing safety assessment (i.e., Probabilistic Safety Assessment (PSA)). Failure Rate (FR =  $\lambda$ ) is defined as the probability per unit time that a component experiences a failure at time "t", given that the component was operating at time "0" and has survived to time "t" [6]. Failure rates can be deemed as a reliability prediction that together with the consequences (Risk =probability of failure \* consequence of failure) determine the Safety Integrity Level (SIL), which in turn specifies a target level of risk reduction that should be considered by a safety function or instrument. The quality of the failure rate measure determines the quality of the PSA. Hardware components are usually provided by generic failure rates which are derived by the statistical analyses of the failure frequency [7]. Failure frequency is usually obtained by the test results and the historical data of the components. Although the calculation of a generic failure rate is based on complex models which include factors using specific component data such as temperature, environment, and stress [6], it is, at its best, just a probability that is still subject to a percentage error even if it is used in the same context as in specifications. Assuming the perfection of the failure

rate calculations is not judicious and can be misleading. Hence, a minimum level of fault tolerance in the architectural design of the safety functions should be considered. For example, the functional safety standards IEC 61508 [8] and IEC 61511 [9] recognise that there is always some degree of uncertainty in the assumptions made in calculation of failure rate and probability [10].

In this paper, we propose a novel technique to detect the discrepancies between the failure rates of system's components during their operational life and their generic failure rates used for analysis and assurance during the design time. Since it is infeasible to monitor the failure rates of all components of a system, the technique utilises probabilistic Fault Tree Analysis (FTA) to evaluate the criticality of the system components, and selects the most critical ones for monitoring. The technique derives safety contracts for the selected components and associate them with the relevant events in the FTA and the relevant parts in the safety case. If a discrepancy is detected between an observed failure rate  $(\lambda_O)$  and a generic failure rate  $(\lambda_G)$  of the same component, where  $\lambda_O > \lambda_G$ , then the relevant contract should be flagged and the referred parts of both the FTA and the safety case should be revisited.

Our hypothesis is that using safety contracts for monitoring the failure rates during the operational life of a system can help to provide essential feedback on the overall confidence in safety. More clearly, getting more precise measure of failure rates than the predicted ones will (1) improve the efficacy of the system design to reduce the risk (mitigate by design), (2) define stronger evidence (e.g., refine or rectify the test results) and (3) highlight the required preventive, corrective, perfective or adaptive maintenance for safer operation

In this paper, we specifically make the following four contributions:

- 1. A novel technique to continuously reassess the failure rates and use the results to suggest system changes or maintenance

- 2. A new way to derive safety contracts to facilitate the traceability between the system design, safety analysis and the safety case

- 3. An example of how to argue more compelling over the failure rate in the light of the derived evidence from the operational phase

- 4. An example of how to carry out a through-life safety assurance

The rest of the paper is organised as follows: In Sect. 2, we present our approach to verify the design assumptions during runtime by safety contracts. In Sect. 3, we apply our technique to an AGV system to illustrate the main steps. In Sect. 4, we discuss how the suggested approach enables a through-life safety assurance. Finally, we conclude and describe the future directions in Sect. 5.

#### 2 Using Safety Contracts to Verify Design Assumptions During Runtime

Failures of components in safety critical systems are typically divided into four modes, namely, Safe Detected (SD), Safe Undetected (SU), Dangerous Detected (DD), and Dangerous Undetected (DU). DD and DU failures can cause loss of

a safety function while we believe that we are protected and this might happen in fraction of diagnostic interval in case of DD failures or during the unknown downtime in case of DU failures [11]. DU failures are typically due to either random or systematic failures. In this paper, we specifically focus on dangerous failures (DD and DU). Whenever FTAs are constructed to evaluate hazards, the basic event failure data must describe only failures that contribute to that hazard and thus only dangerous failure rates ( $\lambda_D$ ) should be included for the basic events, where  $\lambda_D = \lambda_{DD} + \lambda_{DU}$ .

In this section, we propose a technique that aims to determine the  $\lambda_D$  of particular HW components in their operational life (observed  $\lambda_D = \lambda_{D_{-}O}$ ) and compare the results with the design assumptions of these components (generic  $\lambda_D = \lambda_{D_{-}G}$ ) to ultimately highlight any discrepancies between  $\lambda_{D_{-}O}$  and  $\lambda_{D_{-}G}$ . The technique uses criticality importance measure to rank the components from the most to the less critical so that safety engineers can select particular components for monitoring when it is infeasible to monitor all of them. The technique also uses sensitivity analysis to determine whether a highlighted discrepancy is acceptable or not. The technique heavily depends on probabilistic FTAs, and it comprises 8 steps as follows:

#### 2.1 Determine the PFD or the PFH in the FTA

In this step, we calculate the PFD (Probability of Failure on Demand) or the PFH (Probability of Failure per Hour) using a probabilistic FTA where each component is specified by its  $\lambda_{D-G}$ . The selection between PFD and PFH is based on the demand of a safety function. More clearly, if the safety function will be working in a continuous mode, then we have to select PFH [8]. However, if the safety function is expected to work once per year (at most), then PFD should be selected [8]. To calculate the PFD or PFH of an FTA, four sub-steps should be performed as follows:

A. Calculate the Failure Probability of the Basic Events: There are different formulas used to calculate PFD depending on different factors, such as system's structure (K-out-of-N structures), Common Cause Factor (CCF), operational maintenance, safety standards obligations, etc. For example, Exida (a leading product certification and knowledge company) provides a realistic formula to calculate the PFD [12]. However, the difference between PFD formulas will not be influential in our technique. For the sake of simplicity, we adopt the PFD formula given in [13]. Formula 1 shows how we calculate the PFD for the basic events:

$$PFD(i) = \lambda_{D,i} * \tau \tag{1}$$

where i denotes the basic event and  $\tau$  is the proof test interval. The component reparation or replacement time is assumed to be short and thus it is negligible.

The main difference between calculating PFD and PFH is in the logic of determining the probability of failures for the basic events. To calculate the PFH for the FTA's events, Formula 1 should be replaced with Formula 2, which

is basically the famous unreliability exponential equation where only  $\lambda_D$  is considered. Unreliability in the context of functional safety is interpreted as the probability of a function to fail during a given time interval.

$$PFH(i) = 1 - e^{-\lambda_D t} \tag{2}$$

For calculating the PFD or PFH, we assume the failure rates of all components are constants, independent and have the same  $\tau$ . We also assume that all potential CCFs are explicitly modelled as basic events in the FTAs. The rest of the sub-steps (B, C and D) are the same irrespective of we use PFD or PFH.

**B. Determine Minimal Cut Set (MCS) in the FTA:** The MCS is defined as: "A cut set in a fault tree is a set of basic events whose (simultaneous) occurrence ensures that the top event occurs. A cut set is said to be minimal if the set cannot be reduced without losing its status as a cut set" [14]. There are several algorithms to find the MC. We apply Mocus cut set algorithm [14].

**C.** Calculate the Failure Probability of the Determined MCS: Calculating the probability of occurrence for the top event in a FTA with many MCS requires calculating the probability of those MCS. The failure probability of each determined MCS in the previous sub-step should be calculated according to formula 3 [11], as follows:

$$\check{Q}_j(t) = \prod_{i \in C_j} q_i(t) \tag{3}$$

where  $q_i(t)$  denotes the probability of basic event *i* at time *t*,  $\dot{Q}_j(t)$  is the probability that minimal cut set *j* is in failed state at time *t*,  $i \in C_j$  denotes the minimal cut set *j* that contains the basic event *i*.

**D.** Calculate the PFD or PFH of the Top Event: We calculate the actual PFD or PFH by the *upper bound approximation formula* 4 [11] using the determined MCS, as follows:

$$PFD_{Act}(Top), PFH_{Act}(Top) = \sum_{j=1}^{k} \check{Q}_j(t)$$

(4)

So far, all PFD or PFH calculations are based on  $\lambda_{D_G}$ . We refer to the result of the probability calculation based on  $\lambda_{D_G}$  as *Actual or Act*. The PFD<sub>Act</sub>(Top) or PFH<sub>Act</sub>(Top) are design assumptions which will be compared with the observed  $\lambda$  to check the correctness/validity of the design assumptions.

#### 2.2 Identify the Most Critical Components

Monitoring every single component in safety critical systems is infeasible especially since such systems become bigger and more sophisticated over time. However, some components in a system are more critical for the system safety than other components. The objective of this step is to identify the most critical components in a system w.r.t the FTA. There are different measures through which FTA's events can be ranked based on their importance (e.g., Birnbaum, Criticality Importance, Fussel-Vesely Importance, Risk Achievement Worth (RAW)). In our technique, however, we are interested to rank the components based on their contributions to system safety. More specifically, we are interested in the components whose failures have the maximum impact on system safety. RAW is a measure that focuses on the 'worth' of the basic event in 'achieving' the present level of risk and indicates the importance of maintaining the current level of reliability for the basic event [14]. RAW is often used as an importance measure to rank components in terms of safety significance [15] and hence we will adopt it for our work.

The failure probability of the component i at time t may be described as:

$$P(i) = \begin{cases} 0 & \text{if the component is functioning at time } t \\ 1 & \text{if the component is in a failed state at time } t \end{cases}$$

The RAW,  $I^{RAW}(i|t)$  is the ratio of the (conditional) system unreliability if component *i* is P(1), and it is calculated as follows [14]:

$$I^{RAW}(i|t) = \frac{1 - h(0_i, p(t))}{1 - h(p(t))} \text{ for } i = 1, 2, ..., n$$

(5)

where  $h(0_i, p(t))$  is the probability of top event with component i = P(1), and h(p(t)) is probability of top event. All basic events should be ranked from the most important to the less important. The most important event is the event for which Formula 5 has the maximum value.

#### 2.3 Refine the Identified Critical Parts

The idea of this step is to discuss with system developers (e.g., safety engineers) and refine the ranked list of the critical components. This step is important, since it embeds the system level knowledge and experience of engineers regarding the uncertainty in a generic  $\lambda$  as well as helps as a validation step in the decision making process. For example, it could be the case that a high ranked critical component in the list has a stable  $\lambda_G$  and systems engineers decide not to monitor it. That is, it is envisaged that some events may be removed from the list or the rank of some of them change. Moreover, the list can be extended to add any additional events by the developers.

#### 2.4 Perform Sensitivity Analysis

The idea of this step is to determine the maximum allowable  $\lambda_D$  ( $\lambda_{D_-Max}$ ) of the system components which are selected for monitoring. More specifically, we need to define the upper- and lower bounds of the acceptable  $\lambda_D$  of each event in the MCS, where  $\text{PFD}_{Act}(\text{Top})$  or  $\text{PFH}_{Act}(\text{Top})$  is less than or equal to the required probabilities  $PFD_{Req}(Top)$  or  $PFH_{Req}(Top)$ , respectively. The required probability is described as safety requirements by the safety standards (e.g., SIL, ASIL and DAL). It is important for our technique to determine to which extent  $PFD_{Act}(i)$  or  $PFH_{Act}(i)$  can be deviated while  $PFD_{Act}(Top)$  or  $PFH_{Act}(Top)$ still satisfies  $PFD_{Req}(Top)$  or  $PFH_{Req}(Top)$ , respectively. To this end, two main activities should be performed, as follows:

**Determine the Maximum Allowable**  $q_{i, Max(t)}$  for Each Component. The  $q_{i,Max}(t)$  for each component should be determined with respect to  $PFD_{Req}(Top)$  or  $PFH_{Req}(Top)$ . Formula 6 should be used to determine  $q_{i,Max}(t)$  for each component at a time.

$$\frac{PFD_{Req}(Top), PFH_{Req}(Top) - (\sum \check{Q}_{i\notin C_j}(t))}{\sum \check{Q}_{i\in C_j}(t) \neg q_i(t)} = \frac{\sum \check{Q}_{i\in C_j}(t)}{\sum \check{Q}_{i\in C_j}(t) \neg q_i(t)}$$

(6)

where  $i \notin C_j$  denotes the minimal cut set j that does not contain basic event i. **Determine**  $\lambda_{D\_Max}$  for Each Component. Once we have  $q_{i,Max}(t)$  for a component it is easy to determine its  $\lambda_{D,Max}$ . Formula 7 determines  $\lambda_{D,Max}$  in case of PFD, as follows:

$$\lambda_{D,Max} = \frac{q_{i,Max}(t)}{\tau_i} \tag{7}$$

Formula 8 determines  $\lambda_{D,Max}$  in case of PFH, as follows:

$$\lambda_{D-Max} = \frac{-\ln(q_{i,Max}(t))}{\tau_i} \tag{8}$$

After calculating  $\lambda_{D,Max}$  for all events, the latter should be ranked from the most sensitive to the less sensitive to change. The most sensitive event is the event for which Formula 9 is the minimum:

$$Sensitivity(\lambda_{D_i,G}) = \frac{\lambda_{D_i,Max} - \lambda_{D_i,G}}{\lambda_{D_i,G}}$$

(9)

#### 2.5 Derive Safety Contracts

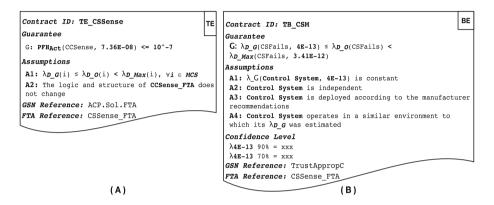

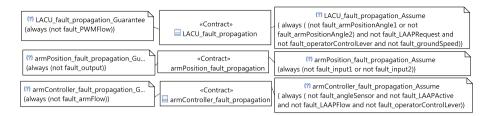

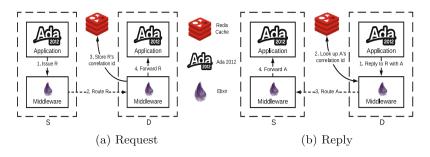

In this step, safety contracts should be derived from FTAs. The main objectives of deriving safety contracts are: (1) highlight the most important components to make them visible up front for developers attention [16], and (2) record the thresholds of  $\lambda_D(i)$  to continuously compare them with the monitoring results  $(\lambda_{D_{-}O})$ . Hence, if  $\lambda_{D_{-}O}$  of component *i* exceeds the guaranteed  $\lambda_{D_{-}Max}(i)$  in the contract of that component, then we can infer that the contract in question is broken and the related FTA should be re-assessed in the light of the  $\lambda_{D_{-}O}$ . Another objective to derive safety contracts is to associate these contracts with safety arguments as reference points so that developers know the related part of the argument when they review a FTA and vice versa. To this end, we introduce two templates to derive contracts. The first contract template is for deriving a contract for the top event only. The top event safety contract is annotated with the abbreviation "**TE**" in the upper-right corner of the contract to denote that this contract is derived for a **Top Event** as shown in Fig. 1-A.

The second contract template is for deriving a safety contract for each event in the MCS (i.e., events related to important components). This type of contracts is referred to as "*monitoring safety contracts*" and it is is annotated with the abbreviation "**BE**" in the upper-right corner to denote that this contract is derived for a **B**asic **E**vent as shown in Fig. 1-B.

Fig. 1. A. Contract template: Top Event. B. Contract template: Basic Event

#### 2.6 Associate Safety Contracts with Safety Arguments

In this step, all safety contracts which were derived in Step 4 should be associated with safety arguments. This step assumes that the safety argument should come down to a claim that the "probability of failure of hazard H due to component failure is acceptable", in turn supported by a context element about what that probability is in the context of an applicable definition of acceptable, in turn supported by the FTA as evidence. An Assurance Claim Points (ACP) [17] should be created between the claim about the acceptable probability and the evidence, where a separate confidence argument should extend this ACP to argue over the quality of the used failure rates to calculate PFD<sub>Act</sub>(Top) or PFH<sub>Act</sub>(Top).

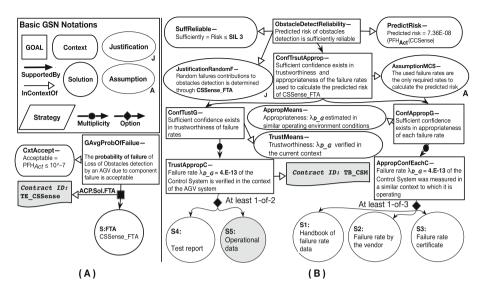

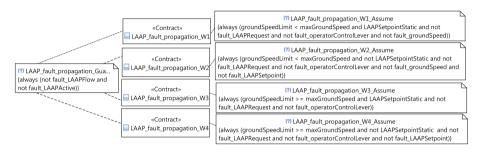

It is necessary that the argument should be clearly structured and the items of evidence to be clearly asserted to support the argument [18]. There are several ways to represent safety arguments (e.g., textual, tabular, graphical, etc.). In this paper, we use the Goal Structuring Notation (GSN) [18], which provides a graphical means of communicating (1) safety argument elements, claims (goals), argument logic (strategies), assumptions, context, evidence (solutions), and (2) the relationships between these elements. The basic notations of GSN are shown in Fig. 2 (in the upper left side corner). A goal structure shows how goals are successively broken down into ('solved by') sub-goals until eventually supported by direct reference to evidence. GSN can clarify the argument strategies adopted

Fig. 2. A. A probability of failure argument with an association of a top event safety contract. B. Confidence argument with an association of a monitoring safety contract

(i.e., how the premises imply the conclusion), the rationale for the approach (assumptions, justifications) and the context in which goals are stated.

Assertions in a safety argument relate to the sufficiency and appropriateness of the inferences declared in the argument, the context and assumptions used and the evidence cited [17]. For example, when an item of evidence is used to support a claim, it is asserted that this evidence is sufficient to support the claim. However, a simple 'SolvedBy' relation between the evidence and the claim will not satisfy a reviewer's concerns to reach a certain level of confidence, such as, 'why the reviewer should believe that the evidence is appropriate for the claim?' or 'whether it is trustworthy'.

Hawkins et al. [17] introduced "An assured safety argument" as a new structure for arguing safety in which the safety argument is accompanied by a confidence argument that documents the confidence in the structure and bases of the safety argument. Hawkins suggests that instead of decomposing the arguments further to argue over the appropriateness and trustworthiness of the supporting evidence, an ACP can be created to indicate an assertion in the safety argument. An ACP is indicated in GSN with a named black rectangle on the relevant link and a confidence argument should be developed for each ACP [17]. Three types of assertions were defined as ACPs as follow:

- 1. Asserted inference: the ACP for an asserted inference is the link between the parent claim and its strategy or sub-claims

- 2. Asserted context: the ACP for asserted context is the link to the contextual element

- 3. Asserted solution: the ACP for asserted solutions is the link to the solution element

Fig. 3. Types of ACPs with an example of each usage [17]

In this step, we suggest to use the principle of the ACP. Hence, the *top* event safety contract should be associated with the ACP (i.e., asserted solution) between the GSN goal which claims the acceptability of the hazard probability due to a component failure and the GSN solution which refers to the relevant FTA. Whereas, each monitoring safety contract should be associated with a GSN goal about the relevant component in the confidence argument. Figure 2-A shows a pattern of PFD or PFH argument and an example of top event safety contract association. Figure 2-B shows a confidence argument pattern with an association of a monitoring safety contract. Figure 3 instantiates an example of each ACP type and it also represents our suggested traceability means which associates the derived contracts from FTAs with safety arguments (the dotted part in the figure).

#### 2.7 Determine $\lambda_{D_{-}O}$ Using the Data from Operation and Compare it to the Guaranteed $\lambda_{D_{-}Max}$ in Safety Contracts

In this step,  $\lambda_D \rho$  of specified components should be obtained during the components' runtime. Using runtime monitors is one way to obtain data from operation. There are many proposed architectures to detect or test a system (or parts of it) for bad behaviour [19]. We provide a monitoring logic which requires two parameters (inputs) from any monitoring framework, namely, the number of recorded failures (i.e., DD and DU) as well as  $\tau$  in time unit (e.g., hours). Algorithm 1 should be used to determine  $\lambda_{D_{-}O}$  using the data from operation and compare it to the guaranteed  $\lambda_{D_{-}Max}$ . The more we monitor a component and record its failures the more confident we will be in its actual  $\lambda_D$  in a specific context. The calculated level of confidence can reveal how long we still need to monitor a component to reach a certain level of confidence. Hence, our algorithm also calculates the confidence level of  $\lambda_{D_{-}O}(i)70\%$  and  $\lambda_{D_{-}O}(i)90\%$  continuously and cumulatively using the Chi-Squared distribution. The calculated levels of confidence of a monitored component are automatically inserted into its "monitoring safety contract" and get updated continuously so that developers and assessors can review them in the FTA and the safety argument.

#### 2.8 Update the Safety Contracts and Re-visit the Safety Argument

If a *monitoring safety contract* is broken it means that there is at least one broken top event safety contract as well. In this case, the broken safety contracts should be used to trace the FTA events and elements of safety arguments (for which the contracts were derived). As a result of doing this, developers can specify the entry point of the impact of failure in the safety analysis and the safety argument. It is worth mentioning that we assume the existence of a redundant component of the failing component. Hence, a broken safety contract does not necessarily lead to a total system failure.

| <b>Algorithm 1.</b> The monitoring logic to determine $\lambda_{D_{-}O}$ and compare it to                                       |

|----------------------------------------------------------------------------------------------------------------------------------|

| $\lambda_{D-Max}$                                                                                                                |

| <b>Data</b> : MissionTime, $\tau$ , $\lambda_{D\_Max}$ , $\lambda_{DU\_O}$ , DUfailures = 0, $\lambda_{DD\_O}$ , DDfailures =    |

| $0, \lambda_{D_{-}O}, $ Num_Comp, CL90, CL70;                                                                                    |

| <b>Result</b> : Determine $\lambda_{D_{-}O}$ and compare it to $\lambda_{D_{-}Max}$                                              |

| 1 TotMonTime = clock(); $\Comment$ : start monitoring the mission time                                                           |

| 2 while $TotMonTime \leq MissionTime$ do                                                                                         |

| <b>3</b> Test_Interval_Monitor = clock(); \\Comment: start the monitoring time of                                                |

| the test interval time                                                                                                           |

| 4 while Test_Interval_Monitor $\leq \tau  do$                                                                                    |

| 5 if a DD failure is found then $(A = A + A + A + A + A + A + A + A + A + $                                                      |

| 6 DDfailures++; \\Comment: add an observed failure from a diagnosis log file                                                     |

| 7 end                                                                                                                            |

| 8 if a DU failure is recorded then                                                                                               |

| 9 DUfailures++; \\Comment: add an observed failure which was                                                                     |

| inserted manually                                                                                                                |

| 10 end                                                                                                                           |

| 11 $\lambda_{DU_{-}O} = 1/((\text{TotMonTime * Num_Comp}) / \text{DUfailures}); \setminus Comment:$                              |

| calculate $\lambda_{DU_{-}O}$                                                                                                    |

| 12 $\lambda_{DD_{-}O} = 1/((\text{TotMonTime * Num_Comp}) / \text{DDfailures}); \setminus Comment:$                              |

| calculate $\lambda_{DD_{-}O}$                                                                                                    |

| <b>13</b> $\lambda_{D_{-}O} = \lambda_{DU_{-}O} + \lambda_{DD_{-}O};$ $\backslash\backslash Comment: calculate \lambda_{D_{-}O}$ |

| 14 $\operatorname{CL70} = \operatorname{Chi}_{2}$                                                                                |

| Squared $(X^2_{70\%,2(DUfailures+DUfailures+1)})/(2*Num_Comp*TotMonTime);$                                                       |

| $\langle Comment: \lambda_{D_O} 70\%$                                                                                            |

| 15 $CL90 = Chi-$                                                                                                                 |

| Squared( $X^{2}_{90\%,2(DUfailures+DUfailures+1)}$ )/(2*Num_Comp*TotMonTime);<br>\\Comment: $\lambda_{D_{-}O}90\%$               |

| 16 if $\lambda_{D,O} \ge \lambda_{D,Max}$ then                                                                                   |

| 17 Contract $[\mathbf{C}]$ is broken; $\backslash Comment$ : highlight the broken contract                                       |

| whenever $\lambda_{D_{-}O} \geq \lambda_{D_{-}Max}$                                                                              |

| 18 end                                                                                                                           |

| 19 end                                                                                                                           |

| <b>20</b> Test_Interval_Monitor = 0; \\Comment: reset the $\tau$ timer to start a new one                                        |

| 21 end                                                                                                                           |

#### 3 Motivating Example: Automated Guided Vehicles (AGVs)

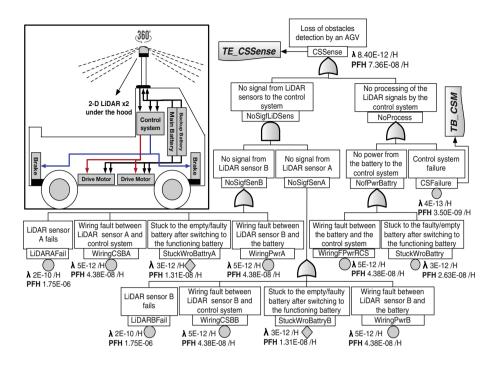

AGVs are being extensively used for more than 40 years now. They are used for intelligent transportation and distribution of materials in warehouses and auto-production lines. There are different setups and operational assumptions for each application of AGVs in industry. In our example, however, the AGVs are a number of battery-powered vehicles whose movements are autonomous. The AGVs are interfaced to automated warehouse and holding area, and to the machine tools, so that stock movement requirements can be fulfilled. The plant, in our example, is not fully automated so that people cannot be fully excluded from the areas where the AGVs work. Clearly, one of the most important safety features of the AGV vehicles is their ability to detect obstacles and stop quickly in order to avoid a collision with humans, hazardous objects (e.g., flammable materials, electrical resources, other AGVs, etc.). After performing safety analysis, a number of safety hazards were identified. In this paper, we will focus on one hazard, which is: Loss of obstacle detection while the vehicle is in motion. A redundant 2-D LiDAR sensor with all-round (360°) visibility is used for detecting obstacles within up to 30 m range. Information about detected obstacles are sent to the control system to determine the manoeuvring strategy to ultimately avoid any potential collision.

According to the likelihood of occurrence, potential consequences and other safety countermeasures in the AGVs, the obstacle detection function is assigned **SIL 3** (Safety Integrity Level) according to IEC 61508. Moreover, since the function under discussion operates in a high demand (i.e., in a continuous mode), the allowable frequency of dangerous failure according to the same standard is PFH <  $10^{-7}$ . The proof test interval  $\tau$  is assumed as 1 year (i.e., 8760 h) for all components. Figure 4 shows an overview of the AGV design (on upper left-hand corner). The figure also shows the FTA of the system where the top event together with the basic events are specified by  $\lambda_{D_{-G}}$ .

Applying the first 5 steps in Sect. 2 is straightforward. Table 1 provides the results of the steps 1–5. The *Refine* column reflects the experts judgment that is supported by the RAW and Sensitivity ranking. For the sake of giving a clear example of what should be done next, we assume that *Control system* got the highest priority for monitoring (the grey row in Table 1). Hence, two contracts should be derived in the case: (1) TE contract  $TB\_CSM$  and, (2) BE contract (i.e., monitoring contract)  $TE\_CSSense$ .

Step 6 requires associating the derived contracts with the safety argument. For AGV system example, we use our suggested GSN patterns in Sect. 2.6 to create the confidence argument first and then associate the contracts with it through an ACP. Figure 2 presents our safety argument and the role of the proposed monitoring technique to provide supportive evidence for the articulated claims about the failure rates in the argument. Figure 1 shows the derived TE and BE for the top event *CSSense* and the basic event *CSFails*. The figure also shows the GSN and FTA references which reveal the associations (or traceability) of the contracts with the safety argument and the FTA, respectively.

Fig. 4. An overview of AGV's and its probabilistic FTA (CSSense\_FTA)

|     |                 |                 | STEP 1   | STEP 2        | STEP 3    |                                        |             | STEP 4 | STEP 5       |

|-----|-----------------|-----------------|----------|---------------|-----------|----------------------------------------|-------------|--------|--------------|

| No. | Events          | $\lambda_{D,G}$ | PFH      | RAW           | Max PFH   | $\lambda_{\mathrm{D}_{-\mathrm{Max}}}$ | Sensitivity | Refine | Contract     |

| 1   | CSSense (Top)   | 8.4E-12         | 7.36E-08 |               | $10^{-7}$ |                                        |             |        | $TE_CSSense$ |

| 2   | CSFails         | 4E-13           | 3.50E-09 | 13589269.0946 | 2.99E-08  | 3.41E-12                               | 7.5380      | 1      | TB_CSM       |

| 3   | WiringFPwrRCS   | 5E-12           | 4.38E-08 | 13589268.5470 | 7.02E-08  | 8.02E-12                               | 0.6030      |        |              |

| 4   | StuckWroBattry  | 3E-12           | 2.63E-08 | 13589268.7851 | 5.27E-08  | 6.02E-12                               | 1.0051      | 3      |              |

| 5   | LiDARAFail      | 2E-10           | 1.75E-06 | 26.3559       | 1.42E-02  | 1.63E-06                               | 8137.5      | 2      |              |

| 6   | WiringCSBA      | 5E-12           | 4.38E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 325499      |        |              |

| 7   | StuckWroBattryA | 3E-12           | 2.63E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 542499      | 3      |              |

| 8   | WiringPwrA      | 5E-12           | 4.38E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 325499      |        |              |

| 9   | LiDARBFail      | 2E-10           | 1.75E-06 | 26.3559       | 1.42E-02  | 1.63E-06                               | 8137.5      | 2      |              |

| 10  | WiringCSBB      | 5E-12           | 4.38E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 325499      |        |              |

| 11  | StuckWroBattryB | 3E-12           | 2.63E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 542499      | 3      |              |

| 12  | WiringPwrB      | 5E-12           | 4.38E-08 | 26.3559       | 1.42E-02  | 1.63E-06                               | 325499      |        |              |

Table 1. A summary of the results of applying the steps 1–5

#### 4 A Through-Life Safety Assurance Technique

Denney et al. [5] introduced the term "Dynamic Safety Cases (DSCs)" as a novel operationalisation of the concept of through-life safety assurance. The main motivation for introducing DSCs is that the appreciable degree of certainty about the expected runtime behaviour of a system might not be precise or it perhaps over- or underestimate the actual behaviour, which can create deficiencies in the reasoning about the safety performance of that system. Hence, there is a need for a new class of safety assurance techniques that exploit the runtime related data (operational data) to continuously assess and evolve the safety reasoning to, ultimately, provide through-life safety assurance [5]. The suggested lifecycle of DSCs comprises four main activities as follows [5]:

- 1. **Identify** the sources of uncertainty in a safety case.

- 2. **Monitor** the runtime operation of the related system to collect data about system and environment variables, events, and assurance deficits in the safety argument(s).

- 3. Analyse the collected operational data from the former activity to examine whether the defined thresholds are met, and to update the confidence in the associated claims.

- 4. **Respond** to operational events that affect safety assurance. Deciding on the appropriate response depends on a combination of factors including the impact of confidence in new data, the available response options already planned, the level of automation provided, and the urgency with which certain stakeholders have to be alerted.

In this section, we explain how using the described technique in Sect. 2 enables a through-life safety assurance, where we (1) identify a source of uncertainty, (2) provide a runtime monitoring mechanism, (3) analyse the collected operational data, and (4) suggest a response to the operational events.

- 1. Identify a source of uncertainty: Evidence supporting a claim about a prediction of a hardware failure rate may be obtained from different sources. Handbooks produced by commercial, military or government sources can support a claimed prediction of a hardware failure rate. A hardware vendor or an expert might also support such claims. The explicit logic of a claim about a failure rate prediction and its supported evidence is that the predicted likelihood of component C to fail during time T of operation is  $\lambda$  because a handbook, a vendor or an expert "says so". The implicit assumption of such claims is that the actual  $\lambda$  will conform to the predicted  $\lambda$  during the operational life. This assumption is an obvious source of *uncertainty* (i.e., lack of confidence) which can influence the level of confidence in the safety argument. Hence, it is particularly important to know whether or not the actual failure rate of a component during the operational life will be similar to the predicted (i.e., generic) rate as the evidence suggests.

- 2. Monitor the actual failure rate: Algorithm 1 provides the runtime monitoring logic through which the number of failures of a hardware component is continuously calculated during runtime.

- 3. Analyse the collected operational data: Algorithm 1 also analyses the calculated number of failures by comparing it with a predefined threshold.

4. Respond to operational events: If an observed  $\lambda$  exceeds the generic  $\lambda$  and it is not tolerated by the maximum allowed  $\lambda$ , then a safety contract is broken. The monitoring algorithm highlights broken contracts indicating that an additional safety countermeasure should be considered, such as replacing a hardware component with an ultra reliable component or add a redundant component. Since the contracts under monitoring by the algorithm is associated with ACPs in the safety argument, a broken contract indicates the affected GSN elements in the argument.

#### 5 Discussion and Conclusion

Numerous studies and data analysis have shown either a decreasing or increasing failure rate with time. Runtime monitoring enables a new source of data which improves our perception of some functions, components, and behaviours within safety critical systems. Monitoring a property of interest of a system component and analysing the collected data enable us to know more about this component (e.g., the way it behaves, fails, etc.). As a result, we can improve our confidence in safety based upon more conscious reasoning that replaces the intuitive evidence by more cognitive one. Some safety standards require monitoring and re-assessing the reliability parameters which were used during the design time. For example, IEC 61511-1 [9] requires operators to monitor and assess whether reliability parameters of the Safety Instrumented Systems (SIS) are in accordance with those assumed during the design time [10]. Although runtime monitoring is not a new technique, there is no single way to specify what to monitor, why and how. Safety contracts, on the other hand, are useful for building, reusing or maintaining safety critical systems. The cost of maintaining system components can be drastically reduced by using contracts as system developers may rework the components with knowledge of the constraints placed upon them [20].

In this paper, we proposed a novel technique to monitor the runtime of a system and detect the divergence between the failure rates (which were used in the safety analyses) and the observed failure rates in the operational life. The technique enables through-life safety assurance by utilising safety contracts to provide prescriptive data for what should be monitored, and what parts of the safety argument should be revisited to maintain system safety when a divergence is detected. Future work will focus on creating a more in-depth case study to validate both the feasibility and efficacy of the technique for software and hardware applications. We also plan to formally define safety contracts and to fully automate the application of the technique.

Acknowledgment. This work has been partially supported by the Swedish Foundation for Strategic Research (SSF) (through SYNOPSIS and FiC Projects) and the EU-ECSEL (through SafeCOP project).

## References

- Knight, J.C.: Safety critical systems: challenges and directions. In: Proceedings of the 24th International Conference on Software Engineering (ICSE), pp. 547–550, May 2002

- Jaradat, O., Sljivo, I., Habli, I., Hawkins, R.: Challenges of safety assurance for industry 4.0. In: European Dependable Computing Conference (EDCC). IEEE Computer Society, September 2017

- Jaradat, O., Graydon, P., Bate, I.: An approach to maintaining safety case evidence after a system change. In: Proceedings of the 10th European Dependable Computing Conference (EDCC), UK (2014)

- 4. Graydon, P.J., Holloway, C.M.: An investigation of proposed techniques for quantifying confidence in assurance arguments. Saf. Sci. **92**(Supplement C), 53–65 (2017)

- Denney, E., Pai, G., Habli, I.: Dynamic safety cases for through-life safety assurance. In: 2015 IEEE/ACM 37th IEEE International Conference on Software Engineering, vol. 2, pp. 587–590, May 2015

- 6. Reliability prediction basics. Technical report, ITEM Software Inc. (2007)

- Pittiglio, P., Bragatto, P., Delle Site, C.: Updated failure rates and risk management in process industries. Energy Procedia 45(Supplement C), 1364–1371 (2014). ATI 2013 - 68th Conference of the Italian Thermal Machines Engineering Association

- 8. Functional safety of electrical/electronic/programmable electronic safety-related systems. IEC 61508-4 (2010)

- 9. Functional safety Safety instrumented systems for the process industry sector. IEC 61511-1 (2016)

- Generowicz, M., Hertel, A.: Reassessing failure rates. Technical report, I&E Systems Pty Ltd. (2017)

- Rausand, M.: Reliability of Safety-critical Systems: Theory and Applications. Wiley, Hoboken (2014)

- 12. van Beurden, I., Goble, W.M.: The Key Variables Needed for PFDavg Calculation. White paper, Exida, Sellersville, PA 18960, USA, July 2015

- 13. Goble, W.M.: Control System Safety Evaluation and Reliability, 2nd edn. (1998)

- Rausand, M., Høyland, A.: System Reliability Theory: Models and Statistical Methods and Applications. Wiley, Hoboken (2004)

- van der Borst, M., Schoonakker, H.: An overview of PSA importance measures. Reliab. Eng. Syst. Saf. **72**(3), 241–245 (2001)

- Jaradat, O., Bate, I., Punnekkat, S.: Using sensitivity analysis to facilitate the maintenance of safety cases. In: Proceedings of the 20th International Conference on Reliable Software Technologies (Ada-Europe), pp. 162–176, June 2015

- Hawkins, R., Kelly, T., Knight, J., Graydon, P.: A new approach to creating clear safety arguments. In: Dale, C., Anderson, T. (eds.) Advances in Systems Safety, pp. 3–23. Springer, London (2011). https://doi.org/10.1007/978-0-85729-133-2\_1

- GSN Community Standard Version 1. Technical report, Origin Consulting (York) Limited, November 2011

- 19. Kane, A.: Runtime monitoring for safety-critical embedded systems. PhD thesis, Carnegie Mellon University, September 2015

- Bates, S., Bate, I., Hawkins, R., Kelly, T., McDermid, J., Fletcher, R.: Safety case architectures to complement a contract-based approach to designing safe systems. In: Proceedings of the 21st International System Safety Conference (ISSC) (2003)

## Tool-Supported Safety-Relevant Component Reuse: From Specification to Argumentation

Irfan Sljivo<br/>^ $^{1(\boxtimes)},$ Barbara Gallina<sup>1</sup>, Jan Carlson<sup>1</sup>, Hans Hansson<sup>1</sup>, and Stefano Puri<sup>2</sup>

<sup>1</sup> Mälardalen University, Västerås, Sweden {irfan.sljivo,barbara.gallina,jan.carlson,hans.hansson}@mdh.se <sup>2</sup> Intecs, SpA, Pisa, Italy stefano.puri@intecs.it

**Abstract.** Contracts are envisaged to support compositional verification of a system as well as reuse and independent development of their implementations. But reuse of safety-relevant components in safetycritical systems needs to cover more than just the implementations. As many safety-relevant artefacts related to the component as possible should be reused together with the implementation to assist the integrator in assuring that the system they are developing is acceptably safe. Furthermore, the reused assurance information related to the contracts should be structured clearly to communicate the confidence in the component. In this work we present a tool-supported methodology for contract-driven assurance and reuse. We define the variability on the contract level in the scope of a trace-based approach to contract-based design. With awareness of the hierarchical nature of systems subject to compositional verification, we propose assurance patterns for arguing confidence in satisfaction of requirements and contracts. We present an implementation extending the AMASS platform to support automated instantiation of the proposed patterns, and evaluate its adequacy for assurance and reuse in a real-world case study.

## 1 Introduction

Software-intensive systems are rarely developed from scratch. Instead, components developed previously are reused for building new systems [1]. The same trend is visible in safety-critical systems, which usually need to be assured that they are acceptably safe to be deployed. The assurance entails gathering a body of evidence in form of a safety assurance case to communicate that any unreasonable risk in the system has been mitigated. Due to this, reuse of components in such systems is not complete without the reuse of assurance information associated with the component. While reuse of safety-related components is very much present in safety-critical systems development, the lack of systematic approaches to managing reuse of both components and their accompanying assurance information has shown to be dangerous in the past [2].

<sup>©</sup> Springer International Publishing AG, part of Springer Nature 2018

A. Casimiro and P. M. Ferreira (Eds.): Ada-Europe 2018, LNCS 10873, pp. 19–33, 2018. https://doi.org/10.1007/978-3-319-92432-8\_2

To address the issue of reuse in safety-critical systems, some reuse principles have been promoted through the safety standards. For example, the automotive functional safety standard ISO 26262 [3] with its concept of Safety Element outof-Context (SEooC) for reuse of components together with the related safety assurance information. It promotes principles that should be followed to begin the assurance process on the level of the SEooC, which is being developed independently from the system in which it will be used. The purpose of the early start of the assurance process is to support the integrator of the SEooC in assuring their system according to the standard. Ideally, if all suppliers would provide their components as SEooC, the integrator should have an easier job of assuring that the integrated system is acceptably safe. The core aspect of SEooC development are assumptions on the context in which the SEooC component could be reused, such that their validation upon reuse establishes whether the component and the related assurance information is reusable in the particular context.

To support SEooC development and reuse, we have proposed to use *assump*tion/guarantee component contracts in our previous work [4]. A contract is a pair of assertions called assumptions and guarantees, where the component guarantees a certain behaviour, given that the environment in which it is deployed fulfils the assumptions [5]. Such contracts provide a systematic way to capture the context assumptions and relate them with the properties that the SEooC component implements. We have proposed to relate contracts with the assurance information [4] and support contract-driven assurance by automating the generation of assurance argument-fragments on satisfaction of both such contracts and the system requirements that can be validated via those contracts.

Reusable components such as SEooC are often characterised with parameters that are used to tailor the behaviour of the component in the different settings in which the component is reused. To address such need for variability at the contract level, we have made a distinction between strong and weak contracts [6]. On the one hand, the strong contracts are those whose assumptions should be met by every context in which the component is reused, hence its guarantees are always offered by the component. On the other hand, the weak contract assumptions do not need to be satisfied by every context in which the component is reused, but when they are met, only then the component offers the corresponding weak guarantees. This variability on the contract level can be used to identify which assumed safety requirements offered by the SEooC component are relevant in the system in which the SEooC is reused. Hence, the safety case information related to those requirements and contracts can also be identified for reuse. To set the ground for tool support, we have proposed a generic SEooC MetaModel (SEooCMM) that defines relationships between SEooC components, contracts, requirements and assurance assets [4]. The basic elements needed for the tool support are a system modelling tool compliant with the SEooCMM, a contract checking engine, and a safety case modelling tool.

In this paper we present our efforts to provide tool-support for contract-based design that incorporates strong and weak contracts as well as the automated

generation of assurance arguments. We turn to the AMASS<sup>1</sup> platform for our implementation as it includes the needed tools for system modelling (CHESS<sup>2</sup>), contract checking ( $OCRA^3$ ) and safety assurance case modelling ( $OpenCert^4$ ). Two challenges arise when using the AMASS platform for contract-driven reuse and assurance: (1) the contract-based design framework [7] implemented in OCRA does not distinguish between the strong and weak contracts; (2) the connection between the system and assurance modelling domains is not clearly defined. To address the first challenge, we define the strong and weak contracts in the scope of the contract-based framework implemented in OCRA. Moreover, we present how refinement checking can be adapted to support strong and weak contracts through the interaction of CHESS and OCRA. To address the second challenge, we first identify the information needed to perform contractdriven assurance and extend CHESS to allow for its modelling. We structure that information by extending the argument pattern for assurance of contract satisfaction to account for the hierarchical component decomposition defined through the notion of refinement. Then, we develop a transformation from the system model to the assurance model that automatically instantiates the defined argument-fragment for each component in the system. Finally, we validate the tool-supported contract-based assurance and reuse methodology in a real-world case study.

As assurance cases are gaining popularity, there is an increasing number of tools supporting their development with particular focus on automation capabilities. For example, Safety.Lab [8] focuses on model-based safety analysis and generates an argument structure from rich models of various safetyrelevant artefacts. The Eclipse-based *Resolute* tool [9] facilitates generating assurance arguments from architectural models. The Evidence Confidence Assessor (EviCA) [10] is a diagramming tool that supports automated generation of confidence arguments related to manually created arguments. The Advo-CATE [11] toolset includes a variety of automated features for assurance case creation and analysis. AdvoCATE automates instantiation of pre-developed argumentation pattern from a hazard and safety requirement analysis. While we also automatically instantiate a pre-developed pattern, we do so from architectural models enriched with assumption/guarantee contracts coupled with safetyrelevant artefacts. This allows us to filter the relevant artefacts and provide additional support for reuse and tailoring of context-specific automated argument generation.

The rest of the paper is organised as follows: In Sect. 2, we present some background information. We present the tool-supported methodology for contractdriven assurance and reuse in Sect. 3. In Sect. 4, we present our case study. Finally, we bring conclusions and indicate future work in Sect. 5.

<sup>&</sup>lt;sup>1</sup> AMASS - Architecture-driven, Multi-concern and Seamless Assurance and Certification of Cyber-Physical Systems, https://amass-ecsel.eu/.

$<sup>^2\ \</sup>rm https://www.polarsys.org/chess.$

<sup>&</sup>lt;sup>3</sup> https://ocra.fbk.eu/.

<sup>&</sup>lt;sup>4</sup> https://www.polarsys.org/projects/polarsys.opencert.

## 2 Background

In this section we first present the tools and concepts we build upon, and then we present the system description of the considered case study.

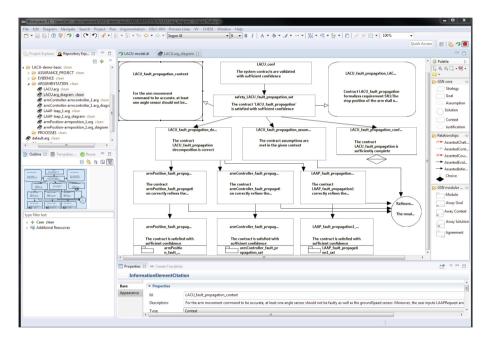

#### 2.1 AMASS Platform

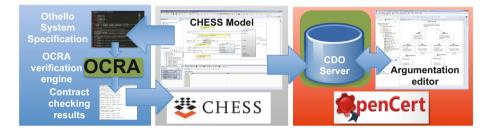

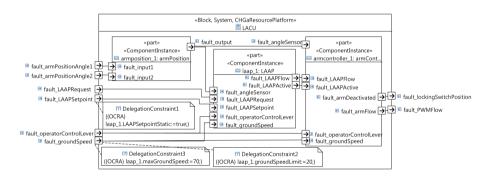

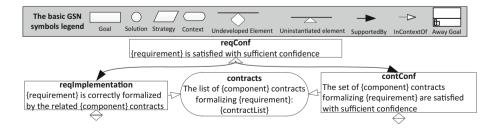

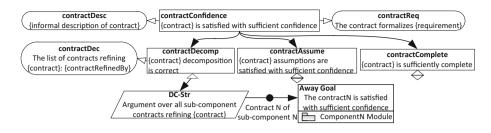

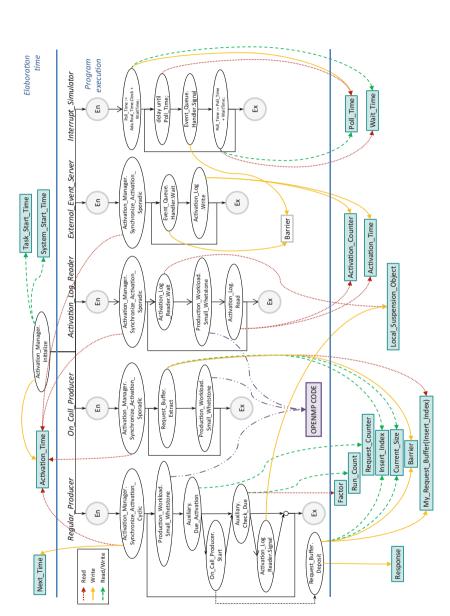

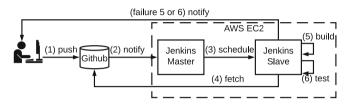

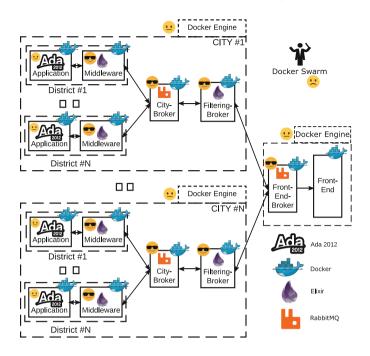

The AMASS platform encompasses different tools, but we focus on the three tools that facilitate system modelling (CHESS), formal verification of assumption guarantee contracts (OCRA), and assurance case modelling (OpenCert). An overview of the three tools is shown in Fig. 1. In the reminder of the section, we present the tools together with their underlying theoretical concepts.

Fig. 1. The overview of the tool information flow