# Bharathwaj Muthuswamy Santo Banerjee

# Introduction to Nonlinear Circuits and Networks

Introduction to Nonlinear Circuits and Networks

Bharathwaj Muthuswamy • Santo Banerjee

# Introduction to Nonlinear Circuits and Networks

Bharathwaj Muthuswamy Department of Physics QuEST Lab Stevens Institute of Technology Hoboken, NJ, USA Santo Banerjee Institute for Mathematical Research University Putra Malaysia Serdang, Malaysia

ISBN 978-3-319-67324-0 ISBN 978-3-319-67325-7 (eBook) https://doi.org/10.1007/978-3-319-67325-7

Library of Congress Control Number: 2018949725

© Springer International Publishing AG, part of Springer Nature 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

Dedicated to Leon O. Chua, Robert M. Fano, Lan J. Chu, and Richard B. Adler

# Preface

The purpose of this course-based text-book is to emphasize introductory concepts from classic ideas in nonlinear circuit theory:

- 1. The book is completely self-contained and does not assume any prior knowledge of circuit theory. It is simply assumed that the reader has taken a first-year undergraduate (elementary) course in differential and integral calculus, along with elementary physics courses in classical mechanics and electrodynamics (with an exposure to matrix algebra). Hence, this book should be accessible to any motivated individual who has taken the abovementioned courses.

- 2. The book also covers topics that are not typically found in standard circuit textbooks, such as:

- **Memristors**. The justification is that although (as the reader will learn from this book) memristors are not used in linear circuit theory, a memristor is the fourth fundamental circuit element. Hence, it is only logical that any text on circuit theory discuss memristors. Thus, ideally our book would have been titled *Introduction to Circuits and Networks*. But then a casual reader might mistake this book for emphasizing only linear circuit theory. However, as this book will show, nonlinear circuit theory (memristor included) is accessible to anyone with the correct background who is interested in fundamental circuit theoretic concepts.

- **Nonlinear chaotic circuits**. We believe that chaotic circuits elegantly integrate a variety of concepts from circuit theory and hence form a natural repository of "projects" for the reader to understand all the concepts discussed in this book.

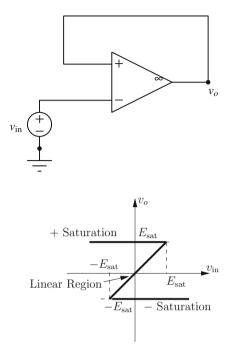

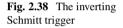

- Nonlinear operational amplifier circuits, for example, Schmitt triggers. As will be clear from this book, accurate analysis of Schmitt triggers will help dispel common misconcepts about the nature of hysteresis in electronic circuits and will also help the reader understand the deep concept of modeling.

- 3. Each chapter has illustrative examples, exercises, and a lab component. We will also have (maximum 20 min) conceptual videos for each chapter and end-of-chapter exercises (lab included) online. The purpose of these supplementary

videos is to (*a*) highlight major concepts in each chapter and (*b*) provide solutions (hints for open-ended problems) to end-of-chapter exercises. This extensive use of electronic aids is the "twenty-first century" approach to nonlinear circuits. In the process, we hope to "transform" fundamental ideas in nonlinear circuits from the classic works of Leon O. Chua and others. Nevertheless, the goal of this book's electronic aids is to supplement, not replace, rigor.

Over the course of a teaching career spanning 10 years at the University of California (UC) Berkeley, Dr. Muthuswamy has coordinated with Dr. Leon O. Chua and others to reintroduce nonlinear circuit theory at an elementary level. Much of the material in this book is thus derived from Dr. Chua's EE100 (Electronic Techniques for Engineering) lecture materials. This course was offered by the Electrical Engineering and Computer Sciences department at UC Berkeley for non-electrical engineering majors. Thus, the approach taken by EE100 (and this book) is a top-down view of circuit analysis where we discuss general principles and emphasize device modeling. Therefore, the material in this book can be adopted for an introductory course in circuit theory.

At the University of California, Berkeley, we were able to cover most (excluding memristors) of the material in this book in one semester. The material on chaotic circuits was used as a source of projects. For schools that are based on the shorter quarter system (10 weeks of instruction), we would suggest splitting the material in this book into two courses. The first course could cover Chaps. 1 and 2 (network elements). The second course would cover Chaps. 3–5, where Chaps. 3 and 4 discuss techniques of network analysis followed by Chap. 5 as a source of course projects. Another option would be to cover resistive networks in the first course and dynamic networks in the second course. Specifically:

- 1. First course—resistive networks: only excluding material on dynamic elements in Chaps. 1 and 2 (Sects. 1.9.3–1.9.5, 2.2.3, 2.2.4) and covering all of Chap. 3.

- 2. Second course—dynamic networks: cover dynamic elements in Chaps. 1 and 2 that were not covered in the first course, followed by Chaps. 4 and 5.

Hence, the way we have organized the chapters is based on the fact that, in circuit theory, the laws of elements are distinct from the laws of networks.

Our goal in writing this book is simple: a student who thoroughly understands the concepts in this book will be well prepared for any follow-up course in circuit theory. For readers who are further interested in advanced concepts, we are planning to write a follow-up volume, *Advanced Nonlinear Circuits and Networks*. A reader who thoroughly understands the material in both volumes will maximize knowledge gained from **any** follow-up electrical engineering course, since our books on circuit theory emphasize both the underlying mathematics and physical experiments.

Hoboken, NJ, USA Serdang, Malaysia Bharathwaj Muthuswamy Santo Banerjee

### Acknowledgements

There are a plethora of folks whom we have to thank. From Dr. Muthuswamy's perspective, first and foremost, he would like to thank his MS and PhD advisor Dr. Leon O. Chua for all his support and guidance. Particularly for this book, Dr. Chua guided us in organizing the content. His advice to extract simple yet novel concepts on nonlinear circuit theory from his classic works, *Introduction to Nonlinear Circuit Theory* and *Linear and Nonlinear Circuits*, paved the way for this book. Dr. Muthuswamy was also deeply influenced by conversations with Dr. H. Gopalakrishna Gadiyar and Dr. Ganesan from the Vellore Institute of Technology in the summer of 2014. Their suggestion was to "capture the nonlinear circuits knowledge" of Dr. Leon O. Chua. Thus, capturing that knowledge is the primary purpose of this book.

Ferenc Kovac, Carl Chun, and Dr. Pravin Varaiya from Berkeley have been both professional and personal mentors throughout the years. From Dr. Muthuswamy's academic career in Wisconsin, interactions with Dr. Jovan Jevtic and Dr. Gerald Thomas have been motivational and inspiring. Dr. Sunil T. Mathew from the University of Oklahoma has provided invaluable advice regarding the role of biological memristors. Dr. Muthuswamy would also like to thank his former colleagues at Tarana Wireless for their support when writing a draft version of this book for approval. The College of New Jersey (Dr. Muthuswamy's employer while writing the majority of the book) also deserves special thanks.

We would also like to thank the anonymous reviewers for helping us reformulate the content of this book, so as to make it sustainable. Without Springer's support throughout the writing process, this book would not have been possible. Dan Funke from the College of New Jersey also read through the manuscript and provided valuable feedback.

Dr. Muthuswamy would also like to thank his family for their moral support throughout the process: daughters Shambavi and Thejasvi, father M.G. Muthuswamy, mother Chandra Muthuswamy, brother Karthikeyan Muthuswamy, and sister-in-law Mamta. Last but not the least, Dr. Muthuswamy would like to thank his spiritual advisor, Rajan Kurunthappan and family, for their continued unconditional support over the last two decades.

## **Mathematical Notation**

The mathematical notation used in this book is standard [15]; nevertheless, this section clarifies the notation used throughout the book.

- Lowercase letters from the Latin alphabet (a-z) are used to represent variables, with italic script for scalars and bold invariably reserved for vectors. The letter t is of course always reserved for time. n is usually reserved for the dimension of the state. j is used for √-1, in accordance with the usual electrical engineering convention. Mathematical constants such as π, e, and h (Planck's constant) have their usual meaning. Other constant scalars are usually drawn from lowercase Greek alphabet. SI units are used.

- 2. Independent variable in functions and differential equations is time (unless otherwise stated) because physical processes change with time.

- 3. Differentiation is expressed as follows. Time derivatives use Leibniz's  $(\frac{dy}{dx})$ , for example) or Newton's notation: one, two, or three dots over a variable correspond to the number of derivatives and a parenthetical superscripted numeral for higher derivatives. Leibniz's notation is used explicitly for non-time derivatives.  $\partial$  is the usual symbol for indicating partial derivatives.

- 4. Real-valued functions, whether scalar- or vector-valued, are usually taken (as conventionally) from lowercase Latin letters *f* through *h*, *r*, and *s*, along with *x* through *z*.

- 5. Vector-valued functions and vector fields are boldfaced as well, the difference between the two being indicated by the argument font, hence  $\mathbf{f}(x)$  and  $\mathbf{f}(\mathbf{x})$ , respectively.

- 6. Constant matrices and vectors are represented with capital and lowercase letters, respectively, from the beginning of the Latin alphabet. Vectors are again bolded.

- 7. In the context of linear time-invariant systems, the usual conventions are respected: **A** is the state matrix; **B**(**b**) is the input matrix (vector).

- 8. Subscripts denote elements of a matrix or vector:  $\mathbf{d}_i$  is the *i*th column of  $\mathbf{D}$ ;  $x_j$  is the *j*th element of  $\mathbf{x}$ . Plain numerical superscripts on the other hand may indicate exponentiation, a recursive operation, or simply a numbering

depending on the context. A superscripted T indicates matrix transpose. I is reserved for the identity matrix. All vectors are assumed to be columns. det stands for determinant of a square matrix.

- 9.  $\Sigma_i$  is used for summations, sampling interval is symbolized by T, and  $\in$  denotes set inclusions.

- 10. Calligraphic script (*R*, etc.) is reserved for sets which use capital letters. Elements of sets are then represented with the corresponding lowercase letter. Excepted are the well-known number sets which are rendered in doublestruck bold: N, Z, Q, R, and C for the naturals, integers, rationals, reals, and complex numbers, respectively. The natural numbers are taken to include 0. Restrictions to positive or negative subsets are indicated by a superscripted + or -. The symbol <sup>△</sup>= is used for definitions. ∀ and ∃ have the usual meaning of "for all" and "there exists," respectively.

# **Conventions Used in the Book**

Each chapter starts with a visual epigraph: the purpose is to evoke the intellectual curiosity of the reader. Chapters are divided into sections and subsections for clarity.

Figures, equations, and definitions are numbered consecutively in each chapter. The book has a variety of solved examples in light gray shade.

Solved Examples

All references are placed at the end of each chapter for convenience. We use a number surrounded by square brackets for in-text references: [5]. We have strived to give credit to the original authors, keeping in mind Stigler's law of eponymy. If we incorrectly attributed an idea to the wrong original contributor, we sincerely apologize.

Important terminology and concepts are **boldfaced**. Important techniques are **framed**. In the electronic copy of this book, online URLs are colored and hyperlinked in midnight blue for ease of access. Also, we have hyperlinked any numbered definitions, equations, figures, etc. Hence, it would be prudent to purchase the ebook.

Figures were generated using a combination of xcircuit, xfig, tikZ, and PNG screen captures in UNIX that were converted to EPS.

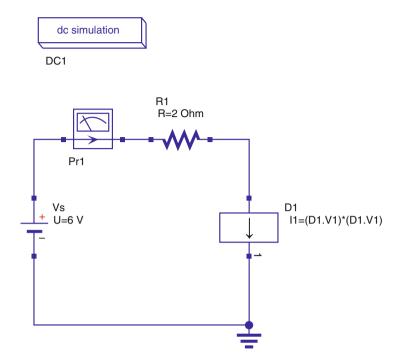

We utilize Quite-Universal Circuit Simulator (QUCS), a functional open-source circuit simulator, which is introduced in lab component for Chap. 1. Installation instructions can be found in Appendix A. The mathematical plots were generated using SageMath. Computer code is in verbatim font. We have not given an extensive tutorial on SageMath because of the abundance of excellent tutorials online. An unintended consequence is: this book should help the reader learn a mathematical simulation tool (like SageMath) via the material (especially Chap. 5). QUCS and SageMath simulation files are available online at the companion website: http://www.harpgroup.org/muthuswamy/IntroToNonlinearCircuitsAndNetworks/.

On a concluding remark, when you find typos in the book please contact the authors with constructive comments: bharath.berkeley@gmail.com, santo-ban@gmail.com.

# Contents

| Terminal Network Elements                                  |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|

| The Discipline of Circuit Theory                           |  |  |  |  |

| Fundamental Circuit Variables                              |  |  |  |  |

| The Simultaneity Postulate in Lumped Circuit Theory        |  |  |  |  |

| Reference Directions                                       |  |  |  |  |

| Kirchhoff's Laws                                           |  |  |  |  |

| 1.5.1 Kirchhoff's Current Law (KCL)                        |  |  |  |  |

| 1.5.2 Kirchhoff's Voltage Law (KVL)                        |  |  |  |  |

| From Circuits to Graphs: The Definition of a Network       |  |  |  |  |

| 1.6.1 Generality of Digraphs: Tellegen's Theorem Example   |  |  |  |  |

| Circuit Theory from Electromagnetic Field Theory           |  |  |  |  |

| 1.7.1 The Art of Modeling                                  |  |  |  |  |

| 1.7.2 KCL and KVL from Field Theory: A Very Brief          |  |  |  |  |

| Overview                                                   |  |  |  |  |

| Characterization of a Two-Terminal Black Box               |  |  |  |  |

| Two-Terminal Elements                                      |  |  |  |  |

| 1.9.1 Resistors                                            |  |  |  |  |

| 1.9.2 Independent Sources                                  |  |  |  |  |

| 1.9.3 Inductors and Capacitors                             |  |  |  |  |

| 1.9.4 Memristors                                           |  |  |  |  |

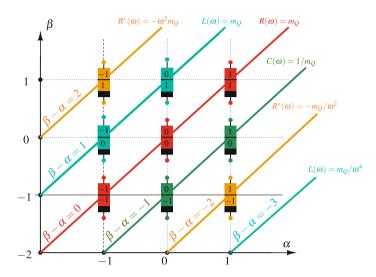

| 1.9.5 Higher-Order Circuit Elements                        |  |  |  |  |

| Series and Parallel Connections of Resistors               |  |  |  |  |

| 1 Conclusion                                               |  |  |  |  |

| ises                                                       |  |  |  |  |

| : Introduction to Quite Universal Circuit Simulator (QUCS) |  |  |  |  |

| ences                                                      |  |  |  |  |

|                                                            |  |  |  |  |

| 2 | Mult  | i-Termi | inal Network Elements                                           | 63  |

|---|-------|---------|-----------------------------------------------------------------|-----|

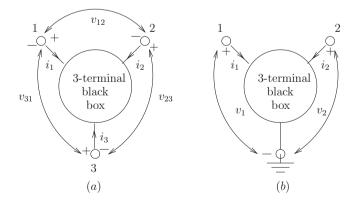

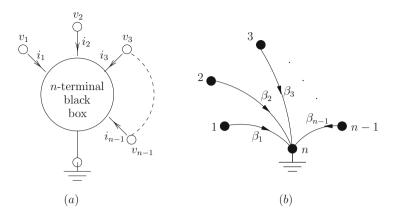

|   | 2.1   | Chara   | cterization of a Multi-Terminal Black Box                       | 63  |

|   | 2.2   | Three   | -Terminal Resistors, Inductors, and Capacitors                  | 67  |

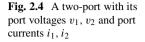

|   |       | 2.2.1   | Two-Port Representation                                         | 67  |

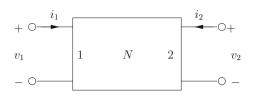

|   |       | 2.2.2   | Three-Terminal Resistors                                        | 79  |

|   |       | 2.2.3   | Three-Terminal Inductors                                        | 84  |

|   |       | 2.2.4   | Three-Terminal Capacitors                                       | 88  |

|   | 2.3   | Three   | -Terminal Memristors                                            | 88  |

|   | 2.4   | The T   | hree-Port Circulator                                            | 88  |

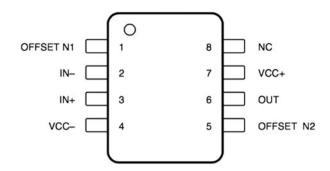

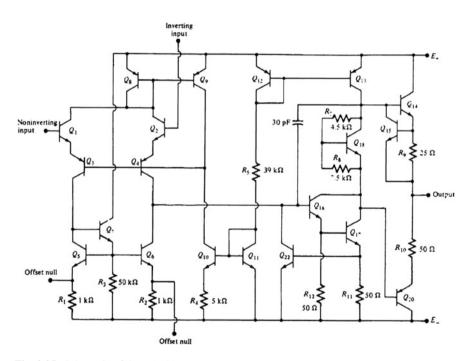

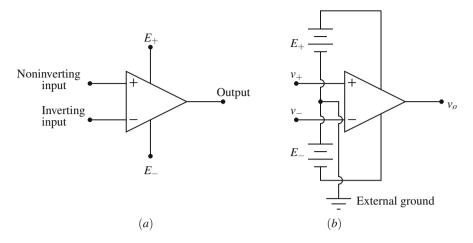

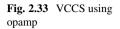

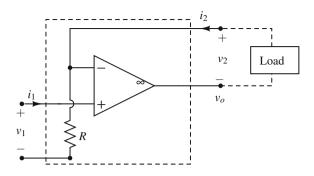

|   | 2.5   | Opera   | tional Amplifier (Opamp)                                        | 91  |

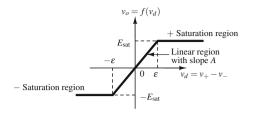

|   |       | 2.5.1   | Device Description, Characteristics, and Model                  | 91  |

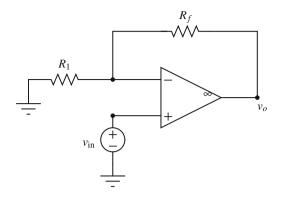

|   |       | 2.5.2   | Linear Opamp Circuits                                           | 97  |

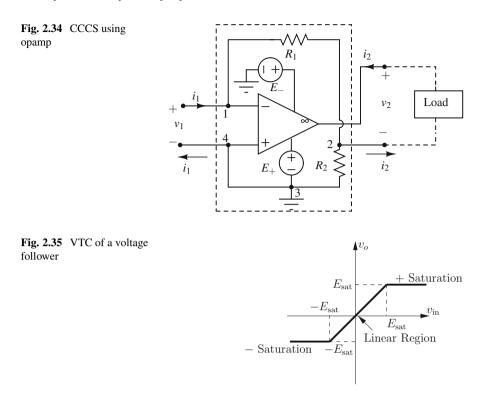

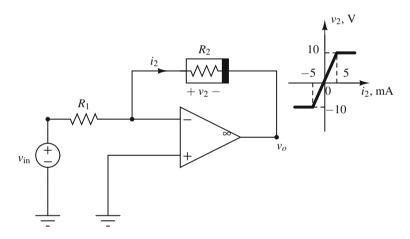

|   |       | 2.5.3   | Nonlinear Opamp Circuits                                        | 106 |

|   |       | 2.5.4   | A Family of Two-Port Resistors                                  | 113 |

|   |       | 2.5.5   | Current Feedback Opamps                                         | 122 |

|   | 2.6   | Concl   | usion                                                           | 124 |

|   |       |         |                                                                 | 125 |

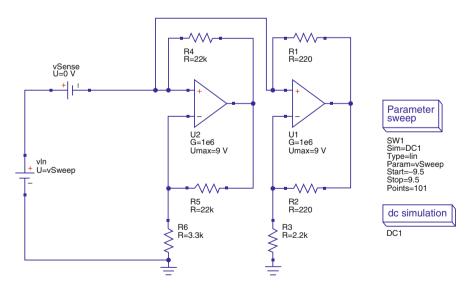

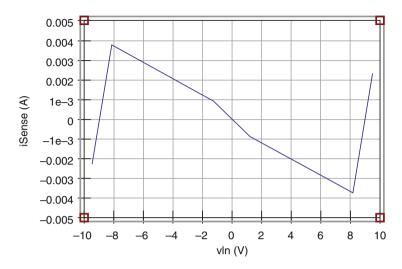

|   | Lab 2 | : Nonir | verting Schmitt Trigger VTC                                     | 129 |

|   | Refer | ences.  |                                                                 | 132 |

| 3 | Resis | tive No | nlinear Networks                                                | 135 |

|   | 3.1   | The O   | perating Point Concept                                          | 136 |

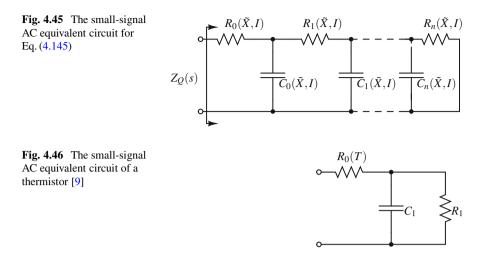

|   |       | 3.1.1   | Small Signal Analysis                                           | 141 |

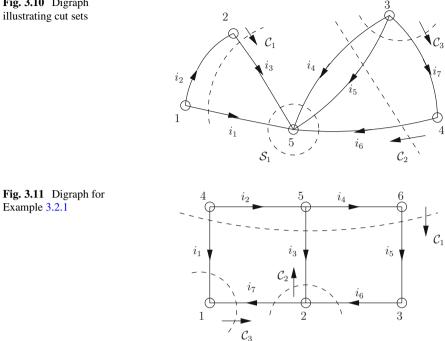

|   | 3.2   | Matrix  | x Formulation of Kirchhoff's Laws                               | 149 |

|   |       | 3.2.1   | Cut Sets, Hinged Graphs, and Linear Independence                | 149 |

|   |       | 3.2.2   | Independent KCL Equations                                       | 154 |

|   |       | 3.2.3   | Independent KVL Equations                                       | 157 |

|   |       | 3.2.4   | A Proof of Tellegen's Theorem                                   | 158 |

|   |       | 3.2.5   | The Relation Between Kirchhoff's Laws and                       |     |

|   |       |         | Tellegen's Theorem                                              | 159 |

|   | 3.3   | An In   | troduction to General Resistive Circuit Analysis                | 159 |

|   | 3.4   | Nodal   | Analysis for Resistive Circuits                                 | 161 |

|   |       | 3.4.1   | Formulation in Terms of Reduced Incidence Matrix                | 163 |

|   |       | 3.4.2   | Existence and Uniqueness of Solutions                           | 167 |

|   |       | 3.4.3   | Node Equation Formulation: Nonlinear Resistive                  |     |

|   |       |         | Circuits                                                        | 168 |

|   | 3.5   |         | au Analysis for Resistive Circuits                              | 170 |

|   |       | 3.5.1   | Tableau Equation Formulation: Nonlinear Resistive      Circuits | 174 |

|   | 3.6   | Gener   | al Properties of Linear Resistive Circuits                      | 174 |

|   | 5.0   | 3.6.1   | Superposition Theorem                                           | 170 |

|   |       | 3.6.2   | Thévenin-Norton Theorem                                         | 180 |

|   | 3.7   |         | General Properties of Nonlinear Resistive Circuits              | 180 |

|   | 5.1   | 3.7.1   | Strict Passivity                                                | 186 |

|   |       | 3.7.1   | Strict Passivity                                                | 180 |

|   |       | 5.1.4   |                                                                 | 107 |

|   | 3.8                        | Conclusion                                                       | 191 |  |  |  |

|---|----------------------------|------------------------------------------------------------------|-----|--|--|--|

|   | Lab 3                      | B: DC Simulation in QUCS                                         | 193 |  |  |  |

|   | Exerc                      | cises                                                            | 194 |  |  |  |

|   | Refe                       | rences                                                           | 197 |  |  |  |

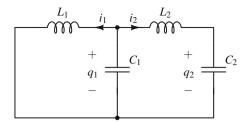

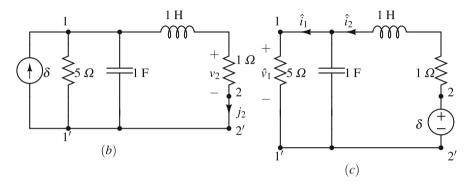

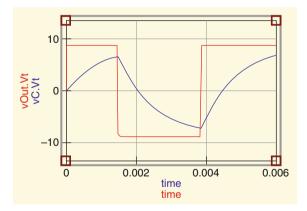

| 4 | Dynamic Nonlinear Networks |                                                                  |     |  |  |  |

|   | 4.1                        | Basic Concepts of Dynamic Nonlinear Networks                     | 199 |  |  |  |

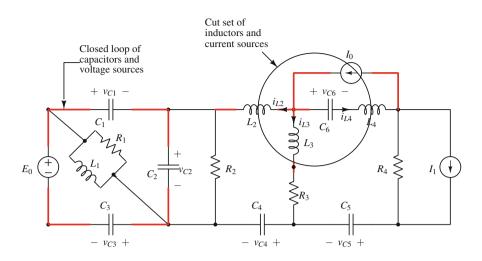

|   |                            | 4.1.1 Order of Complexity                                        | 200 |  |  |  |

|   |                            | 4.1.2 Principles of Duality                                      | 208 |  |  |  |

|   | 4.2                        | Time Domain Analysis of <i>n</i> th-Order Nonlinear Networks     | 212 |  |  |  |

|   |                            | 4.2.1 First-Order Circuits                                       | 213 |  |  |  |

|   |                            | 4.2.2 General Dynamic Circuits                                   | 238 |  |  |  |

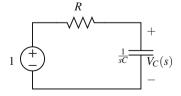

|   | 4.3                        | Frequency Domain Analysis of Linear Time-Invariant Circuits      | 251 |  |  |  |

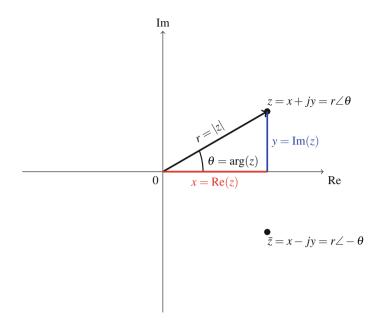

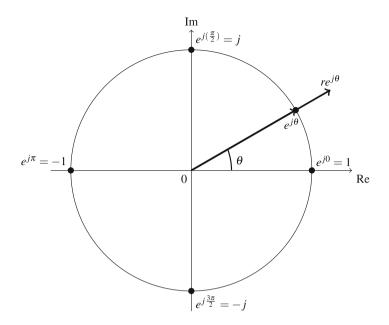

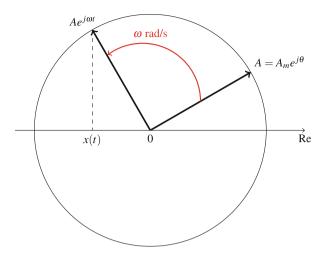

|   |                            | 4.3.1 Complex Numbers and Phasors                                | 252 |  |  |  |

|   |                            | 4.3.2 Sinusoidal Steady-State Analysis Using Phasors             | 258 |  |  |  |

|   |                            | 4.3.3 Laplace Transforms                                         | 266 |  |  |  |

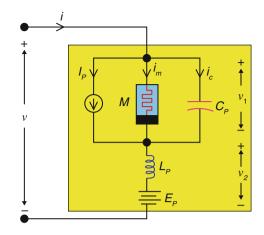

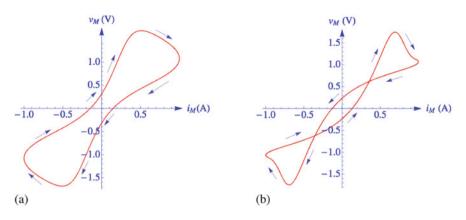

|   | 4.4                        | Memristive Networks                                              | 272 |  |  |  |

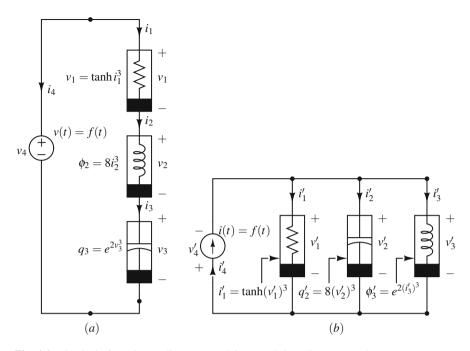

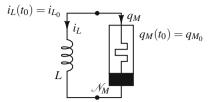

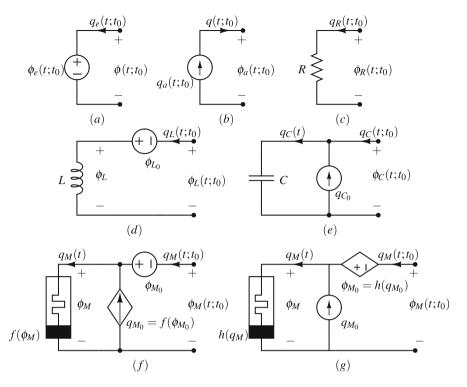

|   |                            | 4.4.1 Flux-Charge Analysis Method (FCAM)                         | 272 |  |  |  |

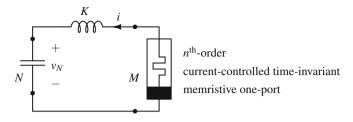

|   |                            | 4.4.2 Memristive Devices                                         | 274 |  |  |  |

|   | 4.5                        | Energy Approach: Lagrangian and Hamiltonian                      | 282 |  |  |  |

|   | 4.6                        | Miscellaneous Topics                                             | 290 |  |  |  |

|   |                            | 4.6.1 Reciprocity                                                | 290 |  |  |  |

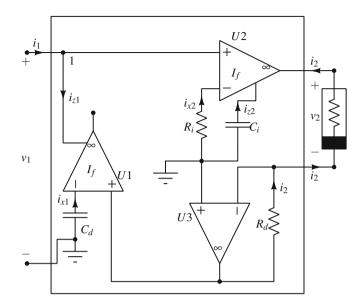

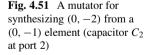

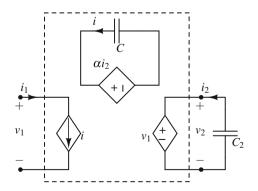

|   |                            | 4.6.2 Synthesis of Higher-Order Circuit Elements                 | 293 |  |  |  |

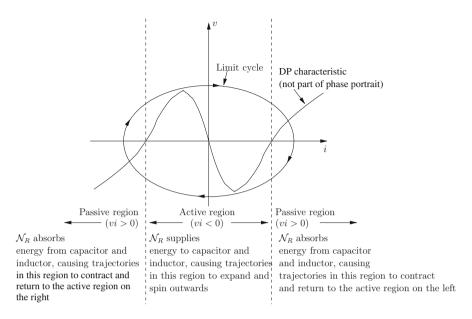

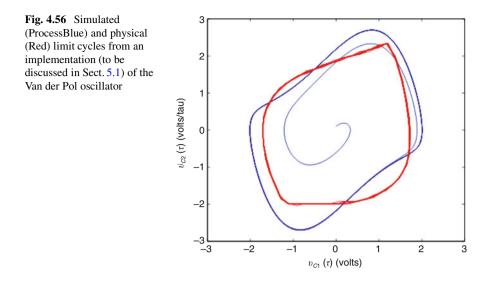

|   |                            | 4.6.3 Limit Cycles                                               | 296 |  |  |  |

|   | 4.7                        | Conclusion                                                       | 304 |  |  |  |

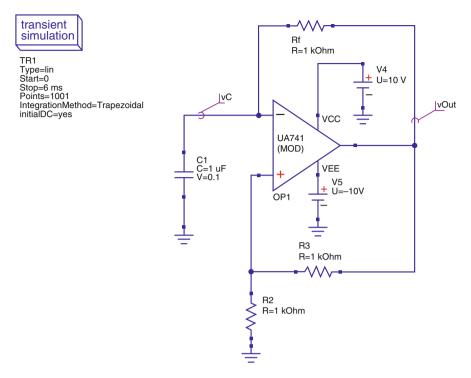

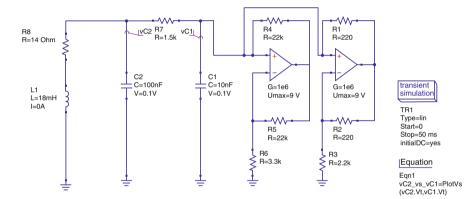

|   | Lab 4                      | 4: Relaxation Oscillator (Transient Simulation) and High-Pass    |     |  |  |  |

|   |                            | filter (AC Simulation)                                           | 306 |  |  |  |

|   | Exerc                      | cises                                                            | 306 |  |  |  |

|   | Refe                       | rences                                                           | 313 |  |  |  |

| 5 | Chao                       | <b>DS</b>                                                        | 315 |  |  |  |

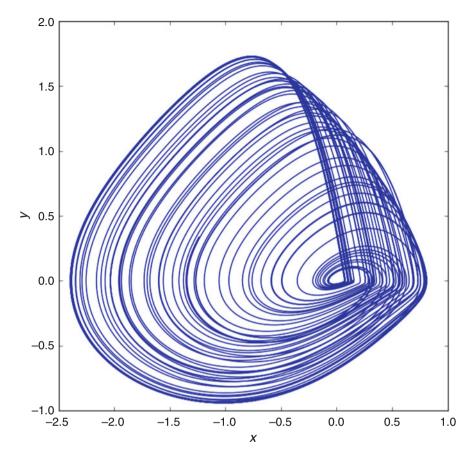

|   | 5.1                        | An Introduction to Chaos                                         |     |  |  |  |

|   | 5.2                        | A History of Chaos in Circuit Theory                             | 328 |  |  |  |

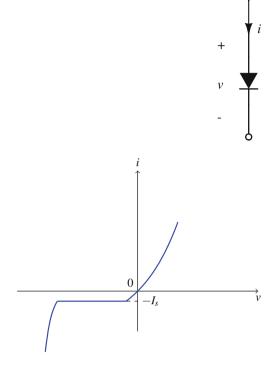

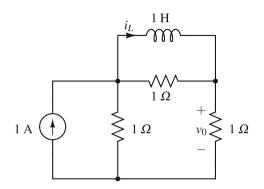

|   | 5.3                        | Chaos from Physical Nonlinearities: <i>pn</i> -Junctions and PWL |     |  |  |  |

|   |                            | Inductors                                                        | 332 |  |  |  |

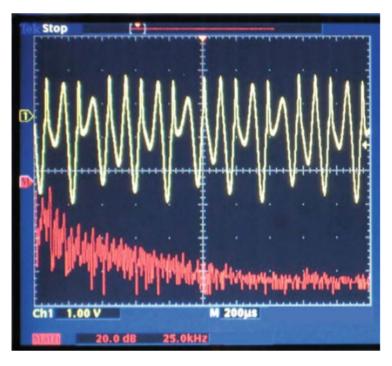

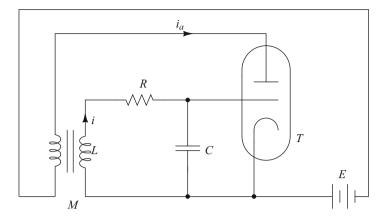

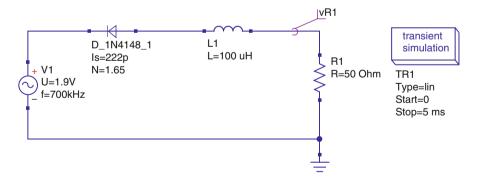

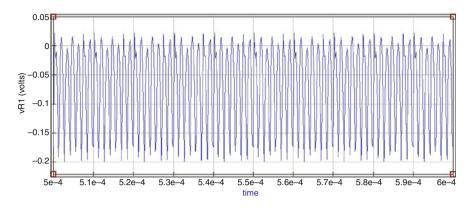

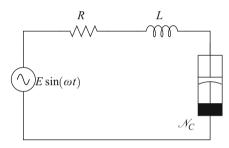

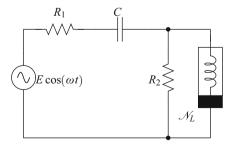

|   |                            | 5.3.1 RLD Chaotic Circuit                                        | 332 |  |  |  |

|   |                            | 5.3.2 PWL Inductor Circuit                                       | 334 |  |  |  |

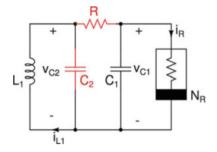

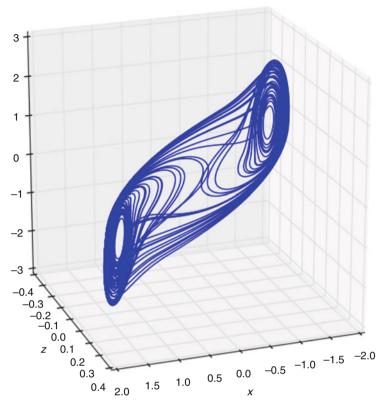

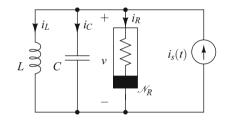

|   | 5.4                        | Memristor Based Chaotic Circuits                                 |     |  |  |  |

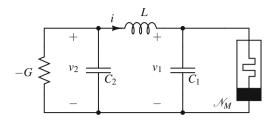

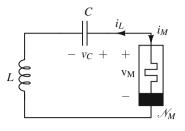

|   |                            | 5.4.1 Muthuswamy-Chua Circuit                                    | 335 |  |  |  |

|   | 5.5                        | Implementing the Duffing Oscillator Using a Higher-Order         |     |  |  |  |

|   |                            | Element                                                          | 343 |  |  |  |

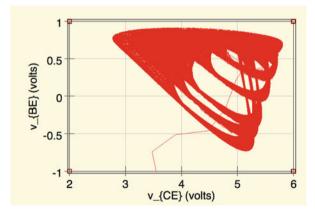

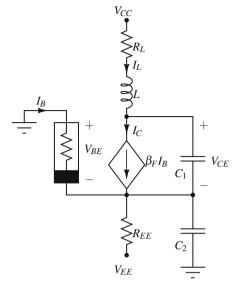

|   | 5.6                        | Transistor Based Chaotic Circuits                                | 344 |  |  |  |

|   | 5.7                        | Conclusion to This Book                                          | 347 |  |  |  |

|   | Exerc                      | cises                                                            | 348 |  |  |  |

|   | Lab 5                      | 5: Capstone Chaos Project(s)                                     | 349 |  |  |  |

|   | Refe                       | rences                                                           | 350 |  |  |  |

| A Installing QUCS |       |         |     |  |  |  |

|-------------------|-------|---------|-----|--|--|--|

|                   | A.1   | Windows | 353 |  |  |  |

|                   | A.2   | OS X    | 353 |  |  |  |

|                   |       | Linux   |     |  |  |  |

|                   | Refer | ence    | 354 |  |  |  |

| Solutions         |       |         |     |  |  |  |

| In                | Index |         |     |  |  |  |

# Acronyms

- AC Alternating Current BJT Bipolar Junction Transistor

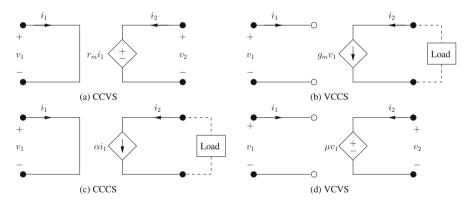

- CCCS Current-Controlled Current Source

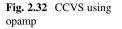

- CCVS Current-Controlled Voltage Source

- CFOA Current Feedback Operational Amplifier

- DC Direct Current

- DIP Dual Inline Package

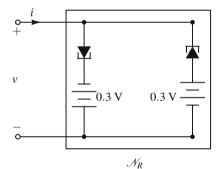

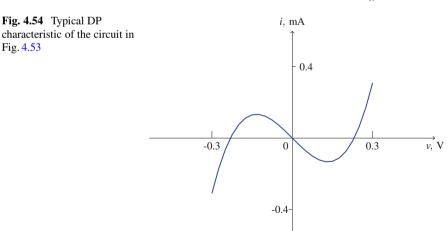

- DP Driving-Point

- FCAM Flux Charge Analysis Method

- KCL Kirchhoff's Current Law

- KVL Kirchhoff's Voltage Law

- MNA Modified Nodal Analysis

- NIC Negative Impedance Converter

- PWL Piecewise-Linear

- VCCS Voltage-Controlled Current Source

- VCVS Voltage-Controlled Voltage Source

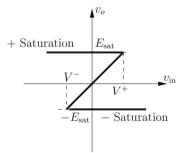

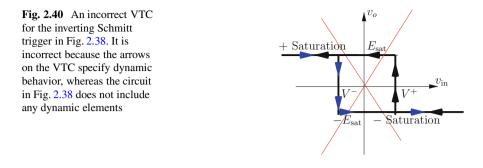

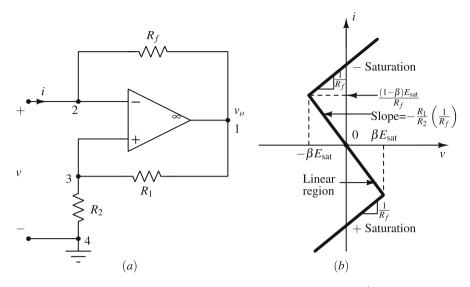

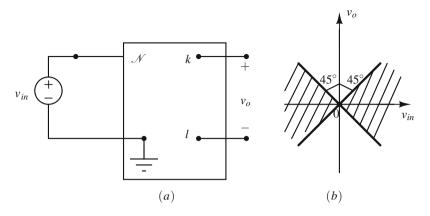

- VTC Voltage Transfer Characteristic

# Chapter 1 Two-Terminal Network Elements

Chua, L. O. Memristor - The Missing Circuit Element [2]

**Abstract** This chapter will set the stage for the rest of this book. We will start by discussing what is the aim of circuit theory, what are the fundamental circuit variables, and when the techniques in this book are valid: the lumped circuit approximation holds (frequencies of interest are not too high). We will discuss the concepts of Kirchhoff's laws, basic circuit topology, Tellegen's theorem, and twoterminal circuit elements.

#### 1.1 The Discipline of Circuit Theory

Circuit<sup>1</sup> theory is a fundamental engineering discipline that pervades all electrical engineering [5, 9]. For the present, by physical circuit, we mean any interconnection of electrical devices. Familiar examples of electrical devices include resistors, diodes, transistors, operational amplifiers (opamps), etc. The goal of circuit theory is to predict the electrical behavior of physical circuits. The purpose of these predictions is to improve their design: in particular, to decrease their cost and improve their performance under all conditions of operation (e.g., temperature effects, aging effects, possible fault conditions, etc.).

<sup>&</sup>lt;sup>1</sup>In this book, we will use circuits and networks interchangeably, the justification will be discussed in Sect. 1.6. Also, at the outset, we encourage the reader to familiarize themselves with the companion website: http://www.harpgroup.org/muthuswamy/IntroToNonlinearCircuitsAndNetworks/.

<sup>©</sup> Springer International Publishing AG, part of Springer Nature 2019

B. Muthuswamy, S. Banerjee, Introduction to Nonlinear Circuits and Networks, https://doi.org/10.1007/978-3-319-67325-7\_1

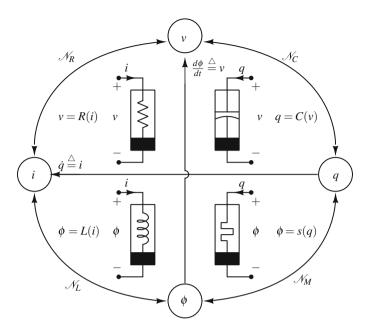

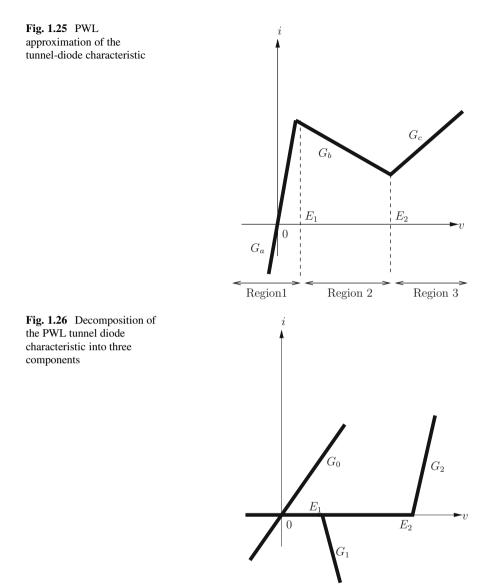

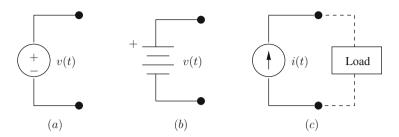

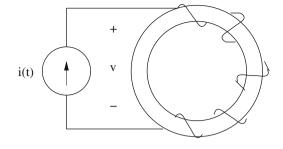

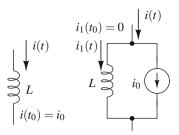

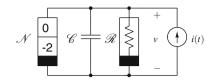

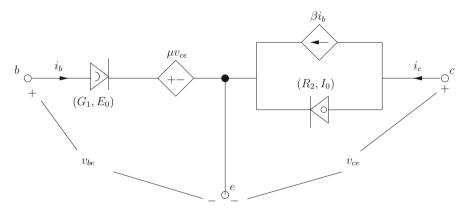

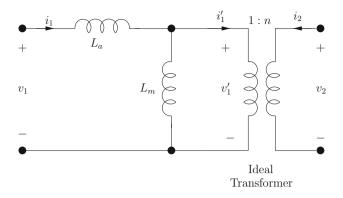

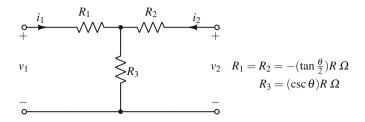

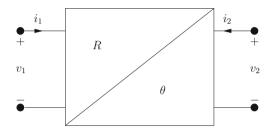

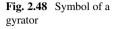

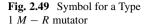

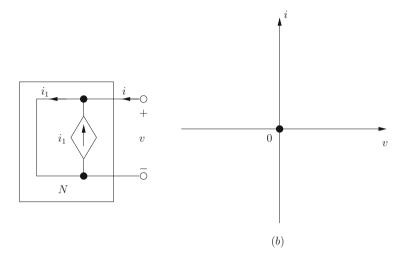

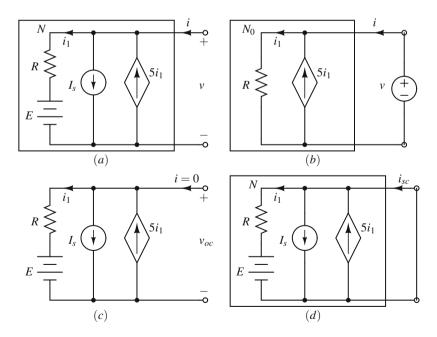

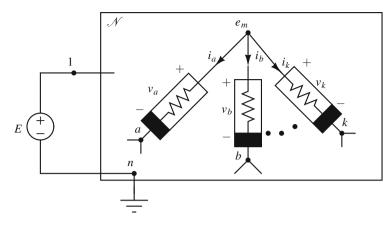

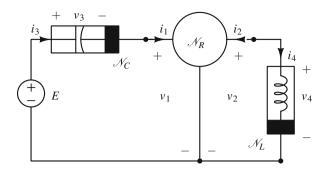

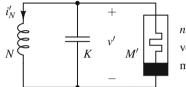

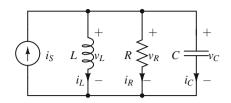

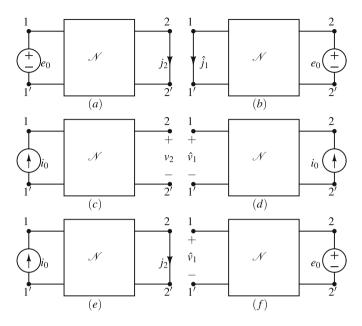

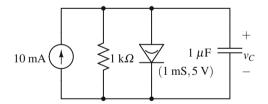

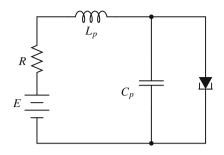

Fig. 1.1 The four fundamental two-terminal circuit elements along with the associated reference directions (Sect. 1.4) relate the fundamental circuit variables, through the **laws of elements**. The elements starting counterclockwise from the top-left are the **resistor**, **inductor**, **memristor**, and **capacitor**. Note that current is defined as the rate of flow of charge. There are **two mutually exclusive** definitions of voltage from electromagnetic field theory, refer to Sect. 1.2. The symbols used for the fundamental circuit elements are standard for nonlinear circuit elements, the reader may be familiar with the circuit symbol for the linear counterparts (excluding the memristor), see Sect. 1.9.4

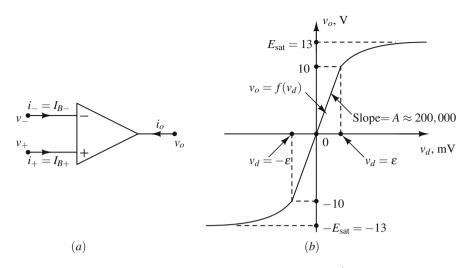

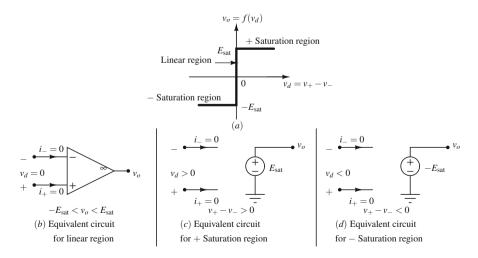

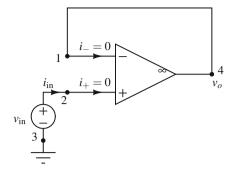

Probably the most fascinating aspect is that lumped circuit theory uses only four fundamental circuit variables: current, charge, voltage and flux-linkage (flux). Moreover, current and voltage are related to charge and flux (Eqs. (1.3) and (1.4) respectively). Thus, fundamentally we have only four elements that are characterized by a mathematical relation between the abovementioned four circuit variables at the element's terminals [10], as shown in Fig. 1.1 [16].

Hence to start our study of circuit theory, we will first discuss the fundamental circuit variables, the topic of Sect. 1.2.

#### **1.2 Fundamental Circuit Variables**

We could say the advent of electricity [1] occurred with the discovery that dry substances such as amber tend to repel or attract each other upon being rubbed by different materials such as silk. This phenomenon was first explained by postulating the existence of a certain basic electrical quantity called the "electric charge" (charge), mathematical symbol q, which may be either positive or negative. Like

charges exert a force of repulsion and unlike charges exert a force of attraction. The practical unit of charge is called the **coulomb** and has been defined to be equivalent to the total charge possessed by  $6.24 \times 10^{18}$  electrons. Charge can be measured by instruments such as the electroscope.

Since charged bodies exert forces on one another, energy or work is involved whenever one charged body is moved in the vicinity of another charged body. Hence if w is the work done by moving a charge q from point j to point k (assuming w is independent of the path taken),<sup>2</sup> the potential difference or voltage between these points is defined as the work per unit charge.

$$v_{jk} = \frac{w}{q} \tag{1.1}$$

Observe that the magnitude of the charge is arbitrary; only the ratio between work and charge is important. Hence, the incremental work dw required to move an incremental test charge dq from point j to point k must also satisfy Eq. (1.1). Thus:

$$v_{jk} = \frac{dw}{dq} \tag{1.2}$$

We will delete the subscripts j and k when there is no possibility of confusion and simply express voltage as v. The unit of voltage is called the **volt** and is measured using a voltmeter.

Charges can be caused to flow from one charged body to another by connecting a conducting wire between the two bodies. Hence, the quantity "rate of flow of charge" becomes very useful, and it has been given the name current with symbol i. By definition,

$$i = \frac{dq}{dt} \tag{1.3}$$

The unit of current is the **ampere**. One ampere represents a charge flowing at the rate of one coulomb per second. Current flow can be measured by an ammeter.

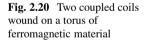

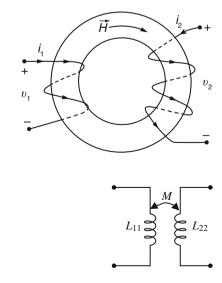

In 1819, Hans Christian Oersted discovered that current flowing through a wire produced a force on a compass needle in the vicinity of the wire. This indicates that the current (or moving charge) produces a magnetic field. This effect can be explained by the generation of a magnetic flux  $\lambda$  by the current. If the conductor is wound into a coil of *n* turns, then by defining  $\phi = n\lambda$  to be the flux-linkage, Faraday discovered that the voltage between the two terminals of the coil is given by

$$v = \frac{d\phi}{dt} \tag{1.4}$$

The unit of flux-linkage is the weber. Flux-linkage can be measured by a fluxmeter.

$<sup>^{2}</sup>$ This assumption is valid only if the simultaneity postulate is satisfied, we will discuss more in Sect. 1.3.

#### 1.3 The Simultaneity Postulate in Lumped Circuit Theory

Having discussed the fundamental circuit variables, the next question we need to address is: when are the techniques discussed in this book valid? The answer to this question is of paramount importance because the domain of application for circuit theory is extremely broad. For example, the size of circuits varies enormously: from very large-scale integrated circuits which include over a billion transistors on a chip the size of a fingernail to telecommunication circuits and power networks that span continents [9]. Throughout this book we shall consider only **lumped circuits** [9]. For a physical circuit to be considered lumped, its physical dimension must be small enough so that, for the problem at hand, **electromagnetic waves propagate across the circuit virtually instantaneously**. Consider the following example:

*Example 1.3.1* Consider an audio circuit whose highest frequency of interest is f = 20 KHz. Discuss the lumped circuit approximation.

**Solution** For electromagnetic waves, f = 20 KHz corresponds to a wavelength of:

$$\lambda = \frac{c}{f}$$

$$= \frac{3 \times 10^8 \text{ m/s}}{2.0 \times 10^4 \text{ s}^{-1}}$$

$$= 15 \text{ km}$$

Based on the calculations above, even if the circuit is spread across a tennis court, the size of the circuit is very small compared to the shortest wavelength of interest  $\lambda$ .

**Definition 1.1 (Lumped Circuit Approximation)** Lumped circuit approximation is valid if  $d \ll c \cdot \Delta t$ , where *d* is the largest dimension of the circuit,  $\Delta t$  the shortest time of interest, and *c* is the velocity of light.

When the conditions in Definition 1.1 are satisfied, electromagnetic theory proves [10] and experiments show that the lumped circuit approximation holds; namely, throughout the physical circuit the current i(t) through any device terminal and the voltage difference v(t) across any part of terminals, at any time t, are well-defined.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Unless otherwise stated, we will assume from now on throughout the book that analogous statements are true for q(t) and  $\phi(t)$ . In this case, we can equivalently discuss q(t) through any device terminal and  $\phi(t)$  across any part of the terminals.

#### 1.4 Reference Directions

*Example 1.3.2* Consider a circuit on a chip whose extent is 1 mm. Let the shortest signal time of interest be 0.1 ns. Discuss the lumped circuit approximation from Definition 1.1.

**Solution** Again, since electromagnetic waves travel at the speed of light, the time it would take for the electromagnetic wave to travel 1 mm is:

$$t = \frac{d}{c}$$

$$= \frac{1 \times 10^{-3} \text{ m}}{3 \times 10^8 \text{ m/s}}$$

$$= 3.3 \text{ ps}$$

Therefore the propagation time in comparison with the shortest signal time of interest is negligible and hence the lumped circuit approximation is valid.

Based on Examples 1.3.1 and 1.3.2, roughly speaking, the higher the frequency of operation, the smaller the device's physical dimension in order for the lumped circuit approximation to be satisfied. From an electromagnetic theory point of view, a lumped circuit reduces to a point since it is based on the approximation that electromagnetic waves propagate through the circuit instantaneously. For this reason, in lumped circuit theory, the respective locations of the elements of the circuit will not affect the behavior of the circuit. The approximation of a physical circuit by a lumped circuit is analogous to the modeling of a rigid body as a particle: in doing so, all data relating to the extent (shape, size, orientation, etc.) of the body are ignored by the theory.

In situations where lumped approximation is invalid, the physical dimensions of the circuit must be considered. To distinguish such circuits from lumped circuits we call them **distributed circuits**, typical examples are transmission lines and waveguides. In distributed circuits, the circuit variables depend not only on time, but also on space variables such as length and width. We need electromagnetic theory for predictions of the behavior of distributed circuits and hence they will not be discussed in this book.

#### **1.4 Reference Directions**

One of the most basic concepts in physical science is that any physical quantity is invariably measured with respect to some "assumed" frame of reference [10]. In electrical network theory, the frame of reference takes the form of an assumed reference direction of the current i and an assumed reference polarity of the

voltage v. A thorough understanding of the concept of reference current direction and reference voltage polarity is absolutely essential in the study of (nonlinear) network theory. It is a fact that a large percentage of the mistakes committed by students of network theory can be traced to either the students' underestimation of the full significance of reference current directions and voltage polarities or the students' failure to maintain a consistent set of references.

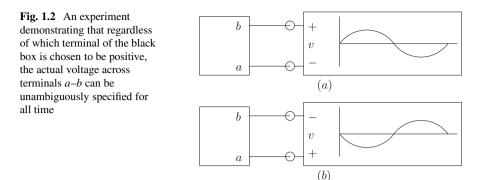

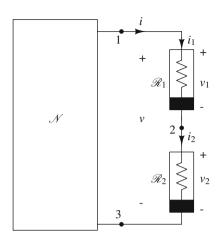

The simplest way to understand the concept of assumed reference direction and polarity is through the experiment illustrated in Fig. 1.2. We will discuss reference voltage polarity. An analogous discussion holds for the reference current direction. Suppose we are given a black box with a pair of **accessible ports** or **terminals** a-b, as shown in Fig. 1.2, and we are required to measure the voltage across terminals a-b. Let us measure the voltage by connecting a-b to the vertical input terminals of an oscilloscope. Since one of the two vertical input terminals of an oscilloscope is marked with a positive sign while the other is marked with a negative sign, the question that immediately arises is which of the two terminals of the black box should we connect to the positive terminal of the oscilloscope in order to obtain the desired information?

The answer is that it does not matter. In order to see this, suppose we **arbitrarily assume** terminal *b* is connected to the positive terminal as shown in Fig. 1.2a. The assumption that terminal *b* is at the positive terminal does not mean that terminal *b* is at a higher potential than terminal *a*. It does mean however that if at any time  $t = t_1, v(t_1) > 0$ , then the potential at *b* is higher than the potential at *a*. On the other hand, if  $v(t_1) < 0$ , then the potential at *b* at  $t = t_1$  is actually lower than the potential at *a*. For example, if the voltage v(t) displayed on the oscilloscope (in volts) is

$$v(t) = 10\sin\pi t \tag{1.5}$$

then terminal b is at a higher potential than terminal a during the time interval 0 < t < 1 s. But during the time interval 1 < t < 2 s, terminal b is at a lower potential than terminal a.

#### 1.4 Reference Directions

Let us now consider what happens when we assume terminal a is connected to the positive terminal of the oscilloscope, instead of terminal b, as shown in Fig. 1.2b. Since this connection is opposite to the connection in Fig. 1.2a, it is clear that the voltage displayed on the oscilloscope (in volts) is given by:

$$v(t) = -10\sin\pi t \tag{1.6}$$

Thus in either case, the final answers are identical. We can therefore conclude that in order to specify the voltage between any pair of terminals unambiguously, we may arbitrarily assume any one of the two possible terminals to be positive. By analogy, we can conclude that in order to specify the current through any wire unambiguously, we may arbitrarily assume any one of the possible two directions to be positive.

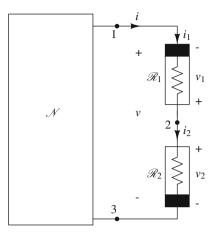

Let us consider next a two-terminal black box N and assume a reference direction for the terminal current i and a reference polarity for the terminal voltage v, see Fig. 1.3. Since the references for both i and v are arbitrary, there are four distinct sets of combinations of references. There is no reason to prefer any one combination over the others. However, in practice, it is usually convenient to choose the combination so that **positive** power represents power **entering** the black box.

From classical mechanics, we know that power is defined by Eq. (1.7).

$$p = \frac{dw}{dt} \tag{1.7}$$

But,

$$vi = \frac{dw}{dq} \frac{dq}{dt}$$

$$= \frac{dw}{dt}$$

(1.8)

**Fig. 1.3** Two possible sets of reference direction for the passive sign convention from Definition 1.2

Thus we have:

$$p(t) = v(t)i(t) \tag{1.9}$$

From the simultaneity postulate, the same current must leave the negative terminal.<sup>4</sup> Hence, based on this observation, we have Definition 1.2.

**Definition 1.2 (Associated Reference Direction or Passive Sign Convention)** Whenever the reference direction for the current *i* in a two-terminal black box is in the direction of the reference voltage drop *v* across the black box (v > 0, i > 0), we use a positive sign in any expression that relates voltage to current. Otherwise, we use a negative sign.

Thus Definition 1.2 implies that the allowable reference combination must be either of the form shown in Fig. 1.3.

#### 1.5 Kirchhoff's Laws

When circuit elements are interconnected to form a circuit, there are some governing laws that all elements in the network must obey. We shall refer to these laws as the **laws of interconnection**. Before we discuss these laws, we need the following definitions:

**Definition 1.3** A **node** is a point in a circuit where two or more circuit elements are interconnected.

**Definition 1.4** A **path** is a trace of adjoining elements, with no elements included more than once.

**Definition 1.5** A **closed node sequence** is a path whose last node is the same as the starting node.

**Definition 1.6** A **loop** is a closed node sequence that traverses only through two-terminal elements.

**Definition 1.7** A **branch** is a path that connects two nodes.

**Definition 1.8** A **connected circuit** is one in which any node can be reached from any other node, by traversing a path through the circuit elements.

Now, given any connected lumped circuit having n nodes, we may choose (arbitrarily) one of the nodes as a **ground** node, i.e., as a reference for measuring electric potentials. Note that a circuit does not have to be physically connected to ground for proper functionality, think about circuits inside our mobile phones.

<sup>&</sup>lt;sup>4</sup>This is also a consequence of Kirchhoff's Current Law, see Sect. 1.5.1.

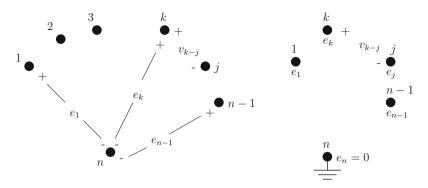

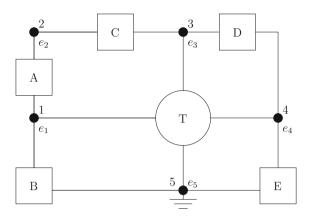

Fig. 1.4 Labeling node-to-ground voltages for a circuit with n nodes

With respect to the chosen ground node, we define n - 1 node-to-ground voltages as shown in Fig. 1.4. Since the circuit is a connected lumped circuit, these n - 1 voltages are well-defined and, in principle, physically measurable quantities. Henceforth, we shall label them  $e_1, e_2, \ldots, e_{n-1}$  and dispense with the + and - signs indicating voltage reference direction. Note that  $e_n = 0$  since node n is chosen as the ground node.

#### 1.5.1 Kirchhoff's Current Law (KCL)

A fundamental law of physics asserts that electrical charge is conserved: There is no known experiment in which a net electric charge is either created or destroyed. KCL expresses this fundamental law in the context of lumped circuits. To state KCL, we first need the definition of a gaussian surface.

**Definition 1.9** A gaussian surface  $\mathscr{S}$  is a two-sided closed surface, that has an "inside" and an "outside."

To express the fact that the sum of the charges inside  $\mathscr{S}$  is constant, we shall require that at all times, the algebraic sum of all the currents leaving the surface  $\mathscr{S}$  is equal to zero.

**Definition 1.10 KCL:** For all lumped circuits, for all  $\mathscr{S}$ , for all times *t*, the algebraic sum of all the currents **leaving**  $\mathscr{S}$  at time *t* is equal to zero.

We will choose  $\mathscr{S}$  so that it cuts only the wires which connect the circuit elements, as discussed in Example 1.5.1.

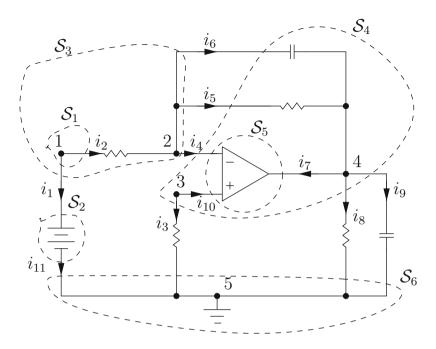

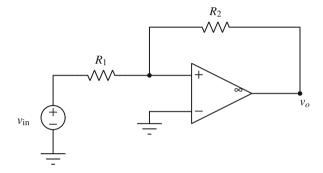

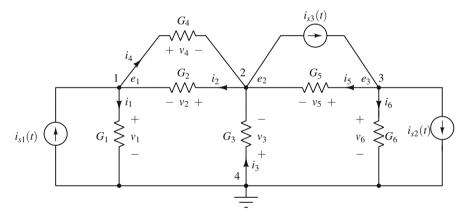

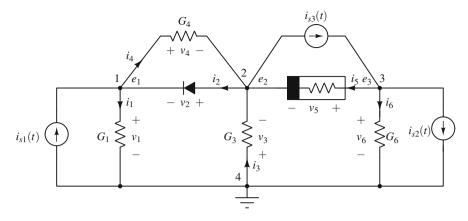

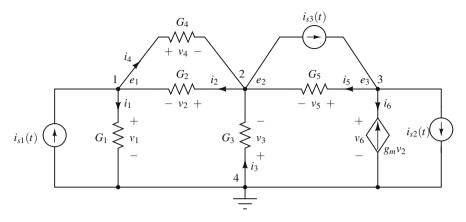

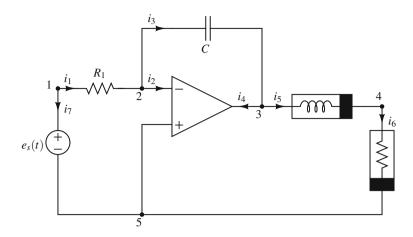

Fig. 1.5 An opamp circuit illustrating gaussian surfaces and KCL

*Example 1.5.1* Write KCL expressions for the circuit in Fig. 1.5.

**Solution** In Fig. 1.5, we have used two-terminal elements and a three-terminal ideal operational amplifier (opamp) (that we will discuss in Sect. 2.5). In the figure, we have drawn six gaussian surfaces  $\mathscr{S}_1, \mathscr{S}_2, \cdots, \mathscr{S}_6$ . We will use these surfaces to illustrate KCL. For  $\mathscr{S}_1$ , KCL states:

$$i_1(t) + i_2(t) = 0 \quad \forall t$$

(1.10)

Note that  $\mathscr{S}_1$  contains only node 1 in its "inside." Thus a node may be considered as a special case of  $\mathscr{S}$ , i.e., the surface is shrunk to a point.

For  $\mathscr{S}_2$ , KCL states:

$$-i_1(t) + i_{11}(t) = 0 \tag{1.11}$$

Note that  $\mathscr{S}_2$  encloses a two-terminal element. Thus we make the conclusion that for a **two-terminal element**, the current entering the element from one

(continued)

Example 1.5.1 (continued)

node at any time t is equal to the current leaving the element from the other node at t.

For  $\mathscr{S}_3$ , KCL states:

$$i_1(t) + i_4(t) + i_5(t) + i_6(t) = 0$$

(1.12)

For  $\mathscr{S}_4$ , KCL states:

$$i_3(t) + i_8(t) + i_9(t) - i_4(t) - i_5(t) - i_6(t) = 0$$

(1.13)

For  $\mathscr{S}_5$ , KCL states:

$$-i_4(t) - i_7(t) - i_{10}(t) = 0 (1.14)$$

Note that these are the three currents pertaining to the opamp. Thus choosing an  $\mathscr{S}$  that encloses any *n*-terminal element, we state that the algebraic sum of the currents leaving or entering the *n*-terminal element is equal to zero at all times *t*. *n*-terminal elements will be covered in more detail in Chap. 2.

For  $\mathscr{S}_6$  (that encloses only the reference node), KCL states:

$$-i_3(t) - i_8(t) - i_9(t) - i_{11}(t) = 0$$

(1.15)

We conclude this section by stating KCL for nodes:

**Definition 1.11 KCL (Node Law):** For all lumped circuits, for all  $\mathscr{S}$ , for all times *t*, the algebraic sum of currents **leaving** any node is equal to zero.

#### 1.5.2 Kirchhoff's Voltage Law (KVL)

Let  $v_{k-j}$  denote the voltage difference between node k and node j as shown in Fig. 1.4. Kirchhoff's voltage law states:

**Definition 1.12 KVL:** For all lumped connected circuits, for all choices of ground node, for all times *t*, for all pairs of nodes *k* and *j*,

$$v_{k-j}(t) = e_k(t) - e_j(t)$$

(1.16)

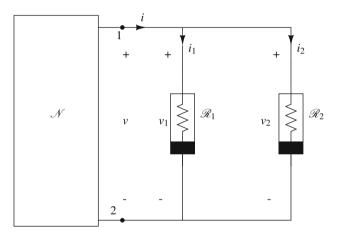

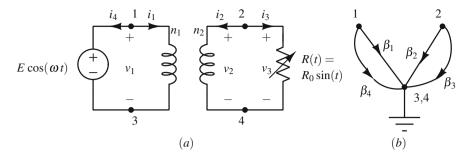

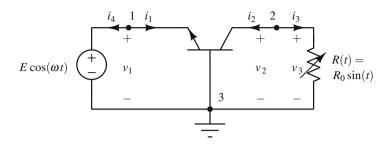

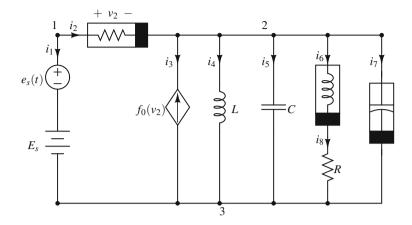

*Example 1.5.2* Write KVL expressions for the circuit in Fig. 1.6.

**Solution** The connected circuit in Fig. 1.6 is made of 5 two-terminal elements and 1 four-terminal element. There are five nodes. Choosing (arbitrarily) node 5 as the ground node, we define the four node-to-ground voltages  $e_1$ ,  $e_2$ ,  $e_3$ , and  $e_4$ . Therefore by KVL, we may write the following seven equations (for convenience, we drop the dependence on t):

$$v_{1-2} = e_1 - e_2$$

$$v_{2-3} = e_2 - e_3$$

$$v_{3-4} = e_3 - e_4$$

$$v_{1-4} = e_1 - e_4$$

$$v_{4-5} = e_4 - e_5 = e_4$$

$$v_{5-1} = e_5 - e_1 = -e_1$$

(1.17)

Note that  $v_{1-2}$ ,  $v_{2-3}$ ,  $v_{3-4}$ ,  $v_{4-5}$ ,  $v_{5-1}$  are the voltages across the twoterminal elements A, C, D, E, B, respectively;  $v_{1-4}$ ,  $v_{4-5}$  and  $v_{5-1}$  are the voltages across the node pairs (1,4); (4,5) and (5,1) of the four-terminal element T, respectively.

If we add the last three equations in Eq. (1.17), we find that:

$$v_{1-4} + v_{4-5} + v_{5-1} = 0 \tag{1.18}$$

Hence for this particular closed node sequence, the sum of the voltages is equal to zero.

(continued)

#### *Example 1.5.2* (continued)

Note also that if we add the first three and last two equations in Eq. (1.17), we find the sum of voltages around a loop is zero:

$$v_{1-2} + v_{2-3} + v_{3-4} + v_{4-5} + v_{5-1} = 0 (1.19)$$

Example 1.5.2 shows that we can state KVL in terms of closed node sequences:

**Definition 1.13 KVL (Closed Node Sequences):** For all lumped connected circuits, for all closed node sequences, for all times t, the algebraic sum of all node-to-node voltages around the chosen closed node sequence is equal to zero.

#### **1.6 From Circuits to Graphs: The Definition of a Network**

It should be clear from our discussions of KCL and KVL that the equations arising from laws of interconnection are independent of the type of elements in a network. We will now state the definition of a network.

**Definition 1.14** A **network** is any interconnection of circuit elements.

Only the network connection diagram, the **topology**, needs to be specified in order to obtain the equations to the laws of interconnection. The topology of a circuit is best exhibited by way of a **graph**.

**Definition 1.15** A graph  $\mathscr{G}$  is specified by a set of nodes  $\{1, 2, \dots, n\}$  together with a set of branches  $\{\beta_1, \beta_2, \dots, \beta_n\}$ .

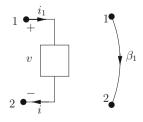

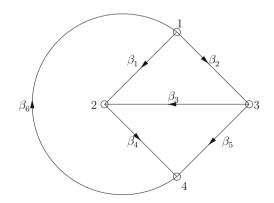

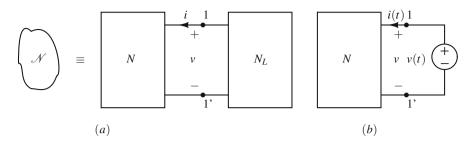

If each branch is given an orientation, indicated by an arrow on the branch, we call the graph directed. For example, a two-terminal element and the associated **element graph** is shown in Fig. 1.7.

Notice that the **element graph** for a two-terminal element has two nodes and one branch. Also note that the directions of the current flow through and voltage drop across the two-terminal element are specified using the passive sign convention from Definition 1.2.

**Fig. 1.7** A two-terminal element and its associated element graph representation

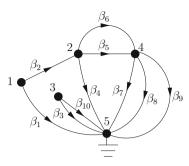

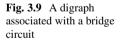

**Fig. 1.8** Digraph associated with the circuit in Fig. 1.5. Detailed derivation of the opamp digraph will be covered in Sect. 2.5

For a given circuit, if we replace each element by its associated element graph, we obtain the **directed circuit graph** or **digraph**  $\mathscr{G}$ . In this book, whenever we refer to a network, we mean the associated digraph of the circuit. We can use either the digraph or the circuit for analysis. Hence, throughout this book, we will use "circuits" and "networks" interchangeably. Note however that the laws of interconnection in circuit theory, such as Tellegen's theorem from Sect. 1.6.1, are essentially graph-theoretic concepts that arise from a network (associated with a given circuit).

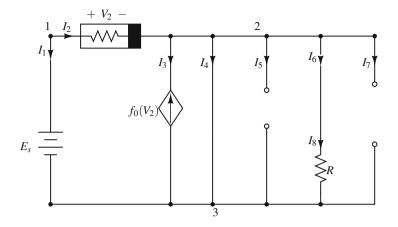

*Example 1.6.1* Write KCL and KVL expressions for the digraph in Fig. 1.8.

**Solution** It is interesting to note that since the circuit contains a threeterminal element, the digraph bears little resemblance to the circuit. In fact, given the digraph, without specifying which nodes belong to the threeterminal element, it is not possible to reconstruct the circuit. This observation is false if the circuit contains only two-terminal elements.

KCL gives:

$$i_{1} + i_{2} = 0$$

$$-i_{2} + i_{4} + i_{5} + i_{6} = 0$$

$$i_{3} + i_{10} = 0$$

$$-i_{5} - i_{6} + i_{7} + i_{8} + i_{9} = 0$$

(1.20)

(continued)

#### Example 1.6.1 (continued)

Let us rewrite Eq. (1.20) in matrix form:

$$\begin{pmatrix} 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & -1 & 0 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & -1 & -1 & 1 & 1 & 1 & 0 \end{pmatrix} \begin{pmatrix} i_1 \\ i_2 \\ i_3 \\ i_4 \\ i_5 \\ i_6 \\ i_7 \\ i_8 \\ i_9 \\ i_{10} \end{pmatrix} = \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}$$

(1.21)

Let:

$$\mathbf{A} \stackrel{\triangle}{=} \begin{pmatrix} 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & -1 & 0 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & -1 & -1 & 1 & 1 & 1 & 0 \end{pmatrix}$$

(1.22)

Thus, Eq. (1.21) can be written as:

$$\mathbf{A}\mathbf{i} = \mathbf{0} \tag{1.23}$$

Matrix A is called the **incidence matrix** (more details in Sect. 3.2.2).

We can express all ten branch voltages in terms of the reference node by using KVL:

$$v_{1} = e_{1}$$

$$v_{2} = e_{1} - e_{2}$$

$$v_{3} = e_{3}$$

$$v_{4} = e_{2}$$

$$v_{5} = e_{2} - e_{4}$$

$$v_{6} = e_{2} - e_{4}$$

$$v_{7} = e_{4}$$

$$v_{8} = e_{4}$$

$$v_{9} = e_{4}$$

$$v_{10} = e_{3}$$

(1.24)

(continued)

*Example 1.6.1* (continued) Rewriting Eq. (1.24) in matrix form:

$$\begin{pmatrix} 1 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & -1 \\ 0 & 1 & 0 & -1 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix} \begin{pmatrix} e_1 \\ e_2 \\ e_3 \\ e_4 \end{pmatrix} = \begin{pmatrix} v_1 \\ v_2 \\ v_3 \\ v_4 \\ v_5 \\ v_6 \\ v_7 \\ v_8 \\ v_9 \\ v_{10} \end{pmatrix}$$

(1.25)

Comparing Eqs. (1.21) and (1.25), we can see that the constant matrix on the LHS of Eq. (1.25) is  $A^T$ . Hence Eq. (1.25) can be written as:

$$\mathbf{A}^T \mathbf{e} = \mathbf{v} \tag{1.26}$$

Much more will be said about topological concepts in circuit theory throughout this book. Specifically, element graphs for multi-terminal elements will be discussed in Chap. 2. We will formalize the matrix formulation of Kirchhoff's laws in Chap. 3, before we discuss general circuit analysis techniques.

#### 1.6.1 Generality of Digraphs: Tellegen's Theorem Example

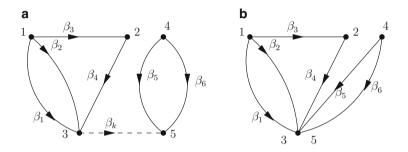

To further illustrate the generality of the digraph approach, we will give an example of Tellegen's theorem [28]. We will formally state and prove the theorem in Chap. 3.

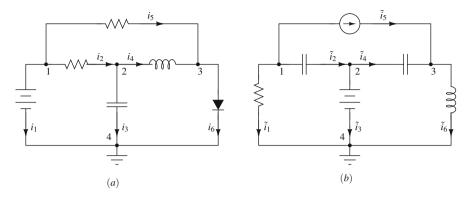

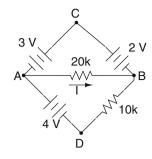

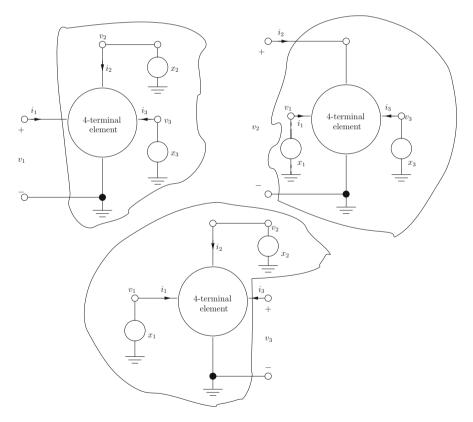

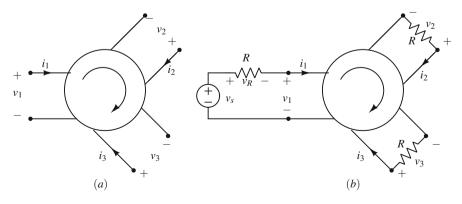

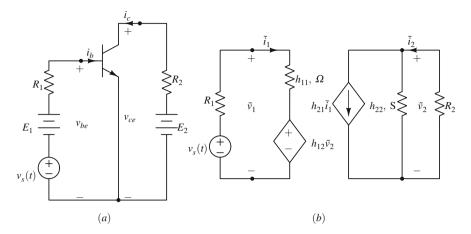

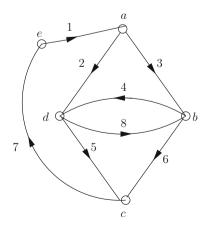

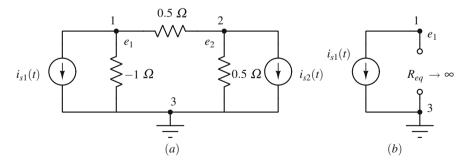

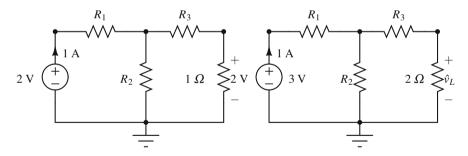

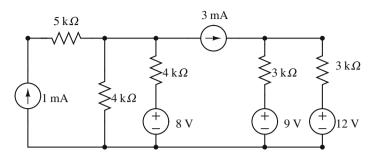

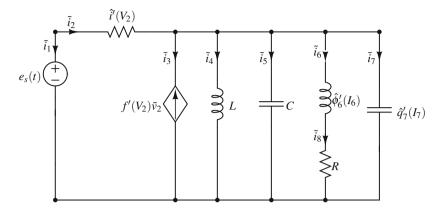

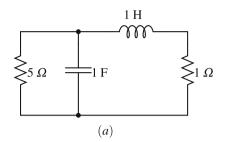

Consider the circuits in Fig. 1.9.

KVL and KCL in matrix form for the circuit in Fig. 1.9a are:

$$\mathbf{A}^T \mathbf{e} = \mathbf{v}$$

$$\mathbf{A}\mathbf{i} = \mathbf{0} \tag{1.27}$$

where:

$$\mathbf{A} = \begin{pmatrix} 1 & 1 & 0 & 0 & 1 & 0 \\ 0 & -1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & -1 & -1 & 1 \end{pmatrix}$$

(1.28)

Fig. 1.9 Circuits for understanding Tellegen's theorem

Let the branch power  $v_k i_k$  be summed for all N branches of the circuit. Then, by Eq. (1.27):

$$\sum_{k=1}^{N} v_k i_k = \mathbf{v}^T \mathbf{i}$$

$$= (\mathbf{A}^T \mathbf{e})^T \mathbf{i}$$

$$= \mathbf{e}^T (\mathbf{A} \mathbf{i})$$

$$= 0 \qquad (1.29)$$

In deriving Eq. (1.29), the familiar rules  $(\mathbf{AB})^T = \mathbf{B}^T \mathbf{A}^T$ ,  $(\mathbf{A}^T)^T = \mathbf{A}$ ,  $\mathbf{e}^T \mathbf{0} = 0$  of vector algebra have been used.

The result in Eq. (1.29) should not be surprising since we have derived the conservation of power in a circuit from Kirchhoff's laws.

Consider however the circuit of Fig. 1.9b which has the same topological configuration, same reference directions and numbering, and hence the same **A** as the circuit in Fig. 1.9a. Hence, the incidence matrix for the circuit in Fig. 1.9b is also given by Eq. (1.28). Let the electrical quantities of the circuit be  $\tilde{\mathbf{i}}$ ,  $\tilde{\mathbf{v}}$ ,  $\tilde{\mathbf{e}}$  in Fig. 1.9b. Then:

$$\mathbf{A}^T \tilde{\mathbf{e}} = \tilde{\mathbf{v}}$$

$$\mathbf{A}\tilde{\mathbf{i}} = \mathbf{0} \tag{1.30}$$

Now consider:

$$\sum_{k=1}^{N} v_k \tilde{i}_k = \mathbf{v}^T \tilde{\mathbf{i}}$$

$$= (\mathbf{A}^T \mathbf{e})^T \tilde{\mathbf{i}}$$

$$= \mathbf{e}^T (\mathbf{A} \tilde{\mathbf{i}})$$

$$= 0 \tag{1.31}$$

While the LHS of Eq. (1.31) has the dimensions of power, the quantity is physically meaningless since  $v_k$  and  $\tilde{i}_k$  exist in two different circuits.

Similarly, we can show:

$$\tilde{\mathbf{v}}^T \mathbf{i} = 0 \tag{1.32}$$

Equations (1.31) and (1.32) are general forms of Tellegen's theorem. We will apply Tellegen's theorem to derive some general properties of nonlinear resistive circuits in Chap. 3.

#### 1.7 Circuit Theory from Electromagnetic Field Theory

Now that we have an understanding of the laws of interconnection, we will have a short discussion in this section on how to arrive at these laws, by using the fact that circuit theory is an approximation of electromagnetic field theory. Although we are only concerned with lumped circuits in this book, this (very short) section should be helpful because the approximation techniques used have roots in the very important concept of modeling [10].

#### 1.7.1 The Art of Modeling

Engineers and scientists seldom analyze a physical system in its original form. Instead, they construct a model which approximates the behavior of the system. By analyzing the behavior of the model, they hope to predict the behavior of the actual system. The primary reason for constructing models is that physical systems are usually too complex to be amenable to a practical analysis. In most cases, the complexity of a system is due in part to the presence of many nonessential factors. The basic principle of modeling consists, therefore, of extracting only the essential factors.

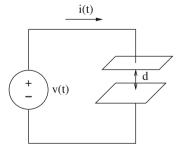

As stated earlier, an electric circuit is an interconnection of electrical devices. We will encounter a plethora of electrical devices (diodes, transistors to name a few) throughout this book. But one has to again understand that we must extract only the essential factors of the device, based on the circuit in question. A classic example is frequency behavior. No device behaves the same at all frequencies. For example, at "low enough" frequencies, metallic parallel plates separated by a (small, compared to the width of the parallel plates) distance act like a capacitor. Increasing the frequency will lead to more complicated behavior, and the device does not behave like an ideal capacitor anymore. Hence, it is vital that the reader understands device modeling is still more of an "art" than science. Although no general theory of device modeling is presently available, there are a variety of techniques available that will help us model physical devices, in terms of the four fundamental circuit elements.

We will start discussing modeling of the fundamental circuit elements in Sect. 1.8 and continue the discussion throughout the book. With respect to circuit theory being an approximation of electromagnetic field theory, we will only discuss the laws of interconnection, namely KCL and KVL. A detailed discussion of how we get the terminal behavior for the four fundamental circuit elements from field theory is beyond the scope of this book. We hope to discuss this in our followup book, "Advanced Nonlinear Circuits and Networks."

#### 1.7.2 KCL and KVL from Field Theory: A Very Brief Overview

From the node form of KCL in Definition 1.11, we know that the sum of the currents flowing out of a node must be equal to zero. From field theory (specifically Gauss' law), the surface integral of the current density over a closed surface must be equal to zero if no charge accumulates inside that surface. Definition 1.3 of a node implies that a node is a theoretical abstraction of a physical interconnection of wires: a node does not have any circuit elements such as capacitors associated with it. Hence, no charge can accumulate on a node, and the sum of currents leaving the node must be equal to zero.

KVL from Definition 1.13 is equivalent to Faraday's law of induction from Maxwell's theory of electromagnetism. This equivalence, however, is not directly evident as the relation between KCL and the law of conservation of charge. Indeed, KVL depends on how the branch voltages are defined in terms of the electromagnetic field. These details are also beyond the scope of this book, and will be discussed in our follow-up volume. But, we can get an intuitive idea by considering the fact that we defined branch voltage as the difference between node-to-ground voltages in Eq. (1.16). In fact, a practical device for measuring branch voltage—the voltmeter—is connected such that voltage is measured across a pair of nodes. Hence a voltmeter is designed to measure the line integral of the electric field

along the path formed by the connecting leads. Thus, the sum of voltages around a closed loop in a circuit has the electromagnetic equivalent of the electric field around a closed path. The electric field involved in this integration is, by assumption, equal (or approximately so) to the negative gradient of a scalar potential [10]. Therefore, the line integral of the electric field should vanish, and this gives us KVL.

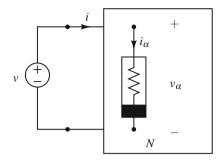

## 1.8 Characterization of a Two-Terminal Black Box

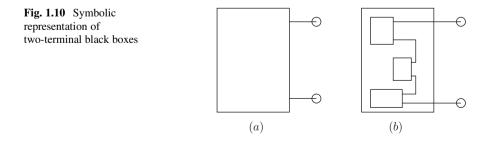

Now that we have discussed interconnection of circuit elements, it is time to discuss the circuit elements themselves. Although we will encounter many physical devices of varying complexity throughout this book, we will model them as black boxes [10]. These boxes may possess many terminals, but **only two of these are accessible to the external world in the sense that the device may be excited only through these terminals**. For our purpose, it is convenient to imagine that the device is enclosed in a box and that the two accessible terminals are brought out by two connecting wires, with the symbol shown in Fig. 1.10a.

It is important to emphasize that the content of the black box may be as simple as a light bulb, or as complicated as an arbitrary interconnection of black boxes as shown in Fig. 1.10b.

The choice of the term "black box" is quite appropriate here because the box is really black inside in the sense that we cannot see its contents. As a matter of fact, unless we open the box and peep inside, there is no way of determining its contents. However, as engineers, we are not so much interested in the contents of the box as in knowing what the box is capable of and how it behaves externally when it is connected with other black boxes into a network. In other words, we are primarily interested in predicting the external behavior of the black box. Our first step toward such an analytical approach is to "characterize" the black box. To properly characterize a black box, it is paramount that we choose the correct set of terminal variables. We will illustrate this idea in this section by modeling a "spring" from basic physics, refer to Fig. 1.11.

Suppose we did not know that in reality we had a spring inside the black box and we were asked to predict the behavior of the external terminals when an arbitrary force f(t) is applied to one end (terminal) of the spring while the other

Fig. 1.11 An example illustrating the characterization of a mechanical black box

end (terminal) is fixed against a wall. The mechanical variables of interest here are the displacement x (displacement to the right of the initial 0 position is assumed positive, as shown in Fig. 1.11), velocity v of the terminal that is free to move and the force f (positive for tension, negative for compression).

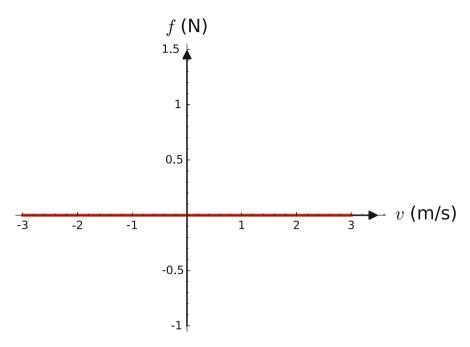

Clearly the only way we can hope to characterize this black box (other than opening the box) is to start performing some experiments. Suppose we begin by applying a constant force f = A and measure the corresponding velocity v. This would give us a point in the velocity-vs-force (v-f) plane.<sup>5</sup> By repeating the above experiment with several values of the force f, we obtain the data shown in Fig. 1.12.

We might be tempted to draw a smooth curve through these data points (which in this case happens to be the f axis) and claim to have characterized the black box in the sense that given any constant force f, we can analytically predict the associated velocity.

However a little thought will show that we have not really characterized the black box yet, for if, instead of applying a constant force we apply a slowly varying sinusoidal force,  $f(t) = A \sin(t)$ . The characteristics in Fig. 1.12 would predict that v = 0.

This is of course contrary to what we observe experimentally: namely,  $v(t) = (A/k) \cos(t)$ , where k is the spring constant. We might hope that this inconsistency can be resolved by plotting all points (v, f). Nevertheless we will again quickly conclude that the length of both axes of the resulting ellipse depends on the amplitude A of the applied force f. For each A we will obtain a unique ellipse and thus we will eventually fill the entire v-f plane. Even if we could draw an infinite set of ellipses, we would be able to predict the velocity only if f is sinusoidal. Using these ellipses to predict v due to non-sinusoidal f would again yield incorrect answers. We must now realize that the useful information we obtained from this experiment is that the black box cannot be characterized by a curve in the v-f plane.

<sup>&</sup>lt;sup>5</sup>When we say x-y plane, we denote specifically x as the horizontal axis and y as the vertical axis of the plane. This is consistent with the conventional usage where the first variable denotes the abscissa and the second variable denotes the ordinate.

**Fig. 1.12** Force-velocity plot for constant force f = A

Suppose we try another set of variables, say the force f and displacement x. Repeating the experiments, we will find that provided f(t) does not change rapidly, the black box can be characterized by a curve in the x-f plane.

After experiencing the length of time needed to carry out the above experiments, we can now begin to appreciate the utility of such a conclusion; namely, the characterization of the black box permits an analytical solution and thereby eliminates the need to carry out any further experiments.

Observe however that our conclusion is based on the assumption that f(t) does not change rapidly. If we were to repeat our experiment with higher-frequency sinusoidal waveforms, as well as non-sinusoidal waveforms which change rapidly, we will find deviations from our conclusions drawn using low frequency waveforms. This will suggest that our earlier assumption, that f does not change rapidly, is indeed necessary. In order to emphasize this restriction, it is a common practice to call a black box characterization as **static characterization**, in contrast to a **dynamic characterization** for higher frequencies. Hence for the black box in Fig. 1.11, the f-x curve is the static characteristic.

Since the deviation of the measured characteristic from the static characteristic increases slowly with frequency rather than abruptly, it is impossible to pick a definite frequency above which the static characteristic does not hold. Neither is it possible to find a single dynamic characteristic that would hold for all frequencies. Hence a certain amount of scientific judgment is involved in deciding whether a certain static characteristic curve can be used to satisfactorily solve a given problem.

It is encouraging, however, to know that a large percentage of practical networks can indeed be analyzed using only static characteristics. Moreover, even in cases where the static characteristic fails to give satisfactory solutions, we shall show in future chapters that we can often patch up the error by including "parasitic elements," namely, elements which are undesirable but which are invariably present in the black box in small quantities. Thus, in this book, we will assume all characteristics are static and will utilize parasitic elements to model the necessary dynamic characteristics. We shall henceforth delete the adjective "static."

For the example in Fig. 1.11, the parasitic element consists of the mass associated with the spring. At low frequencies, the mass being quite small, has relatively no effect on the f-x curve. However as the frequency of the external force increases, the acceleration of the spring increases and the inertia force due to the mass becomes appreciable.

## **1.9** Two-Terminal Elements

From the previous section, we know that it is essential to choose the correct set of variables for characterizing a black box. For two-terminal elements, the circuit variables of interest are those that can be measured externally. Hence the terminal voltage v and terminal current i are of primary interest because they can be readily measured. The charge q and flux-linkage  $\phi$  are also of interest because they can be indirectly measured by **integrating** the measured current i(t) and voltage v(t), respectively. From these measurements, we shall then try to establish a relationship, if any, between each pair of **independent** variables.

*i* and *q* are related by Eq. (1.3); *v* and  $\phi$  are related by Eq. (1.4). Hence the only remaining combinations consist therefore of the relationship between the following variables.

- 1. Relationship between v and i, this is the two-terminal resistor shown in the topleft corner of Fig. 1.1.

- 2. Relationship between  $\phi$  and *i*, this is the two-terminal inductor shown in the bottom-left corner of Fig. 1.1.

- 3. Relationship between  $\phi$  and q, this is the two-terminal memristor shown in the bottom-right corner of Fig. 1.1.

- 4. Relationship between v and q, this is the two-terminal capacitor shown in the top-right corner of Fig. 1.1.

We will now discuss each of these elements in detail. But, before we begin our discussion of two-terminal elements, two important remarks:

• Time-varying elements: each of the four fundamental circuit elements we will discuss can be time-varying. For instance, a time-varying resistor is defined by the relation:  $f_R(v, i, t) = 0$ . A very simple example is a potentiometer (or variable resistor), whose arm is being rotated by say a motor. Nevertheless, the analysis of a nonlinear network containing time-varying elements is a very

**Fig. 1.13** Symbol for a linear resistor with resistance *R*

difficult mathematical problem requiring advanced mathematics. Hence we will primarily discuss nonlinear time-invariant elements in this book and restrict our discussion of time-varying elements to a few examples.

• Memristors: as we will see in Sect. 1.9.4, this device is the fourth fundamental circuit element. However, although a variety of circuit theoretic properties of the memristor can be obtained by studying the terminal behavior, a true understanding of a memristor's behavior requires us (unlike the other resistor, capacitor and inductor) to "peer inside" the black box (see Sect. 4.4.2).

## 1.9.1 Resistors

The **linear resistor** is probably the most familiar circuit element that one encounters in basic physics. This device satisfies Ohm's law: that is, the voltage across such an element is proportional to the current flowing through it. We represent it by the symbol shown in Fig. 1.13 where the current *i* through the resistor and the voltage v across it are measured using the passive sign convention from Definition 1.2.

Ohm's law states that at all times.

$$v(t) = Ri(t) \text{ or}$$

$$i(t) = Gv(t)$$

(1.33)

where the constant *R* is the **resistance**<sup>6</sup> of the linear resistor (measured in the unit of ohms  $(\Omega)$ ) and *G* is the **conductance** measured in units of siemens (S).

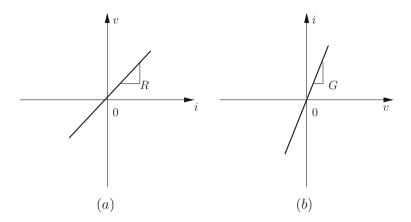

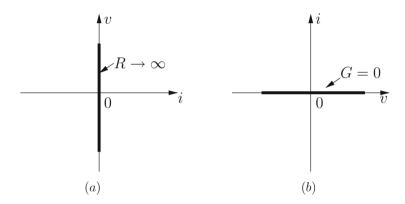

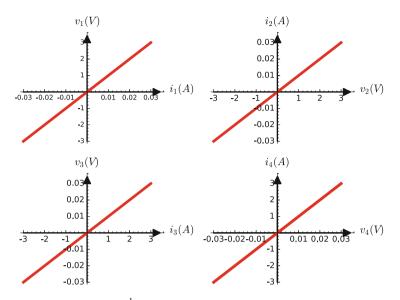

Equation (1.33) can be plotted on the i-v plane or v-i plane as shown in Fig. 1.14.

<sup>&</sup>lt;sup>6</sup>In nonlinear circuits, terms such as resistance (capacitance, inductance) become ambiguous and only the terms "resistor, capacitor and inductor" should be used. Nevertheless, we will refer to the appropriate small-signal quantity with the terms "resistance," "capacitance," and "inductance." Note that there is no confusion with respect to "memristance," since the memristor is fundamentally a nonlinear element.

Fig. 1.14 Linear resistor characteristic plotted on the (a) i-v and (b) v-i plane

Fig. 1.15 Characteristic of an open circuit (a) *i*-*v* plane (b) *v*-*i* plane

There are two special cases of linear resistors which deserve special mention, namely, the **open circuit** and **short circuit**.

**Definition 1.16 (Open Circuit)** A two-terminal resistor is called an open circuit iff its current *i* is identically zero irrespective of the voltage *v*; i.e., f(v, i) = i = 0.

The characteristic of an open circuit is the *v* axis in the *v*-*i* plane, with zero slope (G = 0). In the *i*-*v* plane, it has an infinite slope,  $R \to \infty$ , refer to Fig. 1.15

**Definition 1.17 (Short Circuit)** A two-terminal resistor is called a short circuit iff its voltage v is identically zero irrespective of the current i; i.e., f(v, i) = v = 0.

The characteristic of a short circuit is the *i* axis in the v-i plane, with  $G \to \infty$ . In the *i*-*v* plane, the characteristic has zero slope, G = 0, refer to Fig. 1.16.

Fig. 1.16 Characteristic of a short circuit (a) *i*-*v* plane (b) *v*-*i* plane

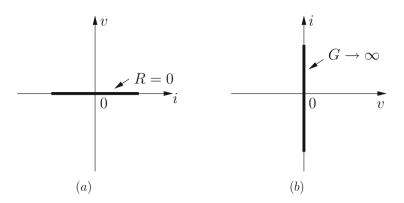

Comparing Figs. 1.15 and 1.16, we see that the curve of the open circuit in one plane is identical to the curve of the short circuit in the other plane. For this reason, the open circuit is said to be the **dual** of the short circuit and vice versa.

*Example 1.9.1* A linear resistor with resistance of  $100 \Omega$  is given. What is its dual?

**Solution** Consider a linear resistor with resistance  $R = \frac{1}{100} \Omega$ . The *i*-v and v-*i* characteristics are plotted in Fig. 1.17. Notice how the  $i_1 - v_1$  characteristic of the resistor with  $R = 100 \Omega$  is equivalent to the  $v_4 - i_4$  characteristic of the resistor with  $R = \frac{1}{100} \Omega$ . Similarly, the  $v_2 - i_2$  characteristic for resistor with  $R = 100 \Omega$  is equivalent to the  $i_3 - v_3$  characteristic for resistor with  $R = \frac{1}{100} \Omega$ . Hence the dual is a resistor with  $R = \frac{1}{100} \Omega$ .

From Eq. (1.9), the power delivered to a linear resistor at time *t* by the remainder of the circuit to which it is connected is:

$$p(t) = v(t)i(t)$$

=  $Ri^{2}(t)$

=  $Gv^{2}(t)$  (1.34)

Thus the power delivered to a linear resistor is always non-negative if  $R \ge 0$ . We say that a linear resistor is passive iff its resistance is non-negative. Thus a passive resistor always absorbs energy from the remainder of the circuit.

**Fig. 1.17**  $R = 100 \Omega$  and  $R = \frac{1}{100} \Omega$  are duals of each other. The dual of the top-left plot  $(i_1 - v_1$  for  $R = 100 \Omega$ ) is in the bottom-right  $(v_4 - i_4 \text{ for } R = \frac{1}{100} \Omega)$ . Similarly, the dual of the top-right plot  $(v_2 - i_2 \text{ for } R = 100 \Omega)$  is in the bottom-left  $(i_3 - v_3 \text{ for } R = \frac{1}{100} \Omega)$

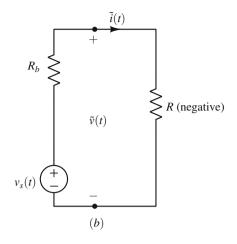

But from Eq. (1.34) we can see the power delivered to a linear resistor is negative if R < 0; i.e., as current flows through it, the resistor delivers energy to the remainder of the circuit. Therefore we call such a linear resistor with negative resistance an active resistor.

While linear passive resistors are familiar to everyone, linear active resistors are perhaps new to some readers. They are one of the basic circuit elements in the design of negative resistance oscillators. We will show how to synthesize piecewise-linear negative resistors using opamps in Sect. 2.5.3.2. We will discuss oscillator design in later parts of the book. For the present we only wish to mention that the linear active resistor is useful in modeling nonlinear devices and circuits over certain ranges of voltages, currents and frequencies.

While the linear resistor is perhaps the most prevalent circuit element in electrical engineering, nonlinear devices which can be modeled with nonlinear resistors have become increasingly important. Hence we will now define the concept of a nonlinear resistor in the most general way. Note that in keeping with the theme of the book, linear resistors (elements) will only be discussed as special cases of nonlinear resistors (elements).

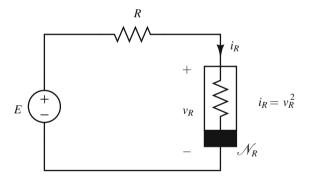

**Fig. 1.18** Nonlinear resistor  $\mathcal{R}$

In general, a two-terminal element will be called a resistor if its voltage v and current *i* satisfy the relation in Eq. (1.35):

$$\mathscr{R} = \{(v, i) : f_R(v, i) = 0\}$$

(1.35)

This relation is called the v-i characteristic of the resistor and can be plotted graphically in the v-i (or i-v) plane. We have already done so for linear resistors. The circuit symbol for the nonlinear resistor was shown in Fig. 1.1, reproduced in Fig. 1.18.

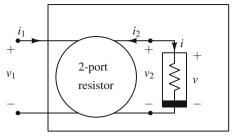

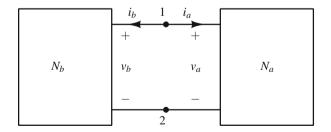

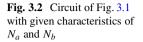

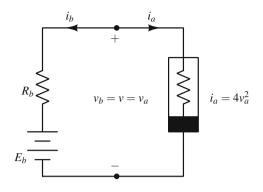

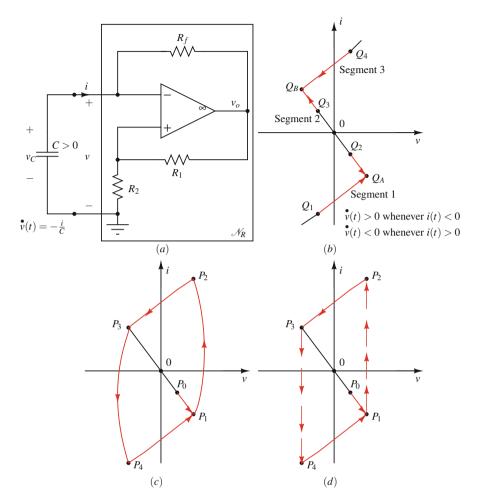

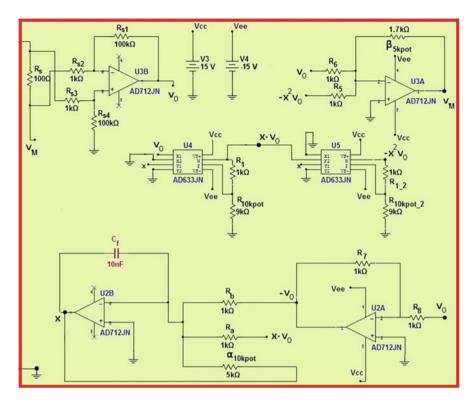

Note that in view of the nonsymmetrical nature of the circuit symbol for the nonlinear resistor (and nonlinear elements in general), we may avoid drawing the associated voltage (flux) polarity and current (charge) direction signs beside the symbol, **provided we agree to assume that the darkened edge is the negative terminal and current (charge) enters the positive terminal**. This convention will be followed in this book, when adding polarities and directions will clutter the circuit diagram.