# André Inácio Reis · Rolf Drechsler *Editors*

# Advanced Logic Synthesis

Advanced Logic Synthesis

André Inácio Reis • Rolf Drechsler Editors

# Advanced Logic Synthesis

*Editors* André Inácio Reis PPGC/PGMICRO Institute of Informatics UFRGS Porto Alegre, RS, Brazil

Rolf Drechsler Group for Computer Architecture University of Bremen Bremen, Germany

Cyber-Physical Systems DFKI GmbH Bremen, Germany

ISBN 978-3-319-67294-6 ISBN 978-3-319-67295-3 (eBook) https://doi.org/10.1007/978-3-319-67295-3

Library of Congress Control Number: 2017956712

#### © Springer International Publishing AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## Preface

For more than four decades, the complexity of circuits and systems has grown according to Moore's law resulting in chips of several billion components. While already the synthesis on the different levels from the initial specification down to the layout is a challenging task, the quality of initial logic synthesis steps is still very determinant for the quality of the final circuit.

Logic synthesis has been evolving into new research directions, including the use of large–scale computing power available through data centers. The availability of warehouse computing opens the way to the use of big data analytics and cognitive applications from recent advances in artificial intelligence and infrastructure for parallel processing of graph data structures.

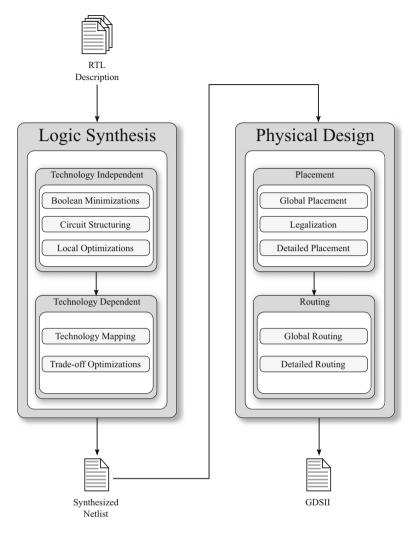

Besides these advances in computer science, the underlying fabrication technology evolution is also bringing emergent circuit technologies that require new synthesis techniques. Advanced fabrication nodes also require a tighter integration of logic synthesis and physical design, in order to bring physical awareness early in the design flow to achieve design convergence.

Logic synthesis can also be expanded to exploit higher level of abstractions, including the identification and manipulation of datapaths. This can be done by identifying data paths at the gate level, as well as by performing architectural transformations at higher levels of abstractions.

The field of SAT solvers and quantified Boolean formula (QBF) solvers has had recent important advances. This way, it is natural that several logic synthesis problems are being addressed, modeled, and solved with these tools.

Stochastic and statistical methods are also gaining importance in the field of logic synthesis. These include stochastic circuits that may arise in novel technologies, as well as methods of synthesis using probabilistic approaches.

This book celebrates the 25th edition of the International Workshop on Logic and Synthesis, which happened in June 2016. In doing so, we present a selection of chapters that originated as keynotes, special sessions, and regular papers from IWLS 2015 and IWLS 2016. The selection of papers reflects relevant topics for the advancement of logic synthesis. World-leading researchers contributed chapters, where they describe the underlying problems, possible solutions, and important directions for future work.

The chapters in the order as they appear in this book are:

- "EDA3.0: Implications to Logic Synthesis" by Leon Stok

- "Can Parallel Programming Revolutionize EDA Tools?" by Yi-Shan Lu and Keshav Pingali

- "Emerging Circuit Technologies: An Overview on the Next Generation of Circuits" by Robert Wille, Krishnendu Chakrabarty, Rolf Drechsler, and Priyank Kalla

- "Physical Awareness Starting at Technology-Independent Logic Synthesis" by André Reis and Jody Matos

- "Identifying Transparent Logic in Gate-Level Circuits" by Yu-Yun Dai and Robert K. Brayton

- "Automated Pipeline Transformations with Fluid Pipelines" by Rafael T. Possignolo, Elnaz Ebrahimi, Haven Skinner, and Jose Renau

- "Analysis of Incomplete Circuits Using Dependency Quantified Boolean Formulas" by Ralf Wimmer, Karina Wimmer, Christoph Scholl, and Bernd Becker

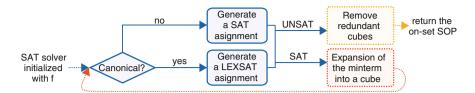

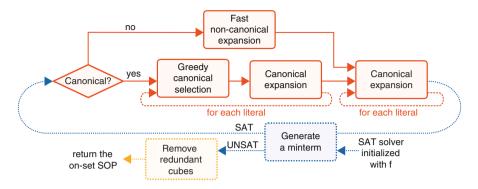

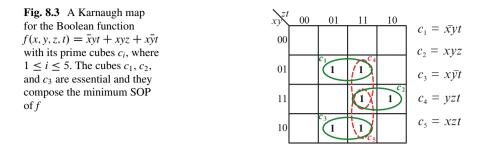

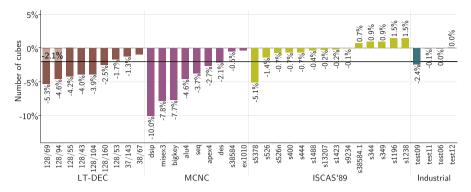

- "Progressive Generation of Canonical Irredundant Sums of Products Using a SAT Solver" by Ana Petkovska, Alan Mishchenko, David Novo, Muhsen Owaida, and Paolo Ienne

- "A Branch-and-Bound-Based Minterm Assignment Algorithm for Synthesizing Stochastic Circuits" by Xuesong Peng and Weikang Qian

- "Decomposition of Index Generation Functions Using a Monte Carlo Method" by Tsutomo Sasao and Jon T. Butler

On the different abstraction layers, it is shown in which way logic synthesis can adapt to recent computer science and technological advances. The contributed chapters cover latest results in academia but also descriptions of industrial tools and users. Also, the chapters are very helpful in pointing out relevant novel topics for future work.

Porto Alegre, Brazil Bremen, Germany June 2017 André Inácio Reis Rolf Drechsler

# Acknowledgments

All contributions in this edited volume have been anonymously reviewed. We would like to express our thanks for the valuable comments of the reviewers and their fast feedback. Here, we also like to thank all the authors who did a great job in submitting contributions of very high quality. Our special thanks go to Jody Matos, Mayler Martins, Vinicius Callegaro, and Vinicius Possani for helping with the preparation of the book. Finally, we would like to thank Charles Glaser, Brian Halm, Nicole Lowary, and Murugesan Tamilselvan from Springer. All this would not have been possible without their steady support.

# Contents

| 1 | EDA3.0: Implications to Logic Synthesis<br>Leon Stok                                                                                                                    | 1   |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | <b>Can Parallel Programming Revolutionize EDA Tools?</b><br>Yi-Shan Lu and Keshav Pingali                                                                               | 21  |

| 3 | Emerging Circuit Technologies: An Overview on the Next<br>Generation of Circuits<br>Robert Wille, Krishnendu Chakrabarty, Rolf Drechsler,<br>and Priyank Kalla          | 43  |

| 4 | Physical Awareness Starting at Technology-Independent Logic<br>Synthesis<br>André Inácio Reis and Jody M.A. Matos                                                       | 69  |

| 5 | Identifying Transparent Logic in Gate-Level Circuits<br>Yu-Yun Dai and Robert K. Brayton                                                                                | 103 |

| 6 | Automated Pipeline Transformations with Fluid Pipelines<br>Rafael T. Possignolo, Elnaz Ebrahimi, Haven Skinner, and Jose Renau                                          | 125 |

| 7 | Analysis of Incomplete Circuits Using Dependency QuantifiedBoolean FormulasRalf Wimmer, Karina Wimmer, Christoph Scholl, and Bernd Becker                               | 151 |

| 8 | Progressive Generation of Canonical Irredundant Sums of<br>Products Using a SAT Solver<br>Ana Petkovska, Alan Mishchenko, David Novo, Muhsen Owaida,<br>and Paolo Ienne | 169 |

| 9 | A Branch-and-Bound-Based Minterm Assignment Algorithm<br>for Synthesizing Stochastic Circuit<br>Xuesong Peng and Weikang Qian                                           | 189 |

| 10  | Decomposition of Index Generation Functions Using a Monte |     |

|-----|-----------------------------------------------------------|-----|

|     | Carlo Method                                              | 209 |

|     | Tsutomu Sasao and Jon T. Butler                           |     |

| Ind | ex                                                        | 227 |

## Chapter 1 EDA3.0: Implications to Logic Synthesis

Leon Stok

#### 1 Introduction

Electronic Design Automation is ripe for a paradigm change. But is it ready? The ubiquitous availability of ample compute power will allow for a different way for designers to interact with their design data and will allow for new optimization algorithms to be invented. In this chapter we will introduce the concept of warehouse-scale computing [1], its software stack, and how it will apply to EDA analysis and optimization.

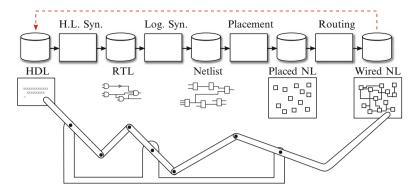

In the early days of Electronic Design Automation, EDA1.0, separate applications were developed. Each ran on individual workstations. Verification, synthesis, placement, and routing were separate tasks carried out by separate tools. The size of the designs that could be handled was limited by the available compute power and the scalability of the algorithms. But since Moore's law had not really taken off, these tools were sufficient for the design sizes at the time. The design flow was carried out by moving design data from tool to tool, with little interaction between the individual steps.

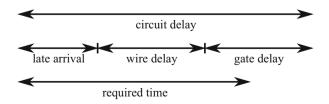

Due to Moore's law and the scaling of the technology designs became larger and larger. At the same time, it became more difficult to predict the result of decisions made early in the design flow on the final result. Wire delay started to play an increasingly larger role in the overall delay of a path because wire delays do not scale as well as gate delays over the last several technology generations. In addition, due to the larger design sizes a certain percentage of the wires became longer and longer. Logic synthesis therefore needed to really understand the effects of interconnect increasingly better to make sensible decisions. To make reasonable accurate timing predictions, placement and routing need to be fairly complete. In the

L. Stok (🖂)

IBM Systems Group, 2455 South Road, Poughkeepsie, NY, 12601, USA e-mail: leonstok@us.ibm.com

<sup>©</sup> Springer International Publishing AG 2018

A.I. Reis, R. Drechsler (eds.), Advanced Logic Synthesis, https://doi.org/10.1007/978-3-319-67295-3\_1

era of EDA2.0, this got handled by integrating the individual tools such as synthesis, placement, and routing as well as the analysis tools (such as timing) together in an integrated tool suite. These integrated tool suites would typically run on larger servers. Scaling to even larger design sizes was obtained by multi-threading many of the core algorithms such that they could take advantage of the many cores and threats in these larger servers.

In the last few generations, technology progress has slowed down from a power/performance perspective. Getting the utmost power and performance out of the smallest possible design has become more crucial to make a design in a new technology worth it. However, technology scaling has allowed for design sizes to continue to grow. At the same time design rule complexity has continued to go up, and people are advocating that handling complex rules needs to become an integral part of the design flow by providing in-design checking tools. As a result, the design work and possibilities for optimization have gone up tremendously. The amount of data that needs to be dealt with in an end-to-end design flow has exploded.

Design teams have increased in size. Despite that, it is impossible to complete a large design on an economically feasible schedule without lots of reuse. This has helped fill up the chips with homogeneous structures. But how many homogeneous cores do we want to continue to put on the same chip? The drive for better power/performance on specific workloads advocates for a lot more heterogeneity on a chip with functions that target a specific workload. To deliver this larger variety of designs, an additional boost in designer productivity will be required. It is time that we look beyond the individual, albeit integrated tools, and start to optimize the iterative end-to-end design flows.

Many of challenges for the future of EDA were outlined in a report on the 2009 NSF Workshop that focused on EDA's Past, Present, and Future. This report was published by Brayton and Cong in two parts in IEEE D&T [2]. The second part of that paper outlines the key EDA challenges. Interestingly, it has only a few challenges printed in bold: intuitive design environments, simplified user interfaces, standardized interfaces, and scalable design methodologies all leading to disciplined and predictable design. These challenges do not really drive the need for new EDA point tools. Instead they all point to problems that need to be solved in the end-to-end design flows. They point to the improvement that is needed in the design environment through which the designers interact with design tools and to the scale of problems that need to be solved.

These challenges have substantial overlap with the areas Big Data and Analytics applications have been focusing on and made tremendous progress in. One can certainly argue that a Big Data application like Google maps has a simple and intuitive user interface, has standard APIs to annotate data, and has been architected to be very scalable. It is therefore very pertinent to look how these applications have been architected and what that means for EDA3.0 applications.

It is time for the next era in EDA that attacks these problems. EDA3.0 will deliver this next step up in productivity. In this era, EDA needs to provide designers with analysis tools that do not just analyze the results and produce reports, but tools that provide real insight. The size of the reports has already become overwhelming for most designers. Analysis tools need to provide data that will give designers insight in how to make their design better. We need to move from the era of analysis tools to analytics tools. These tools should take advantage of the compute power of large warehouse-scale clusters instead of individual servers such that they can provide near real-time insight in the state of a design. At the same time, we want to harness the power of these large compute clusters to devise smarter optimization algorithms that explore a larger part of the design space.

What will need to happen to make EDA3.0 reality? First we will have to capitalize on the changing nature of IT. We need to learn from Big Data, Cognitive and other data, and graph parallel systems. This will allow us to create an integrated design flow on very large compute clusters. Next, we need to change the way designers interact with design data and allow them to get much better insight in the state of their design. They need to understand what needs to be done next to meet their constraints. The analytics tools need to provide this insight. Finally, a new class of optimization algorithms needs to be invented that deliver a faster convergence and therefore designer turn around time (TAT) in meeting the design objectives on increasingly larger designs.

#### 2 Warehouse-Scale Computing

The term warehouse-scale computer was introduced in [1]. "The trend toward server-side computing and the exploding popularity of Internet services has created a new class of computing systems that we have named *warehouse-scale computers*, or *WSCs*. The name is meant to call attention to the most distinguishing feature of these machines: the massive scale of their software infrastructure, data repositories, and hardware platform. This perspective is a departure from a view of the computing problem that implicitly assumes a model where one program runs in a single machine. In warehouse-scale computing, the program is an Internet service, which may consist of tens or more individual programs that interact to implement complex end-user services such as email, search, or maps."

The authors point out many advantages of warehouse-scale computing. Many of them applicable to Electronic Design Automation as well. Before discussing the implications to EDA, let us look deeper into the Software Infrastructure needed for warehouse-scale computing. The authors define three typical software layers in a WSC deployment.

- *Platform-level software:* the common firmware, kernel, operating system distribution, and libraries expected to be present in all individual servers to abstract the hardware of a single machine and provide basic server-level services.

- Cluster-level infrastructure: the collection of distributed systems software that manages resources and provides services at the cluster level; ultimately, we consider these services as an operating system for a datacenter. Examples are distributed file systems, schedulers and remote procedure call (RPC) libraries, as

well as programming models that simplify the usage of resources at the scale of datacenters, such as MapReduce [3], Dryad [4], Hadoop [5], Sawzall [6], BigTable [7], Dynamo [8], Dremel [9], Spanner [10], and Chubby [11].

• *Application-level software:* software that implements a specific service. It is often useful to further divide application-level software into online services and offline computations because those tend to have different requirements. Examples of online services are Google search, Gmail, and Google Maps. Offline computations are typically used in large-scale data analysis or as part of the pipeline that generates the data used in online services; for example, building an index of the Web or processing satellite images to create map tiles for the online service.

How would this apply to a typical Electronic Design environment? Let us look at each of the three layers and start with the Platform-level software. In the early days of WSC, only large organizations like Google and Facebook were able to provide uniform platform-level software in their public clouds. But recent developments such as OpenStack [12] are making similar capabilities available to private clouds. While many EDA users have private clouds that are quite heterogeneous and different from enterprise to enterprise, technologies such as OpenStack drive to homogenize these heterogeneous environments. OpenStack software allows one to control large pools of compute, storage and networking resources throughout a datacenter, managed through a dashboard or via the OpenStack API. OpenStack works with popular enterprise and open source technologies making it ideal for heterogeneous infrastructure. This platform-level software is applicable to the EDA environment mostly as-is.

The cluster-level software provides the management of the resources and the programming models that simplify the usage of these resources. The management portion is in general applicable to EDA applications as well. For example, distributed file systems are key to store the huge amount of design data. Schedulers like Platform LSF [13] have been commonplace in EDA environments and the counter pieces in warehouse-scale computing are equally important.

Several of the programming models are relevant to EDA applications. For simplicity, let us divide the data in an electronic design flow in two categories: coredesign data and derived data.

- Core design data is the data created by the designers such as their Verilog and VHDL descriptions, their floorplan, the timing assertions, the base IP blocks and libraries as well as the data added by construction tools like synthesis, placement and routing to enable tape-out of OASIS.

- *Derived data* is the data produced by (mostly) analysis tools such as: verification traces and coverage, timing, noise and power reports, placement and routing density reports, audit and coverage reports.

Since our chips have grown in size and the capabilities and speed of the analysis tools have drastically improved the amount of derived design data in a design process has exploded. It has become a huge challenge for a design team to manage

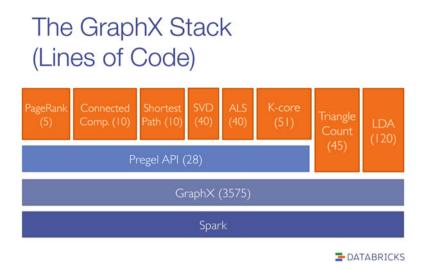

Fig. 1.1 The GraphX stack

this volume of data and more importantly make sense out of it. The insights needed to drive the next iteration of the design process have been more and more difficult to obtain. Many of the programming models described under the Cluster-level infrastructure are very well suited for this type of derived data. A programming paradigm like Bigtable [7] applies really well to most of the well-structured derived data that gets generated in the design process. Similarly, other non-SQL, SQL, and graph databases are very well suited for the volumes of derived data generated in a typical design process.

Cluster-level infrastructure for the core design data is less readily available. EDA research and development has spent many years optimizing core data-structures for fast logic simulation, quick synthesis and place and route, or huge scale checking for timing, LVS or DRC. However, time has come to relook at these now that we enter the era of warehouse-scale computing.

A programming model like Spark has become the basis for many algorithms that are very similar to core algorithms in EDA tools. For example, Fig. 1.1 shows the stack for the GraphX model built on top of Spark. It provides many components for key graph algorithms, such as shortest path algorithms, singular value decomposition, and connected component calculations.

What would be the key programming models that are needed in the EDA space? A distributed version of a network database like OpenAcces(OA), if it were to be designed to scale to very large sizes as Bigtable does, would be an essential programming model in the EDA stack. A very scalable implementation of a graph database would be a great foundation for analysis tools like Static Timing Analysis. Other key programming models are: a model to handle matrices for circuit simulators and a model for graphics data for layout applications. Fortunately, there are only a handful of these core programming models that can cover most of the EDA applications.

Creating these cluster-level programming models for EDA specific usage should be a very fertile ground for academic research. Many of the programming models used widely in analytics, big data and cloud applications are Open Source and came directly out of academic research. In addition to their availability under Open Source licenses, they formed the basis for a new generation of companies. Take, for example, Spark [15], which came out of UCB's AMPlab and led to the foundation of a company like DataBricks [16].

Once several of these cluster-level programming models are in place, EDA research and development should focus on the application-level software. To understand the application space, it is important to take a fresh look at how an end-to-end design flow should be built from these applications and not look at a one-to-one replacement of our current EDA tools. We need to look at the iterative design process through the same lens as many of the big data applications and split them in online services (e.g., interactive, fast response) and offline computations. Take, for example, static timing analysis. Performing the timing analysis itself can take a significant number of hours on a large chip (e.g., the offline computation). However, the user wants to be able to traverse the resulting outcome quickly to find specific problems and devise strategies to address them (e.g., the online service). The insights from the online service are crucial for the designer to drive the next iteration of the design process which can take place as the next offline computation to provide data for the next iteration of analysis. If we can extend this model such that we have a live database (like Google Maps) which reflects the latest state of the entire design (and has versioning to roll-back to earlier versions of the design), this model will be the basis for fast queries.

As soon as the offline computations are finished, they will be reflected back (and versioned) into the live model. This will allow designers to get quick insight in the current state of the entire design and its latest interactions between its partitions. In the next section, we will compare the scale of some of these analytics and big data applications with the scale of EDA applications, to understand if their programming models are suitable for the design sizes we typically encounter in EDA applications.

#### **3** Scale of Applications

In this section we will look at the question if the programming models in the clusterlevel infrastructure can scale to the level of EDA applications. We will look at various applications and compare them to typical EDA applications.

Most EDA tools are deployed in complex design flows and used by a large number of designers. Many tools communicate with each other through arcane file-formats [30] and produce data in huge text based log and report files. Most tools have a very large number of configuration parameters and require a very elaborate setup for a particular technology or design style, usually reflected in elaborate and complex control scripts.

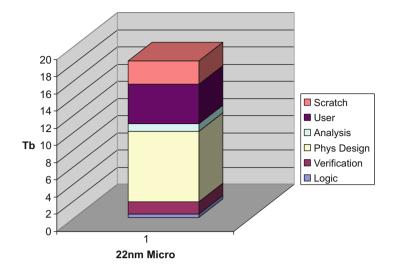

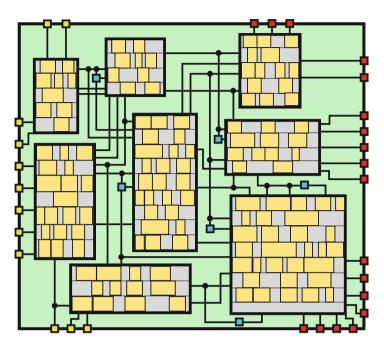

**Fig. 1.2** Design data for a 10 + B transistor 22 nm chip

It is not uncommon for design teams to write 1–2 millions of lines of Skill or Python scripts to create library cells and IP blocks. A complete design and verification flow can quickly add up to 1–2 million lines of TCL to control the tools and deal with the setup and environment in which IP and models are stored. And once the design flow is up and running, a large number of Python and Perl scripts are written to extract the key information from the terabytes of reports and design data. It is often difficult to know how many of these scripts exist in a design environment since they are often owned by individual designers. In addition to all the configuration and control files a large amount of data gets generated and stored.

Let us look at the amount of data produced by a design team designing a 10B + transistor processor in 22 nm technology as shown in Fig. 1.2. It takes about 12 Tb to store the entire golden data (including incremental revisions). Logic and verification setup takes about 2 Tb, the physical design data about 8–9 Tb and another 1–2 Tb for analysis reports. In addition, individual users keep another 6 Tb of local copies in user and scratch spaces. For functional verification, approximate 1.5 Tb of coverage data is collected daily. This data is very transient and about 2 weeks worth of data (21 Tb) is kept in a typical verification process.

After the design is finished, the physical data get compressed and streamed out to about 3Gb of OASIS. The product engineering team blows this up to around 1 Tb during mask preparation operations. Finally, another 5 Tb of test and diagnostics data gets generated in the post-silicon process.

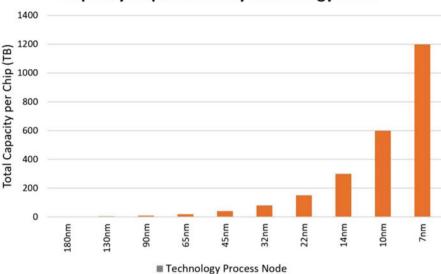

This looks like a significant amount of data but it tops out at 50 Tb for a multiyear design and manufacturing project. Recently a study [17] was published that produced the table in Fig. 1.3. It seems to project the 22 nm chip storage needs

#### Capacity requirement by technology node

Fig. 1.3 Estimated storage capacity requirements by EDA tools for the entire RTL-to-GDSII flow per chip design versus technology process node. (Source: Dell EMC)

at a 150 Tb or about 3x our estimate. It also projects a 2x increase in each of the subsequent technology nodes.

While this was once a phenomenal amount of data that put EDA at the forefront of storage and compute needs, it has been surpassed by many large cloud-based Big Data applications. Let us look at some of them.

Let us try to compare the scale of some of the cloud applications with the problem set we deal with in EDA. We will take a look at Google Maps [18] and some key metrics that we can compare with the design data above.

1. How much data has Google Maps accumulated?

Combining satellite, aerial and street level imagery, Google Maps has over 20 petabytes of data, which is equal to approximately 21 million GB, or around 20,500 Tb

2. How often are the images updated?

Depending on data availability, aerial and satellite images are updated every 2 weeks. Street View images are updated as quickly as possible, though Google wasn't able to offer specific schedules, due to its dependence on factors such as weather, driving conditions, etc.

3. In the history of Google Maps, how many Street View images have been taken? The Street View team has taken tens of millions of images since the Street View project began in 2007, and they've driven more than 5 million unique miles of road. How does this compare to the design data? Comparing the 50 Tb/design versus the 20 Pb of the fully annotated Google maps, the design data is only 1/400th the size. A large chip has 5 km of wire compared to the 5 million miles of road to accumulate street view images. Of course, the scale of intersections on the chips are in nm's and the road crossings are in kilometers. It would be interesting to compare the number of road intersections in the world with the number of vias on a chip. Typically, the street view data annotated with each street is significantly larger than the physical design data needed to be associated with each stretch of wire.

One major difference is that the core EDA design data is certainly more dynamic than the more static base map of roads in an application like Google maps. EDA tools can much more quickly reroute wires than physical roads can be built. But let us look at another data point to illustrate the velocity of data in a cloud application like YouTube. Each minute 300 h of video is uploaded to YouTube [19]. This is indexed, categorized, and made available. While we have no accurate data on how much of the design data changes each day, since it tops out at 50 Tb after a multi-year project, it is safe to assume that only a small fraction of it changes daily.

Based on these examples we conclude that many of the cluster-level programming models will be able to handle the typical data sizes in EDA projects. Let us look at the traversal speed of some of these models as well. Graph databases have become one of the fastest growing segments in the database industry. Graph databases not only perform well in a distributed environment but can also take advantage of accelerators such as GPUs. Blazegraph set up an experiment to run a Parallel Breadth First search on a cluster of GPUs. Using such a cluster, Blazegraph demonstrated a throughput of 32 Billion Traversed Edges Per Second (32 GTEPS), traversing a scale-free graph of 4.3 billion directed edges in 0.15 s [20]. This is a few orders of magnitudes more than a static timing analysis tool which traverses about 10 M edges per second on a single machine. An example of a matrix programming model is shown in Quadratic Programming Solver for Non-negative Matrix Factorization with Spark [21].

Despite the applicability of many of these programming models to EDA relatively little attention has been paid to them. This is caused by the fact that most of the public discussion has been overshadowed by other "cloud" aspects and specifically the element of data security [22, 23]. Indeed, only when sufficient security guarantees are given will designers put their entire IP portfolio on a public cloud. However, EDA applications can run in private (or hybrid) clouds and take full advantage of the massively distributed warehouse-scale computing infrastructure without the security issues.

Unfortunately, this heavy focus on the security aspect has overshadowed the discussion around the opportunities of warehouse-scale computing to the EDA design flows and applications. This is also the reason I am using the term "warehouse scale computing" instead of cloud to not distract from its underlying potential. In the next section, we will describe how EDA tools can take advantage of the warehouse-scale software infrastructure. We will describe how we can make a design flow a lot more productive and designer-friendly.

#### 4 EDA Applications

What does a designer (the EDA tool client) really want? She wants to get to the design DATA from anywhere and any place. She wants the DATA to be there without her waiting for it. She wants to analyze the DATA with whatever tools she can lay her hands on to learn how to improve her design. She wants to know how to get from A to B through the design process and wants design data, design navigation, and a design flow to act like Google maps. For example, wouldn't it be great if understanding timing and congestion problems in your design is no more difficult than turning on traffic congestion information in Google maps? Wouldn't it be great if we could annotate key manufacturing data from inline inspection tools just as easy as Street Views to our design data? This has certainly become easier to accomplish using key elements from cluster level programming models.

This type of rapid analysis and optimization can only be accomplished if the entire design data is in a (set of) live database(s) distributed among many machines in the warehouse-scale compute center. When design changes are made, the live data needs to be incrementally communicated and updated. We know how to do this for timing analysis integrated within a place and route flow. However, this incrementality needs to be extended to all analysis. Analysis engines can run on many parts of the design simultaneously and can be folded together in the live model. The analysis tools will produce the appropriate abstractions that are needed by the higher levels of hierarchy in the design.

Instead of thinking about synthesis, place, route, and timing algorithms, this DATA-centric EDA3.0 paradigm will start from the data, map it to the compute infrastructure using the right cluster-level infrastructure, and put the applications (e.g., placement, routing, timing analysis) on top of that using well-defined cluster-level APIs as services.

Clearly there are some technical challenges here. EDA data is more connected than many of the social networking applications. However, in many applications we have seen that EDA data viewed the right way is inherently more parallel than initially thought. The fact that tens or hundreds designers can work simultaneously and productively on a design makes it clear that the parallelism exists in the design process, albeit sometimes not in a single optimization run.

While EDA data is certainly more volatile during the optimization part of the process, the increased re-use of IP and increased use of hierarchy with appropriate abstractions has resulted in a much larger portion of the design data to be stable in the iterations of modern hierarchical designs. Furthermore, only a small portion of the chip and logic design gets (re-)done each day. With advanced version control fully integrated in the data itself, the knowledge of what actually changed can lead to a whole new class of optimization algorithms.

Large service providers such as Google and Facebook provide their own platform and cluster-level infrastructure based on special versions of open source code. Many smaller companies will build on standardized platforms such as CloudFoundry [24] and Bluemix [25]. The EDA industry needs to ask itself the question: what can we do to customize several of the cluster-level programming models to allow EDA tools to be written like services that interface with live design data through well-defined APIs?

#### 5 EDA Applications: Analysis

As described in Sect. 2 we can leverage many of the existing cluster-level infrastructure programming models for EDA applications. This is particularly true for the EDA applications that perform analysis and reporting. DRC, LVS, and timing analysis applications are well geared to the distributed infrastructure.

As an example, we deployed Neo4i [26] for timing analysis. Using Neo4i we now have an unprecedented capability to store detailed timing information in a highly efficient format, enabling very powerful query analysis. Our current benchmarking efforts have established the feasibility of storing a complete top-level chip timing graph from EinsTimer consisting of nearly 100 million nodes and associated timing properties in Neo4i. Using an IBM Power8 Linux server, we are able to import data within 11 minutes. The resulting graph database is indexed on several key query parameters, such instance names and slack values, within a matter of a few minutes. Once indexed, we have demonstrated the ability to perform lookups, for example iterating through all timing end points in the top-level chip run, and returning the worst N sorted by slack within 2 seconds. Given the underlying graph schema consisting of both properties and labels, we have the ability to support multiple levels of hierarchy within a single graph instance, which then enables efficient cross-hierarchy analysis within a single instance of Neo4J. For example, we have demonstrated the ability to compare in vs. out of context timing for approximately 1000 primary inputs on given macro within its top-level environment within 5 seconds. Previously, such cross-hierarchy analysis would require complex code to parse timing reports and resolve the names throughout the hierarchy. Such powerful analytics can often be achieved in a single line of Neo4J Cypher, illustrating the power of graph databases in analyzing complex EDA data sets.

The other advantage of using a graph database as a timing data server is that it can provide the data as an always on web service. We are fully leveraging Neo4j as a web-server which subsequently allows for a rich variety of applications to be built on top of the underlying graph database service, allowing us to package numerous queries as REST end points - as well as visualize results using custom built webapplications which allow for a clean visual representation of key timing metrics. From the standpoint of a chip designer, the above framework provides "any time anywhere" access to critical EDA timing results for use in triage, as well as trend analysis over time.

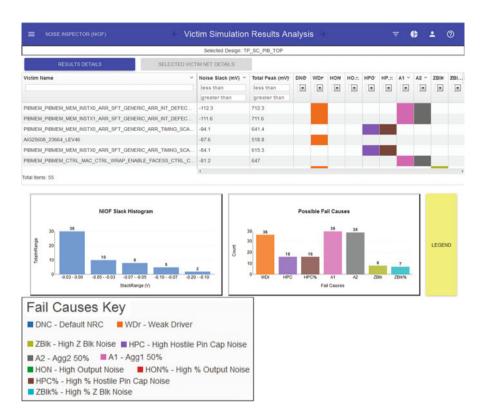

We use a similar framework for noise analysis. In Fig. 1.4 we show an example of a Noise inspection tool that we developed on top of an analytics framework. The cause of noise problems is often not very easy to determine. Noise can be caused by a combination of weak drivers, low tolerance for noise on sink gates, large aggressor

Fig. 1.4 Noise inspection example

couplings, DC aggressor nets, and various other reasons. For a designer or synthesis or routing tool to effectively combat noise problems it is important to get a good profile of the likelihood of each of these causes to try out the best remedies. This requires both a global analysis of the entire design to look for specific weaknesses in certain IP blocks and a detailed drill-down capability to address specific problems on specific instances in a design. We wrote the output of our EinsNoise tool in MongoDB. Using the "R" analysis language we were able to quickly classify these sources as shown in Fig. 1.4.

#### 6 EDA Applications: Synthesis and Optimization

In Sect. 5 we described how several of the programming models apply to EDA analysis applications. A key question is how we can use the massive parallelism for optimization functions such as logic synthesis, placement, and routing. A lot of research and development has gone into multi-threaded applications for optimiza-

Fig. 1.5 Lack of predictability in the design flow

tion. However, effective strategies to leverage massive distributed infrastructure in optimization have not been widely considered. One of the reasons is that most research has focused on optimizing a single algorithm or application instead of looking across the entire design process. Let us look closer at the synthesis, place, and route flow.

In a design project, designers iterate numerous times across this flow. The main reason for these iterations is the lack of prediction of the effect of early decisions on the final outcome. This is best illustrated in the diagram in Fig. 1.5. When a designer is writing her HDL it is still very difficult to predict the outcome on the final placed and routed result. To improve the predictability, we include some prediction of placement into the logic synthesis steps and some routing prediction into the placement steps. But since these steps are fairly compute intensive only a very small part of the design space is explored. This can be illustrated by the effects that tool parameters have on the result. Designers affect the behavior of the tools by hints and the numerous parameters that each of the optimization tools have. Changing a few of these settings can lead to drastically different outcomes. The designers explore this opportunity to get their designs to meet power or timing objectives or ensure they are routable.

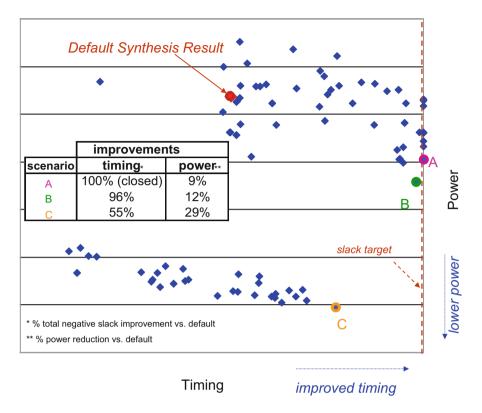

Let us look at an example in Fig. 1.6. This graph shows the results of the same design after synthesis, placement, and routing. The difference between each of the points on the graph is the different parameters that were used in the synthesis tools. The horizontal access shows the results with respect to timing. The vertical access shows the results with respect to power. Improved timing is toward the right on the x-axis. Improved power is lower on the y-axis. The result of the run with default parameters is the red diamond in the middle of the graph. The default result met the timing constraints but significant optimization to improve power is still possible. The blue diamonds show more than one hundred results after placement and routing. The only difference is the parameters used in synthesis. Of particular interest are points A, B, and C. Point A exactly meets timing, but uses 9% less power than the default run. Point C is of particular interest. While not as fast as the default, timing is still better than point A. Power is reduced by 30% versus the default run. This

Fig. 1.6 Impact of synthesis parameters on final placed and routed designs

example is an illustration of the drastic effect that synthesis parameters can have on the final outcome of the optimization process.

In a practical hierarchical design process, the requirements on the implementation of a block change frequently throughout the process. Floorplans might need to be adjusted to accommodate other blocks. Many timing paths run across multiple blocks and timing assertions for one block will depend on the quality of results of other blocks that share these paths.

Running the tools end to end with just a few different parameters is quite wasteful. Most of the steps are repeated in each of the runs, and only the steps following the ones that are affected by the specific parameter changes will produce different results. Can we change the paradigm in optimization to take advantage of the cluster programming models that run very efficiently on warehouse-scale computers?

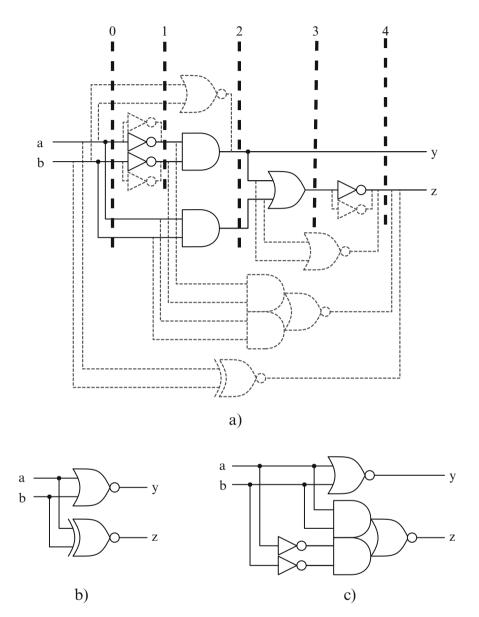

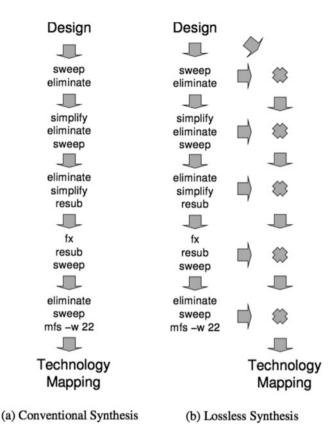

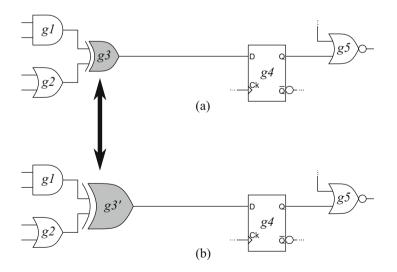

Decisions made during synthesis have a major impact on the outcome of synthesis itself and especially on the structure of the resulting netlist. While subsequent optimizations during physical synthesis will make modifications to this structure, these optimizations are mostly local and do not change the bias that was put in early in the process. Stok observed in the wavefront technology mapping paper [27] that technology mapping is the stage in logic synthesis where a most of the netlist structure gets locked in. By giving more alternatives to technology mapping, it is able to make better choices. As shown in Fig. 1.7, the wavefront paper introduced the concept of the multi-input (choice nets) which allows technology mapping to choose one of the inputs when determining the actual technology implementation of the gate. If timing optimization is the goal, technology mapping can choose the input that produces the fastest timing for each cone of logic (covering step) independently. This will potentially lead to an area increase since implicit cloning of gates is taking place, but can certainly help a lot to get to the fastest timing results.

Chatterjee [28] expands on this idea and shows how to reduce the structural bias in technology mapping by creating even more alternatives in the netlist before technology mapping, so the covering step has more alternatives to choose from. In Fig. 1.8 it is shown how the eliminate, simplify, factoring and re-substitution transformations are changed to add many choices to the netlist before technology mapping.

However, in both of these approaches the choices are locked in during technology mapping. The wavefront algorithm has the advantage that it can see the impact of all gates being mapped to a particular technology implementation before making technology choices in the second pass. While this certainly improved the choices that technology mapping makes, it still required these choices to be made with very imperfect information. We are making these choices before any of the impact of placement, routing or routing congestion is understood. In general, in the overall optimization process we perform many optimizations in sequence, try many alternatives, but quickly lock in a solution before we go into the next optimization step. In many cases, we make the choices before having adequate information to do so. As a result, synthesis algorithms make the major decisions on the structure of the netlist, which in turn will have very significant impact on placement and routing, without having adequate information on the consequences of its choices.

Instead, we would like to leave the "alternative" choices in the network until placement and routing have been completed and only resolve the best choices that make us meet our design constraints once we have sufficient reliable information to do so. However, at the time of creation of the wavefront algorithm we were limited by the available compute power and could not deal with the explosion in data that needs to be handled in placement, timing and routing if all the choices are left around. However, we are getting to a time where this is becoming practical. If we look at applications that run really well on warehouse-scale computers, they very effectively distribute the compute workload across many lighter weight computations.

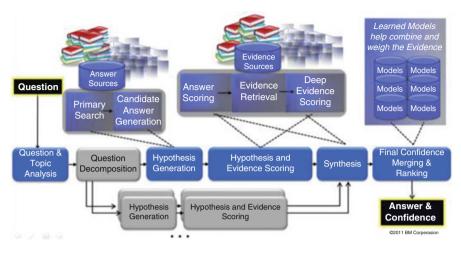

Let us look at Watson as an example. The DeepQA [29] architecture is underlying the capability of Watson to understand and answer questions. Figure 1.9 shows a high-level picture of the DeepQA architecture. "The DeepQA architecture views the problem of Automatic Question Answering as a massively parallel hypothesis generation and evaluation task. As a result, DeepQA is not just about questionin/answer-out—rather it can be viewed as a system that performs differential

Fig. 1.7 Wavefront technology mapping, L. Stok, M. Iyer, A.J. Sullivan, 1998 IWLS

diagnosis: it generates a wide range of possibilities and for each develops a level of confidence by gathering, analyzing and assessing evidence based on available data."

Fig. 1.8 Reducing Structural Bias in Technology Mapping, S. Chatterjee A. Mishchenko R. Brayton, X. Wang T. Kam, 2005 TCAD

What if we looked at the synthesis, placement, and routing design flow through a similar lens? Logic synthesis will be the candidate generator. It will generate many different topologies of netlists that implement the same logic function. To prevent that number of netlists from exploding, many of them can be embedded in a singular netlist using choice nodes or multi-input nets. Placement and routing can elaborate these candidates further such that one gets an understanding how these topologies will be physically implemented. The elaborated alternatives will be physically complete (placed and routed) and a much more reliable source for the analysis tools. Timing, power, and noise analysis will be our scoring engines. As soon as synthesis has generated the choices, the elaboration and scoring of each of them can be done in a very distributed fashion. A final stage scores all the partial alternatives and folds them together in one final result that meets the timing, power, and noise targets. Except for the final folding stage, all other steps can be implemented in a very parallel and distributed fashion. And even the final folding stage can be very parallel as long as the merging steps are very carefully executed.

Fig. 1.9 DeepQA software architecture

Once we start to think about other optimization problems in EDA in this paradigm of "generating many alternatives and scoring them in a very distributed fashion" a larger part of the design space can be explored.

#### 7 Summary

It is time for the design and EDA industry to embrace warehouse-scale computing. We need to look past cloud as an IT cost saving and look at warehouse-scale computing as an opportunity to bring a significant higher level of productivity to the design community. EDA3.0 tools need to be constructed such that the DATA is the central point in the EDA flow, not the optimization and analysis algorithms. These will become the services build around the data. Depending on their runtime they will need to be configured as online or offline services. Taking advantage of analytics technologies will drive to more intuitive and simplified user interfaces that provide better insight in the data. Using programming model Rest APIs will enforce standardized interface development. The massive compute power of a warehouse-scale computer will provide more scalable design solutions and better optimization. Analytics engines will allow for a much better insight in the derived design data than the numerous Perl and Python scripts currently provide.

EDA3.0 design flows will be significantly easier to manage and result in much more robust and predictable design flows. This will be necessary to take on the challenges to design large systems-on-chips built from future nano-scale devices.

#### References

- 1. L.A. Barroso, J. Clidaras, U. Hölzle, The datacenter as a computer: An introduction to the design of warehouse-scale machines. Synth. Lectures Comput. Architec. 8(3), 1–154 (2013)

- 2. R. Brayton, J. Cong, Nsf workshop on EDA: Past, present, and future (part 2). IEEE Design Test Comput. **27**(3), 62–74 (2010)

- 3. J. Dean, S. Ghemawat, MapReduce: Simplified data processing on large clusters. Commun. ACM **51**, 107–113 (2008)

- M. Isard, M. Budiu, Y. Yu, A. Birrell, D. Fetterly, Dryad: Distributed data-parallel programs from sequential building blocks. ACM SIGOPS Oper. Syst. Rev. 41(3), 59–72 (2007)

- 5. The Hadoop Project. [Online] http://hadoop.apache.org

- 6. R. Pike et al., Interpreting the data: Parallel analysis with Sawzall. Sci. Program. J. **13**, 227–298 (2005)

- F. Chang, J. Dean, S. Ghemawat, W.C. Hsieh, D.A. Wallach, M. Burrows, T. Chandra, A. Fikes, R.E. Gruber, Bigtable: A distributed storage system for structured data. ACM Transac. Comput. Syst. 26(2), 4 (2008.) http://static.googleusercontent.com/media/research.google.com/en// archive/bigtable-osdi06.pdf

- G. DeCandia, D. Hastorun, M. Jampani, G. Kakulapati, A. Lakshman, A. Pilchin, S. Sivasubramanian, P. Vosshall, W. Vogels, Dynamo: amazon's highly available key-value store. ACM SIGOPS Oper. Syst. Rev. 41(6), 205–220 (2007)

- S. Melnik, A. Gubarev, J.J. Long, G. Romer, S. Shivakumar, M. Tolton, T. Vassilakis, Dremel: Interactive analysis of web-scale datasets. Proc. VLDB Endowment 3(1–2), 330–339 (2010)

- J.C. Corbett, J. Dean, M. Epstein, A. Fikes, C. Frost, J.J. Furman, S. Ghemawat, A. Gubarev, C. Heiser, P. Hochschild, W. Hsieh, Spanner: Google's globally distributed database. ACM Transac. Comput. Syst. **31**(3), 8 (2012)

- M. Burrows, W.A. Seattle, *The Chubby Lock Service for Loosely-Coupled Distributed Systems*, Proceedings of OSDI'06: Seventh Symposium on Operating System Design and Implementation, 2006

- 12. Openstack, [Online] www.openstack.org

- IBM Spectrum LSF, [Online] IBM, http://www-03.ibm.com/systems/spectrum-computing/ products/lsf/

- 14. OpenAccess, [Online] http://www.si2.org/openaccess/

- 15. Spark, [Online] https://en.wikipedia.org/wiki/Apache\_Spark

- 16. Databricks, [Online] https://databricks.com

- 17. L. Rizzatti, *Digital Data Storage is Undergoing Mind-Boggling Growth*, [Online] http://www.eetimes.com/author.asp?section\_id=36&doc\_id=1330462

- 18. Google Maps facts, [Online] http://mashable.com/2012/08/22/google-maps-facts/

- Data never sleeps, [Online] http://wersm.com/how-much-data-is-generated-every-minute-onsocial-media/#!prettyPhoto

- 20. [Online] https://www.blazegraph.com/whitepapers/mapgraph\_clusterBFS-ieee-bigdata-2014.pdf

- 21. [Online] http://spark-summit.org/2014/talk/quadratic-programing-solver-for-non-negativematrix-factorization-with-spark

- 22. EDA forecast meeting, [Online] 14 Mar 2013, http://www.edac.org/events/2013-EDA-Consortium-Annual-CEO-Forecast-and-Industry-Vision/video

- A. Kuehlmann, R. Camposano, J. Colgan, J. Chilton, S. George, R. Griffith, P. Leventis, D. Singh, *Does IC Design have a Future in the Clouds?*. Proceedings of the 47th Design Automation Conference, 2010 (pp. 412–414). ACM

- 24. [Online] https://www.cloudfoundry.org

- 25. [Online] https://console.ng.bluemix.net

- 26. [Online] Neo4j https://neo4j.com

- 27. L. Stok, M.A. Iyer, A.J. Sullivan, *Wavefront Technology Mapping*, Proceedings of the Conference on Design, Automation and Test in Europe, 1998 (p. 108), ACM

- S. Chatterjee, A. Mishchenko, R.K. Brayton, X. Wang, T. Kam, Reducing structural bias in technology mapping. IEEE Transac. Comput. Aided Design Integr. Circuits Syst. 25(12), 2894–2903 (2006)

- 29. [Online] http://researcher.watson.ibm.com/researcher/view\_group\_subpage.php?id=2159

- 30. EDA file formats, [Online] En.wikipedia.org/wiki/CategoryEDA\_file\_formats

# Chapter 2 Can Parallel Programming Revolutionize EDA Tools?

Yi-Shan Lu and Keshav Pingali

#### 1 Introduction

I think this is the beginning of a beautiful friendship. Humphrey Bogart in Casablanca.

Until a decade ago, research in parallel programming was driven largely by the needs of computational science applications, which use techniques like the finite-difference and finite-element methods to find approximate solutions to partial differential equations. In finite differences, the key computational kernels are stencil computations on regular grids, and the solution of linear systems with structured sparsity such as banded systems. In finite-elements, the key computational kernel is the solution of sparse linear systems in which matrices have unstructured sparsity; these linear systems are usually solved using iterative methods like conjugate gradient in which the main computation is sparse matrix–vector multiplication.

Parallel programming research therefore focused largely on language support, compilation techniques, and runtime systems for matrix computations. Languages like High Performance FORTRAN (HPF) [21] and Coarray FORTRAN [32] were developed to make it easier to write matrix applications. Sophisticated compiler technology based on polyhedral algebra was invented to optimize loop nests that arise in matrix computations [6, 13, 14]. Runtime systems and communication libraries like OpenMP and MPI provided support for communication and synchronization patterns found in these applications.

While computational science applications and matrix computations continue to be important, our group at the University of Texas at Austin and several others across the world have shifted our focus to applications, such as the following ones, which compute on *unstructured graphs*.

Y.-S. Lu (🖂) • K. Pingali

The University of Texas at Austin, Austin, TX, USA e-mail: yishanlu@utexas.edu; pingali@cs.utexas.edu

<sup>©</sup> Springer International Publishing AG 2018

A.I. Reis, R. Drechsler (eds.), Advanced Logic Synthesis, https://doi.org/10.1007/978-3-319-67295-3\_2

- In social network analysis, the key data structures are extremely sparse graphs in which nodes represent entities and edges represent relationships between entities. Algorithms for breadth-first search, betweenness-centrality, page-rank, max-flow, etc. are used to extract network properties, to make friend recommendations, and to return results sorted by relevance for search queries [2, 20].

- Machine-learning algorithms like belief propagation and survey propagation are based on message-passing in a factor graph, which is a sparse bipartite graph [23].

- Data-mining algorithms like k-means and agglomerative clustering operate on dynamically changing sets and multisets [37].

- Traffic and battlefield simulations often use event-driven (discrete-event) simulation [27] in networks.

- Program analysis and instrumentation algorithms used within compilers are usually based on graphical representations of program properties, such as points-to graphs [3, 15, 25, 34].

Irregular graph applications such as these can have a lot of parallelism, but the patterns of parallelism in these programs are very different from the parallelism patterns one finds in computational science programs.

- Graphs in many of these applications are very dynamic data structures since their structure can be morphed by the addition and removal of nodes and edges during the computation. Matrices are not good abstractions for such graphs.

- Even if the graphs have fixed structure, many of the algorithms do not fit the matrix-vector/matrix-matrix multiplication computational patterns that are the norm in computational science. One example is delta-stepping, an efficient parallel single-source shortest-path (SSSP) algorithm [20, 26]. This algorithm maintains a work-list of nodes, partially sorted by their distance labels. Nodes enter and leave the work-list in a data-dependent, statically unpredictable order. This is a computational pattern one does not see in traditional computational science applications.

- Parallelism in irregular graph applications like delta-stepping is dependent not only on the input data but also on values computed at runtime. This parallelism pattern, which we call *amorphous* data-parallelism [33], requires parallelism to be found and exploited at runtime during the execution of the program. In contrast, the conventional data-parallelism in computational science kernels is independent of runtime values and can found by static analysis of the program.<sup>1</sup>

In spite of these difficulties, the parallel programming research community has made a lot of progress in the past 10 years in designing abstractions, programming models, compilers, and runtime systems for exploiting amorphous data-parallelism in graph applications. These advances have not yet had a substantial impact on EDA tools even though unstructured graphs underlie many EDA algorithms. The goal of

<sup>&</sup>lt;sup>1</sup>Sparse direct methods are an exception, but even in these algorithms, a dependence graph, known as the elimination tree, is built before the algorithm is executed in parallel [5].

this paper is to summarize advances reported in previous papers [20, 33] and discuss their relevance to the EDA tools area, with the goal of promoting more interaction between the EDA tools and parallel programming communities.

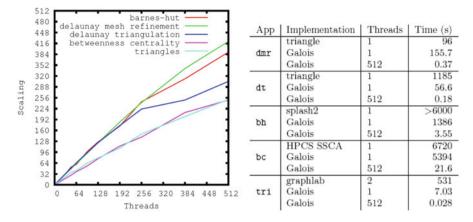

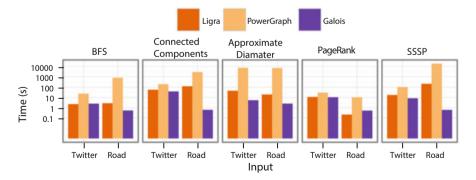

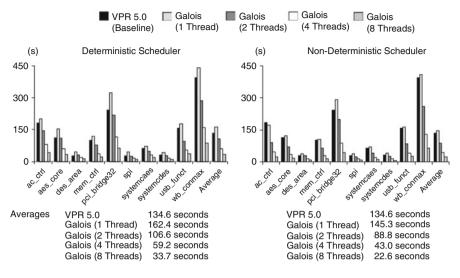

The rest of this paper is organized as follows. Section 2 describes an abstraction for graph algorithms, called the operator formulation of algorithms. Section 3 discusses the patterns of parallelism in graph algorithms, and describes the Galois system, which exploits this parallelism while providing a sequential programming model implemented in C++. Section 4 summarizes the results of several case studies that use the Galois system, including scalability studies on large-scale shared-memory machines [18], and implementations of graph analytics algorithms [31], subgraph isomorphism algorithms, and FPGA maze routing [28]. We conclude in Sect. 5.

#### 2 Abstractions for Graph Algorithms

Parallelism in matrix programs is usually described using program-centric concepts like parallel loops and parallel procedure calls. One lesson we have learned in the past 10 years is that parallelism in graph algorithms is better described using a *data-centric* abstraction called the *operator formulation of algorithms* in which data structures, rather than program constructs, play the central role [33]. To illustrate concepts, we use the single-source shortest-path (SSSP) problem. Given an undirected graph G = (V, E, w) in which V is the set of nodes, E the set of edges, and w a map from edges to positive weights, the problem is to compute for each node the shortest distance from a source node s. There are many algorithms for solving this problem such as Dijkstra's algorithm, Bellman-Ford algorithm, delta-stepping and chaotic relaxation [20], but in the standard presentation, these algorithms appear to be unrelated to each other. In contrast, using the operator formulation elucidates their similarities and differences.

#### 2.1 Operator Formulation

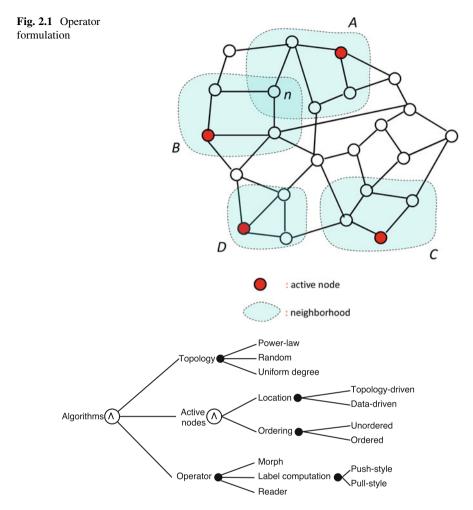

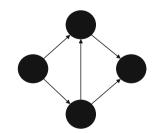

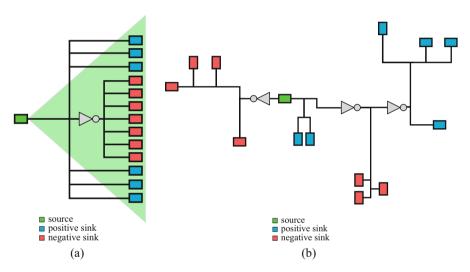

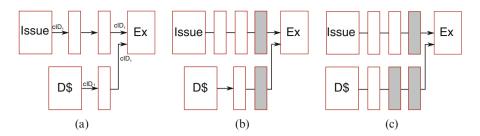

The operator formulation of an algorithm has a *local view* and a *global view*, shown pictorially in Fig. 2.1. This formulation of algorithms leads to a useful classification of algorithms, called TAO analysis, shown in Fig. 2.2.

#### 2.1.1 Local View of Algorithms: Operators

The local view is described by an *operator*, which is a graph update rule applied to an *active node* in the graph (some algorithms have active *edges*, but to avoid verbosity, we refer only to active nodes in this paper). Each operator application,

Fig. 2.2 TAO analysis of graph algorithms

called an *activity*, reads and writes a small region of the graph around the active node, called the *neighborhood* of that activity. In Dijkstra's SSSP algorithm, the operator, called the relaxation operator, uses the label of the active node to update the labels of its immediate neighbors. Figure 2.1 shows active nodes as filled dots, and neighborhoods as clouds surrounding active nodes, for a generic algorithm. An active node becomes inactive once the activity is completed.

In general, operators can modify the graph structure of the neighborhood by adding and removing nodes and edges (these are called *morph* operators). In most graph analytics applications, operators only update labels on nodes and edges, without changing the graph structure. These are called *label computation* operators; a *pull-style operator* reads the labels of nodes in its neighborhood and writes to the

label of its active node, while a *push-style operator* reads the label of the active node and writes the labels of other nodes in its neighborhood. Dijkstra's algorithm uses a push-style operator. In algorithms that operate on several data structures, some data structures may be read-only in which case the operator is a *reader* for those data structures.

Neighborhoods can be distinct from the set of immediate neighbors of an active node, and in principle, can encompass the entire graph, although usually they are small regions of the graph surrounding the active node. Neighborhoods of different activities can overlap; in Fig. 2.1, node *n* is contained in the neighborhoods of both activities *A* and *B*. In a parallel implementation, the semantics of reads and writes to such overlapping regions, known as the *memory model*, must be specified carefully.

#### 2.1.2 Global View of Algorithms: Location of Active Nodes and Ordering

The global view of a graph algorithm is captured by the location of active nodes and the order in which activities must appear to be performed.

Topology-driven algorithms make a number of sweeps over the graph until some convergence criterion is met; in each sweep, all nodes are active initially. The Bellman-Ford SSSP algorithm is an example. Data-driven algorithms, on the other hand, begin with an initial set of active nodes, and other nodes may become active on the fly when activities are executed. These algorithms do not make sweeps over the graph, and terminate when there is no more active nodes. Dijskstra's SSSP algorithm is a data-driven algorithm: initially, only the source node is active, and other nodes become active when their distance labels are lowered.

The second dimension of the global view of algorithms is *ordering*. In *unordered* algorithms, any order of processing active nodes is semantically correct; each sweep of the Bellman-Ford algorithm is an example. Some orders may be more efficient than others, so unordered algorithms sometimes assign *soft* priorities to activities, but these are only suggestions to the runtime system, and priority inversions are permitted in the execution. In contrast, *ordered* algorithms require that active nodes appear to have been processed in a specific order; Dijkstra's algorithm and algorithms for discrete-event simulation are examples. This order is specified by assigning priorities to active nodes, and the implementation is required to process active nodes so that they appear to have been scheduled for execution in *strict* priority order from earliest to latest.

#### 2.2 Trade-offs Between Topology-Driven and Data-Driven Algorithms

Many graph problems, like SSSP, can be solved by both topology- and data-driven algorithms. However, one should be aware of the tradeoffs involved when choosing algorithms.

Topology-driven algorithms are easier to implement because iteration over active nodes can be implemented by traversing the nodes in the representation of the graph (usually arrays). However, there may be wasted work in each sweep because there may not be useful work done at many nodes.

In contrast, data-driven algorithms can be work-efficient since activities are performed where there is useful work to be done. For many problems, data-driven algorithms are asymptotically faster than topology-driven algorithms. For instance, the complexity of the Bellman-Ford algorithm is O(|E||V|), whereas Dijkstra's algorithm is  $O(|E|\log(|V|))$ .

On the other hand, data-driven algorithms can be complicated to implement because they need a work-set to track active nodes. Sequential implementations use lists and priority queues for unordered and ordered algorithms, respectively. Concurrent work-lists for graph algorithms are difficult to implement efficiently: since the amount of work in each activity is usually fairly small, adding and removing active nodes from the work-list can become a bottleneck unless the work-list is designed very carefully. Nguyen et al. [19, 31] describe a scalable work-set called *obim* that supports soft priorities.

The best choice of algorithm for a given problem can also depend on the topology of the graph, as we show in Sect. 4.2 [9, 29]. In many social networks such as the web graph or the Facebook friends graph, the degree distribution of nodes roughly follows a power law, so these are often referred to as *power-law* graphs. In contrast, road networks and 2D/3D grids/meshes are known as *uniform-degree* graphs because most nodes have roughly the same degree. Graphs for VLSI circuits fall in this category. *Random* graphs, which are created by connecting randomly chosen pairs of nodes, constitute another category of graphs. Different graph classes have very different properties: for example, the diameter of a randomly generated power-law graph grows only as the logarithm of the number of nodes in the graph but for uniform-degree graphs, the diameter can grow linearly with the number of nodes [20].

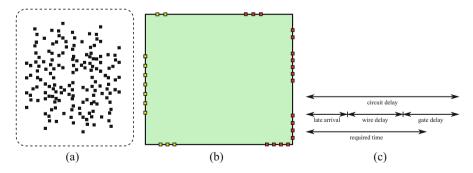

Figure 2.2 summarizes this discussion. We call it TAO analysis for its three main dimensions: Topology of the input graph, Activity location and ordering, and Operator. Note that TAO analysis does not distinguish between sequential and parallel algorithms.

#### **3** Exploiting Parallelism in Graph Algorithms

Parallelism can be exploited by processing active nodes in parallel, subject to neighborhood and ordering constraints. Since neighborhoods can overlap, the memory model, which defines the semantics of reads and writes in overlapped regions, may prevent some activities with overlapping neighborhoods from executing in parallel. In addition, ordering constraints between activities must be enforced. We call this pattern of parallelism *amorphous* data-parallelism [33]; it is a generalization of data-parallelism in which (1) there may be neighborhood and ordering constraints that

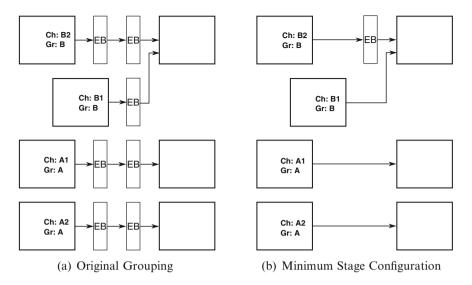

Fig. 2.3 Parallelization strategies

prevent all activities from executing in parallel, and (2) the execution of an activity may create new activities.

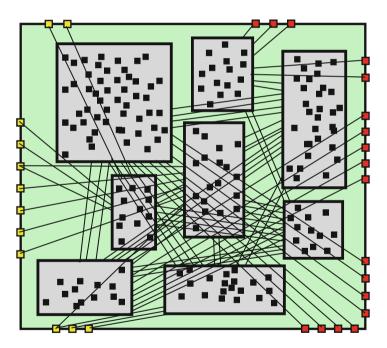

Figure 2.3 summarizes the important choices in implementing parallel graph programs. There are two popular memory models: BSP-style (Bulk-Synchronous Parallel) semantics [39] and transactional semantics.

#### 3.1 BSP-Style Semantics

The program is executed in rounds (also known as super-steps), with barrier synchronization between rounds. Writes to the graph are considered to be communication from a round to the following round, so they are applied to the graph only at the beginning of the following round. Multiple updates to a label are resolved as in PRAM models such as by using a reduction operation to combine the updates into a single update [11].

BSP-style parallelization may work well for graph applications in which the number of activities in each round is large enough to keep the processors of the parallel machine busy. One example is breadth-first search (BFS) on a power-law graph. Each round handles nodes at a single BFS level and computes labels for nodes at the next BFS level. Since the average diameter of power-law graphs is small, there will be a lot of parallel activities in most rounds. On the other hand, BSP-style parallelization may not perform well for graphs that have high average diameter, such as road networks or VLSI circuits, as we show experimentally in Sect. 4.2. This is because the number of super-steps required to execute the algorithm may be large, and the number of activities in each super-step may be small.

#### 3.2 Transactional Semantics

In this model, parallel execution of activities is required to produce the same answer as executing activities one at a time in some order that respects priorities. Intuitively, this means that activities should not "see" concurrently executing activities, and the updates made by an activity should become visible to other activities only after that activity completes execution. Formally, these two properties of transactional execution are known as isolation and atomicity. Transactional semantics are implemented by preventing activities from executing in parallel if they *conflict*. For unordered algorithms, a conservative definition is that activities conflict if their neighborhoods overlap. In Fig. 2.1, activities Aand B conflict because node n is in both their neighborhoods. Activities C and D do not conflict, and they can be executed in parallel with either A or B. Exploiting properties of the operator such as commutativity can lead to more relaxed definitions of conflicts, enhancing parallelism [16]. Given a definition of conflicts, the implementation needs to ensure that conflicting activities do not update the graph in parallel. This can be accomplished using *autonomous scheduling* or *coordinated scheduling*.

In autonomous scheduling, activities are executed speculatively. If a conflict is detected with other concurrently executing activities, some activities are aborted, enabling others to make progress; otherwise, the activity commits, and its updates become visible to other activities. Autonomous scheduling is good for exploiting parallelism but for some unordered algorithms, the output of the program can depend on the precise order in which activities are executed so the output may be non-deterministic in the sense that different runs of the program for the same input may produce different outputs. Delaunay mesh refinement and maze routing, discussed in Sect. 4.4, are examples. It is important to notice that this non-determinism, known as *don't-care non-determinism*, arises from under-specification of the order in which activities must be processed, and not from race conditions in updating shared state: even in a sequential implementation, the output of the program can depend on the order in which the work-list of active nodes is processed.

Coordinated scheduling strategies ensure that conflicting activities do not execute simultaneously [33]. For some algorithms, such as those that can be expressed using generalized sparse matrix–vector product, static analysis of the operator shows that active nodes can be executed in parallel without any conflict-checking. This is called *static parallelization*, and it is similar to auto-parallelization of dense array programs. *Just-in-time parallelization* preprocesses the input graph to find conflict-free schedules (e.g., by graph coloring); it can be used for topology-driven algorithms like Bellman-Ford in which neighborhoods are independent of data values. *Runtime parallelization* is general: the algorithm is executed in a series of rounds, and in each round, a set of active nodes is chosen, their neighborhoods are computed, and a set of non-conflicting activities are selected and executed. This approach can be used for deterministic execution of unordered algorithms [31].

# 3.3 The Galois System

The Galois system is an implementation of these data-centric abstractions.<sup>2</sup> Application programmers write programs in sequential C++, using certain programming

$<sup>^{2}</sup>$ A more detailed description of the implementation of the Galois system can be found in our previous papers such as [31].

```

1

#include "Galois/Galois.h"

2

3

struct Data {int dist;};

4

typedef Galois :: Graph :: LC_CSR_Graph < Data , void > Graph ;

5

typedef Graph :: GraphNode Node;

6

7

struct BFS {

8

Graph& g;

9

BFS(Graph& g) : g(g) {}

void operator () (Node n, Galois :: UserContext <Node>& ctx) {

10

11

int newDist = g.getData(n).dist + 1;

12

for (auto e : g.edges(n)) {

13

Node dst = g.getEdgeDst(e);

14

int& dstDist = g.getData(dst).dist;

15

if (dstDist > newDist) {

16

dstDist = newDist:

17

ctx.push(dst);

18

- }

19

}

20

}

21

};

22

23

int main(int argc, char ** argv) {

24

Graph g;

25

Galois::readGraph(g, argv[1]);

26

Galois:: do all local(g, [&g] (Node n) {g.getData(n).dist = DIST INFINITY;});

27

int start = atoi(argv[2]);

28

Node src = *(std::advance(g.begin(),start));

29

g.getData(src).dist = 0;

30

Galois:: for each(src, BFS{g});

31

return 0:

32 }

```

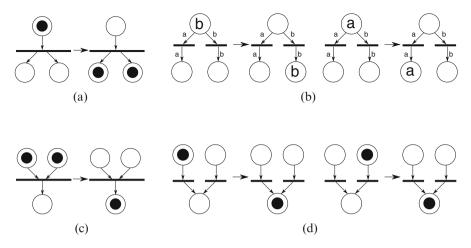

Fig. 2.4 Push-style BFS in Galois

patterns, described below, to highlight opportunities for exploiting amorphous dataparallelism.

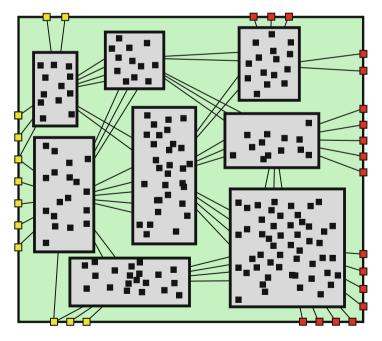

Key features of the system are described below, using the code for push-style BFS shown in Fig. 2.4. This code begins by reading a graph from a file (line 25) and constructing a compressed-sparse-row (CSR) representation in memory (line 4). Line 26 initializes the dist fields of all nodes to  $\infty$ , and lines 27–29 read in the ID of the source node and initialize its dist field to 0.

- Application programmers specify parallelism *implicitly* by using Galois set iterators [33] which iterate over a work-list of active nodes. For data-driven algorithms, the work-list is initialized with a set of active nodes before the iterator begins execution. The execution of a iteration can create new active nodes, and these are added to the work-list when that iteration completes execution. Topology-driven algorithms are specified by iteration over graph nodes, and the iterator is embedded in an ordinary (sequential) loop, which iterates until the convergence criterion is met. In Fig. 2.4, data-driven execution is specified by line 30, which uses a Galois set iterator to iterate over a work-list initialized to contain the source node src.

- The body of the iterator is the implementation of the operator, and it is an imperative action that reads and writes global data structures. In Fig. 2.4, the operator is specified in lines 10–20. This operator iterates over all the neighbors

of the active node, updating their distance labels as needed. Iterations are required to be *cautious*: an iteration must read *all* elements in its neighborhood before it writes to *any* of them [33]. In our experience, this is not a significant restriction since the natural way of writing graph analytics applications results in cautious iterations.

- For unordered algorithms, the relative order in which iterations are executed is left unspecified in the application code. An optional application-specific priority order for iterations can be specified with the iterator [30], and the implementation tries to respect this order when it schedules iterations.

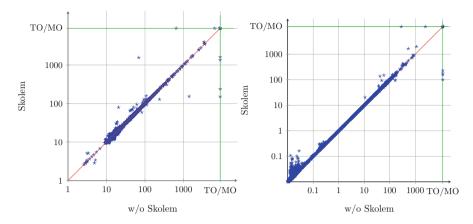

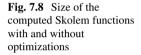

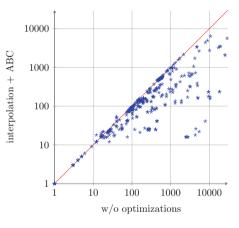

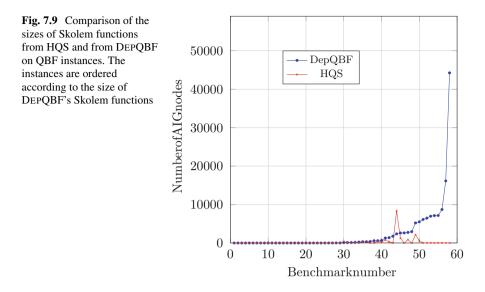

- The system exploits parallelism by executing iterations in parallel. To ensure serializability of iterations, programmers must use a library of built-in concurrent data structures for graphs, work-lists, etc. These library routines expose a standard API to programmers, and they implement lightweight synchronization to ensure serializability of iterations, as explained below.