# Pieter Harpe · Kofi A. A. Makinwa Andrea Baschirotto *Editors*

# Hybrid ADCs, Smart Sensors for the IoT, and Sub-1V & Advanced Node Analog Circuit Design 2017

Hybrid ADCs, Smart Sensors for the IoT, and Sub-1V & Advanced Node Analog Circuit Design Pieter Harpe • Kofi A. A. Makinwa Andrea Baschirotto Editors

# Hybrid ADCs, Smart Sensors for the IoT, and Sub-1V & Advanced Node Analog Circuit Design

Advances in Analog Circuit Design 2017

*Editors* Pieter Harpe Department of Electrical Engineering Eindhoven University of Technology Eindhoven, Noord-Brabant, The Netherlands

Andrea Baschirotto Department of Physics G. Occhialini University of Milan Milano, Italy Kofi A. A. Makinwa Department of Microelectronics Delft University of Technology Delft, Zuid-Holland, The Netherlands

ISBN 978-3-319-61284-3 DOI 10.1007/978-3-319-61285-0

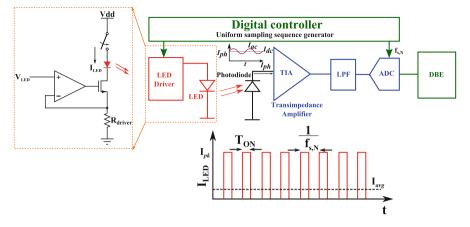

#### ISBN 978-3-319-61285-0 (eBook)

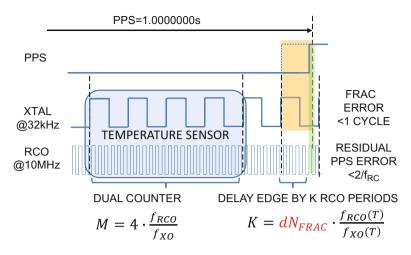

Library of Congress Control Number: 2017949890

© Springer International Publishing AG 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

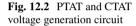

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## Preface

This book is part of the Analog Circuit Design series and contains contributions of all 18 speakers of the 26th workshop on Advances in Analog Circuit Design (AACD). The local organizers were Kathleen Philips, Yao-Hong Liu, and Steffie van de Vorstenbosch from Holst Centre/imec, Eindhoven, the Netherlands. The sponsors of the workshop this year were as follows: NXP Semiconductors (platinum sponsor), Dialog Semiconductor (gold sponsor), and silver sponsors Analog Devices, AnSem, Catena, Huawei, ICsense, ItoM, and Philips. The workshop was held in Eindhoven, the Netherlands, from March 28 to 30, 2017.

The book comprises three parts, covering advanced analog and mixed-signal circuit design topics that are considered highly important by the circuit design community:

- Hybrid data converters

- Smart sensors for the IoT

- Sub-1V and advanced-node analog circuit design

Each part is set up with six papers from experts in the field.

The aim of the AACD workshop is to bring together a group of expert designers to discuss new developments and future options. Each workshop is followed by the publication of a book by Springer in their successful series of Analog Circuit Design. This book is the 26th in this series. The book series can be seen as a reference for all people involved in analog and mixed-signal design. The full list of the previous books and topics in the series is given next.

We are confident that this book, like its predecessors, proves to be a valuable contribution to our analog and mixed-signal circuit design community.

Milano, Italy Delft, The Netherlands Eindhoven, The Netherlands Andrea Baschirotto Kofi A. A. Makinwa Pieter Harpe

# The Topics Covered Before in This Series

| 2016 | Villach (Austria)            | Continuous-time $\Sigma\Delta$ Modulators for Transceivers |

|------|------------------------------|------------------------------------------------------------|

|      |                              | Automotive Electronics                                     |

|      |                              | Power Management                                           |

| 2015 | Neuchâtel (Switzerland)      | Efficient Sensor Interfaces                                |

|      |                              | Advanced Amplifiers                                        |

|      |                              | Low Power RF Systems                                       |

| 2014 | Lisbon (Portugal)            | High-Performance AD and DA Converters                      |

|      |                              | IC Design in Scaled Technologies                           |

|      |                              | Time-Domain Signal Processing                              |

| 2013 | Grenoble (France)            | Frequency References                                       |

|      |                              | Power Management for SoC                                   |

|      |                              | Smart Wireless Interfaces                                  |

| 2012 | Valkenburg (The Netherlands) | Nyquist A/D Converters                                     |

|      |                              | Capacitive Sensor Interfaces                               |

|      |                              | Beyond Analog Circuit Design                               |

| 2011 | Leuven (Belgium)             | Low-Voltage Low-Power Data Converters                      |

|      |                              | Short-Range Wireless Front-Ends                            |

|      |                              | Power Management and DC-DC                                 |

| 2010 | Graz (Austria)               | Robust Design                                              |

|      |                              | Sigma Delta Converters                                     |

|      |                              | RFID                                                       |

| 2009 | Lund (Sweden)                | Smart Data Converters                                      |

|      |                              | Filters on Chip                                            |

|      |                              | Multimode Transmitters                                     |

| 2008 | Pavia (Italy)                | High-Speed Clock and Data Recovery                         |

|      |                              | High-Performance Amplifiers                                |

|      |                              | Power Management                                           |

| 2007 | Oostende (Belgium)           | Sensors, Actuators and Power Drivers for the               |

|      |                              | Automotive and Industrial Environment                      |

|      |                              | Integrated PAs from Wireline to RF                         |

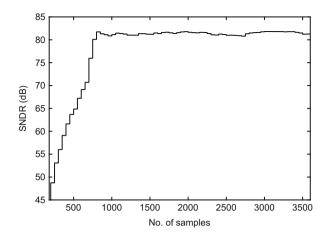

|      |                              | Very High Frequency Front Ends                             |

(continued)

| 2007 | 36 1 .                            |                                                                       |

|------|-----------------------------------|-----------------------------------------------------------------------|

| 2006 | Maastricht<br>(The Netherlands)   | High-Speed AD Converters                                              |

|      | (The rectionands)                 | Automotive Electronics: EMC issues                                    |

|      | T 1 (T 1 1)                       | Ultra Low Power Wireless                                              |

| 2005 | Limerick (Ireland)                | RF Circuits: Wide Band, Front-Ends, DACs                              |

|      |                                   | Design Methodology and Verification of RF and Mixed-Signal<br>Systems |

|      |                                   | Low Power and Low Voltage                                             |

| 2004 | Montreux (Swiss)                  | Sensor and Actuator Interface Electronics                             |

|      |                                   | Integrated High-Voltage Electronics and Power Management              |

|      |                                   | Low-Power and High-Resolution ADCs                                    |

| 2003 | Graz (Austria)                    | Fractional-N Synthesizers                                             |

|      |                                   | Design for Robustness                                                 |

|      |                                   | Line and Bus Drivers                                                  |

| 2002 | Spa (Belgium)                     | Structured Mixed-Mode Design                                          |

|      |                                   | Multi-bit Sigma-Delta Converters                                      |

|      |                                   | Short-Range RF Circuits                                               |

| 2001 | Noordwijk                         | Scalable Analog Circuits                                              |

|      | (The Netherlands)                 | High-Speed D/A Converters                                             |

|      |                                   | RF Power Amplifiers                                                   |

| 2000 | Munich (Germany)                  | High-Speed A/D Converters                                             |

|      |                                   | Mixed-Signal Design                                                   |

|      |                                   | PLLs and Synthesizers                                                 |

| 1999 | Nice (France)                     | XDSL and Other Communication Systems                                  |

|      |                                   | RF-MOST Models and Behavioural Modelling                              |

|      |                                   | Integrated Filters and Oscillators                                    |

| 1998 | Copenhagen<br>(Denmark)           | 1-Volt Electronics                                                    |

|      |                                   | Mixed-Mode Systems                                                    |

|      |                                   | LNAs and RF Power Amps for Telecom                                    |

| 1997 | Como (Italy)                      | RF A/D Converters                                                     |

|      |                                   | Sensor and Actuator Interfaces                                        |

|      |                                   | Low-Noise Oscillators, PLLs and Synthesizers                          |

| 1996 | Lausanne (Swiss)                  | RF CMOS Circuit Design                                                |

|      |                                   | Bandpass Sigma Delta and Other Data Converters                        |

|      |                                   | Translinear Circuits                                                  |

| 1995 | Villach (Austria)                 | Low-Noise/Power/Voltage                                               |

|      |                                   | Mixed-Mode with CAD Tools                                             |

|      |                                   | Voltage, Current and Time References                                  |

| 1994 | Eindhoven<br>(The Netherlands)    | Low-Power Low-Voltage                                                 |

|      |                                   | Integrated Filters                                                    |

|      |                                   | Smart Power                                                           |

| 1993 | Leuven (Belgium)                  | Mixed-Mode A/D Design                                                 |

|      |                                   | Sensor Interfaces                                                     |

|      |                                   | Communication Circuits                                                |

|      |                                   | U COMMUNICATION CITCHIIS                                              |

| 1992 | Scheveningen                      |                                                                       |

| 1992 | Scheveningen<br>(The Netherlands) | OpAmps       ADC                                                      |

# Contents

#### Part I Hybrid Data Converters

| 1   | Hybrid Data Converters<br>Kostas Doris                                                                                                                                                          | 3   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2   | Hybrid and Segmented ADC Techniques to Optimize PowerEfficiency and Area: The Case of a 0.076 mm² 600 MS/s 12bSAR-ΔΣ ADCAlessandro Venca, Nicola Ghittori, Alessandro Bosi,<br>and Claudio Nani | 17  |

| 3   | Interleaved Pipelined SAR ADCs: Combined Power for<br>Efficient Accurate High-Speed Conversion<br>Ewout Martens                                                                                 | 39  |

| 4   | <b>Hybrid VCO Based 0-1 MASH and Hybrid <math>\Delta \Sigma</math> SAR</b><br>Arindam Sanyal, Wenjuan Guo, and Nan Sun                                                                          | 61  |

| 5   | A Hybrid Architecture for a Reconfigurable SAR ADC<br>Yun-Shiang Shu, Liang-Ting Kuo, and Tien-Yu Lo                                                                                            | 79  |

| 6   | A Hybrid ADC for High Resolution: The Zoom ADC<br>Burak Gönen, Fabio Sebastiano, Robert van Veldhoven,<br>and Kofi A. A. Makinwa                                                                | 99  |

| Par | rt II Smart Sensors for the IoT                                                                                                                                                                 |     |

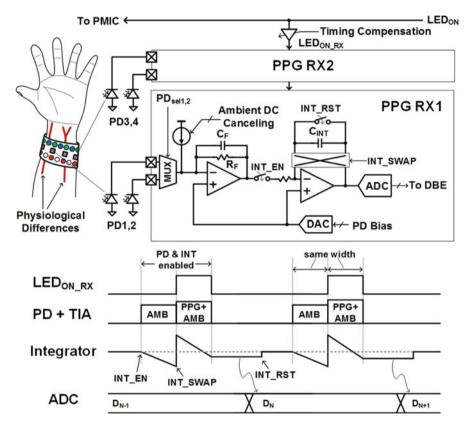

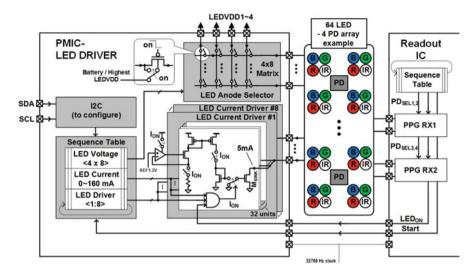

| 7   | Advances in Biomedical Sensor Systems for Wearable Health<br>Nick Van Helleputte, Jiawei Xu, Hyunsoo Ha,<br>Roland Van Wegberg, Shuang Song, Stefano Stanzione,                                 | 121 |

Samira Zaliasl, Richard van den Hoven, Wenting Qiu, Haoming Xin, Chris Van Hoof, and Mario Konijnenburg

ix

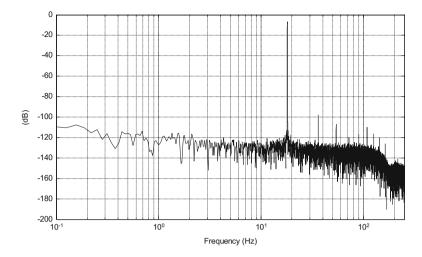

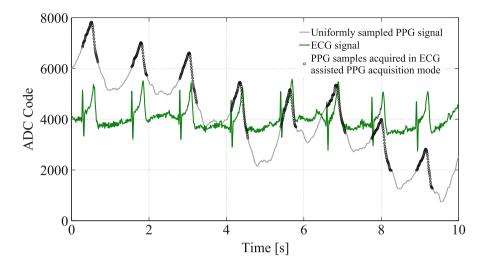

| 8   | An Ultra-low Power, Robust Photoplethysmographic Readout<br>Exploiting Compressive Sampling, Artifact Reduction and<br>Sensor Fusion                                                                                                                              | 145        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | Venkata Rajesh Pamula, Chris Van Hoof, and Marian Verhelst                                                                                                                                                                                                        |            |

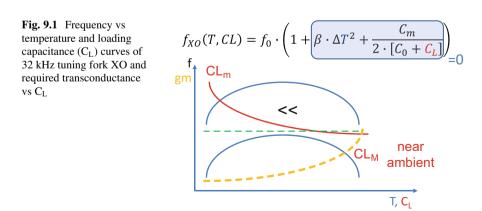

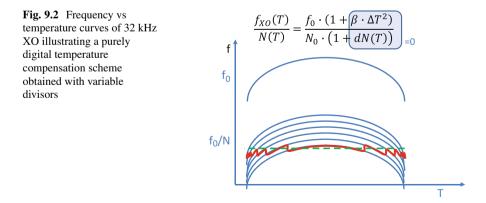

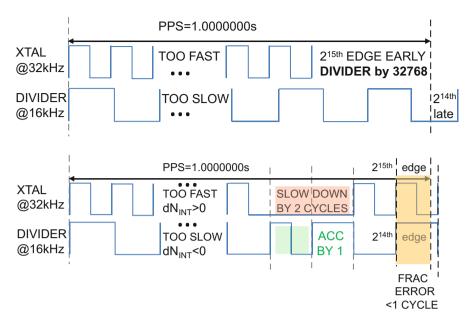

| 9   | A 32 kHz DTCXO RTC Module with an Overall<br>Accuracy of ±1 ppm and an All-Digital 0.1 ppm<br>Compensation-Resolution Scheme<br>David Ruffieux, Nicola Scolari, Frédéric Giroud, Franz Pengg,<br>Daniel Severac, Thanh Le, Silvio Dalla Piazza, and Olivier Aubry | 165        |

| 10  | Energy-Efficient High-Resolution Resistor-Based Temperature<br>Sensors<br>Sining Pan and Kofi A. A. Makinwa                                                                                                                                                       | 183        |

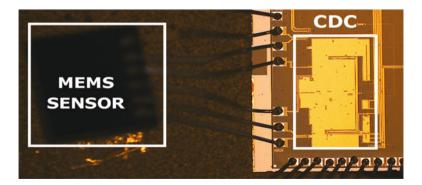

| 11  | A High-Resolution Self-Oscillating Integrating Dual-Slope<br>CDC for MEMS Sensors<br>J. P. Sanjurjo, Enrique Prefasi, C. Buffa, C. Rogi, and R. Gaggl                                                                                                             | 201        |

| 12  | Ultra-low Power Charge-Pump-Based Bandgap References<br>Shikhar Tewari and Aatmesh Shrivastava                                                                                                                                                                    | 219        |

| Par | t III Sub-1V and Advanced-Node Analog Circuit Design                                                                                                                                                                                                              |            |

|     |                                                                                                                                                                                                                                                                   |            |

| 13  | FDSOI Technology, Advantages for Analog/RF<br>and Mixed-Signal Designs<br>Andreia Cathelin                                                                                                                                                                        | 239        |

| 13  | and Mixed-Signal Designs                                                                                                                                                                                                                                          | 239<br>259 |

|     | <ul> <li>and Mixed-Signal Designs</li></ul>                                                                                                                                                                                                                       |            |

| 17 | Time-Based Biomedical Readout in Ultra-Low-Voltage,        |     |

|----|------------------------------------------------------------|-----|

|    | Small-Scale CMOS Technology                                | 311 |

|    | Rachit Mohan, Samira Zaliasl, Chris Van Hoof, and Nick Van |     |

|    | Helleputte                                                 |     |

| 18 | A 4.4 mW-TX, 3.6 mW-RX Fully Integrated Bluetooth Low      |     |

|    | Energy Transceiver for IoT Applications                    | 335 |

|    | Masoud Babaie, Sandro Binsfeld Ferreira, Feng-Wei Kuo,     |     |

|    | and Robert Bogdan Staszewski                               |     |

|    | 6                                                          |     |

# Part I Hybrid Data Converters

The first part of this book is dedicated to recent developments in the field of hybrid data converters. While hybrid architectures, algorithms and circuits have been used for a long time, hybrid converters are much more in the picture recently, thanks to their ability to deal with technology limitations and achieve better performance in terms of speed, accuracy, efficiency and chip area. The first chapter in this part of the book gives an overview of the scope of 'hybrid', while the remaining five chapters introduce hybrid converter examples aiming for different performance directions.

The first chapter, by Kostas Doris, discusses the different dimensions of hybrid converter concepts and shows a classification of these. Combined with concrete examples, it exemplifies the broad nature of hybrid concepts in data converters.

In the second chapter, by Alessandro Venca, Nicola Ghittori, Alessandro Bosi and Claudio Nani, a time-interleaved SAR- $\Delta\Sigma$  ADC is proposed. Moreover, the DAC implementation also uses a hybrid charge redistribution/charge sharing topology. It is shown that this enables excellent performance and also reduces chip area of the integrated system.

The third chapter, by Ewout Martens, discusses several time-interleaved pipelined SAR ADCs, aiming to move the speed-precision-efficiency envelope. The various circuit implementations being used give insight into their respective limitations and advantages.

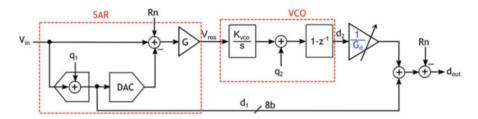

The fourth chapter, by Arindam Sanyal, Wenjuan Guo and Nan Sun, combines a SAR ADC with a  $\Delta\Sigma$  modulator and a VCO-based converter, resulting in noise shaping and higher precision than achievable by a typical SAR ADC.

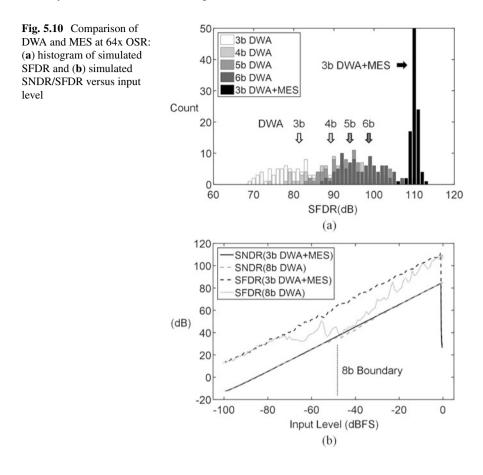

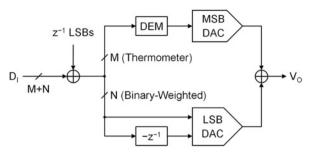

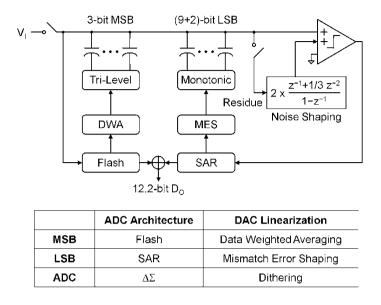

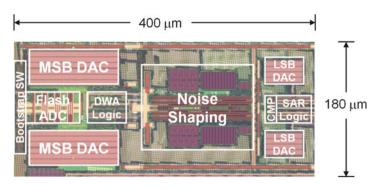

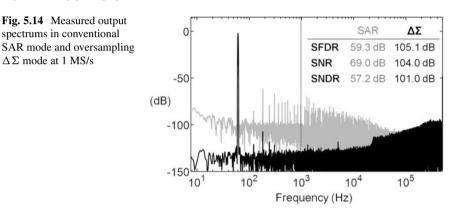

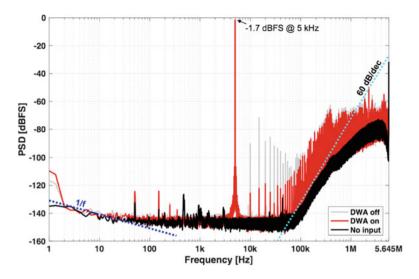

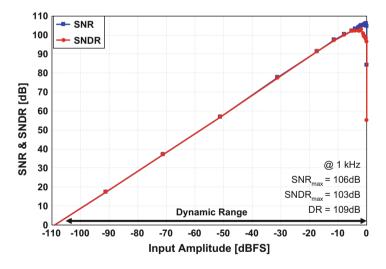

In the fifth chapter, Yun-Shiang Shu, Liang-Ting Kuo and Tien-Yu Lo describe a hybrid architecture for a reconfigurable SAR ADC, including SAR,  $\Delta\Sigma$  and subranging and flash converter techniques. Noise and mismatch shaping techniques enable a state-of-the-art efficiency, up to 101dB SNDR and flexibility in speed and precision.

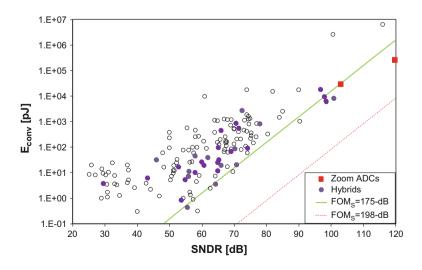

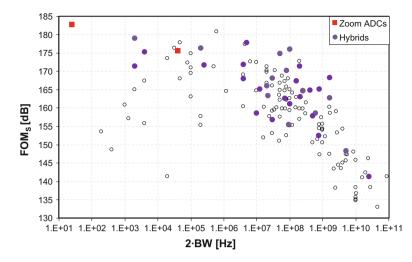

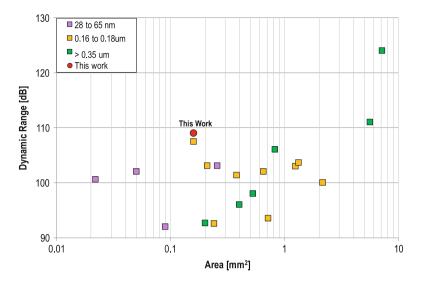

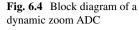

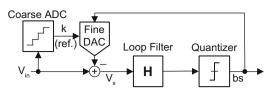

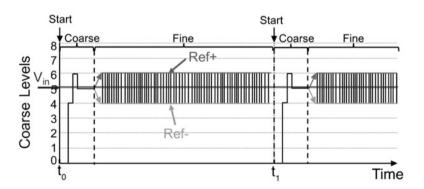

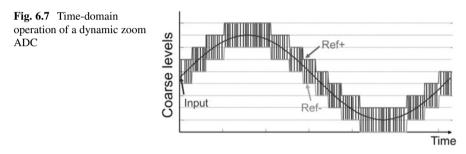

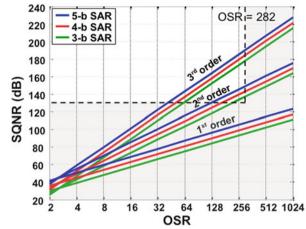

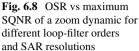

The sixth chapter, by Burak Gönen, Fabio Sebastiano, Robert van Veldhoven, and Kofi Makinwa, presents a dynamic zoom ADC, which is a combination of a SAR and a  $\Delta\Sigma$  ADC. This enables very high resolution while maintaining excellent efficiency in energy and area.

## Chapter 1 Hybrid Data Converters

**Kostas Doris**

#### 1.1 Introduction

Novel circuit and architectural data conversion amalgams employing combinations of conventional converter architectures that exploit the advantages of nm CMOS technologies and mitigate their shortcomings continue to push the envelope in performance and power efficiency across all speed resolution domains.

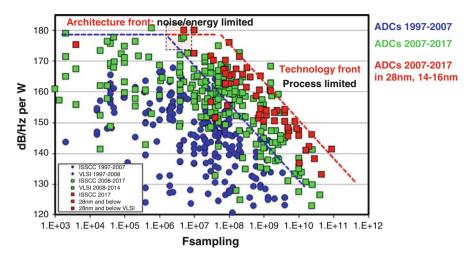

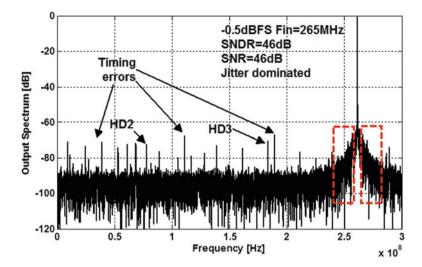

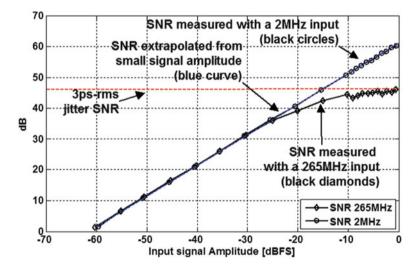

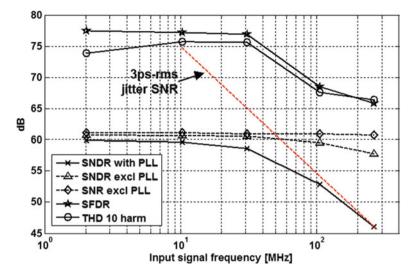

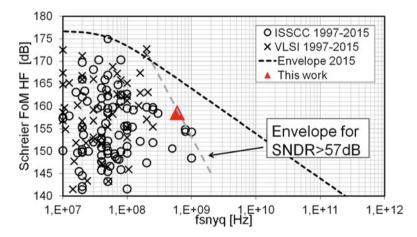

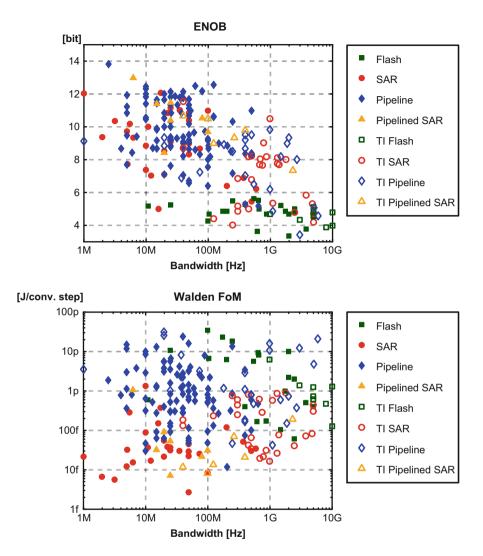

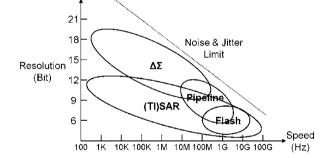

In [1] the author highlighted the transformation of conventional converters to hybrids in its beginning phase. Today, nearly a decade later, with the digital assisted hype beyond it's peak point, hybrid converters are in full deployment and have even claimed dedicated sessions in recent year's ISSCC. Figure 1.1 shows this evolution of CMOS data converters in the last two decades using the Schreier's Figure of Merit. It is apparent that the performance advances are heavily correlated with advanced CMOS nodes. These advances however do not come from the mere adoption of technologies with smaller nodes but by the continuous advance in understanding how to use them optimally encapsulated in today's hybrid data converter architectures.

The objective of this introductory paper is to illustrate the broad and multidimensional nature of hybrid converters, which goes beyond the "combination of known architectures" as it is often referred. It will be argued that hybrid data converters reflect the continuation of a matching driven design policy [3]. According to this the analog to digital conversion from the wired or wireless input interface (e.g. antenna) to digital bits is conditioned optimally to the properties of CMOS technology through combinations of techniques across multiple signal domains

K. Doris  $(\boxtimes)$

NXP Semiconductors, Eindhoven, The Netherlands e-mail: kostas.doris@nxp.com

<sup>©</sup> Springer International Publishing AG 2018

P. Harpe et al. (eds.), Hybrid ADCs, Smart Sensors for the IoT, and Sub-IV

<sup>&</sup>amp; Advanced Node Analog Circuit Design, DOI 10.1007/978-3-319-61285-0\_1

Fig. 1.1 Schreier FoM with data from [2]

and hardware abstraction layers using modulation, redundancy, scheduling, onchip information and other concepts. Dependent on the speed resolution domain, hybrid architectures take a different shape that matches to thermal noise or process technology limitations dominating in the corresponding domain.

#### **1.2** The Role of the Analog to Digital Conversion Interface

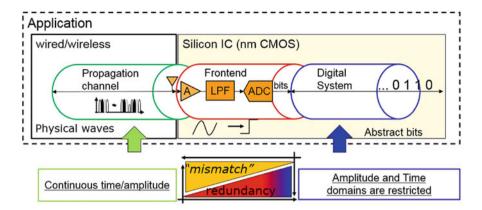

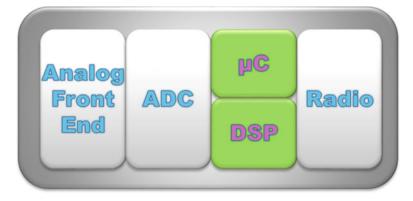

Figure 1.2 shows the receiver part of a communication system represented with a direct conversion architecture without loss of generality.

Physical signals serving as carrier waves propagate information across the propagation medium (the channel) prior to being received at the antenna interface. These information carrier signals are analog and are optimally matched to the physics of the propagation medium for the purpose of carrying information. They are minimally restricted in the amplitude and time domains, which means they have limited redundancy and as a consequence they are sensitive to noise, interference, distortions, etc. Abstract bits on the right side of the figure are maximally restricted in amplitude and time domains. This restriction introduces redundancy which translates to robustness against CMOS technology. In this way they become optimally matched to CMOS technology for the purpose of computation of information.

This leaves us with two signal types and media optimally matched to each other for purposes of propagation and computation of information and one analog mixedsignal domain in the middle, where signals are not optimally matched to its CMOS implementation carrier.

Fig. 1.2 Data converter interface as a matching network to the technology

The conversion of information from one medium to the other is done at the analog to digital interface spanning all the way from the antenna to the bit slicer, the exact point at which conversion from analog to digital fully takes place. We are neglecting for simplicity for now the conversion from the electromagnetic domain to the electrical at the antenna without loss of generality. Please note the distinction between the overall conversion from analog to digital and the data converter block, which is a boundary designers put in practice.

The primary role of this interface is to translate information from one matched domain to the other with minimum loss, from analog (no restrictions in time and amplitude) to digital (amplitude restricted to 0 and 1, sequences replacing time). As the analog signal reaches the boundary of the antenna interface it encounters a large discontinuity. Inversely, as signals go out of the bit slicer, they reach the level of best matching to CMOS technology. By restricting the signals in a stepwise manner across signal domains (continuous/discrete amplitude and time), we introduce redundancy in the signal and enable abstraction from hardware between device, circuit, architecture, algorithm and signal layers.

Abstraction and redundancy in the (mixed) signal allow a gradual functional decoupling across the signal chain. This is a typical property of digital systems but not of analog, which opens up the door for a plethora of transformations (modulation, scheduling, hardware redundancy, averaging, etc.) The hybrid combination of these techniques across the hardware abstraction hierarchy is what provides the optimal match of the conversion function (not just the converter block) to the evolving CMOS technology. This hybrid process goes stepwise along the signal path. It starts at the front-end circuits (e.g. LNA and PA) dealing with the largest discontinuity where especially at higher frequencies (e.g. mmwave) "matching" to technology means physical design approaches (e.g. resonating all nodes to overcome signal losses) and reaches full physical abstraction at the digital calibrations of the ADC.

As it can be seen, the conversion from analog to digital is not restricted to the data converter block and it is hybrid by definition, as already indicated by its dual name.

#### **1.3** Abstraction Hierarchy and Concepts in Hybrid Converters

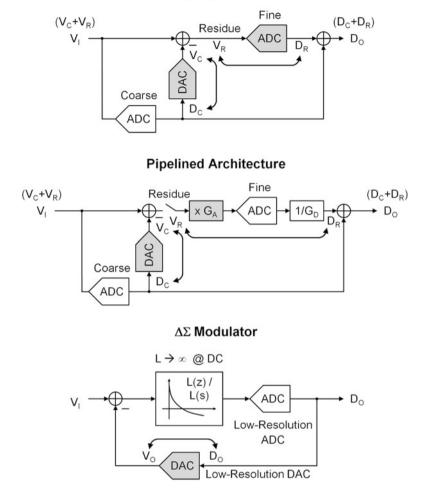

It is a common assumption in literature that a hybrid converter uses a combination of "single" conventional architectures such as pipelined ADCs, SAR, flash and deltasigma in the same converter, each in the amplitude and time range where it exhibits maximum power efficiency [4].

In this context, pipelining of two single bit per cycle SARs [5, 6] is considered as a hybrid converter, and a conventional pipelined ADC using an MDAC combined with a parallel flash sub-ADC stage is not. However, since pipelining deals with the scheduling of the bit operations in time and not with the amplitude domain conversion algorithm, the opposite is actually true. A pipelined single-bit SAR ADC is not a hybrid because it uses only bit serial conversion, and the conventional pipeline ADC is a hybrid because it uses a bit-parallel (flash) algorithm embedded hierarchically into a bit serial conversion. The SAR is also hybrid when it employs multi bits per cycle.

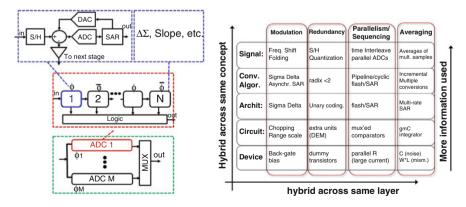

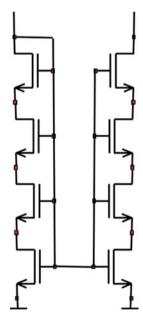

This example illustrates that conventional architectures do not necessarily offer an orthogonal space with which to define what single and what hybrid is and this may lead to misconceptions. Instead, we can use a classification such as the one shown in Fig. 1.3 to analyse hybrid converters in more detail. At the vertical axis of the table at the right side of the figure, we can see the physical abstraction from hardware, whereas at the horizontal axis we list representative concepts.

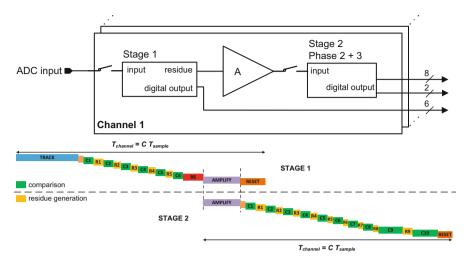

Notice that a concept often requires (or enables) the use of another concept across this two-dimensional space. For example, in the hybrid ADC architecture shown on the left side of the figure, the sampling operation introduces redundancy in the time domain. Within one clock cycle, the time dimension is redundant. This allows time multiplexing of subsequent iterative conversion operations (sub-ADC, SAR, DAC) based on bit-parallel or serial method (e.g. flash/SAR for the ADC)

Fig. 1.3 Abstraction and concepts in analog/digital conversion (non exhaustive list of examples)

that generates an approximating quantized signal iteratively. On a higher abstraction layer, the bit conversion is parallelized in time domain through pipelining, while for the remaining bits, redundancy in time through the hold operation allows us to alter the conversion algorithm to another conversion algorithm, e.g. digital slope or even an incremental. On a higher level, parallelism can be added on sample to sample with interleaving, and even further hierarchy could be added with power splitters to isolate the ADCs electrically from the common input.

In the following, we can assume that a hybrid converter employs various independent concepts across the same horizontal or vertical layer. Some examples from literature are listed next:

- Multiple conversion algorithms in ADCs:

- Multi-bit successive approximation [7, 8] (parallel-bit combined with serialbit).

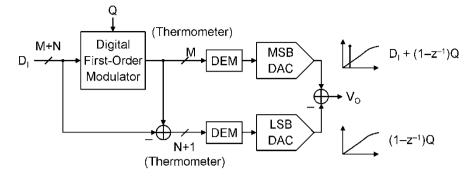

- Successive approximation can be combined with slope [9, 10] and incremental converters [4] and even with oversampled converters and DEM [11–15].

- Redundancy across hardware abstraction layers in ADCs

- Multiple ADCs for redundancy at application level or split ADC architectures used as means to deal with radiation tolerances [16].

- Additional ADC units [17, 18]. This form of redundancy combined with multiplexing and abstraction enables frequency shifting techniques such as DEM and chopping that deal with offset and other interleave artefacts. Here, separation of the conversion function from sampling decouples the conversion function from the specific hardware making it such that the hardware can be interchanged freely. Redundancy in the number of ADCs enables the possibility to perform frequency translation fixed (or quasi-static) offset or gain and timing error signals to broadband ones resembling "noise". Similarly, by alternating the signal path, voltage offsets can be translated to higher frequencies (chopping). This makes them signal tones, which can then filtered. Inverse transformation recovers the signal back.

- Reduced radix or over-ranging techniques increase the amplitude search range against the allowable signal range (see [5, 19] for digital and [20–23] for analog implementations) to increase tolerance to errors from offset, noise and incomplete settling of DAC MSB transitions. For as long there is sufficient range, remaining errors in conversion cycles do not count. For settling errors, this allows trading exponential settling time with linear conversion cycle time with profound benefits at high resolutions where long settling times are required.

- Asynchronous conversion in SAR [24–26] to maximize serial conversion efficiency embedded in fully synchronous overall conversion.

- Parallel processing with hardware hierarchy to address sampling rate limitations at GHz rates

- Bit pipelining in SAR [5, 27] or pipelined ADCs [28]. Not only this offers the benefit of parallelism for speed but it also enables range scaling transformation in the amplitude domain with interstage amplification, which reduces the impact of noise in LSB conversions as well.

- Sample to sample parallelism (interleaving).

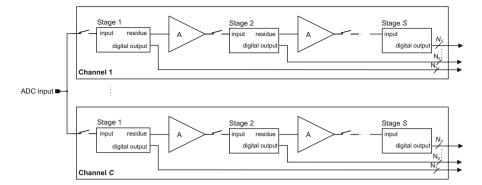

- Hierarchical approaches in sampling, interleaving, demultiplexing and pipelining [18, 23, 29–35].

- Bit multiplexing with separate comparators [36, 37] or interleaved comparators [32].

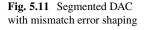

- DACs with current steering flash and delta-sigma for MSB and LSBs [38], hybrid encoding with binary thermometer segmentation and combinations of flash and time interleave [39] and even functional co-integration across the receive/transmit path, e.g. mixing DACs [40].

- · Hybrid circuit block implementations

- DACs based on capacitors [24, 41, 42], resistors[5, 8, 20] or current [23, 43], current steering combined with resistors (e.g. R–2R) [44].

- Class AB amplifiers reconfigured in and out of positive feedback [45] during operation, cascaded class A [11, 23] or class AB dynamic amplifications [27, 28, 46], charge re-use [25, 46], etc.

- Charge sharing combined with charge redistribution DACs [4].

- LDO's based on series-parallel concepts [47].

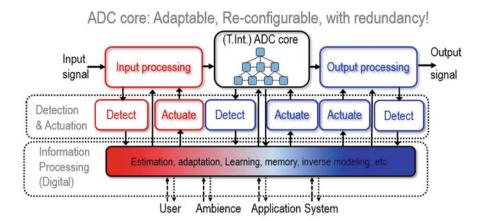

#### 1.4 Reconfiguration and On-Chip Intelligence

Another key ingredient of hybrid converters is reconfiguration triggered by state or events. As the conversion process evolves from bit to bit, the data converter transforms itself through hardware reconfiguration from one to another circuit or architecture that is more optimal for the subsequent bit conversions.

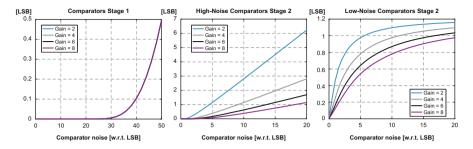

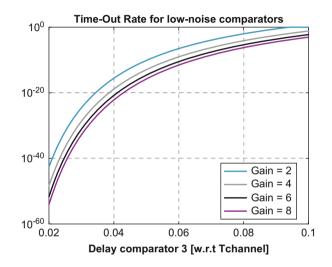

Typical examples at circuit block level include comparator noise programming [25, 48, 49] in order to reduce power dissipation or reduce noise. Architecture reconfiguration has been reported in [4] changing from a 9b SAR to a 3b incremental delta-sigma to improve power efficiency and noise performance achieving 12b ADC conversion. In [48, 50] the ADCs were made reconfigurable to achieve multiple resolution levels with the same converter (here, not during conversion).

On-chip digital assistance and more generally the handling of information with on-chip intelligence are also hybrid in nature. A design policy exploiting digital assistance to address non-idealities of the converter in favour of faster operation has been the intense focus of research in multiple data converter papers the last years.

The hybrid nature of information is exploited in data converters. This can be depicted conceptually in Fig. 1.4. Information can be present in the input or output signal or in sub-signals. It is used a priori the design phase (e.g. technology spread properties, reliability and temperature behaviour) or obtained a posteriori with on-

Fig. 1.4 Hybrid on-chip intelligence in data converters

chip detection (e.g. on-chip monitors) and covers user, application, ambience and technology domains. It is exploited in digital or analog form, continuous time or discrete. Converters today use a multitude of information types and apply hybrid calibration techniques to deal with errors such as time interleave artefacts, transfer function errors, programming the chip for given temperature profiles, etc., for example, time interleave error detection in digital domain and correction in the analog domain.

Such hybrid converters need to be made adaptive (reconfigurable architecture, adaptable parameters, test signals, etc.) to exploit the combination of information types available. They also need hardware redundancy. For example in a DAC, redundancy can be put in the switched hardware units [51, 52], while reconfiguration is done at the decoder. The dual ADC reported in [53] analyses the input data and chooses during operation amongst two ADCs on sample per sample basis reconfiguring the gain applied to the signal to reduce the impact of clipping in multi-carrier signals.

#### **1.5 Functional and Technology Co-integration in Hybrid** Converters

So far we have been talking mainly about hybrid data converters looking in the converter block. Another hybrid dimensions occurs along the signal path in a receiver and transmitter. Most notable examples here include the functional co-integration between the upconverter mixer and the DAC [52] for wireless systems, the power amplifier and DAC in wireline systems driving directly 50  $\Omega$  cable load, the combination of equalization and conversion in wireline systems, etc.

In the same line of thinking, references [18, 23, 43] integrate the buffer driving the large load of the ADC into the SAR loop eliminating its nonlinear behaviour. When combined with demultiplexing, this further enables to reduce the impact of wire interconnect load of the interleave array [23].

Finally, the combination of different technologies can lead also to hybrid data converters, e.g. optical and electronic ADCs.

#### **1.6 Hybrid Analog to Digital Converters Across Speed** and Resolution

The type of hybrid techniques associates strongly with the problem that needs to be addressed at the corresponding resolution speed regime.

At very high sampling rates, combinations of scheduling operations with time interleave error correction techniques dominate hybrid ADCs. Achieving tens of GS/s sampling rate and 10–20 GHz input bandwidth with low clock jitter noise overshadows the low-resolution noise requirements of the unit converters. The main issue is how to deal with the large interconnect capacitance stemming from the large converter interleaved array that is required to get to the required sampling rate (mainly clock and signal interconnect, not sampling capacitors). A large array enables high sampling rate, but limits input bandwidth and clocking performance and translates to high-power dissipation. Bandwidth also brings in additional constrains in the packaging due to input signal losses.

Hybrid concepts help to reduce the size of the interleave array, to divide and reduce the interconnect capacitance that is present at the input or at clock nodes. We observe in both signal and clocking paths hierarchical interleaving forms, multiplexing, resampling, power splitting, etc. [18, 23, 30–33]. Typically flash/SAR ADCs are preferred for either their speed or small area that both help to scale down the array size and complexity. This is achieved thanks to hybrid calibration techniques correcting time and amplitude dimension interleave errors with analog and digital correction techniques. The units need to be as fast as possible, and multiplexing is applied even at the comparator level, e.g. separate comparators [36] or interleaving [32]. Frequency domain multiplexing was also reported [54].

High-resolution levels, e.g. 10–16 b with sampling rates between 1 and 10 GS/s rates, require dealing with thermal noise, matching, large sampling and interconnect capacitance. Here there is a lot of emphasis for hybrid concepts that apply at the converter unit and associated use of on-chip information to calibrate it. Time interleaving is present but reduces drastically as the resolution increases: noise imposes restrictions due to the large sampling capacitors and clock buffers loading the input and clock nodes.

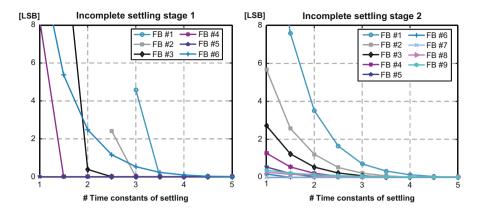

We observe hierarchical combinations of multi-bit MDAC sampling front ends with SAR sub-ADCs [55] but also pipelined multi-bit SARs [37] exploiting dynamic amplifiers and SARs with separate comparators per bit to become the alternatives of conventional pipelined ADCs using flash sub-ADCs [56]. Digital and analog corrections are implemented for nearly everything that can be calibrated in the converter for both pipeline and interleave artefacts such as comparator offsets, gains, signal transfer functions, bandwidth mismatches, interleave errors, track hold errors, clock injections, using DEM, LMS algorithms, dithering, etc. [57].

At speeds below 1 GHz [4, 28] with high-resolution levels, we see combinations of various concepts diverging from the conventional pipelined ADC. The main idea is partitioning the conversion cycle in MSB and LSB parts. A suitable architecture can be chosen for the LSB part that determines noise performance and power dissipation, and a faster architecture can be used to remove speed limitations in the MSB part. Interleaving is a degree of freedom coming on top. The work of [4] introduces an incremental delta-sigma modulator with reconfigurability, whereas [28] uses pipeline of SARs with interstage amplification based on dynamic amplifiers. In [10] an asynchronous digital slope converter is combined with a SAR exploiting also continuous time comparator techniques. The 14b ADC in [58] utilized multi-bit SARs with time interleaving of the single comparator being shared between all DACs. Analog to Digital converters with even lower speed but high resolutions follow and extend the same trend. A recent example can be seen in the audio domain sub-ranging delta-sigma ADC presented in [59].

These examples illustrated how multiple principles and techniques can be used to exploit most optimally CMOS technology to deal with fundamental limitations such as noise. However, the solution space is not restricted to these techniques only. As we move to even higher levels of abstraction, more degrees of freedom will become available. At the transmitter side, one can use spatial signal processing techniques at analog and digital domains. At the circuit layer, for example, power combining allows generating higher signal power compared to what a single amplifier unit can deliver. At the architectural level, spatial processing can be implemented with analog and digital beam forming either with phase rotation or time delays in analog and digital domains, respectively. The trend will continue at application level, for example in the future autonomous driving vehicles multiple sensors with different principles will be combined into one sensor architecture (ultra sound, radar, lidar, camera, etc.) to enable the car process a broad spectrum of signals from low frequencies up to optical wavelengths with high accuracy and reliability.

#### 1.7 Conclusions

To appreciate properly the nature of hybrid converters, one needs to see them from multiple angles and abstraction layers and appreciate the whole conversion from antenna to bits.

In the past, hybrid converters were mostly all about the circuit layer of abstraction. Nowadays, hybrid data converters expand across all abstraction layers, especially with regard to scheduling, algorithmic conversions, handling of information for corrections and the transceiver signal path. The hybrid analog to digital or digital to analog converter has a dual name to begin, analog and digital. It operates in multiple signal amplitude and time domains and utilizes combinations of conversion techniques and concepts such as redundancy, modulation, parallelism, sequencing and sub-ranging across hardware abstraction hierarchy. Through reconfigurable and adaptable hardware, it exploits multiple forms of information to deal with nm CMOS imperfections. The ideal hybrid converter breaks completely the boundaries of conventional converter blocks from antenna to bits and becomes a converter truly *matched* to the application and the properties of silicon technology and propagation channel.

#### References

- 1. Doris, K.: Time interleaved analog-to-digital converters: an algorithmic melting pot. In: 2009 IEEE International Solid-State Circuits Conference (ISSCC), Jan 2009

- 2. Murmann, B.: ADC performance survey. http://www.stanford.edu/~murmann/adcsurvey.html

- 3. van Roermund, A.: Shifting the frontiers of analog and mixed-signal electronics. Advances in Electronics, vol. 2014 (2014)

- 4. Venca, A., et al.: A 0.076 mm<sup>2</sup> 12 b 26.5 mW 600 MS/s 4-way interleaved sub-ranging SAR- $\Delta\Sigma$  ADC with on-chip buffer in 28 nm CMOS. IEEE J. Solid State Circuits **51**(12), 2951–2962 (2016)

- 5. Louwsma, S.M., et al.: A 1.35 GS/s, 10 b, 175 mW time-interleaved AD converter in 0.13  $\mu$ m CMOS. IEEE J. Solid State Circuits **43**(4), 778–786 (2008)

- Verbruggen, B., et al.: A 2.6 mW 6 bit 2.2 GS/s fully dynamic pipeline ADC in 40 nm digital CMOS. IEEE J. Solid State Circuits 45(45), 2080–2090 (2010)

- Cao, Z., et al.: A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 μm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 542–543 (2008)

- Wei, H., et al.: A 0.024 mm<sup>2</sup> 8b 400MS/s SAR ADC with 2b/Cycle and resistive DAC in 65 nm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 188–190 (2011)

- Ding, M., et al.: A 5bit 1GS/s 2.7 mW 0.05 mm<sup>2</sup> asynchronous digital slope ADC in 90 nm CMOS for IR UWB radio. In: 2012 IEEE Radio Frequency Integrated Circuits Symposium, pp. 487–490, June 2012

- Liu, C.C., et al.: A 12 bit 100 MS/s SAR-assisted digital-slope ADC. IEEE J. Solid State Circuits 51(12), 2941–2950 (2016)

- Harsener, M., et al.: A 14b 40 MS/s redundant SAR ADC with 480 MHz clock in 0.13 μm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 248–249 (2007)

- Hurrel, C., et al.: An 18b 12.5 MHz ADC with 93 dB SNR. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 378–379 (2010)

- Fredenburg, J., Flynn, M.: A 90MS/s 11MHz bandwidth 62dB SNDR noise-shaping SAR ADC. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 468–471 (2012)

- Liu, C.-C., et al.: A 0.46 mW 5MHz-BW 79.7 dB SNDR noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR Filter. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 466–467, Jan 2017

- Shu, Y.S., et al.: An oversampling SAR ADC with DAC mismatch error shaping achieving 105 dB SFDR and 101 dB SNDR over 1 kHz BW in 55 nm CMOS. IEEE J. Solid State Circuits 51(12), 2928–2940 (2016)

- 16. Xu, H., et al.: A 78.5dB-SNDR radiation- and metastability-tolerant two-step split SAR ADC operating up to 75MS/s with 24.9 mW power consumption in 65 nm CMOS. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 477–477, Jan 2017

- Ginsburg, B.P., Chandrakasan, A.P.: Highly interleaved 5-bit, 250-MSample/s, 1.2-mW ADC with redundant channels in 65-nm CMOS. IEEE J. Solid State Circuits 43(12), 2641–2650 (2008)

- Janssen, E., et al.: An 11b 3.6GS/s time-interleaved SAR ADC in 65 nm CMOS. In: 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, pp. 464–465, Feb 2013

- Kuttner, F.: A 1.2V 10b 20 MSample/s non-binary successive approximation ADC in 0.13 μm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 176–177 (2002)

- Boyacigiller, Z., et al.: An error-correcting 14b/20ps CMOS A/D converter. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 62–63 (1981)

- Draxelmayr, D.: A self calibration technique for redundant A/D converters providing 16b accuracy. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 204–205 (1988)

- 22. Liu, W., et al.: A 12b 22.5/45MS/s 3.0 mW 0.059 mm<sup>2</sup> CMOS SAR ADC achieving over 90 dB SFDR. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 380–381 (2010)

- Doris, K., et al.: A 480 mW 2.6GS/s 10b 65 nm time-interleaved ADC with 48.5 dB SNDR up to Nyquist. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 180–182 (2011)

- 24. Chen, S.-W.M., Brodersen, R.W.: A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-μm CMOS. IEEE J. Solid State Circuits **41**(12), 731–740 (2006)

- Craninckx, J., Van der Plas, G.: A 65J/conversion-step 0-to-50MS/s 0-to-0.7 mW 9b chargesharing SAR ADC in 90 nm digital CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 246–247 (2007)

- 26. Harpe, P., et al.: A 30fJ/Conversion-Step 8b 0-to-10MS/s asynchronous SAR ADC in 90 nm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 387–389 (2010)

- Verbruggen, B., Iriguchi, M., Craninckx, J.: A 1.7 mW 11b 250MS/s 2x interleaved fully dynamic pipelined SAR ADC in 40 nm Digital CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 466–469 (2012)

- 28. van der Goes, F., et al.: A 1.5 mW 68 dB SNDR 80 Ms/s 2x interleaved pipelined SAR ADC in 28 nm CMOS. IEEE J. Solid State Circuits 49(12), 2835–2845 (2014)

- Gupta, S., et al.: A 1GS/s 11b time-interleaved ADC with 55-dB SNDR, 250 mW power realized by a high bandwidth scalable time-interleaved architecture. IEEE J. Solid State Circuits 41, 2650–2657 (2006)

- Greshishchev, Y., et al.: A 40GS/s 6b ADC in 65 nm CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 390–391 (2010)

- 31. Doris, K., et al.: Interleaving of sar adcs in deep submicron CMOS technology. Advances in Analog and RF IC Design for Wireless Communication Systems, 1st edn. Elsevier. ISBN:9780123983268

- 32. Kull, L., et al.: 22.1 A 90GS/s 8b 667 mW 64x; interleaved SAR ADC in 32 nm digital SOI CMOS. In: 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 378–379, Feb 2014

- Duan, Y., Alon, E.: A 12.8 GS/s time-interleaved ADC with 25 GHz effective resolution bandwidth and 4.6 ENOB. IEEE J. Solid State Circuits 49(8), 1725–1738 (2014)

- 34. Wu, J., et al.: A 4GS/s 13b pipelined ADC with capacitor and amplifier sharing in 16nm CMOS. In: 2016 IEEE International Solid-State Circuits Conference (ISSCC), pp. 466–467, Jan 2016

- 35. Wu, J., et al.: A 5.4GS/s 12b 500 mW pipeline ADC in 28 nm CMOS. In: 2013 Symposium on VLSI Circuits, pp. C92–C93, June 2013

- 36. Kull, L., et al.: A 10b 1.5GS/s pipelined-SAR ADC with background second-stage commonmode regulation and offset calibration in 14 nm CMOS FinFet. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 474–476, Jan 2017

- 37. Vaz, B., et al.: A 13b 4GS/s digital assisted dynamic 3-stage asynchronous pipelined-SAR ADC. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 476–477, Jan 2017

- 38. Su, S., Chen, M.S.W.: A 12b 2GS/s dual-rate hybrid DAC with pulsed timing-error predistortion and in-band noise cancellation achieving >74dBc SFDR up to 1 GHz in 65 nm CMOS. In: 2016 IEEE International Solid-State Circuits Conference (ISSCC), pp. 456–457, Jan 2016

- 39. Olieman, E., et al.: A 110 mW, 0.04 mm<sup>2</sup>, 11gs/s 9-bit interleaved DAC in 28 nm fdsoi with 50 dB SFDR across nyquist. In: 2014 Symposium on VLSI Circuits Digest of Technical Papers, June 2014, pp. 1–2

- Bechthum, E., et al.: A wideband RF mixing-DAC achieving IMD lt; -82 DBC up to 1.9 GHz. IEEE J. Solid State Circuits 51(6), 1374–1384 (2016)

- McCreary, J., Gray, P.: All-MOS charge redistribution analog-to-digital conversion techniques. IEEE J. Solid State Circuits 10(6), 371–379 (1975)

- 42. Alpman, E., et al.: A 1.1V 50 mW 2.5GS/s 7b time-interleaved C-2C SAR ADC in 45 nm LP digital CMOS. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 76–77, 77a (2009)

- 43. Kramer, M.J., et al.: A 14 b 35 MS/s SAR ADC achieving 75 dB SNDR and 99 dB SFDR with loop-embedded input buffer in 40 nm CMOS. IEEE J. Solid State Circuits 50(12), 2891–2900 (2015)

- 44. Poulton, K., et al.: A 7.2-GSa/s, 14-bit or 12-GSa/s, 12-bit DAC in a 165-GHz fT BiCMOS process. In: 2011 Symposium on VLSI Circuits Digest of Technical Papers, pp. 62–63, June 2011

- Hershberg, B., et al.: Ring amplifiers for switched capacitor circuits. IEEE J. Solid-State Circuits 47(12), 2928–2942 (2012)

- 46. van Elzakker, M., et al.: A 10-bit charge-redistribution ADC consuming 1.9μW at 1MS/s. IEEE Journal of Solid-State Circuits **45**(5), 1007–1015 (2010)

- 47. Breems, L., et al.: A 2.2 GHz continuous-time  $\Delta\Sigma$  ADC with 102 dBc THD and 25 MHz bandwidth. IEEE J. Solid-State Circuits **51**(12), 2906–2916 (2016)

- Harpe, P., et al.: A 7-to-10b 0-to-4MS/s flexible SAR ADC with 6.5-to-16fJ/conversionstep. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 472–475 (2012)

- Kramer, M.J., et al.: A 14-bit 30-MS/s 38-mW SAR ADC using noise filter gear shifting. IEEE Trans. Circuits Syst. Express Briefs 64(2), 116–120 (2017)

- Yip, M., Chandrakasan, A.: A resolution-reconfigurable 5-to-10b 0.4-to-1V power scalable SAR ADC. In: IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 190–191 (2011)

- 51. Tang, Y., et al.: A 14 bit 200 MS/s DAC with SFDR > 78 dBc, im3 < -83 dBc and NSD < -163 dbm/Hz across the whole Nyquist band enabled by dynamic-mismatch mapping. IEEE J. Solid State Circuits **46**(6), 1371–1381 (2011)

- 52. de Vel, H.V., et al.: 11.7 a 240 mW 16b 3.2gs/s DAC in 65 nm CMOS with -80 dBc im3 up to 600 MHz. In: 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 206-207, Feb 2014

- 53. Lin, Y.: et al.: An 11b 1GS/s ADC with parallel sampling architecture to enhance SNDR for multi-carrier signals. In: 2013 Proceedings of the ESSCIRC (ESSCIRC), pp. 121–124, Sept 2013

- 54. Greshishchev, Y.: CMOS ADCs for optical communications. In: Proceedings of the 20th Workshop on Advances in Analog Circuit Design (AACD), Apr 2012

- 55. Brandolini, M., et al.: 26.6 A 5GS/S 150 mW 10b SHA-less pipelined/SAR hybrid ADC in 28 nm CMOS. In: 2015 IEEE International Solid-State Circuits Conference – (ISSCC) Digest of Technical Papers, pp. 1–3, Feb 2015

#### 1 Hybrid Data Converters

- 56. Devarajan, S., et al.: A 12b 10GS/s interleaved pipeline ADC in 28 nm CMOS technology. In: 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 288–289, Jan 2017

- Ali, A.M.A., et al.: A 14-bit 2.5GS/s and 5GS/s RF sampling ADC with background calibration and dither. In: 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), pp. 1–2, June 2016

- Kapusta, R., et al.: A 14b 80 Ms/s SAR ADC with 73.6 db SNDR in 65 nm CMOS. IEEE J. Solid State Circuits 48(12), 3059–3066 (2013)

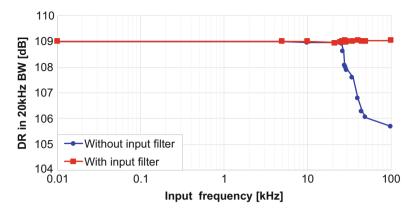

- Gonen, B., et al.: 15.7 A 1.65 mW 0.16 mm2 dynamic zoom-ADC with 107.5 dB DR in 20 kHz BW. In: 2016 IEEE International Solid-State Circuits Conference (ISSCC), pp. 282–283, Jan 2016

## Chapter 2 Hybrid and Segmented ADC Techniques to Optimize Power Efficiency and Area: The Case of a 0.076 mm<sup>2</sup> 600 MS/s 12b SAR- $\Delta \Sigma$ ADC

Alessandro Venca, Nicola Ghittori, Alessandro Bosi, and Claudio Nani

#### 2.1 Introduction

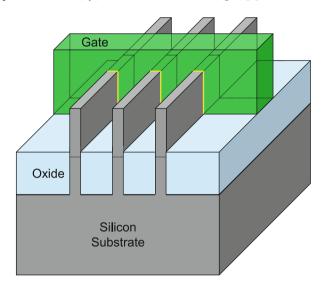

Integration of low-power and area-efficient ADCs is a key differentiator in modern mixed-signal SoCs. The increasing usage of software radio architectures for the design of wireline communication receivers calls for the design of high-speed medium to high-resolution ADCs with high power efficiency [1, 2].

Traditionally, these challenges have been addressed in scaled technologies using SAR architectures, often in combination with techniques like redundancy, asynchronous operation, and time interleaving to meet the required application sampling rate. However, for high-resolution ADCs (9b + ENOB), a traditional SAR is intrinsically energy inefficient since it reuses the same low-noise comparator to perform both coarse conversions (where little accuracy is needed) and fine conversions (where thermal noise is of paramount importance) [8].

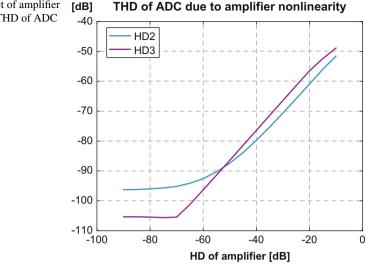

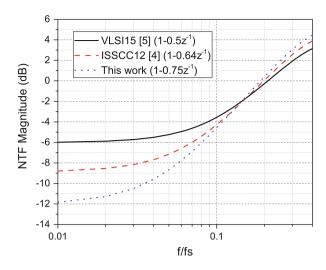

In the last few years, this limit has been addressed by combining SAR with other conversion algorithms like averaging [4], noise shaping with oversampling [5, 7], single slope [6], and pipelining. As an example, in [7], flash, SAR, and noise shaping with oversampling techniques are combined together in a single design to achieve a Schreier FoM of 180 dB in 4 KHz bandwidth. For high-resolution and medium sampling rate converters, excellent power efficiency figures have been achieved with hybrid SAR-pipeline architectures [8, 9] that employ SAR as subADCs, but whose noise performance is determined by a high-efficiency interstage amplifier as opposed to the comparator. All these works focus on combining different conversion techniques in a single design and use each of them in a resolution and

A. Venca • N. Ghittori • A. Bosi • C. Nani (🖂)

Marvell Italia s.r.l., viale Repubblica 38, 27100 Pavia, Italy e-mail: nanis.cn@gmail.com

<sup>©</sup> Springer International Publishing AG 2018

P. Harpe et al. (eds.), Hybrid ADCs, Smart Sensors for the IoT, and Sub-IV

<sup>&</sup>amp; Advanced Node Analog Circuit Design, DOI 10.1007/978-3-319-61285-0\_2

signal amplitude range where they perform at its maximum power efficiency. This approach has become so widespread that the resulting ADC architectures have been denoted as "hybrid ADCs."

At the same time, emerging wireline standards like the G.hn Gen 2 [3] that employ MIMO strategies often require the integration of a large number of analog front ends (AFE) in a single SoC. Such AFEs should therefore require little or no external components as this may have a significant impact on the complete system bill of materials (BoM). In order to tackle these application demands, the design of wide-bandwidth high-resolution ADCs with extremely low power *and* area is clearly of key importance.

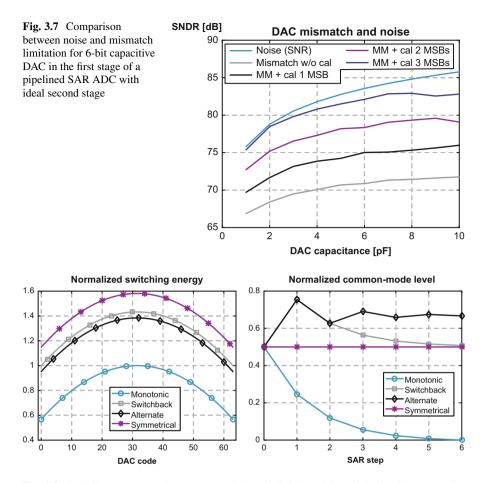

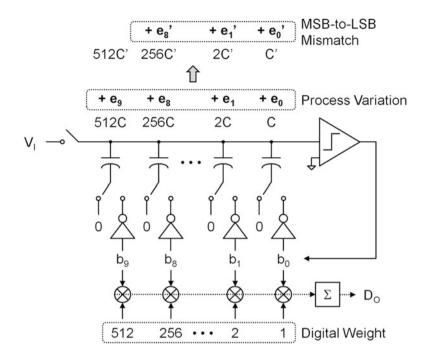

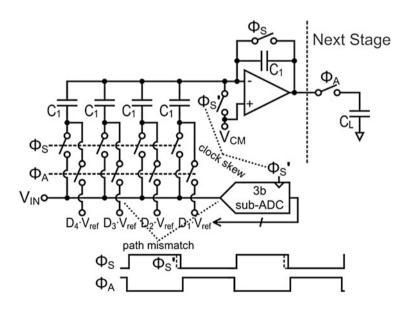

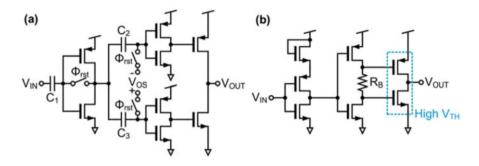

Also in the field of ADC area, the adoption of the SAR architecture and the increasing usage of digital calibrations allowed data converters to reap the benefits of technology scaling. As an example, the introduction of digital DAC linearity calibrations [12] resulted in a significant reduction of matching requirements, allowing scaling down the DAC capacitance to the kT/C limit.

In noise-limited SAR ADCs, for every extra bit of resolution, the sampling and DAC capacitance grows four times, while, at the same time, the ripple on the converter reference voltage has to be reduced two times to preserve linearity. Such a trend sets very tough requirements for the reference generator of highresolution charge-redistribution DAC (CR-DAC) SAR ADCs, especially when no external components can be used, hence requiring the integration of very large onchip capacitors [9]. Another approach to address this issue in literature is using DAC switching schemes that optimize the current drawn from the reference [8, 9] or with DAC topologies more immune to reference ripple, like current-steering [10] or charge-sharing DACs (CS-DAC) [11].

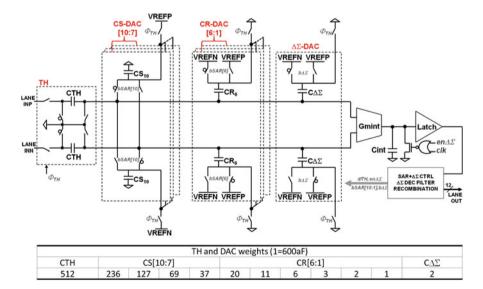

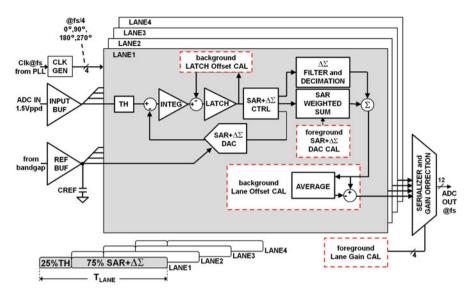

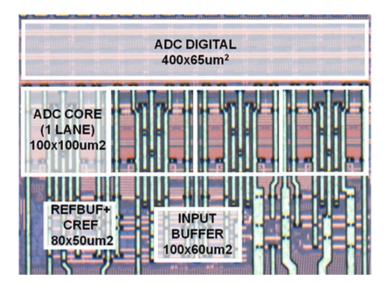

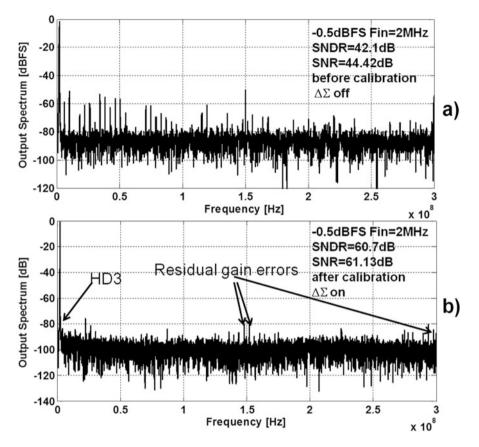

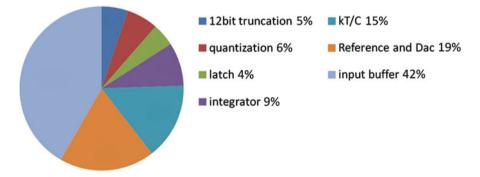

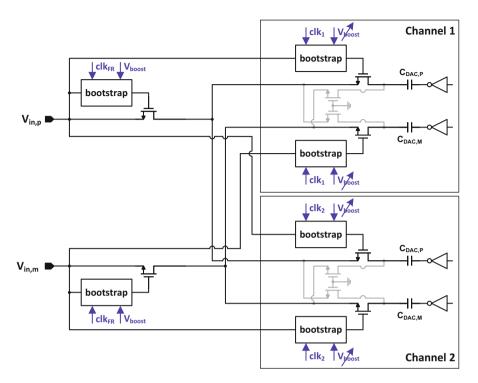

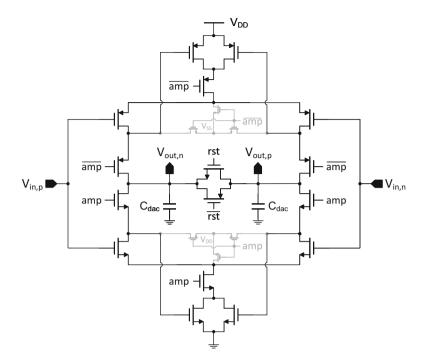

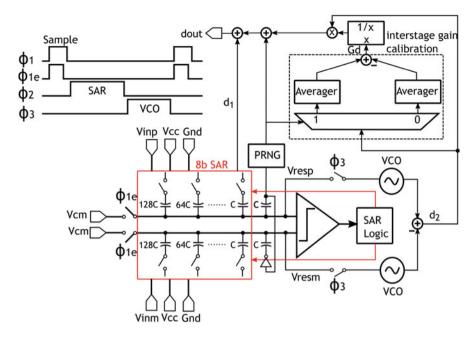

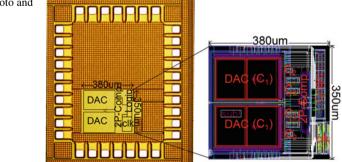

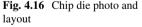

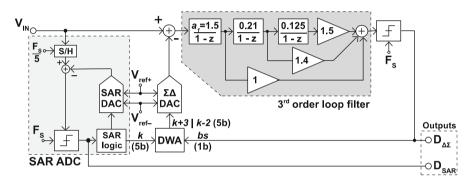

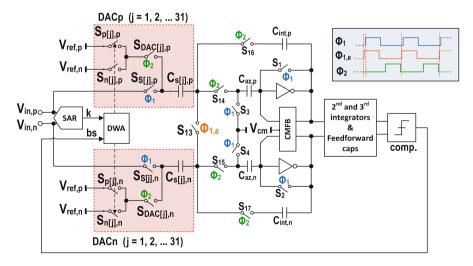

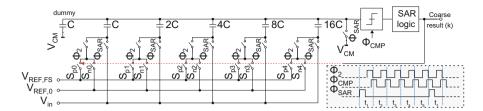

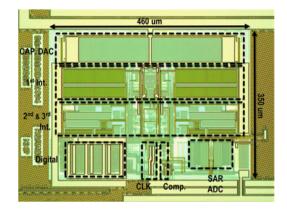

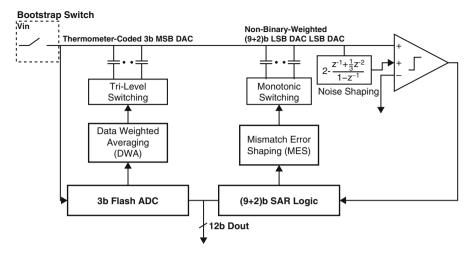

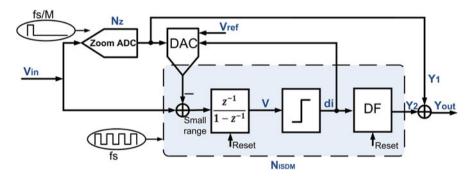

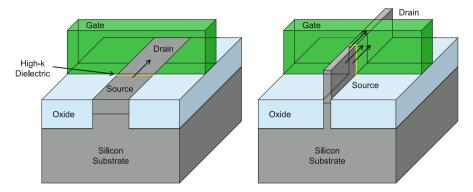

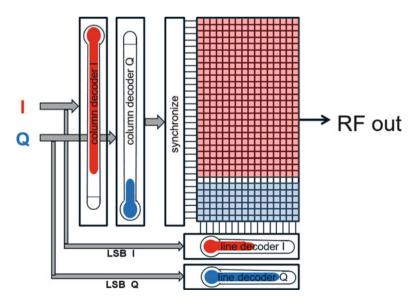

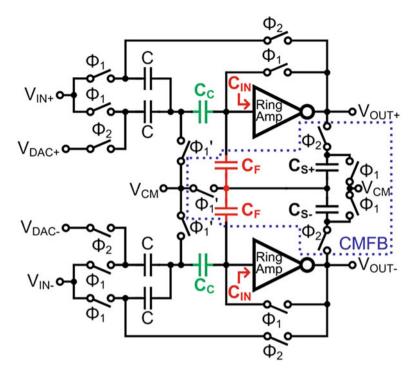

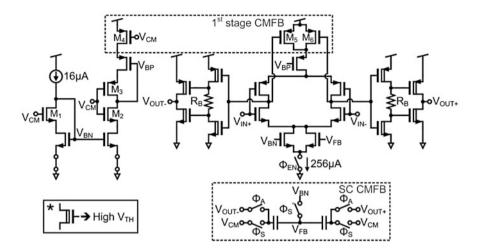

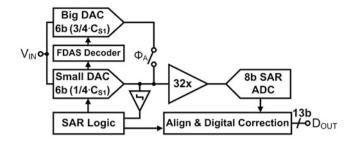

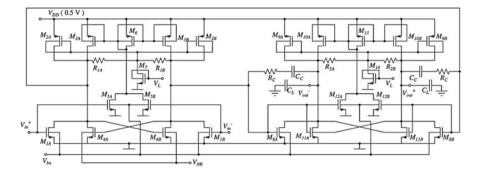

In this paper, a 12b four-way interleaved 600 MS/s ADC with on-chip input signal and reference buffer is presented. The energy efficiency challenge is addressed with a hybrid ADC architecture that employs a SAR as a coarse ADC and an incremental Delta-Sigma as a fine ADC. A significant area reduction is achieved with a segmented charge-sharing charge-redistribution DAC architecture that relaxes significantly the accuracy requirements on the reference generator and can be scaled down to kT/C limit as a conventional CR-DAC.

The 28 nm CMOS ADC prototype delivers 58 dB SNDR at Nyquist for 26.5 mW of power with a total area of only  $0.076 \text{ mm}^2$  and does not require any external component.

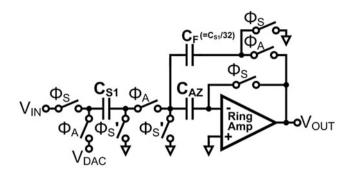

Section 2.2 discusses the thermal noise performance of incremental  $\Delta\Sigma$  ADCs and compares it with the SAR architecture. The subrange SAR- $\Delta\Sigma$  ADC architecture is then introduced in Sect. 2.3. Sections 2.4 and 2.5 review the requirements for the reference generator of high-resolution charge-redistribution DACs and the scalability limits of the charge-sharing DAC architecture. The segmented charge-sharing charge-redistribution DAC architecture is then presented in Sect. 2.6. The overall ADC architecture and calibrations are presented in Sect. 2.7, while in Sect. 2.8 the circuit level implementation is presented. Section 2.9 presents the measurement results, and finally conclusions are drawn in Sect. 2.10.

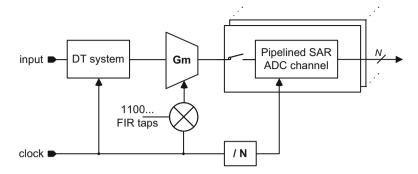

#### 2.2 Incremental $\Delta \Sigma$ Conversion Algorithm

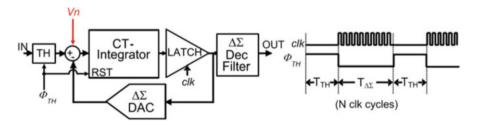

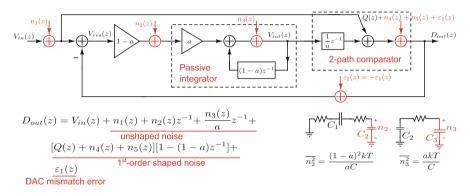

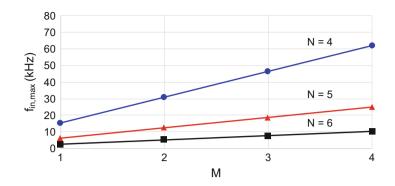

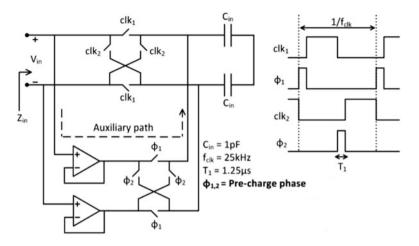

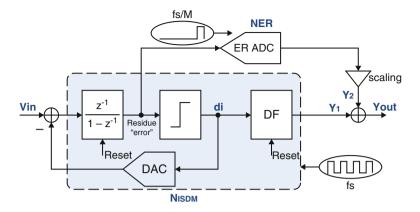

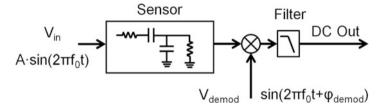

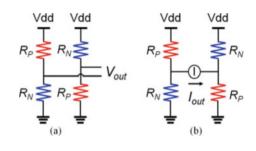

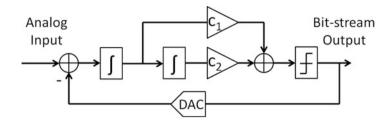

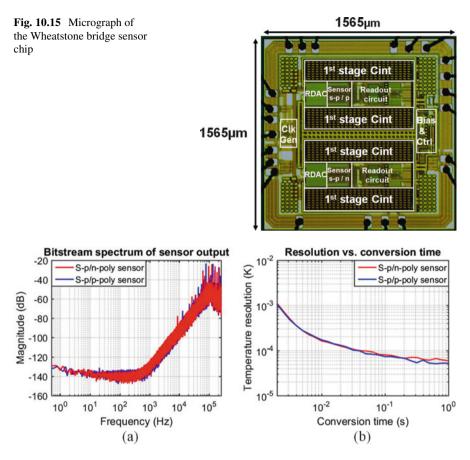

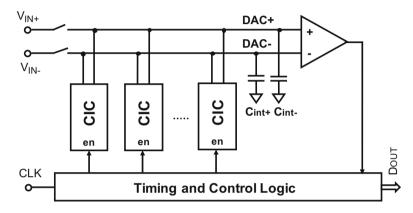

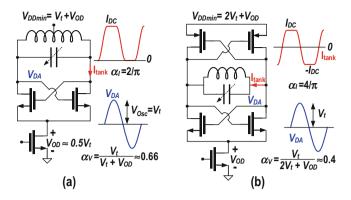

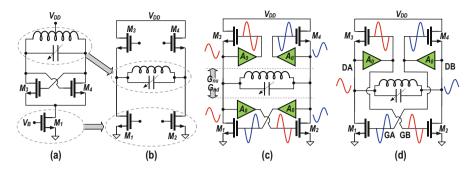

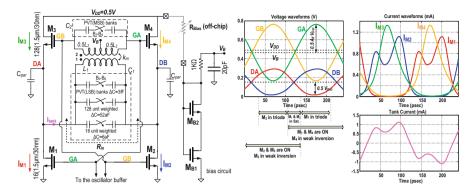

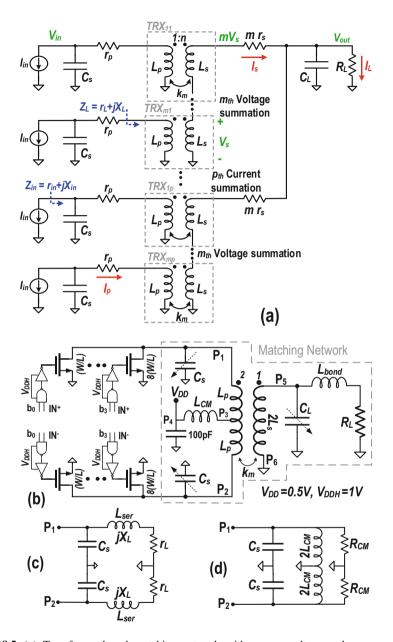

In literature, a very power-efficient conversion technique from a thermal noise perspective is the incremental  $\Delta\Sigma$  algorithm [13–15] whose basic block diagram is shown in Fig. 2.1. It consists of a T/H stage followed by a  $\Delta\Sigma$  modulator whose internal state can be reset. After the sampling phase, the input signal is held constant at the input of the  $\Delta\Sigma$  modulator, and it is converted for N clock cycles  $(NT_{clk} = T_{\Delta\Sigma})$ . At the end of conversion, the state of the  $\Delta\Sigma$  modulator, which is the loop filter capacitances, is reset, and the N samples output sequence is then filtered by a FIR filter and decimated by N.

A key property of continuous-time (CT) incremental  $\Delta\Sigma$  modulators is their behavior with respect to thermal noise added at the modulator inputs, mainly ascribed to DAC and loop filter integrators ( $V_n$  in Fig. 2.1). Unlike the input signal, this noise source is not sampled and therefore is filtered by the CT- $\Delta\Sigma$  modulator signal transfer function and appears at the quantizer output. The digital FIR decimation filter then suppresses the out-of-band noise before the final decimation. By assuming a white Gaussian input thermal noise power spectral density  $S_{Vn}$ , the final output noise power is given by

$$P_n = \int_0^{f \operatorname{clk}/2} S_{Vn} |H_{\operatorname{FIR}}(f)|^2 \simeq S_{Vn} B w_n \text{ with } B w_n = \frac{\sum_{i=1}^N c_i^2}{2T_{clk}} = \frac{1}{\varphi T_{\Delta \Sigma}}$$

(2.1)

where  $H_{\text{FIR}}(f)$  is the FIR frequency response and  $Bw_n$  is the equivalent analog noise bandwidth of the FIR filter. The  $\varphi$  parameter depends on the actual FIR filter coefficients, and it can be proven that it is maximized ( $\varphi = 2$ ) when all the FIR coefficients are equal (dumped integrator). If we implement the loop filter using a simple open-loop integrator (first-order  $\Delta \Sigma$  modulator), this result is similar to the one in [8]; however in this scheme, the integrator, being inside a  $\Delta \Sigma$  loop, does not need gain calibration nor stringent linearity performance.

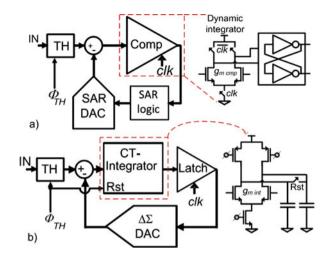

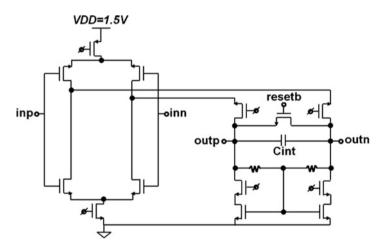

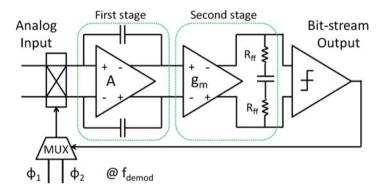

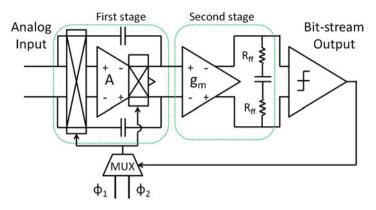

We can compare the incremental  $\Delta\Sigma$  and SAR thermal noise performance by considering the  $\Delta\Sigma$  integrator and the SAR dynamic comparator as the only noise (and power) limiting blocks (see Fig. 2.2). The latter is usually implemented as a dynamic integrator followed by a CMOS latch (see Fig. 2.2a), and its input-referred

Fig. 2.1 Incremental  $\Delta\Sigma$  converter block diagram and timing

thermal noise is dominated by the contribution of the input differential pair that can be written [16] as

$$P_{n \text{ SAR}} = S_{Vn} B w_n \cong \frac{8kT\gamma}{g_{m \text{ cmp}}} \frac{1}{2T_{\text{int}}}$$

(2.2)

where  $T_{int}$  is the duration of the dynamic integrator integration phase. If a simple open-loop integrator is used in an incremental  $\Delta\Sigma$  ADC (assuming no linearity constraints, see Fig. 2.2b), the resulting noise power using Eq. (2.1) is

$$P_{n \ \Delta\Sigma} = S_{Vn} B w_n \simeq \frac{8kT\gamma}{g_{mint}} \frac{1}{\varphi T_{\Delta\Sigma}}$$

(2.3)

Equations (2.2) and (2.3) have very similar structure and show that for both architectures the thermal noise is proportional to the inverse of the product  $g_m \cdot T$ . If we assume the same input pair overdrive  $(V_{ov})$ , the product  $g_m \cdot T = 2I_d/V_{ov} \cdot T$  is proportional to the total charge drawn by the integrators.

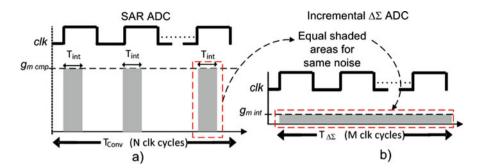

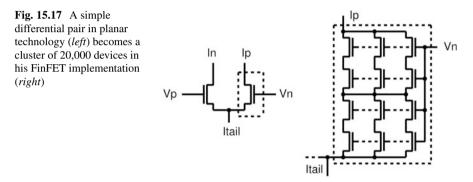

While in an incremental  $\Delta\Sigma$  ADC this charge  $(g_{m \text{ int}} \cdot T_{\Delta\Sigma})$  is drawn only once during the complete  $\Delta\Sigma$  conversion time  $(T_{\Delta\Sigma} \text{ see Fig. 2.3b})$ , in a SAR approximately the same charge  $(g_{m \text{ cmp}} \cdot T_{\text{int}})$  must be drawn every time the comparator is activated (see Fig. 2.3a). That means that in an *N*-bit SAR converter, the total charge drawn by the SAR comparator is *N* times the one used by an incremental  $\Delta\Sigma$  integrator for the same level of thermal noise. In redundant SAR [17], the comparator power and noise can be optimized during conversion, but also in this case, more than one conversion cycle with the final comparator noise level is required when the quantization noise approaches the comparator thermal noise.

Fig. 2.2 (a) SAR and (b) first-order  $\Delta \Sigma$  ADC block diagrams and circuit level implementations of the blocks considered as main contributors to noise power performance

Fig. 2.3 Timing diagram with grey highlights when  $g_m$  is used to suppress thermal noise (a) for SAR ADC and (b) for a first-order  $\Delta \Sigma$  ADC

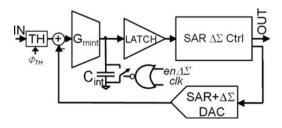

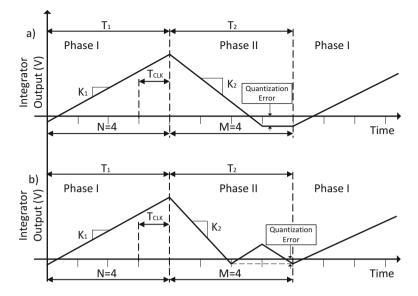

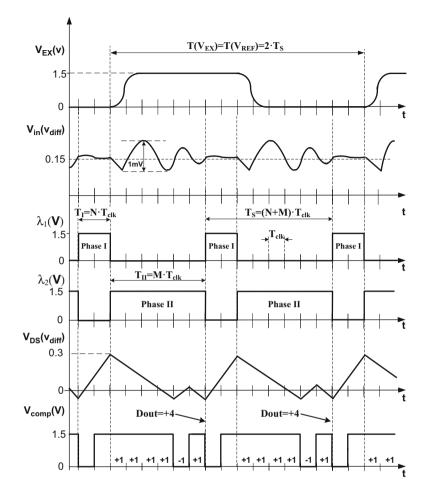

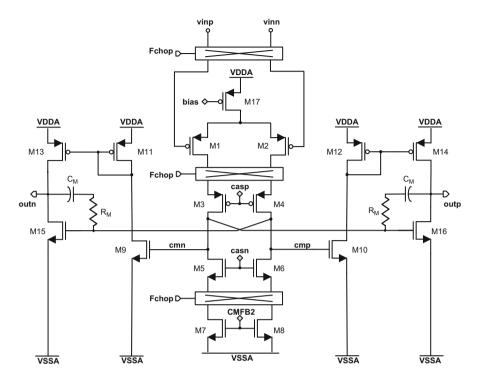

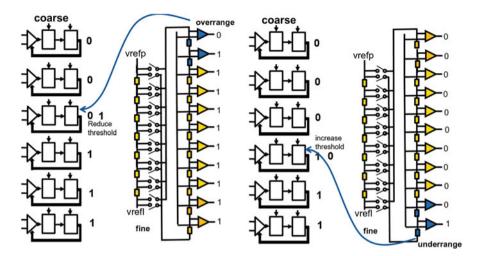

Fig. 2.4 SAR- $\Delta\Sigma$  subrange lane ADC conceptual block diagram and timing

#### **2.3** SAR- $\Delta \Sigma$ Subrange Hybrid ADC Architecture

While CT-incremental  $\Delta\Sigma$  converters are very efficient in mitigating the thermal noise components from the loop filter integrators, their key weakness is the large oversampling ratio, that is, number of clock cycles required to bring quantization noise to the target level.

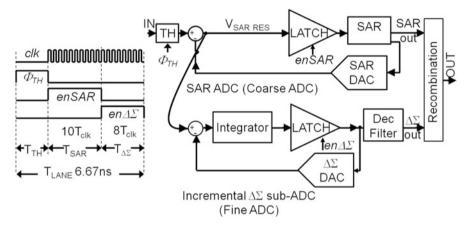

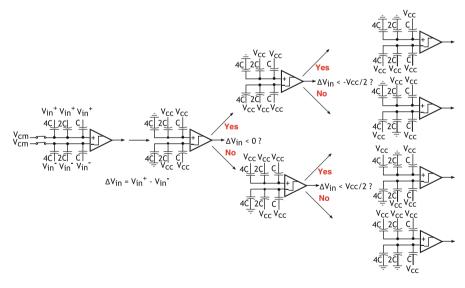

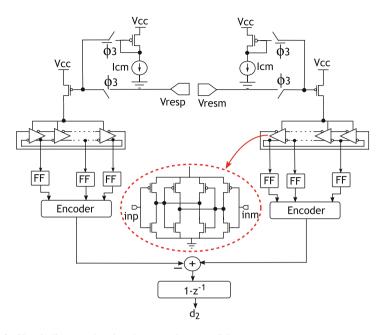

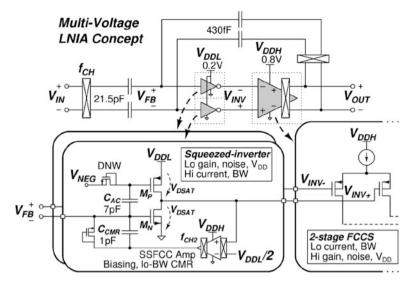

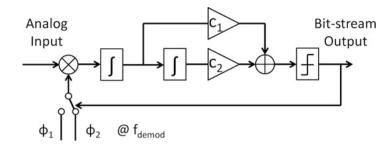

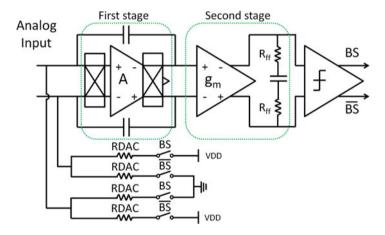

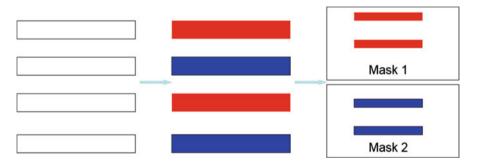

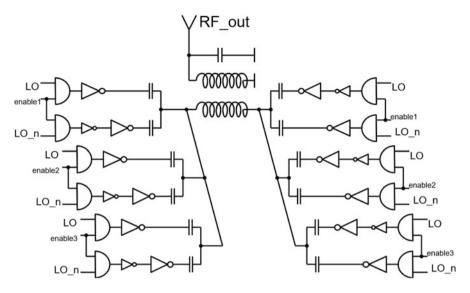

A possible solution is then to build a hybrid converter by combining a midresolution coarse SAR ADC (where SAR algorithm provides maximum power efficiency) with CT-incremental  $\Delta\Sigma$  fine modulator that deals with the thermal noise while providing only few bits of quantization. The resulting hybrid subrange ADC block diagram is shown in Fig. 2.4. By resolving a significant number of bits using the SAR algorithm, the number of clock cycles required by the  $\Delta\Sigma$ -subADC to get to the target final resolution can be reduced drastically. In the presented 12b design, the coarse non-binary SAR ADC provides 9b of equivalent resolution, and the fine ADC ( $\Delta\Sigma$ -subADC) implemented as 1-bit first-order CT-incremental  $\Delta\Sigma$  ADC resolves the remaining 3b to get to the final 12b resolution. 1b overrange is added between the coarse SAR ADC and the  $\Delta\Sigma$ -subADC in order to correct for the coarse SAR ADC error induced by the SAR loop thermal noise leading to a final  $\Delta\Sigma$ -subADC resolution of 4b after filtering and decimation.

The operation phases are shown in Fig. 2.4. After the sampling and the coarse SAR conversion phase (ten clock cycles), the SAR residual error is converted by the fine  $\Delta\Sigma$ -subADC in eight clock cycles. The eight  $\Delta\Sigma$ -subADC comparator decisions are filtered using an 8-taps low-pass FIR filter and decimated by eight before being recombined with the SAR output to get a 12b final code.

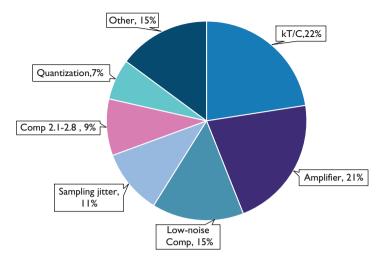

Once the  $\Delta\Sigma$ -subADC and coarse SAR output are recombined, the only residual noise is the sampling kT/C noise and the  $\Delta\Sigma$ -subADC noise, i.e.,  $\Delta\Sigma$  quantization noise, latch thermal noise, and loop filter thermal noise. All these components are low-pass filtered by the  $\Delta\Sigma$ -subADC FIR filter with the equivalent bandwidth of the FIR (approx  $1/\varphi T_{\Delta\Sigma}$  where  $T_{\Delta\Sigma}$  is the  $\Delta\Sigma$ -subADC conversion time) as shown in Sect. 2.2. Since both quantization and latch thermal noise are first-order shaped, they are strongly suppressed by the FIR leaving as dominant terms the sampling (kT/C) noise and the input-referred noise of the  $\Delta\Sigma$  integrator (with integration time  $T_{\Delta\Sigma}$ ). Artifacts due to first-order shaping are dithered by the thermal noise added by the latch.

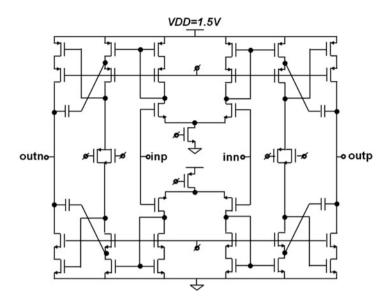

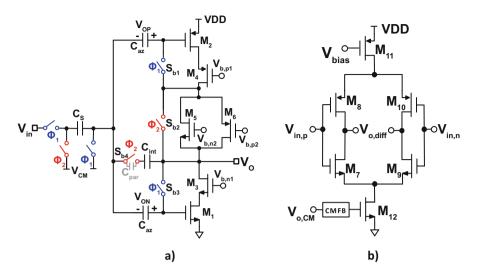

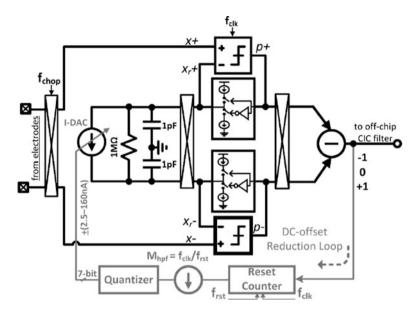

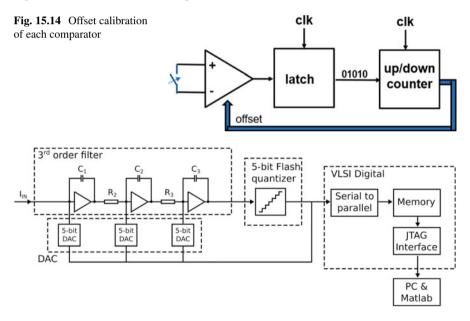

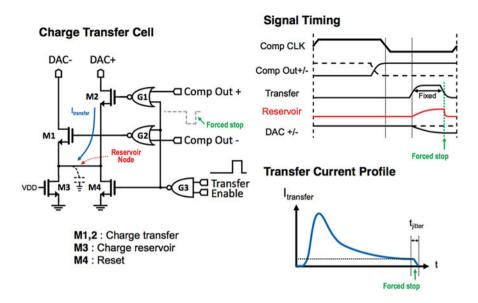

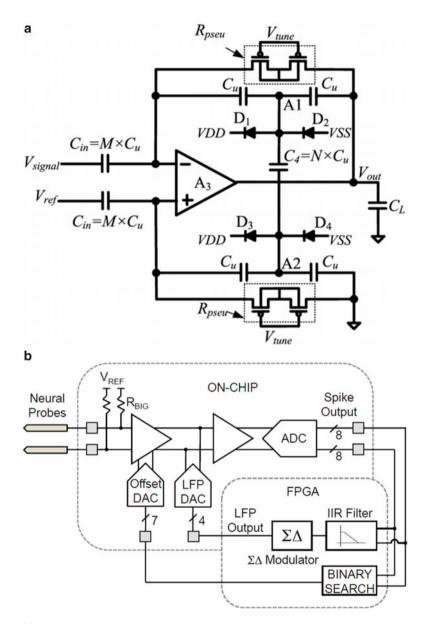

The  $\Delta\Sigma$ -subADC is implemented with minimum hardware overhead by merging the  $\Delta\Sigma$ -DAC with the SAR-DAC and reusing the comparator latch. Reconfiguring the SAR comparator static preamp stage ( $G_{mint}$ ) into the  $\Delta\Sigma$  integrator only requires stopping the reset of its load capacitor ( $C_{int}$ ) after the last SAR cycle (Fig. 2.5).

A consequence of this choice is that the transconductance of the resetting integrator in the SAR phase and of the loop integrator in the  $\Delta\Sigma$  phase are the same. The resetting integrator is designed to have a  $3\sigma$  thermal noise to be less than the coarse LSB (LSB<sub>SAR</sub>) to guarantee the SAR noise (quantization + thermal) to be within the input range of the fine  $\Delta\Sigma$  ADC. The integrator thermal noise power at the  $\Delta\Sigma$  output can then be derived from (Eq. 2.2) and (Eq. 2.3) as

$$P_n = P_{n \text{ SAR}} \cdot \frac{2T_{\text{int}}}{\varphi T_{\Delta \Sigma}}$$

(2.4)

Fig. 2.5 SAR- $\Delta\Sigma$  subrange lane ADC minimum hardware implementation

where the suppression of the integrator thermal noise can be easily appreciated since  $T_{\Delta\Sigma} = N \cdot T_{\text{CLK}}$  where N is the number of  $\Delta\Sigma$  clock cycles, whereas  $T_{\text{int}}$  is a fraction of  $T_{\text{CLK}}$ .

Since a first-order  $\Delta\Sigma$  suppresses the quantization noise with the inverse of the oversampling ratio (OSR  $\cong T_{\Delta\Sigma}/T_{CLK}$ ) at the power of 3, it can be calculated that a first-order modulator is enough to suppress the quantization noise in  $N = 8 \Delta\Sigma$  cycles to roughly the same level as the thermal noise.

The FIR filter frequency response has been designed in order to maximize the final ADC ENOB performance in the presence of all noise sources (including latch thermal noise) as well as quantization noise. The resulting filter shows a  $\varphi$  factor of approximately 1.8. Given the limited number of  $\Delta\Sigma$ -subADC conversion cycles, the digital FIR filter can be implemented in a simple direct form as weighted sum of the eight  $\Delta\Sigma$ -subADC comparator decisions.

In the presented implementation, all timing signals required for the conversion are generated internally using a self-timed loop approach [18]. Jitter on the internal clock during the  $\Delta\Sigma$  phase is minimized by allocating a fixed time to comparator decisions.

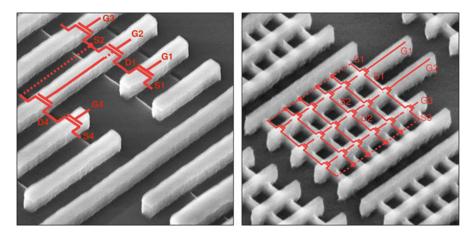

#### 2.4 Charge-Redistribution SAR-DAC

In the previous section, we have seen that it is possible to improve ADC power efficiency by applying a combination of conversion algorithms each of them used in a resolution range where it performs at its peak energy efficiency. A similar approach can be also applied to minimize the converter area, that is, by implementing blocks with a combination of different architectures, it is possible to achieve significant area saving and/or remove the need for external components. In the specific case of SAR- $\Delta\Sigma$  ADC, we are focusing on the DAC and its reference generator blocks which are often the largest contributor to total converter area.

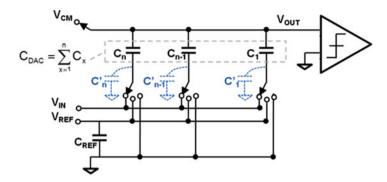

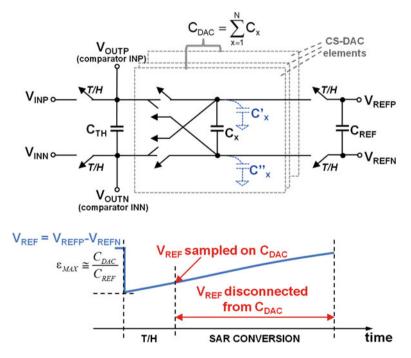

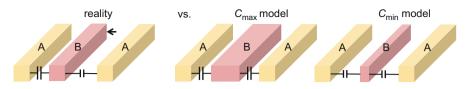

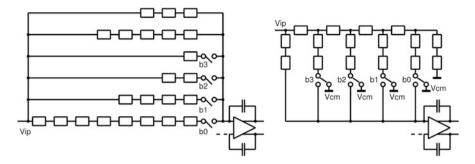

The D/A converter of SAR ADCs is commonly a capacitive-based topology due to the inherent high matching of metal capacitors in deep-submicron technology. Among them, the charge-redistribution DAC (CR-DAC) (Fig. 2.6) [19] is extensively used mainly for its small C-array area. As the DAC switches are on the bottom plate (the side opposite to the comparator), the CR-DAC is inherently insensitive to switch parasitics ( $C'_n$ ,  $C'_{n-1}$ , ...,  $C'_1$ ), since these undesired capacitances are always connected to the reference generator. This property allows scaling down the DAC capacitance eventually to the kT/C noise limit, and it represents the main reason for the small *C*-array area achieved by the CR-DAC topology.

A key limitation of CR-DAC is that it requires a very accurate reference voltage not to impact the linearity performance. In a CR-DAC, in fact, the reference voltages are connected through the DAC switches and capacitors to the comparator inputs during the SAR phase of the ADC. The transfer function from the reference voltage node to the input of the comparator is not linearly code dependent, ranging from a unity transfer function when the DAC has all the capacitors connected between

Fig. 2.6 Single-ended charge-redistribution DAC (CR-DAC) in track mode

the comparator input node and the reference voltage to virtually infinite attenuation when the DAC has all the capacitors connected between the comparator input node and the ground voltage. Therefore, ripples on the reference voltage greater than 1LSB during the SAR phase can cause errors in the comparator decisions that if not corrected may produce distortion in the converted signal. Moreover the net charge absorbed by the reference generator during one conversion, due to the switching of the DAC capacitors, is not linearly code dependent as well, as described in [19]. The net switching charge per conversion is absorbed by the finite impedance of the reference generator and produces a low-frequency code-dependent voltage ripple with a major spectral component at the ADC input signal second harmonic (in differential structures). This ripple, when mixed with the input signal fundamental, produces a third harmonic at the ADC output.

The two nonlinear mechanisms discussed above translate into very tough requirements for the reference generator of high-resolution charge-redistribution SAR ADCs. To mitigate the effects of the nonlinear reference-to-comparator transfer function, a large decoupling capacitance is usually required to reduce the highfrequency ripple, while low output peak impedance of the reference buffer is needed to attenuate the effects of the low-frequency nonlinear current drawn from the references by the switching DAC activity.

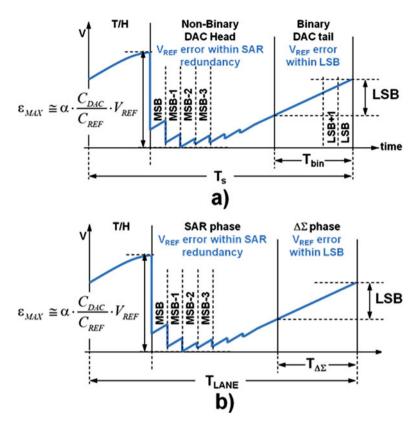

In a SAR ADC using binary-weighted CR-DAC, the reference voltage is required to settle within 1LSB accuracy at every conversion cycle. Non-binary-weighted CR-DAC implementations tolerate larger reference errors in the redundant part of the DAC, but still they require 1LSB settling accuracy during the last few conversion cycles where errors cannot be recovered by redundancy. The requirements on the reference voltage accuracy in a generic non-binary CR-DAC can be evaluated from Fig. 2.7a where the reference voltage ripple is sketched in steady state (ripple recovered within  $T_S$ ). In this qualitative example, the reference generator has a bandwidth much smaller than the ADC conversion frequency  $f_S$ , and the decoupling capacitance is equal to  $C_{\text{REF}}$ . In this condition, by approximating the ripple peak amplitude generated by the first few MSB transitions as  $\varepsilon_{\text{MAX}} = \alpha C_{\text{DAC}}/C_{\text{REF}}$  and assuming a linear reference voltage recovery, the required  $C_{\text{REF}}$  can be estimated as

Fig. 2.7 Qualitative reference voltage ripple (a) in a non-binary CR-DAC and (b) in a non-binary SAR- $\Delta\Sigma$  architecture using a CR-DAC

$$C_{\text{REF}} \ge \alpha \cdot \frac{T_{\text{bin}}}{T_S} \cdot 2^{N-1} \cdot C_{\text{DAC}}$$

(2.5)

where  $C_{\text{DAC}}$  is the total DAC capacitance and the factor  $\alpha$  takes into account for the switching scheme adopted in the DAC. In [20], for example, a switching scheme with  $\alpha$  equal to 0.25 has been presented. This factor can be reduced further but often results in a code-dependent DAC output common mode [21].

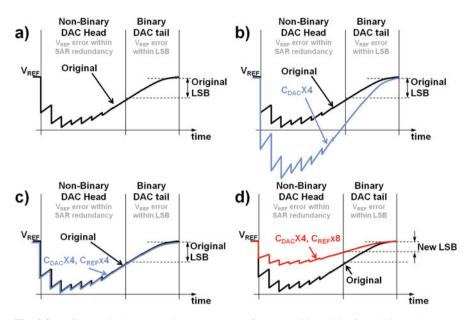

In the case of a noise-limited charge-redistribution SAR ADC, it is interesting to analyze the scaling of the size of the  $C_{\text{REF}}$  as the required resolution increases, by using (Eq. 2.5). In Fig. 2.8 an example for 1 bit of additional resolution requirement is shown. Here the  $C_{\text{DAC}}$  has been multiplied by a factor 4 to meet the kT/C noise requirement (Fig. 2.8b). To recover the original ripple, the  $C_{\text{REF}}$  must be increased by a factor 4 as well (Fig. 2.8c). However since the new LSB is half the original one (*N* is increased by 1), to preserve the linearity specification, the ripple must be reduced by another factor 2, hence requiring  $C_{\text{REF}}$  to be multiplied by a factor 8 (Fig. 2.8d). As a consequence of that in a noise-limited charge-redistribution SAR

**Fig. 2.8** Reference ripple and requirement on  $C_{\text{REF}}$  for one additional bit of resolution (T/H phase omitted to simplify the visualization). (a) Original ripple (*black*), (b) ripple (*blue*) with  $C_{\text{DAC}}$  increased four times to meet kT/C requirements, (c) ripple (*blue*) with  $C_{\text{REF}}$  increased four times to obtain the original ripple, and (d) ripple (*red*) with  $C_{\text{REF}}$  increased eight times to meet linearity requirements

ADC as the resolution increases, the size of the reference capacitance grows with double rate with respect to its core DAC capacitance eventually becoming the main integrated area contributor for resolutions beyond 9/10bit ENOB.

For the specific case of the 12b SAR- $\Delta\Sigma$  architecture using a CR-DAC, the reference ripple can be tolerated to a certain extent in the SAR phase, thanks to the DAC redundancy and to the  $\Delta\Sigma$  overrange, but during the fine  $\Delta\Sigma$  phase, the reference error must be kept within 1LSB as in a non-binary-weighted SAR ADC (Fig. 2.7b). The required  $C_{\text{REF}}$  can be then calculated using (Eq. 2.5) as

$$C_{\text{REF}} \ge \alpha \cdot \frac{T_{\Delta \Sigma}}{T_{\text{LANE}}} \cdot 2^{N-1} \cdot C_{\text{DAC}} \cong 50 \text{pF}$$

(2.6)

where N = 12,  $C_{\text{DAC}} = 300$  fF,  $\alpha = 0.25$ ,  $T_{\Delta\Sigma} = 2.22$  ns, and  $T_{\text{LANE}} = 6.66$  ns.

Integrating such a large capacitance may result in exceeding the area budget as it will most likely dominate the converter area [9]. This example clearly shows that while the CR-DAC is a very area-efficient topology to implement DACs with very small LSB units and/or total DAC capacitance, it becomes less area effective to implement large DACs where total capacitance is dominated by kT/C noise requirements.

#### 2.5 Charge-Sharing SAR-DAC