Julian M. Kunkel · Rio Yokota Pavan Balaji · David Keyes (Eds.)

# LNCS 10266

# High Performance Computing

32nd International Conference, ISC High Performance 2017 Frankfurt, Germany, June 18–22, 2017 Proceedings

#### Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany

#### 10266

More information about this series at http://www.springer.com/series/7407

Julian M. Kunkel · Rio Yokota Pavan Balaji · David Keyes (Eds.)

## High Performance Computing

32nd International Conference, ISC High Performance 2017 Frankfurt, Germany, June 18–22, 2017 Proceedings

*Editors* Julian M. Kunkel Deutsches Klimarechenzentrum (DKRZ) Hamburg Germany

Rio Yokota Tokyo Institute of Technology Tokyo Japan Pavan Balaji Argonne National Laboratory Argonne, IL USA

David Keyes KAUST Thuwal Saudi Arabia

ISSN 0302-9743

ISSN 1611-3349

(electronic)

Lecture Notes in Computer Science

ISBN 978-3-319-58666-3

ISBN 978-3-319-58667-0

(eBook)

DOI 10.1007/978-3-319-58667-0

ISBN 978-3-319-58667-0

ISBN 978-3-319-58667-0

ISBN 978-3-319-58667-0

Library of Congress Control Number: 2017939120

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

ISC High Performance, formerly known as the International Supercomputing Conference, was founded in 1986 as the Supercomputer Seminar. Originally organized by Hans Meuer, Professor of Computer Science at the University of Mannheim and former director of the computer center, the seminar brought together a group of 81 scientists and industrial partners who all shared an interest in high-performance computing (HPC). Since then the annual conference has become a major international event within the HPC community, and accompanying its growth in size over the years, the conference has moved from Mannheim via Heidelberg, Dresden, Hamburg, and Leipzig to Frankfurt. With over 3,000 attendees in 2016, we were happy to see that this steady growth of interest also turned ISC High Performance 2017 into a powerful and memorable event.

In 2007, we decided to strengthen the scientific part of the conference by presenting selected talks on relevant research results within the HPC field. These research paper sessions began as a separate day preceding the conference, where slides and accompanying papers were made available via the conference website. The research paper sessions have since evolved into an integral part of the conference, and this year the scientific presentations took place over a period of three days.

For the past several years, the ISC High Performance conference has presented an ISC-sponsored award to encourage outstanding research in HPC and to honor the overall best research paper submitted to the conference. Two years ago, this annual award was renamed as the Hans Meuer Award in memory of the late Dr. Hans Meuer, general chair of the ISC conference from 1986 through 2014, and co-founder of the TOP500 project. From all research papers submitted, the Research Papers Program Committee nominated the two papers with the highest review scores as finalists for the award and, based on the final presentations during the conference, elected the best paper.

For ISC High Performance 2017, the call for participation was issued in Fall 2016, inviting researchers and developers to submit the latest results of their work to the Program Committee. In all, 66 papers were submitted from authors all over the world. This year, too, a significant effort was made to improve the overall process. The Research Papers Program committee consisted of 52 members selected from several countries throughout the world. Furthermore, 23 external expert reviewers were invited from the community to help with paper reviews of specific topics. After initial reviews were in place, a rebuttal process was organized in which authors were given an opportunity to respond to reviewers' questions and help clarify issues the reviewers might have. To come to a final consensus on the papers to be accepted, we had a face-to-face meeting where each paper was discussed. Finally, the committee selected 22 papers for publication and for presentation in the research paper sessions.

We are pleased to announce that many fascinating topics in HPC are covered by the proceedings. The papers address the following issues in regards to the development of an environment for exascale supercomputers:

- Cost-efficient data centers

- Scalable applications

- Advancements in algorithms

- Scientific libraries

- Programming models

- Architectures

- Performance models and analysis

- Automatic performance optimization

- Parallel I/O

- Energy efficiency

We believe that this selection is highly appealing across a number of specializations. Two award committees selected papers considered to be of exceptional quality and worthy of special recognition:

The Hans Meuer Award honors the overall best research paper submitted to the conference. The two finalists for this award were:

"Designing Dynamic and Adaptive MPI Point-to-point Communication Protocols for Efficient Overlap of Computation and Communication" by Sourav Chakraborty, Hari Subramoni, and Dhabaleswar Panda.

"An Overview of MPI Characteristics of Exascale Proxy Applications" by Benjamin Klenk and Holger Fröning.

The Gauss Centre for Supercomputing sponsors the Gauss Award. This award is assigned to the most outstanding paper in the field of scalable supercomputing and went to:

"Diagnosing Performance Variations in HPC Applications Using Machine Learning" by Ozan Tuncer, Emre Ates, Yijia Zhang, Ata Turk, Jim Brandt, Vitus J. Leung, and Manuel Egele.

We would like to express our gratitude to all our colleagues for submitting papers to the ISC scientific sessions, as well as to the members of the Program Committee for organizing this year's attractive program.

June 2016

Julian M. Kunkel Rio Yokota Pavan Balaji David Keyes

#### Organization

#### **Research Papers Program Committee**

#### **Research Paper Chair and Deputy Chair**

| Pavan Balaji | Argonne National Laboratory, USA |

|--------------|----------------------------------|

| David Keyes  | KAUST, Saudi Arabia              |

#### **Architectures and Networks**

| Hans Eberle      | NVIDIA, USA                                |

|------------------|--------------------------------------------|

| Holger Fröning   | University of Heidelberg, Germany          |

| Pedro Garcia     | University of Castilla-La Mancha, Spain    |

| Wolfgang Karl    | Karlsruhe Institute of Technology, Germany |

| Sébastien Rumley | Columbia University, USA                   |

| Federico Silla   | Technical University of Valencia, Spain    |

| Tor Skeie        | Simula Labs and University of Oslo, Norway |

| Carsten Trinitis | TU München, Germany                        |

| Peter Ziegenhein | Institute of Cancer Research, UK           |

#### **Applications and Algorithms**

| Ilkay Altintas       | San Diego Supercomputing Center, USA                  |

|----------------------|-------------------------------------------------------|

| Yuefan Deng          | Stony Brook University, USA                           |

| Vassil Dimitrov      | University of Calgary, Canada                         |

| Jacek Kitowski       | AGH University of Science and Technology, Poland      |

| Scott Klasky         | Oak Ridge National Laboratory, USA                    |

| Axel Klawonn         | Universität zu Köln, Germany                          |

| Marek Michalewicz    | ICM, University of Warsaw, Poland                     |

| Gabriel Noaje        | HPE-SGI, Singapore                                    |

| Lena Oden            | Argonne National Laboratory, USA                      |

| Ulrich Rüde          | Friedrich-Alexander University of Erlangen-Nuremberg, |

|                      | Germany                                               |

| Sven-Bodo Scholz     | Heriot-Watt University Edinburgh, UK                  |

| Thomas Sterling      | Indiana University, USA                               |

| Antonio Tumeo        | Pacific Northwest National Laboratory, USA            |

| Marian Vajtersic     | University of Salzburg, Austria                       |

| Ana Lucia Varbanescu | University of Amsterdam, The Netherlands              |

| Priya Vashishta      | University of Southern California, USA                |

#### Data, Storage and Visualization

| Thomas Bönisch | High Performance Computing Center Stuttgart, Germany |

|----------------|------------------------------------------------------|

| Mahdi Bohlouli | University of Siegen, Germany                        |

| Luc Bougé          | ENS Rennes, France                            |

|--------------------|-----------------------------------------------|

| André Brinkmann    | Johannes Gutenberg-Universität Mainz, Germany |

| Matthieu Dorier    | Argonne National Laboratory, USA              |

| Steffen Frey       | University of Stuttgart, Germany              |

| Dean Hildebrand    | IBM, USA                                      |

| Hideyuki Kawashima | University of Tsukuba, Japan                  |

| Jay Lofstead       | Sandia National Laboratory, USA               |

| Kathryn Mohror     | Lawrence Livermore National Laboratory, USA   |

| Maria S. Perez     | Universidad Politecnica de Madrid, Spain      |

| Judy Qiu           | Indiana University, USA                       |

| Shinji Sumimoto    | Fujitsu, Japan                                |

| Ryousei Takano     | AIST, Japan                                   |

| Osamu Tatebe       | University of Tsukuba, Japan                  |

#### Programming Models and Systems Software

| Abdelhalim Amer       | Argonne National Laboratory, USA            |

|-----------------------|---------------------------------------------|

| Sunita Chandrasekaran | University of Delaware, USA                 |

| Adrian Jackson        | EPCC, UK                                    |

| Guido Juckeland       | HZDR, Germany                               |

| Michael Klemm         | Intel, Germany                              |

| Arthur Barney Maccabe | Oak Ridge National Laboratory, USA          |

| Naoya Maruyama        | RIKEN AICS, Japan                           |

| Simon McIntosh-Smith  | University of Bristol, UK                   |

| C.J. Newburn          | NVIDIA, USA                                 |

| Will Sawyer           | CSCS, Switzerland                           |

| Sangmin Seo           | Argonne National Laboratory, USA            |

| Martin Schulz         | Lawrence Livermore National Laboratory, USA |

| Michela Taufer        | University of Delaware, USA                 |

| Christian Terboven    | RWTH Aachen University, Germany             |

| Sandra Wienke         | RWTH Aachen University, Germany             |

#### **PHD Forum Program Committee**

| Florina Ciorba       | University of Basel, Switzerland                        |

|----------------------|---------------------------------------------------------|

| Anshu Dubey          | Argonne National Laboratory, USA                        |

| Anne Elster          | Norwegian University of Science and Technology,         |

|                      | Norway                                                  |

| Fernanda Foertter    | Oak Ridge National Laboratory, USA                      |

| William Gropp        | University of Illinois at Urbana-Champaign, USA (Chair) |

| Paul Kelly           | Imperial College London, UK                             |

| Lois Curfman McInnes | Argonne National Laboratory, USA                        |

| Miriam Mehl          | Universität Stuttgart, Germany                          |

| Kengo Nakajima       | University of Tokyo, Japan                              |

| Boyana Norris        | University of Oregon, USA                               |

| Amanda Randles       | Duke University, USA                                    |

| Olaf Schenk          | Università della Svizzera Italiana, Switzerland    |

|----------------------|----------------------------------------------------|

| Ana Lucia Varbanescu | University of Amsterdam, The Netherlands           |

| Richard Vuduc        | Georgia Institute of Technology, USA               |

| Gerhard Wellein      | Friedrich-Alexander University Erlangen-Nuremberg, |

|                      | Germany (Deputy Chair)                             |

| Felix Wolf           | Technische Universität Darmstadt, Germany          |

| Roman Wyrzykowski    | Czestochowa University of Technology, Poland       |

#### **Research Posters Program Committee**

| Alvaro Aguilera       | Technische Universität Dresden, Germany              |

|-----------------------|------------------------------------------------------|

| Thomas Bönisch        | High Performance Computing Center Stuttgart, Germany |

| Sunita Chandrasekaran | University of Delaware, USA                          |

| Andy Herdman          | AWE, UK                                              |

| Julian Kunkel         | Deutsches Klimarechenzentrum, Germany                |

| Simon McIntosh-Smith  | University of Bristol, UK                            |

| Jaejin Lee            | Seoul National University, South Korea               |

| Marek Michalewicz     | ICM, University of Warsaw, Poland                    |

| Matthias Müller       | RWTH Aachen University, Germany (Deputy Chair)       |

| Neil Stringfellow     | iVEC, Australia                                      |

| Jeffrey Vetter        | Oak Ridge National Laboratory, USA (Chair)           |

| Vladimir Voevodin     | Moscow State University, Russia                      |

| Rich Vuduc            | Georgia Institute of Technology, USA                 |

#### **Project Posters Program Committee**

| Alvaro Aguilera     | Technische Universität Dresden, Germany                |

|---------------------|--------------------------------------------------------|

| Yevhen Alforov      | Deutsches Klimarechenzentrum, Germany                  |

| Eugen Betke         | Deutsches Klimarechenzentrum, Germany                  |

| Ramaswamy           | SERC, India                                            |

| Govindarajan        |                                                        |

| David Ham           | Imperial College London, UK                            |

| Weicheng Huang      | National Center for High-Performance Computing, Taiwan |

| Nabeeh Jumah        | University of Hamburg, Germany                         |

| Oleksiy Koshulko    | Glushkov Institute of Cybernetics of NASU, Russia      |

| Michael Kuhn        | University of Hamburg, Germany                         |

| Julian Kunkel       | Deutsches Klimarechenzentrum, Germany (Chair)          |

| Fang-Pang Lin       | National Center for High-Performance Computing, Taiwan |

| Jakob Lüttgau       | Deutsches Klimarechenzentrum, Germany                  |

| Anastasiia Novikova | University of Hamburg, Germany                         |

| Yuichi Tsujita      | RIKEN AICS, Japan                                      |

| Ying Qian           | East China Normal University, China                    |

| Rio Yokota          | Tokyo Institute of Technology, Japan                   |

#### **Tutorials Committee**

| Rosa M. Badia    | Barcelona Supercomputing Center, Spain (Deputy Chair) |

|------------------|-------------------------------------------------------|

| Pavan Balaji     | Argonne National Laboratory, USA                      |

| James Dinan      | Intel, USA                                            |

| Adrian Jackson   | EPCC, The University of Edinburgh, UK                 |

| Alice Koniges    | Lawrence Berkeley National Laboratory, USA            |

| Erwin Laure      | Royal Institute of Technology, Sweden                 |

| Christian Perez  | Inria, France                                         |

| Enrique Quintana | Universidad Jaime I, Spain                            |

| Adrian Tate      | Cray, USA                                             |

| Michèle Weiland  | EPCC, The University of Edinburgh, UK (Chair)         |

#### **BoFs Committee**

| David Bader            | Georgia Institute of Technology, USA                  |

|------------------------|-------------------------------------------------------|

| Toni Collis            | EPCC, University of Edinburgh, UK                     |

| Dona Crawford          | Lawrence Livermore National Laboratory, USA (Chair)   |

| Ewa Deelman            | University of Southern California, USA                |

| Alba Dieguez Alonso    | Technische Universität Berlin, Germany                |

| Fernanda Foertter      | Oak Ridge National Laboratory, USA                    |

| Horst Gietl            | ISC Group, Germany                                    |

| Gerard Gorman          | Imperial College London, UK                           |

| Georg Hager            | University Erlangen-Nuremberg, Germany (Deputy Chair) |

| Peter Kogge            | University of Notre Dame, USA                         |

| Bernd Mohr             | Jülich Supercomputing Centre, Germany                 |

| Kathryn Mohror         | Lawrence Livermore National Laboratory, USA           |

| Kengo Nakajima         | University of Tokyo, Japan                            |

| Marie-Christine Sawley | Intel, France                                         |

| Martin Schulz          | Lawrence Livermore National Laboratory, USA           |

| Happy Sithole          | Centre for High Performance Computing, South Africa   |

| Vladimir Voevodin      | Moscow State University, Russia                       |

| Heike Walther          | ISC Group, Germany                                    |

| Jan Wender             | science+computing, Germany                            |

| Andreas Wierse         | SICOS BW, Germany                                     |

| Roman Wyrzykowski      | Czestochowa University of Technology, Poland          |

#### Workshop Committee

| Rosa M. Badia         | Barcelona Supercomputing Center, Spain      |  |  |

|-----------------------|---------------------------------------------|--|--|

| François Bodin        | IRISA, France                               |  |  |

| Bronis R. de Supinski | Lawrence Livermore National Laboratory, USA |  |  |

| Jay Lofstead          | Sandia National Laboratories, USA           |  |  |

| Naoya Maruyama        | RIKEN, Japan                                |  |  |

| Simon McIntosh-Smith  | University of Bristol, UK                   |  |  |

| Bernd Mohr            | Jülich Supercomputing Centre, Germany       |  |  |

Marie-Christine Sawley Intel, France Seetharami Seelam IBM T.J. Watson Research Center, USA John Shalf Lawrence Berkeley National Laboratory, USA (Deputy Chair) University of Delaware, USA (Chair) Michela Taufer Technische Universität München, Germany Carsten Trinitis Antonino Tumeo Pacific Northwest National Laboratory, USA Didem Unat Koç Universitesi, Turkey Rio Yokota Tokyo Institute of Technology, Japan

#### Contents

#### **Applications and Algorithms**

| Fully Resolved Simulations of Dune Formation in Riverbeds<br>Christoph Rettinger, Christian Godenschwager, Sebastian Eibl,<br>Tobias Preclik, Tobias Schruff, Roy Frings, and Ulrich Rüde                | 3   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

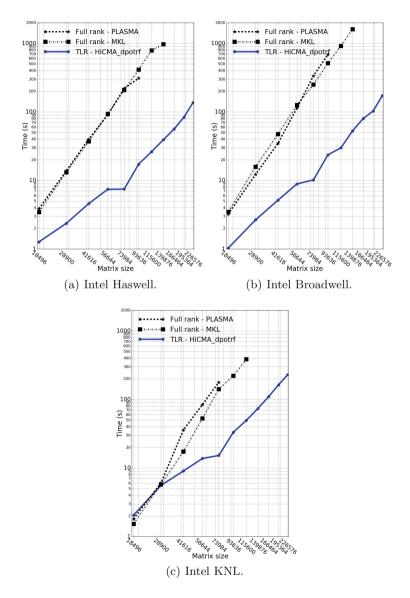

| Tile Low Rank Cholesky Factorization for Climate/Weather Modeling<br>Applications on Manycore Architectures                                                                                              | 22  |

| EDGE: Extreme Scale Fused Seismic Simulations with the Discontinuous<br>Galerkin Method<br>Alexander Breuer, Alexander Heinecke, and Yifeng Cui                                                          | 41  |

| LAMMPS' PPPM Long-Range Solver for the Second Generation Xeon Phi<br>William McDoniel, Markus Höhnerbach, Rodrigo Canales,<br>Ahmed E. Ismail, and Paolo Bientinesi                                      | 61  |

| Communication Reducing Algorithms for Distributed Hierarchical N-Body<br>Problems with Boundary Distributions<br>Mustafa Abduljabbar, George S. Markomanolis, Huda Ibeid,<br>Rio Yokota, and David Keyes | 79  |

| EvoGraph: On-the-Fly Efficient Mining of Evolving Graphs on GPU<br>Dipanjan Sengupta and Shuaiwen Leon Song                                                                                              | 97  |

| High-Performance Incremental SVM Learning<br>on Intel <sup>®</sup> Xeon Phi <sup>™</sup> Processors                                                                                                      | 120 |

| Accelerating Seismic Simulations Using the Intel Xeon Phi Knights<br>Landing Processor<br>Josh Tobin, Alexander Breuer, Alexander Heinecke, Charles Yount,<br>and Yifeng Cui                             | 139 |

| A Framework for Out of Memory SVD Algorithms                                                                                                                                                             | 158 |

#### **Proxy Applications**

| Neuromapp: A Mini-application Framework to Improve Neural Simulators<br>Timothée Ewart, Judit Planas, Francesco Cremonesi, Kai Langen,<br>Felix Schürmann, and Fabien Delalondre |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

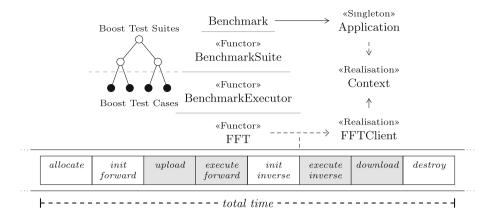

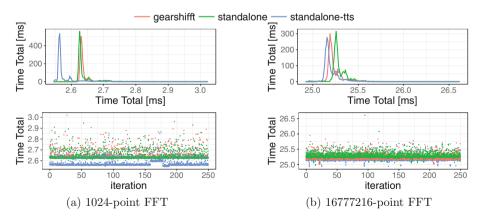

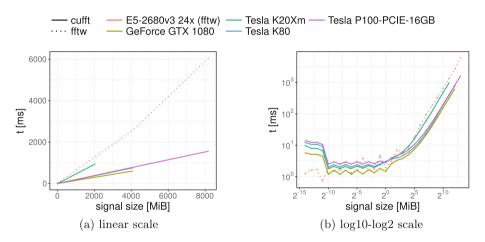

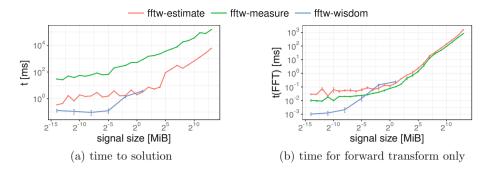

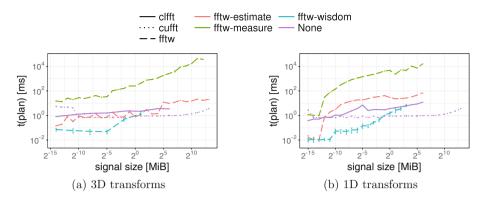

| gearshift – The FFT Benchmark Suite for Heterogeneous Platforms Peter Steinbach and Matthias Werner                                                                              | 199 |

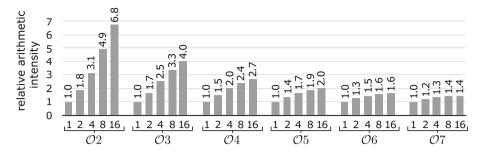

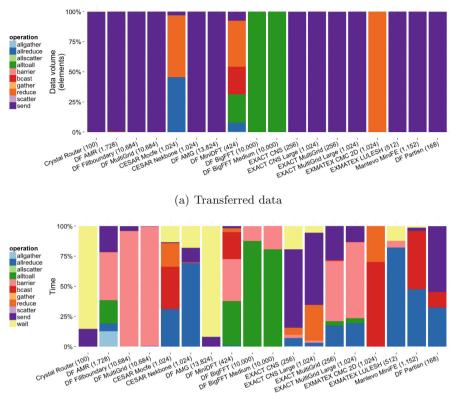

| An Overview of MPI Characteristics of Exascale Proxy Applications<br>Benjamin Klenk and Holger Fröning                                                                           | 217 |

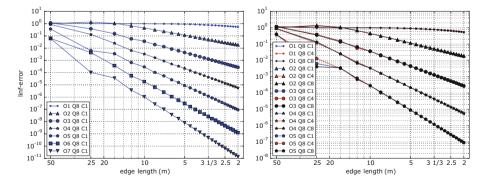

| Fast Matrix-Free Discontinuous Galerkin Kernels on Modern<br>Computer Architectures                                                                                              | 237 |

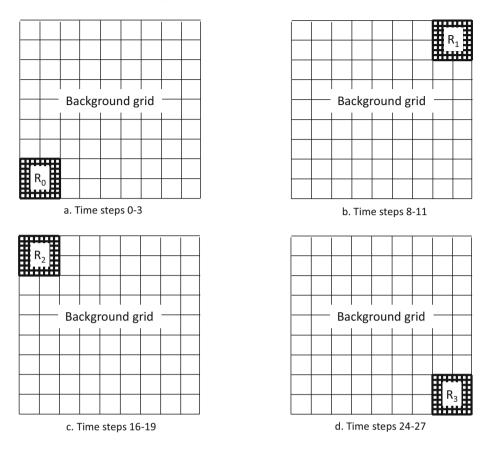

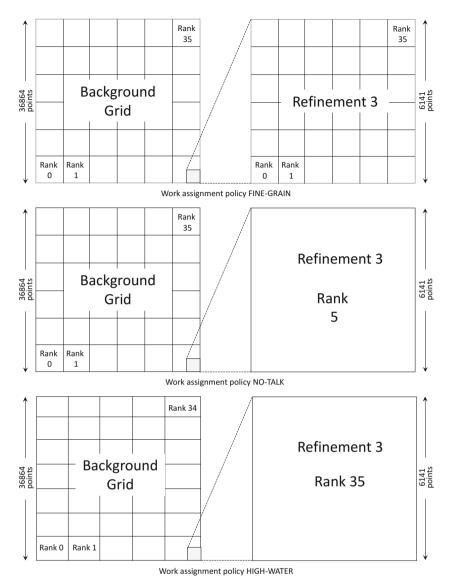

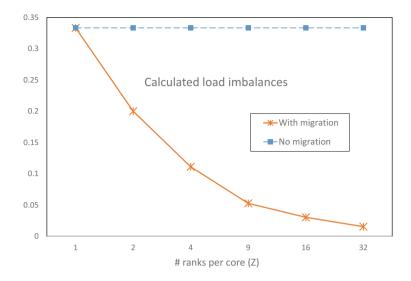

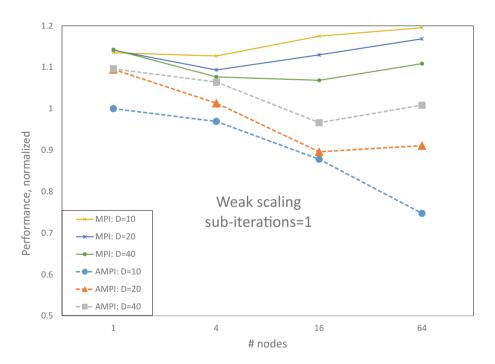

| A New Parallel Research Kernel to Expand Research on Dynamic<br>Load-Balancing Capabilities                                                                                      | 256 |

#### Architecture and System Optimization

| Extreme Event Analysis in Next Generation Simulation Architectures Stephen Hamilton, Randal Burns, Charles Meneveau, Perry Johnson, Peter Lindstrom, John Patchett, and Alexander S. Szalay                              |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An Analysis of Core- and Chip-Level Architectural Features<br>in Four Generations of Intel Server Processors<br>Johannes Hofmann, Georg Hager, Gerhard Wellein, and Dietmar Fey                                          | 294 |

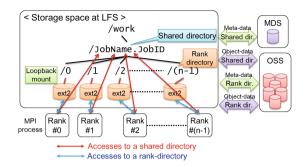

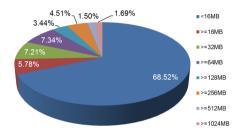

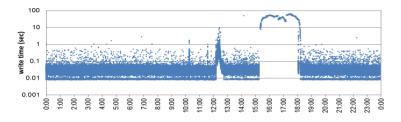

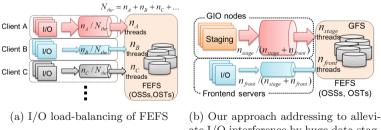

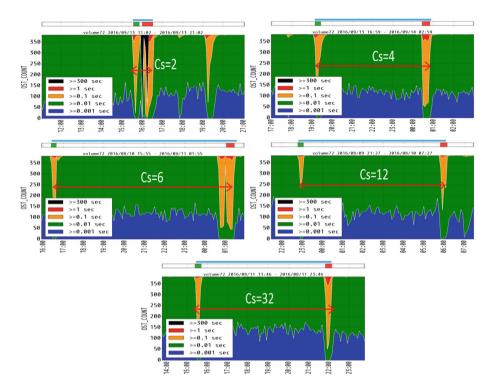

| Alleviating I/O Interference Through Workload-Aware Striping<br>and Load-Balancing on Parallel File Systems<br>Yuichi Tsujita, Tatsuhiko Yoshizaki, Keiji Yamamoto,<br>Fumichika Sueyasu, Ryoji Miyazaki, and Atsuya Uno | 315 |

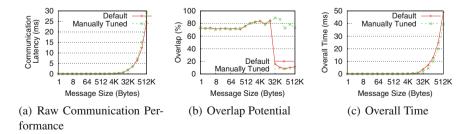

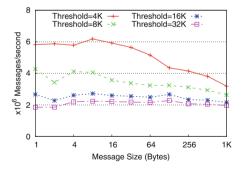

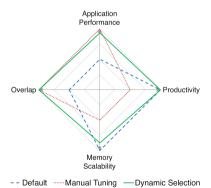

| Designing Dynamic and Adaptive MPI Point-to-Point Communication<br>Protocols for Efficient Overlap of Computation and Communication<br><i>Hari Subramoni, Sourav Chakraborty, and Dhabaleswar K. Panda</i>               | 334 |

| Diagnosing Performance Variations in HPC Applications<br>Using Machine Learning                                                                                                                                          | 355 |

#### **Energy-Aware Computing**

| The Investigation of the ARMv7 and Intel Haswell Architectures Suitability |     |

|----------------------------------------------------------------------------|-----|

| for Performance and Energy-Aware Computing                                 | 377 |

| Vojtech Nikl, Michal Hradecky, Jakub Keleceni, and Jiri Jaros              |     |

| Global Extensible Open Power Manager: A Vehicle for HPC Community          |     |

| Collaboration on Co-Designed Energy Management Solutions                   | 394 |

| Jonathan Eastep, Steve Sylvester, Christopher Cantalupo, Brad Geltz,       |     |

| Federico Ardanaz, Asma Al-Rawi, Kelly Livingston, Fuat Keceli,             |     |

| Matthias Maiterth, and Siddhartha Jana                                     |     |

| Metrics for Energy-Aware Software Optimisation                             | 413 |

| Stephen I. Roberts, Steven A. Wright, Suhaib A. Fahmy,                     |     |

| and Stephen A. Jarvis                                                      |     |

| Author Index                                                               | 431 |

|                                                                            |     |

### **Applications and Algorithms**

#### Fully Resolved Simulations of Dune Formation in Riverbeds

Christoph Rettinger<sup>1(⊠)</sup>, Christian Godenschwager<sup>1</sup>, Sebastian Eibl<sup>1</sup>, Tobias Preclik<sup>1</sup>, Tobias Schruff<sup>2</sup>, Roy Frings<sup>2</sup>, and Ulrich Rüde<sup>1</sup>

<sup>1</sup> Chair for System Simulation, Friedrich-Alexander-Universität Erlangen-Nürnberg, Cauerstraße 11, 91058 Erlangen, Germany christoph.rettinger@fau.de

<sup>2</sup> Institute of Hydraulic Engineering and Water Resources Management, RWTH Aachen University, Mies-van-der-Rohe-Straße 17, 52056 Aachen, Germany

Abstract. The formation and dynamics of dunes is an important phenomenon that occurs in many environmental systems, such as riverbeds. The physical interactions are complex and thus evaluating and quantifying the factors of influence is challenging. Simulation models can be used to conduct large scale parameter studies and allow a more detailed analysis of the system than laboratory experiments. Here, we present new coupled numerical models for sediment transport that are based on first principles. The lattice Boltzmann method is used in combination with a non-smooth granular dynamics model to simulate the fluid flow and the sediment particles. Numerical predictions of dune formation require a fully resolved modeling of the particulate flow which is only achieved by massively parallel simulations. For that purpose, the method employs advanced parallel grid refinement techniques and carefully designed compute kernels. The weak- and strong-scaling behavior is evaluated in detail and shows overall excellent parallel performance and efficiency.

**Keywords:** High performance computing  $\cdot$  Computational fluid dynamics  $\cdot$  Particulate flow  $\cdot$  Fluid structure interaction  $\cdot$  Dune formation  $\cdot$  Lattice Boltzmann method  $\cdot$  Granular dynamics  $\cdot$  Grid refinement

#### 1 Introduction

Sand dunes can be found in many different places on earth, for example in the great deserts of Kalahari, Gobi, Sahara, or at the seashore where sand dunes usually separate the sandy beaches from the hinterland. They are by no means static *topographic features* but their shape changes constantly due to the forces of wind. In fact, depending on their height and volume (some sand dunes have a height of more than 1,000 meters), constant and strong wind can move dunes some tens of meters per year [3]. Large sand dunes have also been found on planet Mars [21], Titan [32], and other planets where strong winds are able to *erode and transport* enormous amounts of sand on the planet surface. But besides wind there is also another universal power that is able to model the shape of planets, and that is *flowing water*.

<sup>©</sup> Springer International Publishing AG 2017

J.M. Kunkel et al. (Eds.): ISC High Performance 2017, LNCS 10266, pp. 3–21, 2017. DOI: 10.1007/978-3-319-58667-0\_1

Due to its high specific weight, flowing water is able to carry not only sand, but also boulders and gravel, collectively also referred to as *sediment* [7,36,46], for many kilometers; often the whole way from the source of a river to its mouth. On its way down along the path of the river or channel, the sediment grain size decreases, starting with large boulders and gravel at the source and ending up with small silt and clay grains at the mouth [13,15]. Somewhere in between, most sediment grains have the size of sand, which is defined to be in the range of 0.063-2.0 mm. If the major part of the sediment mixture is sand, the sediment transport can take place in form of sand dunes that move over the bed [25,28,44].

Those subaqueous dunes can become many meters high depending on the water depth and flow conditions [14, 24] and thus act as obstacles to navigation, and their movement can be a threat to submarine structures. River engineers are interested in dunes because they play an important role in determining the sediment transport rate [44], but also because of their importance in quantifying the resistance of a channel to flowing water [41]. For example, predicting the depth of flow in a channel built with a given slope and designed to carry a given water discharge necessitates knowing the bed roughness.

For over one century, engineers have been conducting laboratory experiments on dunes and other bed forms [44, 46]. Another famous method was (and still is!) observing and measuring bed form movement in natural flows [9, 16, 33]. Both methods come with their individual advantages and disadvantages. Despite significant progress in the past 25 years with regard to the understanding of the dynamics and kinematics of alluvial dunes, there are still some important areas where conventional methods have not been able to comprehensively shed light into the complex nature of dunes [6].

This is why engineers, geologists, sedimentologists, and other researchers are increasingly interested in applying high performance computing (HPC) methods to investigate sediment transport and dunes numerically [26,27]. Such approaches are especially helpful to drive the study of dune formation regarding four specific areas: (1) the influence of dune shape on flow turbulence and distribution of bed shear stress, (2) flow field modification resulting from bed form superimposition and amalgamation, (3) the scale and topology of dunerelated turbulence and its interactions with sediment transport and the flow surface, and (4) the influence of oscillatory and combined flows, e.g., in marine environments, on dune formation. Simulations have several favorable features in comparison to laboratory experiments. Once set up and validated, they allow for large scale studies where single parameters can be adjusted with ease. By tracing the motion of single particles and analyzing the flow field within the sediment bed, a better insight into the physical processes can be obtained.

However, the challenges for a realistic simulation from first principles, i.e., without introducing empirical model assumptions, are numerous: On the one hand, a large enough setup has to be regarded containing several hundred thousand sediment grains. On the other hand, the developing flow structures have to be numerically fully resolved and this may require that each single sediment grain, their variation in size and shape, must be geometrically resolved. This, in

turn, dictates an even finer resolution of the fluid flow, when its interaction with the individual particles must be accounted for. This kind of direct numerical simulation can only be tackled by a combination of efficient numerical algorithms together with the computing power of today's fastest super computers. To fully utilize their capabilities, we employ two coupled software frameworks that offer both, carefully tuned single-node performance and excellent scalability. The WALBERLA framework [18] has been developed for simulating complex flows with the lattice Boltzmann method and has been employed in various application scenarios, such as electron beam melting [2], solidification processes [5], or electro-kinetic flows [4,29]. The physics engine pe [23,38] is used to simulate granular dynamics. The flow over fully resolved porous structures has already been simulated in [11,12], however, assuming a fixed and immobile particle bed. The coupling algorithms for moving particles in a massively parallel setting are based on the methods developed in [19,20,40].

Following this work, we will here extend the functionality of WALBERLA and the coupling mechanism with the pe. We enable grid refinement for the coupled simulation to reduce computational burden in the computational fluid dynamics code. Additionally, we employ a hard contact solver in the granular dynamics code which eliminates particle overlaps and requires no fine temporal resolution of the contact dynamics. To analyze the central aspect of our parallelization strategy, i.e., the use of a co-partitioning between our two frameworks, we conduct a thorough performance study of this approach in the context of HPC and supercomputers. This extends the work reported in [26, 27], where direct numerical simulations were used to study pattern formation of large sediment beds for the first time. We describe the physical background of the application in Sect. 2 which results in an experimental setup well suited for numerical simulations. The applied numerical methods are presented in Sects. 3.1–3.3. Details about their implementation and the parallelization strategy are given in Sect. 4. In Sect. 5, the outcome of a large scale simulation is discussed and both, weak and strong, scaling behaviors are reported. Section 6 concludes the paper with a summary of the main findings and an outlook of future research directions.

#### 2 Physical Background

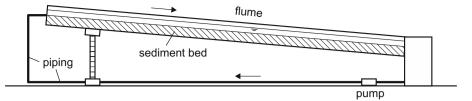

When studying bed forms produced by unidirectional (steady and uniform) flow of water over a sand bed in a laboratory experiment, it is common to use a flume setup like the one illustrated in Fig. 1. The flume has a rectangular cross section with a width of about one meter and is open at the top. The length of the flume is about a few tens of a meter. It is also possible to adjust the slope of the flume, which is why this kind of setup is called *tilting flume*. The sediment bed in our example consists of medium size sand (0.25–0.5 mm) and is planar at the beginning. The pump controls the mean flow velocity and the slope of the flume is adjusted to obtain a constant mean flow depth.

When continuously increasing the flow velocity for a given setup, different bed forms can be observed as depicted in Fig. 2. Besides dunes, ripples and antidunes

Fig. 1. Laboratory flume for studying bed forms produced by unidirectional flow.

**Fig. 2.** Evolution of bed forms as a function of flow velocity at a given flow depth and bed material: (1) initial plane bed, (2) ripples, (3) dunes, (4), planar bed, and (5) antidunes.

are other types of bed forms that frequently occur in natural rivers and predicting their formation still remains a challenging task even at laboratory scales. The complexity mainly stems from the large number of influence factors. Apart from the mean flow rate, the sediment size and the flow depth will affect the transition and evolution of bed configurations. Other parameters are the density of the fluid and of the sediment grains, the fluid viscosity, and the gravitational acceleration.

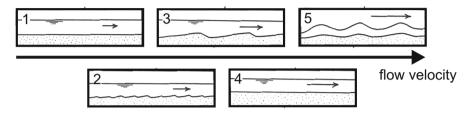

When attempting to simulate such a setup numerically, however, the free flow surface imposes a degree of complexity to the system which can be avoided by slightly changing the setup. Figure 3 illustrates the alternative setup where the flow depth is doubled and the whole flume is covered with a solid plate, parallel to the mean plane of the bed. The flow structure in the lower half of the closed duct is nearly the same as in the original open-channel flow. The sediment

Fig. 3. Schematic setup of numerical flow simulation for the study of dune formation.

dynamics is thus expected to be similar as long as the effect of the free surface can be neglected. This is the case for all bed forms shown in Fig. 2 except for antidunes which necessitate the free surface. The advantage of a setup like this is that the slope of the channel does not need to be adjusted, as the water depth is fixed. This also has a positive effect on the behavior of the sediment bed, as we do not alter the angle at which gravity forces act on grains. From a simulation point of view, the stability is increased as large-scale eddies can now make their way across the center plane of the flow.

The foregoing setup can be used to study the transition between different bed configurations (ripples, dunes, etc.) or how dune height or length are affected by the several parameters (e.g., grain size, water depth, flow velocity, etc.) in numerical simulations.

#### 3 Numerical Methods

#### 3.1 Lattice Boltzmann Method

The lattice Boltzmann method (LBM) [8] is an alternative to conventional computational fluid dynamics (CFD) methods to simulate hydrodynamics, classically described by the Navier-Stokes equations. It originates from statistical mechanics and models the evolution of particle distribution functions (PDFs) on a Cartesian grid. Its high locality, as it requires direct neighbor access only, leads to an outstanding scaling behavior up to the full extent of current peta-scale supercomputers [18,22].

In this work, we apply the D3Q19 lattice model [39] which features 19 PDFs  $f_q, q \in \{0...18\}$ , where each is associated to a three-dimensional discrete lattice velocity  $c_q$ . The computational domain is discretized by cubic lattice cells with cell centers  $\boldsymbol{x}$ . Written in a general form, the lattice Boltzmann equation is commonly subdivided into the *collision* step

$$\tilde{f}_q(\boldsymbol{x}) = f_q(\boldsymbol{x}) + \Omega_q(\boldsymbol{x}) + S_q, \tag{1}$$

with the collision operator  $\Omega_q$  and a source term  $S_q$  resulting in the post-collision values  $\tilde{f}_q$ . Succeeding, the *streaming* of the PDFs to their neighboring lattice cells

$$f'_q(\boldsymbol{x} + \boldsymbol{c}_q) = \tilde{f}_q(\boldsymbol{x}) \tag{2}$$

is carried out to obtain the PDFs at the new time step  $f'_q$ .

The collision operator relaxes the PDFs towards their equilibrium values,

$$f_q^{\text{eq}}(\rho_f, \boldsymbol{u}) = w_q \left( \rho_f + \rho_0 \left( 3\boldsymbol{c}_q \cdot \boldsymbol{u} + \frac{9}{2} (\boldsymbol{c}_q \cdot \boldsymbol{u})^2 - \frac{3}{2} \boldsymbol{u} \cdot \boldsymbol{u} \right) \right).$$

(3)

The macroscopic quantities, density  $\rho_f = \rho_0 + \delta \rho_f$ , with a mean density  $\rho_0$  and a fluctuation  $\delta \rho_f$ , and fluid velocity  $\boldsymbol{u}$ , are obtained as moments of the PDFs in each grid cell. The lattice weights  $w_q$  are stated in [39].

In particular, we make use of the TRT collision operator from [17] which splits the PDFs and their equilibrium values into symmetric and anti-symmetric parts:

$$f_q^{\pm} = \frac{1}{2}(f_q \pm f_{\bar{q}}), \quad f_q^{\mathrm{eq},\pm} = \frac{1}{2}(f_q^{\mathrm{eq}} \pm f_{\bar{q}}^{\mathrm{eq}}),$$

(4)

where  $\bar{q}$  is the opposite lattice direction of q, such that  $c_{\bar{q}} = -c_q$ . The collision operator is then given as

$$\Omega_{q}^{\text{TRT}}(\boldsymbol{x}) = -\frac{1}{\tau_{+}} \left( f_{q}^{+}(\boldsymbol{x}) - f_{q}^{\text{eq},+}(\rho_{f},\boldsymbol{u}) \right) - \frac{1}{\tau_{-}} \left( f_{q}^{-}(\boldsymbol{x}) - f_{q}^{\text{eq},-}(\rho_{f},\boldsymbol{u}) \right).$$

(5)

This model features two relaxation times  $\tau_+, \tau_- \in (\frac{1}{2}; \infty)$ , here related via  $(\frac{1}{2} - \tau_+)(\frac{1}{2} - \tau_-) = \frac{3}{16}$  for improved accuracy [17]. The kinematic viscosity of the fluid can be obtained as  $\nu = \frac{1}{3}(\tau_+ - \frac{1}{2})$ .

To incorporate external forcing that can drive the flow, the source term

$$S_q = 3w_q \rho_0 \left( \boldsymbol{c}_q - \boldsymbol{u} + 3(\boldsymbol{c}_q \cdot \boldsymbol{u}) \boldsymbol{c}_q \right) \cdot \boldsymbol{a}$$

(6)

with the external fluid acceleration a has to be added to Eq. (1) [34].

Recently, LBM variants have been proposed that allow non-uniform grids to enable static and adaptive grid refinement. We employ the variant from [42] which adjusts the relaxation parameters on each grid level and executes twice the amount of LBM steps for each finer level.

#### 3.2 Non-smooth Granular Dynamics

In contrast to the field of fluid dynamics, no equations exist that can accurately describe the bulk behavior of granular matter [35]. Thus, to simulate the response of the sediment bed to the fluid flow, we resolve individual grains including their geometric shape. Each particle is described by position X, orientation Q, translational and rotational velocity V and W. The orientation is parameterized by a quaternion. We restrict ourselves to spherical particles meaning each shape can be simply described by its radius. Under the assumption of uniformly distributed mass, the density then determines the particle mass m and moment of inertia I. The Newton-Euler equations for rigid bodies describe the dynamics of the individual particles given forces F and torques T. The contact model determines the forces and torques arising from contacts between the grains in addition to external forces and torques  $F^{\text{ext}}$  and  $T^{\text{ext}}$ . With the intention to reproduce the stiffness of the collision micro-dynamics as accurately as possible we choose an inelastic hard contact model, where the particles would not overlap in an exact solution and thus leading to a better representation of the solid volume fraction than the commonly applied discrete element method (DEM). The hard contact model implies that velocity functions are discontinuous and position and orientation functions non-smooth. In order to get around resolving impulsive contact reactions in time, we discretize the continuous system by employing a timestepping scheme, where we consider integrals of contact reactions  $\lambda$  over small time steps  $\delta t$ , which readily include the impulsive and non-impulsive contact reactions [43]. The contact model includes Coulomb friction with a coefficient of friction  $\mu$  per contact. The time-stepping scheme is based on an integrator of order one resembling the semi-implicit Euler method. In each time step, the following non-linear system of equations is to be solved for each particle and contact, respectively:

$$\mathbf{X}' = \mathbf{X} + \delta t \mathbf{V}' \tag{7}$$

$$\mathbf{Q}' = \left(\mathbf{Q} + \delta t M(\mathbf{Q}) \mathbf{W}'\right) / \|\mathbf{Q} + \delta t M(\mathbf{Q}) \mathbf{W}'\|$$

(8)

$$\mathbf{V}' = \mathbf{V} + \delta t m^{-1} \mathbf{F} \tag{9}$$

$$\boldsymbol{W}' = \boldsymbol{W} + \delta t \boldsymbol{I}^{-1} \boldsymbol{T} \tag{10}$$

$$\boldsymbol{F} = \sum_{\mathcal{C}_a} \boldsymbol{\lambda} - \sum_{\mathcal{C}_b} \boldsymbol{\lambda} + \boldsymbol{F}^{\text{ext}}$$

(11)

$$\boldsymbol{T} = \sum_{\mathcal{C}_a} (\hat{\boldsymbol{X}} - \boldsymbol{X}_a) \times \boldsymbol{\lambda} - \sum_{\mathcal{C}_b} (\hat{\boldsymbol{X}} - \boldsymbol{X}_b) \times \boldsymbol{\lambda} + \boldsymbol{T}^{\text{ext}}$$

(12)

$$\delta \mathbf{V}' = \mathbf{V}_a' + \mathbf{W}_a' \times (\mathbf{X} - \mathbf{X}_a) - \mathbf{V}_b' - \mathbf{W}_b' \times (\mathbf{X} - \mathbf{X}_b)$$

(13)

$$\lambda_{n} \ge 0 \quad \perp \quad \varepsilon \min(\xi, 0) / \delta t + \max(\xi, 0) / \delta t + \delta V_{n}' \ge 0 \tag{14}$$

$$\|\boldsymbol{\lambda}_{\boldsymbol{to}}\| \le \mu \lambda_{\boldsymbol{n}} \tag{15}$$

$$\|\delta V_{to}'\|\lambda_{to} = -\mu \delta V_{to}' , \qquad (16)$$

where M is the quaternion matrix function, the subscript a (b) identifies the first (second) particle involved in each contact,  $C_a$  ( $C_b$ ) is the set of contacts whose first (second) particle involved in the contact corresponds to the particle in question,  $\hat{X}$  is the point of contact, n is the contact normal pointing from particle b to particle a, and t and o extend the normal to an orthonormal contact frame spanning the tangential plane.  $\xi$  is the contact distance and  $\varepsilon \in [0; 1]$  the error reduction parameter. Equation (14) ensures that contact reactions are repulsive and no penetrations are allowed. The complementarity allows reactions to be non-zero if and only if the contact is closed. Equations (15) and (16) correspond to the conditions imposed by the Coulomb friction. Instead of including all potential collision pairs in the system, a prior contact detection algorithm selects a set of contacts that potentially become active in the current time step and thus reduces the number of constraints to the same order as the number of particles. More details and the extension to non-spherical contact problems can be found in [37, 38].

The system is solved using a blend of a weighted non-linear block Jacobi and a weighted non-linear block Gauss-Seidel with weighting factor  $\omega \in (0; 1]$ . Whether the contact reaction approximation is chosen from the previous iterate or from the current iterate depends on whether the contact is owned by the local process or by a remote process. The parallelization details are described in Sect. 4. The contact constraints of each contact form a block in the relaxation scheme. Since the solver only efficiently removes local errors, the number of iterations is kept low and constant. In order to remove the global error we rely on the error correction term  $\varepsilon \min(\xi, 0)/\delta t$  in Eq. (14).

#### 3.3 Fluid-Particle Interaction

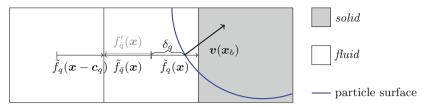

To incorporate the fluid-solid coupling mechanism that transfers the momentum from the fluid to the particulate phase and vice versa, the LBM-specific

Fig. 4. Sketch of the particle mapping and the boundary treatment according to the CLI boundary scheme from Eq. (17).

momentum exchange method is applied which originates from [30] and was then extended in [1]. The main idea is to explicitly map the particle into the computational domain by marking cells with cell centers inside particles as *solid* in contrast to *fluid* cells.

Next to the particle surface, the fluid velocity has to match the particle velocity which is realized via boundary conditions. Here, we use the central linear interpolation (CLI) scheme from [17], given by

$$f'_{\bar{q}}(\boldsymbol{x}) = \tilde{f}_{q}(\boldsymbol{x}) + \frac{1-2\delta_{q}}{1+2\delta_{q}} \left( \tilde{f}_{q}(\boldsymbol{x} - \boldsymbol{c}_{q}) - \tilde{f}_{\bar{q}}(\boldsymbol{x}) \right) - \frac{12 w_{q} \rho_{0}}{1+2\delta_{q}} \boldsymbol{v}(\boldsymbol{x}_{b}) \cdot \boldsymbol{c}_{q},$$

(17)

where  $\mathbf{v}(\mathbf{x}_b) = \mathbf{V} + \mathbf{W} \times (\mathbf{x}_b - \mathbf{X})$  is the particle velocity at the boundary location  $\mathbf{x}_b$ . The variable  $\delta_q$  denotes the relative distance between the cell center and the exact surface position such that  $\mathbf{x}_b = \mathbf{x} + \mathbf{c}_q \delta_q$ . This increases the accuracy of the boundary treatment as subgrid information is used to improve the staircase approximation of the particle shape. A sketch of this boundary treatment is given in Fig. 4.

The momentum exchange idea is applied to obtain the cell local contribution to the hydrodynamic interaction force that acts on the submerged particles. This contribution is given as

$$\boldsymbol{F}_{q}(\boldsymbol{x}_{b}) = \left(\boldsymbol{c}_{q} - \boldsymbol{v}(\boldsymbol{x}_{b})\right) \tilde{f}_{q}(\boldsymbol{x}) - \left(\boldsymbol{c}_{\bar{q}} - \boldsymbol{v}(\boldsymbol{x}_{b})\right) f'_{\bar{q}}(\boldsymbol{x})$$

(18)

for a fluid-solid link q [30,45]. By summing up all contributions corresponding to a single particle, the hydrodynamic force  $\mathbf{F}^{hyd}$  and torque  $\mathbf{T}^{hyd}$  are obtained:

$$\boldsymbol{F}^{\text{hyd}} = \sum \boldsymbol{F}_q(\boldsymbol{x}_b), \tag{19}$$

$$T^{\text{hyd}} = \sum (\boldsymbol{x}_b - \boldsymbol{X}) \times \boldsymbol{F}_q(\boldsymbol{x}_b).$$

(20)

These quantities, together with gravitational and buoyancy forces, represent the total external contributions,  $F^{\text{ext}}$  and  $T^{\text{ext}}$ , which enter Eqs. (11) and (12).

Due to the explicit mapping, cells will change its state from *solid* to *fluid* as particles move across the grid. This requires the reconstruction of the PDF information before the simulation can continue. Here, we initialize the PDFs of such a converted cell with their equilibrium values, Eq. (3), based on a spatially averaged density and the local particle velocity.

11

| Algorithm 1. Coupling algorithm for fluid-particle systems                     |  |  |  |  |

|--------------------------------------------------------------------------------|--|--|--|--|

| for each coarse time step $t$ do                                               |  |  |  |  |

| Map particle into fluid domain and reconstruct PDFs if necessary.              |  |  |  |  |

| for each LBM subcycle do                                                       |  |  |  |  |

| Apply boundary conditions, Eq. (17).                                           |  |  |  |  |

| Perform LBM step, Eqs. $(1)$ and $(2)$ with TRT collision operator Eq. $(5)$ . |  |  |  |  |

| Calculate hydrodynamic forces on particles, Eq. (18).                          |  |  |  |  |

| end for                                                                        |  |  |  |  |

| Average forces on particles over LBM subcycles.                                |  |  |  |  |

| Obtain total force and torque on particles, Eqs. $(19)$ and $(20)$ .           |  |  |  |  |

| for each granular dynamics solver subcycle do                                  |  |  |  |  |

| Perform granular dynamics solver step, solving Eqs. (7)-(16).                  |  |  |  |  |

| end for                                                                        |  |  |  |  |

| end for                                                                        |  |  |  |  |

All these parts are carried out locally and thus work well in combination with the LBM in massively parallel setups [19,20,40]. Because of the explicit particle mapping, the grid can remain unchanged throughout the whole simulation which guarantees computational efficiency.

The complete algorithm for fully resolved simulations of fluid-particle systems is summarized in Algorithm 1. Besides the already mentioned parts, it features possible subcycling for LBM and the granular dynamics solver, i.e., these parts are carried out multiple times in one global time step. Using two LBM subcycles was proposed by [31] to damp oscillations in the hydrodynamic forces which are therefore averaged over the two subcycles. Subcycles for the granular dynamics integration can be necessary when applying solvers that require much smaller time step sizes than the LBM to accurately resolve the contacts between particles. Since our applied non-smooth granular dynamics solver uses internal iterations to achieve this goal, this subcycling is not needed in our case. We will refer to one iteration of Algorithm 1 as a 'coarse time step' to distinguish it from a single LBM time step inside the subcycling, which internally consists again of several subiterations because of the applied refinement strategy, see Sect. 3.1.

#### 4 Implementation and Parallelization

All functionalities presented in Sect. 3 are implemented in the WALBERLA framework<sup>1</sup> which will be used for the reported simulations. WALBERLA is designed to facilitate the creation of portable, maintainable and robust HPC applications. However, its foremost design goals are outstanding performance and scalability to the full extent of current supercomputers. Only with both, a carefully tuned single-node performance and excellent scalability, the scarce and expensive compute hours on modern supercomputers can be used efficiently.

To adhere to these goals, WALBERLA performs the domain partitioning on the level of structured blocks of lattice cells. The concept of blocks allows the

<sup>&</sup>lt;sup>1</sup> http://www.walberla.net.

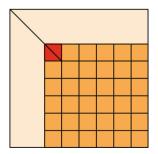

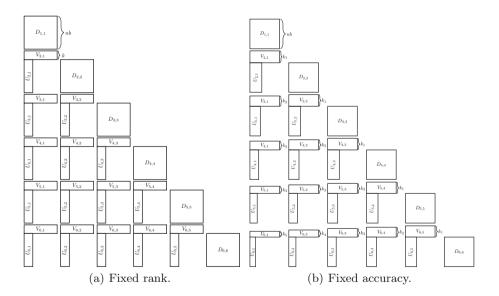

design of efficient LBM kernels and communication schemes due to the structured layout of the lattice cells [18]. WALBERLA's domain partitioning also allows for a local adaption of the grid resolution to the requirements of the simulation. The implemented refinement strategy [42] is based on a forest of octrees: each block may be divided into eight sub-blocks, with the constraint that a neighboring block may only be off by one refinement level. This strategy preserves performance as the structured layout of the LBM cells persists.

The PDFs are stored on a block within a field of four dimensions: three spatial dimensions and one for the 19 PDF values per cell corresponding to the discretized lattice velocities. The communication at the block interfaces is done per *ghostlayer exchange*. This is required by the streaming step of the LBM, Eq. (2), which accesses the PDF values of the neighboring cells. The field's size is extended by one layer of ghost cells in each direction, which is filled with a copy of the PDFs from the neighboring blocks via MPI communication. For more details about WALBERLA's block layout, the reader is referred to [18,42].

The physics engine pe, that carries out the granular dynamics simulation, uses the same block domain decomposition as the fluid simulation in WALBERLA. Each particle is associated to exactly one block based on where the center of mass of the particle lies. All particle information like the state variables (position, orientation, velocities) and constants (mass, inertia matrix, shape) are stored on this block. The process this block belongs to is called parent process of the respective particle. The parent process is responsible for the time integration of each of its particles. If the center of mass of a particle leaves the block, the particle will be migrated to the new block.

In order to detect all contacts between the particles, each block additionally requires information about all particles intersecting with its bounding box. This is realized with the help of *shadow copies* of the intersecting particles and follows a similar concept as the previously described ghostlayers for the field data. Only the parent process integrates and moves the particles and thus has to update these particles' shadow copies on the intersecting blocks. This is implemented by a synchronization step after every time step. During this synchronization step also new shadow copies are instantiated as needed and old ones are deleted if no longer required.

The necessary communication between the shadow copies and the parent copy can be implemented as an efficient next neighbor communication if the following condition holds for all particles at all time steps:

$$r + ||\mathbf{V}||_2 \delta t + \gamma < l_{min} \tag{21}$$

with the bounding radius of the particle r (e.g., for spheres the radius, for boxes half the space diagonal), the particle velocity V, a safety margin  $\gamma$  and the smallest diameter of the blocks  $l_{min}$ . This guarantees that the particles do not extend into the bounding box of the next neighbor block and that they will not reach this block during one single time step.

The treatment of the contacts is also distributed among the processes. The association of one contact to a process is delicate and out of scope of this paper [38]. During the resolution of the contacts an additional communication step is needed in every iteration of the solver (see Sect. 3.2) to collect all contributions to the final reaction from all shadow copies. This again involves a next neighbor communication. More details on the parallelization of the pe can be found in [38].

The applied coupling between the fluid and the particles, Sect. 3.3, uses the block data structures provided by LBM and the granular dynamics simulation. To obtain a consistent body mapping into the domain and to conserve the fine resolution, however, the particles have to remain on the same refinement level throughout the simulation. Thus, the area at which static grid refinement is applied has to be sufficiently large to ensure this condition.

#### 5 Results

#### 5.1 Compute Environment

All experiments are conducted on the petascale supercomputer SuperMUC located at the Leibniz Supercomputing Centre in Garching near Munich. We made use of the 18 thin node islands of SuperMUC phase 1, which consist of 512 nodes each. At most 8 islands are usable at the same time for a job during regular operations. Every node holds two Intel Xeon E5-2680 (Sandy Bridge-EP) eight-core processors and is equipped with 32 GiB of main memory. The interconnect within one island is a non-blocking tree network, while the islands are connected via a 4:1 pruned tree. We use IBM's MPI implementation for the interprocess communication.

#### 5.2 Simulation Experiment Setup

The simulation of a realistic sediment bed and the subsequent dune formation under the effect of a fluid flow above it requires a careful setup of the initial state. This already begins with the generation of a sediment bed inside a horizontally periodic domain of size  $L_x \times L_y \times L_z$ . In our case, layers of spheres with diameter D and density  $\rho_s$  are continuously created at the top of the domain, equipped with random velocities. Affected by the gravitational field acting in negative z direction, the spheres settle and arrange at the bottom which is simulated by non-smooth granular dynamics described in Sect. 3.2. The simulation is terminated when the spheres are at rest. The thus generated flat bed features a solid volume fraction of around 0.63 which agrees well with findings for sphere packings created in this way [10]. Following [26], the average bed height  $h_s$  can be defined as that height at which the solid volume fraction averaged in both horizontal directions hits the threshold value of 0.1. This is then used as input for the actual coupled simulation where LBM is applied to simulate the fluid flow inside and above the bed, as explained in Sects. 3.1 and 3.3. The characteristic parameters of the setup are the bulk Reynolds number  $Re_b = u_b h_f / \nu$ , with the average velocity in streamwise direction  $u_b$  and the water depth  $h_f$ , and the Galileo number  $Ga = u_g D/\nu$ , with  $u_g = ((\rho_s/\rho_f - 1)|\mathbf{g}|D)^{1/2}$  and the gravitational acceleration  $\mathbf{g}$ . In x, i.e., the streamwise, direction, the flow is

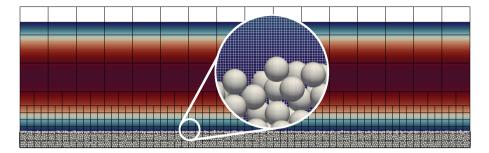

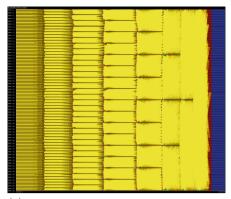

Fig. 5. Cross-sectional view of initial 3D simulation setup together with the block structure of the static grid refinement and a zoom to the fluid solid interface showing the grid cells.

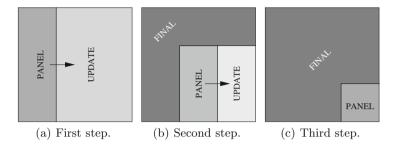

driven via an external fluid force, Eq. (6), that results in a flow rate of  $q_f = u_b h_f$ . No-slip walls are applied in vertical direction z as boundary conditions. The flow velocity above the sediment bed, i.e.,  $h_s \leq z \leq h_s + h_f$ , is initialized with the Poiseuille channel flow profile to yield the desired  $Re_b$  and which corresponds to the applied external fluid force. Three levels of static refinement are applied such that the sediment bed and an area of approximately the same height as the bed reside on the finest level. This allows for efficient simulations of the fluid flow in the large bulk area without losing accuracy in the vicinity of the bed. Since the static refinement poses some restrictions on the actual number of computational cells applied in each direction, i.e., it has to be multiples of the coarsest applied block size, the actual domain height  $L_z$  might be larger than  $h_s + h_f$  but the difference is filled up with boundary cells. An example for the actual setup including the static refinement structure can be seen in Fig. 5 which coincides with the one depicted in Fig. 3.

#### 5.3 Performance Analysis

We conduct strong- and weak-scaling experiments on SuperMUC to asses the efficiency and scalability of our implementation. We try to keep the benchmark problems as close to our production runs as possible, to generate information that helps steering the setup of our production runs towards a solid compromise of efficiency and performance. For all reported scaling results at least three measurements have been performed and the sample with the best performance has been chosen.

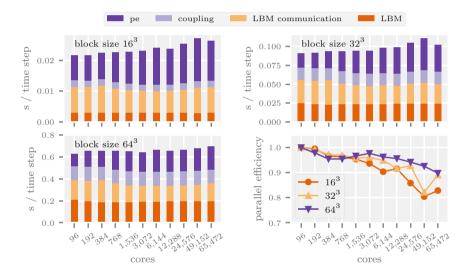

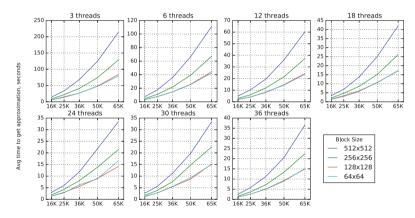

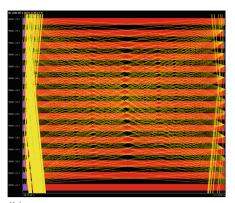

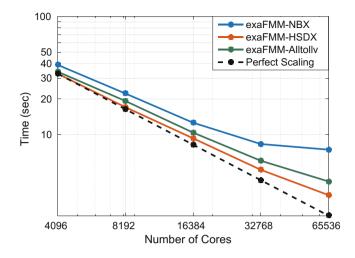

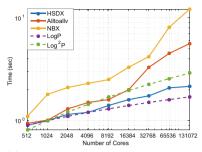

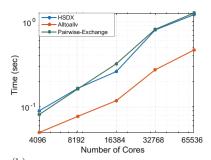

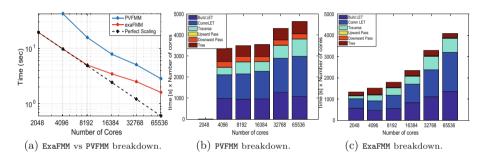

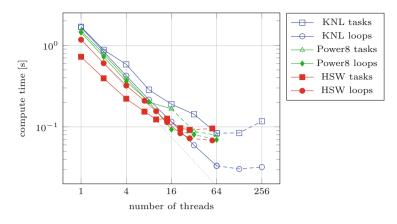

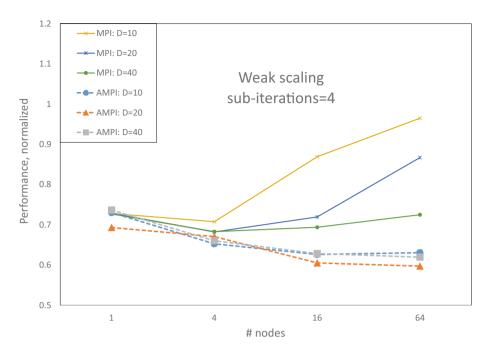

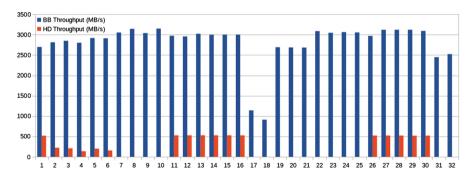

We ran three weak-scaling experiments with the block sizes  $16^3$ ,  $32^3$  and  $64^3$ . We started each experiment with 6 nodes, i.e., 96 processes. The number of processes was chosen such that a refinement configuration close to the production runs could be achieved. This base element was then doubled in size by replicating it alternately in x- and y-direction for each successive run. The exact configuration of the base element is given in Table 1. The results of the weak-scaling experiments can be found in Fig. 6. The results show perfect linear scalability of

Table 1. Parameters of base element of weak-scaling domain. The base element is designed for 96 processes and is replicated in x- and y-direction to conduct weak-scaling experiments.

| Block size               | $16^{3}$                  | $32^{3}$                | $64^{3}$                 |

|--------------------------|---------------------------|-------------------------|--------------------------|

| Domain size              | $64 \times 64 \times 256$ | $128\times128\times512$ | $256\times256\times1024$ |

| Initial avg. bed height  | 39                        | 75                      | 144                      |

| No. of LBM cells         | 417,792                   | 3,342,336               | 26,738,688               |

| No. of fluid cells       | 328,385                   | 2,613,619               | 20,822,174               |

| No. of particles         | 171                       | 1,392                   | 11,297                   |

| No. of blocks on level 0 | 2                         | 2                       | 2                        |

| No. of blocks on level 1 | 4                         | 4                       | 4                        |

| No. of blocks on level 2 | 96                        | 96                      | 96                       |

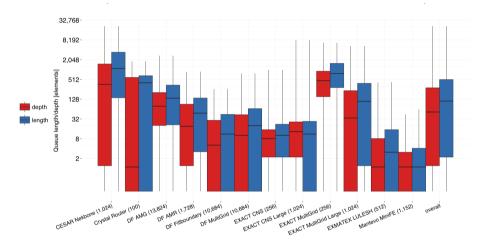

Fig. 6. Weak-scaling results. For each of the block sizes the required time per coarse time step is plotted. Each result is broken down in the four main subroutines of the simulation. On the bottom right the parallel efficiency of all runs is shown.

the LBM and coupling subroutines. The *pe* scales quite well, though not perfectly linear. The LBM communication captures not only the MPI communication but also any load imbalance that occurs due to the unequally distributed particles. In general we can see that the parallel efficiency at full scale is generally better with the larger  $64^3$  blocks (89.80%) than with the  $32^3$  blocks (89.08%) or  $16^3$  blocks (82.88%). We assume this is due to the small message sizes at the smaller blocks which make the communication bound by latency instead of bandwidth.

The variations in execution time between the varying block sizes are clearly visible when comparing the weak-scaling runs. The differences in efficiency were

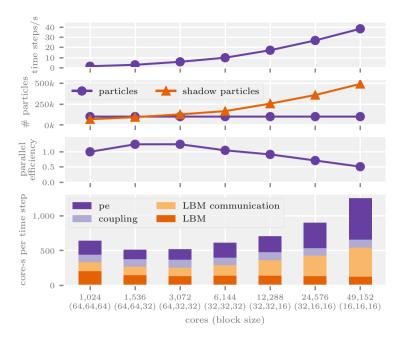

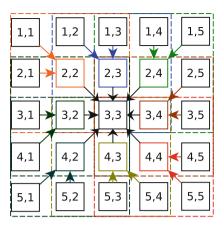

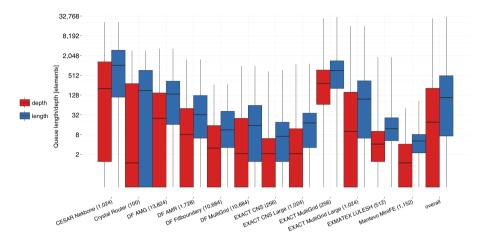

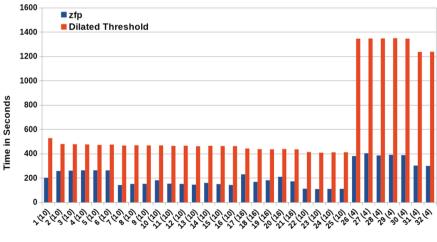

**Fig. 7.** Strong-scaling results of the simulation on SuperMUC. The *bottom* graph shows the amount of core seconds spent in each subroutine per coarse time step. Parallel efficiency is plotted on the *bottom center* graph. The *top center* graph illustrates the rising number of shadow particles as blocks get smaller. At the *top* the number of coarse time steps performed per second is visualized.

studied in detail during a strong-scaling experiment. The strong-scaling domain has size  $2,048 \times 512 \times 512$  and consists of 213.91 M cells from which 160.50 M are fluid cells. It is spread over three refinement levels. In the special case of blocks of size  $64^3$  the domain consists of 301.99 M cells from which 248.58 M are fluid cells. Here, the domain is spread over two refinement levels.

The riverbed consists of 101,970 particles with a diameter of 10 and has an average height of 84. In Fig. 7, the efficiency of a fixed setup ran at different block sizes and number of cores can be seen. We measure the efficiency in the amount of core-seconds (core-s) we spend in each coarse time step. In general it becomes obvious that larger blocks offer better efficiency but less performance, which we measure in the number of coarse time steps computed per second. A slight anomaly can be seen at the largest block size of  $64^3$ , where the efficiency drops compared to the next three smaller block sizes. This is due to the refinement setup and the requirement that neighboring blocks may not differ by more than one refinement level. Due to this restriction, the top layer cannot be coarsened twice but only once. Therefore more fluid cells are created and more core seconds have to be spent to update them. Another effect, that is well visible, is the *pe*'s quickly deteriorating efficiency with small block sizes. This corresponds well with the increasing amount of shadow particles that have to be updated in each of *pe*'s iterations. While at blocks of size  $64^3$  for each particle there are 0.68 shadow

17

particles, at blocks of size  $16^3$  for each particle 4.85 shadow particles have to be updated on average.

Using the scaling runs as guideline we chose to use a block size of  $32^3$  for the production runs, as it is a good compromise between efficiency and performance.

#### 5.4 Dune Formation Results

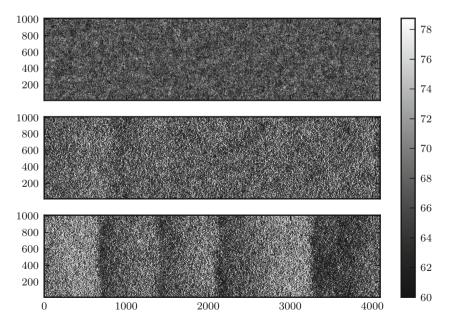

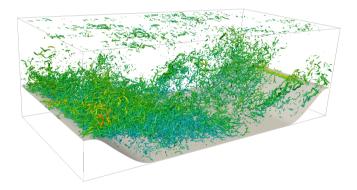

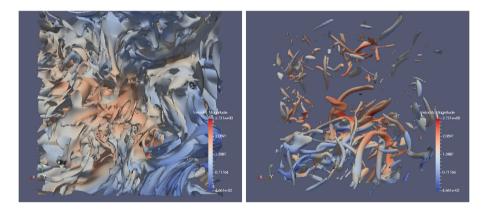

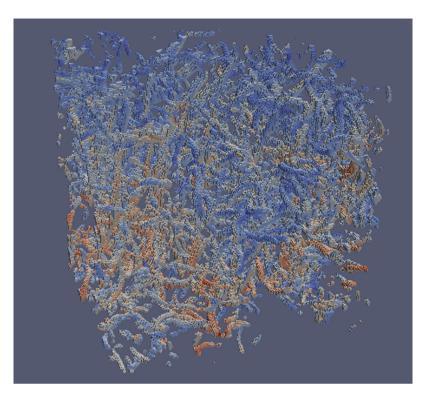

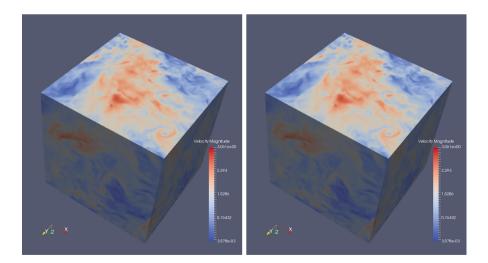

To study the evolution of the sediment bed surface, we use a domain size of  $L_x/D \times L_u/D \times L_z/D = 409.6 \times 102.4 \times 64$  and 350,000 spherical particles, generated as described in the previous section. This results in the sediment bed height  $h_s/D = 7.5$ . Blocks of size  $32^3$  are used and distributed to 24,576 cores. The fluid height is set to  $h_f/D = 50$ . Regarding the characteristic parameters,  $Re_b = 6022, Ga = 8.3$  and  $\rho_s/\rho_f = 2.5$  is used. To fully resolve the particles, ten cells per diameter are applied. This setup features 864.02 M cells in total compared to 2.684.35 M if no refinement were used. The simulation is then started from the initialized Poiseuille velocity profile from Fig. 5. In Fig. 8, the temporal change of the bed surface is visualized. Initially, the structure is random as a result from the randomized flat bed generation. Next, the sediments with a slightly exposed position compared to their direct neighbors are carried away by the flow. They get transported over the sediment bed which now features a chaotic structure  $(t^* = 53)$ . Afterwards, they begin to arrange such that they form spanwise clusters. Viewed from the top, these appear as dunes that move across the sediment bed  $(t^* = 277)$ .

Fig. 8. Temporal evolution of the sediment bed at different non-dimensional times  $t^* = tu_b/h_f$  (top:  $t^* = 0$ , center:  $t^* = 53$ , bottom:  $t^* = 277$ ). The color depicts the local bed height when viewed from the top.

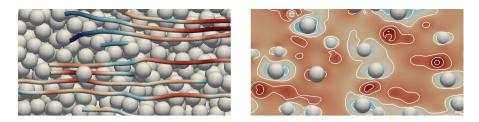

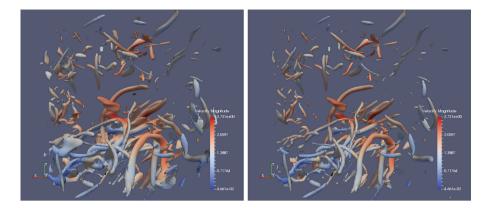

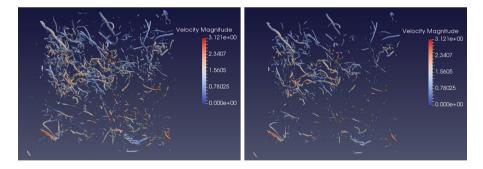

Fig. 9. Close-up top view of the riverbed and the flow properties. Left: Streamlines in the vicinity of the bed. Right: Wall shear stress distribution in a plane placed at the average bed height.

Furthermore, the simulation results allow a detailed analysis of the flow properties in the vicinity of the moving particles at the top of the bed. In Fig. 9, the velocity field is visualized with the help of stream lines to show the flow structures above and below the particles resulting from the flow from left to right. Additionally, the distribution of the wall shear stress at the position of the average bed height is given which exhibits complex pattern due to the interaction with the particles.

#### 6 Conclusion

In this work, we presented a suitable and flexible approach to study dune formation in riverbeds via fully resolved numerical simulations. It uses the lattice Boltzmann method to represent the fluid dynamics which is especially well-suited for massively parallel simulations on supercomputers due to its strictly local data accesses. The interaction of the particles inside the sediment bed is described by non-smooth granular dynamics. The fact that momentum is transferred between the fluid and the solid phase and vice versa is used to establish the fluid-particle coupling. The efficient implementation of these algorithms into the WALBERLA framework in combination with static grid refinement techniques allowed us to simulate dune formation in systems with up to 864.02 M computational cells and 350,000 spherical particles. We conducted strong- and weak-scaling benchmarks on the SuperMUC supercomputer that showed perfect linear scaling behavior for the LBM and the coupling subroutines. The performance of the granular dynamics simulation is affected by the applied block size as the synchronization overhead grows drastically for smaller block sizes. This shows an apparent challenge of such fully resolved coupled simulations: efficient particle simulations require several hundred particles per block which would then result in a too large number of computational cells per block. This, on the other hand, is undesired in the fluid simulation as it decreases the throughput in terms of time steps per second. Finally, these benchmarks allowed us to identify a suitable workload per process in terms of fluid cells and particles as a compromise between efficiency and performance. This carefully tuned setup can now be used for extensive validation against existing experimental data and ensures efficient usage of the valuable resources provided by the supercomputer. The physical focus of this work was

on unidirectional non-oscillatory flow and spherical particles. However, the formation and dynamics of dunes is a complex physical phenomenon and depends on various physical parameters. Future work will thus investigate the influence of oscillatory and combined flows, different sediment shapes and size distributions on the system. Adaptive grid refinement for the coupling method and a synchronization strategy suitable for particles larger than one block will be added to the software framework to enable these studies. Such fully resolved simulations will then lead to a better understanding of the various physical mechanisms acting inside a riverbed.

Acknowledgments. The authors gratefully acknowledge the Gauss Centre for Supercomputing e.V. (www.gauss-centre.eu) for funding this project by providing computing time on the GCS Supercomputer SuperMUC at Leibniz Supercomputing Centre (LRZ, www.lrz.de).

#### References

- 1. Aidun, C.K., Lu, Y., Ding, E.J.: Direct analysis of particulate suspensions with inertia using the discrete Boltzmann equation. J. Fluid Mech. **373**, 287–311 (1998)

- Ammer, R., Markl, M., Ljungblad, U., Körner, C., Rüde, U.: Simulating fast electron beam melting with a parallel thermal free surface lattice Boltzmann method. Comput. Math. Appl. 67(2), 318–330 (2014). doi:10.1016/j.camwa.2013.10.001

- Andreotti, B., Claudin, P., Douady, S.: Selection of dune shapes and velocities part 1: dynamics of sand, wind and barchans. Eur. Phy. J. B-Condens. Matter Complex Syst. 28(3), 321–339 (2002). doi:10.1140/epjb/e2002-00236-4

- Bartuschat, D., Rüde, U.: Parallel multiphysics simulations of charged particles in microfluidic flows. J. Comput. Sci. 8, 1–19 (2015). doi:10.1016/j.jocs.2015.02.006

- Bauer, M., Hötzer, J., Jainta, M., Steinmetz, P., Berghoff, M., Schornbaum, F., Godenschwager, C., Köstler, H., Nestler, B., Rüde, U.: Massively parallel phasefield simulations for ternary eutectic directional solidification. In: Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis, SC 2015, pp. 8:1–8:12. ACM, New York (2015). doi:10.1145/ 2807591.2807662

- Best, J.: The fluid dynamics of river dunes: a review and some future research directions. J. Geophys. Res.: Earth Surface 110(F4) (2005). doi:10.1029/2004JF000218

- Buffington, J.M., Montgomery, D.R.: A systematic analysis of eight decades of incipient motion studies, with special reference to gravel-bedded rivers. Water Resour. Res. 33(8), 1993–2029 (1997). doi:10.1029/96WR03190

- Chen, S., Doolen, G.D.: Lattice Boltzmann method for fluid flows. Annu. Rev. Fluid Mech. 30(1), 329–364 (1998). doi:10.1146/annurev.fluid.30.1.329

- Doucette, J.S.: Geometry and grain-size sorting of ripples on low-energy sandy beaches: field observations and model predictions. Sedimentology 49(3), 483–503 (2002). doi:10.1046/j.1365-3091.2002.00456.x

- Dullien, F.A.: Porous Media: Fluid Transport and Pore Structure. Academic Press, Cambridge (2012)

- Fattahi, E., Waluga, C., Wohlmuth, B., Rüde, U.: Large scale lattice Boltzmann simulation for the coupling of free and porous media flow. In: Kozubek, T., Blaheta, R., Šístek, J., Rozložník, M., Čermák, M. (eds.) HPCSE 2015. LNCS, vol. 9611, pp. 1–18. Springer, Cham (2016). doi:10.1007/978-3-319-40361-8\_1

- Fattahi, E., Waluga, C., Wohlmuth, B., Rüde, U., Manhart, M., Helmig, R.: Lattice Boltzmann methods in porous media simulations: from laminar to turbulent flow. Comput. Fluids 140, 247–259 (2016). doi:10.1016/j.compfluid.2016.10.007

- Ferguson, R., Hoey, T., Wathen, S., Werritty, A.: Field evidence for rapid downstream fining of river gravels through selective transport. Geology 24(2), 179–182 (1996)

- Flemming, B.W.: Underwater sand dunes along the southeast African continental margin — Observations and implications. Marine Geol. 26(3–4), 177–198 (1978). doi:10.1016/0025-3227(78)90059-2

- Frings, R.M.: Downstream fining in large sand-bed rivers. Earth-Sci. Rev. 87(1-2), 39-60 (2008). doi:10.1016/j.earscirev.2007.10.001

- Frings, R.M., Kleinhans, M.G.: Complex variations in sediment transport at three large river bifurcations during discharge waves in the River Rhine. Sedimentology 55(5), 1145–1171 (2008). doi:10.1111/j.1365-3091.2007.00940.x

- Ginzburg, I., Verhaeghe, F., d'Humieres, D.: Two-relaxation-time lattice Boltzmann scheme: about parametrization, velocity, pressure and mixed boundary conditions. Commun. Comput. Phys. 3(2), 427–478 (2008)

- Godenschwager, C., Schornbaum, F., Bauer, M., Köstler, H., Rüde, U.: A framework for hybrid parallel flow simulations with a trillion cells in complex geometries. In: Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis, SC 2013, pp. 35:1–35:12. ACM, New York (2013). doi:10.1145/2503210.2503273

- Götz, J., Iglberger, K., Feichtinger, C., Donath, S., Rüde, U.: Coupling multibody dynamics and computational fluid dynamics on 8192 processor cores. Parallel Comput. 36(2), 142–151 (2010). doi:10.1016/j.parco.2010.01.005

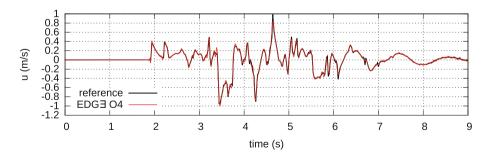

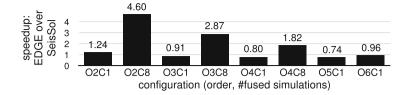

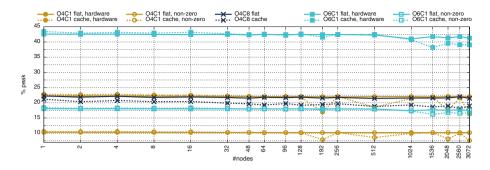

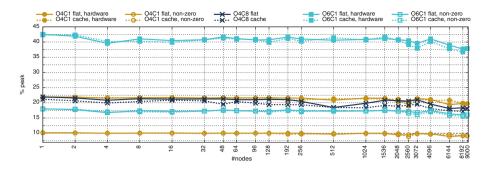

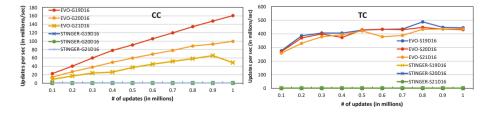

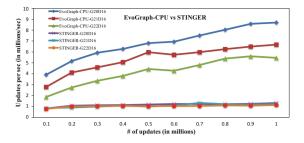

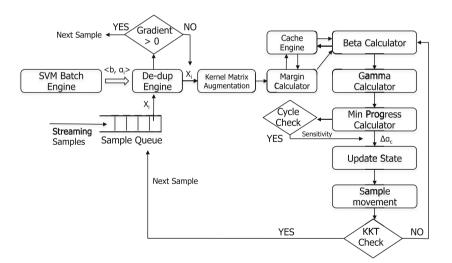

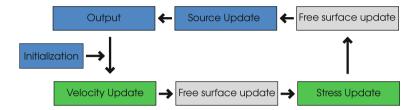

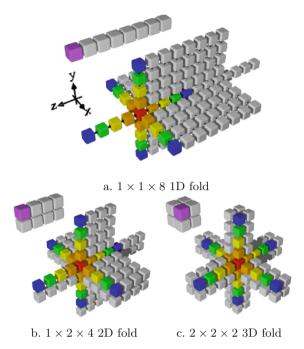

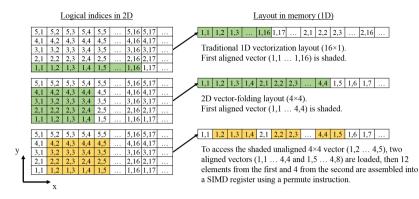

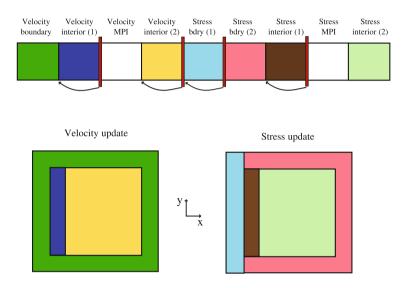

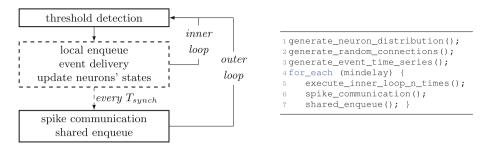

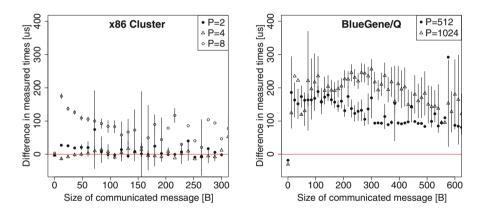

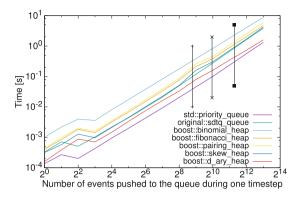

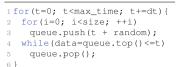

- Götz, J., Iglberger, K., Stürmer, M., Rüde, U.: Direct numerical simulation of particulate flows on 294912 processor cores. In: Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1–11. IEEE Computer Society (2010). doi:10.1109/SC.2010.20