Spyros Blanas Rajesh Bordawekar Tirthankar Lahiri Justin Levandoski Andrew Pavlo (Eds.)

# Data Management on New Hardware

7th International Workshop on Accelerating Data Analysis and Data Management Systems Using Modern Processor and Storage Architectures, ADMS 2016 and 4th International Workshop on In-Memory Data Management and Analytics, IMDM 2016 New Delhi, India, September 1, 2016, Revised Selected Papers

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7409

Spyros Blanas · Rajesh Bordawekar Tirthankar Lahiri · Justin Levandoski Andrew Pavlo (Eds.)

# Data Management on New Hardware

7th International Workshop on Accelerating Data Analysis and Data Management Systems Using Modern Processor and Storage Architectures, ADMS 2016 and 4th International Workshop on In-Memory Data Management and Analytics, IMDM 2016 New Delhi, India, September 1, 2016 Revised Selected Papers

*Editors* Spyros Blanas Ohio State University Columbus, OH USA

Rajesh Bordawekar IBM Thomas J Watson Research Center Yorktown Heights, NY USA

Tirthankar Lahiri Oracle Cor. Redwood Shores, CA USA Justin Levandoski Microsoft Corporation Redmond, WA USA

Andrew Pavlo Computer Science Department Carnegie Mellon University Pittsburgh, PA USA

ISSN 0302-9743

ISSN 1611-3349

(electronic)

Lecture Notes in Computer Science

ISBN 978-3-319-56110-3

ISBN 978-3-319-56111-0

(eBook)

DOI 10.1007/978-3-319-56111-0

ISBN 978-3-319-56111-0

ISBN 978-3-319-56111-0

ISBN 978-3-319-56111-0

Library of Congress Control Number: 2017935567

LNCS Sublibrary: SL3 - Information Systems and Applications, incl. Internet/Web, and HCI

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Preface

The International Workshop on Accelerating Analytics and Data Management Systems Using Modern Processor and Storage Architectures (ADMS) and the International Workshop on In-Memory Data Management (IMDM) were held jointly this year.

The objective of this workshop is to investigate opportunities in accelerating analytics/data management systems and workloads (which include traditional OLTP, data warehousing/OLAP, ETL, streaming/real-time, business analytics, and XML/RDF processing) running in memory-only environments, using processors (e.g., commodity and specialized multi-core, GPUs, and FPGAs), storage systems (e.g., storage-class memories like SSDs and phase-change memory), and hybrid programming models such as CUDA, OpenCL, and OpenACC. The workshop hopes to explore the interplay between overall system design, core algorithms, query optimization strategies, programming approaches, as well as performance modeling and evaluation, from the perspective of data management applications.

In addition, over the past 30 years, memory prices have been dropping by a factor of 10 every 5 years. Main memory is the "new disk" for data storage. The number of I/O operations per second (IOPS) in DRAM is far greater than other storage media such as hard disks and SSDs. DRAM is readily available in the market at a better price point in comparison with DRAM alternatives. These trends make DRAM a better storage media for latency-sensitive database applications, large-scale Web applications, and future applications such as wearable devices. The International Workshop on In-Memory Memory Data Management and Analytics (IMDM) aims to bring together researchers and practitioners interested in the proliferation of in-memory data management and analytics infrastructures.

These proceedings contain papers from the joint ADMS/IMDM workshop that was co-located with VLDB 2016 in New Delhi, India. The workshops were well-attended and sparked interesting technical discussions.

All papers in these proceedings were peer-reviewed by an expert Program Committee comprising experts from both industry and academia. We would like to thank these committee members as well as the authors for contributing high-quality work.

February 2017

Spyros Blanas Rajesh Bordawekar Tirthankar Lahiri Justin Levandoski Andrew Pavlo

# Organization

#### **Workshop Organizers**

| Spyros Blanas     |

|-------------------|

| Rajesh Bordawekar |

| Tirthankar Lahiri |

| Justin Levandoski |

| Andrew Pavlo      |

Ohio State University, USA IBM T.J. Watson Research Center, USA Oracle, USA Microsoft Research, USA Carnegie Mellon University, USA

#### **Program Committee**

Reza Azimi Nipun Agarwal Christoph Dubach Oiong Luo Sina Merji Mohammad Sadoghi Nadathur Satish Sudhakar Yalamanchili David Schwalb Viktor Rosenfeld Shirish Tatikonda Christian Lang Vincent Kulandaisamy Eric Boutin Badrish Chandramouli Martin Grund Ryan Johnson Hideaki Kimura Viktor Leis **Ippokratis** Pandis Evangelia Sitaridi Ryan Stutsman Sandeep Tata Pinar Tozun Oded Shmueli

Huawei, China Oracle Labs, USA University of Edinburgh, UK Hong Kong University of Science and Technology (HKUST), Hong Kong IBM Toronto, Canada IBM T.J. Watson Research, USA Intel. USA Georgia Tech, USA Hasso-Plattner Institute (HPI), Germany TU Berlin, Germany Target, USA Acelot, USA IBM Analytics, USA MemSOL, USA Microsoft Research, USA Amazon, USA LogicBlox, USA Hewlett Packard Enterprise, USA TU Munich, Germany Amazon, USA Columbia University, USA University of Utah, USA Google, USA IBM Research, USA Technion. Israel

# Contents

| Cache-Sensitive Skip List: Efficient Range Queries on Modern CPUs<br>Stefan Sprenger, Steffen Zeuch, and Ulf Leser                                                                                                   | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Exploit Every Cycle: Vectorized Time Series Algorithms on Modern<br>Commodity CPUs<br>Bo Tang, Man Lung Yiu, Yuhong Li, and Leong Hou U                                                                              | 18  |

| Compression-Aware In-Memory Query Processing: Vision, System Design<br>and Beyond                                                                                                                                    | 40  |

| Overtaking CPU DBMSes with a GPU in Whole-Query Analytic<br>Processing with Parallelism-Friendly Execution Plan Optimization<br>Adnan Agbaria, David Minor, Natan Peterfreund, Eyal Rozenberg,<br>and Ofer Rosenberg | 57  |

| To Copy or Not to Copy: Making In-Memory Databases Fast<br>on Modern NICs                                                                                                                                            | 79  |

| DBMS Data Loading: An Analysis on Modern Hardware<br>Adam Dziedzic, Manos Karpathiotakis, Ioannis Alagiannis,<br>Raja Appuswamy, and Anastasia Ailamaki                                                              | 95  |

| Locality-Adaptive Parallel Hash Joins Using Hardware<br>Transactional Memory                                                                                                                                         | 118 |

| SwingDB: An Embedded In-memory DBMS Enabling Instant<br>Snapshot Sharing<br><i>Qingzhong Meng, Xuan Zhou, Shiping Chen, and Shan Wang</i>                                                                            | 134 |

| Runtime Fragility in Main Memory<br>Endre Palatinus and Jens Dittrich                                                                                                                                                | 150 |

| Author Index                                                                                                                                                                                                         | 167 |

# Cache-Sensitive Skip List: Efficient Range Queries on Modern CPUs

Stefan Sprenger<sup>( $\boxtimes$ )</sup>, Steffen Zeuch, and Ulf Leser

Institute for Computer Science, Humboldt-Universität zu Berlin, Unter den Linden 6, 10099 Berlin, Germany {sprengsz,zeuchste,leser}@informatik.hu-berlin.de

Abstract. Due to ever falling prices and advancements in chip technologies, many of today's databases can be entirely kept in main memory. However, reusing existing disk-based index structures for managing data in memory leads to suboptimal performance due to inefficient cache usage and negligence of the capabilities of modern CPUs. Accordingly, a number of main-memory optimized index structures have been proposed, yet most of them focus entirely on single-key lookups, neglecting the equally important range queries. We present Cache-Sensitive Skip Lists (CSSL) as a novel index structure that is optimized for range queries and exploits modern CPUs. CSSL is based on a cache-friendly data layout and traversal algorithm that minimizes cache misses, branch mispredictions, and allows to exploit SIMD instructions for search. In our experiments, CSSL's range query performance surpasses all competitors significantly. Even for lookups, it is only surpassed by the recently presented ART index structure. We therefore see CSSL as a serious alternative for mixed key/range workloads on main-memory databases.

Keywords: Index structures  $\cdot$  Main-memory databases  $\cdot$  Scientific databases

# 1 Introduction

Over the last years, various index structures were designed for fast and spaceefficient execution of search operations in main memory, like the adaptive radix tree (ART) [13] or Cache-Sensitive  $B^+$ -tree (CSB<sup>+</sup>) [18]. By reducing cache misses, improving cache line utilization, and exploiting vectorized instructions, they outperform conventional database index structures, like B-trees [5], which were mostly designed to reduce disk accesses. Most of these novel index methods focus on single-key lookups and show suboptimal performance for range queries, despite their importance in many applications. Use cases for range queries are numerous, such as: queries in a data warehouse that ask for sales in a certain price range, analysis of meteorological data that considers certain yearly time periods in long time series, and Bioinformaticians who build databases of hundreds of millions of mutations in the human genome that are analyzed by ranges defined by genes [9].

S. Blanas et al. (Eds.): ADMS 2016/IMDM 2016, LNCS 10195, pp. 1–17, 2017. DOI: 10.1007/978-3-319-56111-0\_1

<sup>©</sup> Springer International Publishing AG 2017

In this paper, we introduce the Cache-Sensitive Skip List (CSSL), a novel main-memory index structure specifically developed for efficient range queries on modern CPUs. CSSL is based on skip lists as described in [16], yet uses a very different memory layout to take maximal advantage of modern CPU features like CPU-near cache lines, SIMD instructions, and pipelined execution. In this work, we focus on read performance but provide a technique for handling updates, too. Besides many other use cases, we see CSSL as perfectly suited for scientific databases that prefer fast reads over fast writes and need range queries in many cases. Especially the bioinformatics community, which is confronted with an exponentially growing amount of genomic data that is mostly analyzed with range queries to investigate certain genomic regions [20], may benefit from our approach.

We evaluated CSSL on data sets of various sizes and properties and compared its performance to CSB<sup>+</sup>-tree [18], ART [13], B<sup>+</sup>-tree [7], and binary search on a static array. We also include experiments with real-world data from the bioinformatics domain to investigate performance on non-synthetic key distributions. For range queries and mixed workloads, CSSL is consistently faster than all state-of-the-art approaches, often by an order of magnitude; also its lookup performance is way ahead of all competitors except ART.

The remaining paper is structured as follows. The next section introduces skip lists, the index structure that CSSL is based on. Section 3 presents the Cache-Sensitive Skip List as our main contribution. Section 4 describes algorithms for executing lookups and range queries on CSSL. In Sect. 5, we compare CSSL against other state-of-the-art index structures using synthetic as well as nonsynthetic data. Section 6 discusses related work, and Sect. 7 concludes this paper.

#### 2 Preliminaries

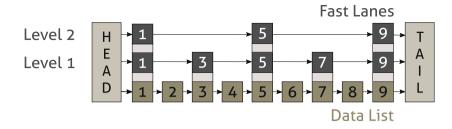

Skip lists were originally presented as a probabilistic data structure similar to B-trees [16]. Skip lists consist of multiple lanes of keys organized in a hierarchical fashion (see Fig. 1). At the highest level of granularity, a skip list contains a linked list of all keys in sorted order. In addition to this so-called *data list*, skip lists maintain *fast lanes* at different levels. A fast lane at level *i* contains  $n * p^i$  elements on average, where *n* is the number of keys to be stored and 0 is a parameter. Skip lists were originally proposed as probabilistic data structures, as the elements to be stored in higher lanes are randomly chosen from those at lower lanes: Every element of fast lane*i*appears in fast lane <math>i + 1 with probability *p*. This scheme allows for efficient updates and inserts, yet makes the data structure less predictable.

In our work, we use a deterministic variant of skip lists, so-called *perfectly* balanced skip lists [15]. In balanced skip lists, the fast lane at level i + 1 contains every 1/p'th element of the fast lane at level i. Accordingly, for p = 0.5 a lane at level i + 1 contains every second element of level i, in which case a skip list resembles a balanced binary search tree. Figure 1 shows a balanced skip list over nine integer keys with two fast lanes for p = 0.5.

Fig. 1. A balanced skip list that manages nine keys and two fast lanes; each fast lane skips over two elements (p = 1/2).

In case of a low p value, fast lanes skip over many elements, therefore, fast lanes can be considered sparse. In case of a high p value, fast lanes skip over few elements, therefore, fast lanes can be considered dense. Fast lanes are used to narrow down the data list segment that may contain the searched element to avoid a full scan. For instance, a search for key 6 would traverse the skip list of Fig. 1 as follows. First, search determines the first element of the highest fast lane at level 2 by using the head element. Second, the fast lane will be traversed until the subsequent element is either equal to the searched element, in which case search terminates, or greater than the searched element. In this example, search stops at element 5. Third, search moves down to the next fast lane. In this example, traversal jumps to element 5 of the fast lane at level 1. Fourth, steps two and three are repeated until the data list is reached. Fifth, the data list is scanned until the searched element is found or proven to be non-existing. In a fully built balanced skip list for p = 0.5, search requires O(loq(n)) key comparisons in the worst case. Parameter p directly influences the structure of the fast lane hierarchy and should be chosen depending on the expected number of keys. If p is too high, only few keys need to be compared per fast lane when searching, but a lot of fast lane levels are required to fully build a balanced skip list. If p is too low, a lot of keys need to be compared per fast lane when searching, but only few fast lane levels are required to fully build a balanced skip list.

Besides single-key lookups, skip lists also offer very efficient range queries. Since the data list is kept in sorted order, implementing a range query requires two steps: (1) Search the first element that satisfies the queried range, and (2) traverse the data list to collect all elements that match the range boundaries.

In the original paper [16], skip lists are implemented using so-called *fat keys*. A fat key is a record that contains a key and an array, which holds pointers to subsequent elements for every fast lane and for the data list. The advantage of this approach is that all nodes are uniform, which simplifies the implementation. Furthermore, if a key is found in an upper lane, search immediately stops as all instances of a key are kept in the same record. On the other hand, such an implementation is space inefficient, because it requires space for O(m \* n)

pointers (if m is the number of fast lane levels), although most values in higher levels are padded with NULL.

Searching in skip lists using fat keys requires to follow many pointers. This layout is suboptimal on modern CPUs, as it incurs many cache misses due to jumps between non-contiguous parts of allocated memory. Even when searching the data list, cache utilization is suboptimal due to the *fatness* of keys. For instance, in a skip list that stores 32-bit integer keys and maintains five fast lanes in addition to the data list, each node takes 4 bytes + 6 \* 8 bytes = 52 bytes of memory on a 64-bit architecture. Given that a cache line is typically 64 bytes, each traversal step fills almost an entire cache line although only a small part of it is used. Typically, traversal steps just need the key and one pointer to find the subsequent element on a certain fast lane, i.e., 4 bytes + 8 bytes = 12 bytes.

#### 3 Cache-Sensitive Skip List

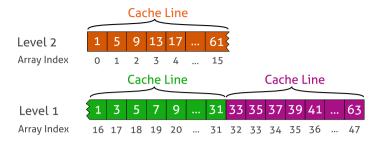

In this paper, we present Cache-Sensitive Skip List as alternative implementation for balanced skip lists, which uses a radically different memory layout that leads to much higher efficiency in today's CPU architectures. The first and most obvious idea is to keep fast lanes as separate entities in dense arrays. This leads to less cache misses, improves the utilization of cache lines, and allows to use SIMD instructions. Figure 2 shows a Cache-Sensitive Skip List that manages 32 integer keys with two fast lanes for p = 0.5. The traversal path, which search would take to find key 7, is highlighted in red.

CSSL's main contributions are threefold: First, fast lanes are linearized and managed in one dense array, which is called *Linearized Fast Lane Array*, instead

Fig. 2. A cache-sensitive skip list that manages 32 keys with two fast lanes (p = 1/2). (Color figure online)

of being kept in data list nodes. This improves utilization of cache lines when executing a lookup or range query. Second, by linearizing fast lanes we eliminate the need to store and follow pointers. For a given n, the number of fast lane elements is known a-priori since we build on balanced skip lists. Thus, we can simply compute the position of follow-up elements within the array, making pointers completely superfluous. In Fig. 2, pointerless traversal over fast lanes is indicated by dotted arrows. In our current implementation, we always preallocate a certain amount of memory per fast lane based on a hypothetical maximum t of keys. As long as n < t, all inserts can be managed inside the data structure; as soon as n exceeds t, we rebuild fast lanes and increase t by a fixed fraction (see Sect. 3.2 for details on an update strategy). Third, CSSL uses SIMD instructions to iterate over matching keys when executing range queries, which is especially useful in the case of large ranges. We exploit the lowest fast lane, i.e., the fast lane at level 1, to search for the last key that satisfies the queried range. To the best of our knowledge, CSSL is the first index structure that can make significant use of SIMD instructions when executing range queries.

Our approach to linearization of fast lanes has the following benefits compared to conventional skip lists: First, CSSL need less memory. Let k be the size of a key and r be the size of a pointer. Ignoring space requirements for data objects, which is equal in both layouts, conventional skip lists require n \* (m \* r + r + k) space, whereas CSSL only require  $n * (r + k) + \sum_{i=1}^{m} p^i * n * k$ . Second, traversing linearized fast lanes has a better cache line utilization because we always use the whole cache line content until we abort search and jump to a lower layer. In the case of 32-bit keys, 16 fast lane elements fit into one 64-byte cache line while only one fat key of a conventional skip list fits into it. Third, since traversal of linearized fast lanes accesses successive array positions, we can make use of prefetched cache lines. Fourth, array-based storage of fast lane elements allows the usage of SIMD instructions and enables data-level parallelism. Given that s is the size of a SIMD register and k is the key size,  $\frac{s}{k}$  fast lane elements can be compared in parallel. Modern CPUs usually feature SIMD registers having a size of 128 or 256 bits, thus four or eight 32-bit integers can be processed per instruction. For the implementation of CSSL, we use Intel's AVX instructions [2] that support 256-bit SIMD registers.

#### 3.1 Optimizations

Besides these main concepts, we apply a number of further optimizations to fully exploit modern CPUs. First, we always tailor the size of fast lanes as multiples of the CPU cache line size (see Fig. 3). This especially affects the highest fast lane level. Second, we introduce an additional lane, called *proxy lane*, between the lowest fast lane and the data list (see Fig. 2). For each key, the proxy lane maintains a pointer to its corresponding data object. Connections between the proxy lane, which is implemented as an array of structs, and the fast lane at level 1 are implicit: The *i*'th fast lane element is part of the struct that can be found at index i - 1 of the proxy lane. We use the proxy lane to connect the lowest fast lane with the data list. Third, in practice we observed that searching

Fig. 3. Linearized fast lane array of a CSSL that indexes all 32-bit integers in  $\{1, .., 64\}$  with two levels (p = 1/2).

the highest fast lane is very expensive in terms of CPU cycles if it contains lots of elements. This is especially the case if the number of fast lanes is kept small and the highest fast lane contains a lot more than 1/p elements. In the worst case, we have to scan the whole lane, while searching the remaining fast lanes can never require more than 1/p comparisons per lane. We accelerate searching the highest fast lane by using a binary search instead of sticking to a sequential scan.

#### 3.2 Updates

In our implementation, a CSSL is initialized with a sorted set of keys. Nonetheless, we still want to support *online updates*. In the following, we describe techniques for inserting new keys, updating existing keys, and removing keys.

**Inserting Keys:** Since CSSL employs dense arrays for managing fast lanes, directly inserting keys into fast lanes would require a lot of shift operations to preserve the order of fast lane elements. For this reason, new keys are only inserted into the data list, which is implemented as a common linked list. We create a new node and add it at the proper position. As soon as the fast lane array gets rebuilt to allocate more space, new keys are also reflected in the fast lane hierarchy. Nonetheless, we can find new keys in the meantime. If search does not find a key in the fast lanes, it moves down to the data list and scans it until the key is found or proven to be non-existing. The insert algorithm can be implemented latch-free by using an atomic compare-and-swap instruction for changing pointers in the data list.

**Deleting Keys:** In contrast to insertions, we cannot delete keys from the data list but leave fast lanes untouched, because this would lead to invalid search results. In the first step of deleting a key from CSSL, we need to eliminate it from the fast lane array. Just changing the corresponding entry to *NULL* would require reshift operations to close gaps in the array. Therefore, we replace to-be-deleted entries with a copy of the successive fast lane element. This allows fast deletes but leaves the fast lane structure intact. We end up with duplicates in

the fast lane array that are removed as soon as the array gets rebuilt. As last step, the *next* pointer of the preceding node in the data list is changed to point to the successor of the to-be-removed-node and the node is deleted.

**Updating Keys:** Updates are basically implemented as an insert operation followed by a deletion.

Though being based on balanced skip lists, which leads to less flexibility compared to common skip lists, CSSL is able to handle online updates. By limiting in-place updates on the fast lane array, we can keep the number of cache invalidations small.

#### 4 Algorithms

In this section, we describe in detail algorithms for executing lookups and range queries using CSSL. We start by presenting the lookup algorithm, because the execution of range queries is based on it.

**Lookups:** Pseudocode for lookups is shown in Algorithm 1. If search is successful the element's key will be returned, if not  $INT\_MAX$  will be returned. The algorithm can be split into multiple parts. First, the highest fast lane is processed with a binary search (see Line 1). Second, the remaining fast lanes are searched hierarchically to narrow down the data list segment that may hold the search key (see Lines 2–8). We scan each fast lane sequentially instead of employing a binary search, because we need to compare only 1/p elements per fast lane level. Third, if the last fast lane contains the searched element, it is immediately returned (see Line 9); otherwise the associated proxy node is loaded and all keys of the data list are compared with the searched element (see Lines 10-12).  $INT\_MAX$  is returned if no matching element is found (see Line 13).

```

Algorithm 1: lookup(key)

```

```

1: pos = binary_search_top_lane(flanes, key);

2: for (level = MAX_LEVEL - 1; level > 0; level--) {

3:

rPos = pos - level_start_pos[level];

while (key >= flanes[++pos])

4:

5:

rPos++;

if (level == 1) break;

6:

7:

pos = level_start_pos[level-1] + 1/p * rPos;

8: }

9: if (key == flanes[--pos]) return key;

10: proxy = proxy_nodes[pos - level_start_pos \cite{bib1}];

11: for (i = 1; i < 1/p; i++)

if (key == proxy->keys[i]) return key;

12:

13: return INT_MAX;

```

**Range Queries:** Pseudocode for range queries is shown in Algorithm 2. Search returns pointers to the first and last data list element that match the given range defined by *start* and *end*, i.e., it returns a linked list that can be used for further processing. Execution of range queries is implemented as follows.

First, the first matching element is searched similar to executing a lookup (see Lines 1–16 of Algorithm 2). Second, the algorithm jumps back to the lowest fast lane and scans it using vectorized instructions to find the last element that satisfies the queried range. Using AVX, CSSL can process eight 32-bit integer keys in parallel (see Lines 17–25). Third, the proxy node, which is associated with the matching fast lane entry, is loaded and compared with the range end to determine the last matching element (see Lines 29–35). Fourth, range search returns a struct that provides pointers to the first and last matching element in the data list (see Line 36).

```

Algorithm 2: searchRange(start, end)

1: RangeSearchResult res;

2: pos = binary_search_top_lane(flanes, start);

3: for (level = MAX_LEVEL - 1; level > 0; level--) {

4:

rPos = pos - level_start_pos[level];

5:

while (start >= flanes[++pos])

6:

rPos++;

7:

if (level == 1) break;

pos = level_start_pos[level-1] + 1/p * rPos;

8:

9: }

10: proxy = proxy_nodes[rPos];

11: res.start = proxy->pointers[1/p - 1]->next;

12: for (i=0; i < 1/p; i++) {

if (start <= proxy->keys[i]) {

13:

14:

res.start = proxy->pointers[i]; break;

}

15:

16: }

17: sreg = _mm256_castsi256_ps(_mm256_set1_epi32(end));

18: while (rPos < level_items \cite{bib1} - 8) {</pre>

19:

creg = _mm256_castsi256_ps(

_mm256_loadu_si256((__m256i const *) &flanes[pos]));

20:

21:

res = _mm256_cmp_ps(sreg, creg, 30);

22:

bitmask = _mm256_movemask_ps(res);

23:

if (bitmask < 0xff) break;</pre>

24:

pos += 8; rPos += 8;

25: }

26: pos--; rPos--;

27: while (end >= flanes[++pos] && rPos < level_items \cite{bib1})

28:

rPos++;

29: proxy = proxy_nodes[rPos];

30: res.end = proxy->pointers[1/p - 1];

31: for (i=1; i < 1/p; i++) {

if (end < proxy->keys[i]) {

32:

```

```

33: res.end = proxy->pointers[i - 1]; break;

34: }

35: }

36: return res;

```

#### 5 Evaluation

We compare CSSL to other index structures optimized for in-memory storage. We also include B<sup>+</sup>-tree [7] as baseline approach, though we note that it is designed to be stored on disk. We compare competitors w.r.t. performance of range queries (see Sect. 5.1), performance of lookups (see Sect. 5.2), performance on a mixed workload (see Sect. 5.3), and space consumption (see Sect. 5.5). An evaluation with real-world data from the bioinformatics domain can be found in Sect. 5.4; results are very similar to those for synthetic data sets. Search performance is measured in throughput, i.e., how many queries are processed per second. For our main evaluation, we use n 32-bit integer keys with dense and sparse distribution. For dense distribution, every key in [1, n] is indexed; for sparse distribution n random keys from  $[1, 2^{31})$  are indexed. We evaluate CSSL with two configurations, CSSL<sub>2</sub> with p = 1/2 and CSSL<sub>5</sub> with p = 1/5, to investigate effects on dense and sparse fast lanes. In both cases, we use nine fast lanes, because this setting results in a balanced number of inter- and intra-fast lane traversals in our experiments.

We compare to the following approaches:

- the adaptive radix tree (ART) [13], a recent radix tree variant designed for main memory,

- the  $CSB^+$ -tree [18], a cache-sensitive variant of the  $B^+$ -tree,

- a binary search (BS) on a static array,

- and a B<sup>+</sup>-tree [1] as baseline approach.

For ART and CSB<sup>+</sup>, we used implementations provided by the authors. For CSB<sup>+</sup>, we had to implement range queries. We consider BS as the only index structure that is read-only by design.

Our test system consists of the following hardware: a Intel Xeon E5-2620 CPU with 6 cores, 12 threads, 15 MB Level 3 Cache, 256-bit SIMD registers (AVX) and a clock speed of 2 GHz. The evaluation system runs Linux and has 32 GB RAM. All experiments are single-threaded. All competitors including CSSL were compiled with GCC 4.8.4 using optimization -O3. We use PAPI [3] to collect performance counters.

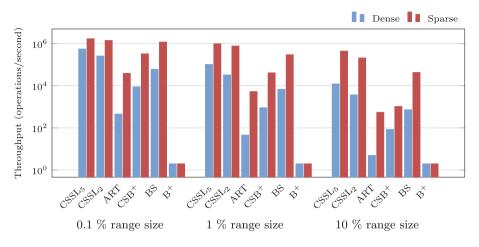

#### 5.1 Range Queries

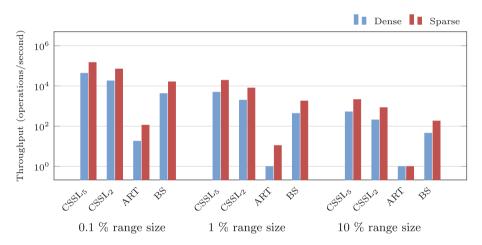

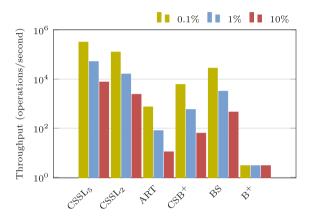

The goal of CSSL is to achieve high range query performance by employing a data layout tailored to the cache hierarchy of modern CPUs, which also can be traversed using SIMD instructions. In this section, we evaluate all approaches for

Fig. 4. Range query throughput for 16 M 32-bit integer keys w.r.t. different range sizes (logarithmic scale).

Fig. 5. Range query throughput for 256 M 32-bit integer keys w.r.t. different range sizes (logarithmic scale).

range queries on 16 M and 256 M 32-bit integer keys w.r.t. different range sizes (0.1%, 1%, and 10% of n). We determine to-be-evaluated ranges by selecting a random key from the set of indexed elements as lower bound and adding the range size to define the upper bound. For dense distribution, this creates a range covering  $|upper\_bound - lower\_bound|$  elements. For sparse distribution, ranges are created in the same way, yet contain less elements, which usually leads to higher throughput.

Figure 4 shows results for executing range queries on 16 M keys. Both CSSL configurations outperform all contestants for both key distributions and all

11

| Performance Counter   | $\mathrm{CSSL}_5$ | $\mathrm{CSSL}_2$ | ART              | $CSB^+$         | BS   | $B^+$            |

|-----------------------|-------------------|-------------------|------------------|-----------------|------|------------------|

| Dense                 |                   |                   |                  |                 |      |                  |

| CPU Cycles            | 202k              | 661k              | 501M             | $27 \mathrm{M}$ | 3.4M | 1,070M           |

| Branch Mispredictions | 12                | 15                | 813k             | 46              | 13   | 1.4k             |

| Level 3 Cache Hits    | 8k                | 24k               | 1.3M             | 49k             | 21k  | 1.6k             |

| Level 3 Cache Misses  | <b>21</b>         | 7.3k              | $2.7 \mathrm{M}$ | 243k            | 7.4k | $7.8 \mathrm{M}$ |

| TLB Misses            | <b>5</b>          | 13                | 1.6M             | 99              | 24   | 381k             |

| Sparse                |                   |                   |                  |                 |      |                  |

| CPU Cycles            | 5k                | 13k               | 4.5M             | 620k            | 59k  | 1,095M           |

| Branch Mispredictions | 13                | 16                | 16k              | 4.6k            | 13   | 832              |

| Level 3 Cache Hits    | <b>139</b>        | 373               | 14k              | 364             | 325  | 1.8k             |

| Level 3 Cache Misses  | <b>23</b>         | 165               | 28k              | 5.7k            | 278  | $7.4\mathrm{M}$  |

| TLB Misses            | 3                 | 5                 | 19k              | 958             | 10   | 369k             |

Fig. 6. Performance counters per range query on 16M 32-bit integer keys (10% range size).

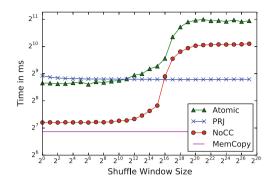

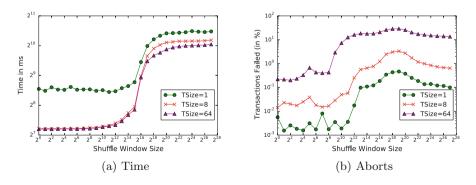

evaluated range sizes. In contrast to all competitors, CSSL does not need to follow pointers when iterating over matching keys but can use SIMD instructions to traverse the fast lane array, which results in an outstanding performance. The usage of SIMD instructions accelerates the performance of CSSL by a factor between 2 to 3.  $\text{CSSL}_5$  is faster than  $\text{CSSL}_2$ , which is due to the fact that fast lanes skip over five instead of only two elements, thus less keys have to be compared when searching for the range end (see Lines 17–28 of Algorithm 2). The sequential access pattern of CSSL has several benefits as revealed by analyzing performance counters (see Fig. 6). CSSL utilizes most prefetched cache lines, which leads to only few cache misses. Furthermore, CSSL generates less branch mispredictions than the contestants, because it processes mostly consecutive positions of the fast lane array. This benefits the number of CPU cycles needed to execute a range query.

For this experiment, BS is the second best competitor followed by  $CSB^+$ , ART and  $B^+$ . By eliminating pointer accesses and taking cache line sizes into account,  $CSB^+$  is able to reduce cache misses significantly compared to  $B^+$ -tree as shown in Fig. 6.

For 16 M dense keys,  $CSSL_5$  is up to 16.8X faster (10.4X for sparse data) than the second best competitor BS. Compared to all competitors, CSSL achieves the best relative performance for large range sizes, i.e., the speedup factor is the highest for large ranges, because it can traverse matching keys without chasing pointers. Figure 5 shows results for executing range queries on 256 M keys. Both  $CSB^+$  and  $B^+$  were not able to index this amount of data, because they ran out of memory. Again, CSSL outperforms BS and ART significantly.

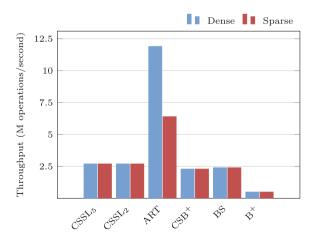

#### 5.2 Lookups

We evaluate the execution of single-key lookups. Lookups are a common operation in database management systems and needed for various use cases. Figure 7 shows our evaluation results concerning lookup performance on 16 M 32-bit integer keys for all contestants. ART achieves the best performance for both distributions. Furthermore, ART is the only competitor that can boost performance on dense keys, for instance by using lazy expansion; the remaining competitors show identical results on both distributions. CSSL achieves the second best performance, closely followed by BS and CSB<sup>+</sup>. B<sup>+</sup> shows the worst performance. The density of fast lanes has almost no influence on executing lookups as CSSL<sub>2</sub> and CSSL<sub>5</sub> show an identical performance. ART is 4.4X faster than CSSL for dense keys, and 2.4X faster than CSSL for sparse keys.

In Fig. 8, we present performance counters per lookup on 16 M 32-bit integer keys for all competitors. ART produces no branch mispredictions and only few level 3 cache misses, while  $B^+$ -tree shows the worst performance parameters. As in the case of range queries, CSSL produces only few cache and TLB misses. Though being optimized for range queries, CSSL is able to achieve a lookup throughput that outperforms BS, CSB<sup>+</sup> and B<sup>+</sup> and is almost as fast as ART in the case of sparse keys.

#### 5.3 Mixed Workload

Many real-world applications do neither use lookups nor range queries exclusively, but employ a mix of both. We investigate the throughput when executing a mixed workload consisting of an equal number of lookups and range queries. In this experiment, we run a benchmark of 1 M randomly generated queries, i.e., 500 k lookups and 500 k range queries, on 16 M dense and sparse 32-bit integer

Fig. 7. Lookup throughput for 16M 32-bit integer keys.

| Performance Counter   | $\mathrm{CSSL}_5$ | $\mathrm{CSSL}_2$ | ART        | $CSB^+$ | BS    | $B^+$ |

|-----------------------|-------------------|-------------------|------------|---------|-------|-------|

| Dense                 |                   |                   |            |         |       |       |

| CPU Cycles            | 927               | 956               | <b>209</b> | 1,068   | 1,036 | 5,889 |

| Branch Mispredictions | 9                 | 13                | 0          | 1       | 12    | 12    |

| Level 3 Cache Hits    | 11                | 8                 | <b>2</b>   | 3       | 21    | 28    |

| Level 3 Cache Misses  | 5                 | 8                 | <b>2</b>   | 5       | 9     | 39    |

| TLB Misses            | 1                 | 3                 | 2          | 3       | 4     | 20    |

| Sparse                |                   |                   |            |         |       |       |

| CPU Cycles            | 926               | 951               | 383        | 1,054   | 1,029 | 5,789 |

| Branch Mispredictions | 9                 | 13                | 0          | 3       | 12    | 12    |

| Level 3 Cache Hits    | 11                | 8                 | 5          | 3       | 20    | 29    |

| Level 3 Cache Misses  | 5                 | 8                 | 3          | 4       | 10    | 38    |

| TLB Misses            | 1                 | 3                 | 4          | 5       | 4     | 20    |

Fig. 8. Performance counters per lookup on 16M 32-bit integer keys.

Fig. 9. Throughput for a mixed lookup/range query workload on 16 M 32-bit integer keys (logarithmic scale).

keys. For range queries, we always use a range size of 500 k. Figure 9 shows the results of this experiment.

CSSL shows the best performance across all competitors when confronted with a mixed workload. As in the case of the range query benchmark, it is followed by BS, CSB<sup>+</sup>, ART and B<sup>+</sup>. Although ART shows the best single-key lookup performance, CSSL is magnitude faster when running a workload that also includes range queries besides lookups. This emphasizes the need for a fast range query implementation in index structures.

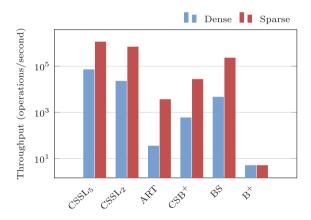

#### 5.4 Evaluation with Genomic Data

We evaluate all competitors on real-world data from the bioinformatics domain to investigate their performance when managing data that features a non-synthetic key distribution. As data source, we used the 1000 Genomes Project [19] that sequenced the whole genomes of 2,504 people from across the world. Data is provided in text files and can be downloaded from the project website for free. We indexed the genomic locations of all mutations that were found on chromosomes 1 and 2, i.e., 13,571,394 mutations in total, and queried them using randomly generated ranges of different sizes (0.1%, 1%, and 10% of the featured genomic interval). Figure 10 shows results of this benchmark.

Fig. 10. Range query throughput for genomic data (13,571,394 mutations) w.r.t. different range sizes (logarithmic scale).

As for synthetic data, CSSL dominates all competitors in executing range queries. Again, BS achieves the second best throughput, followed by CSB<sup>+</sup>, ART and B<sup>+</sup>. All competitors, except B<sup>+</sup>, show better performance for smaller range sizes, which is due to the fact that less mutations are covered, i.e., less keys need to be compared. For a range size of 10%, CSSL<sub>5</sub> is 16.7X faster than BS, 121.6X faster than CSB<sup>+</sup>, and 696X faster than ART.

#### 5.5 Space Consumption

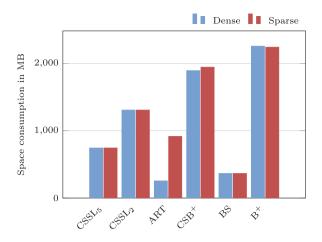

We compare the space consumption of all competitors for storing 16 M 32-bit integer keys, i.e., 64 MB of raw data (see Fig. 11). As already seen in the evaluation of search performance, ART is better suited for managing dense data than sparse data. For a dense key distribution, ART requires the least space followed by BS and CSSL. The tree-based approaches  $B^+$  and  $CSB^+$  show the worst memory consumption. For a sparse key distribution, BS achieves the best result followed by  $CSSL_5$  and ART. Again,  $B^+$  and  $CSB^+$  achieve the worst results. For 16M keys,  $CSSL_2$  requires 1.8X more memory than  $CSSL_5$ , because fast lanes hold more entries.

ART's space efficiency would probably grow for larger keys. Then, ART is able to employ further optimization techniques, e.g., path compression, that are not beneficial for small keys [13].

Fig. 11. Space consumption for 16 M 32-bit integer keys (lower is better).

#### 6 Related Work

Although concepts like tailored data layouts, index traversal with SIMD instructions, and pointer elimination have been investigated before [11, 17, 18], to the best of our knowledge, we are the first to combine these to accelerate range queries. Skip lists [16] were proposed as a probabilistic alternative to B-trees [5]. In the last years, they have been applied in multiple areas and have been adapted to different purposes, e.g., lock-free skip list [8], deterministic skip list [15], or concurrent skip list [10]. In [21], Xie et al. present a parallel skip list-based mainmemory index, PI, that processes query batches using multiple threads. CSSL is based on [15], but employs a cache-friendly data layout that is tailored to modern CPUs.

There are several others approaches addressing in-memory indexing [6,11-13,17,18], yet few specifically target range queries. CSS-trees [17] build a treebased dictionary on top of a sorted array that is tailored to cache hierarchy and can be used to search in logarithmic time. CSS-trees are static by design and need to be completely rebuilt when running updates. Rao and Ross [18] introduce the CSB<sup>+</sup>-tree, a cache-conscious B<sup>+</sup>-tree [7] variant, which minimizes pointer accesses and reduces space consumption. As shown in Sect. 5, CSSL outperforms CSB<sup>+</sup>-tree significantly for all workloads. Masstree [14] is an in-memory database that employs a trie of B<sup>+</sup>-trees as index structure. It supports arbitrary-length keys, which may be useful when indexing strings. We did not include Masstree in our evaluation, because its implementation is multi-threaded, which prevents a fair comparison. Instead, we considered its base index structure, the B<sup>+</sup>-tree, as competitor. In [22], Zhang et al. introduce a hybrid two-stage index that can be built on top of existing index structures like B-trees or skip lists. They also propose a paged-based skip list implementation that is tailored to main memory. In contrast to CSSL, it is completely static by design and does not exploit SIMD instructions.

The adaptive radix tree [13] is a main-memory index structure based on radix trees. ART employs adaptive node sizes and makes use of CPU features like SIMD instructions to boost search performance. While it achieves high lookup performance currently only superseded by hash tables [4], its support for range queries is much less efficient since these require traversing over the tree by chasing pointers. As shown in Sect. 5, CSSL outperforms ART significantly for range queries. We assume that the results of our comparison between CSSL and ART would carry over to other index structures based on prefix trees, such as generalized prefix trees [6], or KISS-Tree [12]. Another recent data structure is FAST [11], a binary search tree tuned to the underlying hardware by taking architecture parameters like page or cache line size into account. It achieves both thread-level and data-level parallelism, the latter by using SIMD instructions. Similar to CSSL, FAST does not need to access pointers when traversing the tree. However, FAST is optimized for lookup queries only, where it is clearly outperformed by ART [13]. Therefore, we did not include it in our evaluation.

# 7 Conclusions

We presented the Cache-Sensitive Skip List (CSSL), a main-memory index structure for efficiently executing range queries on modern processors. CSSL linearizes fast lanes to achieve a CPU-friendly data layout, to reduce cache misses, and to enable the usage of SIMD instructions. We compared CSSL with three mainmemory index structures, the adaptive radix tree, a CSB<sup>+</sup>-tree, and binary search, and one baseline, a B<sup>+</sup>-tree. CSSL outperforms all competitors when executing range queries on synthetic and real data sets. Even when confronted with a mixed key/range workload, CSSL achieves the best results in our evaluation. CSSL's search performance and memory consumption is influenced by the number of elements each fast lane skips over (1/p). Sparse fast lanes show better results regarding memory consumption and range query execution.

In future work, we will add multithreaded query execution to further accelerate read performance. We plan to work on both inter- and intra-query parallelism.

Acknowledgments. Stefan Sprenger and Steffen Zeuch are funded by the Deutsche Forschungsgemeinschaft through graduate school SOAMED (GRK 1651).

# References

- 1. B+ tree source code (C 1999). http://www.amittai.com/prose/bpt.c

- 2. Introduction to inteladvanced vector extensions. https://software.intel.com/en-us/articles/introduction-to-intel-advanced-vector-extensions

- 3. PAPI. http://icl.cs.utk.edu/papi/

- Alvarez, V., Richter, S., Chen, X., Dittrich, J.: A comparison of adaptive radix trees and hash tables. In: 31st IEEE International Conference on Data Engineering (2015)

- 5. Bayer, R., McCreight, E.: Organization and maintenance of large ordered indices. In: SIGFIDET (1970)

- Boehm, M., Schlegel, B., Volk, P.B., Fischer, U., Habich, D., Lehner, W.: Efficient in-memory indexing with generalized prefix trees. In: BTW (2011)

- 7. Comer, D.: Ubiquitous B-tree. ACM Comput. Surv. 11(2), 121–137 (1979)

- Fomitchev, M., Ruppert, E.: Lock-free linked lists and skip lists. In: Proceedings of 23rd Annual ACM Symposium on Principles of Distributed Computing, pp. 50–59 (2004)

- Hakenberg, J., Cheng, W.Y., Thomas, P., Wang, Y.C., Uzilov, A.V., Chen, R.: Integrating 400 million variants from 80,000 human samples with extensive annotations: towards a knowledge base to analyze disease cohorts. BMC Bioinf. 17(1), 1 (2016)

- 10. Herlihy, M., Lev, Y., Luchangco, V., Shavit, N.: A provably correct scalable concurrent skip list. In: Conference on Principles of Distributed Systems (2006)

- Kim, C., Chhugani, J., Satish, N., Sedlar, E., Nguyen, A.D., Kaldewey, T., Lee, V.W., Brandt, S.A., Dubey, P.: FAST: fast architecture sensitive tree search on modern CPUs and GPUs. In: Proceedings of the International Conference on Management of Data, pp. 339–350 (2010)

- Kissinger, T., Schlegel, B., Habich, D., Lehner, W.: KISS-Tree: Smart latch-free in-memory indexing on modern architectures. In: Proceedings of the Eighth International Workshop on Data Management on New Hardware, pp. 16–23 (2012)

- Leis, V., Kemper, A., Neumann, T.: The adaptive radix tree: ARTful indexing for main-memory databases. In: 29th IEEE International Conference on Data Engineering (2013)

- 14. Mao, Y., Kohler, E., Morris, R.T.: Cache craftiness for fast multicore key-value storage. In: Proceedings of the Seventh EuroSys Conference, pp. 183–196 (2012)

- Munro, J.I., Papadakis, T., Sedgewick, R.: Deterministic skip lists. In: Proceedings of the Third Annual ACM-SIAM Symposium on Discrete Algorithms, pp. 367–375 (1992)

- Pugh, W.: Skip lists: a probabilistic alternative to balanced trees. Commun. ACM 33(6), 668–676 (1990)

- Rao, J., Ross, K.A.: Cache conscious indexing for decision-support in main memory. In: Proceedings of 25th International Conference on Very Large Data Bases, pp. 78–89 (1999)

- Rao, J., Ross, K.A.: Making B<sup>+</sup>-trees cache conscious in main memory. In: Proceedings of the 2000 ACM SIGMOD International Conference on Management of Data, pp. 475–486 (2000)

- The 1000 Genomes Project Consortium: A global reference for human genetic variation. Nature 526(7571), 68–74 (2015)

- Xie, X., Lu, J., Kulbokas, E., Golub, T.R., Mootha, V., Lindblad-Toh, K., Lander, E.S., Kellis, M.: Systematic discovery of regulatory motifs in human promoters and 3' UTRs by comparison of several mammals. Nature 434(7031), 338–345 (2005)

- Xie, Z., Cai, Q., Jagadish, H., Ooi, B.C., Wong, W.F.: PI: a parallel in-memory skip list based index. arXiv preprint (2016). arXiv:1601.00159

- Zhang, H., Andersen, D.G., Pavlo, A., Kaminsky, M., Ma, L., Shen, R.: Reducing the storage overhead of main-memory OLTP databases with hybrid indexes. In: Proceedings of the International Conference on Management of Data, pp. 1567– 1581 (2016)

# Exploit Every Cycle: Vectorized Time Series Algorithms on Modern Commodity CPUs

Bo Tang<sup>1( $\boxtimes$ )</sup>, Man Lung Yiu<sup>1</sup>, Yuhong Li<sup>2</sup>, and Leong Hou U<sup>2</sup>

<sup>1</sup> Hong Kong Polytechnic University, Hung Hom, Hong Kong {csbtang,csmlyiu}@comp.polyu.edu.hk

<sup>2</sup> University of Macau, Av. Padre Tomás Pereira, Taipa, Macau

$\{yb27407, ryanlhu\}$ @umac.mo

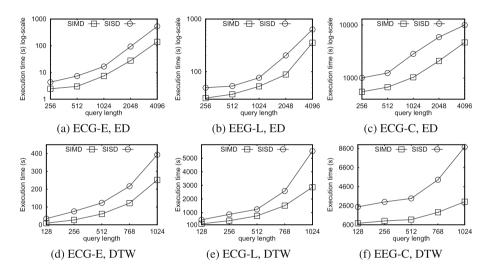

Abstract. Many time series algorithms reduce the computation cost by pruning unpromising candidates with lower-bound distance functions. In this paper, we focus on an orthogonal research direction that further boosts the performance by unlocking the potentials of modern commodity CPUs. First, we conduct a performance profiling on existing algorithms to understand where does time go. Second, we design vectorized implementations for lower-bound and distance functions that can enjoy characteristics (e.g., data parallelism, caching, branch prediction) provided by CPU. Third, our vectorized methods are general and applicable to many time series problems such as subsequence search, motif discovery and kNN classification. Our experimental study on real datasets shows that our proposal can achieve up to 6 times of speedup.

#### 1 Introduction

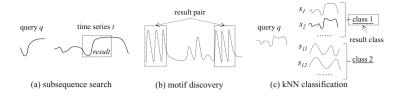

Time series data has various applications in medical diagnosis, speech processing, climate analysis, financial analysis, etc. It has attracted extensive research in the literature [4,9,14,20–22,25,30]. We illustrate representative problems in Fig. 1: (a) the subsequence search problem, which takes a query sequence q and finds its most similar subsequence  $t_c$  of a time series t, (b) the motif discovery problem, which reports the most similar pair of subsequences in a time series t, and (c) the kNN classification problem. These problems typically use the Euclidean Distance (ED) and Dynamic Time Warping (DTW) as the similarity measure.

These problems are computation bound rather than disk I/O bound [22]. Many time series algorithms have been evaluated on commodity CPU [4,9,14, 20–22,25,30] in single machine. These works focus on devising lower-bound distance functions to prune unpromising candidates and thus reduce calling expensive distance computations.

Even with these effective lower bounds, the above time series problems are still computation intensive, especially for increasingly long time series nowadays (e.g., medical physiological signals<sup>1</sup>). For example, the subsequence search on a trillion scale time series [22] would take 3.1 hours (under the Euclidean distance) and 34 hours (under Dynamic Time Warping) on a commodity PC.

<sup>&</sup>lt;sup>1</sup> http://www.physionet.org/physiobank/.

<sup>©</sup> Springer International Publishing AG 2017

S. Blanas et al. (Eds.): ADMS 2016/IMDM 2016, LNCS 10195, pp. 18–39, 2017. DOI: 10.1007/978-3-319-56111-0\_2

Fig. 1. Problems on time series data

Nevertheless, existing techniques overlook the characteristics of CPU and they have not studied the effect of those characteristics on the CPU time. In general, the CPU time consists of (i) busy cycles, for executing instructions, and (ii) stall cycles, for waiting for instructions or data.

We raise the following questions:

Q1: "In these algorithms, where does time go?"

To answer this question, we profile the performance [3,27] of existing timeseries algorithms (cf. Sect. 3). Surprisingly, most of the CPU time (70%) is spent on stalling.

Q2 "What cause CPU stall cycles?"

According to our performance profiling, the CPU stall is mainly (more than 80%) caused by branch mispredictions, cache misses, and ALU stall in lowerbound and distance functions.

Q3 "How to reduce CPU stall cycles in modern CPUs?"

Modern CPUs have built-in hardware for branch prediction, caching, and processing vector data efficiently (through SIMD instructions). Recent researches have utilized these characteristics to offer speedup on different problems like join [10], sorting [11], set intersection [16]. In this paper, we will design efficient implementations for lower-bound and distance functions by exploiting the characteristics of modern commodity CPUs. Note that our research direction is orthogonal to the development of lower-bound functions [4,9,14,20–22,25,30]. Besides, our proposed techniques are also applicable to mobile time series applications (e.g., continuous heart rate monitoring on Apple watch) as Apple mobile processors (e.g., A5) have supported advanced SIMD instructions since 2011<sup>2</sup>.

Our proposed techniques achieve performance gain through: (i) reducing branch mispredictions and cache misses, (ii) incorporating parallelism for vector processing in our computations. We then elaborate these issues in the following two paragraphs.

Conditional branches (e.g., if-then-else, case statements) are commonly used in the lower-bound and distance functions on time series. With branch prediction, a CPU can speculatively execute one path of a conditional branch. A correct prediction can improve the performance due to the CPU's instruction pipeline. However, if the prediction is wrong (i.e., *branch misprediction*), then many CPU cycles will be wasted to flush the instruction pipeline, flush and

fetch the relevant data, and restart the execution for the other branch. Therefore, it is desirable to rewrite algorithms to use fewer branching statements and avoid cache pollution. Also, we need to reduce non-compulsory cache misses brought by random memory accesses in our algorithms.

Data-intensive functions, like lower-bound and distance functions on time series, execute certain arithmetic operations (e.g., multiplication, division) that incur many CPU cycles and thus cause ALU stall. To reduce ALU stall, we use SIMD instructions to process multiple data values per instruction. For example, a SIMD division instruction takes two vectors of values  $V_a$  and  $V_b$  as input, and perform division  $V_a[i]/V_b[i]$  for each position *i* simultaneously. In this paper, we present vectorized implementations for lower-bound and distance functions by using SIMD. In addition, our vectorized implementations are designed to avoid using conditional branches.

Besides, our proposed techniques are generic and applicable to many time series problems (e.g., subsequence search, motif discovery, kNN classification). In summary, our contributions are:

- We profile the performance of existing time series algorithms and summarize the key insights (Sect. 3).

- We design vectorized implementations for lower-bound and distance functions. They incur fewer branch mispredictions, cache misses, and ALU stall (Sect. 4).

- We evaluate the efficiency of our proposed techniques for different time series algorithms on different datasets. Our techniques can achieve up to 6 times of speedup (Sect. 5).

The rest of this paper is organized as follows. Section 2 clarifies the preliminaries of our research problem. We present the profiling of existing time series algorithms in Sect. 3. Then, we propose our vectorized implementations in Sect. 4, perform experimental evaluation on existing time series algorithms in Sect. 5. Finally, we discuss the related work in Sect. 6, and conclude this paper in Sect. 7.

# 2 Preliminaries

#### 2.1 Fundamental Distance Measurement

In this work, we consider two most popular distance functions, i.e., Euclidean Distance (ED) and Dynamic Time Warping (DTW), in time series problems [13, 18, 19, 21, 22, 24]. We follow the suggestion from prior literatures [19, 22] that every subsequence should be Z-normalized in order to capture the similarity between the shapes of the sequences. Formally, the *i*-th value of a Z-normalized sequence  $\hat{q}$  can be calculated by  $\hat{q}[i] = \frac{q[i]-\mu_q}{\sigma_q}$ , where  $\mu_q$  and  $\sigma_q$  are the mean and standard deviation of q, respectively, and q[i] indicates the *i*-th element of q. For ease of presentation, we use dist(q, t) to denote the distance  $dist(\hat{q}, \hat{t})$  between Z-normalized subsequences in this paper.

**Euclidean Distance:** This is the most common similarity metric in time series [13, 19, 22, 25, 30] due to its simplicity. We give the definition of squared ED<sup>3</sup> in Eq. 1. It takes O(m) time for a query q of length m.

$$ED(q, t_c) = \sum_{i=1}^{m} (\hat{q}[i] - \hat{t}_c[i])^2$$

(1)

**Dynamic Time Warping:** DTW can capture the similarity of two sequences which may vary in time or have missing values. It is shown to be effective in time series applications [5, 18, 24]. DTW aims to find the optimal alignment (i.e., minimum distance) between two sequences, according to the following recursive equation.

$$DTW(q, t_c) = (\hat{q}[1] - \hat{t}_c[1])^2 + \min \begin{cases} DTW(\hat{q}[2...last], \hat{t}_c) \\ DTW(\hat{q}[2...last], \hat{t}_c[2...last]) \\ DTW(\hat{q}, \hat{t}_c[2...last]) \end{cases}$$

(2)

where  $\hat{q}[2...last]$  denotes the subsequence of  $\hat{q}$  containing values from the  $2^{nd}$  to the last offset. To avoid pathological warping (and reduce the computational cost), the literature [22] suggests to limit the warping length r such that  $\hat{q}[i]$  can be matched with  $\hat{t}_c[j]$  when  $|i-j| \leq r$ . This reduces the time complexity of DTW from  $O(m^2)$  to O(mr).

#### 2.2 Time Series Algorithms

In Table 1, we summarize the computation techniques (e.g., lower-bounds functions and distance functions) that can be used in three representative time series problems: subsequence search, motif discovery, and classification. Where LB prefixed function provides a lower bound of the exact distance.

| Problem                    | Technique(s)                                            | Distance |

|----------------------------|---------------------------------------------------------|----------|

| Subsequence search         | Early distance stop                                     | ED       |

| Motif discovery            | $LB_{Kim\mathbf{FL}}, LB_{Keogh}^{EQ}, LB_{Keogh}^{EC}$ | DTW      |

|                            | $LB_{ref}$ (uses reference indices)                     | ED       |

| Classification (by $kNN$ ) | Early distance stop                                     | ED       |

|                            | $LB_{Kim\mathbf{FL}}, LB_{Keogh}^{EQ}, LB_{Keogh}^{EC}$ | DTW      |

Table 1. Computation techniques and distance functions used in time series problems

**Subsequence search.** Formally, given a time series t of length n, a query q of length m, and a distance function  $dist(\cdot)$ , the subsequence search problem returns a length-m subsequence  $t_c \in t$  such that  $dist(q, t_c)$  is the minimum (among all length-m subsequences in t).

$<sup>^3\,</sup>$  The squared distance preserves the relative ordering of distances, and it avoids expensive square root calculations.

To the best of our knowledge, UCR Suite [22] is the state-of-the-art solution for the subsequence search problem. It adopts the filter-and-refinement paradigm to reduce exact distance computations. Let bsf be the best-so-far distance obtained during the search process. For ED subsequence search, UCR Suite does not apply any lower-bound function. It accumulates the distance step-by-step and early stops the distance computation  $dist(q, t_c)$  as soon as the accumulated value exceeds bsf. For DTW subsequence search, UCR Suite examines each candidate subsequence  $t_c$  and applies lower-bound functions on  $t_c$  in ascending order of their computation cost: first  $LB_{KimFL}$ , then  $LB_{Keogh}^{EQ}$  and finally  $LB_{Keogh}^{EC}$ .  $t_c$ gets pruned as soon as some  $LB(q, t_c)$  exceeds bsf. If  $t_c$  survives, then UCR Suite executes the distance function on  $t_c$ . We proceed to introduce these lower-bound functions as follows.

$\underline{LB_{Kim}}$  is derived from the **F**irst and the **L**ast sequence values, taking only O(1) time to compute. It is defined as

$$LB_{KimFL}(q, t_c) = (\hat{q}[1] - \hat{t}_c[1])^2 + (\hat{q}[m] - \hat{t}_c[m])^2$$

(3)

$LB_{Keogh}^{EQ}$  is derived from the distance between the candidate subsequence  $\hat{t}_c$ and the envelop of  $\hat{q}$ . Given the warping length r, the upper and lower envelop of  $\hat{q}$  are defined as  $\hat{q}^u[i] = \max_{j=i-r}^{i+r} \hat{q}[j]$  and  $\hat{q}^l[i] = \min_{j=i-r}^{i+r} \hat{q}[j]$ , respectively, Accordingly, we have

$$LB_{Keogh}^{EQ}(q,t_c) = \sum_{i=1}^{m} \begin{cases} (\hat{t}_c[i] - \hat{q}^u[i])^2 & \text{if } \hat{t}_c[i] > \hat{q}^u[i] \\ (\hat{t}_c[i] - \hat{q}^l[i])^2 & \text{if } \hat{t}_c[i] < \hat{q}^l[i] \\ 0 & \text{otherwise} \end{cases}$$

(4)

$LB_{Keogh}^{EC}$  is derived similarly to  $LB_{Keogh}^{EQ}$  but the lower-bound is derived from the distance between the query and the envelop of  $\hat{t}_c$  (i.e., switching roles).

**Motif Discovery.** Formally, given a time series t of length n, and a query length m, the motif discovery problem returns a pair of length-m subsequences  $t_c, t'_c \in t$  such that the Euclidean distance  $ED(t_c, t'_c)$  is the minimum among all pairs.

MK [20] is a representative solution for motif discovery. To avoid examining every subsequence pair, it proposes a reference based lower-bound. Given a set of subsequences and their distances to a set of references R, the lower-bound of two subsequences  $t_a$  and  $t_b$  can be derived as follows.

$$LB_{ref}(t_a, t_b) = \max_{\substack{r_i \in R \\ r_i \in R}} |distRef[r_i][t_a] - distRef[r_i][t_b]|$$

(5)

where  $distRef[r_i][t] = ED(r_i, t)$ .

MK first constructs a sorted list of every subsequence in terms of their distances to a reference. Intuitively, if the lower-bound of every  $1^{st}$  neighbor pair (in terms of their positions in the sorted list) is worse than bsf, then it is not necessary to examine further neighbor pairs (e.g.,  $2^{nd}$  neighbor pairs) due to the monotonicity of the sorted list. Thereby, MK iteratively examines the subsequence pairs based on their sorted list positions. At the end of an iteration, the search terminates when no neighbor pair has lower-bound better than bsf. **Classification.** ED and DTW are widely accepted for describing the similarity between time series in the classification problem [12]. We can apply the same techniques for subsequence search (i.e., early distance stop for ED and lower-bound techniques for DTW) to boost the classification process.

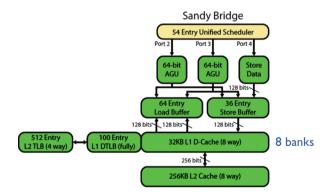

#### 2.3 Modern Commodity CPUs

Modern commodity CPUs share the following hardware characteristics that can be further exploited in algorithm design.

- (1) Single instruction multiple data: Modern commodity CPUs provide vector instructions (SIMD) operating on 256-bit vector registers that allow to perform the same instruction on multiple data values in parallel.

- (2) Hardware prefetcher: Modern commodity CPUs have built-in hardware prefetcher. It allows to prefetch additional lines of instruction or data into the L1 or L2 cache in CPU cores.

The modern commodity CPUs also have multiple cores and simultaneous multithreading technique. We leave the study on multi-threading issues for time series algorithms as future work. All algorithms in this paper run in single thread model by default.

# 3 Profiling of Algorithms

We first describe our experimental platform and then present the profiling result on existing time series algorithms.

#### 3.1 Experimental Setting

In all experiments, we use a machine with a 3.40 GHz Intel(R) Core(TM) i7-4770 CPU based on Haswell micro-architecture, 16 GB main memory, and a SSD (solid state drive, 256 GB capacity, 545 MB/s sequential read throughput). The CPU has 4 physical cores and supports simultaneous multithreading. The machine runs Ubuntu 14.04. All algorithms have been implemented in C++ and compiled by GNU C++ compiler with level 3 optimization.

We use the following real datasets and list their information in Table 2. All datasets are stored in the SSD.

• For the subsequence search problem, we use three datasets. Both  $\mathbf{ECG}-\mathbf{E}^4$  and  $\mathbf{ECG}-\mathbf{L}^5$  are electrocardiography (ECG) recordings, and we use the same query sequences (of length 421) as in [22] as the default query sequences.  $\mathbf{EEG}-\mathbf{C}^6$  contains electroencephalography (EEG) recordings, and we randomly extract query sequences (of length 128) from the epileptic seizure recording as in [26]. For each dataset, we follow the experimental methodology in [22], and obtain a single time series by concatenating all data sequences.

<sup>&</sup>lt;sup>4</sup> http://www.physionet.org/physiobank/database/edb/.

<sup>&</sup>lt;sup>5</sup> http://www.physionet.org/physiobank/database/ltstdb/.

<sup>&</sup>lt;sup>6</sup> http://www.physionet.org/pn6/chbmit/.

- For the kNN classification problem, we use **Weather**<sup>7</sup> dataset, which contains the temperature data extracted from weather forecast records. It contains 11,508 sequences, each sequence in Weather corresponds to a one-year time series collected from 5,936 locations. We use the attribute "Country" as the class attribute. We randomly choose data sequences as queries and exclude them from the data.

- For the motif discovery problem, we use two datasets: EEG-MK<sup>8</sup> and TAO-MK [19].

#### 3.2 Measurement Methodology

**Program execution time:** According to the Intel performance analysis manual [1], the program execution time  $(T_R)$  consists of: computation time  $(T_C)$ , branch misprediction stall  $(T_{Br})$ , backend stall  $(T_{Be})$ , and frontend stall  $(T_{Fe})$ . The computation time  $(T_C)$  is regarded as '*CPU busy*', and the rest as '*CPU stall*'. The backend stall occurs when the requested resource is being held-up in back end. It includes ALU stall  $(T_{ALU})$  and memory stall  $(T_{Cache})$ .  $T_{ALU}$  is the ALU execution unit stall, which is caused by the execution of arithmetic operations (e.g., divide, square root) that require many cycles.  $T_{Cache}$  is the memory-bound stall, which is caused by L1 data cache misses, L2 cache misses, L3 cache misses or TLB cache misses.

| Dataset | Sequence length     | Data size          | Problem                    |

|---------|---------------------|--------------------|----------------------------|

| ECG-E   | $1.60 \cdot 10^{8}$ | $611\mathrm{MB}$   | Subsequence search         |

| ECG-L   | $1.89 \cdot 10^9$   | $7.06\mathrm{GB}$  |                            |

| EEG-C   | $1.01\cdot 10^{10}$ | $37.5\mathrm{GB}$  |                            |

| EEG-MK  | $1.80 \cdot 10^5$   | $704\mathrm{KB}$   | Motif discovery            |

| TAO-MK  | $7.42 \cdot 10^{5}$ | $2.82\mathrm{MB}$  |                            |

| Weather | $1.81 \cdot 10^3$ , | $19.86\mathrm{MB}$ | $k{\rm NN}$ classification |

Table 2. Dataset information

We summarize the breakdown of execution time in a CPU as follows:

$$T_R = T_C + T_{stall}$$

; where  $T_{Stall} = T_{Br} + T_{ALU} + T_{Cache} + T_{Fe}$

**Profiling experiments:** To measure the above components of CPU time, we used PAPI [8] to obtain hardware performance counters from CPU, e.g., the number of stall cycles and the number of CPU cycles. In each subsequence search and classification experiment, we report the average CPU time over 10 queries.

$<sup>^{7}</sup>$  http://data.gov.uk/metoffice-data-archive.

<sup>&</sup>lt;sup>8</sup> http://www.cs.ucr.edu/~mueen/OnlineMotif/index.html.

To ensure the confidence level, we repeat running each query until the maximum standard deviation of the important counters (UOPS\_RETIRED:RETIRE\_SLOTS, CPU\_CLK\_UNHALTED:THREAD\_P) is less than 3%.

**Experimental reproducibility:** For the sake of experimental reproducibility, we have posted the datasets and source codes at  $[2]^9$ .

### 3.3 Identifying the Performance Bottleneck

In this section, we profile the performance of existing solutions and then identify the performance bottleneck. We conduct experiments to profile the performance of representative solutions: (i) UCR Suite [22] for the subsequence search problem, (ii) MK [20] for the motif discovery problem, and (iii) kNN classification [22] for the classification problem.

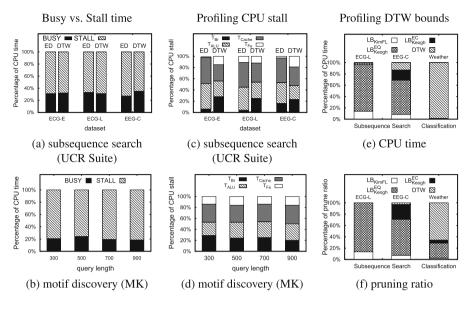

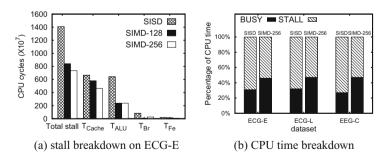

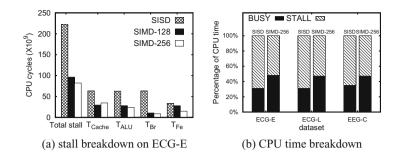

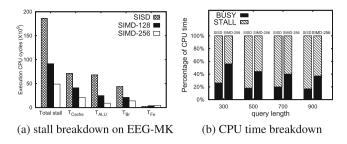

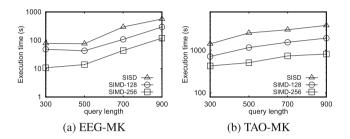

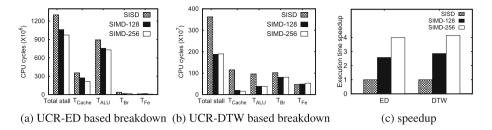

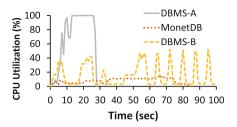

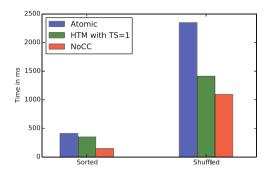

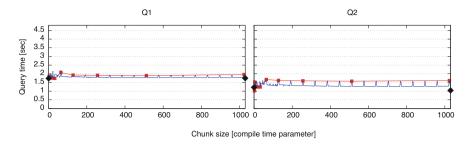

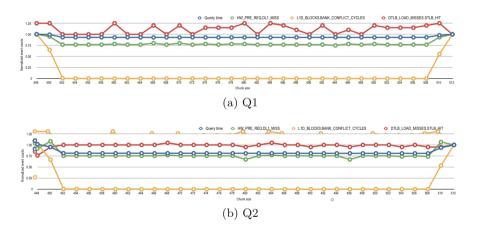

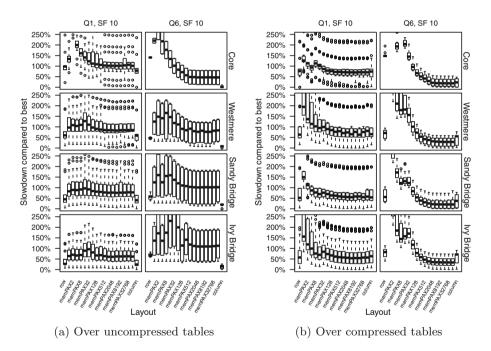

**CPU stall and CPU busy:** Figures 2(a) and (b) report the CPU time breakdown of existing solutions into *busy* time and *stall* time, for subsequence search and motif discovery, respectively.

Observation: The majority (65–70%) of the CPU time is spent on stalling (i.e., wasted CPU cycles).

**CPU stall breakdown:** We then delve into CPU stall and plot the breakdown of CPU stall time in Figs. 2(c) and (d).

Observation: The CPU stall is dominated (more than 80%) by ALU stall, cache misses, and branch mispredictions penalties.

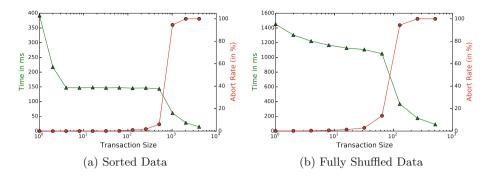

**CPU time of different functions:** The DTW function and its lower-bound functions  $(LB_{KimFL}, LB_{Keogh}^{EQ}, LB_{Keogh}^{EC})$  are applicable to the subsequence search problem and the classification problem [22]. We profile the performance of [22] on these two problems in Fig. 2(e). Different functions incur different portions of time and pruning ratio (cf. Fig. 2(f)) in different scenarios. For example, lower-bound functions  $LB_{Keogh}^{EQ}, LB_{Keogh}^{EC}$  dominate the time for subsequence search. However, the DTW computation incurs more time in kNN classification problems.

Observation: Different time series problems spend very different proportions of time on different functions. Therefore, it is important to optimize the computation of both lower-bound functions  $LB_{Keogh}^{EQ}$ ,  $LB_{Keogh}^{EC}$  and the DTW function.

# 4 Accelerating Distance Functions with SIMD

As shown in the previous section, the majority of CPU stall is caused by ALU stall, cache misses and branch mispredictions. In this section, we will design vectorized implementations for exact distance and lower-bounds functions to reduce those stalls. We will also evaluate the efficiency of our implementations with experiments.

$<sup>^9</sup>$  For consistency, we use the 'float' data type to represent time series values in all evaluated methods.

Fig. 2. Profile existing solutions

#### 4.1 How Do SIMD Instructions Reduce Stall?

**SIMD Vectorization: Reduce ALU Stall.** The ALU stall is caused by the execution of arithmetic operations that require many CPU cycles. For example, the 'division' instruction for two floating-point values takes 24 CPU cycles [1].

Modern CPU provides SIMD instructions to perform the same instruction (e.g.,  $+, -, \times, /, \min, \max$ ) on multiple data values in parallel. For instance, Intel i7-4770 and AMD Phenom II support the AVX2 instruction set (SIMD instructions on 256-bit registers). The SIMD instruction simd\_div (e.g., \_mm256\_div\_ps in AVX2) performs division on 8 pairs of values in two SIMD registers  $R_a$  and  $R_b$  simultaneously. It takes only 21 CPU cycles [1], which is much cheaper than executing the 'division' instruction on 8 pairs one-by-one (using 24\*8 = 192 cycles). Thus, SIMD instructions help reduce the ALU stall significantly.

Distance computation indeed fits well with SIMD instructions. As we illustrate in Fig. 3, we may divide subsequences into groups of length 8, and then apply SIMD instructions on each group to compute distances for pairs.

**Typical SIMD width:** Our CPU (Intel i7-4770) is a modern commodity CPU. It supports the following SIMD widths and instruction sets: (i) 64 bits (i.e., MMX instruction set), (ii) 128 bits (i.e., SSE instruction set), (iii) 256 bits (i.e., AVX instruction set). Since the MMX instruction set does not support floating-point values, it cannot be used in time series problems. Thus, we report the results for 128 bits (SIMD-128) and 256 bits (SIMD-256) in following experiments. For simplicity, we set 256 bits (SIMD-256) as default SIMD register.

Fig. 3. Using SIMD for distance computation

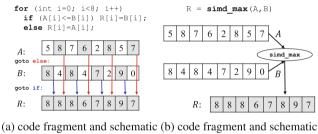

Hardware Prefetching: Reduce Branch Misprediction. Modern CPU is equipped with a branch prediction unit and it speculatively executes a conditional branch to maximize the utilization of CPU resources. A correct prediction can improve the performance due to the built-in instruction pipeline and hardware prefetching. However, incorrect prediction will bring cache pollution<sup>10</sup> and waste CPU cycles to flush instructions and restart execution.

for if-else statement

Fig. 4. Example for reducing branching statements

for SIMD max instruction

Some SIMD instructions help reduce branch misprediction. For example, for the code fragment in Fig. 4(a), the CPU may incur up to 8 branch mispredictions in the worst case. In contrast, the alternative implementation in Fig. 4(b) has no branch mispredictions because it uses a single instruction simd\_max instead of conditional branches.

We observe that DTW and its lower-bound functions (cf. Sect. 2) have many conditional branches. Therefore, we need to design SIMD implementations for DTW and its lower-bound functions without using conditional branches.

#### 4.2 Accelerating ED with SIMD

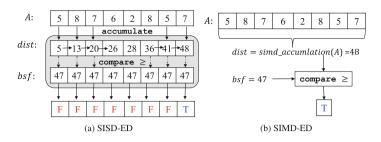

Before presenting our SIMD solutions, we first introduce the existing implementation of Euclidean distance. We call it as SISD-ED (cf. Algorithm 1) because it uses traditional CPU instructions, i.e., *Single Instruction, Single Data* (SISD).

<sup>&</sup>lt;sup>10</sup> http://en.wikipedia.org/wiki/Cache\_pollution.

According to Sect. 2, we perform Z-normalization on the subsequence  $t_c$  (cf. Line 3). It early stops the computation if the accumulated distance *dist* exceeds the best-so-far distance *bsf* (cf. Line 5).

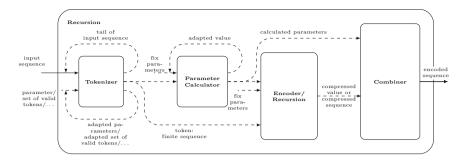

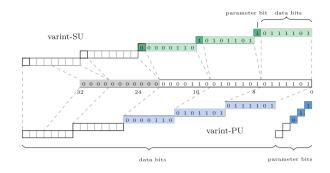

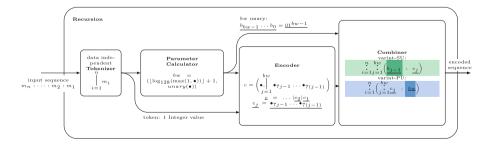

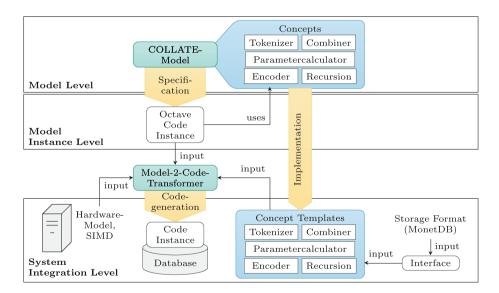

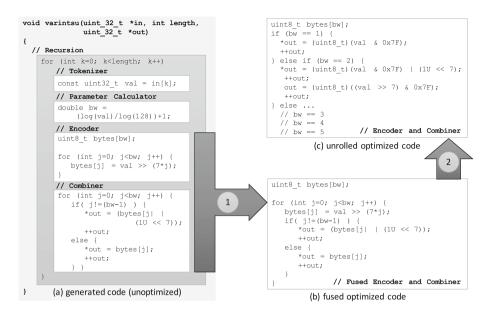

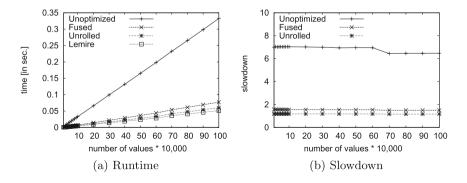

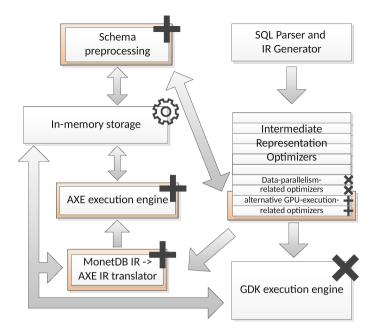

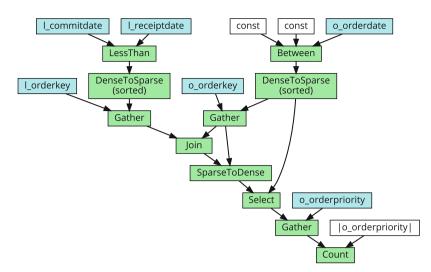

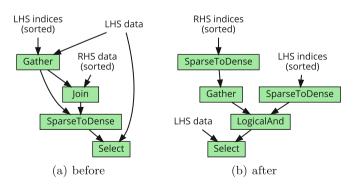

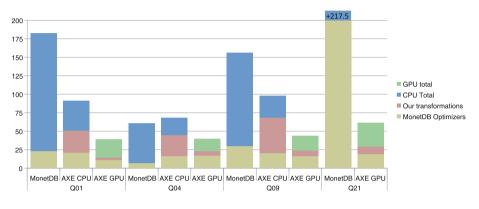

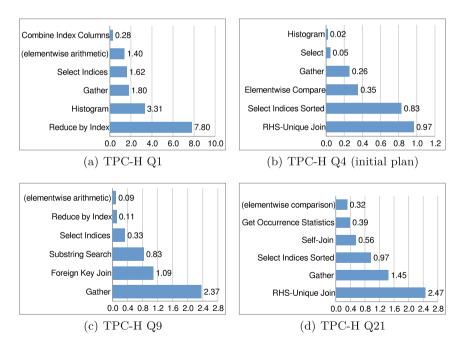

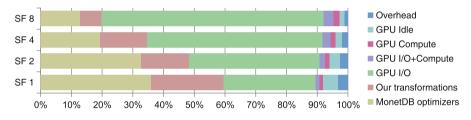

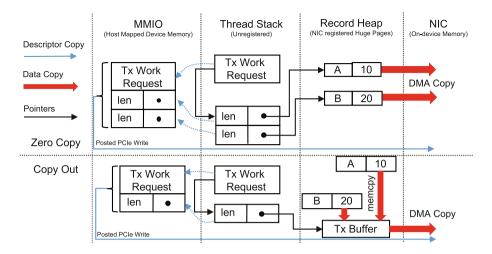

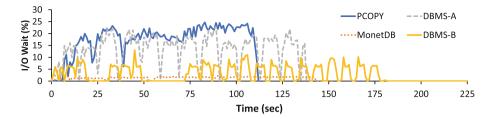

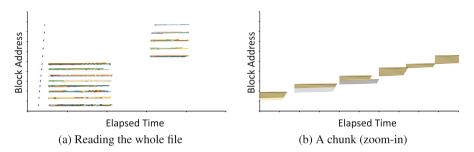

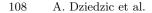

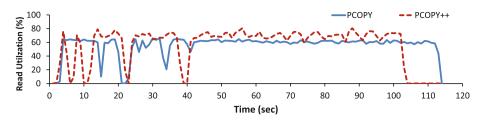

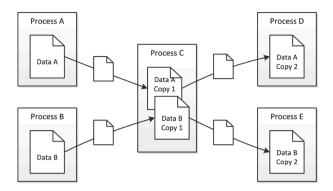

| Algorithm 1. SISD- $ED(q, t_c)$                                                                                                                                                                                                                                                                   |                                                                                     |