Claude Carlet M. Anwar Hasan Vishal Saraswat (Eds.)

# Security, Privacy, and Applied Cryptography Engineering

6th International Conference, SPACE 2016 Hyderabad, India, December 14–18, 2016 Proceedings

## Lecture Notes in Computer Science

## Commenced Publication in 1973 Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany

## 10076

More information about this series at http://www.springer.com/series/7410

Claude Carlet · M. Anwar Hasan Vishal Saraswat (Eds.)

## Security, Privacy, and Applied Cryptography Engineering

6th International Conference, SPACE 2016 Hyderabad, India, December 14–18, 2016 Proceedings

*Editors* Claude Carlet Universities of Paris 8 and Paris 13, LAGA Paris France

M. Anwar Hasan University of Waterloo Waterloo, ON Canada Vishal Saraswat CRRao AIMSCS Hyderabad India

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-49444-9 ISBN 978-3-319-49445-6 (eBook) DOI 10.1007/978-3-319-49445-6

Library of Congress Control Number: 2016957643

LNCS Sublibrary: SL4 - Security and Cryptology

#### © Springer International Publishing AG 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## Preface

This volume contains the papers accepted for presentation at the 6th International Conference on Security, Privacy, and Applied Cryptography Engineering 2016 (SPACE 2016), held during December 14–18, 2016, at the C.R. Rao Advanced Institute of Mathematics, Statistics and Computer Science (AIMSCS), University of Hyderabad, India. This annual event is devoted to various aspects of security, privacy, applied cryptography, and cryptographic engineering. This is indeed a very challenging field, requiring expertise from diverse domains, ranging from mathematics to solid-state circuit design.

This year we received 54 submissions from about 20 countries, out of which, after an extensive review process, 16 papers were accepted for presentation at the conference, and one shorter paper was accepted for short presentation. The submissions were evaluated based on their significance, novelty, technical quality, and relevance to the SPACE conference. The submissions were reviewed in a double-blind mode by at least three members of the 35-member Program Committee (one more if at least one of the authors was member of the Program Committee). The Program Committee was aided by 36 additional reviewers. The Program Committee meetings were held electronically, with intensive discussions.

The program also included eight invited talks and four tutorials on several aspects of applied cryptology, delivered by world-renowned researchers: Lejla Batina, Shivam Bhasin, Swarup Bhunia, Craig Costello, Joan Daemen, Christian Grothoff, Debdeep Mukhopadhyay, Emmanuel Prouff, François-Xavier Standaert, and Ingrid Verbauwhede. We sincerely thank the invited speakers for accepting our invitations in spite of their busy schedules.

Like its previous editions, SPACE 2016 was organized in co-operation with the International Association for Cryptologic Research (IACR). We are thankful to AIMSCS for being the gracious host of SPACE 2016.

There is a long list of volunteers who invested their time and energy to put together the conference, and who deserve accolades for their efforts. We are grateful to all the members of the Program Committee and the additional reviewers for all their hard work in the evaluation of the submitted papers. We thank Cool Press Ltd., owner of the EasyChair conference management system, for allowing us to use it for SPACE 2016, which was a great help. We also sincerely thank our publisher Springer for agreeing to continue to publish the SPACE proceedings as a volume in the *Lecture Notes in Computer Science* (LNCS) series. We are further very grateful to the members of the local Organizing Committee, including Sahana Subbarao, for their assistance to Vishal Saraswat in ensuring the smooth organization of the conference. Special thanks to our general chairs, Arun Kumar, Arun Agarwal and Sitaram Chamarty, for their constant support and encouragement.

#### VI Preface

Last, but certainly not least, our sincere thanks go to all the authors who submitted papers to SPACE 2016, and to all the attendees. The conference was made possible by you, and the proceedings are dedicated to you. We sincerely hope you find the program proceedings stimulating and inspiring.

December 2016

Claude Carlet M. Anwar Hasan Vishal Saraswat

## Organization

## **Chief Patron**

| V.K. Saraswat | NITI Aayog, India |

|---------------|-------------------|

|               |                   |

## Patron

Alok Joshi NTRO, India

## **General Co-chairs**

| M. Arun Kumar    | CRRao AIMSCS, India                  |

|------------------|--------------------------------------|

| Arun Agarwal     | SCIS, University of Hyderabad, India |

| Sitaram Chamarty | Tata Consultancy Services, India     |

## **Program Co-chairs**

Claude CarletUniversities of Paris 8 and Paris 13, LAGA, FranceM. Anwar HasanUniversity of Waterloo, CanadaVishal SaraswatCRRao AIMSCS, India

## **Steering Committee**

| Debdeep Mukhopadhyay  | IIT, Kharagpur, India |

|-----------------------|-----------------------|

| Veezhinathan Kamakoti | IIT, Madras, India    |

| Sanjay Burman         | CAIR-DRDO, India      |

## **Program Committee**

| Lejla Batina<br>Guido Marco Bertoni<br>Francesco Buccafurri | Radboud University Nijmegen, The Netherlands<br>STMicroelectronics, Italy<br>DIIES - Università Mediterranea di Reggio Calabria,<br>Italy |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Claude Carlet (Co-chair)                                    | University of Paris 8 and LAGA, France                                                                                                    |

| Rajat Subhra Chakraborty                                    | IIT, Kharagpur, India                                                                                                                     |

| Pandu Rangan                                                | IIT, Madras, India                                                                                                                        |

| Chandrasekaran                                              |                                                                                                                                           |

| Ashish Choudhury                                            | IIIT, Bangalore, India                                                                                                                    |

| Giovanni Di Crescenzo                                       | Applied Communication Sciences, USA                                                                                                       |

| Sylvain Guilley                                             | GET/ENST, CNRS/LTCI, France                                                                                                               |

| Indivar Gupta                                               | SAG, DRDO, India                                                                                                                          |

|                                                             |                                                                                                                                           |

| M. Anwar Hasan (Co-chair)  | University of Waterloo, Canada               |

|----------------------------|----------------------------------------------|

| Thomas Johansson           | Lund University, Sweden                      |

| Marc Joye                  | NXP Semiconductors, USA                      |

| Subhamoy Maitra            | Indian Statistical Institute, India          |

| Keith Martin               | Royal Holloway, University of London, UK     |

| Mitsuru Matsui             | Mitsubishi, Japan                            |

| Willi Meier                | FHNW, Switzerland                            |

| Debdeep Mukhopadhyay       | IIT, Kharagpur, India                        |

| Elisabeth Oswald           | University of Bristol, UK                    |

| Gilles Piret               | Oberthur Technologies, France                |

| Emmanuel Prouff            | SAFRAN Identity and Security, France         |

| Matthieu Rivain            | CryptoExperts, France                        |

| Bimal Roy                  | Indian Statistical Institute, Kolkata, India |

| Dipanwita Roy Chowdhury    | IIT, Kharagpur, India                        |

| Rei Safavi-Naini           | University of Calgary, Canada                |

| Rajeev Anand Sahu          | CRRao AIMSCS, Hyderabad, India               |

| Somitra Sanadhya           | IIT, Delhi, India                            |

| Vishal Saraswat (Co-chair) | CRRao AIMSCS, Hyderabad, India               |

| Palash Sarkar              | Indian Statistical Institute, Kolkata, India |

| Kannan Srinathan           | IIIT, Hyderabad, India                       |

| Sirisinahal Srinivasachary | DRDO, India                                  |

| François-Xavier Standaert  | UCL Crypto Group, Belgium                    |

| Y.V. Subba Rao             | University of Hyderabad, India               |

| Venkaiah V. Ch             | University of Hyderabad, India               |

| Amr Youssuf                | Concordia University, Canada                 |

|                            |                                              |

#### **Additional Reviewers**

Urbi Chatterjee Jean-Luc Danger Ashok Das Nicolas Debande Dhananjoy Dey Jacques Fournier Mohona Ghosh Michael Hutter Arpan Jati Anthony Journault Sabyasachi Karat Ilya Kizhvatov Philippe Loubet-Moundi Houssem Maghrebi Marco Martinoli Pedro Maat Massolino Filippo Melzani Prasanna Mishra Surya Prakash Mishra Nicolas Morin Saibal Pal Kostas Papagiannopoulos Goutam Paul Thomas Peters Stjepan Picek Jeyavijayan Rajendran Debapriya Basu Roy Durga Prasad Sahoo Santanu Sarkar Ahmadou Séré Takeshi Sugawara Ruggero Susella Daisuke Suzuki Toyohiro Tsurumaru Rei Uno Srinivas Vivek

## **Organizing Institution**

C.R. Rao Advanced Institute of Mathematics, Statistics and Computer Science (AIMSCS), Hyderabad, India

## **Organizing Chair**

Vishal Saraswat

CRRao AIMSCS, Hyderabad, India

**Abstracts of Tutorials**

## **Side-Channel Attacks on PKC**

Lejla Batina

Radboud University, Nijmegen, The Netherlands

**Abstract.** We give an introduction to physical attacks, in particular to passive attacks exploiting leakages of secret data from power consumption or EM emanations. Several issues such as leakage models, attack scenarios and countermeasures are outlined. We focus on public-key cryptosystems and their specifics with side-channel attacks and countermeasures. Recent attacks such as horizontal and online template attacks (OTA) are described and their experimental demonstrations on elliptic-curve cryptosystems are presented.

## **Sponge-Based Cryptography**

#### Joan Daemen

STMicroelectronics, Diegem, Belgium Radboud University, Nijmegen, The Netherlands

**Abstract.** Keccak, the winner of the SHA-3 competition, has at its core a permutation and uses this in a mode that is known as the sponge construction. Previous hash standards, from MD5 to SHA-2, all had at its core a block-cipher like primitive. Similarly, block ciphers have also been at the core of encryption, MAC computation and authenticated encryption schemes since the introduction of DES in the seventies. Recently, in the slipstream of Keccak, permutation-based alternatives have been proposed for all these cryptographic services. It turns out that they are at the same time more efficient and more elegant. In this tutorial we will give an introduction to unkeyed (sponge and SHA-3) and keyed (full-state keyed duplex and Keyak) permutation-based modes.

## Elliptic Curve Cryptography and Isogeny-Based Cryptography

Craig Costello

Microsoft Research, Redmond, WA, USA

**Abstract.** Elliptic curves have reigned supreme as a foundation for classical public-key cryptography due to the exponential hardness of the elliptic curve discrete logarithm problem (ECDLP). The gap between the hardness of the ECDLP and the subexponential hardness of problems like integer factorization and finite field discrete logarithms ultimately means that public-key cryptography based on elliptic curves is much faster and much more compact than its alternatives. The first half of this tutorial will give a gentle introduction to elliptic curve cryptography (ECC). All of the above classically difficult problems (including the ECDLP) become easy in the presence of a large-scale quantum computer. Thus, cryptographers are currently examining a range of new foundations that are believed to offer security against quantum adversaries. Interestingly, elliptic curves have also surfaced as a promising foundation in the post-quantum space, in particular in the realm of isogeny-based key exchange. The second half of this tutorial will give a gentle introduction to isogenies and their role in providing post-quantum primitives.

**Abstracts of Keynotes**

## Secure Hardware and Hardware-Enabled Security

Swarup Bhunia

University of Florida, Gainesville, USA

Abstract. Security has emerged as a critical design parameter for modern electronic hardware that builds the foundation for exciting new applications from smart wearables to smart cities. However, recent discoveries and reports on numerous attacks on microchips violate the well-regarded concept of hardware trust anchors. It has prompted system designers to develop wide array of design-for-security and test/validation solutions to achieve high security assurance. At the same time, emerging security issues and countermeasures have led to interesting interplay between security, energy, reliability, and test. Hardware faults and parametric variations, on one hand, have created new barriers to establishing hardware integrity in ever-complex semiconductor supply chain. On the other hand, reliability issues - in particular, those induced by process variations and aging effects, create new opportunities in designing powerful security primitives to protect against supply chain security issues as well as to enable better functional security solutions. This talk will highlight the interaction of hardware security issues and protection mechanisms with hardware faults and reliability issues. It will present new frontiers in hardware security with the rapidly diversifying application space and their symbiosis as well as conflicts with test. The talk will also cover promising role of hardware in security of various consumables, including food, supplements, and medicine.

## Practical Post-quantum Key Exchange from Supersingular Isogenies

Craig Costello

Microsoft Research, Redmond, WA, USA

Abstract. Academic groups, corporate bodies, and government agencies from all over the world are hastily examining a range of cryptographic primitives that are believed to remain secure in the presence of a large-scale quantum computer. Indeed, all of the currently standardized public-key cryptography will offer little or no security if such a computer is realized. In their Februrary 2016 report on post-quantum cryptography, NIST stated that "It seems improbable that any of the currently known algorithms can serve as a drop-in replacement for what is in use today," citing one challenge as being that quantum resistant algorithms have larger key sizes than the algorithms they will replace. While this statement is certainly applicable to many of the lattice- and code-based schemes, Jao and De Feo's 2011 supersingular isogeny Diffie-Hellman (SIDH) proposal is one post-quantum candidate that could serve as a drop-in replacement to existing internet protocols. Not only are high-security SIDH public keys smaller than their lattice- and code-based counterparts, they are even smaller than some of the traditional (i.e., finite field) Diffie-Hellman public keys. Moreover, in contrast to the proposed lattice- and code-based schemes (which are all either KEMs or encryption protocols), SIDH affords the option of restoring the elegant symmetry of the original Diffie-Hellman protocol.

This talk will give a detailed overview of isogeny-based key exchange, and will present a full-fledged software implementation of SIDH that is designed to provide 128 bits of security against a quantum adversary. We will conclude by pointing out some important open problems and interesting research directions in the realm of isogeny-based cryptography.

This talk is based on recent work with Patrick Longa and Michael Naehrig [1], and in turn on the original paper(s) by De Feo, Jao and Plût [2]. The two tutorials preceding the talk will (1) give a gentle introduction to elliptic curve cryptography, and (2) give a gentle introduction to isogenies.

#### References

- 1. Costello, C., Longa, P., Naehrig, M.: Efficient algorithms for super-singular isogeny Diffie-Hellman. In: CRYPTO 2016, pp. 572–601 (2016)

- De Feo, L., Jao, D., Plûut, J.: Towards quantum-resistant cryp-tosystems from supersingular elliptic curve isogenies. J. Math. Crypt. 8(3), 209–247 (2014)

## Contents

## Deep Learning and Fault Based Attacks

| Breaking Cryptographic Implementations Using Deep Learning Techniques<br>Houssem Maghrebi, Thibault Portigliatti, and Emmanuel Prouff                                                                                                                            | 3   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Cheap and Cheerful: A Low-Cost Digital Sensor for Detecting Laser Fault<br>Injection Attacks                                                                                                                                                                     | 27  |

| Comprehensive Laser Sensitivity Profiling and Data Register Bit-Flips<br>for Cryptographic Fault Attacks in 65 Nm FPGA                                                                                                                                           | 47  |

| Fault Based Almost Universal Forgeries on CLOC and SILC<br>Debapriya Basu Roy, Avik Chakraborti, Donghoon Chang,<br>S.V. Dilip Kumar, Debdeep Mukhopadhyay, and Mridul Nandi                                                                                     | 66  |

| Applied Cryptography                                                                                                                                                                                                                                             |     |

| Implementing Complete Formulas on Weierstrass Curves in Hardware<br>Pedro Maat C. Massolino, Joost Renes, and Lejla Batina                                                                                                                                       | 89  |

| Partially Homomorphic Encryption Schemes over Finite Fields<br>Jian Liu, Sihem Mesnager, and Lusheng Chen                                                                                                                                                        | 109 |

| Light Weight Key Establishment Scheme for Wireless Sensor Networks<br>Payingat Jilna and P.P. Deepthi                                                                                                                                                            | 124 |

| A Scalable and Systolic Architectures of Montgomery Modular<br>Multiplication for Public Key Cryptosystems Based on DSPs<br>Amine Mrabet, Nadia El-Mrabet, Ronan Lashermes,<br>Jean-Baptiste Rigaud, Belgacem Bouallegue, Sihem Mesnager,<br>and Mohsen Machhout | 138 |

| Iterative Ciphers                                                                                                                                                                                                                                                |     |

| Spectral Characterization of Iterating Lossy Mappings | 159 |

|-------------------------------------------------------|-----|

| Joan Daemen                                           |     |

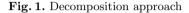

| Decomposed S-Boxes and DPA Attacks: A Quantitative Case Study<br>Using PRINCE                                                              | 179 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Ravikumar Selvam, Dillibabu Shanmugam, Suganya Annadurai,<br>and Jothi Rangasamy                                                           | 179 |

| GAIN: Practical Key-Recovery Attacks on Round-reduced PAEQ<br>Dhiman Saha, Sourya Kakarla, Srinath Mandava,<br>and Dipanwita Roy Chowdhury | 194 |

| Hardware Security                                                                                                                          |     |

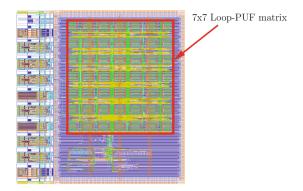

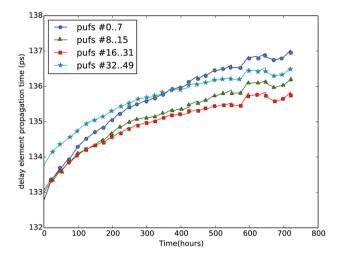

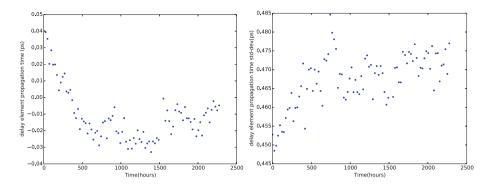

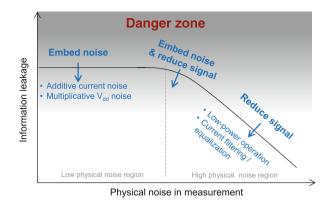

| Predictive Aging of Reliability of Two Delay PUFs<br>Naghmeh Karimi, Jean-Luc Danger, Florent Lozac'h,<br>and Sylvain Guilley              | 213 |

| Towards Securing Low-Power Digital Circuits with Ultra-Low-Voltage                                                                         |     |

| Vdd Randomizers                                                                                                                            | 233 |

| Security                                                                                                                                   |     |

| Enabling Secure Web Payments with GNU Taler<br>Jeffrey Burdges, Florian Dold, Christian Grothoff,<br>and Marcello Stanisci                 | 251 |

| Malware Characterization Using Windows API Call Sequences<br>Sanchit Gupta, Harshit Sharma, and Sarvjeet Kaur                              | 271 |

| VMI Based Automated Real-Time Malware Detector for Virtualized<br>Cloud Environment                                                        | 281 |

| Post-quantum Cryptology                                                                                                                    |     |

| Solving Binary $\mathcal{MQ}$ with Grover's Algorithm<br>Peter Schwabe and Bas Westerbaan                                                  | 303 |

| Ring-LWE: Applications to Cryptography and Their Efficient Realization<br>Sujoy Sinha Roy, Angshuman Karmakar, and Ingrid Verbauwhede      | 323 |

| NewHope on ARM Cortex-M<br>Erdem Alkim, Philipp Jakubeit, and Peter Schwabe                                                                | 332 |

## Leakage, Power and Fault Analysis

| Towards Fair and Efficient Evaluations of Leaking Cryptographic Devices: |     |

|--------------------------------------------------------------------------|-----|

| Overview of the ERC Project CRASH, Part I (Invited Talk)                 | 353 |

| François-Xavier Standaert                                                |     |

| A Methodology for the Characterisation of Leakages                       |     |

| in Combinatorial Logic                                                   | 363 |

| Guido Bertoni and Marco Martinoli                                        |     |

| Exploiting the Leakage: Analysis of Some Authenticated                   |     |

| Encryption Schemes                                                       | 383 |

| Donghoon Chang, Amit Kumar Chauhan, Naina Gupta, Arpan Jati,             |     |

| and Somitra Kumar Sanadhya                                               |     |

| Breaking Kalyna 128/128 with Power Attacks                               | 402 |

| Stephane Fernandes Medeiros, François Gérard, Nikita Veshchikov,         |     |

| Liran Lerman, and Olivier Markowitch                                     |     |

| Fault Injection Attacks: Attack Methodologies, Injection Techniques      |     |

| and Protection Mechanisms: A Tutorial                                    | 415 |

| Shivam Bhasin and Debdeep Mukhopadhyay                                   |     |

| Author Index                                                             | 419 |

| Autor muca                                                               | 717 |

**Deep Learning and Fault Based Attacks**

## Breaking Cryptographic Implementations Using Deep Learning Techniques

Houssem Maghrebi, Thibault Portigliatti, and Emmanuel  $\operatorname{Prouff}^{(\boxtimes)}$

SAFRAN Identity and Security, 18, Chaussée Jules César, 95520 Osny, France {houssem.maghrebi,thibault.portigliatti,emmanuel.prouff}@safrangroup.com

Abstract. Template attack is the most common and powerful profiled side channel attack. It relies on a realistic assumption regarding the noise of the device under attack: the probability density function of the data is a multivariate Gaussian distribution. To relax this assumption, a recent line of research has investigated new profiling approaches mainly by applying machine learning techniques. The obtained results are commensurate, and in some particular cases better, compared to template attack. In this work, we propose to continue this recent line of research by applying more sophisticated profiling techniques based on deep learning. Our experimental results confirm the overwhelming advantages of the resulting new attacks when targeting both unprotected and protected cryptographic implementations.

**Keywords:** Deep learning  $\cdot$  Machine learning  $\cdot$  Side channel attacks  $\cdot$  Template attack  $\cdot$  Unprotected AES implementation  $\cdot$  Masked AES implementation

## 1 Introduction

Side Channel Attacks. Side Channel attacks (SCA) are nowadays well known and most designers of secure embedded systems are aware of them. They exploit information leaking from the physical implementations of cryptographic algorithms. Since, this leakage (*e.g.* the power consumption or the electromagnetic emanations) depends on the internally used secret key, the adversary may perform an efficient key-recovery attack to reveal these sensitive data. Since the first public reporting of these threats [30], a lot of effort has been devoted towards the research on side channel attacks and the development of corresponding countermeasures.

Amongst side channel attacks, two classes may be distinguished.

- The so-called *profiling SCA* are the most powerful kind of SCA and consist of two steps. First, the adversary procures a copy of the *target device* and uses it to characterize the dependency between the manipulated data and the device behavior. Secondly, he performs a key-recovery attack on the target

© Springer International Publishing AG 2016

T. Portigliatti—Work done when the author was at SAFRAN Identity and Security.

C. Carlet et al. (Eds.): SPACE 2016, LNCS 10076, pp. 3–26, 2016.

DOI: 10.1007/978-3-319-49445-6\_1

device. The set of profiled attacks includes Template attacks [10] and Stochastic cryptanalyses (aka Linear Regression Analyses) [16, 47, 48].

- The set of so-called *non-profiling SCA* corresponds to a much weaker adversary who has only access to the physical leakage captured on the target device. To recover the secret key in use, he performs some statistical analyses to detect dependency between the leakage measurements and this sensitive variable. The set of non-profiled attacks includes Differential Power Analysis (DPA) [30], Correlation Power Analysis (CPA) [9] and Mutual Information Analysis (MIA) [20].

Side Channel Countermeasures. A deep look at the state-of-the-art shows that several countermeasures have been published to deal with side channel attacks. Amongst SCA countermeasures, two classes may be distinguished [36]:

- The set of so-called masking countermeasures: the core principle of masking is to ensure that every sensitive variable is randomly split into at least two shares so that the knowledge of a strict sub-part of the shares does not give information on the shared variable itself. Masking can be characterized by the number of random masks used per sensitive variable. So, it is possible to give a general definition for a  $d^{\text{th}}$ -order masking scheme: every sensitive variable Z is randomly split into d + 1 shares  $M_0, \dots, M_d$  in such a way that the relation  $M_0 \perp \dots \perp M_d = Z$  is satisfied for a group operation  $\perp$ (e.g. the XOR operation used in the Boolean masking, denoted as  $\oplus$ ) and no tuple of strictly less than d+1 shares depends on Z. In the literature, several provably secure higher-order masking schemes have been proposed (see for instance [13, 19, 44].).

- The set of so-called *hiding countermeasures*: the core idea is to render in making the activity of the physical implementation constant by either adding complementary logic to the existing logic [11] (in a hardware setting) or by using a *specific encoding* of the sensitive data [27,50] (in a software setting).

Machine Learning Based Attacks. A recent line of works has investigated new profiling attacks based on Machine Learning (ML) techniques to defeat both unprotected [5,23,28,32,34] and protected cryptographic implementations [21, 33]. These contributions focus mainly on two techniques: the Support Vector Machine (SVM) [14,57] and the Random Forest (RF) [45]. Practical results on several data-sets have demonstrated the ability of these attacks to perform successful key recoveries. Besides, authors in [23] have shown that the SVM-based attack outperforms the template attack when applied on highly noisy traces.

Mainly, ML-based attacks exploit the same discriminating criteria (*i.e.* the dependence between the sensitive data and some statistical moments of the leakage) as a template attack. Two major differences between these attacks exist. They are listed hereafter.

- The template attack approximates the data distribution by a multivariate Gaussian distribution (*aka Gaussian leakage assumption*) [10] whose parameters (*i.e.* the mean vector and the covariance matrix) are estimated during

the profiling phase. This implies that the statistical moments of the leakage distribution whose order is greater than 2 are not exploited which can make the attack sub-optimal and even ineffective in some contexts.

The ML-based attacks make no assumption on the data distribution and build classifications directly from the raw data-set.

Despite the fact that Gaussian leakage is a fairly realistic assumption in side channel context [35, 43], applying distribution-agnostic statistical techniques would appear to be a more rational approach.

**Our Contribution.** Over the past few years, there has been a resurgence of interest in using Deep Learning (DL) techniques which have been applied in several signal processing areas where they have produced interesting results [1,15]. Deep learning is a parallel branch of machine learning which relies on sets of algorithms that attempt to model high-level abstractions in data by using model architectures with multiple processing layers, composed of a sequence of scalar products and non-linear transformations called *activation functions* [51]. Several recent results have demonstrated that DL techniques have convincingly outperformed other existing machine learning approaches in image and automatic speech recognition.

In this work, we propose to apply DL techniques in side channel context. Actually, we highlight the ability of DL to build an accurate profiling leading to an efficient and successful side channel key recovery attack. Our experiments show that our proposed DL-based attacks are more efficient than the ML-based and template attacks when targeting either unprotected or masked cryptographic implementations.

**Paper Outline.** The paper is organized as follows. In Sects. 2 and 3, we provide an overview on machine learning and deep learning techniques. Then, in Sect. 4 we describe how to use deep learning techniques to perform a successful key recovery. This is followed in Sect. 5 by some practical attack experiments applied on unprotected and masked AES implementations. Finally, Sect. 6 draws general conclusions and opens some perspectives for future work.

#### 2 Overview on Machine Learning Techniques

Machine learning techniques have been developed and used in order to build efficient pattern recognition and features extraction algorithms. Mainly, ML techniques are divided into three categories depending on the learning approach: *unsupervised*, *semi-supervised* and *supervised*. In this paper, we focus on supervised and unsupervised learning techniques.

- Unsupervised learning is mainly used when profiling information (*i.e.* training data-set) is not available. So, the purpose is to ensure an efficient data partitioning without any prior profiling or data modeling. Two classic examples of unsupervised learning techniques are *clustering* (*e.g.* K-means [17]) and *dimensionality reduction* (*e.g.* Principal Component Analysis (PCA)). These techniques have been widely used in side channel contexts to perform either successful key recovery [24, 52] or some pre-processing of the physical leakage [4].

- Supervised learning refers to techniques that involve a training data-set<sup>1</sup> (aka labeled data-set) to build a model. Once the learning has been performed, a supervised learning algorithm is executed which returns, for a new incoming input, an output that is the most accurate one according to the previously learned model. Typical supervised learning techniques include neural networks [8], random forest [45] and support vector machines [14,57].

In the following sections we provide a survey of some supervised learning techniques and their applications in side channel analysis. All of them take as input a training data-set composed of vectors  $X^{(i)} = (x_1, \ldots, x_n) \in \mathbb{R}^n$  and their corresponding labels  $y_i \in \mathbb{R}$  (*e.g.* scores or values of the manipulated sensitive data). After the learning step, their goal is to associate a new vector X with the correct label y.

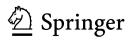

#### 2.1 Perceptron

The perceptron is the simplest neural network model [8]. It is a linear classifier that uses a learning algorithm to tune its weights in order to minimize a so-called loss function<sup>2</sup> as described in Fig. 1. We detail hereafter how perceptron works to perform classification:

- first, an input vector  $X = (x_1, \ldots, x_n) \in \mathbb{R}^n$  is presented as an entry to the perceptron.

- then, components of X are summed over the weights  $w_i \in \mathbb{R}$  of the perceptron connections (*i.e.*  $w_0 + \sum_{i=1}^n w_i x_i$ , with  $w_0$  being a bias<sup>3</sup>).

- finally, the output of the perceptron is computed by passing the previously computed sum to an *activation function*<sup>4</sup> denoted f.

<sup>&</sup>lt;sup>1</sup> The training data-set is composed of pairs of some known (input, output).

$<sup>^{2}</sup>$  The loss (*aka* cost, error) function quantifies in a supervised learning problem the compatibility between a prediction and the ground truth label (output). The loss function is typically defined as the negative log-likelihood or the mean squared error.

<sup>&</sup>lt;sup>3</sup> Introducing a value that is independent of the input shifts the boundary away from the origin.

<sup>&</sup>lt;sup>4</sup> In the case of the perceptron, the activation function is commonly a Heaviside function. In more complex models (*e.g.* the multilayer perceptron that we will describe in the next section), this function can be chosen to be a sigmoid function (tanh).

Fig. 1. Representation of a perceptron.

During the training phase, the perceptron weights, initialized at zeros or small random values, are learned and adjusted according to the profiling data-set  $(X^{(i)}, y_i)$ . By *e.g.* applying a *gardient descent* algorithm, the goal is to find/learn the optimal connecting weights moving the perceptron outputs as close as possible<sup>5</sup> to the correct labels/scores (*e.g.* to minimize the sum of squared differences between the labels  $y_i$  and the corresponding perceptron's output).

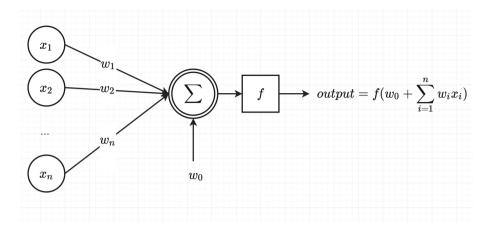

#### 2.2 Multilayer Perceptron

A Multilayer Perceptron (MLP) is nothing more than a specific way to combine perceptrons<sup>6</sup> in order to build a classifier for more complex data-sets [8]. As shown in Fig. 2, the information is propagated from the left to the right and each units (perceptrons) of a layer is connected to every unit of the previous layer in this model. This is called a *fully connected network*. Each neuron belongs to a layer and the number of layers is a parameter which has to be carefully chosen by the user.

An MLP is made of three different types of layers:

- Input Layer: in the traditional model, this layer is only an intermediate between the input data and the rest of the network. Thus the output of the neurons belonging to this layer is simply the input vector itself.

- Hidden layer: this layer aims at introducing some non-linearity in the model so that the MLP will be able to fit a non-linear separable data-set. Indeed, if the data that have to be learned are linearly separable, there is no need for any hidden layer. Depending on the non-linearity and the complexity of the data model that has to be fit, the number of neurons on the hidden layer or even the number of these layers can be increased. However, one hidden layer is sufficient for a large number of natural problems.

<sup>&</sup>lt;sup>5</sup> E.g. for the Euclidean distance.

<sup>&</sup>lt;sup>6</sup> Perceptrons are also called "units", "nodes" or neurons in this model.

Fig. 2. Example of MLP, where each node is a perceptron as described in Sect. 2.1.

Regarding the number of neurons on the hidden layers, it has been demonstrated that using a huge number of neurons can lead to *over-fitting* if the model that has to be learned is close to a linear one [8]. It means that the algorithm is able to correctly learn weights leading to a perfect fit with the training data-set while these weights are not representative of the whole data. On the other hand, the opposite may happen: for a complex data-set, using too few neurons on the hidden layers may lead the gradient minimization approach to fail in returning an accurate solution.

- Output layer: this is the last layer of the network. The output of the nodes on this layer are directly mapped to classes that the user intends to predict.

Training a multilayer perceptron requires, for each layer, the learning of the weighting parameters minimizing the loss function. To do so, the so-called *back-propagation* [8] can be applied. It consists in computing the derivative of the loss function with respect to the weights, one layer after another, and then in modifying the corresponding weights by using the following formula:

$$w_{ij} = -\frac{\partial E}{\partial w_{i,j}} \; \; ,$$

where E is the loss function and  $w_{i,j}$  denotes the weight of the connection between two neurons of indices (i, j).

In several recent works, MLP has been applied to perform successful side channel key recovery. For instance, in [21], authors have presented a neural network based side channel attack to break the masked AES implementation of the DPA contest V4 [55]. In fact, the authors of [21] assume that the adversary has access to the mask values during the profiling phase. Under this assumption, the proposed attack consists first in identifying the mask by applying a neural network mask recovery. Then, a second neural network based attack is performed to recover the secret key with a single trace. While the results of this work are quite interesting, the considered assumption is not always met in real world circumstances.

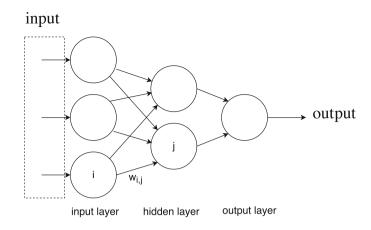

#### 2.3 Decision Trees and Random Forest

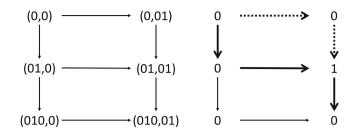

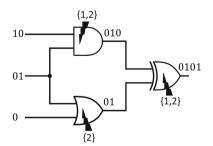

A decision tree is a tool involving binary rules to classify data [45]. It is made of a root, several nodes and leaves. Each leaf is associated to a label corresponding to the target value to be recovered. Each node that is not a leaf can lead to two nodes (or leaves). First, the input is presented to the root. It is then forwarded to one of the possible branch starting from this node. The process is repeated until a leaf is reached. An illustration of this process for a 2-bit XOR operation is depicted in Fig. 3.

A random forest is composed of many decision trees, each one working with a different subset of the training data-set [45]. On the top of all of the trees, the global output is computed through a majority vote among these classification trees outputs. RFs have been successfully applied in SCA context to defeat

**Fig. 3.** Partial graphical representation of a decision tree performing the XOR operation between 2 bits variables  $x_1$  and  $x_2$ . The leaves correspond to the XOR result.

cryptographic implementations [33,34]. In this paper, we will try to compare RF-based attack with deep learning ones in terms of key recovery effectiveness.

#### 2.4 Support Vector Machine

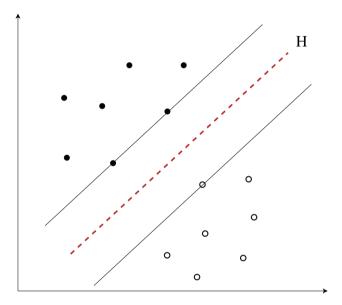

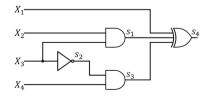

A support vector machine [14, 57] is a linear classifier that not only intends to find an hyper-plane to separate data classes but also intends to find the optimal one maximizing the margin between these classes as described in Fig. 4. To deal with non-linearly separable data-sets, it is possible for instance to use a *kernel function* for instance that maps these data into a feature space of higher dimensions in which the classes become linearly separable [49].

Fig. 4. Binary hyper-plane Classification.

In the side channel literature, several works have investigated the use of SVM towards performing successful attacks to break either unprotected [5,23,28,32, 34] or protected cryptographic implementations [33]. Actually, authors in [23] have demonstrated that when the Signal-to-Noise Ratio (SNR)<sup>7</sup> of the targeted data-set is very low, the SVM-based attack outperforms the template attack.

## 3 Overview on Deep Learning Techniques

For several reasons (mainly the *vanishing gradient problem* [25] and the lack of computational power), it was not possible to train many-layered neural networks

$<sup>^7</sup>$  The SNR is defined as the ratio of signal power to the noise power.

until a few years ago. Recent discoveries, taking full advantage of GPU for computations and using the *rectified linear unit function*  $(f : x \mapsto max(0, x))$  as an activation function instead of the classical sigmoid  $(g : x \mapsto \frac{1}{1+e^{-x}})$ , made it possible to stack many layers allowing networks to learn more and more abstract representation of the training data-set [29]. This is known as deep learning techniques [1]. One major difference between deep learning and usual machine learning is that the latter ones are classifiers usually working from human-engineered features while the former ones learn the features directly from the raw data before making any classification [6]. In the following sections, some of the most widely used learning techniques are detailed.

#### 3.1 Convolutional Neural Networks

A Convolutional Neural Network (CNN) is a specific kind of neural network built by stacking the following layers [31,40]:

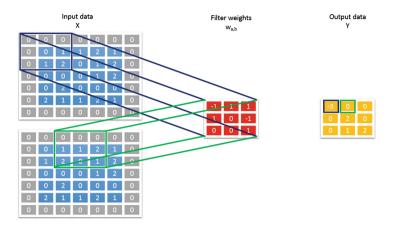

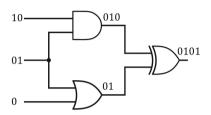

- A convolutional layer: on this layer, during the forward computation phase, the input data are convoluted with some filters. The output of the convolution is commonly called a *feature map*. It shows where the features detected by the filter can be found on the input data. In Fig. 5, we provide an example of a convolutional layer where the input vector X is represented as a matrix (*i.e.*  $X = (x_{i,j}) \in \mathbb{R}^{t \times t}$  where t is smallest square integer greater than the size n of X viewed as a vector) and padded with zeros around the border<sup>8</sup>. The output values can be expressed as  $y_{i,j} = \sum_{a=1}^{m} \sum_{b=1}^{m} w_{a,b} x_{i+a,j+b}$ , where  $w_{a,b}$  denotes the weights of the filter viewed as an m-by-m matrix. During the backward computation, the filter weights are learned<sup>9</sup> by trying to minimize the overall loss.

- A Max Pooling layer: this is a sub-sampling layer. The feature map is divided into regions and the output of this layer is the concatenation of the maximum values of all these regions. Such layers can help reducing computation complexity and enhance the robustness of the model with respect to a translation of the input.

- A SoftMax layer: it is added on the top of the previous stacked layers. It converts scores from the previous layer to a probability distribution over the classes.

Learning the filters enables to extract high level features from the data. This step may therefore be used as a dimensionality reduction or a Points Of Interest (POI) selection technique (e.g. a PCA). Based on this remark, it would be interesting to assess the efficiency of the CNN internal features extraction function in selecting the most informative points to perform a successful key recovery attack.

<sup>&</sup>lt;sup>8</sup> The goal is to control the size of the output.

<sup>&</sup>lt;sup>9</sup> As for the MLP weights estimations, the filter parameters are learned using the back-propagation algorithm.

Fig. 5. An example of a convolutional layer where n = 25, t = 5 and m = 3.

#### 3.2 Stacked Auto-Encoders

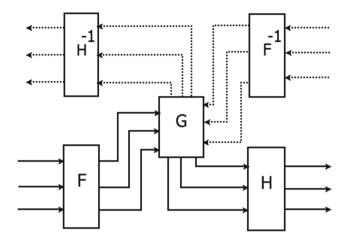

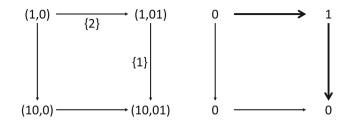

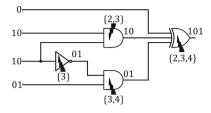

Stacked auto-encoders are artificial neural networks with many layers trained by following a very specific procedure [37]. This procedure consists in training each layer independently, using the output of the previous layer as input for the current one. Each layer is composed of an encoder and a decoder, both being a dense layer (*i.e.* fully connected layer)<sup>10</sup>. The role of the encoder is to generate higher level features from the inputs. Whereas, the decoder role is to reconstruct the inputs from the intermediate features learned by the encoder<sup>11</sup> as described in Fig. 6. A very uninteresting network would learn the identity function. To avoid such a behavior, a thumb rule could be that each layer has to be smaller than the previous one<sup>12</sup>. This way the network will be forced to learn a compressed representation of the input. Once the training is done, the decoder is removed, the newly generated encoder is stacked with the previously trained ones and the procedure can be repeated using the output of the newly trained layer.

On the top of the stacked auto-encoder layers, a SoftMax classifier is usually added to predict the class of the input using the high level extracted features of the last layer. Each of these layers (including the SoftMax layer) is trained sequentially. But once the last layer is trained, a global training using the wellknown Back-propagation algorithm is performed. This technique is known as fine tuning [37].

<sup>&</sup>lt;sup>10</sup> This is also known as a restricted Boltzmann machine [46].

<sup>&</sup>lt;sup>11</sup> We refer the interested reader to another type of auto-encoder deep learning technique called *Denoising auto-encoder* [56, 58]. This specific kind of auto-encoder aims at removing the noise when fed with a noisy input.

<sup>&</sup>lt;sup>12</sup> This is not mandatory; some empirical results have shown that it might be better to sometimes have more neurons on the first hidden layer than on the output as a "pre-learning" step.

**Fig. 6.** Learning an auto-encoder layer. First, the input  $X = (x_0, x_1, x_2, x_3, x_4) \in \mathbb{R}^5$  is encoded. Then, the obtained result  $H = (h_0, h_1, h_2, h_3, h_4) \in \mathbb{R}^5$  is decoded using the second layer of the diagram to reconstruct the input  $\hat{X} = (\hat{x}_0, \hat{x}_1, \hat{x}_2, \hat{x}_3, \hat{x}_4) \in \mathbb{R}^5$ . The difference  $(X - \hat{X})$  is then computed and fed to the back-propagation algorithm to estimate the optimal weights minimizing the loss function.

Like CNN, auto-encoders are features extractors. Their role is to build high level features that are easier to use in a profiling task. This task is particularly meaningful in SCA where the features selection method is critical.

#### 3.3 Recurrent Neural Networks

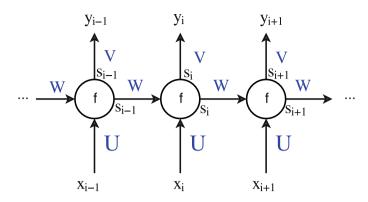

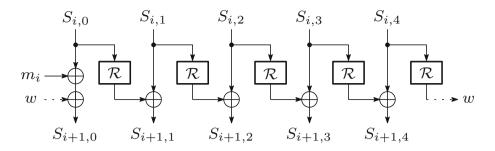

The Recurrent Neural Networks (RNN) [22] are dedicated to data for which the same information is spread over several time samples. Thus, instead of assuming that the components of the input vectors are mutually independent, each neuron will infer its output from both the current input and output of previous units. The RNN technique could be applied in the context of SCA since the leakage is spread actually over several time samples.

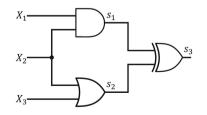

In Fig. 7, we explain how this time-dependency is used by the RNN during the profiling phase. Let n be the number of sample in our trace. For any i in [1, n], the  $i^{\text{th}}$  output  $s_i$  rewrites  $s_i = f(U \cdot x_i + W \cdot s_{i-1})$ , where (U, W) are the connecting weights that the RNN have to learn and f denotes the activation function. To get the  $i^{\text{th}}$  output  $y_j$ , a SoftMax layer is added such that  $y_j = \text{SoftMax}(V \cdot s_i)$  where V is a connecting weight. Unlike traditional deep learning techniques which use different weights at each layer, a RNN shares the same parameters (U, V, W) across all layers<sup>13</sup>. To adjust the network weights of the  $i^{\text{th}}$  unit, two different back-propagation phases are processed: the classical one (to learn U) and a temporal one (to learn W which depends on  $(i - 1)^{\text{th}}$  output).

<sup>&</sup>lt;sup>13</sup> The purpose is to reduce the number of parameters to be learned.

Fig. 7. An unrolled recurrent layer.

#### 3.4 Long and Short Term Memory Units

The Long and Short Term Memory (LSTM) is based on the RNN [26]. It has been originally introduced to solve problems that had been reported when using RNN, mainly the vanishing or the exploding gradients [7]. It enables the network to deal with long time lags between relevant time-series of the processed dataset. To do so, a *cell state* (*aka* memory cell) is added inside each unit. It contains some statistical information (*e.g.* mean, variance) computed over a previously processed time-series of the data. This cell can either be written on or erased depending on the relevance of the stored information. The decision of writing on the cell or of clearing it is taken by a small neural network [26].

In side channel context, this feature is quite interesting when dealing with higher-order attacks where the adversary have to combine several delayed time samples in order to defeat masked implementations for instance.

In the rest of this paper, we will focus on LSTM rather than RNN for the reasons outlined above.

#### 4 Towards New Profiling Methods

Several profiling approaches have been introduced in the literature. A common profiling side channel attack is the template attack proposed in [10] which is based on the Gaussian assumption<sup>14</sup>. It is known as the most powerful type of profiling in a SCA context when (1) the Gaussian assumption is verified and (2) the size of the leakage observations is small (typically smaller than 10.000).

When the Gaussian assumption is relaxed, several profiling based side channel attacks have been suggested including techniques based on machine learning. Actually, machine learning models make no assumption on the probability density function of the data. For example, random forest model builds a set of

<sup>&</sup>lt;sup>14</sup> which is that the distribution of the leakage when the algorithm inputs are fixed is well estimated by a Gaussian Law.

decision trees that classifies the data-set based on a voting system [34] and SVMbased attack discriminates data-set using hyper-plane clustering [23]. Indeed, one of the main drawbacks of the template attacks is their high data complexity [12] as opposed to the ML-based attacks which are generally useful when dealing with very high-dimensional data [34].

In the following section, we describe the commonly used template attack before introducing our new profiling approaches based on deep learning techniques.

#### 4.1 Template Attack

Template attacks have been introduced in 2002 by Chari *et al.* [10]. Since then, many works have been published proposing either some efficiency improvements (*e.g.* using Principal Component Analysis) [4,5,12] or to extend it to break protected implementations [41]. The seminal template attack consists first in using a set of profiling traces<sup>15</sup> and the corresponding intermediate results in order to estimate the probability density function (pdf)  $f_z(L|Z = z)$  where Z and L are random variables respectively denoting the target intermediate result and the corresponding leakage during its processing by the device, and where z ranges over all the definition set of Z. Usually L is multivariate, say defined over  $\mathbb{R}^d$  for some integer d (*e.g.* d = 1.000). Under the Gaussian assumption, this pdf is estimated by a multivariate normal law:

$$f_z(L|Z=z) \simeq \frac{1}{(2\pi)^d det(\Sigma_z)} exp\left(-\frac{1}{2}(L-\mu_z)^T \Sigma_z(L-\mu_z)\right) ,$$

where  $\Sigma_z$  denotes the  $(d \times d)$ -matrix of covariances of (L|Z = z) and where the *d*-dimensional vector  $\mu_z$  denotes its mean<sup>16</sup>.

Next, during the attack phase, the adversary uses a new set of traces  $(l_i)_{1 \le i \le n}$  for which the corresponding values  $z_i$  are unknown. From a key hypothesis k, he deduces predictions  $\hat{z}_i$  on these values and computes the maximum likelihood approach  $\prod_{j=1}^n f_{\hat{z}_j}(l_j|Z = \hat{z}_j)$ . To minimize approximation errors, it is often more convenient in practice to process the log-likelihood.

#### 4.2 Deep Learning in Side Channel Analysis Context

Like other machine learning techniques (e.g. SVM and RF), a deep learning technique builds a profiling model for each possible value  $z_i$  of the targeted sensitive variable Z during the training phase and, during the attack phase these models are involved to output the most likely key (*i.e.* label)  $k^*$  used during the acquisition of the attack traces set  $(l_i)_{1 \le i \le n}$ .

In side channel attack context, an adversary is rather interested in the computation of the probability of each possible value  $\hat{z}_i$  deduced from a key hypothesis.

<sup>&</sup>lt;sup>15</sup> This set of traces is typically acquired on an open copy of the targeted device.

<sup>&</sup>lt;sup>16</sup> The couple  $(\mu_z, \Sigma_z)$  represents the template of the value z.

Therefore, to recover the good key, the adversary computes the maximum or the log-maximum likelihood approach like for template attack  $(\prod_{i=1}^{n} P(l_j|Z = \hat{z}_j)).$

Indeed, our deep learning techniques only differs from the machine learning one in the method used to profile data. However, the attack phase remains the same for both kinds of attack.

## 5 Experimental Results

In the following section, we compare for different implementation sets the effectiveness and the efficiency of our proposed DL-based attacks with those of MLbased and template-based attacks. Mainly, we have targeted a hardware and a software implementation of an unprotected AES and a first-order masked AES implementation.

#### 5.1 Experimental Setup

We detail hereafter our experimental setup.

Attacker Profile. Since we are dealing with profiled attacks, we assume an attacker who has full control of a training device during the profiling phase and is able to measure the power consumption during the execution of a cryptographic algorithm. Then during the attack phase, the adversary aims at recovering the unknown secret key, processed by the same device, by collecting a new set of power consumption traces. To guarantee a fair and realistic attack comparison, we stress the fact that the training and the attack data-sets must be different.

**Targeted Operation.** Regarding the targeted operation, we consider one or several AES SBox outputs during the first round:  $Z = SBox[X \oplus k^*]$  where X and  $k^*$  respectively denote the plaintext and the secret key. We motivate our choice towards targeting this non-linear operation by the facts that it is a common target in side channel analysis and that it has a high level of confusion.

**Training and Attack Phase Setup.** For fair attack comparison, we have considered fixed size data-sets for the profiling and the attack: 1.000 power traces per sensitive value (*i.e.* Z = z) for the training phase and 20.000 power traces with a fixed key  $k^*$  for the attack phase.

**Evaluation Metric.** For the different targeted implementations, we have considered a fixed attack setup. In fact, each attack is conducted on 10 independent sets of 2.000 traces each (since we have a set of 20.000 power traces for the attack phase). Then, we have computed the averaged rank of the correct key among all key hypotheses (*aka* the *guessing entropy metric* [53]).

17

#### 5.2 Unprotected AES Implementations

**DPA Contest V2.** Our first experiments were carried out on the DPA contest V2 data-set [54]. It is an FPGA-based unprotected AES implementation. Each trace contains 3.253 samples measuring the power consumption of an AES execution.

To break this hardware implementation, we have conducted 4 different DLbased attacks (AE, CNN, LSTM and MLP)<sup>17</sup>. For the MLP-based attack, we have considered two versions: for the first one, we have pre-processed traces by applying a PCA in order to extract the 16 most informative components (since we will target the 16 SBox outputs). For the second MLP-based attack, no dimensionality technique was applied. Our purpose here is to check if the commonly used PCA technique could enhance the efficiency of deep learning based attacks.

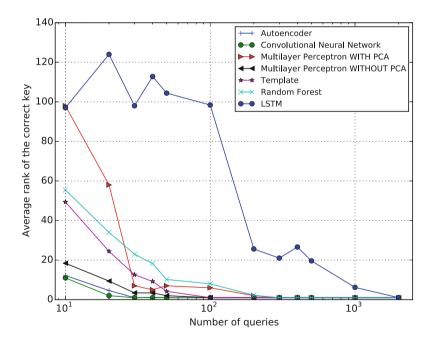

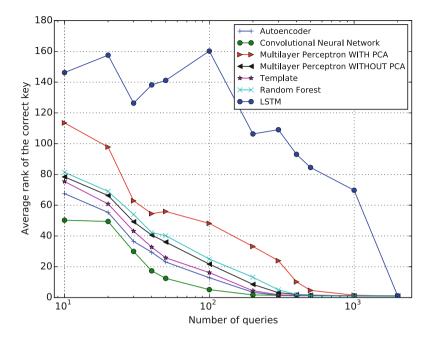

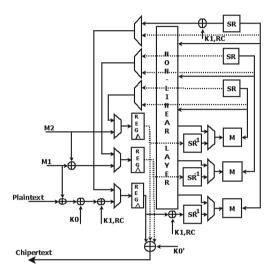

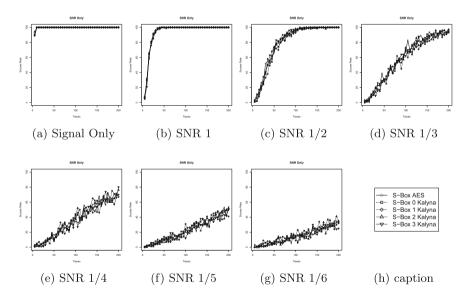

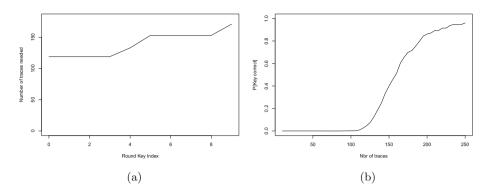

For the sake of completeness, we have performed the seminal template attack and the RF-based attack<sup>18</sup>. The evolution of the correct key rank according to the number of traces for each attack when targeting the first AES SBox is

Fig. 8. Evolution of the correct key rank (y-axis) according to an increasing number of traces (x-axis in log scale base 10) for each attack when targeting the first AES SBox

$<sup>^{17}</sup>$  The parameters for each attack are detailed in Appendix A.

<sup>&</sup>lt;sup>18</sup> In our attack experiments, we didn't reported the results of the SVM-based attack since it achieves a comparable results as those obtained for the RF-based attack. The same observations were highlighted in [33].

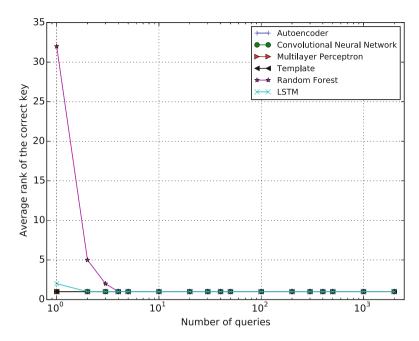

Fig. 9. Averaged guessing entropy over the 16 AES SBoxes (y-axis) according to an increasing number of traces (x-axis in log scale base 10).

described in Fig. 8. Besides, the averaged guessing entropy over the 16 AES SBox is shown in Fig. 9.

From Fig. 9, the following observations may be emphasized:

- the CNN and the AE-based attack slightly outperform template attack. For instance, for the CNN-based attack 200 traces are roughly needed in average to recover the key with a success rate of 100 %. For the template attack, an adversary needs roughly 400 traces. This could be explained by the fact that CNN applies a nice features extraction technique based on filters allowing dealing with the most informative samples form the processed traces.

- Prepossessing with PCA does not enhance the efficiency of MLP-based attack. In fact, the PCA is probably removing some data components which are informative for linear clustering representation, but negatively impact the accuracy of the non-linear model profiling of the MLP network.

- The LSTM performs worse compared to the other types of deep learning techniques. This could be due to the fact that the leakage of this hardware implementation is not time-dependent (*i.e.* the leakage is spread over few time samples).

Software Unprotected AES Implementation. For our second experiments, we have considered an unprotected AES implementation on the ChipWhisperer-Capture Rev2 board [39]. This board is a very compact side channel attack

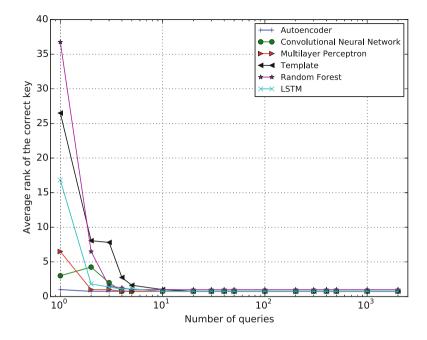

Fig. 10. Evolution of the correct key rank (y-axis) according to an increasing number of traces (x-axis in log scale base 10) for each attack when targeting the first AES SBox.

platform. It enables users to quickly and easily test their implementation against side channel attacks.

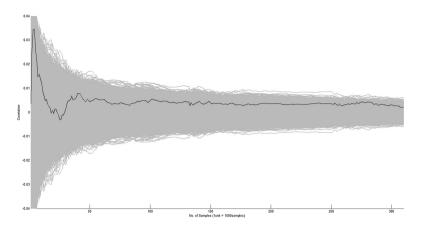

For the sake of comparison, we have performed the same attacks as these conducted on the DPA contest V2 implementation. In Figs. 10 and 11, we reported respectively the guessing entropy when targeting the first AES SBox and the averaged guessing entropy over the first four SBoxes for each attack and for an increasing attack traces set.

From Fig. 11, the following observations could be emphasized:

- Our proposed deep learning based attacks outperform both template and RF-based attack. For instance, for the AE-based attack 20 traces are roughly needed in average to recover the first four bytes of AES key with a success rate of 100 %. For the template attack and RF-based attack, an adversary needs respectively 100 and 80 traces.

- The performed attacks requires less than 100 traces to recover the first four bytes of the key. A natural explanation of this result could be that the SNR is very high on the ChipWhisperer side channel platform.

- The LSTM performs well compared to the results obtained on the DPA contest V2 data-set. This could be due to the facts that the leakage of a software implementation is very time-dependent and that the samples are less noisy.

Fig. 11. Averaged guessing entropy over the first four AES SBoxes (y-axis) according to an increasing number of traces (x-axis in log scale base 10).

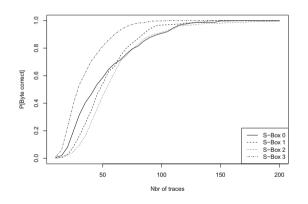

### 5.3 First-Order Masked AES Implementation

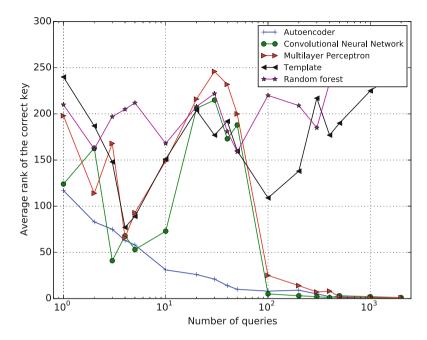

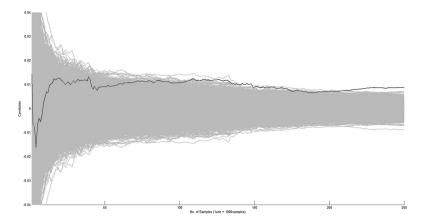

Our last experiments were carried out on a first-order masked AES implementation on the ChipWhisperer-Capture Rev2 board. The 16 SBoxes outputs are masked with the same mask. Our attacks were performed using the same leakage model as that used for the previously evaluated unprotected implementations (*i.e.* the training data were profiled with respect to the SBox output  $S[X \oplus k]$ ). Unlike the recently published ML-based attacks to break masked implementations [21,33], we stress the fact that no prior profiling of the mask values was made during the training phase. The attack results when targeting the first SBox are shown in Fig. 12.

From Fig. 12, one can conclude that our deep learning based attacks perform well against masked implementation. In fact, 500 and 1000 traces are respectively needed for AE and CNN/MLP-based attacks to recover the key. Actually, the deep learning techniques apply some activation functions as described in Sect. 2.1. Those functions (*e.g.* a sigmoid) implicitly perform product combinations of the data samples which has as an effect the removal of the mask dependency<sup>19</sup> exactly like a second-order side channel attack [42].

For template attack and RF-based attack more traces are needed to reach a success rate of  $100\,\%.$

<sup>&</sup>lt;sup>19</sup> The product combining function maps the leakages of the masked data  $(Z \oplus M)$  and the mask (M) into a univariate sample depending on the sensitive data Z.

Fig. 12. Evolution of the correct key rank (y-axis) according to an increasing number of traces (x-axis in log scale base 10) for each attack when targeting the first AES SBox.

## 6 Conclusion and Perspectives

In this paper, to the best of our knowledge, we study for the first time the application of deep learning techniques in the context of side channel attacks. The deep learning techniques are based on some nice features suitable to perform successful key recovery. Mainly, they use different methods of features extraction (CNN and AE) and exploit time dependency of samples (RNN, LSTM). In order to evaluate the efficiency of our proposed attacks, we have compared them to the most commonly used template attack and machine learning attacks. The comparison between these attacks was conducted on three different data-sets by evaluating the number of traces required during the attack phase to achieve a unity guessing entropy with a fixed size of profiling data-set. Our practical results have shown the overwhelming advantage of our proposal in breaking both unprotected and protected AES implementations. Indeed, for the different targeted implementations, our attacks outperform the state-of-the-art profiling side channel attacks.

A future work may consist in targeting other types of protection (*e.g.* shuffling, combined masking and shuffling) with our proposed DL-based attacks. Moreover, our work opens avenues for further research of new deep learning techniques in order to better adapt them to challenge cryptographic implementations.

# A Attack Settings

Our proposed deep learning attacks are based on Keras library [2]. We provide hereafter the architecture and the used parameters for our deep learning networks.

- Multilayer Perceptron:

- Dense input layer: the number of neurons = the number of samples in the processed trace

- Dense hidden layer: 20 neurons

- Dense output layer: 256 neurons

- Stacked Auto-Encoder:

- Dense input layer: the number of neurons = the number of samples in the processed trace

- Dense hidden layer: 100 neurons

- Dense hidden layer: 50 neurons

- Dense hidden layer: 20 neurons

- Dense output layer: 256 neurons

- Convolutionnal Neural Network:

- Convolution layer

- \* Number of filters: 8

- \* Filters length: 16

- \* Activation function: Rectified Linear Unit

- Dropout

- Max pooling layer with a pooling size: 2

- Convolution layer

- \* Number of filters: 8

- \* Filters length: 8

- \* Activation function: tanh(x)

- Dropout

- Dense output layer: 256 neurons

- Long and Short Term Memory:

- LSTM layer: 26 units

- LSTM layer: 26 units

- Dense output layer: 256 neurons

- Random Forest: For this machine learning based attack, we have used the *scikit-learn* python library [3].

- Number of trees: 300

In several published works [23,28], authors have noticed the influence of the parameters chosen for SVM and RF networks on the attack results. When dealing with deep learning techniques we have observed the same effect. To find the optimal parameters setup for our practical attacks, a deeply analyzed method is detailed in the following section.

#### A.1 How to Choose the Optimal Parameters?

When dealing with *artificial neural networks*, several meta-parameters have to be tuned (*e.g.* number of layers, number of neurons on each layer, activation function, ...). One common technique to find the optimal parameters is to use *evolutionary algorithms* [18] and more precisely the so-called *genetic algorithm* [38].

At the beginning of the algorithm, a *population* (a set of *individuals* with different *genes*) is randomly initialized. In our case, an individual is a list of the parameters we want to estimate (*e.g.* number of layers, number of neurons on each layer, activation function, ...) and the genes are the corresponding values. Then, the performance of each individual is evaluated using what is called a *fitness function*. In our context, the fitness function is the guessing entropy outputted by the attack. Said, differently, for each set of parameters we perform the attack and we note the guessing entropy obtained. Only the individuals that achieve good guessing entropy scores are kept. Their genes are mutated and mixed to generate a better population. This process is repeated until a satisfying fitness is achieved (*i.e.* a guessing entropy equals one).

## References

- 1. Deep learning website. http://deeplearning.net/tutorial/

- 2. Keras library. https://keras.io/

- 3. Scikit-learn library. http://scikit-learn.org/stable/

- Archambeau, C., Peeters, E., Standaert, F.-X., Quisquater, J.-J.: Template attacks in principal subspaces. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249, pp. 1–14. Springer, Heidelberg (2006). doi:10.1007/11894063\_1

- Bartkewitz, T., Lemke-Rust, K.: Efficient template attacks based on probabilistic multi-class support vector machines. In: Mangard, S. (ed.) CARDIS 2012. LNCS, vol. 7771, pp. 263–276. Springer, Heidelberg (2013). doi:10.1007/ 978-3-642-37288-9\_18

- Bengio, Y.: Learning deep architectures for ai. Found. Trends Mach. Learn. 2(1), 1–127 (2009)

- Bengio, Y., Simard, P., Frasconi, P.: Learning long-term dependencies with gradient descent is difficult. Trans. Neur. Netw. 5(2), 157–166 (1994)

- Bishop, C.M.: Neural Networks for Pattern Recognition. Oxford University Press Inc., New York (1995)

- Brier, E., Clavier, C., Olivier, F.: Correlation power analysis with a leakage model. In: Joye, M., Quisquater, J.-J. (eds.) CHES 2004. LNCS, vol. 3156, pp. 16–29. Springer, Heidelberg (2004). doi:10.1007/978-3-540-28632-5\_2

- Chari, S., Rao, J.R., Rohatgi, P.: Template attacks. In: Kaliski, B.S., Koç, K., Paar, C. (eds.) CHES 2002. LNCS, vol. 2523, pp. 13–28. Springer, Heidelberg (2003). doi:10.1007/3-540-36400-5\_3

- Chen, Z., Zhou, Y.: Dual-rail random switching logic: a countermeasure to reduce side channel leakage. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249, pp. 242–254. Springer, Heidelberg (2006). doi:10.1007/11894063\_20

- Choudary, O., Kuhn, M.G.: Efficient Template Attacks. Cryptology ePrint Archive, Report 2013/770 (2013). http://eprint.iacr.org/2013/770

- Coron, J.-S.: Higher order masking of look-up tables. In: Nguyen, P.Q., Oswald, E. (eds.) EUROCRYPT 2014. LNCS, vol. 8441, pp. 441–458. Springer, Heidelberg (2014). doi:10.1007/978-3-642-55220-5\_25

- Cortes, C., Vapnik, V.: Support-vector networks. Mach. Learn. 20(3), 273–297 (1995)

- Deng, L., Yu, D.: Deep learning: methods and applications. Found. Trends Signal Process. 7(3–4), 197–387 (2014)

- Doget, J., Prouff, E., Rivain, M., Standaert, F.-X.: Univariate side channel attacks and leakage modeling. J. Cryptographic Eng. 1(2), 123–144 (2011)

- Duda, R.O., Hart, P.E., Stork, D.G.: Pattern Classification, 2nd edn. Wiley-Interscience (2000)

- Eiben, A.E., Smith, J.E.: Introduction to Evolutionary Computing. Springer, Heidelberg (2003)

- Genelle, L., Prouff, E., Quisquater, M.: Thwarting higher-order side channel analysis with additive and multiplicative maskings. In: Preneel, B., Takagi, T. (eds.) CHES 2011. LNCS, vol. 6917, pp. 240–255. Springer, Heidelberg (2011). doi:10. 1007/978-3-642-23951-9\_16

- Gierlichs, B., Batina, L., Tuyls, P., Preneel, B.: Mutual information analysis. In: Oswald, E., Rohatgi, P. (eds.) CHES 2008. LNCS, vol. 5154, pp. 426–442. Springer, Heidelberg (2008). doi:10.1007/978-3-540-85053-3\_27

- Gilmore, R., Hanley, N., O'Neill, M.: Neural network based attack on a masked implementation of aes. In: 2015 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), pp. 106–111, May 2015

- Hermans, M., Schrauwen, B.: Training and analysing deep recurrent neural networks. In: Burges, C.J.C., Bottou, L., Welling, M., Ghahramani, Z., Weinberger, K.Q. (eds.) Advances in Neural Information Processing Systems 26, pp. 190–198. Curran Associates Inc. (2013)

- Heuser, A., Zohner, M.: Intelligent machine homicide breaking cryptographic devices using support vector machines. In: Schindler, W., Huss, S.A. (eds.) COSADE 2012. LNCS, vol. 7275, pp. 249–264. Springer, Heidelberg (2012). doi:10. 1007/978-3-642-29912-4\_18

- Heyszl, J., Ibing, A., Mangard, S., Santis, F.D., Sigl, G.: Clustering Algorithms for Non-Profiled Single-Execution Attacks on Exponentiations. IACR Cryptology ePrint Archive 2013, 438 (2013)

- Hochreiter, S.: The vanishing gradient problem during learning recurrent neural nets and problem solutions. Int. J. Uncertain. Fuzziness Knowl. Based Syst. 6(2), 107–116 (1998)

- Hochreiter, S., Schmidhuber, J.: Long short-term memory. Neural Comput. 9(8), 1735–1780 (1997)

- Hoogvorst, P., Danger, J.-L., Duc, G.: Software implementation of dual-rail representation. In: COSADE, Darmstadt, Germany, 24–25 February 2011

- Hospodar, G., Gierlichs, B., De Mulder, E., Verbauwhede, I., Vandewalle, J.: Machine learning in side-channel analysis: a first study. J. Cryptographic Eng. 1(4), 293–302 (2011)

- 29. Jarrett, K., Kavukcuoglu, K., Ranzato, M., LeCun, Y.: What is the best multistage architecture for object recognition? In: ICCV, pp. 2146–2153. IEEE (2009)

- Kocher, P., Jaffe, J., Jun, B.: Differential power analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999). doi:10. 1007/3-540-48405-1.25

- LeCun, Y., Bengio, Y.: Convolutional networks for images, speech, and time series. In: Handbook of Brain Theory and Neural Networks, pp. 255–258. MIT Press, Cambridge (998)

- Lerman, L., Bontempi, G., Markowitch, O.: Power analysis attack: an approach based on machine learning. Int. J. Appl. Cryptography 3(2), 97–115 (2014)

- 33. Lerman, L., Medeiros, S.F., Bontempi, G., Markowitch, O.: A Machine Learning Approach Against a Masked AES. In: Francillon, A., Rohatgi, P. (eds.) CARDIS 2013. LNCS, vol. 8419, pp. 61–75. Springer, Heidelberg (2014). doi:10. 1007/978-3-319-08302-5\_5

- Lerman, L., Poussier, R., Bontempi, G., Markowitch, O., Standaert, F.-X.: Template attacks vs. machine learning revisited (and the curse of dimensionality in sidechannel analysis). In: Mangard, S., Poschmann, A.Y. (eds.) COSADE 2014. LNCS, vol. 9064, pp. 20–33. Springer, Heidelberg (2015). doi:10.1007/978-3-319-21476-4\_2

- 35. Lomné, V., Prouff, E., Rivain, M., Roche, T., Thillard, A.: How to estimate the success rate of higher-order side-channel attacks, pp. 35–54. Heidelberg (2014)

- Mangard, S., Oswald, E., Popp, T.: Power Analysis Attacks: Revealing the Secrets of Smart Cards. Springer, December 2006. ISBN 0-387-30857-1, http://www. dpabook.org/

- Masci, J., Meier, U., Cireşan, D., Schmidhuber, J.: Stacked convolutional autoencoders for hierarchical feature extraction. In: Honkela, T., Duch, W., Girolami, M., Kaski, S. (eds.) ICANN 2011. LNCS, vol. 6791, pp. 52–59. Springer, Heidelberg (2011). doi:10.1007/978-3-642-21735-7\_7

- Mitchell, M.: An Introduction to Genetic Algorithms. MIT Press, Cambridge (1998)

- O'Flynn, C., Chen, Z.D.: Chipwhisperer: An open-source platform for hardware embedded security research. Cryptology ePrint Archive, Report 2014/204 (2014). http://eprint.iacr.org/2014/204

- O'Shea, K., Nash, R.: An introduction to convolutional neural networks. CoRR, abs/1511.08458 (2015)

- Oswald, E., Mangard, S.: Template attacks on masking—resistance is futile. In: Abe, M. (ed.) CT-RSA 2007. LNCS, vol. 4377, pp. 243–256. Springer, Heidelberg (2006). doi:10.1007/11967668\_16

- 42. Prouff, E., Rivain, M., Bevan, R.: Statistical analysis of second order differential power analysis. IEEE Trans. Computers **58**(6), 799–811 (2009)

- Rivain, M.: On the exact success rate of side channel analysis in the gaussian model. In: Avanzi, R.M., Keliher, L., Sica, F. (eds.) SAC 2008. LNCS, vol. 5381, pp. 165–183. Springer, Heidelberg (2009). doi:10.1007/978-3-642-04159-4\_11

- Rivain, M., Prouff, E.: Provably secure higher-order masking of AES. In: Mangard, S., Standaert, F.-X. (eds.) CHES 2010. LNCS, vol. 6225, pp. 413–427. Springer, Heidelberg (2010). doi:10.1007/978-3-642-15031-9\_28

- Rokach, L., Maimon, O.: Data Mining with Decision Trees: Theroy and Applications. World Scientific Publishing Co. Inc., River Edge (2008)

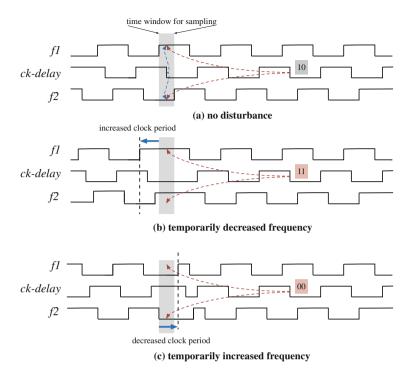

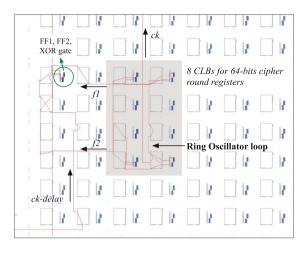

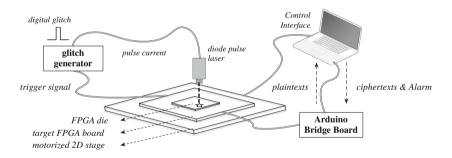

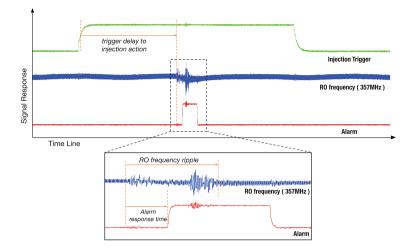

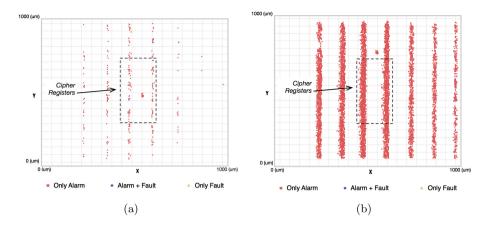

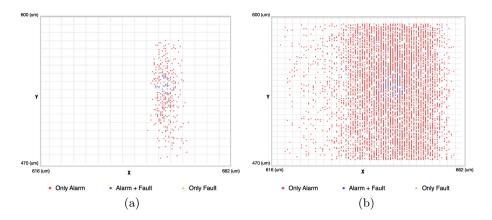

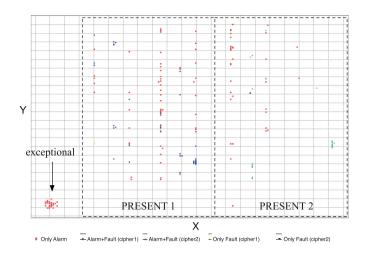

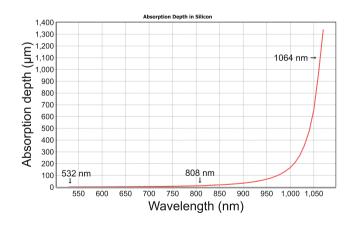

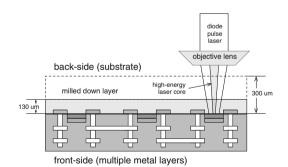

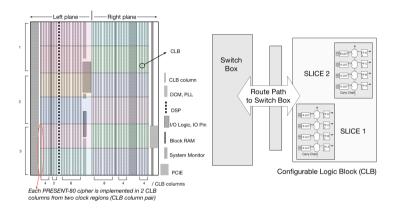

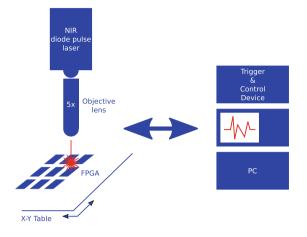

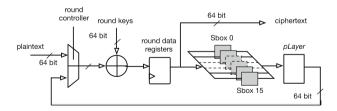

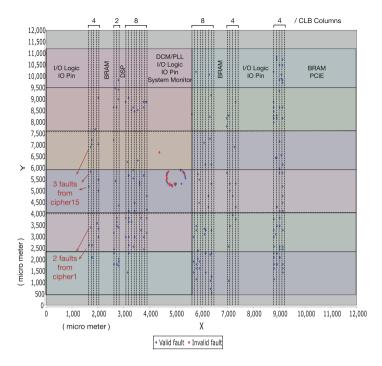

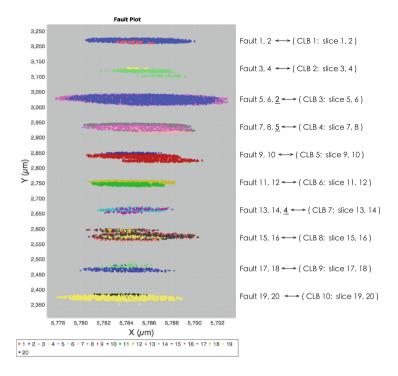

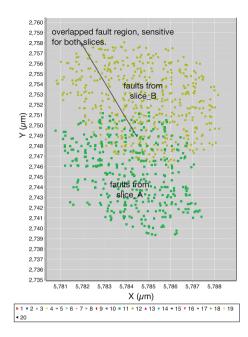

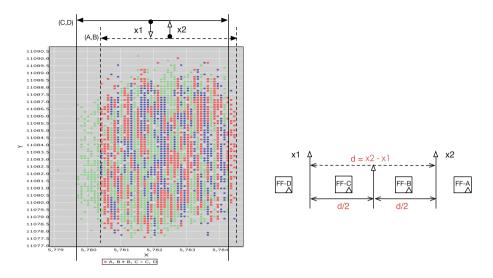

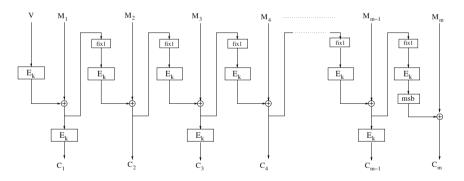

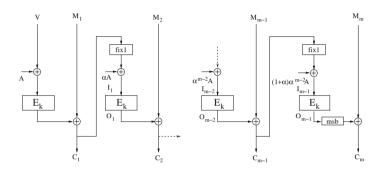

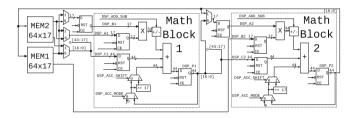

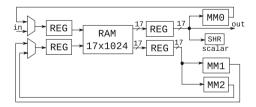

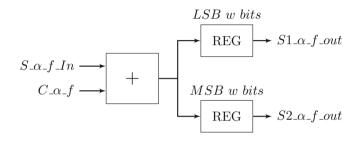

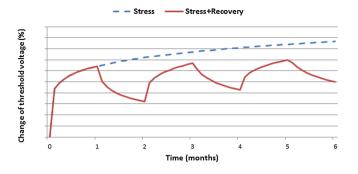

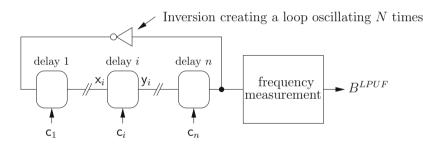

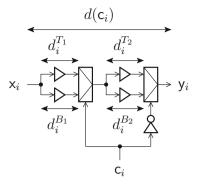

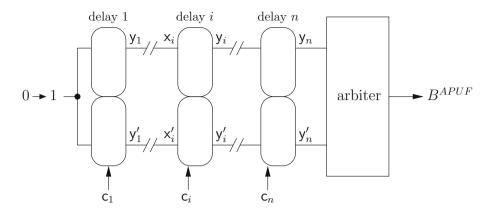

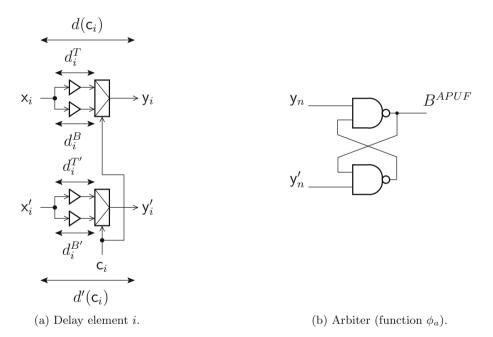

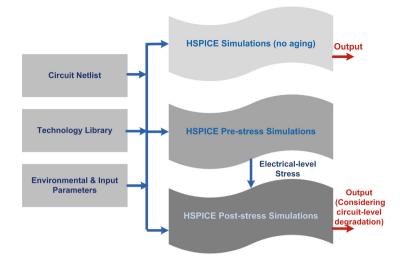

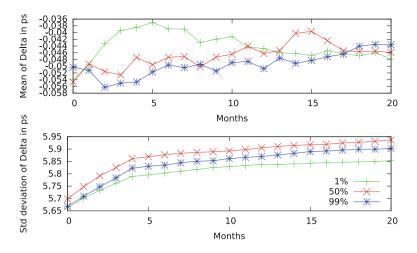

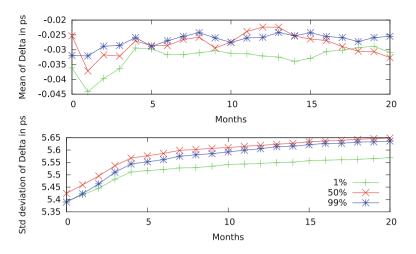

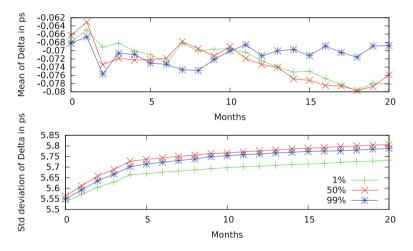

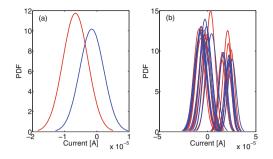

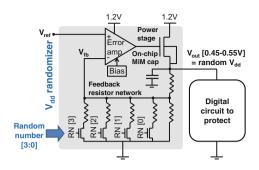

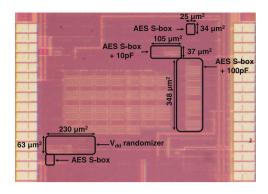

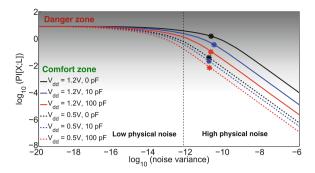

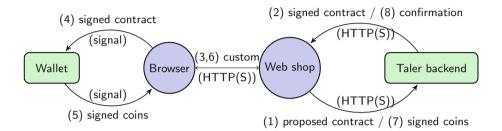

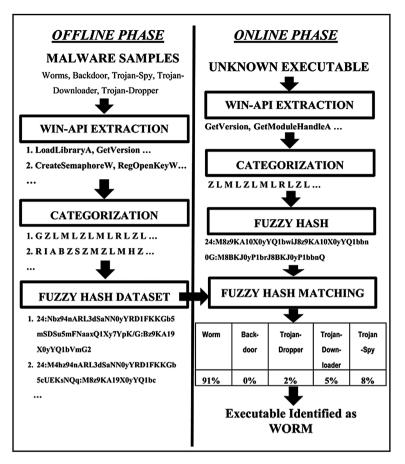

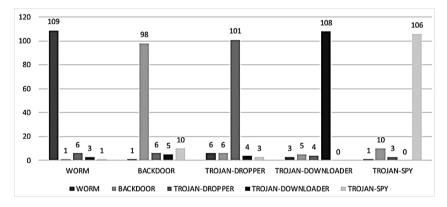

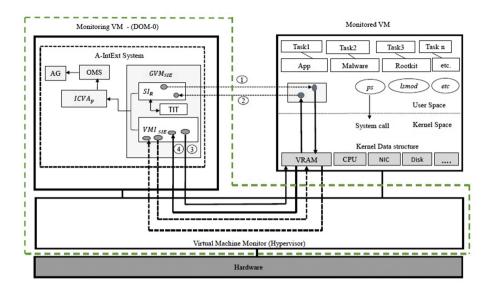

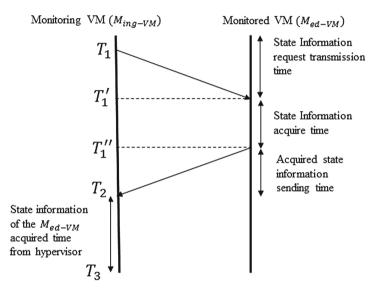

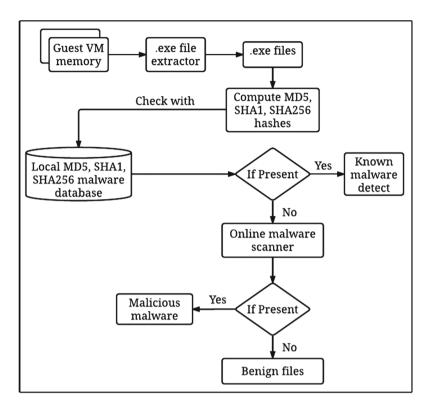

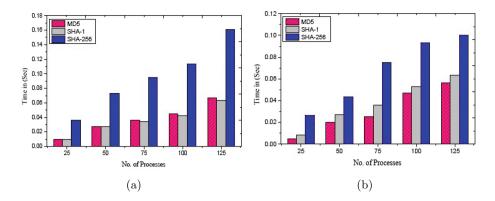

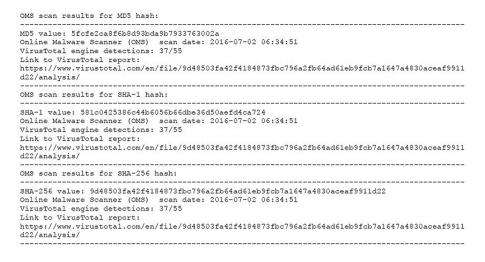

- Salakhutdinov, R., Mnih, A., Hinton, G.: Restricted boltzmann machines for collaborative filtering. In: Proceedings of the 24th International Conference on Machine Learning, ICML 2007, pp. 791–798. ACM, New York (2007)