Mike G. Hinchey Jonathan P. Bowen Ernst-Rüdiger Olderog *Editors*

# Provably Correct Systems

# NASA Monographs in Systems and Software Engineering

### Series editor

Mike G. Hinchey, Limerick, Ireland

The NASA Monographs in Systems and Software Engineering series addresses cutting-edge and groundbreaking research in the fields of systems and software engineering. This includes in-depth descriptions of technologies currently being applied, as well as research areas of likely applicability to future NASA missions. Emphasis is placed on relevance to NASA missions and projects.

More information about this series at http://www.springer.com/series/7055

Mike G. Hinchey · Jonathan P. Bowen Ernst-Rüdiger Olderog Editors

# **Provably Correct Systems**

Editors

Mike G. Hinchey

Lero-The Irish Software Research Centre

University of Limerick

Limerick

Ireland

Jonathan P. Bowen School of Engineering London South Bank University London UK Ernst-Rüdiger Olderog Department für Informatik Universität Oldenburg Oldenburg Germany

ISSN 1860-0131 ISSN 2197-6597 (electronic) NASA Monographs in Systems and Software Engineering ISBN 978-3-319-48627-7 ISBN 978-3-319-48628-4 (eBook) DOI 10.1007/978-3-319-48628-4

Library of Congress Control Number: 2016959748

### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### **Foreword**

The ProCoS Project (1989–1991) was funded by the European Community as a Basic Research Project, with a continuation (ProCoS II) also funded from 1992 to 1995. It was included in the ESPRIT programme of internationally collaborative research in Information Technology. The inspiration of the project was the recent completion of the Stack verification project, undertaken by Computational Logic, Inc. This was a start-up company founded and directed by Bob Boyer and J Moore, professors at the University of Texas at Austin. Both the European and the US projects sought to advance the technology of software verification by accepting the challenge of verification of components of a free-standing computer system. These included its operating system, its assembler, and its automatic verification aids, and even the hardware of a processor chip.

Many technological breakthroughs were triggered by these two challenge projects. The international collaboration which was forged by the ProCoS Project has continued under support of the individual national funding agencies. It has inspired and accelerated the automation of program verification. The resulting tools have found application in many advanced modern industries, including industrial giants in aerospace, electronics, silicon fabrication, automobiles, communications, advertising, social networks, retail sales, as well as suppliers of compilers and of operating systems and general software.

Many of the collaborators in the original ProCoS project, together with their students and followers, have contributed to this broadening of the application of the original basic research. A representative selection of their recent work was presented at the ProCoS Workshop in March 2015; and I welcome the publication of the proceedings in book form. I offer its authors and readers my best wishes for further progress in the understanding of the basic science, coupled with its broadest possible application.

Cambridge, UK June 2016

Tony Hoare

### **Preface**

ProCoS is the acronym for "Provably Correct Systems", a basic research project funded in two phases by the European Commission from 1989 to 1995. This project was planned by Tony Hoare (Oxford University), Dines Bjørner (DTU, Technical University of Denmark, Lyngby), and Hans Langmaack (University of Kiel). Its goal was to develop a mathematical basis for the development of embedded, real-time computer systems.

The survey paper on ProCoS presented at the conference FTRTFT (Formal Techniques in Real-Time and Fault-Tolerant Systems) 1994 states in its introduction:

An embedded computer system is part of a total system that is a physical process, a plant, characterized by a state that changes over time. The role of the computer is to monitor this state through sensors and change the state through actuators. The computer is simply a convenient device that can be instructed to manipulate a mathematical model of the physical system and state. Correctness means that the program and the hardware faithfully implement the control formulas of the mathematical model of the total system, and nothing else. However, the opportunities offered by the development of computer technology have resulted in large, complex programs which are hard to relate to the objective of system control.

The ProCoS project developed a particular approach to mastering the complexity of such systems. Its emphasis was on proving system correctness across different abstraction layers. The inspiration for ProCoS stems from a sabbatical of Tony Hoare at the University of Austin at Texas in 1986. There he was impressed by the work of Robert S. Boyer and J Strother Moore on automated verification with their "Boyer-Moore" prover ACL2 at their company "Computational Logic, Inc." (CLI), in particular its application to a case study known as the "CLInc Stack". Discussing later with Dines Bjørner and Hans Langmaack, a project on the foundation of verification of many-layered systems was conceived: ProCoS. The different levels of abstraction studied in this project became known as the "ProCoS Tower". They comprised (informal) expectations, (formal) requirements, (formal) system specifications, programs (in the "occam" programming language), machine code (for the "transputer" microprocessor), and circuit diagrams (described using "netlists").

viii Preface

During the final deliverable for the first phase of ProCoS, Tony Hoare wrote in 1993:

In summary, our overall goal is not to produce a single verified system or any particular verified language or compiler, but rather to advance the state of the art of systematic design of complex heterogeneous systems, including both hardware and software; and to concentrate attention on reducing the risk of error in the specification, design and implementation of embedded safety critical systems.

In the first phase, the ProCoS project comprised seven partners: Oxford University, Technical University of Denmark at Lyngby, Christian-Albrechts Universität Kiel, Universität Oldenburg, Royal Holloway and Bedford New College, Århus University, and the University of Manchester. In the second phase (ProCoS II), the team consisted of the first four original partners. The EU funding of ProCoS was relatively small. During the second phase only one researcher at each of the four partner sites was funded, but many more students and researchers at these sites contributed to the goals.

ProCoS was much influenced by the work of two Chinese scientists contributing to the project at Lyngby and Oxford: Zhou Chaochen and He Jifeng.

Zhou Chaochen and Anders P. Ravn initiated a major conceptual development of ProCoS: the Duration Calculus, an interval-based logic for specifying real-time requirements. The first paper on it was published by Zhou Chaochen, Tony Hoare and Anders P. Ravn in 1991. The types of durational properties that can be expressed in the Duration Calculus were motivated by the case study of a gas burner that was defined by E.V. Sørensen from DTU in collaboration with a Danish gas burner manufacturer. He Jifeng cooperated closely with Tony Hoare on a predicative approach to programming that led to the book "Unifying Theories of Programming" (UTP) published in 1998. The work on UTP has attracted a number of researchers and led to a series of symposiums on this topic.

To bridge the gap from requirements to programs, a combination of specification techniques for data and processes with transformation rules was developed by the group of E.-R. Olderog in Oldenburg. The topic of correct compilers, exemplified for the translation of an occam-like programming language to transputer machine code, was investigated in the group of Hans Langmaack in Kiel. Oxford contributed an algebraic approach to compiling verification.

Associated with the ProCoS project was an EU-funded ProCoS Working Group (1994–1997) of 25 academic and industrial partners interested in provably correct systems, arranging various meetings around Europe.

Other associated national projects in the United Kingdom included the "safemos" project (1989–1993), a UK EPSRC project on "Provably Correct Hardware/Software Co-design" (1993–1996), and an EPSRC Visiting Fellowship on "Provably Correct Real Time Systems" (1996–1997). Associated travel funding to encourage collaboration included ESPRIT/NSF ProCoS-US initiative on "Provably Correct Hardware Compilation" with Cornell University in the US, and KIT (Keep in Touch) grants with UNU/IIST in Macau (1993–1998) and PROCORSYS with the Federal University of Pernambuco in Brazil (1994–1997).

Preface

### **Impact**

An extension of the Duration Calculus to cover continuous dynamical systems was led by Anders P. Ravn and Hans Rischel at DTU to contribute to the initial research on hybrid systems.

From 1992 until 1997, Dines Bjørner was the founding director of UNU-IIST, the International Institute for Software Technology of the United Nations University in Macau. Ideas from the ProCoS project flourished at the institute and were taken up by researchers from Asia working there. Also, a number of scientists associated with ProCoS visited UNU-IIST or had research posts for several years, including He Jifeng and Zhou Chaochen. From 1997 until 2002, Zhou Chaochen succeeded Dines Bjørner as the director of UNU-IIST, during the time of transition of Macau from a Portuguese to a Chinese city. Regrettably, in 2013 the United Nations decided to disband academic staff at UNU-IIST.

A number of young ProCoS contributors pursued academic careers. Martin Fränzle and Markus Müller-Olm, students in Kiel during the ProCoS project, are now professors at the universities of Oldenburg and Münster, respectively. Also, Debora Weber-Wulff and Bettina Buth, at Kiel during the ProCoS project, are now professors in Berlin and Hamburg, respectively. Michael Schenke, a ProCoS contributor at Oldenburg, is now a professor in Merseburg. Augusto Sampaio, during ProCoS working on his Ph.D. at Oxford on an algebraic approach to compilation during ProCoS, has became a professor at the University of Pernambuco, Brazil. Paritosh K. Pandya, working at Oxford during the ProCoS project, has become a professor at the Tata Institute of Fundamental Research in Mumbai, India. Zhiming Liu, who during ProCoS times spent a year as a postdoc at DTU and later was a researcher at UNI-IIST, is now professor at the Southwest University in Chongqing, China.

The collaborative project Verifix (*Construction and Architecture of Verifying Compilers*) directed by Gerhard Goos, Friedrich von Henke and Hans Langmaack and funded 1995–2004 by the German Research Foundation (DFG) deepened research on compiler correctness begun in the ProCoS project.

The large-scale Transregional Collaborative Research Center AVACS (*Automatic Verification and Analysis of Complex Systems*), directed by Werner Damm and funded by German Research Foundation (DFG) during the period 2004–2015, continued research pioneered in ProCoS but with emphasis on automation and for wider classes of systems. The collaborating sites were Oldenburg, Freiburg, and Saarbrücken. AVACS comprised of nine projects in the areas of real-time systems, hybrid systems, and systems of systems.

A series of conferences called VSTTE (*Verified Systems—Theories, Tools and Experiments*), was initiated by a vision for a Grand Challenge project formulated by Tony Hoare and Jay Misra in July 2005.

The ProCoS project and its related initiatives have inspired a number of books, including the following:

He Jifeng, Provably Correct Systems—Modelling of Communicating Languages and Design of Optimized Compilers, McGraw-Hill, 1994. x Preface

• Jonathan P. Bowen (ed.), *Towards Verified Systems*, Elsevier Science, Real-Time Safety Critical Systems Series, 1994.

- Mike G. Hinchey and Jonathan P. Bowen (eds.), *Applications of Formal Methods*, Prentice Hall, Series in Computer Science, 1995.

- C.A.R. Hoare and He Jifeng, *Unifying Theories of Programming*, Prentice Hall, Series in Computer Science, 1998.

- Jonathan P. Bowen and Mike G. Hinchey, *High-Integrity System Specification and Design*, Springer, FACIT Series, 1999.

- Zhou Chaochen and Michael R. Hansen, *Duration Calculus—A Formal Approach to Real-Time Systems*, Springer, 2004.

- E.-R. Olderog and Henning Dierks, *Real-Time Systems—Formal Specification and Automatic Verification*, Cambridge University Press, 2008.

### Structure of this Book

In September 2013, Jonathan Bowen and Ernst-Rüdiger Olderog met at the Festschrift Symposium for He Jifeng in Shanghai and discussed the possibility of having a workshop celebrating 25 years of ProCoS. This idea materialized with the help of Mike Hinchey in March 2015, when a two-day ProCoS Workshop with around 40 invited researchers and 25 presentations on the topic of "Provably Correct Systems" took part in the rooms of the BCS in London. This book consists of 13 chapters mainly describing recent advances on "Provably Correct Systems", based on presentations at that workshop. Each paper has been carefully reviewed by three to five reviewers. The chapters address the following topics:

- Historic Account,

- Hybrid Systems,

- Correctness of Concurrent Algorithms,

- Interfaces and Linking,

- Automatic Verification,

- Run-time Assertions Checking,

- · Formal and Semi-formal Methods, and

- Web-Supported Communities in Science.

### **Historic Account**

In the note "ProCoS: How it all Began—as seen from Denmark", Dines Bjørner opens his diary and shows entries by Tony Hoare during a meeting of IFIP Working Group 2.3 at Château du Pont d'Oye in Belgium in 1987. The author explains that this was a first draft on the content of ProCoS.

хi

### **Hybrid Systems**

Martin Fränzle, Yang Gao, and Sebastian Gerwinn review in Chap. "Constraint-Solving Techniques for the Analysis of Stochastic Hybrid Systems" definitions of (parametric) stochastic hybrid automata as needed for reliability evaluation. The authors then discuss automatic verification and synthesis methods based on arithmetic constraint solving. The chapters are able to solve step-bounded stochastic reachability problems and multi-objective parameter synthesis problems, respectively.

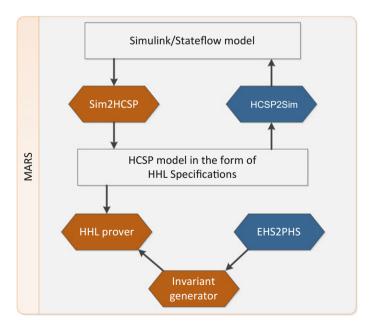

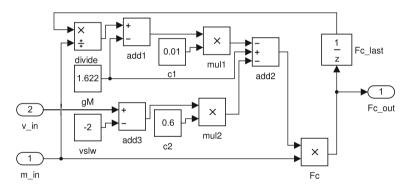

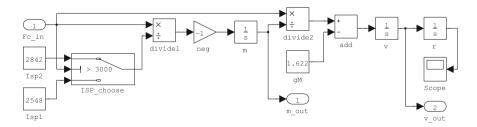

Mingshuai Chen, Xiao Han, Tao Tang, Shuling Wang, Mengfei Yang, Naijun Zhan, Hengjun Zhao, and Liang Zou introduce in Chap. "MARS: A Toolchain for Modelling, Analysis and Verification of Hybrid Systems" the toolchain MARS for Modelling, Analysing and verifying hybrid Systems. Using MARS, they build executable models of hybrid systems using the industrial standard environment Simulink/Stateflow, which facilitates analysis by simulation. The toolchain includes a translation of Simulink/Stateflow models to Hybrid CSP and verification using an interactive prover for Hybrid Hoare Logic.

### **Correctness of Concurrent Algorithms**

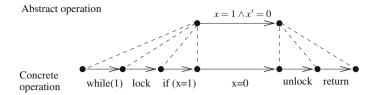

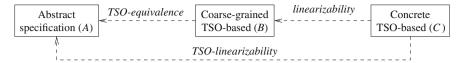

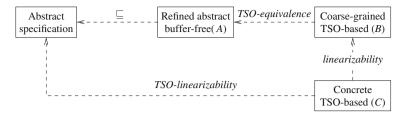

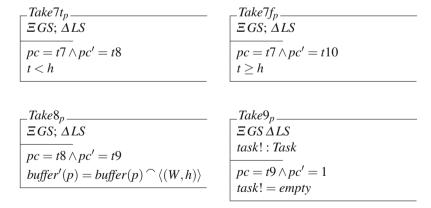

John Derrick, Graeme Smith, Lindsay Groves, and Brijesh Dongol study in Chap. "A Proof Method for Linearizability on TSO Architectures" the correctness of non-atomic concurrent algorithms on a weak memory model, the TSO (Total Store Order) model. They show how linearizability is defined on TSO, and how one can adapt a simulation-based proof method for use on TSO. Their central result is a proof method that simplifies simulation-based proofs of linearizability on TSO.

### **Interfaces and Linking**

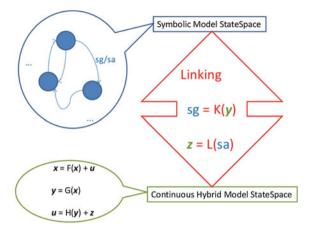

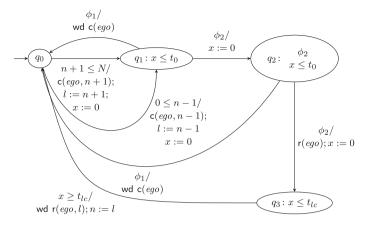

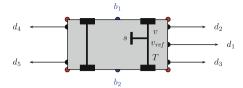

E.-R. Olderog, A.P. Ravn, and R. Wisniewski investigate in Chap. "Linking Discrete and Continuous Models, Applied to Traffic Manoeuvrers" the interplay between discrete and continuous dynamical models, and combine them with linking predicates. The topic of linking system specifications at different levels of abstraction was central to the ProCoS project. However, here the application area is more advanced: traffic manoeuvrers of multiple vehicles on highways.

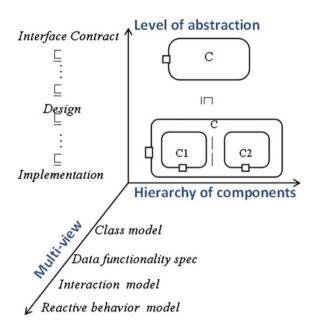

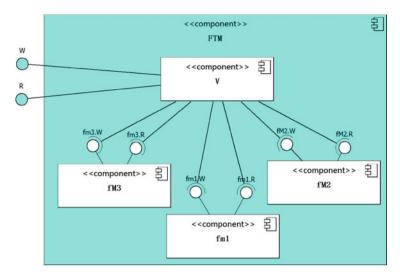

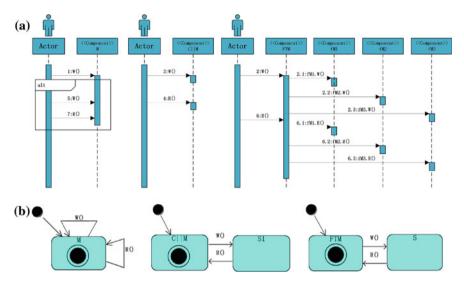

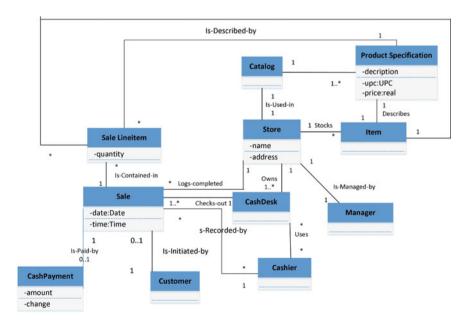

Zhiming Liu and Xin Chen discuss in Chap. "Towards Interface-Driven Design of Evolving Component-Based Architectures" how software design for complex evolving systems can be supported by an extension of the rCOS method for

xii Preface

refinement of component and object systems. It shows the need for a suitable interface theory and of multi-modelling notations for the description of multi-viewpoints of designs. This requires a theoretical foundation in the style of Unifying Theories of Programming as proposed by Tony Hoare and He Jifeng.

### **Automatic Verification**

J Strother Moore presents in Chap. "Computing Verified Machine Address Bounds During Symbolic Exploration of Code" an abstract interpreter for machine address expressions that attempts to produce a bounded natural number interval guaranteed to contain the value of the expression. The interpreter has been proved correct by the ACL2 theorem prover. The author discusses the interpreter, what has been proved about it by ACL2, and how it is used in symbolic reasoning about machine code.

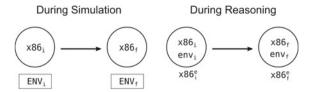

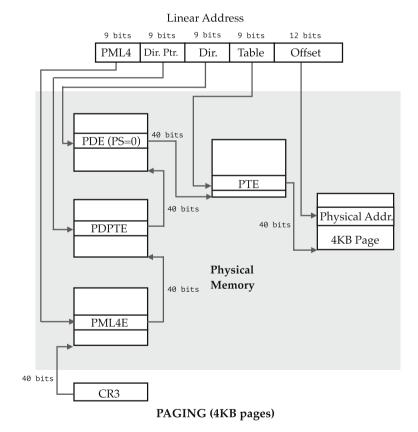

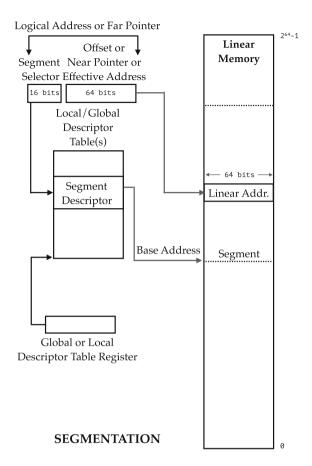

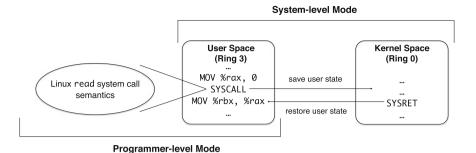

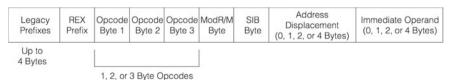

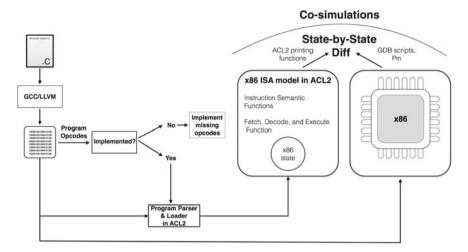

Shilpi Goel, Warren A. Hunt, Jr., and Matt Kaufmann describe in Chap. "Engineering a Formal, Executable x86 ISA Simulator for Software Verification" a formal, executable model of the x86 instruction-set architecture (ISA). They use this model to reason about x86 machine-code programs. Validation of the x86 ISA model is done by co-simulating it regularly against a physical x86 machine.

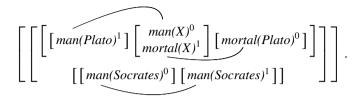

Jens Otten and Wolfgang Bibel present in Chap. "Advances in Connection-Based Automated Theorem Proving" calculi to automate theorem proving in classical and some important non-classical logics, namely first-order intuitionistic and first-order modal logics. These calculi are based on the connection method. The authors present details of the leanCoP theorem prover, a very compact PROLOG implementation of the connection calculus for classical logics. leanCoP has also been adapted to non-classical logics by integrating a prefix unification algorithm.

### **Run-Time Assertion Checking**

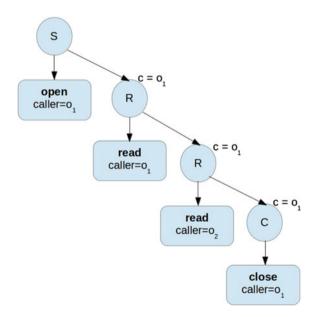

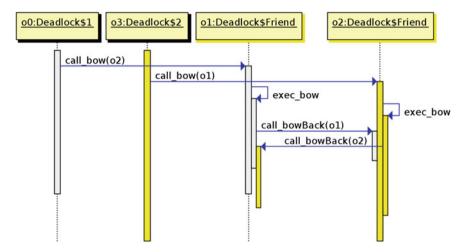

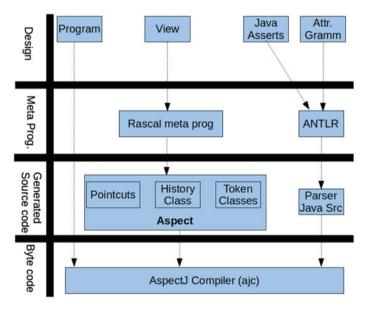

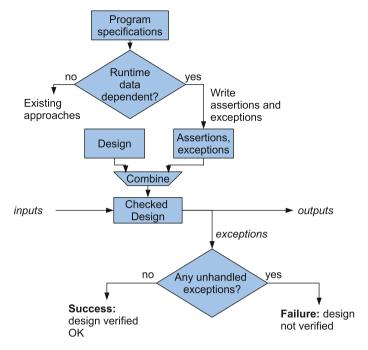

Frank S. de Boer and Stijn de Gouw extend in Chap. "Run-Time Deadlock Detection" run-time assertions by attribute grammars for specifying properties of message sequences. These assertions are used in a method for detecting deadlocks at run-time in both multi-threaded Java programs and systems of concurrent objects.

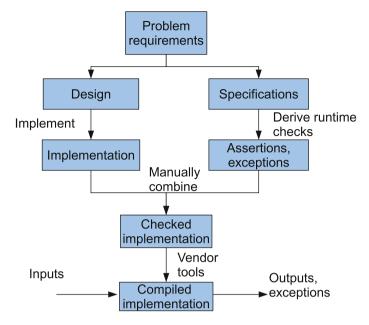

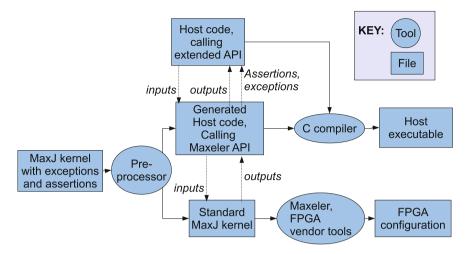

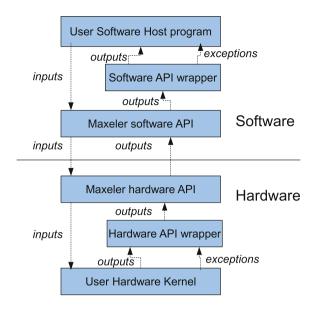

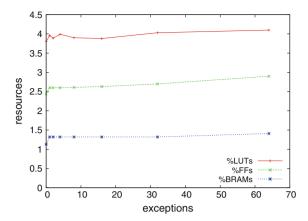

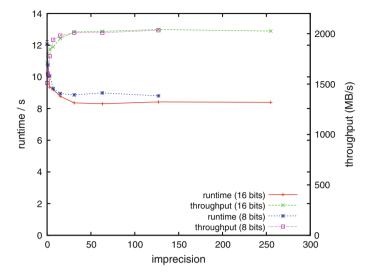

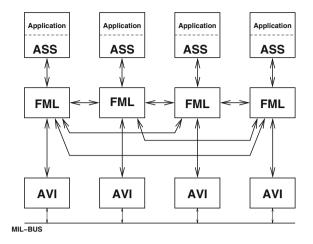

Tim Todman and Wayne Luk present in Chap. "In-Circuit Assertions and Exceptions for Reconfigurable Hardware Design" a high-level approach to adding assertions and exceptions in a hardware design targeting FPGAs (Field Programmable Gate Arrays). They allow for imprecise assertions and exceptions to trade performance for accurate location of errors.

### Formal and Semi-formal Methods

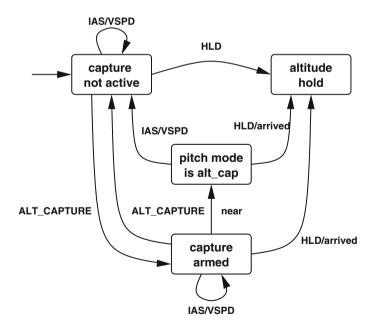

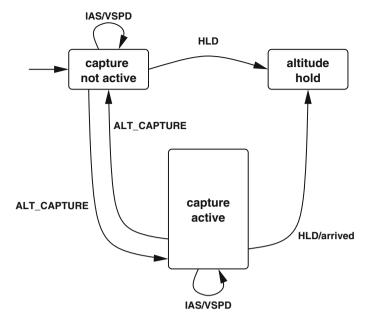

Bettina Buth reports in Chap. "From ProCoS to Space and Mental Models – A Survey of Combining Formal and Semi-Formal Methods" on work influenced by the ProCoS project. Systems from the application areas of space and aerospace are analysed using suitable abstractions to CSP specifications and the FDR model checker.

### **Web-Supported Communities in Science**

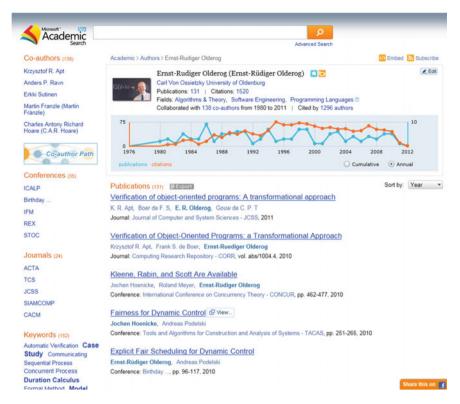

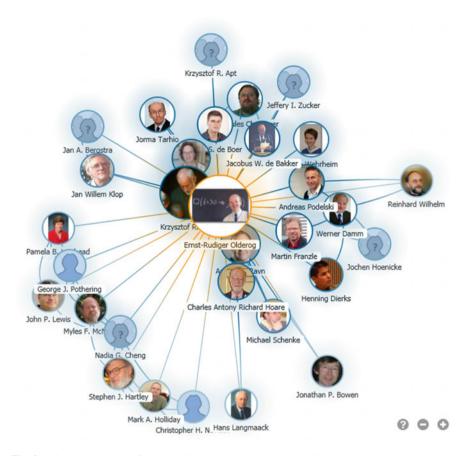

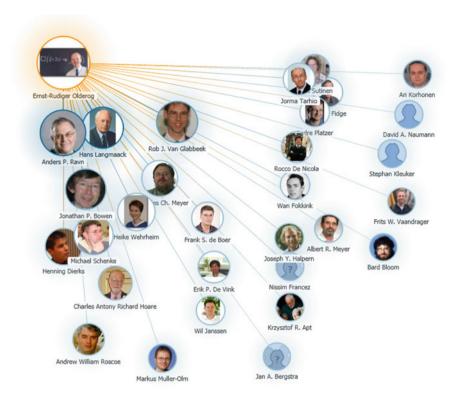

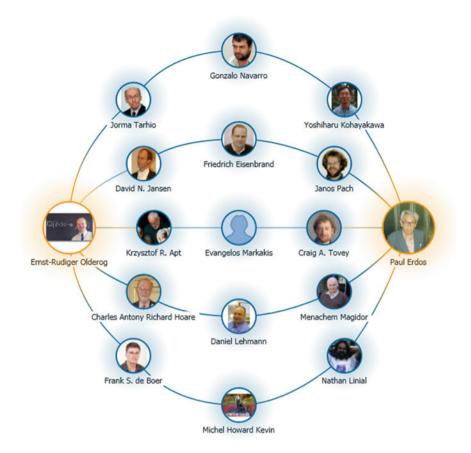

Jonathan P. Bowen studies in Chap. "Provably Correct Systems: Community, Connections, and Citations" the building and support of scientific communities and collaboration, especially online, visualized graphically and formalized using the Z notation, including the concept of a "Community of Practice". His examples are drawn from the ProCoS project.

In summary, we hope that you enjoy this volume, providing a selection of research developments and perspectives since the original ProCoS initiatives of the 1990s. Further ProCoS-related information can be found online under:

http://formalmethods.wikia.com/wiki/ProCoS

Limerick, Ireland London, UK Oldenburg, Germany Mike G. Hinchey Jonathan P. Bowen Ernst-Rüdiger Olderog

### Acknowledgements

The following reviewed papers in these proceedings: Wolfgang Bibel, Darmstadt University of Technology, Germany Simon Bliudze, EPFL, Switzerland Jonathan P. Bowen, London South Bank University, UK Bettina Buth, HAW Hamburg, Germany Michael Butler, University of Southampton, UK Ana Cavalcanti, University of York, UK Frank de Boer, CWI, The Netherlands Willem-Paul de Roever, University of Kiel, Germany John Derrick, Unversity of Sheffield, UK Martin Fränzle, University of Olderburg, Germany Anthony Hall, Independent consultant, UK Jifeng He, East China Normal University, China Warren Hunt, University of Texas, USA Cliff Jones, Newcastle University, UK Zhiming Liu, Southwest University, China Annabelle McIver, Macquarie University, Australia Dominique Méry, University of Lorraine, LORIA, France Ernst-Rüdiger Olderog, University of Olderburg, Germany Jan Peleska, University of Bremen, Germany Anders P. Ravn, Aalborg University, Denmark Augusto Sampaio, Federal university of Pernambuco, Brazil Elizabeth Scott, University of London, UK Jiangi Shi, National University of Singapore, Singapore Marina Waldén, Åbo Akademi University, Finland Jim Woodcock, University of York, UK Naijun Zhan, Institute of Software, Chinese Academy of Sciences, China Huibiao Zhu, East China Normal University, China

# **Contents**

| Part I Historic Account                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| ProCoS: How It All Began – as Seen from Denmark                                                                       | 3   |

| Part II Hybrid Systems                                                                                                |     |

| Constraint-Solving Techniques for the Analysis of Stochastic  Hybrid Systems                                          | ç   |

| MARS: A Toolchain for Modelling, Analysis and Verification of Hybrid Systems                                          | 39  |

| Part III Correctness of Concurrent Algorithms                                                                         |     |

| A Proof Method for Linearizability on TSO Architectures John Derrick, Graeme Smith, Lindsay Groves and Brijesh Dongol | 61  |

| Part IV Interfaces and Linking                                                                                        |     |

| Linking Discrete and Continuous Models, Applied to Traffic Manoeuvrers                                                | 95  |

| Towards Interface-Driven Design of Evolving Component-Based Architectures                                             | 121 |

xviii Contents

| Part V Automatic Verification                                                                    |     |

|--------------------------------------------------------------------------------------------------|-----|

| Computing Verified Machine Address Bounds During Symbolic Exploration of Code                    | 151 |

| Engineering a Formal, Executable x86 ISA Simulator for Software Verification                     | 173 |

| Advances in Connection-Based Automated Theorem Proving  Jens Otten and Wolfgang Bibel            | 211 |

| Part VI Run-Time Assertion Checking                                                              |     |

| Run-Time Deadlock Detection                                                                      | 245 |

| In-Circuit Assertions and Exceptions for Reconfigurable Hardware Design Tim Todman and Wayne Luk | 265 |

| Part VII Formal and Semi-formal Methods                                                          |     |

| From ProCoS to Space and Mental Models—A Survey of Combining Formal and Semi-formal Methods      | 285 |

| Part VIII Web-Supported Communities in Science                                                   |     |

| Provably Correct Systems: Community, Connections, and Citations                                  | 313 |

| Erratum to: ProCoS: How It All Began – as Seen from Denmark                                      | E1  |

# Part I Historic Account

# ProCoS: How It All Began – as Seen from Denmark

Dines Bjørner

**Abstract** I reminisce over an episode at the 9–13 November 1987 IFIP WG2.3 meeting at Château du Pont d'Oye in Belgium — and at what followed.

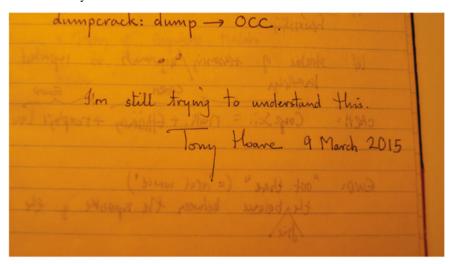

I had given a half hour presentation of how we, in Denmark, had developed a compiler for the full Ada programming language. My presentation had evolved around a single slide showing boxes and arrows between these, all properly labeled. Edsger W. Dijkstra had railed during my short presentation against my using diagrams — despite my claiming that boxes denoted certain kinds of algebras and arrows certain kind of morphisms between these. After my talk there was a coffee break. Tony Hoare took me aside. Asked permission to write in my note book. And this is what he wrote:

As he wrote it, Tony carefully explained what he was after. To me that became the day of conception of the first ProCoS project. I leave it to you to decipher the characteristic handwriting of Tony. OCC is some programming language. So is CSP. A specification maps programs in OCC into programs in CSP. VLSI is a language for specifying VLSI designs. Its semantics, in terms of CSP, is behav.

Now find, i.e., develop, a VLSI implemented machine, M, and some OCC code which maps into traces of the behaviour of M such that for all programs, D, in OCC, the VLSI machine implements the OCC specification correctly.

At the end of writing and narrating this, Tony asked: should we try get an ESPRIT BRA project around this idea? We did.

• • •

To me a deciding moment of the project occurred during our Bornholm workshop. Prof. E.V. Sørensen had given a talk in which he sketched, from the background of his field, Circuit Theory, some ideas about handling digital signal transitions. I

Paper read at the BCS-FACS ProCoS Workshop on Provably Correct Systems, London, UK, 9–10 March 2015.

The original version of this chapter was revised: For detailed information please see Erratum. The erratum to this chapter is available at 10.1007/978-3-319-48628-4\_14

D. Bjørner (⊠) Fredsvej 11, 2840 Holte, Denmark e-mail: mike.hinchey@lero.ie 4 D. Bjørner

believe that Erling's talk gave impetus to the Duration Calculus. During the break, after EVS' talk, I saw Anders (Ravn), Tony and Zhou discussing, it appeared, the evolving DC ideas.

• • •

During the ProCoS "25'th Anniversary" event, in London, 9–10 March, 2015, in the afternoon, after my morning presentation of the above "reminiscences", Tony wrote in the same notebook:

| 13. KJ                                                     | Tony Hope Hope d'ayz lorgium 75<br>13.88 87 "Fady the 13.80"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIVEN.                                                     | 3 Accountability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OCC a programming notation                                 | . Machine must output current state on req.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| spec: OCC -> CSP its semantics                             | Let to = storaget tragers, or Erapopers in t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VLSI a VLSI design notation                                | then behav (M)/tr = behav (M)/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| behav: VLSI -> CSP its semantics.                          | < behav (M)/load (t)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FIND - Suppose OF E. S. To Charles                         | where load = codeodumperack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| M: V251                                                    | FIND dumperack: dump - OCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| and code; OCC→ traces (behav (M)) such that For all D: OCC | Mary a character product to the state of the |

| $behav(M)/code(D) \leq spec(D)$                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (i.e. code is loaded only once at the beginning)           | Europe and disease to be the second of the desire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

I leave this to you to work on!

# Part II Hybrid Systems

## Constraint-Solving Techniques for the Analysis of Stochastic Hybrid Systems

Martin Fränzle, Yang Gao and Sebastian Gerwinn

Abstract The ProCoS project has been seminal in widening the perspective on verification of computer-based systems to a coverage of the detailed interaction and feedback dynamics between the embedded system and its environment. We have since then seen a steady increase both in expressiveness of the "hybrid" modeling paradigms adopting such an integrated perspective and in the power of automatic reasoning techniques addressing relevant fragments of logic and arithmetic. In this chapter we review definitions of stochastic hybrid automata and of parametric stochastic hybrid automata, both of which unify the hybrid view on system dynamics with stochastic modeling as pertinent to reliability evaluation, and we elaborate on automatic verification and synthesis methods based on arithmetic constraint solving. The procedures are able to solve step-bounded stochastic reachability problems and multi-objective parameter synthesis problems, respectively.

### 1 Introduction

An increasing number of the technical artifacts shaping our ambience are relying on often invisible embedded computer systems, rendering embedded computers the most common form of computing devices today. The vast majority — 98% according

This research has partially been funded by the German Research Foundation through the Collaborative Research Action SFB-TR 14 "Automatic Verification and Analysis of Complex Systems" (AVACS, www.avacs.org) and the Research Training Group DFG-GRK 1765: "System Correctness under Adverse Conditions" (SCARE, scare.uni-oldenburg.de).

M. Fränzle ( $\boxtimes$ ) · Y. Gao

Department of Computing Science, Carl von Ossietzky Universität Oldenburg,

Oldenburg, Germany

e-mail: fraenzle@informatik.uni-oldenburg.de

Y. Gac

e-mail: yang.gao@informatik.uni-oldenburg.de

S. Gerwinn

OFFIS Institute for Information Technology, Oldenburg, Germany e-mail: sebastian.gerwinn@offis.de

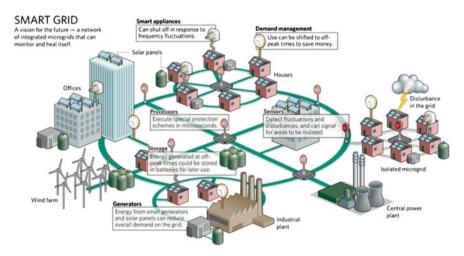

© Springer International Publishing AG 2017 M.G. Hinchey et al. (eds.), *Provably Correct Systems*, NASA Monographs in Systems and Software Engineering, DOI 10.1007/978-3-319-48628-4\_2 to www.artemis-ju.eu — of all processing elements manufactured goes to embedded applications, where they monitor and control all kinds of physical processes. Such interactions of the virtual with the physical world range from traditional control applications, like controlling an automotive powertrain, over computer-controlled active safety systems, like the anti-locking brake, the electronic stability program, or recently pedestrian detection integrated with emergency braking capabilities, to the vision of cyber-physical networks bringing even remote physical processes into our sphere of control.

Even to the general public, it has become evident that such immersion of computing elements into physical environments renders their functionality critical in many respects: critical to the function of the overall product, where a malfunction or undesired interaction of the embedded system may render the whole product partially or totally dysfunctional; critical to the performance of the overall product, where embedded control may influence power consumption, environmental impact, and many more performance dimensions; finally safety-critical, as causal chains mediated by the physical environment may propagate software faults and thus endanger life and property. A direct consequence is that correctness (in a broad sense) of embedded systems most naturally is defined in terms of the possible physical impact of its interaction with the environment. This insight marked a paradigm shift in the attitude to software correctness at the times when the ProCoS project was conceived a good quarter of a century ago. Rather than saying that correct software ought to infallibly implement some abstract algorithm or establish correctness properties in terms of conditions on intrinsic program variables (and other notions intrinsic to the algorithm, like termination), correctness became defined in terms of observables of external physical processes underlying an independent dynamics extrinsic to and only partially controllable by the software.

Within the ProCoS project, this issue was taken up by Zhou Chaochen and Anders Rayn, who first together with Tony Hoare defined the Duration Calculus [9] and later together with Hans Rischel and Michael R. Hansen extended it to cover hybrid discrete-continuous phenomena [10, 34]. While the former took the perspective of durational metric-time properties at the interface between embedded system and environment, thus not really covering environmental dynamics, the extension to Extended Duration Calculus in [10] permitted integration about environmental variables and thus formulation of integral equations, as equivalent to initial-value problems of ordinary differential equations. It thus is an example of a formal model permitting to model and analyze the tight interaction, and hence feedback dynamics, of the discrete switching behavior of embedded systems and the continuous dynamics of the physical environment as well as of continuous control components embedded into it. A related model also confining the description of environmental dynamics to ordinary differential equations and also adopting a qualitative view of the embedded system as a potentially demonically non-deterministic discrete computational device is Hybrid Automata [1]. Such models support qualitative behavioral verification in the sense of showing that a system behaving according to its nominal dynamics would never be able to engage in an undesired behavior, which, however, is a goal unlikely to be achieved in practice. First, designing systems to that level of correctness may be prohibitively expensive or it may be impractical due to necessary inclusion of components lacking tangible models of nominal behavior, like, e.g., computer vision and image classification algorithms. Second, even when possible in principle, the systems verified to that level will necessarily eventually deviate from their nominal behavior due to, e.g., component failures. Reflecting the consequential need for *quantitative* verification, stochastic variants of hybrid-system models have been suggested, like Probabilistic Hybrid Automata (PHA) [35] or Stochastic Hybrid Automata (SHA) [25]. In such extensions, either discrete actions can feature probabilistic branching or continuous evolution can evolve stochastic along, e.g., stochastic differential equations, or both.

The resulting models are inherently hard to analyze, as they combine various sources of undecidability, like state reachability in even the simplest classes of hybrid automata and the fragments of arithmetic induced by ordinary differential equations, with the necessity of reasoning about probability distributions over complexly shaped and sometimes not even first-order definable carriers, like the reachable states. It is thus obvious that exact automatic analysis methods for properties of interest, like the probability of reaching undesirable states, are impossible to attain. Nevertheless, safe approximations can be computed effectively, and often prove to be of sufficient accuracy to answer relevant questions with scrutiny, like certifying that the probability of reaching undesirable states remains below a given quantitative safety target. The pertinent techniques do either rely on state-space discretization by safe abstraction, e.g. Hahn et al.'s approach [43], or on constraint solving for stochastic logic involving arithmetic [15, 19], or on massive simulation paired with statistical hypothesis testing, beginning with Younes' seminal work [42]. We will in the remainder of this chapter report on our contributions to the constraint-based approach, thereby building on a series of results obtained over the past decade.

### Structure of the Chapter

In the next section, we provide an introduction to a class of stochastic hybrid automata featuring stochasticity—paired with non-determinism or parametricity—in their transitions. In Sect. 3, we move on to the depth-bounded safety analysis of such stochastic hybrid automata. The underlying technology is an extension of satisfiability-modulo-theory solving (SMT, [4]) to Stochastic Satisfiability-Modulo-Theory (SSMT) akin to the extension of Propositional Satisfiability (SAT) to Stochastic Propositional Satisfiability (SSAT) suggested by Papadimitriou and Majercik [28, 33]. Section 4, finally, turns to the problem of multi-objective parameter synthesis in parametric variants of stochastic hybrid automata, which we solve by a machine-learning style integration of simulation and arithmetic constraint solving.

### 2 Stochastic Hybrid Transition Systems

The model of hybrid automata [1, 2, 22, 26] has been suggested as a formal set-up for analyzing the the interaction of discrete and continuous processes in hybrid-state dynamical systems. They combine pertinent formalism for describing discrete,

12 M. Fränzle et al.

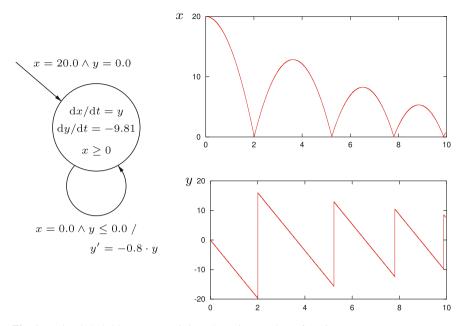

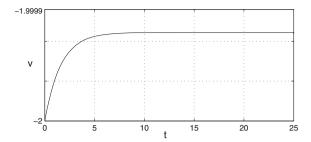

Fig. 1 A simple hybrid automaton (*left*) and a trajectory thereof (*right*)

computational and continuous, mostly physical or control-oriented dynamical processes by extending finite automata with a vector of continuous variables and "decorating" them with ordinary differential equations in each location and assignments to these extra variables upon transitions. A simple hybrid automaton and its associated dynamic behavior, which is a piece-wise continuous trajectory, are depicted in Fig. 1.

While this model permits the analysis of deterministic as well as uncertain hybrid-state systems, as the latter can be modeled by various forms of non-determinism in the automata, like uncontrolled inputs, non-deterministic transition selection, or parameter ranges in the differential (in-)equations, it is confined to *qualitative* behavioral verification in the sense of showing that a system behaving according to its nominal dynamics would never be able to engage in an undesired behavior. This ideal, however, is hardly achieved in practice, as systems strictly adhering to their nominal behavior would either be prohibitively expensive or even infeasible to design. Qualitative verification consequently is indicative of the nominal behavior only, yet does not cover the full set of expected behaviors of the system under design, which includes (traditionally rare, but with the advent of trained classifiers in, e.g., computer vision systems for automated driving increasingly frequent) deviations from nominal behavior also.

As the expected low to moderate frequency of deviations from nominal behavior would not justify the same demonic view of uncertainties in system dynamics as adopted in qualitative verification, namely that every single abnormal behavior that

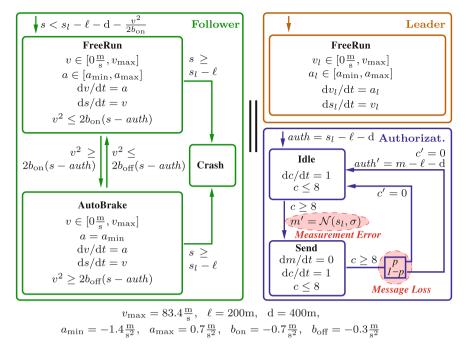

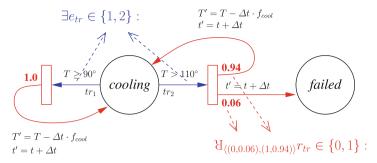

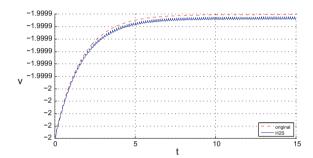

Fig. 2 Model of moving-block train control in ETCS level 3 including relevant random disturbances (encircled areas) in the form of measurement error in positional information and possible message loss, after [17]

might be possible would render the system design incorrect, *quantitative* counterparts to qualitative hybrid models and verification methods have been developed. The corresponding *probabilistic* or *stochastic* models provide more concise quantitative information about the uncertainties involved in terms of probabilities. To incorporate this kind of information, both the underlying models and the corresponding analysis techniques have to be adapted. Verifying reachability and safety properties within this extended setting then corresponds to obtaining statements about the probability of these properties to be satisfied.

To illustrate the challenges arising in incorporating the information about random disturbances into the model of hybrid automata, we show a model model mimicking distance control at level 3 of the European train control systems ETCS in Fig. 2. The idea of the control system is to switch to an automatic braking mode "AutoBrake" initiating a controlled emergency deceleration whenever the necessary deceleration rate for coming to a standstill at a safety distance (400 m) behind the preceding train exceeds a threshold value ( $-0.7 \, \frac{\text{m}^2}{\text{s}}$ ). The function of this control system, however, is impeded by measurement noise in determining train positions and the risk of message loss between trains, as positions are determined locally in a train and announced via train-to-train communication. The extended hybrid model depicted in Fig. 2 incorporates these stochastic disturbances. More specifically, the perturbed measurement

14 M. Fränzle et al.

of the position of the leading train is characterized by a normal distribution  $\mathcal{N}(s_l, \sigma)$  centered around the true position  $s_l$  and the measurement process itself is modeled by copying this skewed image of the physical entity  $s_l$  into its real-time image m. This is in contrast to a typical nominal model, where the controller may be modeled as having direct access to the physical entities. Additionally, unreliable communication is also considered, i.e., the communication of resultant movement authorities is allowed to fail with probability 0.1. The resulting model is called a *Stochastic Hybrid Automaton (SHA)* [25, 35]. Note that the automaton in Fig. 2 features both non-determinism and stochasticity in its transitions, with the former being interpreted demonically.

For such models, we are interested in solving two problems, which will be the subjects of Sects. 3 and 4:

- 1. Given a stochastic hybrid automaton A and a set of undesirable states G in the state set of A, determine whether the probability of reaching G stays below a given safety target  $\varepsilon$ . Given that non-determinism is interpreted demonically, the probability of reaching G thereby has to be determined w.r.t. a most malicious adversary resolving the non-deterministic choices.

- Given a stochastic hybrid automaton featuring parameters in its probability distributions, determine whether there is a parameter instance satisfying a design objective in terms of expectations on some cost and/or reward variables in the hybrid system.

Formally, SHA are infinite-state Markov Decision Processes (MDP), where the infinite-state behavior is induced by the hybrid discrete-continuous state dynamics, while the MDP property arises from the interplay of stochastic and non-deterministic choices. A stochastic hybrid system (in its continuous-time variant) thus interleaves

- 1. *continuous flows* arising while residing in a discrete location and being governed by the differential (in-)equation and the invariant condition assigned to the location with

- 2. immediate transitions featuring a guard condition on the continuous variables, a deterministic or non-deterministic state update w.r.t. both some continuous variables and possibly the discrete successor location, and potentially a series of randomized updates to continuous variables are the successor location.

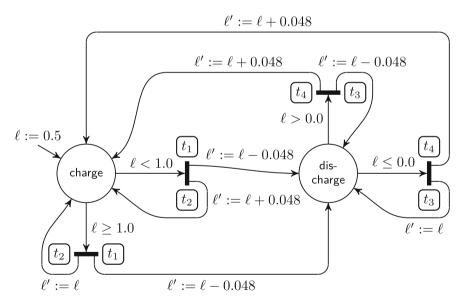

As a suitable semantic basis for the automatic analysis of hybrid automata featuring stochastic behavior, we can consequently base our investigations on a more abstract definition of hybrid-state transition systems featuring stochastic behavior, a form of infinite-state Markov Decision Process (MDP). In full generality, such a (parametric) hybrid stochastic transition system comprises the following:

1. A finite set  $D = \{d_1, \dots, d_m\}$  of discrete variables. Discrete variables range over  $\mathbb{Z}^{1}$ .

<sup>&</sup>lt;sup>1</sup>The reader might expect to rather see finite sub-ranges of  $\mathbb Z$  or other finite sets as domains. To avoid cluttering the notation, we abstained from this. It should be noted that this does not induce a loss of generality, as not all of  $\mathbb Z$  need to be dynamically reachable.

- 2. A finite set  $C = \{x_1, \dots, x_n\}$  of continuous variables. Continuous variables range over  $\mathbb{R}^2$ .

- 3. A finite (and possibly empty) set  $P = \{p_1, \dots, p_k\}$  of parameters with associated range  $\theta \subseteq \mathbb{R}^k$ .

- 4. An initial state  $i \in \Sigma$ , where  $\Sigma = \mathbb{Z}^m \times \mathbb{R}^n$  is the state set of the transition system.

- 5. A finite set  $T = \{t_1, \dots, t_l\}$  of stochastic transitions. Each such transition comprises a non-deterministic guarded assignment, expressed as a pre-post relation in  $\Sigma \times \Sigma$ , followed by a finite (possibly empty) sequence of stochastic assignments to individual variables, which are executed in sequence and may depend on the preceding ones and on the parameters.

Traditional stochastic hybrid automata diagrams, as depicted in Figs. 2 and 6, can easily be interpreted as instances of this model by interpreting both their continuous flows and immediate transitions as stochastic transitions. To this end, please note that stochastic transitions need not contain a proper stochastic part, but may also be just non-deterministic or even deterministic.

In order to achieve a uniform treatment of discrete and continuous stochastic assignments, we equip  $\mathbb R$  with the Lebesgue measure and  $\mathbb Z$  with cardinality of its subsets as a measure. Given this convention, we can uniformly write  $\int_a^b p(x) \mathrm{d}x$  for determining the probability mass assigned by a density (or, in the discrete case, a distribution) p to the interval [a,b], as the measure is understood. Note that in the discrete case,  $\int_a^b p(x) \mathrm{d}x = \sum_{x=a}^b p(x)$  due to the particular choice of the measure for  $\mathbb Z$ . This permits us to uniformly treat densities over the continuum and distributions over discrete carriers as densities. A density over domain X, where X is either  $\mathbb R$  or  $\mathbb Z$ , is a measurable function  $\delta: X \to \mathbb R_{\geq 0}$  with  $\int_{-\infty}^\infty \delta(x) \mathrm{d}x = 1$ . We denote by  $P_X$  the set of all densities over X. A stochastic assignment for a variable  $v \in D \cup C$  with its associated domain  $V \in \{\mathbb Z, \mathbb R\}$  is a mapping  $sa_v: \theta \to \Sigma \to P_V$ . It assigns to each parameter instance and each state a density of the successor values for v.

We are ultimately interested in determining the probability of reaching a certain set  $G \subset \Sigma$  of goal states or the expectation of a function  $f: \sigma \to \mathbb{R}$ . As the former is a special case of the latter, using the characteristic function  $\chi_G^3$  as reward, it suffices to define expectations.

Given that a non-deterministic assignment simply is a relation between pre- and post-states, i.e., a subset of  $\Sigma \times \Sigma$  defining both the transition guard (due to possible partiality of the relation) and the (possibly non-deterministic) update to all the variables, depth-bounded expectations in the infinite-state MDP mediated by the stochastic hybrid transition system can now be defined inductively by means of a Bellmann backward induction [5] as follows: The (best-case) expectation  $\mathcal{E}_f^k(\sigma,\theta)$  of reward f over k steps of the transition system under parameterization  $\theta$  and starting from state  $\sigma \in \Sigma$  is

<sup>&</sup>lt;sup>2</sup>As for discrete variables, this does not exclude the possibility that only a bounded sub-range may dynamically be reachable.

<sup>&</sup>lt;sup>3</sup>Defined as  $\chi_G(\sigma) = \begin{cases} 1 & \text{if } \sigma \in G, \\ 0 & \text{if } \sigma \notin G. \end{cases}$

16 M. Fränzle et al.

$$\begin{split} \mathcal{E}_f^0(\sigma,\theta) &= f(\sigma) \ , \\ \mathcal{E}_f^{k+1}(\sigma,\theta) &= \max_{t = \langle na,sa_1,\dots,sa_n \rangle \in T} \quad \max_{\sigma_1 \in \Sigma \text{ such that } (\sigma,\sigma_1) \in na} \\ &\int \dots \int sa_1^{\theta}(\sigma_1)(\sigma_2) \cdots sa_n^{\theta}(\sigma_n,)(\sigma_{n+1}) \mathcal{E}_f^k(\sigma_{n+1},\theta) \mathrm{d}\sigma_1 \dots \mathrm{d}\sigma_{n+1} \ . \end{split}$$

Here, na denote the non-deterministic assignment and  $sa_i^{\theta}$  denotes the effect of a stochastic assignment, resp., in a transition  $t = \langle na, sa_1, \ldots, sa_n \rangle$ . The effect  $sa^{\theta}$  of a stochastic assignment sa to variable v is

$$sa^{\theta}(\sigma)(x) = \begin{cases} \sigma(x) & \text{if } x \neq v, \\ sa(\theta)(\sigma)(v) & \text{if } x = v. \end{cases}$$

Taken together, the non-deterministic transition selection as well as the non-deterministic assignment thus implements an oracle maximizing rewards, while the stochastic assignments just implement their stochastic transition kernels.

### 3 Bounded Reachability Checking for Stochastic Hybrid Automata

In order to analyze Stochastic Hybrid Automata (SHA) models, like the one depicted in Fig. 2, we need techniques being able to analyze their intrinsic combination of stochastic dynamics and infinite-state behavior. Formally, SHA are infinite-state Markov Decision Processes (MDP), where the infinite-state behavior is induced by the hybrid discrete-continuous state dynamics, while the MDP property arises from the interplay of stochastic and non-deterministic choices (e.g., concerning *a* in Fig. 2). As verification tools for finite-state MDP are readily available, a particular technique is to use abstraction for obtaining a safe finite-state overapproximation, subsequently verifying the properties of interest on the abstraction, as pursued e.g. in [17]. A more direct approach along the lines of bounded model checking (BMC) [6, 21] in its variant for hybrid automata [3, 12, 23] is to encode the stochastic behavior within the constraint formula. This requires more expressive constraint logic then the satisfiability-modulo-theory calculi used in the case of qualitative verification [3, 12, 23, among others], which have been pioneered by Fränzle, Hermanns, and Teige under the name *Stochastic Satisfiability Modulo Theory (SSMT)* [15].

### 3.1 Stochastic Satisfiability Modulo Theory

The idea of modeling uncertainty in satisfiability problems was first proposed within the framework of propositional satisfiability (SAT) by Papadimitriou, yielding

Stochastic SAT (SSAT) [33], a logic featuring both existential quantifiers and randomized quantifiers allowing to express  $1\frac{1}{2}$  player games (one strategic, one randomized player). This work has been lifted to Satisfiability Modulo Theories (SMT) by Fränzle, Teige et al. [15, 38], providing a logic called Stochastic Satisfiability Modulo Theory (SSMT) permitting symbolical reasoning about bounded reachability problems of probabilistic hybrid automata (PHA). Instead of being true or false, an SSAT or SSMT formula  $\Phi$  has a probability as semantics. This quantitative semantics reflects the probability of satisfaction of  $\Phi$  under optimal resolution of the non-random quantifiers. SSAT and SSMT permit concise description of diverse problems combining reasoning under uncertainty with data dependencies. Applications range from AI planning [27, 29, 30] to analysis of PHA [15]. A major limitation of the SSMT-solving approach pioneered by Teige [37] is that all quantifiers (except for implicit innermost existential quantification of all otherwise unbound variables) are confined to range over finite domains. As this implies that the carriers of probability distributions have to be finite, a large number of phenomena cannot be expressed within that SSMT framework, such as continuous noise or measurement error in hybrid systems. To overcome this limitation, our recent work [19] relaxes the constraints on the domains of randomized variables, now also admitting quantification over continuous domains and continuous probability distributions in SSMT solving.

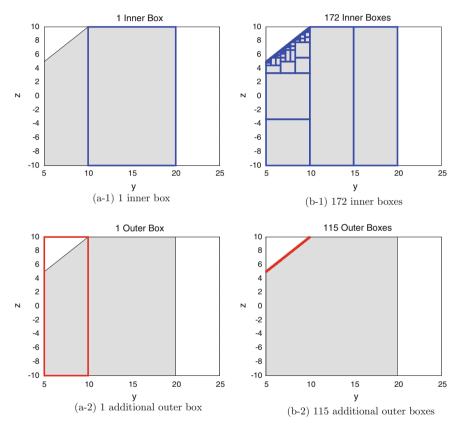

The approach is based on a combination of the iSAT arithmetic constraint solver [13] with branch-and-prune rules for the quantifiers generalizing those suggested in [14, 37]. Covering an undecidable fragment of real arithmetic involving addition, subtraction, multiplication and transcendental functions, measuring solution sets exactly by an algorithm obviously is infeasible. The solving procedure therefore approximates the exact satisfaction probability of the formula under investigation and terminates with a conclusive result whenever the approximation gets tight enough to answer the question whether the satisfaction probability is above or below a target value specified by the user, e.g., a safety target.

We will subsequently introduce the logic manipulated by our solver, then explain the solving procedure, and finally demonstrate its use for analyzing stochastic hybrid automata.

The syntax of the input language of the solver, which is SSMT formulae over continuous quantifier domains, CSSMT for short, agrees with the discrete version from [15], except that continuous quantifier ranges are permitted.

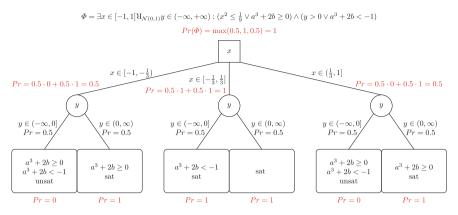

**Definition 1** An SSMT formula with continuous domain (CSSMT formula) is of the form  $\Phi = \mathcal{Q} : \varphi$ , where