Kazuhiro Ogata Mark Lawford Shaoying Liu (Eds.)

# Formal Methods and Software Engineering

18th International Conference on Formal Engineering Methods, ICFEM 2016 Tokyo, Japan, November 14–18, 2016, Proceedings

## Lecture Notes in Computer Science

## 10009

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7408

Kazuhiro Ogata · Mark Lawford Shaoying Liu (Eds.)

## Formal Methods and Software Engineering

18th International Conference on Formal Engineering Methods, ICFEM 2016 Tokyo, Japan, November 14–18, 2016 Proceedings

*Editors* Kazuhiro Ogata School of Information Science Japan Advanced Institute of Science and Technology (JAIST) Nomi Japan

Mark Lawford Department of Computing and Software McMaster University Hamilton, ON Canada Shaoying Liu Department of Computer Science Hosei University Tokyo Japan

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-47845-6 ISBN 978-3-319-47846-3 (eBook) DOI 10.1007/978-3-319-47846-3

Library of Congress Control Number: 2016954467

LNCS Sublibrary: SL2 - Programming and Software Engineering

#### © Springer International Publishing AG 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## Preface

The International Conference on Formal Engineering Methods (ICFEM) is a premier conference for research in all areas related to formal engineering methods, such as verification and validation, software engineering, formal specification and modeling, software security, and software reliability. Since 1997, ICFEM has been serving as an international forum for researchers and practitioners who have been seriously applying formal methods to practical applications. Researchers and practitioners, from industry, academia, and government, are encouraged to attend, present their research, and help advance the state of the art. We are interested in work that has been incorporated into real production systems, and in theoretical work that promises to bring practical and tangible benefit.

In recent years, ICFEM has taken place in Paris, France (2015), Luxembourg (2014), Queenstown, New Zealand (2013), Kyoto, Japan (2012), Durham, UK (2011) and Shanghai, China (2010). The 18<sup>th</sup> edition of ICFEM took place in Tokyo during November 16–18, 2015. The Program Committee (PC) received 64 full research papers. Each paper received at least three reports from PC members or external reviewers. On the basis of these reports, each submission was extensively discussed in the virtual meeting of the PC, and the PC decided to accept 27 papers. The proceedings also include a full paper and two short summary papers from the three keynote speakers, Tom Maibaum (McMaster University), W. Eric Wong (University of Texas at Dallas), and Keijiro Araki (Kyushu University).

ICFEM 2016 was organized and supported by Hosei University. The conference would not have been possible without the contributions and the support of the following organizations: the Institute of Electronics, Information and Communication Engineers (IEICE), Japan Society for Software Science and Technology (JSSST), and The Murata Science Foundation. We thank also the Local Organizing Committee for their hard work in making ICFEM 2016 a successful and exciting event.

The main event was preceded by three workshops and a tutorial: the 5<sup>th</sup> International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2016), the 6<sup>th</sup> International Workshop SOFL+MSVL, the Workshop on Formal and Model-Driven Techniques for Developing Trustworthy Systems, and a one day tutorial on formal specification and verification with CafeOBJ.

We would like to thank the numerous people who contributed to the success of ICFEM 2016: the Steering Committee members, the PC members and the additional reviewers for their support in selecting papers and composing the conference program, and the authors and the invited speakers for their contributions without which, of course, these proceedings would not exist. We would like also to thank Springer for

VI Preface

their help during the production of this proceedings volume and the EasyChair team for their great conference system.

August 2016

Kazuhiro Ogata Mark Lawford Shaoying Liu

## Organization

## **Program Committee**

Bernhard K. Aichernig TU Graz. Austria Étienne André Université Paris 13, France JAIST, Japan Toshiaki Aoki Christian Attiogbe University of Nantes, France **Richard Banach** University of Manchester, UK Ezio Bartocci TU Wien, Austria Michael Butler University of Southampton, UK University of York, UK Ana Cavalcanti Korea University, South Korea Sungdeok Cha Yuting Chen Shanghai Jiao Tong University, China Université Paris-Sud, France Svlvain Conchon Frank De Boer CWI. The Netherlands Zhenhua Duan Xidian University, China University of Oxford, UK Jeremy Gibbons Stefania Gnesi **ISTI-CNR**, Italy Victoria University of Wellington, New Zealand Lindsav Groves Ian J. Hayes University of Queensland, Australia Michaela Huhn TU Clausthal, Germany Newcastle University, UK Alexei Iliasov National Institute of Informatics, Japan Fuyuki Ishikawa Weigiang Kong Dalian University of Technology, China Fabrice Kordon LIP6/UPMC, France Mark Lawford McMaster University, Canada Xiaoshan Li University of Macau, SAR China Hosei University, Japan Shaoying Liu Yang Liu Nanyang Technological University, Singapore Larissa Meinicke University of Queensland, Australia Stephan Merz Inria Nancy, France Huaikou Miao Shanghai University, China Mohammadreza Mousavi Halmstad University, Sweden National Institute of Informatics, Japan Shin Nakajima Akio Nakata Hiroshima City University, Japan UC, Spain Manuel Nuñez Kazuhiro Ogata JAIST, Japan Shinshu University, Japan Kozo Okano Jun Pang University of Luxembourg TZI, Universität Bremen, Germany Jan Peleska

| Ion Petre       | Åbo Akademi University, Finland                     |

|-----------------|-----------------------------------------------------|

| Shengchao Qin   | Teesside University, UK                             |

| Silvio Ranise   | FBK-Irst, Italy                                     |

| Adrian Riesco   | Universidad Complutense de Madrid, Spain            |

| Jing Sun        | University of Auckland, New Zealand                 |

| Kenji Taguchi   | AIST, Japan                                         |

| Jaco van de Pol | University of Twente, The Netherlands               |

| Thomas Wahl     | Northeastern University, USA                        |

| Xi Wang         | Hosei University, Japan                             |

| Alan Wassyng    | McMaster University, Canada                         |

| Fatiha Zaidi    | Université Paris-Sud, France                        |

| Jian Zhang      | Institute of Software, Chinese Academy of Sciences, |

|                 | China                                               |

| Min Zhang       | East China Normal University, China                 |

| Hong Zhu        | Oxford Brookes University, UK                       |

| Huibiao Zhu     | Software Engineering Institute, East China Normal   |

|                 | University, China                                   |

|                 |                                                     |

## **Additional Reviewers**

Aiguier, Marc Azadbakht, Keyvan Basile. Davide Bloemen, Vincent Briday, Mikaël Ciancia, Vincenzo Colley, John De Masellis, Riccardo Dokter, Kasper Fei, Yuan Frehse, Goran Gao, Honghao Hartmanns, Arnd He, Mengda Hoang, Thai Son Kamali, Mojgan Khakpour, Narges Kitamura, Takashi Konnov, Igor Kuruma, Hironobu Laarman, Alfons Li. Li Lorber, Florian

Millet, Laure Oh, Hakjoo Patcas, Lucian Petre, Luigia Renault, Etienne Ribeiro, Pedro Salehi Fathabadi, Asieh Semini, Laura Souma, Daisuke Steel, Jim Su, Wen Sznajder, Nathalie Tappler, Martin Taromirad, Masoumeh Traverso, Riccardo Wang, Luyao Winter, Kirsten Wu, Xingming Xu, Zhiwu Yang, Yilong Yuan, Qixia Zheng, Zheng

**Abstracts of Keynotes**

## **Combinatorial Testing and Its Applications**

W. Eric Wong

Advanced Research Center for Software Testing and Quality Assurance, Department of Computer Science, University of Texas at Dallas, Richardson, USA http://www.utdallas.edu/~ewong ewong@utdallas.edu

Studies have shown that combinatorial testing can help programs detect hard-to-find software bugs that may not be revealed by test cases generated using other testing techniques. The first part of this talk focuses on traditional black-box requirements-based combinatorial testing. In particular, I will discuss results and lessons learned from two real-life industry applications: a control panel of a rail-road system and a Linux system. The second part extends the concept of combinatorial testing to a white-box structure-based setting. I will present an advanced coverage criterion, *Combinatorial Decision Coverage*, in conjunction with symbolic execution to achieve high coverage cost-effectively without suffering from potential space exploration. Finally, I will explain how combinatorial testing can be applied to a graph-based methodology for testing IoT (Internet of Things).

#### Bio

W. Eric Wong received his M.S. and Ph.D. in Computer Science from Purdue University, West Lafayette, Indiana, USA. He is a Full Professor, the Director of International Outreach, and the Founding Director of Advanced Research Center for Software Testing and Quality Assurance (http://paris.utdallas.edu/stqa) in Computer Science at the University of Texas at Dallas (UTD). He also has an appointment as a guest researcher at the National Institute of Standards and Technology, an agency of the U.S. Department of Commerce. Prior to joining UTD, he was with Telcordia Technologies (formerly Bellcore) as a senior research scientist and the project manager in charge of Dependable Telecom Software Development.

Dr. Wong is the recipient of the 2014 IEEE Reliability Society Engineer of the Year. He is also the Edit-in-Chief of the IEEE Transactions on Reliability. His research focuses on helping practitioners improve software quality while reducing production cost. In particular, he is working on software testing, program debugging, risk analysis, safety, and reliability. Dr. Wong has published more than 180 papers and edited 2 books.

Dr. Wong is also the Founding Steering Committee Chair of the IEEE International Conference on Software Security and Reliability (SERE) and the IEEE International Workshop on Program Debugging. In 2015, the SERE conference and the QSIC conference (International Conference on Quality Software) merged into one large conference, QRS, with Q representing *Quality*, R for *Reliability*, and S for *Security*. Dr. Wong continues to be the Steering Committee Chair of this new conference (http://paris.utdallas.edu/qrs).

## A (Proto) Logical Basis for the Notion of a Structured Argument in a Safety Case

Valentín Cassano<sup>(⊠)</sup>, Thomas S.E. Maibaum, and Silviya Grigorova

McMaster Centre for Software Certification, McMaster University, Hamilton, Canada.

{cassanv,grigorsb}@mcmaster.ca, tom@maibaum.org

Abstract. The introduction of safety cases was a step in the right direction in regards to safety assurance. As presently practiced, safety cases aim at making a serious attempt to explicate, and to provide some structure for, the reasoning involved in assuring that a system is safe, generally in terms of so-called structured arguments. However, the fact current notations for expressing these structured arguments have no formal semantics and, at best, are loosely linked to goal structuring ideas and to Toulmin's notion of an argument pattern, is a crucial issue to be addressed. History clearly demonstrates that languages that have no formal semantics are deficient in relation to the requirements of a serious approach to engineering. In other words, one can only go so far with intuition, and certainly not far enough to justify the safety of complex systems, such as Cyber Physical Systems or autonomous cars. By rehearsing Gentzen's program for formalizing mathematical reasoning, his famous Calculus of Natural Deduction, we show how we can begin a program of formalizing safety reasoning by developing a working definition of a structured argument in a safety case and a calculus for safety reasoning.

## Promotion of Formal Approaches in Japanese Software Industry and a Best Practice of FeliCa's Case (Extended Abstract)

Keijiro Araki<sup>1(\Box)</sup> and Taro Kurita<sup>2</sup>

<sup>1</sup> Kyushu University, 744 Motooka, Nishi-ku, Fukuoka 819-0395, Japan araki@ait.kyushu-u.ac.jp

<sup>2</sup> Sony Corporation, 2-10-1 Osaki, Shinagawa-ku, Tokyo 141-8610, Japan

**Abstract.** We have been making much effort to promote formal methods in Japan, especially Japanese IT companies. This paper describes our activities in Japan for almost twenty years, and shows typical reactions from such Japanese companies for application of formal methods. We mention about the obstacles they think to adopting formal methods in their real software development projects. On the other hand we also present a case of FeliCa Networks, Inc. as a best practice of applying formal methods in Japan. We discuss the lessons learned from our efforts of promoting formal methods and the FeliCa's case. Finally, we briefly introduce our research project to support software developers in adopting formal approaches to real projects.

Keywords: Formal methods  $\cdot$  Rigorous specification  $\cdot$  Practice  $\cdot$  Development process  $\cdot$  FeliCa IC Chip  $\cdot$  VDM  $\cdot$  VDMPad  $\cdot$  ViennaTalk

## Contents

| A (Proto) Logical Basis for the Notion of a Structured Argument<br>in a Safety Case                                                                                                   | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Valentín Cassano, Thomas S.E. Maibaum, and Silviya Grigorova                                                                                                                          | 1   |

| Promotion of Formal Approaches in Japanese Software Industry<br>and a Best Practice of FeliCa's Case (Extended Abstract)                                                              | 18  |

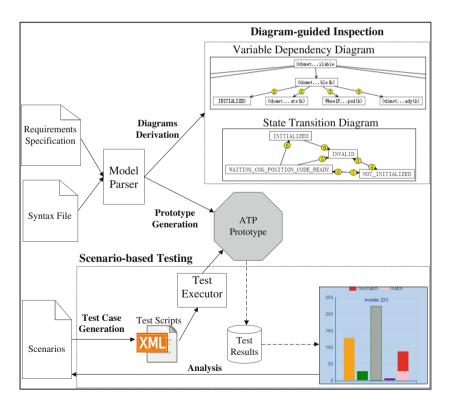

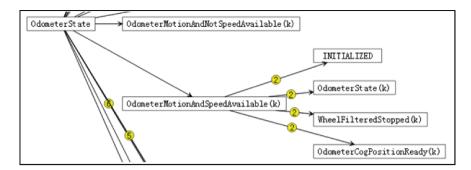

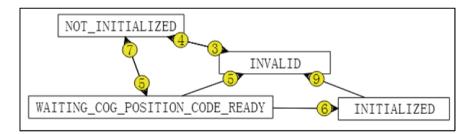

| Automated Requirements Validation for ATP Software via Specification<br>Review and Testing                                                                                            | 26  |

| Automatic Generation of Potentially Pathological Instances<br>for Validating Alloy Models<br><i>Takaya Saeki, Fuyuki Ishikawa, and Shinichi Honiden</i>                               | 41  |

| A General Lattice Model for Merging Symbolic Execution Branches<br>Dominic Scheurer, Reiner Hähnle, and Richard Bubel                                                                 | 57  |

| A Case Study of Formal Approach to Dynamically Reconfigurable Systems<br>by Using Dynamic Linear Hybrid Automata                                                                      | 74  |

| Modelling Hybrid Systems in Event-B and Hybrid Event-B: A Comparison<br>of Water Tanks                                                                                                | 90  |

| A System Substitution Mechanism for Hybrid Systems in Event-B Guillaume Babin, Yamine Aït-Ameur, Neeraj Kumar Singh, and Marc Pantel                                                  | 106 |

| Service Adaptation with Probabilistic Partial Models                                                                                                                                  | 122 |

| A Formal Approach to Identifying Security Vulnerabilities<br>in Telecommunication Networks<br>Linas Laibinis, Elena Troubitsyna, Inna Pereverzeva, Ian Oliver,<br>and Silke Holtmanns | 141 |

| Multi-threaded On-the-Fly Model Generation of Malware<br>with Hash Compaction                                                                                                        | 159 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CPDY: Extending the Dolev-Yao Attacker with Physical-Layer Interactions<br>Marco Rocchetto and Nils Ole Tippenhauer                                                                  | 175 |

| Towards the Formal Verification of Data-Intensive Applications<br>Through Metric Temporal Logic                                                                                      | 193 |

| Proving Event-B Models with Reusable Generic Lemmas<br>Alexei Iliasov, Paulius Stankaitis, and Alexander Romanovsky                                                                  | 210 |

| Formal Availability Analysis Using Theorem Proving                                                                                                                                   | 226 |

| Formal Verification of the <i>rank</i> Algorithm for Succinct Data Structures<br><i>Akira Tanaka, Reynald Affeldt, and Jacques Garrigue</i>                                          | 243 |

| Contextual Trace Refinement for Concurrent Objects: Safety and Progress<br>Brijesh Dongol and Lindsay Groves                                                                         | 261 |

| Local Livelock Analysis of Component-Based Models<br>Madiel S. Conserva Filho, Marcel Vinicius Medeiros Oliveira,<br>Augusto Sampaio, and Ana Cavalcanti                             | 279 |

| Session-Based Compositional Analysis for Actor-Based Languages<br>Using Futures                                                                                                      | 296 |

| An Event-B Development Process for the Distributed BIP Framework<br>Badr Siala, Mohamed Tahar Bhiri, Jean-Paul Bodeveix,<br>and Mamoun Filali                                        | 313 |

| Partial Order Reduction for State/Event Systems<br>Shuanglong Kan, Zhiqiu Huang, and Zhe Chen                                                                                        | 329 |

| Concolic Unbounded-Thread Reachability via Loop Summaries<br>Peizun Liu and Thomas Wahl                                                                                              | 346 |

| Scaling BDD-based Timed Verification with Simulation Reduction<br><i>Truong Khanh Nguyen, Tian Huat Tan, Jun Sun, Jiaying Li, Yang Liu,</i><br><i>Manman Chen, and Jin Song Dong</i> | 363 |

| Contents | XVII |

|----------|------|

| Contento |      |

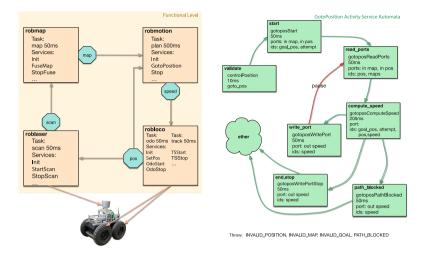

| Model Checking Real-Time Properties on the Functional Layer<br>of Autonomous Robots                                        | 383 |

|----------------------------------------------------------------------------------------------------------------------------|-----|

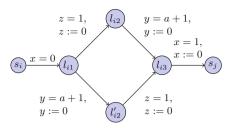

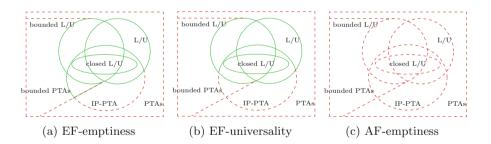

| Decision Problems for Parametric Timed Automata<br>Étienne André, Didier Lime, and Olivier H. Roux                         | 400 |

| Verifying Nested Lock Priority Inheritance in RTEMS with Java Pathfinder<br>Saurabh Gadia, Cyrille Artho, and Gedare Bloom | 417 |

| An SMT-Based Approach to the Formal Analysis of MARTE/CCSL<br>Min Zhang, Frédéric Mallet, and Huibiao Zhu                  | 433 |

| Checking SysML Models for Co-simulation                                                                                    | 450 |

| A CEGAR Scheme for Information Flow Analysis                                                                               | 466 |

| Erratum to: Formal Availability Analysis Using Theorem Proving Waqar Ahmad and Osman Hasan                                 | E1  |

| Author Index                                                                                                               | 485 |

## A (Proto) Logical Basis for the Notion of a Structured Argument in a Safety Case

Valentín Cassano<sup>(⊠)</sup>, Thomas S.E. Maibaum, and Silviya Grigorova

McMaster Centre for Software Certification, McMaster University, Hamilton, Canada {cassanv,grigorsb}@mcmaster.ca, tom@maibaum.org

Abstract. The introduction of safety cases was a step in the right direction in regards to safety assurance. As presently practiced, safety cases aim at making a serious attempt to explicate, and to provide some structure for, the reasoning involved in assuring that a system is safe, generally in terms of so-called structured arguments. However, the fact current notations for expressing these structured arguments have no formal semantics and, at best, are loosely linked to goal structuring ideas and to Toulmin's notion of an argument pattern, is a crucial issue to be addressed. History clearly demonstrates that languages that have no formal semantics are deficient in relation to the requirements of a serious approach to engineering. In other words, one can only go so far with intuition, and certainly not far enough to justify the safety of complex systems, such as Cyber Physical Systems or autonomous cars. By rehearsing Gentzen's program for formalizing mathematical reasoning, his famous Calculus of Natural Deduction, we show how we can begin a program of formalizing safety reasoning by developing a working definition of a structured argument in a safety case and a calculus for safety reasoning.

#### 1 Introduction

Safety cases were introduced into safety practice as a way of making explicit and organizing the justification for a claim that some engineered artifact is safe. Initially, safety cases were cast as natural language documents whose nature and structure were only informally defined, complicating the knowing of what is required of them. The introduction of the idea that a safety case is a structured argument, with references to Toulmin's notion of an argument pattern (see [1]), was a big step forward in providing a more rigorous definition of a safety case. A lot of very useful work has been done in developing these ideas into useful methods and notations and software based tools to support the development of safety cases. To make further progress in transforming safety cases into a properly grounded engineering tool, enabling a systematic and scientific construction and analysis, we need to develop a more formal, logically principled basis for them.

What exactly do we mean by "more logically principled"? Firstly, to date, existing notations and languages for safety cases do not have a rigorous logical semantics. When presented with a safety case, say in GSN or CAE notation (see [2,3]), we have no mean for deciding whether the safety case is syntactically well

© Springer International Publishing AG 2016

K. Ogata et al. (Eds.): ICFEM 2016, LNCS 10009, pp. 1–17, 2016.

DOI: 10.1007/978-3-319-47846-3\_1

formed, never mind whether the reasoning it purports to represent is sound, in the usual sense of properly defined logical systems. Though this state of affairs has persisted for 25 years and people have developed and used safety cases with some success, it is time to take action. The present practice of safety cases seems to be supported by intuition and experience rather than science. This brings with it a number of worrisome difficulties. The complexity of new systems, such as Cyber Physical Systems or autonomous cars, increases as time goes on. How can we expect to deal with this increase in complexity solely based on intuition? We know that, in the end, intuition always fails us when confronted by complexity. Would we have entrusted the lives of astronauts in our missions into space if they were engineered based on intuition and not science? The answer is a clear NO. So it must be with the development of safety cases for complex systems. Lastly, there is the problem of education: How do we teach new safety professionals the necessary rigour required in safety engineering without a scientific basis? Do we appeal to intuition and experience?

The aim of this paper is to set off on the long road to developing a logical calculus in which to incorporate the kind of reasoning involved in safety assurance. Though we will not be presenting such a logical calculus, we do not yet know enough to do so, we will attempt a *working definition* of a structured argument in a safety case in said logical calculus. Our goal is twofold. First, to lay out a foundation for systematization. Second, to set a standard against which progress can be measured. Working definitions are the basis of science and engineering and are an essential tool against which to measure scientific progress. Scientific progress will enable us to systematize, and make more measurable, our approach to making safety case practice more rigorous, if not yet fully formalized. We will happily make changes as we learn more and are able to justify their necessity.

## 2 Preliminary Observations

We will begin by outlining some of our observations about important elements of safety case reasoning. Perhaps the first point to make is that notations for presenting so called structured arguments in safety cases, such as GSN or CAE diagrams (see [2,3]; to save us from having to continually refer to all of them, we will use GSN as a witness of a set of similar notations) do not present arguments as such, they present safety goal decomposition structures, goal G can be achieved via its decomposition into sub-goals  $G_1, \ldots, G_n$ , with some reference to goal decomposition justification. In GSN diagrams, this justification takes the form of *strategies*: They justify why the proposed goal decomposition achieves the goal G, if appropriately combined. This is reminiscent of problem solving by decomposition (see [4]), where solutions to sub-problems can be combined in a prescribed way to solve the original problem, and also of goal structured requirements approaches such as KAOS (see [5]), which applies problem decomposition ideas to requirements definition. However, goal decomposition and structured arguments in safety cases are completely different things: Goal decomposition serves as a way of breaking down the structure of complex goals into more manageable ones, in contrast, safety arguments serve as a way of substantiating the notion that a safety claim follows from

others. For us, notations like GSN fall short at presenting arguments, and what they do well at representing, goal decomposition, while very important, is hindered by not having a properly defined semantics (in comparison, KAOS trees enjoy of a formal semantics, well defined decomposition patterns, etc., making them better suited for engineering use.)

To further complicate things, attempts at supporting safety reasoning by casting it into First Order Logic (FOL) and using FOL automated deduction support (see [6]) are bound to face a great obstacle to overcome: Safety reasoning is not that of FOL (and, more generally, it is quite different from that captured by classical deductive logics). There are several reasons for this, but we will focus only on some of them. Firstly, some of the inference licenses used in safety reasoning are textbook examples of fallacies in FOL (e.g., judgments from expert opinions). Secondly, some of the inference licenses used in safety reasoning are inductive in nature (as in inductive reasoning). An obvious example of the latter occurs in reasoning about test cases: Concluding from a test set where every test case is successful that the corresponding program is correct for all input data, a proper generalization, requires a truly inductive reasoning step. Thirdly, safety case reasoning includes elements of defeasible reasoning, i.e., reasoning in which conclusions are open to revision or annulment (as discussed in the field of non-monotonic logics; see [7]). We make contingent inferences in the absence of certain information. They are contingent because further investigation may invalidate the conclusions drawn from them. Fourthly, safety case reasoning sometimes also uses a form of reasoning called eliminative induction (see [8]). Eliminative induction, first developed by Francis Bacon, and taken up by philosophers such as John Stuart Mill, John Maynard Keynes, Karl Popper, et al., works like this: Suppose that we want to conclude property A and we have identified that A may not be true if one or more properties  $B_1, \ldots, B_n$ are true; if we can prove that no  $B_i$  holds, then we can conclude that A holds. This form of reasoning is in fact an example of a form of probabilistic reasoning that departs from the frequentist based reasoning of probability and is more related to confidence (as in confidence in a scientific theory). Confidence underlies reasoning about scientific theories, legal cases, and in other domains. For example, it is the basis on which semantics for statements in law like "beyond a reasonable doubt" or "on the balance of probabilities" can be defined. In safety reasoning confidence is absolutely necessary for it manifests the conventional wisdom that safety cannot be absolutely guaranteed. Lastly, safety reasoning has a global rather than a localized inductive nature (as in mathematical induction). Defeasible and probabilistic reasoning exhibit this particularity. In defeasible and probabilistic reasoning it is in general not possible to just add another branch to a proof in a soundness-preserving way (see [9]). This has grave consequences for the possibility of devising incremental safety approaches that support the well tried and understood concept of incremental design improvement (see [10]). The above combined lead to the observation that FOL, and, more generally, classical deductive settings, may be unfit for the purposes of safety reasoning.

In summary, to no one's surprise, safety reasoning presents a challenging topic for research with important practical implications. Taking on this challenge, we proceed by outlining and justifying a working definition of a structured argument in a safety case that, in our view, has some chance of having a well defined logical semantics. We illustrate with an example how the ideas may be used in practice.

## 3 Safety Cases, Structured Arguments, and Evidence

The commonly found definition of a safety case reads: "A safety case is a structured argument [...] that provides a compelling, comprehensible, and valid case that a system is safe for a given application in a given operating environment" (see [11]). On the one hand, safety cases are a step in the right direction in regards to safety assurance. They make a serious attempt to explicate, and to provide some structure for, the inference licenses used in guaranteeing that a system is safe. On the other hand, a striking feature of the definition of a safety case just given is its logical vagueness. It is unclear what is to be taken as constituting a structured argument, i.e., what are its defining characteristics, and how is such a structured argument to be assessed in terms of the soundness of the reasoning it involves. We discuss these issues from a logical point of view.

#### 3.1 Gentzen's Calculus of Natural Deduction

To provide some context for discussion, and to fix the terminology we will use in what follows, let us recall some basic facts about Gentzen's Calculus of Natural Deduction for Classical First Order Logic ( $\mathcal{NK}$  for short; see [12–14]). In brief, with his  $\mathcal{NK}$ , Gentzen aimed at developing: "A formalism that reflects as accurately as possible the actual logical reasoning involved in mathematical proofs" (see [12, p. 291]). Gentzen offers as an example of this kind of reasoning:

" $(\exists x \forall y Fxy) \supset (\forall y \exists x Fxy)$ . The argument runs as follows: Suppose there is an x such that for all y Fxy holds. Let a be such an x. Then for all y: Fay. Now let b be an arbitrary object. Then Fab holds. Thus there is an x, viz., a, such that Fxb holds. Since b was arbitrary, our result therefore holds for all objects, i.e., for all y there is an x, such that Fxy holds. This yields our assertion" (see [12, p. 292]).

Gentzen's program consists of the integration of the kind of mathematical proofs carried out in an exactly defined calculus: The  $\mathcal{NK}$ . Towards this end, Gentzen provides precise definitions of so-called symbols, expressions, and figures. Symbols are the alphabet of Classical First Order Logic (FOL for short). Expressions are the language of FOL, i.e., the set of all formulæ defined recursively over the alphabet of FOL. Figures are inference or proof figures. The former are written

$$rac{\mathbf{A}_1,\ldots,\mathbf{A}_n}{\mathbf{B}}$$

where  $\mathbf{A}_1, \ldots, \mathbf{A}_n, \mathbf{B}$  are formulæ. The formulæ  $\mathbf{A}_1, \ldots, \mathbf{A}_n$  appearing in an inference figure such as the one given above are called upper formulæ and the formula  $\mathbf{B}$  is called a lower formula. Regarding inference figures Gentzen explains: "We shall have inference figures and they will be stated for each calculus as they arise" (see [12, p. 291]). The permissible inference figures which make up the  $\mathcal{NK}$  correspond to the well-known rules of introduction and elimination of the logical connectives of the alphabet of FOL and the law of the excluded middle (see [12, pp. 292–295]). Gentzen states these permissible inference figures via inference figure schemata, such as

$$\frac{\mathbf{[A]}}{\mathbf{A} \supset \mathbf{B}} \supset -I$$

An inference figure schemata is to be understood as: The permissible inference figure obtains from the inference figure schemata by instantiating the syntactical variables for formulæ by corresponding formulæ. Proof figures, also called derivations, consist of a number of formulæ which are combined to form inference figure; each formula (with the exception of exactly one: the *endformula*) is an upper formula of at least one inference figure; and the system of inference figures is non-circular, i.e., there is in the derivation no cycle (no series whose last member is again succeeded by its first member) of formulæ of which each upper formula of an inference figure has the lower formula as the next figure one in the series" (see [12, p. 291]). The following derivation illustrates the result of incorporating the mathematical proof given above in  $\mathcal{NK}$ .

$$\begin{array}{c} \frac{[\forall yFay]^1}{Fab} \forall -E \\ \frac{Fab}{\exists xFxb} \exists -I \\ \forall y\exists xFxy \\ \forall y\exists xFxy \\ \hline \forall y\exists xFxy \\ \exists x\forall yFxy) \supset (\forall y\exists xFxy) \\ \neg -I_2 \end{array}$$

(Numbering annotations above are used to identify instances of permissible inference figures and discharged assumptions.) Introducing some further terminology that we will use later on, Gentzen calls the formulæ of a derivation that are not lower formulæ of an inference figure, initial; the formulæ of a derivation, D-formulæ; the inference figures of a derivation, D-inferences; and a branch in a derivation, a series of D-formulae whose first formula is an initial one and whose last formula is the endformula, and of which each formula but the last is an upper formula of a D-inference figure whose lower formula is next in the branch.

#### 3.2 Structured Arguments in Safety Cases

Why recall some basic facts about  $\mathcal{NK}$ ? First, because, indirectly via the integration of mathematical proofs into  $\mathcal{NK}$ , Gentzen provides a precise definition

of what is a mathematical proof, enabling an analysis of its scope and limits. Second, because we consider that the notion of a mathematical proof stands somewhat in analogy with that of a structured argument in a safety case: While the former aims at capturing the kind of reasoning involved in mathematics, the latter aims at capturing the kind of reasoning involved in safety assurance. Third, because we consider that the notion of a structured argument in a safety case should be given a definition akin to the one that Gentzen provides for the notion of a mathematical proof: Without such a definition it is impossible to judge whether a proposed structured argument in a safety case is indeed such. Fourth, because we consider that if logic, logical methods, and their history have taught us anything at all, it is that only through the provision of precise definitions and their analyses can we avoid fallacious reasoning steps: Two of the most important results about Gentzen's definition of a derivation are the Soundness and Completeness Theorems (see [14]).

As an aside in light of the previous paragraph, we offer some clarifications to avoid any subsequent confusion. We are not saying that the kind of reasoning involved in mathematics and the kind of reasoning involved in safety assurance are one and the same. There are most definitely some points of departure between the two, some of which we referred to above and will further make clear below. Moreover, we are not saying that without a definition of a structured argument in a safety case that stands on grounds analogous to Gentzen's definition of a derivation, safety reasoning is vacuous. Though with some reservations, even in the absence of such a definition of a structured argument in a safety case, we see no major reason preempting logical progress in safety reasoning. (After all, it is not as if mathematical reasoning was impaired before Gentzen's definition of derivation.) Lastly, we are not saying that the aforementioned definition of a structured argument in a safety case shall be given from the outset. This would be a clear impossibility given the current state of the art of safety reasoning. Instead, our remarks are oriented towards the formulation of a working definition of a structured argument in a safety case that is (i) suitable for capturing as accurately as possible the actual logical reasoning involved in safety assurance, and (ii) amenable for the logical analyses that are needed to establish the well-formedness and the soundness of the inference licenses to be used in safety assurance. It is our hope that by discussing and refining such a working definition we can establish a strong logical foundation on which to improve safety reasoning.

How to cope with the issues mentioned above? Similarly to Gentzen's aim of incorporating mathematical proofs into a well defined calculus, what we have in mind is the integration of structured arguments in safety cases, safety arguments for short, in an exactly defined calculus, which we refer to as SK. We consider this integration provides the sought after definition of a safety argument. Thus, we make precise first the concept of a s-derivation. Reminiscent of Gentzen's derivations, s-derivations consist of a number of s-formulæ which are combined to form s-inference figures in a way such that: Each s-formula is a lower s-formula of at most one s-inference figure; each s-formula (with the exception of exactly

one: the s-endformula) is an upper s-formula of at least one s-inference figure; and the system of s-inference figures is non-circular. We write a s-inference figure

$$rac{\mathbf{A}_1,\ldots,\mathbf{A}_n}{\mathbf{B}}\left<\mathbf{R}\right>$$

where  $\mathbf{A}_1, \ldots, \mathbf{A}_n, \mathbf{B}, \mathbf{R}$  are s-formulæ. In a s-inference step figure the s-formula  $\mathbf{R}$  is optional. Following Gentzen's terminology, for a s-inference figure such as the one given above, we call  $\mathbf{A}_1, \ldots, \mathbf{A}_n$  upper s-formulæ and  $\mathbf{B}$  lower s-formula.  $\mathbf{R}$  occupies a special place in s-derivations. We will return to it later on. We call the s-formulæ participating in a s-derivation S-formulæ and the s-inference figures participating in a s-derivation S-inference figures. Moreover, we call the s-formulæ of a s-derivation that are not lower formulæ of a S-inference figure initial s-formulæ. By way of example, the figure below illustrates a s-derivation

$$\mathbf{I}_{1} \underbrace{\frac{\overset{\mathbf{I}_{2},\mathbf{I}_{3}}{\mathbf{S}_{1}}\left\langle \mathbf{R}_{1}\right\rangle \quad \mathbf{I}_{4}}{\mathbf{S}_{3}} \left\langle \mathbf{R}_{3}\right\rangle \quad \frac{\mathbf{I}_{5} \quad \overset{\mathbf{I}_{6}}{\mathbf{S}_{2}} \left\langle \mathbf{R}_{2}\right\rangle }{\mathbf{E}}$$

where  $\mathbf{I}_i, \mathbf{S}_j, \mathbf{R}_k, \mathbf{E}$  are the S-formulæ of the s-derivation,  $\mathbf{I}_i$  are its initial s-formulæ,  $\mathbf{E}$  is its s-endformula, and

$$\frac{\mathbf{I}_2,\mathbf{I}_3}{\mathbf{S}_1}\ \langle \mathbf{R}_1\rangle,\quad \frac{\mathbf{I}_6}{\mathbf{S}_2}\ \langle \mathbf{R}_2\rangle,\quad \frac{\mathbf{S}_1,\mathbf{I}_4}{\mathbf{S}_3}\ \langle \mathbf{R}_3\rangle,\quad \frac{\mathbf{I}_5,\mathbf{S}_2}{\mathbf{S}_4},\quad \frac{\mathbf{I}_1,\mathbf{S}_3,\mathbf{S}_4}{\mathbf{E}}\ \langle \mathbf{R}_4\rangle$$

are its S-inference figures. When there is no place for ambiguities, we write a s-derivation with initial s-formulæ  $\mathbf{I}_1, \ldots, \mathbf{I}_n$  and s-endformula  $\mathbf{E}, \mathbf{I}_1, \ldots, \mathbf{I}_n \mathscr{D} \mathbf{E}$ . The definition of  $\mathcal{SK}$  concludes with the definition of the language of s-formulæ and the formulation of the permitted s-inference figures via s-inference figure schemata. We envision the language of s-formulæ as the  $\mathcal{SK}$  counterpart of the claims involved in safety arguments, safety claims for short, and the permitted s-inference figures used in the formulation of safety arguments. Their precise formulation is, however, an open research question and part of what makes the definition of a safety argument, via its integration into an exactly defined calculus, a working definition.

#### 3.3 Some Comments on the Logical Basis of Safety Arguments

A significant part of our working definition of a safety argument needs to be completed. We need to provide a formal definition of s-formulæ; we need to formulate the s-inference figure schemata for the permissible s-inference figures of  $S\mathcal{K}$ ; and, more importantly, we need to integrate a basic stock of safety arguments into  $S\mathcal{K}$ . Three important reasons for use of 'Proto' in the main title. Nevertheless, even at this early stage, the initial definition of a s-derivation allows us to discuss technically certain important issues regarding safety reasoning. **Regarding s-Formulæ.** To provide some context for discussion: It is noted by Gentzen in [12] that in the formalization of mathematics, to the concept of 'object', 'function', 'predicate', 'variable', 'proposition', and so on, there corresponds certain symbols or combinations thereof. What Gentzen then assumes implicitly is the translation of some ordinary language of mathematics into a formal language. In Gentzen's world, this formal language is that of FOL: The set of all formulæ defined in the standard recursive way over an alphabet of so-called logical and non-logical symbols; logical symbols are symbols for the logical operators of universal truth  $(\top)$ , universal falsehood  $(\bot)$ , conjunction  $(\wedge)$ , disjunction  $(\vee)$ , material implication  $(\supset)$ , and the universal  $(\forall)$  and existential  $(\exists)$  quantifiers; non-logical symbols are symbols for variables, constants, predicates, and functions (with their corresponding arity). There is, in Gentzen's world, no danger in assuming the translation of statements in the ordinary language of mathematics into that of FOL. First, because, to a large extent, the language of FOL has been designed having in mind the ordinary language of mathematics. Second, because mathematical statements are rigorously precise and unambiguous. For instance, no one will doubt that to the ordinary statement of mathematics 'There is no natural number whose successor is zero' there corresponds the formula  $\forall n S(n) \neq 0$  in the standardly defined way.

More generally, the faithfulness of the translation of an ordinary language. such as English, into a formal language, such as that of FOL, depends on a systematic understanding of the formal language and on the suitability of such a formal language for the problem at hand. Is there a formal language in which to provide a precise definition for a s-formula that caters for a faithful translation of safety claims formulated, say, in plain English? Keeping in mind that what we are after is the integration of safety arguments into a precisely defined calculus, this question is of great relevance. The answer, however, is nontrivial. First, because it is not at all clear how to faithfully translate logical connectives in an ordinary language, such as English, into a formal language. Second, because a quick perusal of some safety claims reveals a heavy use of modal logical connectives ('acceptably', 'sufficiently', 'adequately') in combination with quantifiers of a restricted nature ('All identified hazards'). It is well known in classical logical studies that modal logical connectives and logical quantifiers are not easily dealt with. Following from these observations, perhaps Carnap's distinction between the observable and the theoretical in the language of science (see [15, ch. 23]) provides a better foundation than classical logical languages for formally defining the concept of a s-formula. But this thesis needs of further investigation.

Why should we even bother in giving a formal definition of s-formulæ? First, because formal languages are often unambiguous, easier to provide a clear semantics for, and, ultimately, more amenable to analyses and tool support. Second, because the unrestricted use of an ordinary language, such as English, is likely to be prone to paradoxes of self-reference: 'This sentence has five words' or the more hideous 'This sentence is false'. Regarding problems of self-reference, we consider that a version of a problem of this kind is already present in safety claims. To explain this consideration, let us recall some basic facts of Hoare's

Calculus (see [16]). Hoare's Calculus is a formalism enabling us to prove deductively that a program is correct. There is, however, no expression of the formal language of Hoare's Calculus which captures the expression 'The program S is correct'. The formal language of Hoare's Calculus consists of triples  $\{P\} \in \{Q\}$ capturing expressions of the form: 'If (the precondition) P is true before the initiation of (the program) S, then, (the postcondition) Q will be true upon the completion of S'. 'The program S is correct' is a statement which is formulated outside of Hoare's Calculus and that corresponds to the concept of a derivation which has the triple  $\{P\}$  S  $\{Q\}$  as an endformula inside the calculus. The formulation of the claim 'The program S is correct' inside Hoare's Calculus yields a calculus which can assert its own provability. This gives rise to all sorts of logical problems. Here is our observation: Though programs and systems are distinct entities, and so is correctness and safety and the kind of reasoning they involve, we consider that in the same way that the correctness of a program S is to be established with respect to a property Q about S under the proviso P, the safety of a system S is to be established with respect to a property E about S under certain provisos  $I_i$ . A safety argument would then be in place to structure the inference licenses which would lead us from  $\mathbf{I}_i$  to **E**. This understood, a claim such as 'The system S is (acceptably/sufficiently/adequately) safe' is about the calculus for safety reasoning, our  $\mathcal{SK}$ , and, as such, it should not belong to the calculus itself. This is precisely the kind of problems we wish to avoid. Fallacious reasoning begins with the use of formulæ that are, from the point of view of the candidate calculus, already logically problematic.

In summary, we should exercise great care in the formulation of safety claims, and what they are about, to avoid the kind of problems mentioned above, or others of a similarly problematic logical nature. To being with, we may restrict the formulation of safety claims to fragments of ordinary languages, such as English, that are expressive enough to capture the safety claims we need, but that maintain a reasonable degree of logical tractability. In doing so, we may be able to provide a precise definition of the language of s-formulæ, and a corresponding formal semantics, which caters for a faithful translation of safety claims.

**Regarding s-Inference Figures.** The definition of a s-inference figure given in Sect. 3.2 provides a necessary level of technicality for putting in context an important topic present in notations in which to formulate safety arguments: The appeal to Toulmin's argument patterns (see [1]) in the formulation of a safety argument. We begin by setting up the context in which we discuss our ideas. One of the research questions posited by Toumin in [1] is: How should we lay an argument out, if we want to show the sources of its validity? In answering this question, Toulmin identifies the following elements: claim (C), data (D), warrant (W), qualifier (Q), rebuttal (R), and backing (B). Resorting to this basic stock of concepts, Toulmin lays out his famous argument pattern in the following "form"

$$\begin{array}{c|c} D & & & \\ & & & \\ \hline \\ On \ account \ of \ B - Since \ W & Unless \ R \end{array}$$

As is explained in [17], Toulmin articulates his argument patterns in the context of justifying an assertion in response to a challenge. The challenge starts with the assertion of a claim (C), of which we may be asked: What have we got to go on? To which we would answer with the data (D). Following the acceptance of D, we may be asked: How do you get there? (How do we get from D to C?) Our answer to this second question would be the warrant (W). The warrant is, thus, what allows us to infer the claim from the data. Warrants may be qualified by modalities (Q) such as 'probably', 'generally', 'necessarily, or 'presumably'. If the warrant is defeasible, i.e., open to revision or annulment, then, we ought to state the conditions of rebuttal (R). Finally, we may be asked for a justification of the warrant itself. Our answer to this last question would be the backing (B).

It is easy to see that, though with some restrictions, our formulation of a s-inference figure borrows elements from Toulmin's argument patterns and articulates them in Gentzen's terminology. More precisely, incorporating the modalities (Q) into the logical connectives of the language of s-formulæ, an inference figure

$$rac{\mathbf{A}_1,\ldots,\mathbf{A}_n}{\mathbf{B}}\,\left<\mathbf{R}\right>$$

may be viewed as standing in analogy with Toulmin's triple of claim (C), data (D), and rebuttal (R) in the obvious way, i.e., D stands in analogy with the upper s-formulæ  $\mathbf{A}_1, \ldots, \mathbf{A}_n$ , C stands in analogy with the lower s-formula **B**, and R stands in analogy with the s-formula  $\mathbf{R}$ ; for the latter reason, we also call the s-formula **R** a rebuttal. Rebuttals occupy a special place in s-inference figures and we will return to them immediately below. Moreover, Toulmin's notion of a warrant may be viewed as standing in analogy with a s-inference figure scheme. (If viewed in this light, [17] provides some insight into what a proper formulation of a s-inference figure scheme may look like.) Lastly, Toulmin's notion of a backing may be viewed as standing in analogy with a soundness statement about a s-inference figure scheme. The restrictions that we refer to are linguistic and logical constraints on the kind of rebuttals allowed. To provide some context for discussion: According to Toulmin, rebuttals indicate circumstances in which the general authority of the warrant would have to be set aside (see [1, p. 94]). In this respect, there are, at least, two possible ways in which Toulmin's view of a rebuttal may be understood: (i) As indicating a set of circumstances in which the *claim* licensed by the warrant would have to be set aside; (ii) As indicating a set of circumstances in which the *warrant itself* would have to be set aside. The analogy between a warrant and a s-inference figure scheme allows for the following clarification: (i) Implies that an instance of the s-inference scheme cannot be used in a particular s-derivation; (ii) Implies that the s-inference scheme cannot be part of the s-inference figure schemata defining our proposed calculus,  $\mathcal{SK}$ . If understood in this sense, (i) speaks to the defeasible aspect of s-derivations, a point that we will return to later on, whereas (ii) results in a denial of the proposed calculus (the so-called paradoxes of deontic logic present examples of the second kind of rebuttals; see [18]). In defining rebuttals as s-formulæ, and under the proviso that the language for s-formulæ cannot refer to properties of the  $\mathcal{SK}$ , we preempt the formulation of rebutals of the second kind. In principle,

such a restriction is not necessary and could be lifted. However, at this point, it presents a firmer basis on which to start building a calculus for safety reasoning.

The relation between Toulmin's argument patterns and s-inference figures places the work of Toulmin in the context of safety reasoning: Toulmin's argument patterns present an interesting framework in which to formulate what s-inference figures, or s-figure schemata, may look like. However, in and of themselves, Toulmin's argument patterns are not s-inference figures nor s-figure schemata. This means that Toulmin's argument patterns do not define, at least not obviously, a calculus for safety reasoning, our sought after SK. Such a calculus, which we view as a fundamental tool for analyzing the logical well-formedness of safety arguments, is only defined by the provision and justification of a sensible set of s-inference figures via s-inference figure schemata. In other words, the appeal to Toumin's argument patterns in the context of safety reasoning is rather limited, it serves as a way of showing the sources of validity of a safety argument, but it does not propose a way of assessing the validity of said sources.

**Regarding s-Derivations.** The following two questions immediately arise: (i) Are s-derivations suitable for formalizing the kind of reasoning involved in safety assurance? (ii) Do they support the logical analyses needed to establish the well-formedness and soundness of the inference licenses used in said kind of reasoning?

Our answer to question (i) is, at this point, mostly an expression of desire. Evidently, we consider that s-derivations present a suitable framework for the formalization of safety arguments and the kind of reasoning involved in safety assurance. This view is partly justified by safety arguments expressed as GSN or CAE diagrams. However, whether this view is fully justified is certainly open for debate, in particular, because we have been unable to produce an example of the incorporation of a safety argument as a s-derivation. This inability is (a) partly due to our own limitations and to the logical rigour that we intend to put in place in the integration of a safety argument into a s-derivation, we refer back to our discussion on the definition of s-formulæ and s-inference figures, and to the upcoming discussion on s-derivations, and (b) partly due to the logical havoc reigning over the handful of examples of safety arguments that we have taken a close look at, a situation to reverse and that we expect to shed some light on.

Our answer to question (ii) is, even at this point, more satisfactory, in particular, in relation to the well-formedness of a s-derivation  $\mathbf{I}_1, \ldots, \mathbf{I}_n \mathscr{D} \mathbf{E}$ . More precisely, given a s-derivation  $\mathbf{I}_1, \ldots, \mathbf{I}_n \mathscr{D} \mathbf{E}$ , we call another s-derivation  $\mathbf{I}_i, \ldots, \mathbf{I}_j \mathscr{D} \mathbf{R}$ , for  $\mathbf{I}_i, \ldots, \mathbf{I}_j \mathscr{D} \mathbf{E}$ , a subset of  $\mathbf{I}_1, \ldots, \mathbf{I}_n$  and  $\mathbf{R}$  a rebuttal of one of the S-inference figures of  $\mathbf{I}_1, \ldots, \mathbf{I}_n \mathscr{D} \mathbf{E}$ , a rebutting s-derivation for  $\mathbf{I}_1, \ldots, \mathbf{I}_n \mathscr{D} \mathbf{E}$ . A s-derivation is internally coherent in the absence of a rebutting s-derivation for it. (Note that we are calling a s-derivation coherent in the absence of a rebutting s-derivation for it and not in the presence of a proof that such a rebutting s-derivation does not exist; the latter is far more difficult to establish.) It is obvious that s-derivations that are internally incoherent are logically ill-formed. Moreover, the notion of internal coherence speaks to the defeasible aspects of a s-derivation, i.e., the conditions under which a s-derivation is open to revision or annulment. By way of example, consider the following two s-derivations

$$rac{\mathbf{I}_1,\mathbf{I}_2}{\mathbf{S}_1} egin{array}{ccc} \langle \mathbf{R}_1

angle & \mathbf{I}_3 \ \mathbf{E} & \langle \mathbf{R}_2

angle & & rac{\mathbf{I}_1}{\mathbf{R}_2} egin{array}{ccc} \langle \mathbf{R}_3

angle & & rac{\mathbf{I}_1}{\mathbf{R}_2} \end{array}$$

If taken on its own accord,  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \ \mathscr{D} \mathbf{E}$  is coherent. However,  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \ \mathscr{D} \mathbf{E}$ is incoherent when paired up with  $I_1, I_3 \mathscr{D} \mathbf{R}_2$  (for the reason that  $I_1, I_3 \mathscr{D} \mathbf{R}_2$ establishes the rebuttal of one of the S-inference figures of  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \mathscr{D} \mathbf{E}$ , i.e., the S-inference figure which has  $\mathbf{R}_2$  as its rebuttal). In the latter scenario, the use of the S-inference figure of  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \mathcal{D} \mathbf{E}$  which has  $\mathbf{R}_2$  as its rebuttal condition is locally unsound in  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \mathscr{D} \mathbf{E}$ ; "locally unsound" for there may be other situations in which the use of such an inference figure is perfectly permissible, e.g., situations in which there is no s-derivation with  $\mathbf{R}_2$  as its s-endformula. This calls for a revision of  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3 \mathcal{D} \mathbf{E}$  as a whole, possibly establishing its annulment. Why possibly and not necessarily? Because, even in the presence of  $\mathbf{I}_1, \mathbf{I}_3$   $\mathscr{D}$   $\mathbf{R}_2$ , we may still be able to "repair"  $\mathbf{I}_1, \mathbf{I}_2, \mathbf{I}_3$   $\mathscr{D}$   $\mathbf{E}$  by resorting to a s-inference figure which does not have  $\mathbf{R}_2$  as a rebuttal. The discussion on the internal coherence of a s-derivation is important, not only because it clearly sets apart safety reasoning from mathematical reasoning but also, because it has a bearing on compositional safety argumentation: The composition of internally coherent s-derivations to form a larger s-derivation (a composition reminiscent of Gentzen's use of the cut rule) may result in a s-derivation that is incoherent.

#### 4 Illustrating Some of Our Points

We proceed to illustrate some of the points that we made above by elaborating on some basic elements of a safety argument intended to make a case that a warning light is lit under certain conditions. Our emphasis will be placed on laying out explicitly the underlying logical structure that such a safety argument may have.

For the safety argument under consideration, we list the following representative elements. Firstly, the safety claim that the safety argument makes a case for: (E) 'Under certain critical conditions, the warning light is lit'. The critical conditions that E refers to will play no role in our example; we will refer to them as C. Moreover, we will refer to the claim 'The warning light is lit' as W. Secondly, an explicit inference license: (L) 'E follows from W being the case, assuming that C is the case'; since E is of a conditional nature ('Under ..., ...'), we consider an inference license involving a hypothetical reasoning step. Thirdly, and completing the safety argument under consideration, a sub-safety argument making a case for W being the case assuming that C is the case. We consider this sub-safety argument to be developed from properties of an action t (or a combination thereof) described in the design and the implementation of the system that turns on the warning light. These properties may be: (T) 'The execution of t lights the warning light', together with (Done(t)) 't is executed'. We are now in a position to make explicit part of the logical structure of the safety argument under consideration via a s-derivation. To be noted first is that the language of s-formulæ will need to cater for the faithful translation of E (and consequently C and W), T (and consequently t), and Done(t). Let us suppose that in the language of s-formulæ, E is denoted by a s-formula  $\mathbf{C} \rightsquigarrow \mathbf{W}$ (provided that C is denoted by a s-formula  $\mathbf{C}$ , W is denoted by a s-formula  $\mathbf{W}$ , and  $\rightsquigarrow$  captures the meaning of the logical operator corresponding to the conditional in E); T is denoted by a s-formula  $\langle t \rangle \mathbf{W}$  (provided that t is denoted by t', and  $\langle \cdot \rangle$  captures the meaning of the logical modality in T); and Done(t)is denoted by Done(t). On this basis, we may formulate  $\mathbb{L}$  as a s-inference figure

$$\frac{\begin{bmatrix} \mathbf{C} \end{bmatrix}}{\mathbf{C} \rightsquigarrow \mathbf{W}} \rightsquigarrow -I$$

(As usual, square brackets indicate discharged assumptions.) The complete safety argument under consideration may be incorporated into a s-derivation such as

$$\begin{split} [\mathbf{C}]^1, \langle \mathsf{t} \rangle \mathbf{W}, \mathsf{Done}(\mathsf{t}) \\ \mathcal{D} \\ \mathbf{W} \\ \mathbf{W} \\ \mathbf{C} \rightsquigarrow \mathbf{W} \\ \rightsquigarrow -I_1 \end{split}$$

where  $[\mathbf{C}], \langle t \rangle \mathbf{W}, \mathsf{Done}(t) \mathcal{D} \mathbf{W}$  is the s-derivation corresponding to the sub-safety argument referred to above.

#### 5 Discussion

There are some points worth noting about the difference in nature between the s-derivation that we presented in the previous section,  $\langle t \rangle W$ , Done(t)  $\mathcal{D} \mathbf{C} \rightsquigarrow \mathbf{W}$ , and the formulation of a safety arguments typically presented, say, as GSN diagrams. Firstly, there is a clear distinction between the formulation of the safety claim E from which  $\mathbf{C} \rightsquigarrow \mathbf{W}$  obtains and the commonly found formulation of safety claims that play the same role. E is a specific property of the system that turns on a warning light, the warning light being lit under certain conditions, and  $\mathbf{C} \rightsquigarrow \mathbf{W}$  is a s-formula. The relation between E, and/or  $\mathbf{C} \rightsquigarrow \mathbf{W}$ , and 'The system is (acceptably/adequately/sufficiently) safe', where 'system' refers to the system that turns on the warning light, is one of design intent: Presumably, the warning light being lit under certain critical conditions issues a warning so that an agent can take whatever appropriate actions are necessary, serving in this way as a safety mechanism, thus contributing to whatever conception of safety the designer had in mind. Now, as commented on in Sect. 3.3,  $\mathbf{C} \rightsquigarrow \mathbf{W}$  is internal to the calculus of safety argumentation (compare program correctness), our sought after  $\mathcal{SK}$ , whereas 'The system is safe' is about the calculus, i.e., it corresponds to a claim about what  $\langle t \rangle W$ , Done(t)  $\mathcal{D} \mathbf{C} \rightsquigarrow W$  represents to the designer, i.e., there has to be an agreement that 'The system is safe' can be made on the basis of  $\mathbf{C} \rightsquigarrow \mathbf{W}$  and the s-derivation. Secondly, there is a clear cut distinction between

E and  $\mathbb{L}$ . Again, E is a property of the system that turns on the warning light. Instead,  $\mathbb{L}$  is a consequence conducive statement about E seen as a safety claim, i.e., as part of a safety argument, and the safety claims from which it follows. This distinction is of utmost importance for the logical analysis of the soundness of inference licenses and s-inference figures. There is one last distinction between inference licenses such as  $\mathbb{L}$  and the kind of strategies present in GSN diagrams that is worth noting: GSN strategies have no concept analogous to that of discharging an assumption. Unless other measures are taken, this limitation severely restricts most forms of conditional reasoning in the kind of Gentzen-like logical calculi that we have considered here, making it too severe a restriction.

There are also some important elements worth noting about the formulation of  $\langle t \rangle W$ , Done(t)  $\mathcal{D} \mathbf{C} \rightsquigarrow \mathbf{W}$ , in particular, in relation to the standard formalization of the logical concepts it involves. Firstly: Are we to interpret  $\rightarrow$  as the symbol for material implication? Thought it is known that material implication does not cope well with ordinary understandings of conditional statements, if we were to answer the question in the negative, say by interpreting  $\rightarrow$  as relevant or strict implication, then, we need to provide clarification as to how the s-inference figure corresponding to the introduction of  $\rightsquigarrow$  differs from  $\supset -I$  (see [13]). Secondly, the standard interpretation of  $\langle t \rangle W$  reads as: There is a possible execution of t which results in W being the case. Such an interpretation of  $\langle t \rangle W$  is seemingly appropriate for capturing T, i.e., 'The execution of t lights the warning light'. After all, it is not difficult to envision scenarios where t may be executed and yet the warning light might not be lit, e.g., scenarios where not all things went according to plan. At the same time, the standard reading of  $\langle t \rangle W$ preempts us from concluding  $\mathbf{W}$  from the assumption that  $\mathsf{Done}(\mathsf{t})$  is the case, for we would have to ensure that the execution of t referred to by Done(t) is one which lead us to  $\mathbf{W}$  being the case and no other – a nontrivial matter. This said, there may be a formulation of a s-derivation which allows us to conclude W from  $\langle t \rangle$ W and Done(t) via appropriate s-inference figure schemata which include "scenarios where not all things went according to plan" as rebuttals. In such a s-derivation, the s-endformula **W** will be open to revision and potential annulment if things do not go according to plan. Altogether, the scheme of things just discussed is not a matter of logical pedantry, but rather they are important issues, and the leading causes of fallacies in safety reasoning, that are being brought into the foreground by the use of appropriate logical machinery.

There is a final issue to discuss: The use of evidence in s-derivations as a way of grounding initial s-formulæ. To provide some context for discussion, let us first recall some basic facts about the role of initial formulæ in  $\mathcal{NK}$ . According to Gentzen, a distinguishing feature of  $\mathcal{NK}$  is that derivations start from assumptions, some of which may subsequently be discharged, to which logical deductions are then applied (see [12, p. 292]). These initial assumptions are the initial formulæ of a derivation. An important thing to notice about Gentzen's treatment of initial formulæ is their assumptive nature; they are, in a sense, "true" in themselves, given *deus ex machina*, and, as such, are accepted as the basis on which the derivation is built. In contrast, in safety reasoning, it is typically proposed that the safety claims from which a safety argument is built need to be provided with a rationale which justifies their postulation. This means that the initial s-formulæ in s-derivations lack the assumptive nature enjoyed by Gentzen's view of initial formulæ in derivations. Providing a rationale for justifying the postulation of a safety claim is reminiscent of the notion of justified belief in studies in epistemology or scientific explanation. It is at this point where evidence makes an appearance. Bringing in the concept of evidence in safety reasoning is a topic for research in its own right. In this respect, without elaborating at length, we cannot do more than offer some pointers to some of the literature which we consider provides a proper context for discussing the use of evidence in safety cases, and some of the challenges that this use presents (see classic texts such as [15, 19], or more recent works such as [20-22]).

#### 6 Conclusions

The present practice of safety cases, recorded in some notation, is the result of over 25 years of work. The object-oriented (OO) community and the Unified Modeling Language (UML) underwent a similar situation over a similar period. In both cases it has been pointed out that simply providing a loose syntax is not enough. Engineering disciplines rely on scientific theories and mathematics to enable precision in design and analyses to support sound design decisions. This was acknowledged by the OO community, who started incorporating mathematical precision into its notations some years ago, not without its hurdles and sometimes against the protests of the notation's inventors! The safety case community is slowly awakening to this; pushed by a need for proper engineering guarantees about safety, especially due to the increasing complexity of safety critical systems, and by the recognition that relying on the informal understanding and intuition of individuals, no matter how experienced, is not only unscientific, but a historic invitation to disaster.

In this paper, we have tried to take the first steps towards developing a proper scientific and logical basis for safety case understanding and construction: A working definition of a safety case via its incorporation in a precisely defined calculus. We start from two pillars. The first pillar, in line with other researchers in the area (see [23]), is the observation that assurance case reasoning is more akin to the argument based reasoning ideas of Toulmin than to the conventional deductive logic reasoning well known to mathematicians and software engineers (or computer scientists). This form of reasoning is already (more or less) well known in domains such as legal reasoning and scientific reasoning/explanation. The second pillar is Gentzen's program for formalizing mathematical reasoning in terms of a logical language, inference rules to support reasoning steps, and proofs to capture the "informal" notion of argument used by mathematicians. One can debate about the adequacy of Gentzen's formalization, but if one accepts it, and most mathematicians have, then one can make remarkable progress in analyzing mathematical reasoning, including developing automated tools such as theorem provers and model checkers. Though safety reasoning is very different in character from mathematical reasoning, we can use an analogous approach to that of Gentzen; in particular, we can focus on the same ingredients, i.e., a formalized logical language for expressing safety claims, a well defined notion of inference step (perhaps one based on Toulmin's idea of an argument step), a well defined notion of derivation (capturing the notion of safety argument), and a new ingredient, grounded proofs, i.e., the idea that all initial formulæ in a derivation cannot be taken for granted, i.e., gaining a proper understanding of the notion of evidence. We hope to have taken some steps in this direction.

## References

- 1. Toulmin, S.: The Uses of Argument. Cambridge University Press, Cambridge (2003)

- 2. The GSN Working Group: Goal Structuring Notation. Version 1, November 2011

- 3. Adelard: Claim, Argument, Evidence Notation. Accessed 25 Jan 2016

- 4. Pólya, G.: How to Solve It, 2nd edn. Princeton University Press, Princeton (2004)

- van Lamsweerde, A.: Requirements Engineering: From System Goals to UML Models to Software Specifications. Wiley, Hoboken (2009)

- Rushby, J.: Logic and epistemology in safety cases. In: Bitsch, F., Guiochet, J., Kaâniche, M. (eds.) SAFECOMP 2013. LNCS, vol. 8153, pp. 1–7. Springer, Heidelberg (2013). doi:10.1007/978-3-642-40793-2\_1

- Bochman, A.: Non-monotonic reasoning. In: Gabbay, D., Woods, J. (eds.) Handbook of the History of Logic: The Many Valued and Nonmonotonic Turn in Logic, vol. 8, pp. 555–632. North-Holland, Amsterdam (2007)

- Goodenough, J., Weinstock, C., Klein, A.: Eliminative induction: a basis for arguing system confidence. In: 35th International Conference on Software Engineering (ICSE 2013), pp. 1161–1164 (2013)

- Bloomfield, R., Littlewood, B.: Multi-legged arguments: the impact of diversity upon confidence in dependability arguments. In: International Conference on Dependable Systems and Networks (DSN 2003), pp. 25–34 (2003)

- 10. Vincenti, W.: What Engineers Know and How They Know It: Analytical Studies from Aeronautical History. Johns Hopkins University Press, Baltimore (1993)

- 11. UK Ministry of Defense: Defence standard 00–56 issue 4: safety management requirements for defence systems (2007)

- Gentzen, G.: Investigations into logical deduction. Am. Philos. Q. 1(4), 288–306 (1964)

- 13. Prawitz, D.: Natural Deduction: A Proof-theoretical Study. AWE (1965)

- 14. van Dalen, D.: Logic and Structure, 5th edn. Springer, Heidelberg (2013)

- Carnap, R.: An Introduction to the Philosophy of Science, 5th edn. Dover, Mineola (1966)

- Hoare, C.: An axiomatic basis for computer programming. Commun. ACM 12(10), 576–580 (1969)

- Hitchcock, D.: Toulmin's warrants. In: van Eemeren, F., et al. (eds.) Anyone Who Has a View: Theoretical Contributions to the Study of Argumentation, vol. 8, pp. 69–82. Springer, Heidelberg (2003)

- Åqvist, L.: Deontic logic. In: Gabbay, D., Guenthner, F. (eds.) Handbook of Philosophical Logic, vol. 8, 2nd edn, pp. 1–12. Springer, Heidelberg (2002)

- Hempel, C.: Philosophy of Natural Science. Prentice Hall, Upper Saddle River (1966)

- 20. Achinstein, P.: The Book of Evidence. Oxford University Press, Oxford (2001)

- 21. Haack, S.: Evidence Matters: Science, Proof, and Truth in the Law. Cambridge University Press, Cambridge (2014)

- 22. Mayo, D., Spanos, A.: Error and Inference: Recent Exchanges on Experimental Reasoning, Reliability, and the Objectivity and Rationality of Science. Oxford University Press, Oxford (2010)

- McDermid, J.: Safety arguments, software and system reliability. In: 2nd International Symposium on Software Reliability Engineering (ISSRE 1991), pp. 43–50 (1991)

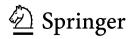

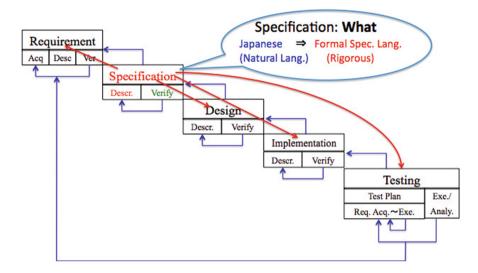

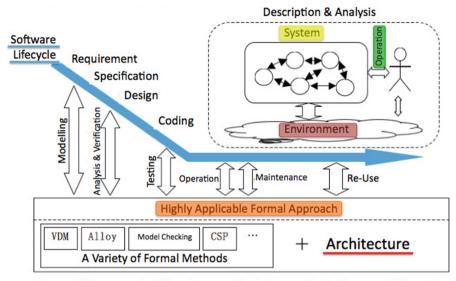

## Promotion of Formal Approaches in Japanese Software Industry and a Best Practice of FeliCa's Case (Extended Abstract)

Keijiro Araki<sup>1( $\boxtimes$ )</sup> and Taro Kurita<sup>2</sup>

<sup>1</sup> Kyushu University, 744 Motooka, Nishi-ku, Fukuoka 819-0395, Japan araki@ait.kyushu-u.ac.jp

$^2\,$ Sony Corporation, 2-10-1 Osaki, Shinagawa-ku, Tokyo 141-8610, Japan

Abstract. We have been making much effort to promote formal methods in Japan, especially Japanese IT companies. This paper describes our activities in Japan for almost twenty years, and shows typical reactions from such Japanese companies for application of formal methods. We mention about the obstacles they think to adopting formal methods in their real software development projects. On the other hand we also present a case of FeliCa Networks, Inc. as a best practice of applying formal methods in Japan. We discuss the lessons learned from our efforts of promoting formal methods and the FeliCa's case. Finally, we briefly introduce our research project to support software developers in adopting formal approaches to real projects.

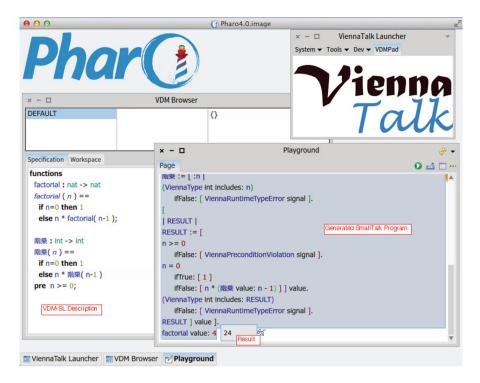

Keywords: Formal methods  $\cdot$  Rigorous specification  $\cdot$  Practice  $\cdot$  Development process  $\cdot$  FeliCa IC chip  $\cdot$  VDM  $\cdot$  VDMPad  $\cdot$  ViennaTalk

## 1 Introduction

We promote formal methods in Japan, and reported the status of formal methods in Japan. [1,2] Many Japanese companies are interested in formal methods in development of software systems. Some companies introduce and apply formal approaches successfully in their own development processes. However, there are not so many companies apply formal methods in their real development projects.