Michela Taufer · Bernd Mohr Julian M. Kunkel (Eds.)

# High Performance Computing

ISC High Performance 2016 International Workshops ExaComm, E-MuCoCoS, HPC-IODC, IXPUG, IWOPH, P<sup>3</sup>MA, VHPC, WOPSSS Frankfurt, Germany, June 19–23, 2016, Revised Selected Papers

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7407

Michela Taufer · Bernd Mohr Julian M. Kunkel (Eds.)

# High Performance Computing

ISC High Performance 2016 International Workshops ExaComm, E-MuCoCoS, HPC-IODC, IXPUG, IWOPH, P^3MA, VHPC, WOPSSS Frankfurt, Germany, June 19–23, 2016 Revised Selected Papers

*Editors* Michela Taufer University of Delaware Newark, DE USA

Bernd Mohr Forschungszentrum Jülich Jülich Germany Julian M. Kunkel DKRZ Hamburg Germany

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-46078-9 ISBN 978-3-319-46079-6 (eBook) DOI 10.1007/978-3-319-46079-6

Library of Congress Control Number: 2016942512

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer International Publishing AG 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

A separate workshop day attached to the ISC High Performance, formerly known as the International Supercomputing Conference, was first added to the technical program in 2015 under the leadership of Bernd Mohr (Forschungszentrum Jülich GmbH). Supported by the success of the last year, ISC High Performance renewed and further extended the workshop program in 2016. This year Michela Taufer (University of Delaware, USA) joined Bernd Mohr to co-lead the workshop organization. Julian Kunkel (German Climate Computing Center) joined the team as the proceedings chair and managed the organization of proceedings for the workshops.

As in 2015, the 21 workshops at ISC High Performance provided a focused, indepth platform with presentations, discussions, and interaction on topics related to all aspects of research, development, and application of large-scale, high-performance experimental and commercial systems. Workshop topics included: HPC computer architecture and hardware; programming models, system software, and applications; solutions for heterogeneity, reliability, power efficiency of systems; virtualization and containerized environments; big data and cloud computing; as well as international collaborations. Workshops were selected via a peer-review process by an international committee of 10 experts in the field from Europe, the USA, and Asia.

For the first time, ISC High Performance provided a platform for workshops with their own call for papers and individual peer-review process through an early deadline in December 2015. In all, 13 workshop proposals were submitted before this deadline from organizers all over the world; the committee accepted 10 workshops (seven full-day and two half-day workshops) after a rigorous review process in which each proposal received three reviews. Additionally, each reviewer was given the possibility to discuss all the submissions.

Workshops without a call for papers were invited to submit their proposals in February 2016. For this second deadline, 13 workshop proposals were submitted and 11 workshops (two full-day and nine half-day workshops) were accepted by the committee with the same rigorous peer-review process as for workshops with proceedings.

The 21 workshops were held on Thursday, June 26, 2016, at the Frankfurt Marriott Hotel with over 600 registered attendees, about 170 presentations, and over a dozen panel discussions. Workshop organizers were asked to collect the slides of all presentations at their workshops. PDF versions of the presentation slides were included in the ISC 2016 online proceedings, which were made available online to conference attendees a few days after the conference.

The workshop proceedings volume collects all the accepted papers of the workshops with a call for papers. Each chapter of the book contains the accepted and revised papers for one of the workshops. For some workshops, an additional preface describes the review process for the workshop and provides a summary of the outcome.

June 2016

Michela Taufer Bernd Mohr Julian M. Kunkel

# Organization

# **ISC High Performance Workshops Co-chairs**

| Bernd Mohr     | Forschungszentrum Jülich GmbH, Germany |

|----------------|----------------------------------------|

| Michela Taufer | University of Delaware, USA            |

#### **ISC High Performance Workshops Committee**

| Rosa M. Badia          | Barcelona Supercomputing Center, Spain      |

|------------------------|---------------------------------------------|

| Franois Bodin          | University of Rennes, France                |

| Bronis R. de Supinski  | Lawrence Livermore National Laboratory, USA |

| Jay Lofstead           | Sandia National Laboratories, USA           |

| Craig Lucas            | NAG, UK                                     |

| Naoya Maruyama         | RIKEN, Japan                                |

| Satoshi Matsuoka       | Tokyo Institute of Technology, Japan        |

| Marie-Christine Sawley | Intel, France                               |

| Seetharami Seelam      | IBM T.J. Watson Research Center, USA        |

| John Shalf             | Lawrence Berkeley National Laboratory, USA  |

| Antonino Tumeo         | Pacific Northwest National Laboratory, USA  |

#### **ISC High Performance Workshops Proceedings Chair**

| Julian Kunkel | DKRZ, Germany |

|---------------|---------------|

|---------------|---------------|

#### International Workshop on OpenPOWER for HPC (IWOPH)

#### **Organizing Committee**

| Dirk Pleiter | Jülich Supercomputing Centre, Germany |

|--------------|---------------------------------------|

| Jack Wells   | Oak Ridge National Laboratory, USA    |

#### **Program Committee**

| Zaid Al-Ars           | TU Delft, The Netherlands                    |

|-----------------------|----------------------------------------------|

| Mike Ashworth         | STFC, UK                                     |

| Costas Bekas          | IBM, Switzerland                             |

| Sunita Chandrasekaran | University of Delaware, USA                  |

| Norbert Eicker        | Jülich Supercomputing Centre, Germany        |

| Oscar Hernandez       | Oak Ridge National Laborator, USA (Co-chair) |

| Guido Juckeland       | TU Dresden, Germany                          |

| Graham Lopez<br>Barney Maccabe<br>Marek Michaelewicz<br>Rob Neely<br>Kevin O'Brien<br>Duncan Poole<br>Swaroop Pophale<br>Maciej Remiszewski<br>Vivek Sarkar<br>Jim Sexton<br>Gilad Shainer<br>Pavel Shamis<br>Sameer Shende<br>Tjerk Straatsma | Oak Ridge National Laboratory, USA (Co-chair)<br>Oak Ridge National Laboratory, USA<br>A-Star, Singapore<br>Lawrence Livermore National Laboratory, USA<br>IBM, USA<br>NVIDIA, USA<br>Oak Ridge National Laboratory, USA<br>ICM, Poland<br>Rice University, USA<br>IBM, USA<br>Mellanox, Israel<br>Oak Ridge National Laboratory, USA<br>University of Oregon, USA<br>Oak Ridge National Laboratory, USA |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bronis de Supinski                                                                                                                                                                                                                             | Oak Ridge National Laboratory, USA<br>Lawrence Livermore National Laboratory, USA                                                                                                                                                                                                                                                                                                                        |

| Michael Wolfe                                                                                                                                                                                                                                  | PGI, USA                                                                                                                                                                                                                                                                                                                                                                                                 |

# Workshop on Performance & Scalability of Storage Systems (WOPSSS)

#### **Organizing Committee**

Jean-Thomas Acquaviva DDN, USA

#### **Program Committee**

| Francisco J. Alfaro<br>André Brinkmann | University of Castilla-La Mancha, Spain<br>Mainz University, Germany |

|----------------------------------------|----------------------------------------------------------------------|

| Jason Chun Xue                         | City University of Hong Kong, Hong Kong,                             |

|                                        | SAR China                                                            |

| Toni Cortes                            | Barcelona Supercomputing Centre, Spain                               |

| Stefano Cozzini                        | NR, Italy                                                            |

| Liu Duo                                | Chongqing University, China                                          |

| Juan Piernas                           | University of Murcia, Spain                                          |

| Rekha Singhal                          | Tata CS Innovation Labs, India                                       |

# International Workshop on Performance Portable Programming Models for Accelerators (P^3MA)

# **Organizing Committee**

| Sunita Chandrasekaran | University of Delaware, USA        |

|-----------------------|------------------------------------|

| Graham Lopez          | Oak Ridge National Laboratory, USA |

# **Program Committee**

| Michael KlemmIntel, USAEric StotzerTexas Instruments, USAAmit AmritkarUniversity of Houston, USA |

|--------------------------------------------------------------------------------------------------|

|                                                                                                  |

| Guido Juckeland HZDR, Germany                                                                    |

| Will Sawyer ETH, Zurich                                                                          |

| Sameer Shende University of Oregon, USA                                                          |

| Costas Bekas IBM Zurich, Switzerland                                                             |

| Toni Collis University of Edinburgh, UK                                                          |

| Adrian Jackson University of Edinburgh, UK                                                       |

| Henri Jin NASA, USA                                                                              |

| Andreas Knuepfer TU Dresden, Germany                                                             |

| Steven Olivier Sandia National Laboratory, USA                                                   |

| Suraj Prabhakaran TU Darmstadt, Germany                                                          |

| Bora Ucar ENS Lyon, France                                                                       |

| Sandra Wienke Aachen University, Germany                                                         |

# Application Performance on Intel Xeon Phi – Being Prepared for KNL & Beyond (IXPUG)

# **Organizing Committee**

| atory, |

|--------|

|        |

|        |

|        |

|        |

|        |

## **Program Committee**

| Damian Alvarez-Mallon<br>Ryan Coleman | Forschungszentrum Jülich GmbH, Germany<br>Sandia National Laboratories, USA |

|---------------------------------------|-----------------------------------------------------------------------------|

|                                       | ,                                                                           |

| Douglas Doerfler                      | NERSC and Lawrence Berkeley National Laboratory,<br>USA                     |

| Antonio Gomez                         | TACC, USA                                                                   |

| Simon Hammond                         | Sandia National Laboratories, USA                                           |

| Rahul Hardikar                        | Indian Institute of Science, India                                          |

| Helen He                              | NERSC and Lawrence Berkeley National Laboratory, USA                        |

| Michael KlemmIntel, GermanyLars KoesterkeTACC, USABalaach KrichmeinerIntel, USA |

|---------------------------------------------------------------------------------|

| ,                                                                               |

| Deltach Krishneitzen Intel USA                                                  |

| Rakesh Krishnaiyer Intel, USA                                                   |

| Olli-Pekka Lehto CSC - IT Center for Science Ltd., Finland                      |

| John Linford ParaTools, Inc., USA                                               |

| Simon McIntosh-Smith Bristol University, UK                                     |

| John Michalakes NREL, USA                                                       |

| Dmitry Prohorov Intel, USA                                                      |

| Karthik Raman Intel, USA                                                        |

| Carlos Rosales TACC, USA                                                        |

| Hideki Saito Intel, USA                                                         |

| Abhinav Sarje Lawrence Berkeley National Laboratory, USA                        |

| Estella Suarez Forschungszentrum Jülich GmbH, Germany                           |

| Srinath Vadlamani Paratools, Inc., USA                                          |

| Jerome Vienne TACC, USA                                                         |

# HPC I/O in the Data Center (HPC-IODC)

#### **Organizing Committee**

| Julian Kunkel   | DKRZ, Germany                     |

|-----------------|-----------------------------------|

| Jay Lofstead    | Sandia National Laboratories, USA |

| Colin McMurtrie | CSCS, Switzerland                 |

# **Program Committee**

| Wolfgang Frings    | Jülich Supercomputing Centre, Germany         |

|--------------------|-----------------------------------------------|

| Javier Garcia Blas | University Carlos III of Madrid, Spain        |

| Rob Ross           | Argonne National Laboratory, USA              |

| Carlos Maltzahn    | University of California, Santa Cruz, USA     |

| Kathryn Mohror     | Lawrence Livermore National Laboratory, USA   |

| Xiaosong Ma        | North Carolina State University and Oak Ridge |

|                    | National Laboratory, USA                      |

### Second International Workshop on Communication Architectures at Extreme Scale (ExaComm)

# **Organizing Committee**

| Khaled Hamidouche    | Ohio State University, USA |

|----------------------|----------------------------|

| Dhabaleswar K. Panda | Ohio State University, USA |

| Hari Subramoni       | Ohio State University, USA |

# **Program Committee**

| Taisuke Boku     | University of Tsukuba, Japan                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------|

| Ron Brightwell   | Sandia National Laboratories, USA                                                                      |

| Hans Eberle      | NVIDIA, Germany                                                                                        |

| Ada Gavrilovska  | Georgia Tech, USA                                                                                      |

| Brice Goglin     | Inria, France                                                                                          |

| Dror Goldenberg  | Mellanox Technologies, Israel                                                                          |

| R. Govindarajan  | Indian Institute of Science, Bangalore, India                                                          |

| Hai Jin          | Huazhong University of Science and Technology,                                                         |

|                  | Wuhan, China                                                                                           |

| Yutong Lu        | National University of Defense Technology, China                                                       |

| Takeshi Nanri    | University of Kyushu, Japan                                                                            |

| Sebastien Rumley | Columbia University, USA                                                                               |

| Martin Schulz    | Lawrence Livermore National Laboratory, USA                                                            |

| John M. Shalf    | National Energy Research Scientific Computing Center<br>and Lawrence Berkeley National Laboratory, USA |

| Tor Skeie        | Simula Research Laboratory, Norway                                                                     |

| Sayantan Sur     | Intel, USA                                                                                             |

| Xin Yuan         | Florida State University, USA                                                                          |

# Workshop on Exascale Multi/Many Core Computing Systems (E-MuCoCoS)

# **Organizing Committee**

| Sabri Pllana | Linnaeus University, Sweden |

|--------------|-----------------------------|

| Achim Streit | KIT, Germany                |

# **Program Committee**

| RWTH Aachen University, Germany            |

|--------------------------------------------|

| University of Vienna, Austria              |

| IBM Research, Brazil                       |

| UAB, Spain                                 |

| University of Vienna, Austria              |

| Universidad Complutense de Madrid, Spain   |

| University of Oslo, Norway                 |

| Karlsruhe Institute of Technology, Germany |

| SENAI CIMATEC, Brazil                      |

| Tohoku University, Japan                   |

| LaBRI, University of Bordeaux 1, France    |

|                                            |

# Workshop on Virtualization in High-Performance Cloud Computing (VHPC'16)

# **Organizing Committee**

| Michael Alexander (Chair) | TU Wien, Austria |

|---------------------------|------------------|

| Anastassios Nanos         | NTUA, Greece     |

| (Co-chair)                |                  |

| Balazs Gerofi (Co-chair)  | RIKEN, Japan     |

# **Program Committee**

| Stergios Anastasiadis | University of Ioannina, Greece                  |

|-----------------------|-------------------------------------------------|

| Costas Bekas          | IBM Zurich Research Laboratory, Switzerland     |

| Jakob Blomer          | CERN                                            |

| Ron Brightwell        | Sandia National Laboratories, USA               |

| Roberto Canonico      | University of Napoli Federico II, Italy         |

| Julian Chesterfield   | OnApp, UK                                       |

| Stephen Crago         | USC ISI, USA                                    |

| Christoffer Dall      | Columbia University, USA                        |

| Patrick Dreher        | MIT, USA                                        |

| Robert Futrick        | Cycle Computing, USA                            |

| Robert Gardner        | University of Chicago, USA                      |

| William Gardner       | University of Guelph, Canada                    |

| Wolfgang Gentzsch     | UberCloud, USA                                  |

| Kyle Hale             | Northwestern University, USA                    |

| Marcus Hardt          | Karlsruhe Institute of Technology, Germany      |

| Krishna Kant          | Temple University, USA                          |

| Romeo Kinzler         | IBM, Switzerland                                |

| Brian Kocoloski       | University of Pittsburgh, USA                   |

| Kornilios Kourtis     | IBM Research, Switzerland                       |

| Nectarios Koziris     | National Technical University of Athens, Greece |

| John Lange            | University of Pittsburgh, USA                   |

| Nikos Parlavantzas    | IRISA, France                                   |

| Kevin Pendretti       | Sandia National Laboratories, USA               |

| Che-Rung Roger Lee    | National Tsing Hua University, Taiwan           |

| Giuseppe Lettieri     | University of Pisa, Italy                       |

| Qing Liu              | Oak Ridge National Laboratory, USA              |

| Paul Mundt            | Adaptant, Germany                               |

| Amer Qouneh           | University of Florida, USA                      |

| Carlos Reaño          | Technical University of Valencia, Spain         |

| Seetharami Seelam     | IBM Research, USA                               |

| Dieter Suess          | TU Wien, Austria                                |

| Josh Simons           | VMWare, USA                                     |

| Borja Sotomayor       | University of Chicago, USA                      |

|                       |                                                 |

- Craig Stewart Anata Tiwari Kurt Tutschku Amit Vadudevan Yasuhiro Watashiba Nicholas Wright Chao-Tung Yang Gianluigi Zanetti

- Indidana University, USA San Diego Supercomputer Center, USA Blekinge Institute of Technology, Sweden Carnegie Mellon University, USA Osaka University, Japan Lawrence Berkely National Laboratory, USA Tunghai University, Taiwan CRS4, Italy

# Contents

#### E-MuCoCoS

| 2016 Workshop on Exascale Multi/Many Core Computing Systems         (E-MuCoCoS)         Sabri Pllana and Achim Streit                                                                        | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Behavioral Emulation for Scalable Design-Space Exploration of Algorithms<br>and Architectures                                                                                                | 5  |

| Closing the Performance Gap with Modern C++<br>Thomas Heller, Hartmut Kaiser, Patrick Diehl, Dietmar Fey,<br>and Marc Alexander Schweitzer                                                   | 18 |

| Energy Efficient Runtime Framework for Exascale Systems                                                                                                                                      | 32 |

| Extreme-Scale In Situ Visualization of Turbulent Flows on IBM Blue<br>Gene/Q JUQUEEN<br>Jens Henrik Göbbert, Mathis Bode, and Brian J.N. Wylie                                               | 45 |

| The EPiGRAM Project: Preparing Parallel Programming Models<br>for Exascale                                                                                                                   | 56 |

| Work Distribution of Data-Parallel Applications on Heterogeneous Systems<br>Suejb Memeti and Sabri Pllana                                                                                    | 69 |

| ExaComm                                                                                                                                                                                      |    |

| Reducing Manipulation Overhead of Remote Data-Structure by Controlling<br>Remote Memory Access Order<br>Yuichiro Ajima, Takafumi Nose, Kazushige Saga, Naoyuki Shida,<br>and Shinji Sumimoto | 85 |

| SONAR: Automated Communication Characterization<br>for HPC Applications                                                                                                                      | 98 |

#### HPC-IODC

| HPC I/O in the Data Center Workshop (HPC-IODC) Julian M. Kunkel, Jay Lofstead, and Colin McMurtrie                                                                                                               | 116 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An Overview of the Sirocco Parallel Storage System<br>Matthew L. Curry, H. Lee Ward, Geoff Danielson, and Jay Lofstead                                                                                           | 121 |

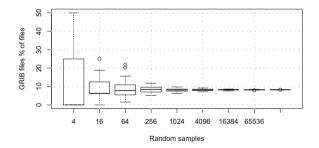

| Analyzing Data Properties Using Statistical Sampling Techniques –<br>Illustrated on Scientific File Formats and Compression Features Julian M. Kunkel                                                            | 130 |

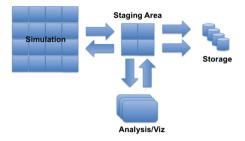

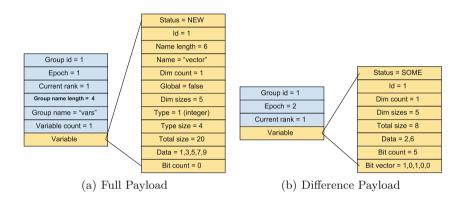

| Delta: Data Reduction for Integrated Application Workflows<br>and Data Storage                                                                                                                                   | 142 |

| Investigating Read Performance of Python and NetCDF When<br>Using HPC Parallel Filesystems<br>Matthew Jones, Jon Blower, Bryan Lawrence, and Annette Osprey                                                      | 153 |

| ІЖОРН                                                                                                                                                                                                            |     |

| International Workshop on OpenPOWER for HPC (IWOPH)                                                                                                                                                              | 170 |

| Early Application Performance at the Hartree Centre<br>with the OpenPOWER Architecture                                                                                                                           | 173 |

| Early Experiences Porting the NAMD and VMD Molecular Simulation<br>and Analysis Software to GPU-Accelerated OpenPOWER Platforms<br>John E. Stone, Antti-Pekka Hynninen, James C. Phillips,<br>and Klaus Schulten | 188 |

| Exploring Energy Efficiency for GPU-Accelerated POWER Servers<br>Thorsten Hater, Benedikt Anlauf, Paul Baumeister, Markus Bühler,<br>Jiri Kraus, and Dirk Pleiter                                                | 207 |

| First Experiences with <i>ab initio</i> Molecular Dynamics on OpenPOWER:<br>The Case of CPMD                                                                                                                     | 228 |

| High Performance Computing on the IBM Power8 Platform                                                                                                                                                            | 235 |

| Conter                                                                                                                                                                                        | nts XVII |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Measuring and Managing Energy in OpenPOWER<br>Todd Rosedah, Charles Lefurgy, and Martha Broyles                                                                                               | 255      |

| Performance Analysis of Spark/GraphX on POWER8 Cluster<br>Xinyu Que, Lars Schneidenbach, Fabio Checconi, Carlos H.Ã. Costa<br>and Daniele Buono                                               |          |

| Performance of the 3D Combustion Simulation Code RECOM®-AIOL<br>on IBM® POWER8® Architecture                                                                                                  | 286      |

| Performance-Portable Many-Core Plasma Simulations: Porting PIConGl<br>to OpenPower and Beyond                                                                                                 |          |

| IXPUG                                                                                                                                                                                         |          |

| Application Performance on Intel Xeon Phi – Being Prepared for KNL<br>and Beyond                                                                                                              | 304      |

| A Comparative Study of Application Performance and Scalability<br>on the Intel Knights Landing Processor                                                                                      | 307      |

| Application Suitability Assessment for Many-Core Targets<br>Chris J. Newburn, Jim Sukha, Ilya Sharapov, Anthony D. Nguyen,<br>and Chyi-Chang Miao                                             | 319      |

| Applying the Roofline Performance Model to the Intel Xeon Phi Knigh                                                                                                                           |          |

| Landing Processor<br>Douglas Doerfler, Jack Deslippe, Samuel Williams, Leonid Oliker,<br>Brandon Cook, Thorsten Kurth, Mathieu Lobet, Tareq Malas,<br>Jean-Luc Vay, and Henri Vincenti        | 339      |

| Dynamic SIMD Vector Lane Scheduling                                                                                                                                                           | 354      |

| High Performance Optimizations for Nuclear Physics Code MFDn on K<br>Brandon Cook, Pieter Maris, Meiyue Shao, Nathan Wichmann,<br>Marcus Wagner, John O'Neill, Thanh Phung, and Gaurav Bansal | NL 366   |

| Optimization of the Sparse Matrix-Vector Products of an IDR Krylov<br>Iterative Solver in EMGeo for the Intel KNL Manycore Processor<br><i>Tareq Malas, Thorsten Kurth, and Jack Deslippe</i> | 378      |

| Optimizing a Multiple Right-Hand Side Dslash Kernel for Intel<br>Knights Corner                                                                                                                                                                                                 | 390 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Aaron Walden, Sabbir Khan, Bálint Joó, Desh Ranjan,<br>and Mohammad Zubair                                                                                                                                                                                                      |     |

| Optimizing Excited-State Electronic-Structure Codes for Intel Knights<br>Landing: A Case Study on the BerkeleyGW Software<br>Jack Deslippe, Felipe H. da Jornada, Derek Vigil-Fowler,<br>Taylor Barnes, Nathan Wichmann, Karthik Raman, Ruchira Sasanka,<br>and Steven G. Louie | 402 |

| Optimizing Wilson-Dirac Operator and Linear Solvers for Intel <sup>®</sup> KNL<br>Bálint Joó, Dhiraj D. Kalamkar, Thorsten Kurth,<br>Karthikeyan Vaidyanathan, and Aaron Walden                                                                                                 | 415 |

| P^3MA                                                                                                                                                                                                                                                                           |     |

| First International Workshop on Performance Portable Programming<br>Models for Accelerators (P^3MA)                                                                                                                                                                             | 430 |

| A C++ Programming Model for Heterogeneous System Architecture<br>Ralph Potter, Russell Bradford, Alastair Murray, and Uwe Dolinsky                                                                                                                                              | 433 |

| Battling Memory Requirements of Array Programming Through Streaming<br>Mads R.B. Kristensen, James Avery, Troels Blum,<br>Simon Andreas Frimann Lund, and Brian Vinter                                                                                                          | 451 |

| From Describing to Prescribing Parallelism: Translating the SPEC ACCEL<br>OpenACC Suite to OpenMP Target Directives                                                                                                                                                             | 470 |

| GPU-STREAM v2.0: Benchmarking the Achievable Memory Bandwidth<br>of Many-Core Processors Across Diverse Parallel Programming Models<br><i>Tom Deakin, James Price, Matt Martineau, and Simon McIntosh-Smith</i>                                                                 | 489 |

| Porting the MPI Parallelized LES Model PALM to Multi-GPU<br>Systems – An Experience Report<br>Helge Knoop, Tobias Gronemeier, Christoph Knigge,<br>and Peter Steinbach                                                                                                          | 508 |

| Software Cost Analysis of GPU-Accelerated Aeroacoustics Simulations                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| in C++ with OpenACC                                                                                                            | 524 |

| Marco Nicolini, Julian Miller, Sandra Wienke,                                                                                  |     |

| Michael Schlottke-Lakemper, Matthias Meinke, and Matthias S. Müller                                                            |     |

| Task-Based Cholesky Decomposition on Knights Corner Using OpenMP<br>Joseph Dorris, Jakub Kurzak, Piotr Luszczek, Asim YarKhan, | 544 |

| and Jack Dongarra                                                                                                              |     |

| Using CLL AMD to Appalerate LIDC Applications on Multiple Distances                                                            | 562 |

| Using C++ AMP to Accelerate HPC Applications on Multiple Platforms | 563 |

|--------------------------------------------------------------------|-----|

| M. Graham Lopez, Christopher Bergstrom, Ying Wai Li, Wael Elwasif, |     |

| and Oscar Hernandez                                                |     |

# WOPSSS

| Analysis of Memory Performance: Mixed Rank Performance<br>Across Microarchitectures                                                                                 | 579 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Considering I/O Processing in CloudSim for Performance and Energy<br>Evaluation                                                                                     | 591 |

| Early Evaluation of the "Infinite Memory Engine" Burst Buffer Solution<br>Wolfram Schenck, Salem El Sayed, Maciej Foszczynski,<br>Wilhelm Homberg, and Dirk Pleiter | 604 |

| Motivation and Implementation of a Dynamic Remote Storage System<br>for I/O Demanding HPC Applications                                                              | 616 |

| Parallel I/O Architecture Modelling Based on File System Counters<br>Salem El Sayed, Matthias Bolten, and Dirk Pleiter                                              | 627 |

| User-Space I/O for µs-level Storage Devices                                                                                                                         | 638 |

| Scaling Spark on Lustre                                                                                                                                             | 649 |

#### XX Contents

#### VHPC

| Accelerating Application Migration in HPC                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| and André Brinkmann                                                                                                                 |     |

| Migrating LinuX Containers Using CRIU<br>Simon Pickartz, Niklas Eiling, Stefan Lankes, Lukas Razik,<br>and Antonello Monti          | 674 |

| Providing Security in Container-Based HPC Runtime Environments<br>Holger Gantikow, Christoph Reich, Martin Knahl, and Nathan Clarke | 685 |

| Author Index                                                                                                                        | 697 |

# E-MuCoCoS

# 2016 Workshop on Exascale Multi/Many Core Computing Systems (E-MuCoCoS)

Sabri Pllana<sup>1</sup> and Achim Streit<sup>2</sup>

<sup>1</sup> Department of Computer Science, Linnaeus University, Vaxjo, Sweden <sup>2</sup> Steinbuch Centre for Computing, Karlsruhe Institute of Technology, Karlsruhe, Germany

#### Overview

Exascale computing will revolutionize computational science and engineering by providing 1000x the capabilities of currently available computing systems, while having a similar power footprint. The HPC community is working towards the development of the first Exaflop computer after reaching the Petaflop milestone in 2008. There are concerns that computer designs based on existing multi-core and many-core solutions will not scale to Exascale considering technical challenges (such as, productivity, energy consumption or reliability) and reasonable economic constraints. Therefore, novel multi-core and many-core solutions are required to reach Exascale.

The E-MuCoCoS workshop series focuses on multi/many core languages, system software and architectural solutions for extreme-scale systems towards Exascale. The topics of the workshop include but are not limited to:

- Methods and tools for preparing applications for Exascale

- Extreme-scale data analysis and visualization

- Extreme-scale performance visualization, analysis, modeling, and tuning

- Adaptive run-time systems for extreme-scale

- Architectures for extreme-scale computing

E-MuCoCoS 2016 is organized in conjunction with the International Supercomputing Conference (ISC), Frankfurt, Germany, June 23, 2016.

Earlier editions of E-MuCoCoS workshop have not emphasized extreme-scale computing and the workshop was known as MuCoCoS. Previous MuCoCoS workshops include MuCoCoS 2014 (Porto, PT), MuCoCoS 2013 (Edinburgh, UK), MuCoCoS 2012 (Salt Lake City, US), MuCoCoS 2011 (Seoul, KR), Mu-CoCoS 2010 (Krakow, PL), MuCoCoS 2009 (Fukuoka, JP), and MuCoCoS 2008 (Barcelona, ES).

#### **Program Chairs**

| Sabri Pllana | Linnaeus University, SE               |

|--------------|---------------------------------------|

| Achim Streit | Karlsruhe Institute of Technology, DE |

#### **Program Committee**

| RWTH Aachen University, DE            |  |

|---------------------------------------|--|

| University of Vienna, AT              |  |

| IBM Research, BR                      |  |

| UAB, ES                               |  |

| University of Vienna, AT              |  |

| Universidad Complutense de Madrid, ES |  |

| University of Oslo, NO                |  |

| Karlsruhe Institute of Technology, DE |  |

| SENAI CIMATEC, BR                     |  |

| Linnaeus University, SE               |  |

| Karlsruhe Institute of Technology, DE |  |

| Tohoku University, JP                 |  |

| LaBRI, Universite Bordeaux 1, FR      |  |

|                                       |  |

#### Program

E-MuCoCoS 2016 workshop program included two keynotes, four selected speakers, and two invited talks of the European Exascale projects. The academic keynote speech was given by Ivona Brandić, who is Professor at the Vienna University of Technology and member of the Young Academy of Austrian Academy of Sciences. Hans-Christian Hoppe, who is Principal Engineer with Intel and director of the ExaCluster Lab at Jülich Supercomputing Centre, gave the industrial keynote speech.

In what follows in this section we list the workshop program.

- Session 1: Towards Exascale Computing Chair: Sabri Pllana (LNU, SE)

- Welcome to E-MuCoCoS 2016

Sabri Pllana (LNU, SE) and Achim Streit (SCC, KIT, DE)

- Academic Keynote: Exascale System Management What can we learn from efficient management of Ultra-scale Distributed Systems? Ivona Brandić (Vienna University of Technology, AT)

- Extreme-Scale In-Situ Visualization of Turbulent Flows on IBM Blue Gene/Q JUQUEEN

- Jens Henrik Göbbert (Jülich Supercomputing Centre, DE)

- Behavioral Emulation for Scalable Design-Space Exploration of Algorithms and Architectures

- Nalini Kumar (University of Florida, US)

- Energy Efficient Runtime Framework for Exascale Systems Yousri Mhedheb (Karlsruhe Institute of Technology, DE)

- Work Distribution of Data-parallel Applications on Heterogeneous Systems Suejb Memeti (Linnaeus University, SE)

#### 4 S. Pllana and A. Streit

- Session 2: Invited Talks of European Exascale Projects Chair: Achim Streit (SCC, KIT, DE)

- Industrial Keynote: *Intel HPC Co-Design Activities in Europe* Hans-Christian Hoppe (Intel Deutschland GmbH, DE)

- EPiGRAM: Preparing Message-Passing and PGAS Programming Models for Exascale

- Stefano Markidis (KTH, SE)

- AllScale: Closing the Performance Gap with Modern C++ Thomas Heller (Friedrich-Alexander-Universität Erlangen-Nürnberg, DE)

# Behavioral Emulation for Scalable Design-Space Exploration of Algorithms and Architectures

Nalini Kumar<sup>(⊠)</sup>, Carlo Pascoe, Christopher Hajas, Herman Lam, Greg Stitt, and Alan George

Department of ECE, PSAAP II Center for Compressible Multiphase Turbulence, NSF Center for High-Performance Reconfigurable Computing, University of Florida, Gainesville, FL 32608, USA {nkumar,pascoe,hajas,hlam,stitt,george}@chrec.org

Abstract. This paper presents a simulation methodology called Behavioral Emulation (BE) for scalable design-space exploration of algorithms and architectures. By design, BE is independent of simulation vehicle (e.g., simulation in software or emulation in hardware) and addresses system-simulation complexity with a coarse-grained, multi-scale approach. We describe the BE methodology, component models, and simulation workflow from calibration to validation of applications simulated on existing architectures and present a device-level case study with roughly 10% relative error. Finally, we discuss the extension of validated models to predict application performance on notional architectures.

**Keywords:** Behavioral Emulation  $\cdot$  Performance modeling  $\cdot$  Coarse-grained simulation  $\cdot$  Design space exploration

#### 1 Introduction

Large-scale simulations are vital scientific tools, especially when direct experimentation is expensive or infeasible [1–3]. Over several decades, these simulations have required constant growth in high-performance computing (HPC) to simulate more complex phenomena, with emerging applications [4] now requiring Exascale performance. In a rapidly evolving landscape of HPC systems [5], it is increasingly difficult for application developers to optimize code across system generations, a fact worsened by the trend towards many-core architectures and hardware accelerators (e.g., Intel Xeon Phi and Nvidia GPUs) [6]. Efficient optimization will require *co-design*, where application developers work with computer scientists and engineers to explore the design space to better design and optimize algorithms on different architectures and systems [7,8].

For design-space exploration (DSE) to be effective, it is important that turnaround between application performance analysis and code development be timely [9]. Architectural simulation/emulation plays a key role in design trade-off evaluation, but traditional approaches face several challenges, key among them optimizing the delicate balance between simulation speed, model accuracy, and design scalability. Unfortunately, traditional cycle-accurate simulators [10–12]

© Springer International Publishing AG 2016

M. Taufer et al. (Eds.): ISC High Performance Workshops 2016, LNCS 9945, pp. 5–17, 2016. DOI: 10.1007/978-3-319-46079-6\_1

and even functional simulators [13, 14], while highly accurate, lack scalability for DSE at extreme scales [15]. At the other extreme, purely analytical models [16-18] can provide quick performance estimates, but limit one's ability to gain detailed insight into the behavior of individual system components. As existing simulation methods do not provide an appropriate combination of fast turnaround time, scalability, and accuracy for large-scale system simulation, there is a need for a simulation framework that can fulfill these requirements.

In this paper, we present a novel multi-scale and coarse-grained methodology for large-scale system simulation called Behavioral Emulation (BE). The term *emulation* often refers to pre-fabrication simulation of architecture designs in hardware, but we use it to mean mimicking (i.e., emulating) behavior of the system under study. BE handles the complexity of extreme-scale system modeling and simulation by reducing it to a problem of modeling system components and their interactions at different levels of system organization—micro, meso, and macro—and by abstracting away low-level operational details at each of these levels. After a brief discussion of related research (Sect. 2), we expand our discussion of BE with more details on the approach (Sect. 3), modeling workflow and underlying BE component models (BE Objects or BEOs) (Sect. 4). Although our ultimate goal is prediction on large-scale systems, in this paper we limit our focus to establishing the BE methodology by presenting proof-of-concept design, calibration, and validation results for device-level experiments. In Sect. 5, we discuss our application (Spectral Element Solver kernel from CMT-nek) and architecture (mesh-based Tile-Gx36 many-core processor) case studies used in Sect. 6.1 to showcase validated BE simulation results with roughly 10% relative error for an existing system. Additionally, to demonstrate the applicability of BE for architecture DSE, in Sect. 6.2 we expand our "library" of BEOs by modeling additional devices, then mix, match, and modify components to model more notional architectures. Finally, in Sect. 7, we present conclusions and our future work towards realizing Exascale application and architecture DSE with BE.

#### 2 Related Research

Various modeling and simulation approaches, varying greatly in their accuracy and scalability, have been developed and used for design space exploration. Cycle-accurate simulation approaches (e.g., Gem5 [10], SimpleScalar [12], Simics [11] etc.) offer high accuracy but are prohibitively slow for simulating complex systems. Cycle-accurate emulation in hardware (e.g., Palladium [19], Veloce [20]) is a faster alternative, but it requires more resources, effort, and expertise that can be impractical for study of entire extreme-scale systems. While these approaches are impractical for use in isolation, they are complementary to Behavioral Emulation. Results of high-fidelity simulations of some system components can be used to calibrate models that be used in BE.

In addition to the cycle-accurate and analytical simulators already mentioned, functional simulation attempts to balance the tradeoff between simulation time and accuracy by modeling systems at a higher level of granularity. Manifold [14, 21], an execution-based simulator, follows a component-based approach, allowing users to piece together in-built (cycle-level models) or usergenerated components and tools to perform system performance, power, thermal, and reliability analysis. BigSim [13], a trace-driven simulator, analyzes the performance of sequential code-segments with variable-resolution architecture models that can be swapped to tune simulation speed/accuracy. FASE [22], another trace-driven simulator, characterizes the behavior of performance-critical components and allows users to build virtual system prototypes for analysis. BE uses a component-based approach similar to these simulators, but further decomposes the simulation into device-, node-, and system-level while using coarser-grained models for system components and a minimal application representation (as opposed to traces or application source). The fine-grained simulation approaches mentioned above can complement BE by providing data for calibrating BE component models.

SST (Structural Simulation Toolkit) [23,24] is a popular component-based simulation framework, with a parallel discrete-event simulation back-end and a standardized front-end used to interface various models (component simulators) to build a larger system. While high-fidelity models for system components are frequently used (e.g., gem5 [10]) within the SST framework, it is not a requirement. Because of the "plug-and-play" infrastructure and the freedom to model components at different granularities, we have adopted SST as the platform (backend) for our BE simulations.

#### 3 Behavioral Emulation: Overview and Approach

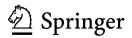

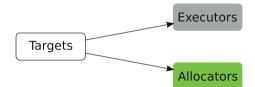

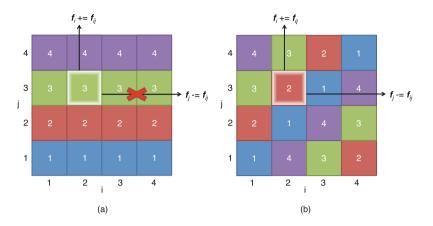

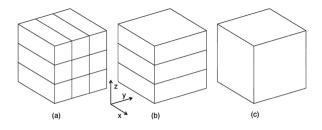

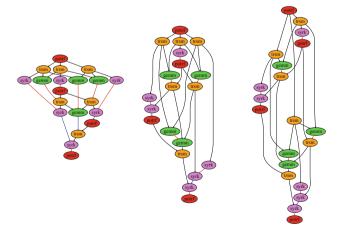

Behavioral Emulation (BE) is a coarse-grained modeling and simulation approach that aims to provide timely, flexible, and scalable estimates of application performance on existing and future system architectures. In BE, the complexity of large-scale system simulation is handled by simultaneously dividing the simulation into different levels of system abstraction (e.g., device, node, rack, system) and abstracting the behavior of the components at each of these levels. The coarse-grained component models mimic or emulate the observed execution behavior of the component instead of its cycle-accurate operation. Key features present within the BE approach (Fig. 1) are summarized below:

**Coarse-grained**. Coarse-grained application and architecture models allow BE to tradeoff acceptable accuracy for speed to enable fast DSE. High-level application models enable rapid prototyping of candidate algorithms and negate the need for working code. In addition, because BE coarse-grained performance models are pre-trained from samples of actual execution, they provide sufficiently accurate analysis in a short amount of time.

**Multi-scale**. Rather than simulate the entire HPC system, simulation is divided into separate levels of system organization such that the lower levels appear as a black box to the higher levels. We define device-, node-, and system-level simulations as micro-, meso-, and macro-scale simulations. Decomposing the problem in this manner allows us to prune the design space independently at

| Coarse-grained Modeling                       | Multi-scale Simulation                        |

|-----------------------------------------------|-----------------------------------------------|

| - High-level application models capture basic | - Divide simulation based on system hierarchy |

| blocks and communication patterns             | into micro-, meso-, and macro-scale           |

| - Behavioral, not detailed execution,         | - Lower levels are black boxes                |

| architecture models                           | to higher levels                              |

| - System is modeled as a group of             | - Use the same simulation                     |

| interacting component models called           | framework for performance, reliability,       |

| Behavioral Emulation Objects (BEOs)           | and power/energy models                       |

| Component-based Modeling                      | Multi-objective Simulation                    |

Fig. 1. Key features of Behavioral Emulation

lower scales (i.e., micro- and meso-) and evaluate only promising configurations at the macro-scale.

**Component-based**. In BE simulations, a system is modeled as a collection of interacting component models called Behavioral Emulation Objects (BEOs) (detailed in Sect. 4). For example, a micro-scale device simulation can be modeled as a combination of several parallel processing cores each able to communicate with their local L1 cache, the shared L2 and L3 caches, and memory all modeled as separate BEOs. At macro-scale, a simulation may consist of interacting devices or nodes, network switches, routers, and storage BEO models.

**Multi-objective**. The BE approach chiefly deals with various ways of reducing system simulation complexity and can be applied to study any aspect of system behavior such as performance, power, and reliability concerns.

In this paper, we focus on demonstrating the component-based and coarsegrained modeling aspects of BE by limiting ourselves to performance (execution time) modeling and simulation at micro-scale (device-level), while our ultimate goal remains to scale beyond device-level and study performance, power, and reliability tradeoffs.

#### 4 BE Modeling and Workflow

Figure 2 illustrates three key steps of the BE workflow: (1) design and calibration of application and architecture component models (i.e., BEOs), (2) validation of simulation (architecture and application model interactions) results against testbed measurements, and (3) using the verified models for performance prediction and HW/SW co-design. Each BEO from step (1) models the observed highlevel behavior of the component it represents, interacts with other BEOs in the simulation via event tokens, and gathers metrics of interest for post-simulation analysis. We classify these BEOs in two groups—Application BEOs (AppBEO) and Architecture BEOs (ArchBEOs).

AppBEOs are high-level, architecture-agnostic representations for the computation and communication blocks in a target application provided by the user

**Fig. 2.** BE workflow outlining major steps: (1) BEO design and calibration, (2) Validation of BE simulations, and (3) BE predictions for HW/SW co-design

(Fig. 3(c)). They are described in a simple, extensible, platform-independent, high-level API and compiled into events for ArchBEOs to interpret and process. By doing so, algorithms of interest can be easily prototyped at the expense of exact execution details which, in some cases, may be of interest to the user.

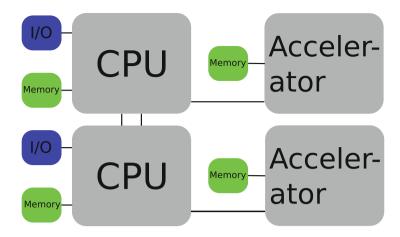

ArchBEOs are coarse-grained models crafted to mimic the behavior of various systems components such as processors (ProcBEO), network switches and routers (CommBEO), memory (MemBEOs), processing nodes (NodeBEO), storage (DiskBEO) etc. ArchBEOs have two functions—emulation and management. Emulation tasks include processing event queues, handling and creating events, updating simulation timestamps, and interacting with other BEOs in the simulation. Management tasks include tracking results and statistics for run-time or post-simulation analysis.

In a BE simulation, operations defined in the AppBEO (e.g., matrix multiply, fast fourier transform) are compiled into events (e.g., update timestamp, wait, generate event token) to be handled by ArchBEOs. The events are processed and simulation clocks are updated based on multi-dimensional performance models (surrogates [25]) when an event is processed. Data collected from microbenchmarked testbeds (or external fine-grained architecture simulation tools) is used to calibrate surrogates for existing systems. By tweaking ArchBEO simulation parameters (e.g., network bandwidths, latencies, or topology) or replacing BEO models with other validated BEO models, it becomes possible to simulate notional architectures. These BEOs use a parallel discrete-event simulation back-end for event handling and synchronization. We use Lamport clocks [26] to maintain event ordering.

#### 5 Application and Architecture Case Study

In this section, we describe the application (Sect. 5.1) and architecture (Sect. 5.2) case-studies used in Sect. 6 experiments.

#### 5.1 Application Case Study: Spectral Element Solver

In this Section, we discuss the Spectral Element Solver (SES) [27] within CMT-nek [4], a large-scale simulation code under development by the PSAAP II Center for Compressible Multiphase Turbulence (CCMT) at University of Florida. Although CMT-nek will leverage several aspects of the petascale code Nek5000 [1] (e.g., optimized linear algebra operations, element topology, approximation polynomials, MPI strategies), one significant contribution will be the extension of NavierStokes equations within the SES to their compressible forms. With many possible implementations, early algorithm DSE for target systems (current and future) will help to maximize application performance and minimize wasted effort.

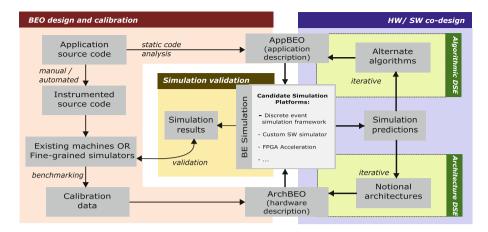

The majority of CMT-nek execution time is spent computing the *flux divergence* terms within the SES (Fig. 3(a)). Flux divergence is essentially a dot product of the gradient operator and the flux vector implemented as the multiplication of the derivative operator matrix (N, N) and the element matrix (N, N, K, E)

**Fig. 3.** (a) Pseudo-code for the partial derivative calculation for estimating the fluxdivergence term, (b) Pairwise exchange communication between the neighboring elements located on processes in X, Y and Z directions, and (c) Partial AppBEO for the spectral element solver

to calculate the partial derivatives along the three Cartesian coordinate dimensions (r, s, t). Here  $N \in [5, 25]$  is the number of grid points along a direction in a cubic reference element and E is the total number of elements in the computational domain. For our case study, we use a straightforward implementation of this operation where explicit optimizations, such as loop fusion or loop unroll, are not applied. *Numerical flux* is evaluated to ensure continuity on the element boundaries and requires exchanging surface data between neighboring elements. Currently, CMT-nek uses a *pairwise exchange* communication strategy, a simple implementation of which is used for crafting our AppBEOs (Fig. 3(b) and (c)).

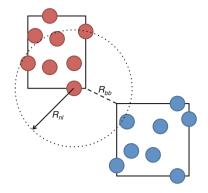

#### 5.2 Architecture Case Study: Mesh-Based Many-Core Device

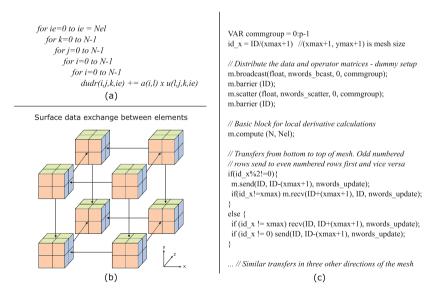

As previously mentioned, in this paper we limit our focus to the design, calibration, and validation of device-level models. For our experiments we use TILE-Gx36, a 36-core many-core processor [28] from Mellanox (Tilera corporation before acquisition). The 36 cores, or *tiles*, are arranged as a  $6 \times 6$  2D mesh. Each tile contains a 64-bit SIMD processor core, L1 and L2 cache, and a non-blocking switch for connection to the *iMesh* network. The iMesh interconnect has five independent low-latency mesh networks for memory, I/O, and user communication. Of these, explicit transfer of data between tiles occurs via packets on the User Dynamic Network (UDN). The packets are routed in dimension-order and cut-through switching with each hop taking a single clock cycle.

The BE description of TILE-Gx36 consists of 36 ProcBEOs (model for a single tile) and 36 CommBEOs (model for a single iMesh switch) connected as a 2D mesh. The ProcBEO is responsible for sequentially processing

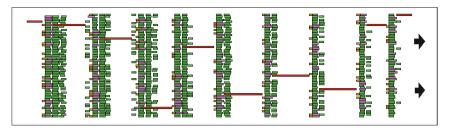

Fig. 4. Pseudo-code for CommBEO and data obtained from the TILE-Gx36 testbed to calibrate iMesh model for BE simulation

AppBEO instructions (events), estimating the performance of computation events, sending/receiving communication events to/from CommBEOs, updating local simulation clocks, and logging of event outcomes for future analysis or visualization. Each ProcBEO has models calibrated for setup times, overheads, and the time taken for several computation operations (e.g., addition, multiplication, dotproduct). CommBEOs interface with each other to model communication over the mesh network. Each CommBEO is calibrated with tile-to-tile one-way transfer latencies, hop times, and routing procedures as shown in Fig. 4.

### 6 Experiments: BE Validation and Prediction

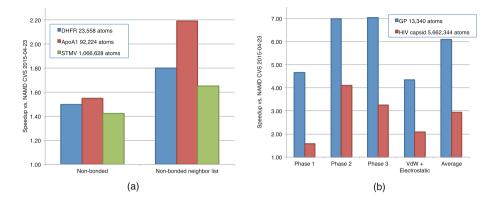

In this Section, we evaluate the BE approach by validating simulations of SES (Sect. 5.1) executed on TILE-Gx36 by comparing the simulation results with device benchmarking measurements. We then extend our architecture models to predict the performance of the same kernel on notional device architectures.

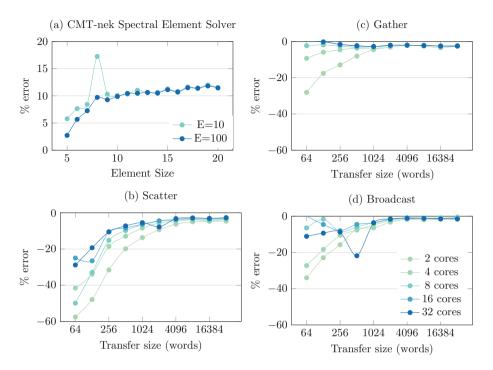

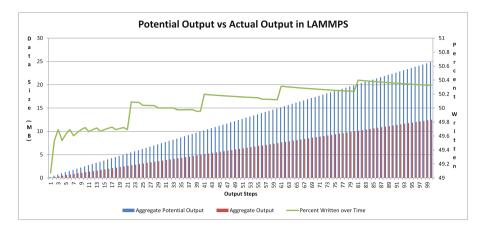

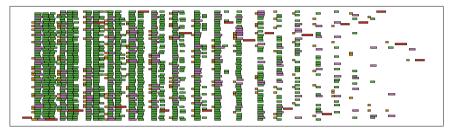

#### 6.1 Simulation Validation

We compare BE simulations of SES on TILE-GX36 against benchmarking data collected by running the same SES configurations on the TILE-Gx36 platform. For processor loads of E = 10 and E = 100 elements, BE predicted the execution times for varied element sizes (i.e., gridpoints) from N = 5 to 20. This setup is representative of experiments used to identify the optimal N value for SES on a particular architecture (i.e., algorithm and architecture DSE). Figure 5(a) shows the relative error between predicted and actual execution times. From the plot we can see that number of elements has almost no influence on relative error and element size has little influence on simulation accuracy. Within the simulation range, error is approximately 10%, which is acceptable for DSE where the goal is to find design alternatives which offer significant performance improvement. BE simulations of SES take considerably less time than running the actual code on the testbed (microseconds for a second of real execution), which enables us to quickly simulate a large number of design options, ultimately supporting our argument for using BE for fast DSE.

To better understand these results, we need to look more closely at our network and processor models. Figure 5(b-d) shows simulations of different collective operations (implemented using P2P transfers) on Tile iMesh. We observe that in all cases BE under-predicts execution time, and as the message size increases (to transfer sizes common in SES), the modeling accuracy improves considerably. From these plots we can conclude that while BE models accurately capture the underlying bandwidth behavior, we need more accurate latency models for the smaller transfer sizes to increase overall simulation accuracy.

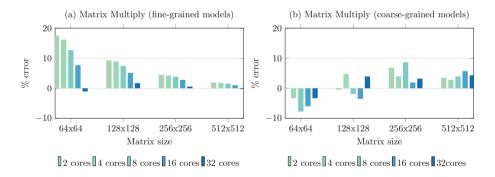

Processor models estimate the execution time for basic computation blocks, where the definition of what constitutes a basic block is left to the user. For example, a parallel matrix multiplication can be thought of as each processor computing several smaller matrix multiplies (coarse-grain decomposition) or as computing several dot products (fine-grained decomposition). While BE gives

**Fig. 5.** Percent relative error in simulations of (a) Spectral Element Solver on TILE-Gx36, (b) Scatter over iMesh, (c) Gather over iMesh, and (d) Broadcast over iMesh

Fig. 6. Percent relative error in simulations of matrix multiplication configured as (a) fine-grained vector dot-products, and (b) smaller coarse-grained matrix multiplications

the flexibility of using either decomposition, we observed using coarse-grained models can improve simulation accuracy as shown in Fig. 6 and improve simulation speed by reducing the total number of processed events. The SES App-BEO used for simulation in Fig. 5(a) followed the coarse-grained decomposition approach.

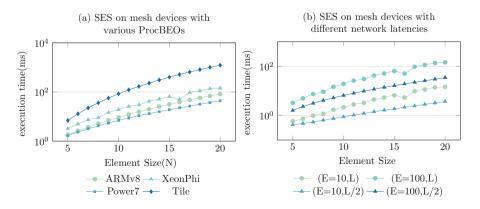

#### 6.2 Performance Prediction on Notional Architectures

The same modeling procedure from Sect. 5.2 was used to generate ArchBEOs for the following devices: Applied Micro X-Gene (64-bit ARMv8), IBM Power7, and Intel Xeon Phi (5110P). With a "library" of calibrated BEOs, it becomes possible to mix and match components from different devices as well as configure those components in different ways. Such a library, in combination with the ability to incorporate altered BEOs (e.g., an iMesh topology with 2x bandwidth or 3x shorter link-to-link transfer latency) into system simulations, allows for relatively quick architectural DSE, most notably for notional architectures. As mentioned earlier, in this paper we limit our focus to device-level exploration of many-core processors.

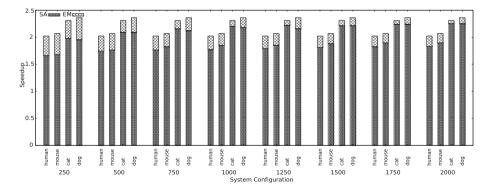

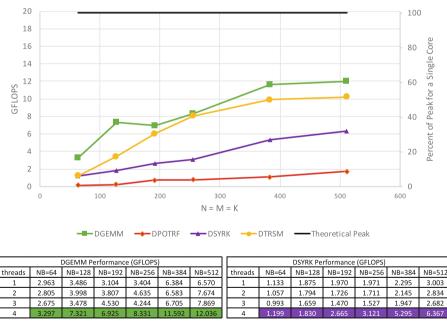

Figure 7(a) shows simulated weak-scaling performance of SES with E = 100 and varied element size for several notional many-core devices. First, we extended the TILE-Gx36 simulation setup from Sect. 6.1 to describe a notional  $9 \times 8$  mesh rather than  $6 \times 6$ , increasing the total number of Proc and CommBEOs from 36 each to 72 (Tile curve). Keeping the CommBEO constant, we replaced the TILE-Gx36 ProcBEO model with calibrated BEOs for other processor types. Ignoring the technical challenges of actual device implementation, as one would expect, more complex core architectures are predicted to perform better when placed in a many-core configuration with communication behavior held constant.

Figure 7(b) shows simulated weak-scaling performance of SES with varied processor load and element size for two notional Xeon-Phi-based  $9 \times 8$  manycore devices. One device is configured with the same link-to-link transfer latency from Fig. 7(a) experiments and the other with half of that latency. We observed that, for these application configurations, reducing the link-to-link latency by half increased the overall application performance between 28 and 78 percent depending upon the exact computation to communication ratios. While we used 50% latency reduction for illustrative purposes, it would be advantageous to insert actual numbers from existing product data sheets or upcoming product press releases.

Fig. 7. Architecture DSE of SES on notional device architectures

15

#### 7 Conclusions and Future Work

In this paper, we introduced Behavioral Emulation, a coarse-grained, componentbased, multi-scale simulation methodology for fast and scalable DSE of algorithms and architectures. We demonstrated the value of such an approach for kernel optimization by modeling the SES used within CMT-nek and predicting its performance for an existing many-core device (TILE-Gx36). We then extended the models for performance prediction to notional mesh-based manycore devices and demonstrated the ease and utility of BE methodology for DSE.

Although this paper was limited to device-level experiments, we discussed the extensibility of our methods to node- and system-levels. Working towards this goal, we are modeling a larger portion of the current CMT-nek implementation (than described in this paper) and its execution on contemporary HPC systems (e.g., Vulcan [29], CAB [30]). Furthermore, we are beginning to model several candidate implementations of certain CMT-nek kernels and exploring their performance on HPC systems utilizing accelerators such as GPUs. In the future, we plan to model additional metrics (e.g., reliability, power) to enable multi-objective DSE.

Determining the optimal degree of behavioral abstraction becomes more difficult at the system-level prompting us to employ more robust uncertainty quantification and analysis techniques when evaluating new design decisions (e.g., sophistication of performance interpolation techniques, detail of network congestion models). We have incorporated mechanisms for Monte-Carlo-based (MC) uncertainty propagation [31] into the BE framework, greatly improving model development and simulation accuracy. The increased computation required for MC-based simulations may limit the practical scale of BE simulations in software; we are currently investigating the use of FPGA acceleration techniques to alleviate this issue. Our early functioning prototype running on Novo-G [32, 33] is capable of performing simulations in Sect. 6 about 100x faster than our software simulator and we are currently integrating functionality for random distribution sampling to enable MC simulations in hardware.

Acknowledgment. This work is supported by the U.S. Department of Energy, National Nuclear Security Administration, Advanced Simulation and Computing Program, as a Cooperative Agreement under the Predictive Science Academic Alliance Program, under Contract No. DE-NA0002378. This work was supported in part by the I/UCRC Program of the National Science Foundation under Grant Nos. EEC-0642422 and IIP-1161022.

#### References

- 1. Fischer, P.F., Lottes, J.W., Kerkemeier, S.G.: Nek5000 (2008). http://nek5000. mcs.anl.gov

- Berna, G., Beyer, G., Davis, K., Lanning, D.: FRAPCON-3: a computer code for the calculation of steady-state, thermal-mechanical behavior of oxide fuel rods for high burnup, December 1997

- Hamidouche, T., Bousbia-Salah, A., Adorni, M., D'Auria, F.: Dynamic calculations of the iaea safety mtr research reactor benchmark problem using relap5/3.2 code. Ann. Nucl. Energy **31**(12), 1385–1402 (2004)

- 4. CCMT: Psaap-ii center for compressible multiphase turbulence. https://www.eng.ufl.edu/ccmt/

- Kogge, P., Bergman, K., Borkar, S., Campbell, D., Carson, W., Dally, W., Denneau, M., Franzon, P., Harrod, W., Hill, K., et al.: Exascale computing study: technology challenges in achieving exascale systems (2008)

- 6. Top500: The top500 list, November 2015. http://www.top500.org/lists/2015/11/

- Barrett, R.F., Borkar, S., Dosanjh, S.S., Hammond, S.D., Heroux, M.A., Hu, X.S., Luitjens, J., Parker, S.G., Shalf, J., Tang, L.: On the role of co-design in high performance computing, vol. 24, pp. 141–155 (2013)

- Dosanjh, S., Barrett, R., Doerfler, D., Hammond, S., Hemmert, K., Heroux, M., Lin, P., Pedretti, K., Rodrigues, A., Trucano, T., et al.: Exascale design space exploration and co-design. Future Gener. Comput. Syst. 30, 46–58 (2014)

- Ang, J.A., Hoang, T.T., Kelly, S.M., McPherson, A., Neely, R.: Advanced simulation and computing co-design strategy. Technical report, Sandia National Laboratories (SNL-NM), Albuquerque, NM (United States) (2015)

- Binkert, N., Beckmann, B., Black, G., Reinhardt, S.K., Saidi, A., Basu, A., Hestness, J., Hower, D.R., Krishna, T., Sardashti, S., Sen, R., Sewell, K., Shoaib, M., Vaish, N., Hill, M.D., Wood, D.A.: The gem5 simulator. SIGARCH Comput. Archit. News 39(2), 1–7 (2011)

- Magnusson, P.S., Christensson, M., Eskilson, J., Forsgren, D., Hallberg, G., Hogberg, J., Larsson, F., Moestedt, A., Werner, B.: Simics: a full system simulation platform. Computer 35(2), 50–58 (2002)

- Austin, T., Larson, E., Ernst, D.: Simplescalar: an infrastructure for computer system modeling. Computer 35(2), 59–67 (2002)

- Zheng, G., Kakulapati, G., Kalé, L.V.: Bigsim: a parallel simulator for performance prediction of extremely large parallel machines. In: Proceedings of the 18th International Symposium on Parallel and Distributed Processing, vol. 78. IEEE (2004)

- Wang, J., Beu, J., Yalamanchili, S., Conte, T.: Designing configurable, modifiable and reusable components for simulation of multicore systems. In: 2012 SC Companion: High Performance Computing, Networking, Storage and Analysis (SCC), pp. 472–476. IEEE (2012)

- Tan, Z., Waterman, A., Avizienis, R., Lee, Y., Cook, H., Patterson, D., Asanović, K.: Ramp gold: an fpga-based architecture simulator for multiprocessors. In: Proceedings of the 47th Design Automation Conference, pp. 463–468. ACM (2010)

- Culler, D., Karp, R., Patterson, D., Sahay, A., Schauser, K.E., Santos, E., Subramonian, R., von Eicken, T.: Logp: towards a realistic model of parallel computation. In: Proceedings of the Fourth ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPOPP 1993, New York, NY, USA, pp. 1–12. ACM (1993)

- Alexandrov, A., Ionescu, M.F., Schauser, K.E., Scheiman, C.: Loggp: incorporating long messages into the logp modelone step closer towards a realistic model for parallel computation. In: Proceedings of the Seventh Annual ACM Symposium on Parallel Algorithms and Architectures, pp. 95–105. ACM (1995)

- Ino, F., Fujimoto, N., Hagihara, K.: Loggps: a parallel computational model for synchronization analysis. In: ACM SIGPLAN Notices, vol. 36, pp. 133–142. ACM (2001)

- 19. Cadence palladium ii

- 20. Mentor graphics corporation. veloce emulation platform

- Dong, Z., Wang, J., Riley, G., Yalamanchili, S.: An efficient front-end for timingdirected parallel simulation of multi-core system. In: Proceedings of the 7th International ICST Conference on Simulation Tools and Techniques, ICST (Institute for Computer Sciences, Social-Informatics and Telecommunications Engineering), pp. 201–206 (2014)

- Grobelny, E., Bueno, D., Troxel, I., George, A.D., Vetter, J.S.: Fase: a framework for scalable performance prediction of hpc systems and applications. Simulation 83(10), 721–745 (2007)

- Rodrigues, A.F., Hemmert, K.S., Barrett, B.W., Kersey, C., Oldfield, R., Weston, M., Risen, R., Cook, J., Rosenfeld, P., CooperBalls, E., et al.: The structural simulation toolkit. ACM SIGMETRICS Perform. Eval. Rev. 38(4), 37–42 (2011)

- Janssen, C.L., Adalsteinsson, H., Cranford, S., Kenny, J.P., Pinar, A., Evensky, D.A., Mayo, J.: A simulator for large-scale parallel computer architectures. Technol. Integr. Advancements Distrib. Syst. Comput. **179**, 179–195 (2012)

- Rudolph, D., Stitt, G.: An interpolation-based approach to multi-parameter performance modeling for heterogeneous systems. In: 2015 IEEE 26th International Conference on Application-specific Systems, Architectures and Processors (ASAP), pp. 174–180. IEEE (2015)

- Lamport, L.: Time, clocks, and the ordering of events in a distributed system. Commun. ACM 21(7), 558–565 (1978)

- Kumar, N., Sringarpure, M., Banerjee, T., Hackl, J., Balachandar, S., Lam, H., George, A., Ranka, S.: CMT-bone: a mini-app for compressible multiphase turbulence simulation software. In: Proceedings of the 2015 IEEE International Conference on Cluster Computing (CLUSTER 2015), pp. 785–792. IEEE Computer Society, Washington, DC (2015)

- Tilera: Tile-gx8036 processor specification brief (2012). http://www.tilera.com/ sites/default/files/productbriefs/TILE-Gx8036PB033-02.pdf

- Barney, B.: Using the sequoia and vulcan bg/q systems, Tutorial Lawrence Livermore National Laboratory, Lawrence Livermore National Laboratory, 8 (2014). https://computing.llnl.gov/tutorials/bgq/#ParallelIO

- 30. LLNL: Open computing facility-ocf, resource overview: Cab, October 2014

- Helton, J.: Uncertainty and sensitivity analysis in the presence of stochastic and subjective uncertainty. J. Stat. Comput. Simul. 57(1-4), 3-76 (1997)

- George, A., Lam, H., Stitt, G.: Novo-g: at the forefront of scalable reconfigurable supercomputing. Comput. Sci. Eng. 13(1), 82–86 (2011)

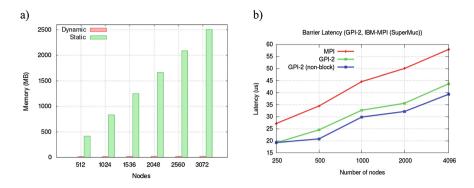

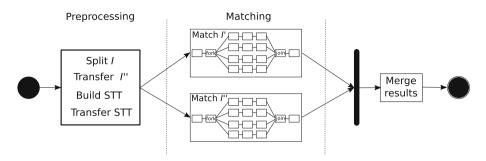

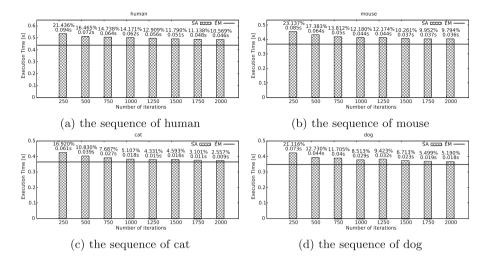

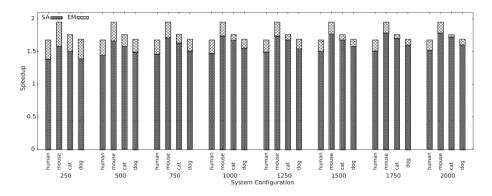

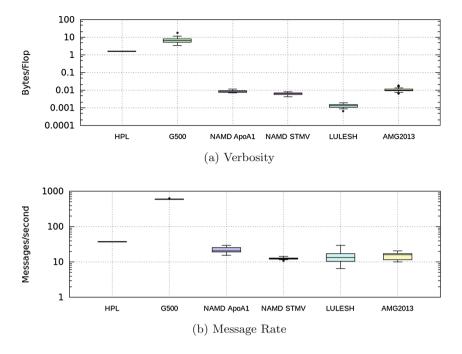

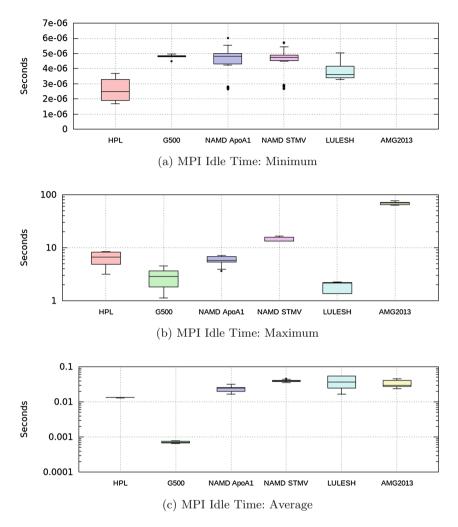

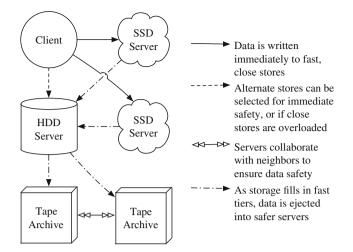

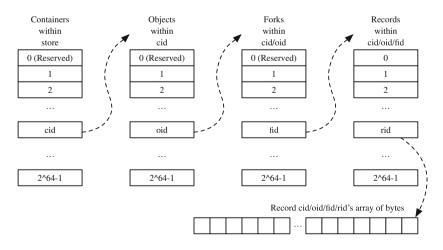

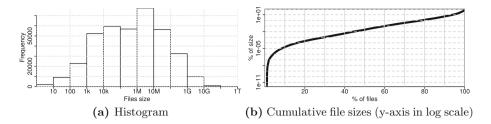

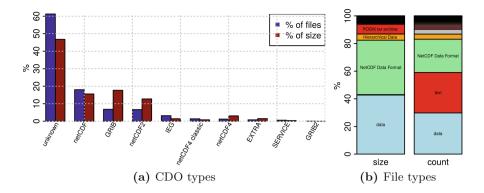

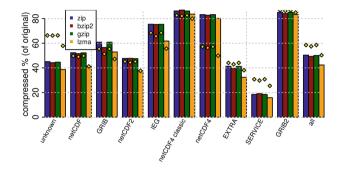

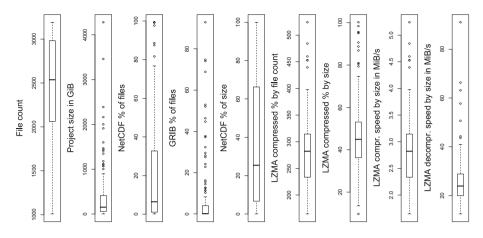

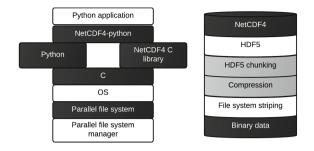

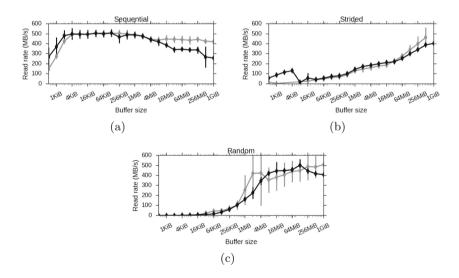

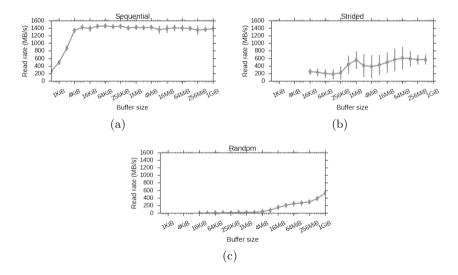

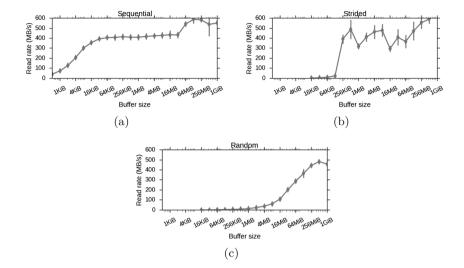

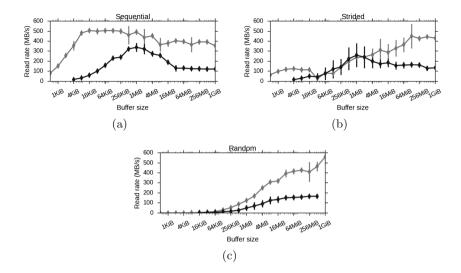

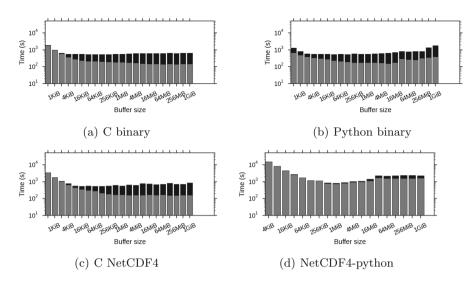

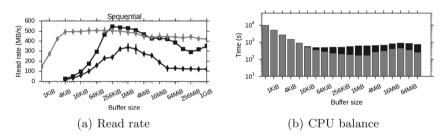

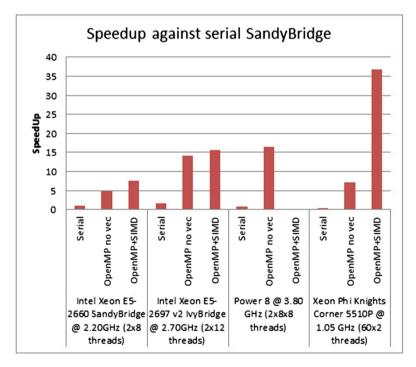

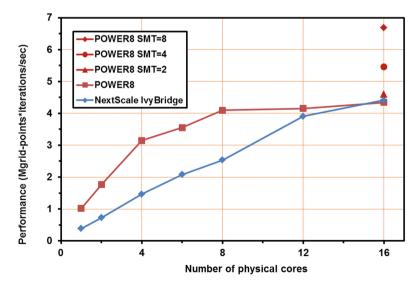

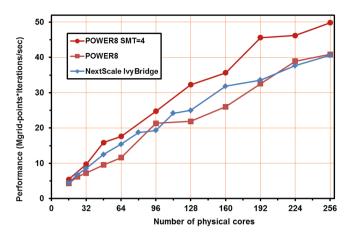

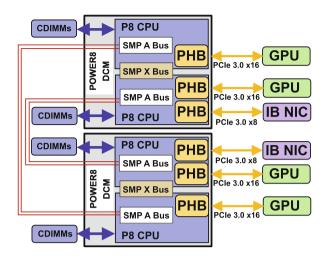

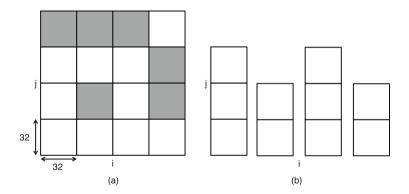

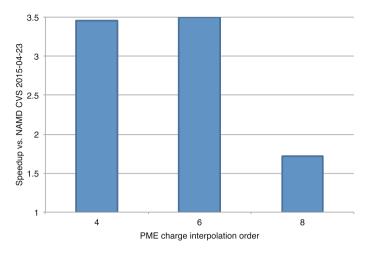

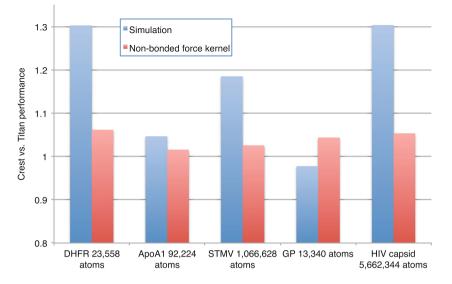

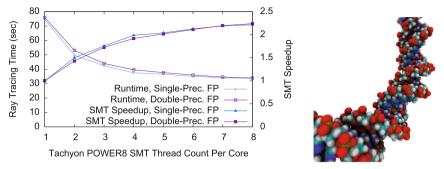

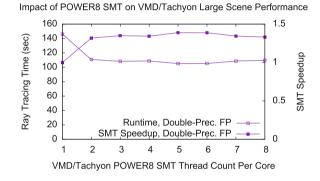

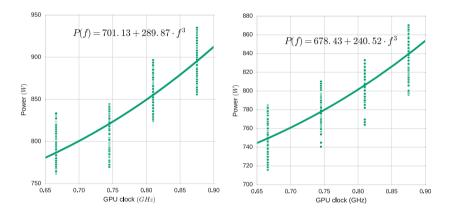

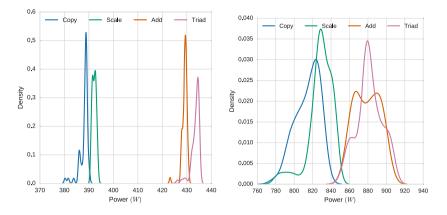

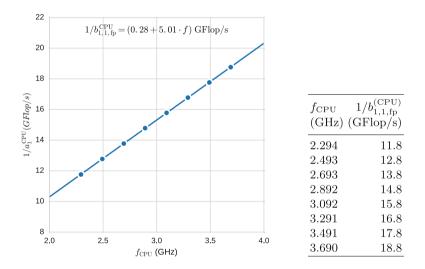

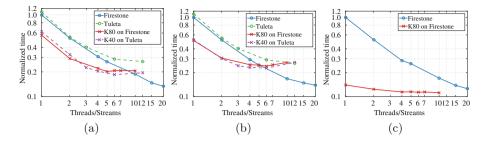

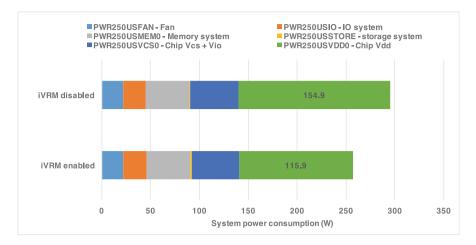

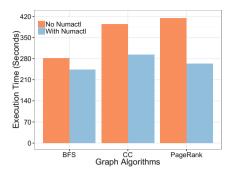

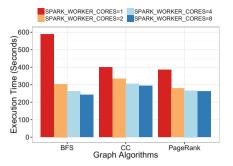

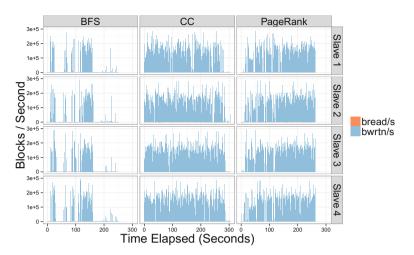

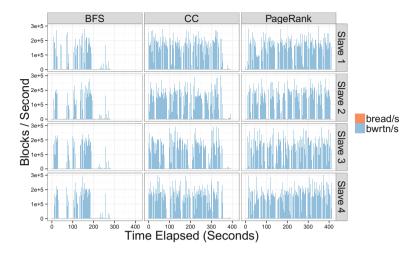

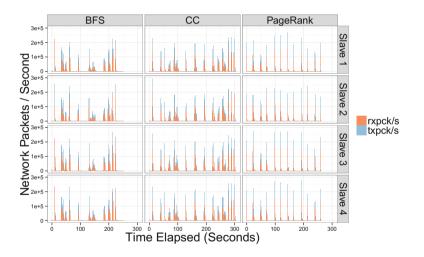

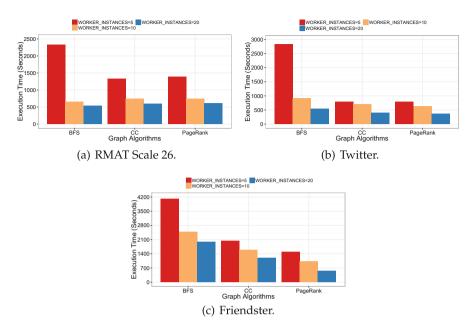

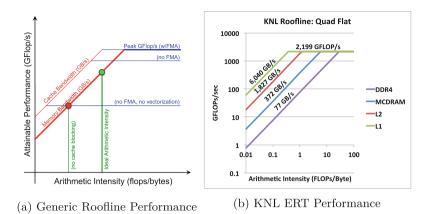

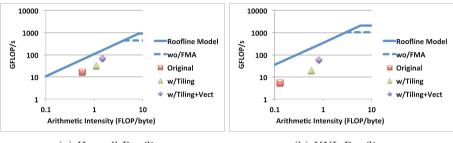

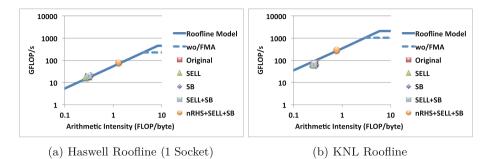

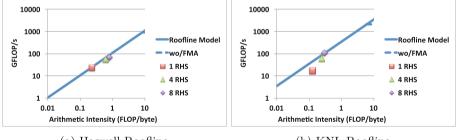

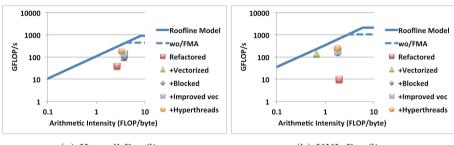

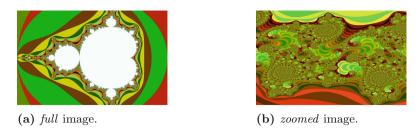

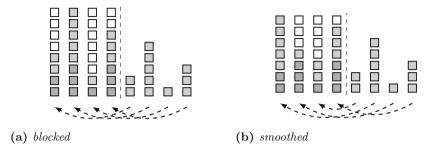

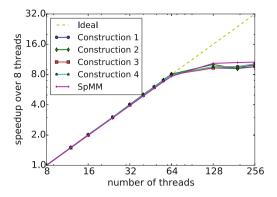

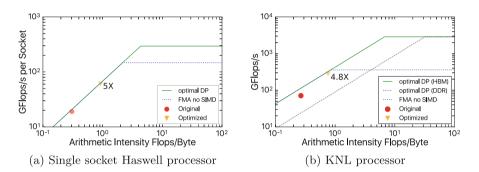

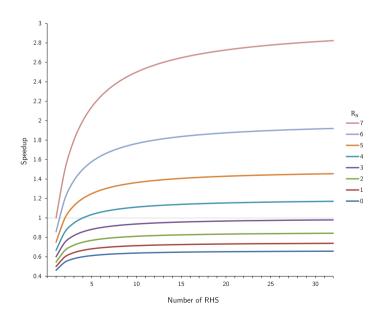

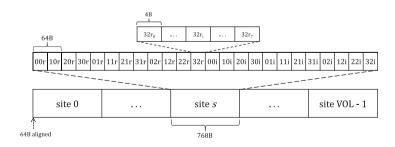

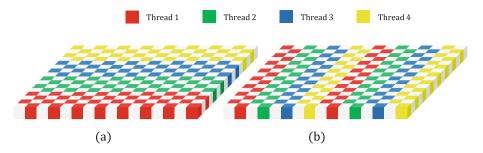

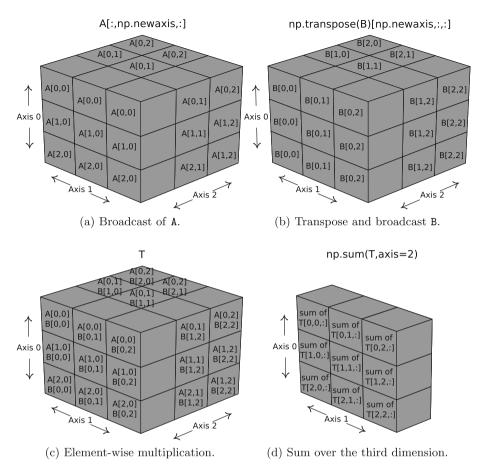

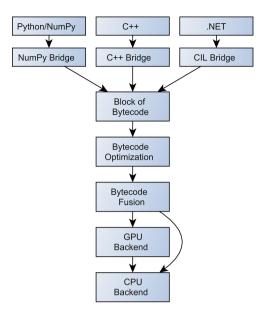

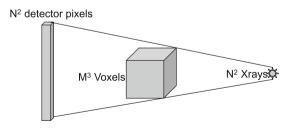

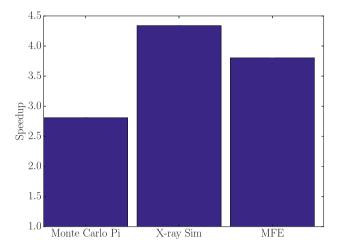

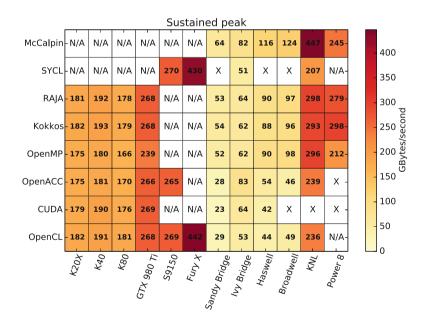

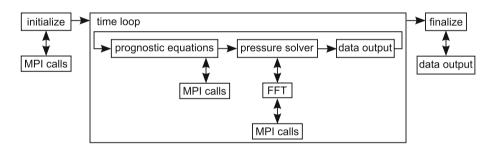

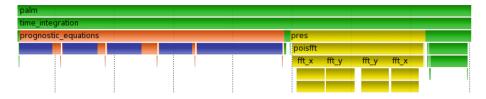

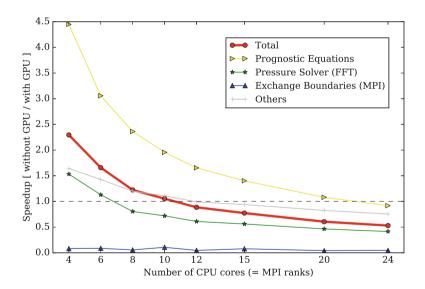

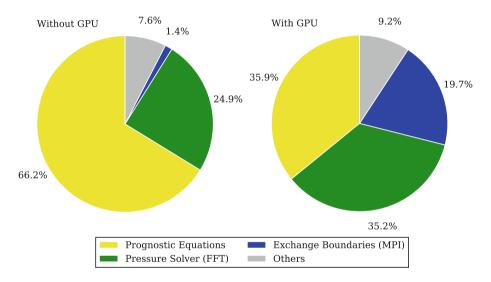

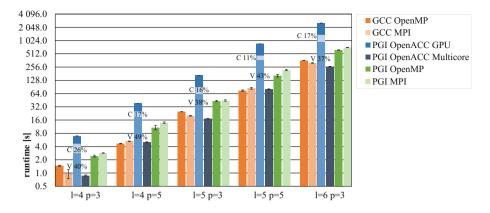

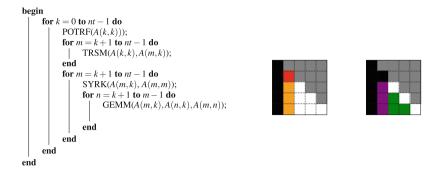

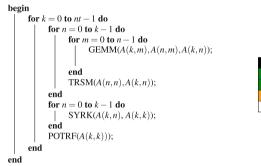

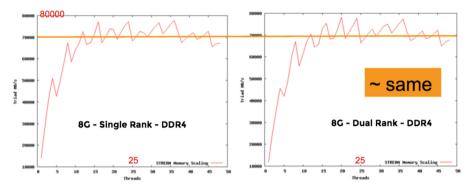

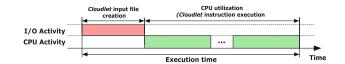

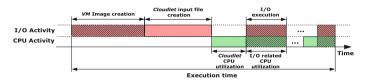

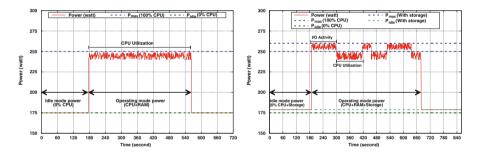

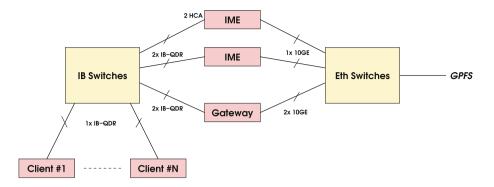

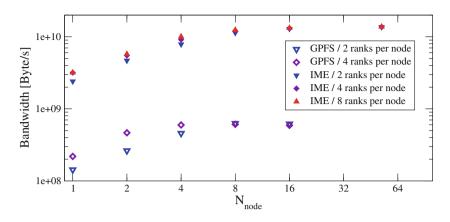

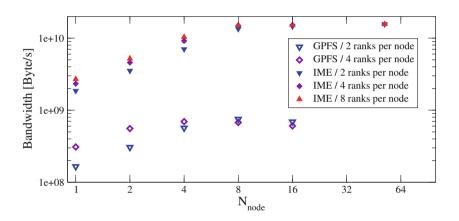

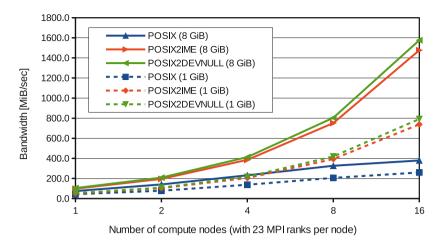

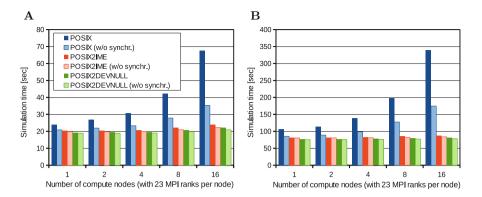

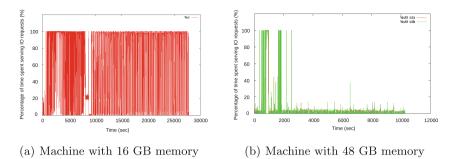

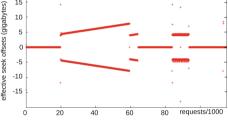

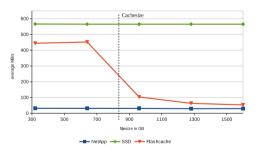

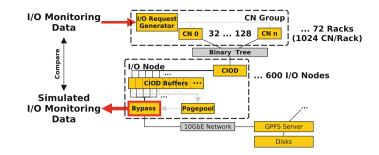

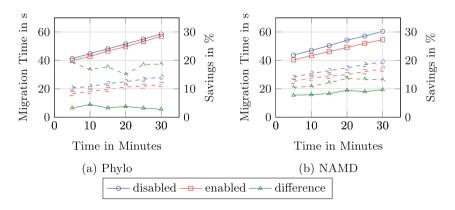

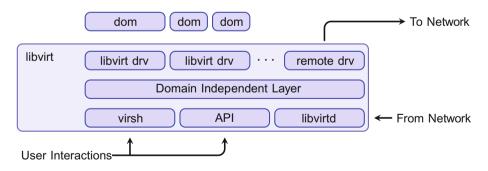

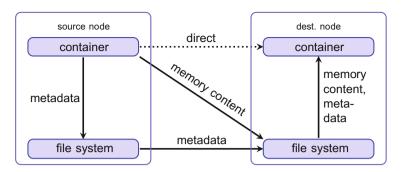

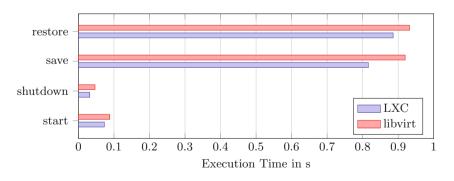

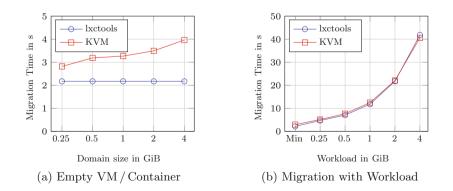

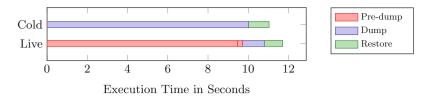

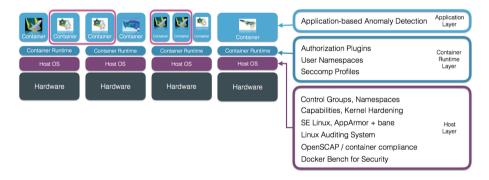

- Lawande, A.G., George, A.D., Lam, H.: Novo-g#: a multidimensional torus-based reconfigurable cluster for molecular dynamics. Concurrency Comput. Pract. Experience 28, 2374–2393 (2015)