Swarat Chaudhuri Azadeh Farzan (Eds.)

# LNCS 9780

# **Computer Aided Verification**

28th International Conference, CAV 2016 Toronto, ON, Canada, July 17–23, 2016 Proceedings, Part II

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zürich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7407

Swarat Chaudhuri · Azadeh Farzan (Eds.)

# Computer Aided Verification

28th International Conference, CAV 2016 Toronto, ON, Canada, July 17–23, 2016 Proceedings, Part II

*Editors* Swarat Chaudhuri Rice University Houston, TX USA

Azadeh Farzan University of Toronto Toronto, ON Canada

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-41539-0 ISBN 978-3-319-41540-6 (eBook) DOI 10.1007/978-3-319-41540-6

Library of Congress Control Number: 2015943799

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG Switzerland

# Preface

It is our pleasure to welcome you to the proceedings of CAV 2016, the 28th International Conference on Computer-Aided Verification, held in Toronto, Ontario, during July 17–23, 2016.

The CAV conference series is dedicated to the advancement of the theory and practice of computer-aided formal analysis of hardware and software systems. The conference covers the spectrum from theoretical results to concrete applications, with an emphasis on practical verification tools and the algorithms and techniques that are needed for their implementation. CAV considers it vital to continue spurring advances in hardware and software verification while expanding to new domains such as biological systems and computer security.

The CAV 2016 program included four invited keynote talks, four invited tutorials, 58 technical papers (consisting of 46 regular papers and 12 tool papers) accepted out of 195 submissions, and briefings from the SYNTCOMP and SYGUS synthesis competitions. The conference was accompanied by six co-located events: VSTTE (Verified Software: Theories, Tools, and Experiments), NSV (Numerical Software Verification), SYNT (Synthesis), EC<sup>2</sup> (Exploiting Concurrency Efficiently and Correctly), HCCV (High-Consequence Control Verification), and VMW (Verification Mentoring Workshop).

Our invited keynote speakers were Gilles Barthe (IMDEA Software Institute), Gerwin Klein (NICTA and University of New South Wales), and Moshe Vardi (Rice University). Parosh Aziz Abdulla (Uppsala University), Vitaly Chipounov (EPFL), Paulo Tabuada (UCLA), and Martin Vechev (ETH Zurich) gave invited tutorials.

We introduced three significant changes to CAV's review process this year. First, CAV 2016 employed a lightweight double-blind reviewing process. This meant that committee members did not have access to the names and affiliations of the authors as they reviewed a paper, and were able to produce an unbiased initial review. However, author names were revealed late in the online discussion process to permit calibration against the authors' prior work. Second, we introduced an External Review Committee, consisting of reviewers committed to producing four to five reviews, and also increased the size of the main Program Committee. These changes significantly reduced the number of papers that a committee had to review. Third, CAV 2016 had a two-phase evaluation process. Each paper received three reviews by the end of the first phase; considering the reviews and accounting for feedback from the reviewers, we solicited up to two additional reviews for papers for which consensus did not exist or further expertise was considered necessary.

Many people worked hard to make CAV 2016 a success. We thank the authors and the invited speakers for providing the excellent technical material, the Program Committee and the External Review Committee for their thorough reviews and the time spent on evaluating all the submissions and discussing them during the online discussion period, and the Steering Committee for their guidance.

We thank Pavol Černý, Sponsorship Chair, for helping to bring much-needed financial support to the conference; Zachary Kincaid, Workshop Chair, and all the organizers of the co-located events for bringing their events to the CAV week; Roopsha Samanta, Publicity Chair, for diligently publicizing the event; and Aws Albarghouthi, Artifact Evaluation Chair, and the Artifact Evaluation Committee for their work on evaluating the artifacts submitted. We gratefully acknowledge NSF for providing financial support for student participants. We sincerely thank the sponsors of CAV 2016 for their generous contributions.

We also thank the University of Toronto and Rice University for their support. Finally, we hope you find the proceedings of CAV 2016 intellectually stimulating and practically valuable.

July 2016

Swarat Chaudhuri Azadeh Farzan

# Organization

#### **Program Committee**

Rajeev Alur Christel Baier Clark Barrett Roderick Bloem Pavol Cerny Adam Chlipala Swarat Chaudhuri Alessandro Cimatti Loris D'Antoni Constantin Enea Javier Esparza Kousha Etessami Azadeh Farzan Susanne Graf Orna Grumberg Franjo Ivancic Somesh Jha Raniit Jhala Joost-Pieter Katoen Zachary Kincaid Laura Kovacs Viktor Kuncak Marta Kwiatkowska Shuvendu Lahiri Akash Lal Pete Manolios Kenneth McMillan David Monniaux Kedar Namjoshi David Parker Corina Pasareanu Ruzica Piskac Andreas Podelski Shaz Qadeer Andrey Rybalchenko Mooly Sagiv Sriram Sankaranarayanan

University of Pennsylvania, USA Technische Universität Dresden, Germany New York University, USA Graz University of Technology, Austria University of Colorado, Boulder, USA MIT, USA Rice University, Houston, USA Fondazione Bruno Kessler, Italy University of Wisconsin, Madison, USA University of Paris Diderot (Paris 7), France Technische Universität München, Germany University of Edinburgh, UK University of Toronto, Toronto, Canada VERIMAG. France Technion, Israel Google, USA University of Wisconsin, Madison, USA University of California, San Diego, USA **RWTH** Aachen University, Germany University of Toronto, Canada Chalmers University of Technology, Sweden EPFL, Switzerland Oxford University, UK Microsoft Research, Redmond, USA Microsoft Research, Bangalore, India Northeastern University, USA Microsoft Research, Redmond, USA VERIMAG. France Bell Labs, Alcatel-Lucent, USA University of Birmingham, UK Carnegie Mellon Silicon Valley; NASA Ames, USA Yale University, USA University of Freiburg, Germany Microsoft Research, Redmond, USA Microsoft Research, Cambridge, UK Tel Aviv University, Israel University of Colorado, Boulder, USA

| Sanjit Seshia      | University of California, Berkeley, USA       |

|--------------------|-----------------------------------------------|

| Natasha Sharygina  | University of Lugano, Switzerland             |

| Sharon Shoham      | Academic College of Tel Aviv-Yaffo, Israel    |

| Fabio Somenzi      | University of Colorado, Boulder, USA          |

| Serdar Tasiran     | Koç University, Turkey                        |

| Mahesh Viswanathan | University of Illinois, Urbana-Champaign, USA |

| Bow-Yaw Wang       | Academia Sinica, Taiwan                       |

| Thomas Wies        | New York University, USA                      |

| Lenore Zuck        | University of Illinois, Chicago, USA          |

|                    |                                               |

# **External Review Committee**

| Aws Albarghouthi         | University of Wisconsin, Madison, USA              |

|--------------------------|----------------------------------------------------|

| Jade Alglave             | Microsoft Research Cambridge; University College   |

|                          | London, UK                                         |

| Sagar Chaki              | Software Engineering Institute, Carnegie Mellon    |

|                          | University, USA                                    |

| Hana Chockler            | King's College London, UK                          |

| Byron Cook               | University College London; Amazon, UK              |

| Deepak D'Souza           | Indian Institute of Science, India                 |

| Thao Dang                | CNRS, France                                       |

| Cezara Dragoi            | Inria, France                                      |

| Pierre Ganty             | IMDEA, Spain                                       |

| Ganesh Gopalakrishnan    | University of Utah, USA                            |

| Arie Gurfinkel           | Software Engineering Institute, Carnegie Mellon    |

|                          | University, USA                                    |

| Jan Hoffmann             | Carnegie Mellon University, USA                    |

| William Hung             | Synopsys, USA                                      |

| Joxan Jaffer             | National University of Singapore                   |

| Naoki Kobayashi          | University of Tokyo, Japan                         |

| Igor Konnov              | Vienna University of Technology, Austria           |

| Hillel Kugler            | Bar-Ilan University, Israel                        |

| Rupak Majumdar           | Max Planck Institute for Software Systems, Germany |

| Sayan Mitra              | University of Illinois at Urbana Champaign, USA    |

| Peter Mueller            | ETH Zurich, Switzerland                            |

| Tim Nelson               | Brown University, USA                              |

| Jan Otop                 | University of Wroclaw, Poland                      |

| Gennaro Parlato          | University of Southampton, UK                      |

| Madhusudan Parthasarathy | University of Illinois at Urbana Champaign, USA    |

| Doron Peled              | Bar Ilan University, Israel                        |

| Pavithra Prabhakar       | Kansas State University, USA                       |

| Arjun Radhakrishna       | University of Pennsylvania, USA                    |

| Zvonimir Rakamaric       | University of Utah, USA                            |

| Nishant Sinha            | IBM Research, Bangalore, India                     |

| Ana Sokolova             | University of Salzburg, Austria                    |

| Armando Solar-Lezama     | MIT, USA                                           |

| Viktor Vafeiadis | Max Planck Institute for Software Systems, Germany |

|------------------|----------------------------------------------------|

| Martin Vechev    | ETH Zurich, Switzerland                            |

| Willem Visser    | Stellenbosch University, South Africa              |

| Tomas Vojnar     | Brno University of Technology, Czech Republic      |

| Thomas Wahl      | Northeastern University, USA                       |

| Eran Yahav       | Technion, Israel                                   |

| Karen Yorav      | IBM Haifa Research Lab, Israel                     |

| Florian Zuleger  | Vienna University of Technology, Austria           |

|                  |                                                    |

# **Additional Reviewers**

| Houssam Abbas<br>Stavros Aronis<br>Amir Ben-Amram<br>Dirk Beyer<br>Armin Biere<br>David Binkley<br>James Brotherston<br>Domenico Cantone<br>Ernie Cohen<br>Sylvain Conchon<br>Chris Hawblitzel | University of Pennsylvania, USA<br>Uppsala University, Sweden<br>The Academic College of Tel Aviv-Yaffo, Israel<br>University of Passau, Germany<br>Johannes Kepler University, Austria<br>Loyola University, USA<br>University College London, UK<br>University of Catania, Italy<br>Amazon, USA<br>LRI, Univesité Paris-Sud 11, France<br>Microsoft Research, Redmond, USA |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                              |

| Ernie Cohen                                                                                                                                                                                    | Amazon, USA                                                                                                                                                                                                                                                                                                                                                                  |

| Sylvain Conchon                                                                                                                                                                                | LRI, Univesité Paris-Sud 11, France                                                                                                                                                                                                                                                                                                                                          |

| Chris Hawblitzel                                                                                                                                                                               | Microsoft Research, Redmond, USA                                                                                                                                                                                                                                                                                                                                             |

| Jean-François Raskin                                                                                                                                                                           | Université Libre de Bruxelles, Belgium                                                                                                                                                                                                                                                                                                                                       |

| Antoine Miné                                                                                                                                                                                   | UPMC University, France                                                                                                                                                                                                                                                                                                                                                      |

| Anders Møller                                                                                                                                                                                  | Aarhus University, Denmark                                                                                                                                                                                                                                                                                                                                                   |

| Andrew Reynolds                                                                                                                                                                                | University of Iowa, USA                                                                                                                                                                                                                                                                                                                                                      |

| Ulrich Schmid                                                                                                                                                                                  | Vienna University of Technology, Austria                                                                                                                                                                                                                                                                                                                                     |

| Margus Veanes                                                                                                                                                                                  | Microsoft Research, Redmond, USA                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                              |

# **Contents – Part II**

# Verification in Practice

| Model Checking at Scale: Automated Air Traffic Control Design                                                                                                                                                                       | 2   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Space Exploration                                                                                                                                                                                                                   | 3   |

| Investigating Safety of a Radiotherapy Machine Using System Models with<br>Pluggable Checkers<br>Stuart Pernsteiner, Calvin Loncaric, Emina Torlak, Zachary Tatlock,<br>Xi Wang, Michael D. Ernst, and Jonathan Jacky               | 23  |

| End-to-End Verification of ARM <sup>®</sup> Processors with ISA-Formal<br>Alastair Reid, Rick Chen, Anastasios Deligiannis, David Gilday,<br>David Hoyes, Will Keen, Ashan Pathirane, Owen Shepherd,<br>Peter Vrabel, and Ali Zaidi | 42  |

| A Practical Verification Framework for Preemptive OS Kernels<br>Fengwei Xu, Ming Fu, Xinyu Feng, Xiaoran Zhang, Hui Zhang,<br>and Zhaohui Li                                                                                        | 59  |

| Probabilistic Automated Language Learning for Configuration Files<br>Mark Santolucito, Ennan Zhai, and Ruzica Piskac                                                                                                                | 80  |

| Concurrency                                                                                                                                                                                                                         |     |

| The Commutativity Problem of the MapReduce Framework:<br>A Transducer-Based Approach                                                                                                                                                | 91  |

| Liveness of Randomised Parameterised Systems under Arbitrary Schedulers<br>Anthony W. Lin and Philipp Rümmer                                                                                                                        | 112 |

| Stateless Model Checking for POWER<br>Parosh Aziz Abdulla, Mohamed Faouzi Atig, Bengt Jonsson,<br>and Carl Leonardsson                                                                                                              | 134 |

| Hitting Families of Schedules for Asynchronous Programs<br>Dmitry Chistikov, Rupak Majumdar, and Filip Niksic                                                                                                                       | 157 |

| ParCoSS: Efficient Parallelized Compiled Symbolic Simulation                                                                                                                                                                        | 177 |

# **Constraint Solving II**

| XSat: A Fast Floating-Point Satisfiability Solver                                                                                        | 187 |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Effectively Propositional Interpolants<br>Samuel Drews and Aws Albarghouthi                                                              | 210 |

| Array Folds Logic<br>Przemysław Daca, Thomas A. Henzinger, and Andrey Kupriyanov                                                         | 230 |

| Automata and Games                                                                                                                       |     |

| Compositional Synthesis of Reactive Controllers for Multi-agent Systems<br><i>Rajeev Alur, Salar Moarref, and Ufuk Topcu</i>             | 251 |

| Solving Parity Games via Priority Promotion                                                                                              | 270 |

| A Simple Algorithm for Solving Qualitative Probabilistic Parity Games<br>Ernst Moritz Hahn, Sven Schewe, Andrea Turrini, and Lijun Zhang | 291 |

| Limit-Deterministic Büchi Automata for Linear Temporal Logic                                                                             | 312 |

| Slugs: Extensible GR(1) Synthesis<br>Rüdiger Ehlers and Vasumathi Raman                                                                  | 333 |

| Synthesis II                                                                                                                             |     |

| Synthesis of Fault-Attack Countermeasures for Cryptographic Circuits<br>Hassan Eldib, Meng Wu, and Chao Wang                             | 343 |

| A SAT-Based Counterexample Guided Method for Unbounded Synthesis<br>Alexander Legg, Nina Narodytska, and Leonid Ryzhyk                   | 364 |

| QLOSE: Program Repair with Quantitative Objectives<br>Loris D'Antoni, Roopsha Samanta, and Rishabh Singh                                 | 383 |

| BDD-Based Boolean Functional Synthesis<br>Dror Fried, Lucas M. Tabajara, and Moshe Y. Vardi                                              | 402 |

| Soufflé: On Synthesis of Program Analyzers         | 422 |

|----------------------------------------------------|-----|

| Herbert Jordan, Bernhard Scholz, and Pavle Subotić |     |

# Model Checking II

| Property Directed Equivalence via Abstract Simulation<br>Grigory Fedyukovich, Arie Gurfinkel, and Natasha Sharygina                         | 433 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

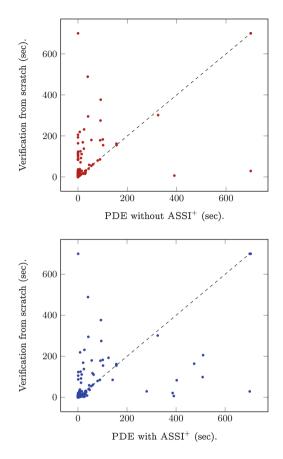

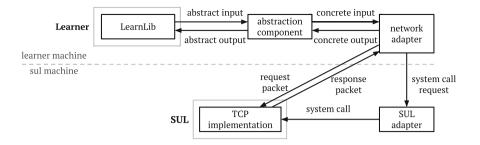

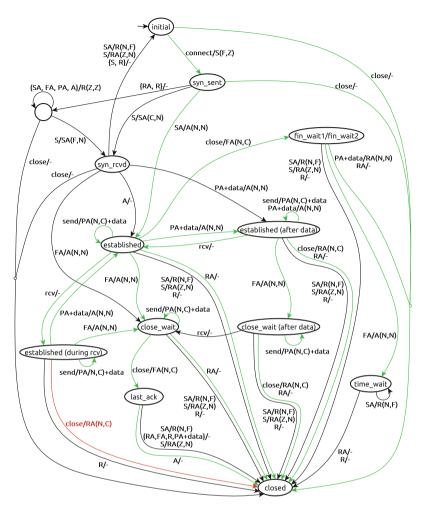

| Combining Model Learning and Model Checking to Analyze<br>TCP Implementations<br>Paul Fiterău-Broștean, Ramon Janssen, and Frits Vaandrager | 454 |

| BFS-Based Model Checking of Linear-Time Properties<br>with an Application on GPUs<br>Anton Wijs                                             | 472 |

| BigraphER: Rewriting and Analysis Engine for Bigraphs                                                                                       | 494 |

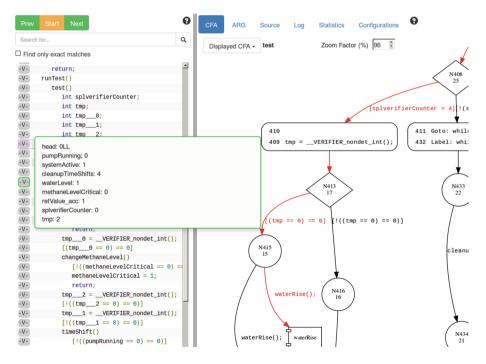

| Verification-Aided Debugging: An Interactive Web-Service<br>for Exploring Error Witnesses<br>Dirk Beyer and Matthias Dangl                  | 502 |

| The KIND 2 Model Checker Adrien Champion, Alain Mebsout, Christoph Sticksel, and Cesare Tinelli                                             | 510 |

| Author Index                                                                                                                                | 519 |

# **Contents – Part I**

# **Probabilistic Systems**

| Termination Analysis of Probabilistic Programs Through<br>Positivstellensatz's                                                                       | 3   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Krishnendu Chatterjee, Hongfei Fu, and Amir Kafshdar Goharshady                                                                                      |     |

| Markov Chains and Unambiguous Büchi Automata<br>Christel Baier, Stefan Kiefer, Joachim Klein, Sascha Klüppelholz,<br>David Müller, and James Worrell | 23  |

| Synthesizing Probabilistic Invariants via Doob's Decomposition Gilles Barthe, Thomas Espitau, Luis María Ferrer Fioriti, and Justin Hsu              | 43  |

| PSI: Exact Symbolic Inference for Probabilistic Programs<br>Timon Gehr, Sasa Misailovic, and Martin Vechev                                           | 62  |

| PSCV: A Runtime Verification Tool for Probabilistic SystemC Models Van Chan Ngo, Axel Legay, and Vania Joloboff                                      | 84  |

| Synthesis I                                                                                                                                          |     |

| Structural Synthesis for GXW Specifications<br>Chih-Hong Cheng, Yassine Hamza, and Harald Ruess                                                      | 95  |

| Bounded Cycle Synthesis<br>Bernd Finkbeiner and Felix Klein                                                                                          | 118 |

| Fast, Flexible, and Minimal CTL Synthesis via SMT<br>Tobias Klenze, Sam Bayless, and Alan J. Hu                                                      | 136 |

| Synthesis of Self-Stabilising and Byzantine-Resilient Distributed Systems Roderick Bloem, Nicolas Braud-Santoni, and Swen Jacobs                     | 157 |

| Constraint Solving I                                                                                                                                 |     |

| A Decision Procedure for Sets, Binary Relations and Partial Functions<br>Maximiliano Cristiá and Gianfranco Rossi                                    | 179 |

| Precise and Complete Propagation Based Local Search for Satisfiability<br>Modulo Theories                                                            | 199 |

|                                                                                                                                                      |     |

| Progressive Reasoning over Recursively-Defined Strings                                                                                                                                         | 218  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

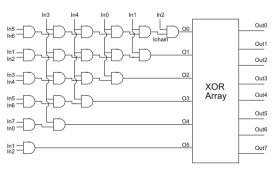

| String Analysis via Automata Manipulation with Logic Circuit<br>Representation                                                                                                                 | 241  |

| RAHFT: A Tool for Verifying Horn Clauses Using Abstract Interpretation<br>and Finite Tree Automata                                                                                             | 261  |

| Model Checking I                                                                                                                                                                               |      |

| Infinite-State Liveness-to-Safety via Implicit Abstraction<br>and Well-Founded Relations<br>Jakub Daniel, Alessandro Cimatti, Alberto Griggio, Stefano Tonetta,<br>and Sergio Mover            | 271  |

| Proving Parameterized Systems Safe by Generalizing Clausal Proofs of<br>Small Instances<br>Michael Dooley and Fabio Somenzi                                                                    | 292  |

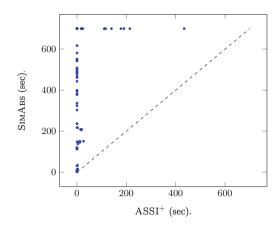

| Learning-Based Assume-Guarantee Regression Verification<br>Fei He, Shu Mao, and Bow-Yaw Wang                                                                                                   | 310  |

| Automated Circular Assume-Guarantee Reasoning with N-way<br>Decomposition and Alphabet Refinement<br><i>Karam Abd Elkader, Orna Grumberg, Corina S. Păsăreanu,</i><br><i>and Sharon Shoham</i> | 329  |

| JayHorn: A Framework for Verifying Java programs<br>Temesghen Kahsai, Philipp Rümmer, Huascar Sanchez,<br>and Martin Schäf                                                                     | 352  |

| Program Analysis                                                                                                                                                                               |      |

| Trigger Selection Strategies to Stabilize Program Verifiers                                                                                                                                    | 361  |

| Satisfiability Modulo Heap-Based Programs                                                                                                                                                      | 382  |

| Automatic Verification of Iterated Separating Conjunctions Using                                                                                                                               | 40.7 |

| Symbolic Execution                                                                                                                                                                             | 405  |

| From Shape Analysis to Termination Analysis in Linear Time<br>Roman Manevich, Boris Dogadov, and Noam Rinetzky                                                    | 426 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| RV-Match: Practical Semantics-Based Program Analysis<br>Dwight Guth, Chris Hathhorn, Manasvi Saxena, and Grigore Roşu                                             | 447 |

| Timed and Hybrid Systems                                                                                                                                          |     |

| Under-Approximating Backward Reachable Sets by Polytopes<br>Bai Xue, Zhikun She, and Arvind Easwaran                                                              | 457 |

| Parsimonious, Simulation Based Verification of Linear Systems<br>Parasara Sridhar Duggirala and Mahesh Viswanathan                                                | 477 |

| Counterexample Guided Abstraction Refinement for Stability Analysis<br>Pavithra Prabhakar and Miriam García Soto                                                  | 495 |

| Symbolic Optimal Reachability in Weighted Timed Automata<br>Patricia Bouyer, Maximilien Colange, and Nicolas Markey                                               | 513 |

| Automatic Reachability Analysis for Nonlinear Hybrid Models with C2E2<br>Chuchu Fan, Bolun Qi, Sayan Mitra, Mahesh Viswanathan,<br>and Parasara Sridhar Duggirala | 531 |

| Author Index                                                                                                                                                      | 539 |

# **Verification in Practice**

# Model Checking at Scale: Automated Air Traffic Control Design Space Exploration

Marco Gario<sup>1(⊠)</sup>, Alessandro Cimatti<sup>1</sup>, Cristian Mattarei<sup>1</sup>, Stefano Tonetta<sup>1</sup>, and Kristin Yvonne Rozier<sup>2(⊠)</sup>

> <sup>1</sup> Fondazione Bruno Kessler, Trento, Italy {gario,cimatti,mattarei,tonettas}@fbk.eu <sup>2</sup> Iowa State University, Ames, IA, USA kyrozier@iastate.edu

**Abstract.** Many possible solutions, differing in the assumptions and implementations of the components in use, are usually in competition during early design stages. Deciding which solution to adopt requires considering several trade-offs. Model checking represents a possible way of comparing such designs, however, when the number of designs is large, building and validating so many models may be intractable.

During our collaboration with NASA, we faced the challenge of considering a design space with more than 20,000 designs for the NextGen air traffic control system. To deal with this problem, we introduce a compositional, modular, parameterized approach combining model checking with contract-based design to automatically generate large numbers of models from a possible set of components and their implementations. Our approach is fully automated, enabling the generation and validation of all target designs. The 1,620 designs that were most relevant to NASA were analyzed exhaustively. To deal with the massive amount of data generated, we apply novel data-analysis techniques that enable a rich comparison of the designs, including safety aspects. Our results were validated by NASA system designers, and helped to identify novel as well as known problematic configurations.

#### 1 Introduction

When multiple system design configurations are possible, there is a need to map the design space in order to understand the big picture, and be able to demonstrate the impact of design choices, such as different combinations of potential subcomponents with different features, on the overall functionality and safety of the system. Safety assessment of complex and critical systems can clearly benefit from the use of formal methods techniques [14, 15, 20, 22, 24, 27–31, 34], but a large space of possible designs presents major challenges for model-checking analysis,

Thanks to the Flight Trajectory Dynamics and Controls Branch of NASA Ames Research Center, NASA's Functional Allocation Project, and NSF CAREER Award CNS-1552934 for supporting this work. All models and specifications are available at https://es-static.fbk.eu/projects/nasa-aac/.

<sup>©</sup> Springer International Publishing Switzerland 2016

S. Chaudhuri and A. Farzan (Eds.): CAV 2016, Part II, LNCS 9780, pp. 3–22, 2016. DOI: 10.1007/978-3-319-41540-6\_1

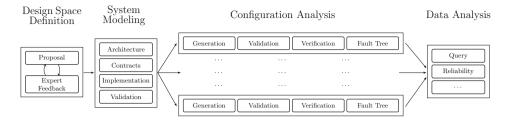

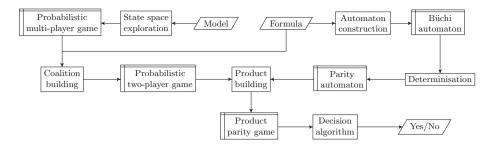

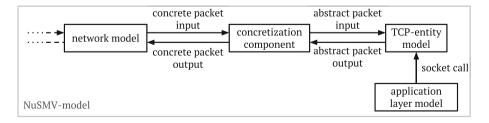

Fig. 1. Process overview

including producing models of each design, cross-design validation, and comparative safety analysis across the large design space. We address these challenges, exemplifying our methodology on NASA's full-scale design space for NextGen air traffic control, in which there are many ways to allocate essential functions such as aircraft separation assurance [26], and competing possible implementations of the same components. The U.S. government made NASA primarily responsible for the design and verification of NextGen air traffic control [2,3]. The new air traffic management system is expected to be in place for decades to come [5] so we must evaluate the design space thoroughly to ensure that we guarantee safety while allowing optimization for important secondary considerations. The importance of early-design stage optimization carries to many classes of critical or long-lived projects, including commercial aircraft and space missions, where the need to change the design later in the system development process would be extremely difficult, and very costly.

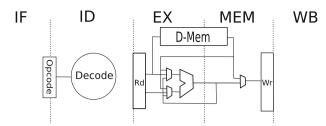

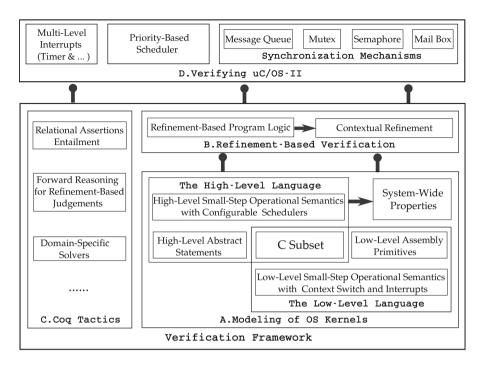

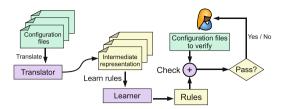

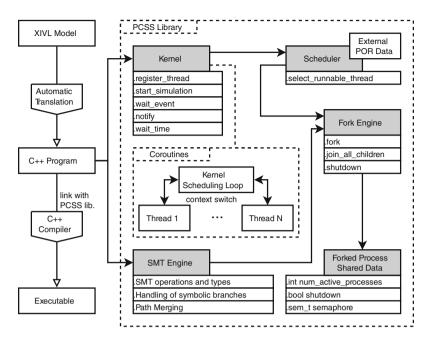

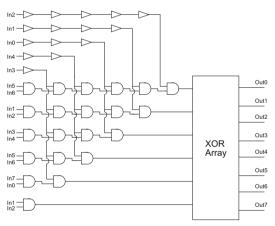

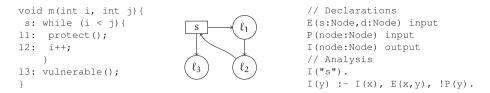

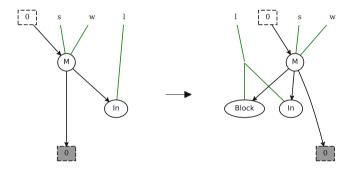

In this paper, we discuss the application of model-checking-based techniques to support the exploration of the NextGen design space. This is one of six studies funded within NASA's Functional Allocation Project; it will contribute directly to the final system design. We define a compositional, parameterized modeling framework that can generate more than 20,000 possible designs. In collaboration with NASA Ames and NASA Langley experts, we focus in on the 1,620 that they identified as the most instructive configurations for a comparative analysis. The outcome of this analysis provides significant insights into the features of the various configurations. In order to tackle the huge design space, we develop a new process that relies on multiple tools. The activities, depicted in Fig. 1, can be summarized in four main phases: *Design Space Definition, System Modeling, Configuration Analysis*, and *Data Analysis*.

Design Space Definition. The stage was set by working with NASA in order to identify precisely (yet informally [26]) the situations of interest, and by defining the modeling dimensions to capture them.

System Modeling. Modeling each solution independently would be too timeconsuming (if not outright unfeasible). Plus each model needs to be properly validated to ensure that it upholds the expected properties. Furthermore, independent models would require a lot of maintenance effort to propagate changes and ensure that they are all aligned with NASA's most current designs. We can manage these sources of complexity by combining several ingredients. First, we use an architectural language (i.e., OCRA [17]) to separate the system architecture from the implementation of the single components (obtained as SMV [16] models). This allows us to model each component in isolation, partitioning the effort, and minimizing the time required to validate changes in any component. Additionally, this permits changes to the implementation of a single component without impacting the rest of the system. Second, we use contracts (encoded in OCRA as LTL formulas) to characterize each component. This allows us to properly specify the interactions between components, and decompose the validation properties into more localized subcomponent properties. Third, we use parameters to factor out multiple configurations into a single (although more complex) model. If two configurations require only marginal changes to an implementation, we capture these changes using parameters within the models. These techniques allow us to automatically generate a formal representation for each configuration in the design space, with great confidence in their correctness and alignment.

Configuration Analysis. We verify each model against the properties of interest; in addition, techniques for safety assessment identify which combinations of faults lead to the violation of fundamental properties. The corresponding Fault Trees are automatically computed (using xSAP [10]), thus providing additional information on the reliability of each configuration. We instantiate and analyze each configuration independently, exploiting the typical parallelism of modern computing infrastructures, thus significantly speeding up the analysis.

Data Analysis. Such analysis results in a significant amount of data, and poses the problem of how to analyze it. We combine this data into a symbolically represented dataset, linking each configuration to its satisfied properties and Fault Trees. This dataset is particularly useful in such an exploratory phase, since it describes the whole design space and can be studied offline. For example, by automatically extracting sets of configurations enjoying specific properties (e.g., absence of single points of failure), it is possible to achieve a better understanding of the design space. Our focused analysis of NASA's air traffic control design space confirmed expected results [23,25] as well as identifying novel ones. In particular, we highlighted the need for additional assumptions when dealing with changes in delegation of separation assurance from an aircraft to the ground, e.g., in case of a request for backup.

The contribution of this paper is twofold. First, we develop a complex and realistic case study of public relevance, and make models, tools, and results publicly available for future investigation (at [4]). This is no ordinary case study, and to be able to handle the massive size, we need to exploit a novel process that is our second contribution. Our process is able to scale to address a large design space exploration problem. The process builds on existing tools and techniques and adds a novel data analysis phase that is necessary to obtain insights from the large amount of generated artifacts. We show that this technology is mature and able to assist designers in formalizing and narrowing down design choices in an early phase of system design.

The rest of the paper is structured according to the process described above (Fig. 1). Sections 2 to 5 illustrate each phase of the process in greater detail. Related works are discussed in Sects. 6 and 7 concludes with possible directions for future work.

### 2 Design Space Definition

The main objective of an air traffic control system is to avoid aircraft collisions. In air traffic management, a Loss of Separation (LOS) between two aircraft occurs when they are predicted to pass too close to each other. One of the major goals of the next generation of air traffic control is to minimize the number of times that a LOS ever occurs. This task is called *Separation Assurance*. In this case study, we are interested in studying the separation assurance provided by different designs when splitting the functionality between components on-board airplanes and on-ground. In particular, aircraft that always rely on the ground for separation assurance are called Ground Separated (GSEP), while aircraft with on-board separation assurance capabilities are called Self-Separating (SSEP). The main distinction between the two types of aircraft is the ability of SSEP to perform self-separation, without the need for approval from ground control. The goal of distributing the responsibility for separation assurance across different components is to increase efficiency and improve fault tolerance.

Our work started by considering several proposals from NASA's *Flight Dynamics, Trajectory, and Controls* Branch for different solutions regarding Function Allocation for Separation Assurance [26]. These ideas were the result of considering several features and characteristics in a preliminary phase.

Our first step was to identify and formalize the dimensions shared by different proposals, and this allowed us to define the design space. In order to model the airspace and its dynamics, we track each aircraft's intended trajectory through four different time-windows: Current, Near, Mid, and Far. These indicate increasingly distant points in time. For each window, we encode the intended position of the aircraft. However, since we are only interested in whether two aircraft can potentially be in a conflict, we simplify this information. For a given timewindow, we say that two aircraft are in the same Conflict Area (CA) iff their trajectories are too close to each other and would cause a Loss of Separation. We say that two aircraft are in LOS *iff* they are in the same conflict area in the Current time-window. If two aircraft are in the same CA in another window, we say that they have a *predicted* LOS. These abstractions make it possible to focus on the other modeling dimensions: what information the different agents share, how they behave in case of predicted LOS, and the impacts of the actions of each agent on the overall system. Contrary to previous works (e.g., [28]), we consider more complex interactions between separation agents, components with

multiple implementations, and priorities in case of predicted LOS. We derived six modeling dimensions that enable us to capture these different trade-offs:

- 1. SSEP Separation Agent

- 2. Aircraft Mix

- 3. Information Sharing

- 4. Burdening Rules

- 5. Communication Steps

- 6. ACDR (Airborne Conflict Detection and Resolution) Implementations.

SSEP Separation Agent. A key difference between the solutions is who is responsible for performing separation for the SSEPs. We split this task into separation for the Tactical (Near- and Mid-) and Strategic (Far-) windows. For each of these windows we define who is in charge of separating the SSEPs: the ground (ATC), the aircraft (SELF), or the aircraft with possible delegation to ground (SATC). If the ground ATC is in charge of separating the SSEPs, then it computes the resolutions and sends them to the aircraft. If the aircraft is in charge of its own separation, computation of a resolution strategy happens on-board, possibly involving coordination between aircraft. The third case (SATC) captures the possibility for an SSEP to delegate its own separation to the ground. This is used to capture different situations such as backup in case of a fault, privileged traffic corridors, and transfer of responsibility in designated airspace regions. In the future, we expect other cases to be studied. For example, resolutions might be computed on-board but require approval from ground.

Aircraft Mix. We consider situations in which all aircraft are of the same type, and also where mixed types coexist. The same design can be analyzed without SSEPs, with an even number of GSEPs and SSEPs, without GSEPs, or any option in-between. Each combination is indicated by the number of GSEPs and SSEPs, i.e.,  $\langle \#GSEP, \#SSEP \rangle$ .

Burdening Rules. A priority must be defined in order to address detected conflicts between aircraft of different types. Burdening rules define who should move when such a conflict occurs: (1) Undefined, (2) GSEP, (3) SSEP. For example, if the burden is on the GSEP, then the conflict should be resolved by changing the trajectory of the GSEP. If the burdening rules are undefined, then each agent will arbitrarily choose a burdened strategy, and consistently apply it to every conflict.

Information Sharing. It is important to consider the minimization of required communications, in order to reduce reaction times and system complexity. Therefore, we need to understand what is the minimum amount of intent that aircraft need to share. We make two main distinctions: information sharing from *GSEPs* to *SSEPs* and from *SSEPs* to *ATC*. For each of these two information sharing pipelines, we consider scenarios from sharing no information (*None*) to sharing information concerning just the *Current*-window, up to the *Near*-window, up to the *Mid*-window, or all the windows (*Far*-window).

*Communication Steps.* In some situations, multiple communication rounds might be needed in order to reach an agreement among the parties. However, delays in

| Name                 | Possible                                                                                                                         |        | Considered                                                                                                                       |       |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|-------|

|                      | Values                                                                                                                           | Size   | Values                                                                                                                           | Size  |

| SSEP TS SA           | ATC, SELF, SATC                                                                                                                  | 3      | ATC, SELF, SATC                                                                                                                  | 3     |

| SSEP SS SA           | ATC, SELF, SATC                                                                                                                  | 3      | ATC, SELF, SATC                                                                                                                  | 3     |

| Aircraft mix         | $\begin{array}{l} \langle 4,0\rangle,\langle 3,1\rangle,\langle 2,2\rangle,\\ \langle 1,3\rangle,\langle 0,4\rangle \end{array}$ | 5      | $\begin{array}{l} \langle 4,0\rangle,\langle 3,1\rangle,\langle 2,2\rangle,\\ \langle 1,3\rangle,\langle 0,4\rangle \end{array}$ | 5     |

| Burdening rules      | Undef, GSEP, SSEP                                                                                                                | 3      | Undef, GSEP, SSEP                                                                                                                | 3     |

| GSEPs to SSEPs info  | None, Current,<br>Near, Mid, Far                                                                                                 | 5      | Current, Far                                                                                                                     | 2     |

| SSEPs to ATC info    | None, Current,<br>Near, Mid, Far                                                                                                 | 5      | Far                                                                                                                              | 1     |

| Com steps            | 1, 2,                                                                                                                            | 2      | 1, 2                                                                                                                             | 2     |

| ACDR implementations | Simple, Asymmetric,<br>Non-receptive                                                                                             | 3      | Simple, Asymmetric,<br>Non-receptive                                                                                             | 3     |

| TOTAL                |                                                                                                                                  | 20,250 |                                                                                                                                  | 1,620 |

Table 1. Summary of possible and considered design dimensions (difference in size is highlighted in bold)

communication and availability of the networks make it necessary to minimize the number of communication rounds that need to occur.

ACDR Implementations. We considered different implementations for the Airborne Conflict Detection and Resolution (ACDR) component. The simplest implementation of the ACDR computes a resolution without considering the behavior of the other aircraft ("ACDR Simple"). A more complex implementation instead takes into account how the other SSEPs are going to resolve the conflict, and uses this knowledge to compute a resolution that is guaranteed to solve the current conflict ("ACDR Asymmetric"). Finally, the last implementation (called "ACDR Non-Receptive") is the one in which we declaratively enforce the assumption that conflicts among SSEPs will be resolved without specifying how, thus constraining the environment with a non-receptive specification [6]; this last option is useful to study the system behavior assuming a perfect ACDR.

Table 1 shows the possible dimensions defined during the first analysis, and yields a design space with 20,250 configurations. Though we can scale to automatically generate and analyze this many models, further discussions with NASA domain experts led us to focus our exhaustive analysis on the subset of 1,620 configurations most interesting from the domain point of view. In particular, they decided to fix the information sharing of the SSEPs in order to provide all information (i.e., *Far*) and consider only the two extreme cases for the information shared by the GSEPs: *Current* and *Far*. This reduced the design space to a set of 1,620 configurations (right part of Table 1). These are the configurations analyzed in the rest of the paper.

#### 3 System Modeling

The dimensions described in Table 1 are captured by defining a unified structure including all possible configurations. This structure is equipped with parameters and multiple implementations of the components, making it possible to model the whole system once, and then automatically generate any of the 1,620 possible instances. This reduces the modeling effort that is, in terms of resources, the most expensive part of the process. However, we need to pay particu-

lar attention to the validation of the instantiated models, in order to make sure that all expected behaviors are properly captured.

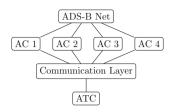

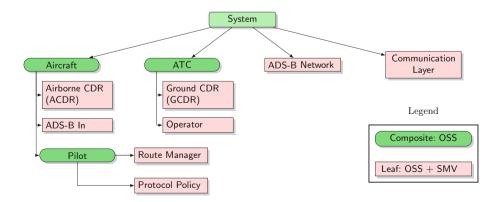

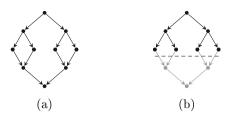

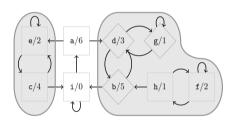

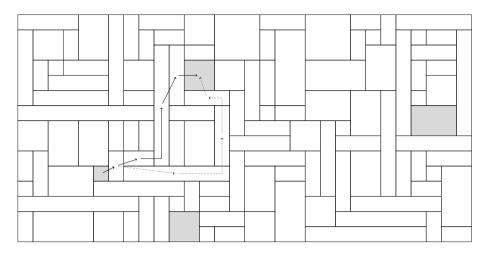

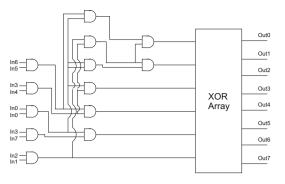

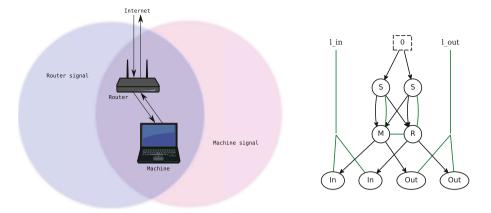

The general structure of the model is shown in Fig. 2, and includes four aircraft, the ATC, and two different types of networks: ADS-B and Communication Layer. ADS-B is used only among the aircraft, while the Communication Layer is used between the aircraft and the ATC. This choice makes it simple to provide different characteristics to the two networks: faults, symmetry, amount of information, delays, etc. We always consider up to four aircraft instances. This is sufficient to capture all combinations of conflicts between aircraft of different types: GSEP-to-SSEP, GSEP-to-GSEP, SSEP-to-SSEP. This abstraction only represents how many aircraft can be in a single conflict at the same time, and does not assume anything about the size of the airspace [34].

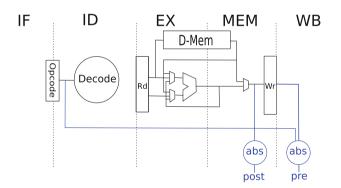

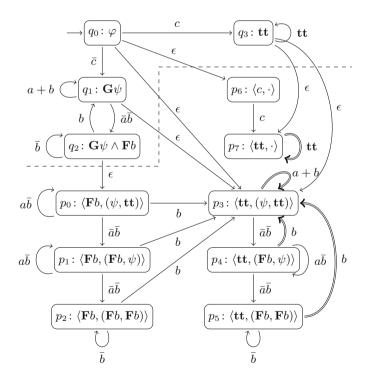

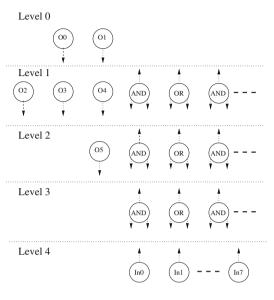

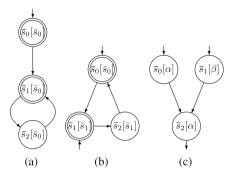

Figure 3 shows the decomposition of the system into a hierarchy of component types, and this provides an architecture that can be incrementally refined. For example, we break down the definition of the Aircraft and ATC components into subcomponents, and this compositional approach allows us to simplify modeling and validation.

Fig. 3. Hierarchical decomposition

We use the Aircraft component (the most complex component) to exemplify our parametric modeling approach. There are two types of aircraft: SSEP and GSEP. Since these two types differ only in few ways, they are modeled as a generic aircraft component whose behavior is selected via a set of parameters, as listed in Table 2. More specifically, we model the *Aircraft* component as having the following parameters: adsb\_in, ts\_agent, ss\_agent, and burdening. The parameters ts\_agent and ss\_agent are used to specify who is in charge of the Tactical Separation (TS) (i.e., Near- and Mid-window) and Strategic Separation (SS) (i.e., Far-window). Similarly, the parameters burdening and adsb\_in capture, respectively, the information about the burdening rule in use and the availability of the ADS-B receiver. Using this parametric model, we can describe a GSEP as an aircraft that is always separated by the ground controller, and that does not have an ADS-B In component:

#### Aircraft(adsb\_in=No, ts\_agent=ATC, ss\_agent=ATC, burdening=GSEP).

The impact of parameter choice is localized to the parameterized subcomponent. For example, the **burdening** parameter has an impact only on the ACDR component. Having components whose implementations are independent of the model's parameters makes it possible to *re-use* these components for multiple configurations. We also use a similar approach for modeling faults in the communication networks, and we localize all of those faults within the network components: ADS-B Network and Communication Layer. As shown in Fig. 3, there are two different components that are used to capture the ADS-B functionality: the ADS-B Network and the ADS-B In component. By separating these (conceptually related) components, we are able to model the aircraft independently of the faults, and the number of aircraft connected to the network. Table 2 provides a summary of the input and output information, and of the parameters for the Aircraft component. In each configuration, we enforce that all GSEPs must have the same parameters, and this applies also for the SSEPs. Therefore, in the same configuration there cannot be two SSEPs with, e.g., two different separation assurance agents. This is not a limitation of the model or tools, but a design choice motivated by the domain that we are exploring and our choice to keep the model more understandable and limit the scope to realistic scenarios.

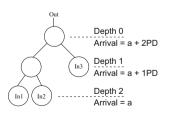

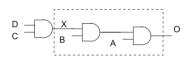

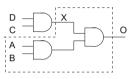

The architecture shown in Figs. 2 and 3 is captured using the OCRA language [17]. Breaking components (e.g., Aircraft) into simpler components simplifies both modeling and validation. In particular, we can write properties about the Aircraft and then decompose them into properties of the subcomponents. This pattern is called *Contract-Based Design*, and it is supported by OCRA using contracts expressed in Linear Temporal Logic (LTL). For example, we write a contract for the Aircraft (Fig. 4) and decompose it into contracts on its subcomponents (see **REFINEDBY** in the Figure). To take advantage of contractbased design we need to perform two steps [18]. First, we need to check that the refinement of the contract is correct. This means that the guarantees provided by the subcomponents in the refinement are sufficient to prove the guarantee of the supercomponent. After performing this step, we know that independently of the choice of parameters, if the implementations of the ACDR and Pilot satisfy

| Type      | Name                                             | Domain                          |  |

|-----------|--------------------------------------------------|---------------------------------|--|

| Parameter | id                                               | [14]                            |  |

|           | adsb_in                                          | Boolean                         |  |

|           | ts_sa_agent                                      | {ATC, SELF, SATC}               |  |

|           | ss_sa_agent                                      | {ATC, SELF, SATC}               |  |

|           | burdening                                        | $\{$ Undefined, GSEP, SSEP $\}$ |  |

| Input     | $suggestion_{near,mid,far}_{ground}$             | Conflict area [04]              |  |

|           | communication_phase                              | Boolean                         |  |

|           | $ac_{1,2,3,4}$ _intention_{current,near,mid,far} | Conflict area $[04]$            |  |

|           | $ac_{1,2,3,4}_{ts,sa}_{agent}$                   | {ATC, SELF, SATC}               |  |

| Output    | $intention_{current,near,mid,far}$               | Conflict area [04]              |  |

|           | $predicted\_conflict_{near,mid,far}$             | Boolean                         |  |

|           | request_{ts,ss}_sa_ground                        | Boolean                         |  |

Table 2. Parameters, Inputs and Outputs of the Aircraft model

their contracts, then also the Aircraft satisfies its contract. As a second step, we verify that the implementations of each component satisfy their contracts. This operation is done locally on the component in isolation and, since most components are relatively small, it can be performed efficiently. Every time we modify a basic component, we only need to validate it against its contracts, and we are guaranteed that the composite components will still satisfy their contracts. This way of using contracts significantly speeds up the design loop. To draw a parallel with software engineering, the contracts that we write are comparable to unit tests in which we focus on the correctness of the component in isolation.

Fig. 4. Example of a contract on the Aircraft component

An added benefit of this process of contract decomposition is that it requires a rigorous understanding of the relationships between the components. This raises interesting questions about how to define the components, how to divide responsibilities, and what behavior can be expected by every component in nominal situations. In fact, we are forced to define requirements that all component implementations must satisfy. In our case, this investigation was supported by a close collaboration with NASA, which resulted for example, in the definition of multiple possible ACDR implementations, and the definition of more than 130 contracts.

# 4 Configuration Analysis

Once the unified model is complete, we proceed to analyze each possible configuration in isolation. For each configuration we break the analysis into the following steps:

- 1. Instance Generation

- 2. Airspace, Nominal, and Extended Validation

- 3. Nominal and Extended Verification

- 4. Fault Tree and Reliability Analysis.

Automation of this phase is very important. Each step is run automatically, from the definition of the instance to the generation of all verification and Fault Tree artifacts. This ensures that the process is reproducible and scalable.

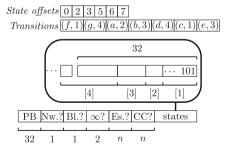

Instance Generation. Each leaf component in our hierarchical architecture is associated with an implementation (a behavioral model defined as an SMV file) by defining a *map* file. The OCRA tool uses this mapping to generate a single monolithic SMV file of the instance. This makes it extremely easy to instantiate the system with multiple functional implementations of the components, and also to create instances with and without faults. We pass parameters through the OCRA architecture using pre-processing instructions to define constants. In this way, the variability of the model is limited to the OCRA architecture and map files used during the generation phase. The outcomes of this phase are three models: *airspace*, *nominal*, and *extended*. These are standard SMV files, without parameters, that can be analyzed by any out-of-the-box technique.

Airspace, Nominal, and Extended Validation. The models for the configuration are generated automatically, therefore, before proceeding to the verification step, we need to gain confidence in the quality of the generated models. For this reason, we perform these additional validation steps.

The *airspace* model captures the system without separation assurance agents. This is the first validation check: the model must allow the occurrence and resolution of LOS. We generated this model by mapping the separation agents to implementations that have no constraints, while using nominal implementations for the aircraft and networks. To certify that the components work correctly together, we verify 18 CTL properties encoding the possibilities of bad and good behaviors, and 24 LTL properties derived from contracts.

The *nominal* model uses a nominal implementation for every component, including separation agents. Unlike the extended model, in this case we do not allow components to fail. We validate this model with 29 LTL properties derived from the contracts of the components.

Finally, the *extended* model uses an implementation for every component that includes faults (95 faults in total, as described in [28]). The validation of the extended model checks that all faults are possible (through 137 CTL possibility properties), and that they respect their dynamics, i.e., permanent or transient, with 29 LTL properties.

Overall, the validation of the 3 models requires a combination of different techniques in order to be effective and be carried out in a limited time. The CTL verification requires a fixpoint-based approach, using BDDs, while for the LTL properties, we use the IC3-based algorithms implemented in nuXmv [16]. Every property is checked against a known result that, if violated, causes the analysis to stop for further investigation.

Nominal and Extended Verification. In this step, we characterize different configurations by verifying additional properties. The most important is whether LOS can always be avoided (NO-LOS), followed by stronger versions: NO-LOS-Near, -Mid, -Far. Other properties provide additional information on the quality of the configuration, e.g., Detect-Near "Every conflict in the Near-window (Mid-, Far- respectively) is detected by at least one Agent." This property is satisfied if the ATC (which is an Agent, in this context) detects a conflict between two aircraft, without either of the aircraft detecting it. It is clear that we can devise stronger versions of this property, and apply them to different time-windows (e.g., Detect-Mid, -Far). This provides a simple way of ranking configurations according to how many and which properties they satisfy. During extended verification, we check instead whether these properties are still satisfied in the presence of faults. For most properties this will not be the case. However, if some property is satisfied even with faults, it means that the property and the faults have no relationship in the given configuration. In this step, we verify 24 LTL and 30 invariant properties on both the nominal and extended models.

Fault Tree and Reliability Analysis. We compute the Fault Tree associated with each safety property in order to understand the resilience of each configuration in the presence of faults. Fault Trees are a standard in safety-critical domains [7, 8,32]. More specifically, we compute the set of minimal cutsets, i.e., all possible faults configurations (called cutsets) that can cause the violation of the given property. These cutsets are minimal because they only include the faults that are necessary to violate the property. Minimal cutsets are computed automatically from the formal model, using the IC3-based technique described in [11] and implemented in xSAP [10]. For each Fault Tree, we also generate a *reliability* function [12]. This function relates the probability of violating the property to the probability of occurrence of each basic fault.

# 5 Data Analysis

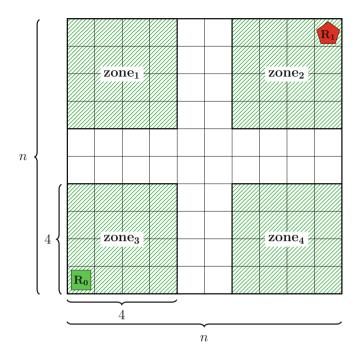

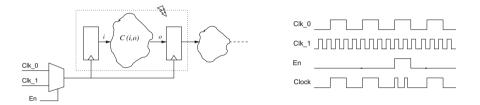

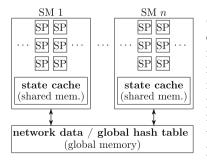

Each configuration can be analyzed independently. We exploit this fact and run the analysis on a cluster with 12 Intel Xeon X5650 processors (72 cores). The average size of the models was  $10^{107}$  states, and each model was checked against 346 properties. The two most difficult steps were those of model validation, due to the need for BDD-based reasoning, and minimal cutset computation, since it requires solving a parameter synthesis problem. These two steps were completed within an hour for most configurations, but for roughly 10% of the models, they required several hours to complete. Verification of the LTL properties was performed using the nuXmv [16] IC3 implementation, requiring roughly 5 min per model.

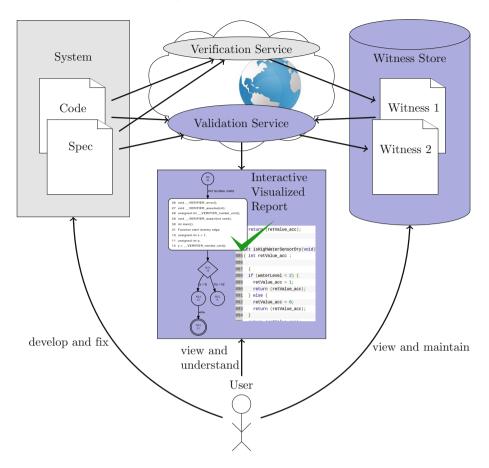

Once all results are available, we can perform the last step of the process: *Data Analysis.* Each configuration provides us with a set of verification results and a set of Fault Trees. Therefore, we face the challenge of how to intuitively represent the information provided by more than 1,600 Fault Trees and verification results. We approached the problem by collecting these artifacts into relations. The first,  $V \subseteq C \times \mathbb{B}^n$ , relates each configuration (i.e., a set of values for the parameters) to the satisfaction of the verification properties. The second,  $FT \subseteq C \times \mathbb{N} \times 2^{MCS}$  instead relates each configuration and property index to the set of minimal cutsets (MCS) associated with it. This data can be queried and manipulated offline, by the domain experts, in order to obtain more insights into the design space.

#### 5.1 Summary of Results

Most of the configurations (Table 3) satisfy the key property of avoiding Loss of Separation (NO-LOS). The fact that NO-LOS-Far is satisfied by some SSEP-Only configurations is due to the non-receptive implementation of the ACDR, which assumes that trajectories are computed in a way that avoids potential conflicts in the Far-window. However, not all configurations using the SSEP-Only ACDR are immune to LOS. For example, when including burdening rules, GSEPs (that do not use the ACDR) can interfere with the SSEPs and lead to a LOS.

|             | GSEP-Only | Mixed | Mixed | Mixed | SSEP-Only | Total |

|-------------|-----------|-------|-------|-------|-----------|-------|

|             | 4-0       | 3-1   | 2-2   | 1-3   | 0-4       |       |

| NO-LOS      | 324       | 244   | 212   | 213   | 258       | 1251  |

| NO-LOS-Near | 324       | 244   | 209   | 210   | 252       | 1239  |

| NO-LOS-Mid  | 324       | 192   | 138   | 141   | 198       | 993   |

| NO-LOS-Far  | 0         | 0     | 0     | 18    | 84        | 102   |

Table 3. Models satisfying NO-LOS for different windows

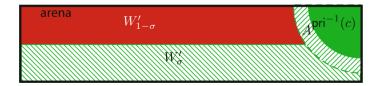

*Prime Implicants.* To extract interesting facts from the verification results, we synthesize the region of parameters that satisfy a property of interest. To compute the region of parameters that satisfy a property, we fix the property value and quantify away the other properties in the relation V. E.g., for NO-LOS we define:

$$NO\_LOS(C) = \exists P_1, \cdots, P_n. V(C, P_1, \cdots, P_n) \land P_{NO\_LOS}$$

where  $P_i$  is a Boolean variable associated with the verification result for property i, and C is the set of configuration variables (i.e., parameters). In this way, we can compute the region of parameters associated with the satisfaction of each property. Very few of these regions have a compact representation. To extract interesting facts from these regions, we compute the *prime implicants* of the region, i.e., the set of minimal elements that are sufficient to enforce the satisfaction of the property. For cardinality 1, we obtain the following implicant for NO-LOS:

$$(MIX = \langle 4, 0 \rangle) \lor (SSEP\_TS\_SA = ATC) \lor (SSEP\_SS\_SA = ATC)$$

This tells us that there are three ways to guarantee NO-LOS: (i) having only GSEP airplanes, or having the ATC in control of the (ii) Strategic or (iii) Tactical separation of any SSEP.

By checking that NO-LOS-Far is achieved only by configurations using nonreceptive ACDR, we verified the corresponding claim from Table 3. Moreover, we verified that not all configurations using non-receptive ACDR can satisfy NO-LOS-Far, thus discovering a necessary but not sufficient condition. These analyses were performed using pySMT [21] in order to represent the data using BDDs [13] for efficient querying.

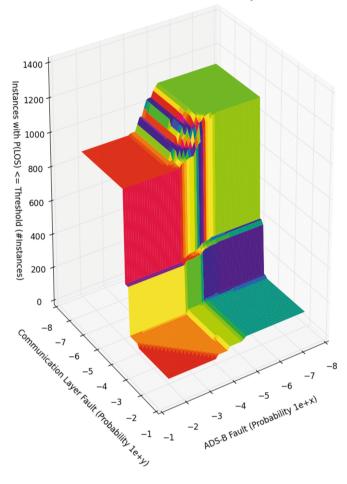

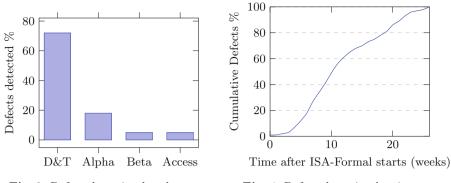

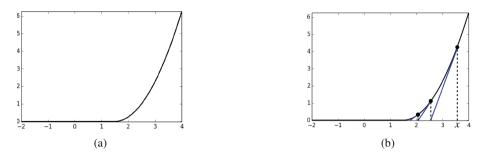

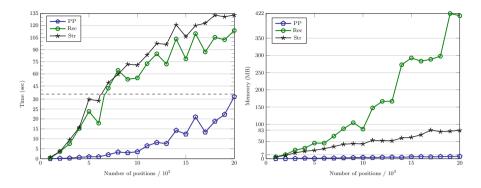

*Reliability Functions*. Analyzing the reliability functions obtained from the Fault Trees, we can synthesize the region of configurations that have a probability of violating a property below a given threshold. This result provides us different sets of candidates that are able to guarantee a high reliability. In addition to that, we want also to analyze the impact of a variation in the probability of failure of different groups of components. In Fig. 5 we demonstrate this last analysis by proceeding as follows. First, we partition the faults into three groups: the ones related to the Communication Layer, the ADS-B, and all the others. For each configuration and each value of the probability of the faults of the Communication Network (y axis) and of the ADS-B Network (x axis), we compute the probability of reaching a LOS, by considering all other faults to have a fixed probability of  $10^{-8}$  (Basic Probability). In Fig. 5, we summarize this information by plotting how many configurations have a probability of leading to a LOS that is below the threshold of  $10^{-4}$  for the given probability of the faults. Interestingly, we see that reducing the reliability of the Communication Layer has a bigger impact than reducing the reliability of the ADS-B network. We see this because when the probability of faults in the ADS-B is high (x axis close to -2), but the probability of fault of the communication layer is low (y axis close to -8), the probability of reaching a LOS is

Threshold = 1e-4; Basic Probability=1e-8

Fig. 5. Impact of the communication faults on LOS probability.

below the threshold of  $10^{-4}$  for more than 800 configurations. If we look at the opposite situation, instead, we see that less than 100 configurations have a probability of reaching LOS that is below the threshold. The insight that we gain from this is that many of the analyzed configurations are robust with respect to failures of the ADS-B.

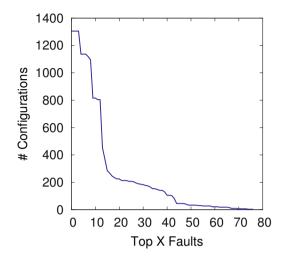

A different analysis is presented in Fig. 6 in which we analyze how many configurations share the same top N single points of failure. A single point of failure is a single fault that is sufficient to (in our case) cause a LOS, and corresponds to a minimal cutset of cardinality one. There are roughly 10 single points of failure that are shared by more than a thousand configurations. However, we also notice that most faults are single points of failure for a limited number of configurations; recall that there are 95 faults in total. If the probability of those

Fig. 6. Configurations impacted by the top N single points of failure.

10 faults is very high, then we can significantly prune the design space, and focus only on the configurations that are not affected by those faults.

### 5.2 Interesting Executions

A selection of the most relevant results was discussed with the domain experts. In particular, we were able to independently reproduce two known issues, *side-walk* [25,33] and *coincidental* conflicts [23], and discover a new one.

Side-walk Conflict. Side-walk conflicts occur whenever we use the "simple" implementation of the ACDR, in which conflicts between SSEPs are resolved by choosing a free conflict area. The problem occurs when more than one SSEP decides to move to the same conflict area. Due to the symmetry of the resolution algorithm, this strategy is not guaranteed to resolve the conflict. To break this symmetry, we developed the asymmetric version of the ACDR.

Coincidental Conflict. The asymmetric ACDR is not able to resolve conflicts early. In particular, we would like to always satisfy NO-LOS-Mid, i.e., avoid predicted LOS in the Mid-window. This is not possible if we allow only one communication step. In fact, if four aircraft are in two different conflicts that are resolved correctly, they might still end up in a new conflict. Consider the two conflict sets {AC1, AC2} and {AC3, AC4}. AC1 and AC3 decide to move to solve their respective conflicts. However, they choose to move to the same conflict area. An additional round of communication is needed in order to resolve this conflict, and this generalizes to needing at most log(n) communication steps when considering n aircraft.

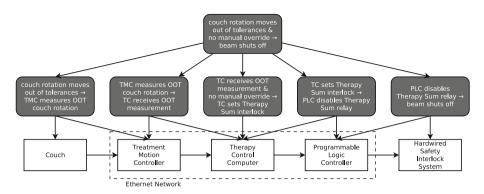

Backup From Ground. The novel problematic configuration that we identified stems from limited requirements on the behavior of the backup operation,