Arie Gurfinkel Sanjit A. Seshia (Eds.)

# Verified Software: Theories, Tools, and Experiments

7th International Conference, VSTTE 2015 San Francisco, CA, USA, July 18–19, 2015 Revised Selected Papers

## Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zürich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7408

Arie Gurfinkel · Sanjit A. Seshia (Eds.)

## Verified Software: Theories, Tools, and Experiments

7th International Conference, VSTTE 2015 San Francisco, CA, USA, July 18–19, 2015 Revised Selected Papers

*Editors* Arie Gurfinkel Software Engineering Institute Carnegie Mellon University Pittsburgh, PA USA

Sanjit A. Seshia Department of Electrical Engineering and Computer Science University of California Berkeley USA

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-29612-8 ISBN 978-3-319-29613-5 (eBook) DOI 10.1007/978-3-319-29613-5

Library of Congress Control Number: 2016930277

LNCS Sublibrary: SL2 - Programming and Software Engineering

#### © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by SpringerNature The registered company is Springer International Publishing AG Switzerland

#### Preface

This volume contains the papers presented at the 7th International Conference on Verified Software: Theories, Tool and Experiments (VSTTE), which was held in San Francisco, California, USA, during July 18–19, 2015, co-located with the 27th International Conference on Computer-Aided Verification. The final version of the papers was prepared by the authors after the event took place, which permitted them to take feedback received at the meeting into account.

VSTTE originated from the Verified Software Initiative (VSI), which is an international initiative directed at the scientific challenges of large-scale software verification. The inaugural VSTTE conference was held at ETH Zurich in October 2005, and was followed by VSTTE 2008 in Toronto, VSTTE 2010 in Edinburgh, VSTTE 2012 in Philadelphia, VSTTE 2013 in Menlo Park, and VSTTE 2015 in Vienna. The goal of the VSTTE conference is to advance the state of the art through the interaction of theory development, tool evolution, and experimental validation.

The call for papers for VSTTE 2015 solicited submissions describing large-scale verification efforts that involve collaboration, theory unification, tool integration, and formalized domain knowledge. We were especially interested in papers describing novel experiments and case studies evaluating verification techniques and technologies. We welcomed papers describing education, requirements modeling, specification languages, specification/verification, formal calculi, software design methods, automatic code generation, refinement methodologies, compositional analysis, verification tools (e.g., static analysis, dynamic analysis, model checking, theorem proving), tool integration, benchmarks, challenge problems, and integrated verification environments.

There were 25 submissions. Each submission was reviewed by at least three members of the Program Committee. The committee decided to accept 12 papers. The program also included two invited talks, given by Chris Hawblitzel (Microsoft Research) and Lee Pike (Galois Inc.), and a panel on "Software Verification Competitions: Lessons Learned and Challenges Ahead."

We would like to thank the invited speakers, the panel members, and all submitting authors for their contribution to the program. We thank Natarjan Shankar for the help with the organization, our publicity chair, Daniel Bundala, our general chair, Martin Schaef, and the CAV workshop chair, Dirk Beyer. Finally, we thank the external reviewers and the Program Committee for their reviews and their help in selecting the papers that appear in this volume.

December 2015

Arie Gurfinkel Sanjit A. Seshia

## Organization

## **Program Committee**

| Elvira Albert         | Complutense University of Madrid, Spain          |

|-----------------------|--------------------------------------------------|

| Nikolaj Bjorner       | Microsoft Research, USA                          |

| Bor-Yuh Evan Chang    | University of Colorado at Boulder, USA           |

| Ernie Cohen           | Amazon, USA                                      |

| Vijay D'Silva         | University of California, Berkeley, USA          |

| Jyotirmoy Deshmukh    | Toyota Technical Center, USA                     |

| Jinsong Dong          | National University of Singapore, Singapore      |

| Vijay Ganesh          | University of Waterloo, Canada                   |

| Alex Groce            | Oregon State University, USA                     |

| Arie Gurfinkel        | Software Engineering Institute, Carnegie Mellon  |

|                       | University, USA                                  |

| William Harris        | University of Wisconsin-Madison, USA             |

| Chris Hawblitzel      | Microsoft Research, USA                          |

| Bart Jacobs           | Katholieke Universiteit Leuven, Belgium          |

| Susmit Jha            | Strategic CAD Lab, Intel, USA                    |

| Rajeev Joshi          | Laboratory for Reliable Software, Jet Propulsion |

|                       | Laboratory, USA                                  |

| Vladimir Klebanov     | Karlsruhe Institute of Technology, Germany       |

| Akash Lal             | Microsoft Research, India                        |

| Ruzica Piskac         | Yale University, USA                             |

| Zvonimir Rakamaric    | University of Utah, USA                          |

| Kristin Yvonne Rozier | NASA Ames Research Center, USA                   |

| Martin Schäf          | SRI International, USA                           |

| Sanjit Seshia         | UC Berkeley, USA                                 |

| Natarajan Shankar     | SRI International, USA                           |

| Nishant Sinha         | IBM Research Labs, India                         |

| Carsten Sinz          | Karlsruhe Institute of Technology (KIT), Germany |

| Alexander J. Summers  | ETH Zurich, Switzerland                          |

| Zach Tatlock          | University of Washington, USA                    |

| Sergey Tverdyshev     | SYSGO AG, Germany                                |

| Arnaud Venet          | Google, USA                                      |

| Karen Yorav           | IBM Haifa Research Lab, Israel                   |

|                       |                                                  |

## **Additional Reviewers**

Arechiga, Nikos Bai, Guangdong Berezish, Murphy Din, Crystal Chang Fremont, Daniel J. Liu, Yan Nejati, Saeed Prabhu, Vinayak Rabe, Markus N. Román-Díez, Guillermo Santolucito, Mark Schwerhoff, Malte Shurek, Gil

## Contents

| A Proof-Sensitive Approach for Small Propositional Interpolants<br>Leonardo Alt, Grigory Fedyukovich, Antti E.J. Hyvärinen,<br>and Natasha Sharygina | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Recursive Games for Compositional Program Synthesis                                                                                                  | 19  |

| Testing the IPC Protocol for a Real-Time Operating System<br>Achim D. Brucker, Oto Havle, Yakoub Nemouchi, and Burkhart Wolff                        | 40  |

| Pseudo-Random Number Generator Verification: A Case Study<br>Felix Dörre and Vladimir Klebanov                                                       | 61  |

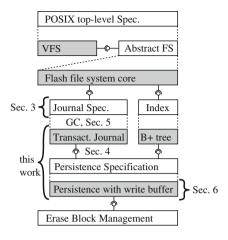

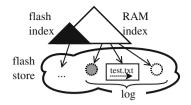

| Inside a Verified Flash File System: Transactions and Garbage Collection<br>Gidon Ernst, Jörg Pfähler, Gerhard Schellhorn, and Wolfgang Reif         | 73  |

| How to Avoid Proving the Absence of Integer Overflows                                                                                                | 94  |

| Machine-Checked Proofs for Realizability Checking Algorithms<br>Andreas Katis, Andrew Gacek, and Michael W. Whalen                                   | 110 |

| Dynamic Frames Based Verification Method for Concurrent Java Programs<br>Wojciech Mostowski                                                          | 124 |

| A Simpler Reduction Theorem for x86-TSO Jonas Oberhauser                                                                                             | 142 |

| Moving Around: Lipton's Reduction for TSO (Regular Submission) <i>Ali Sezgin and Serdar Tasiran</i>                                                  | 165 |

| Android Platform Modeling and Android App Verification in the ACL2<br>Theorem Prover<br><i>Eric Smith and Alessandro Coglio</i>                      | 183 |

| AUSPICE: <u>Automatic Safety Property Verification for Unmodified</u> <u>Executables</u> Jiaqi Tan, Hui Jun Tay, Rajeev Gandhi, and Priya Narasimhan | 202 |

| Author Index                                                                                                                                         | 223 |

## A Proof-Sensitive Approach for Small Propositional Interpolants

Leonardo Alt<sup>(⊠)</sup>, Grigory Fedyukovich, Antti E.J. Hyvärinen, and Natasha Sharygina

Formal Verification Lab, USI, Lugano, Switzerland leonardoaltt@gmail.com

Abstract. The labeled interpolation system (LIS) is a framework for Craig interpolation widely used in propositional-satisfiability-based model checking. Most LIS-based algorithms construct the interpolant from a proof of unsatisfiability and a fixed labeling determined by which part of the propositional formula is being over-approximated. While this results in interpolants with fixed strength, it limits the possibility of generating interpolants of small size. This is problematic since the interpolant size is a determining factor in achieving good over a performance in model checking. This paper analyses theoretically how labeling functions can be used to construct small interpolants. In addition to developing the new labeling mechanism guaranteeing small interpolants, we also present its versions managing the strength of the interpolants. We implement the labeling functions in our tool PeRIPLO and study the behavior of the resulting algorithms experimentally by integrating the tool to a variety of model checking applications. Our results suggest that the new proofsensitive interpolation algorithm performs consistently better than any of the standard interpolation algorithms based on LIS.

#### 1 Introduction

In SAT-based model checking, a widely used workflow for obtaining an interpolant for a propositional formula A is to compute a proof of unsatisfiability for the formula  $\phi = A \wedge B$ , use a variety of standard techniques for compressing the proof (see, e.g., [17]), construct the interpolant from the compressed proof, and finally simplify the interpolant [4]. The *labeled interpolation system* (LIS) [9] is a commonly used, flexible framework for computing the interpolant from a given proof that generalizes several interpolation algorithms parameterized by a *labeling function*. Given a labeling function and a proof, LIS uniquely determines the interpolant. However, the LIS framework allows significant flexibility in constructing interpolants from a proof through the choice of the labeling function.

Arguably, the suitability of an interpolant depends ultimately on the application [17], but there is a wide consensus that small interpolants lead to better overall performance in model checking [3, 17, 21]. However, generating small interpolants for a given partitioning is a non-trivial task. This paper presents, to the best of our knowledge, the first thorough, rigorous analysis on how labeling

<sup>©</sup> Springer International Publishing Switzerland 2016

A. Gurfinkel and S.A. Seshia (Eds.): VSTTE 2015, LNCS 9593, pp. 1–18, 2016. DOI: 10.1007/978-3-319-29613-5\_1

in the LIS framework affects the size of the interpolant. The analysis is backed up by experimentation showing also the practical significance of the result. We believe that the results reported here will help the community working on interpolation in designing interpolation algorithms that work well independent of the application. Based on the analysis we present the *proof-sensitive interpolation algorithm* PS that produces small interpolants by adapting itself to the proof of unsatisfiability. We prove under reasonable assumptions that the resulting interpolant is always smaller than those generated by any other LIS-based algorithms, including the widely used algorithms  $M_s$  (McMillan [13]), P (Pudlák [16]), and  $M_w$  (dual to  $M_s$  [9]).

In some applications it is important to give guarantees on the logical strength of the interpolants. Since the LIS framework allows us to argue about the resulting interpolants by their logical strength [9], we know that for a fixed problem  $A \wedge B$  and a fixed proof of unsatisfiability, an interpolant constructed with  $M_s$ implies one constructed with P which in turn implies one constructed with  $M_w$ . While PS is designed to control the interpolant size, we additionally define two variants controlling the interpolant strength: the strong and the weak proofsensitive algorithms computing, respectively, interpolants that imply the ones constructed by P and that are implied by the ones constructed by P.

We implemented the new algorithms in the PERIPLO interpolation framework [17] and confirm the practical significance of the algorithms with an experimentation. The results show that when using PS, both the sizes of the interpolants and the run times when used in a model-checking framework compare favorably to those obtained with  $M_s$ , P, and  $M_w$ , resulting occasionally in significant reductions.

#### 1.1 Related Work

Interpolants can be compacted through applying transformations to the resolution refutation. For example, [17, 18] compare the effect of such compaction on the interpolation algorithms  $M_s$ , P, and  $M_w$  in connection with functionsummarization-based model checking [10, 20]. A similar approach is studied in [9]combined with an analysis on the strength of the resulting interpolant. Different size-based reductions are further discussed in [4, 11]. While often successful, these approaches might produce a considerable overhead in large problems. Our approach is more light-weight and uses directly the flexibility of LIS to perform the compression. An interesting analysis similar to ours, presented in [3], concentrates on the effect of identifying subsumptions in the resolution proofs. A significant reduction in the size of the interpolant can be obtained by considering only CNF-shaped interpolants [21]. However, the strength of these interpolants is not as easily controllable as in the LIS interpolants, making the technique harder to apply in certain model checking approaches. A light-weight interpolant compaction can be performed by specializing through simplifying the interpolant with a truth assignment [12].

In many verification approaches using counter-examples for refinement it is possible to abstract an interpolant obtained from a refuted counter-example. For instance, [2,19] present a framework for generalizing interpolants based on templates. A related approach for generalizing interpolants in unbounded modelchecking through abstraction is presented in [5] using incremental SAT solving. While this direction is orthogonal to ours, we believe that the ideas presented here and addressing the interpolation back-end would be useful in connection with the generalization phase.

Linear-sized interpolants can be derived also from resolution refutations computed by SMT solvers, for instance in the combined theory of linear inequalities and equalities with uninterpreted functions [14] and linear rational arithmetic [1]. These approaches have an interesting connection to ours since they also contain a propositional part. It is also possible to produce interpolants without a proof [7]. However, this method gives no control over the relative interpolant strength and reduces in the worst case to enumerating all models of a SAT instance. Finally, conceptually similar to our work, there is a renewed interest in interpolation techniques used in connection with modern ways of organizing the high-level model-checking algorithm [6,15].

#### 2 Preliminaries

Given a finite set of propositional variables, a *literal* is a variable p or its negation  $\neg p$ . A clause is a finite set of literals and a formula  $\phi$  in conjunctive normal form (CNF) is a set of clauses. We also refer to a clause as the disjunction of its literals and a CNF formula as the conjunction of its clauses. A variable p occurs in the clause C, denoted by the pair (p, C), if either  $p \in C$  or  $\neg p \in C$ . The set  $var(\phi)$ consists of the variables that occur in the clauses of  $\phi$ . We assume that double negations are removed, i.e.,  $\neg \neg p$  is rewritten as p. A truth assignment  $\sigma$  assigns a Boolean value to each variable p. A clause C is satisfied if  $p \in C$  and  $\sigma(p)$  is true, or  $\neg p \in C$  and  $\sigma(p)$  is false. The propositional satisfiability problem (SAT) is the problem of determining whether there is a truth assignment satisfying each clause of a CNF formula  $\phi$ . The special constants  $\top$  and  $\perp$  denote the empty conjunction and the empty disjunction. The former is satisfied by all truth assignments and the latter is satisfied by none. A formula  $\phi$  implies a formula  $\phi'$ , denoted  $\phi \to \phi'$ , if every truth assignment satisfying  $\phi$  satisfies  $\phi'$ . The size of a propositional formula is the number of logical connectives it contains. For instance the unsatisfiable CNF formula

$$\phi = (x_1 \lor x_2) \land (\neg x_2 \lor x_4) \land (\neg x_2 \lor \neg x_3 \lor \neg x_4) \land (x_1 \lor x_3) \land (\neg x_1)$$

(1)

of size 14 consists of 4 variables and 5 clauses. The occurrences of the variable  $x_4$  are  $(x_4, \neg x_2 \lor x_4)$  and  $(x_4, \neg x_2 \lor \neg x_3 \lor \neg x_4)$ .

For two clauses  $C^+$ ,  $C^-$  such that  $p \in C^+$ ,  $\neg p \in C^-$ , and for no other variable q both  $q \in C^- \cup C^+$  and  $\neg q \in C^- \cup C^+$ , a resolution step is a triple  $C^+$ ,  $C^-$ ,  $(C^+ \cup C^-) \setminus \{p, \neg p\}$ . The first two clauses are called the *antecedents*, the latter is the resolvent and p is the pivot of the resolution step. A resolution refutation R of an unsatisfiable formula  $\phi$  is a directed acyclic graph where the nodes are clauses and the edges are directed from the antecedents to the resolvent. The nodes of a refutation R with no incoming edge are the clauses of  $\phi$ , and the rest of the clauses are resolvents derived with a resolution step. The unique node with no outgoing edges is the empty clause. The *source clauses* of a refutation R are the clauses of  $\phi$  from which there is a path to the empty clause.

Given an unsatisfiable formula  $A \wedge B$ , a *Craig interpolant I* for A is a formula such that  $A \to I$ ,  $I \wedge B$  is unsatisfiable and  $var(I) \subseteq var(A) \cap var(B)$ . An interpolant can be seen as an over-approximation of A that is still unsatisfiable when conjoined with B. In the rest of the paper we assume that A and B only consist of the source clauses of R.

The labeled interpolation system [9] (LIS) is a framework that, given propositional formulas A, B, a refutation R of  $A \wedge B$  and a labeling function L, computes an interpolant I for A based on R. The refutation together with the partitioning A, B is called an *interpolation instance* (R, A, B). The labeling function L assigns a label from the set  $\{a, b, ab\}$  to every variable occurrence (p, C) in the clauses of the refutation R. A variable is *shared* if it occurs both in A and B; otherwise it is *local*. For all variable occurrences (p, C) in R, L(p, C) = a if p is local to A and L(p, C) = b if p is local to B. For occurrences of shared variables in the source clauses the label may be chosen freely. The label of a variable occurrence in a resolvent C is determined by the label of the variable in its antecedents. For a variable occurrence is ab, and in all other cases the label is equivalent to the label in its antecedent or both antecedents.

An interpolation algorithm based on LIS computes an interpolant with a dynamic algorithm by annotating each clause of R with a *partial interpolant* starting from the source clauses. The partial interpolant of a source clause C is

$$I(C) = \begin{cases} \bigvee \{l \mid l \in C \text{ and } L(var(l), C) = b\} & \text{if } C \in A, \text{ and} \\ \bigwedge \{\neg l \mid l \in C \text{ and } L(var(l), C) = a\} & \text{if } C \in B, \end{cases}$$

(2)

The partial interpolant of a resolvent clause C with pivot p and antecedents  $C^+$ and  $C^-$ , where  $p \in C^+$  and  $\neg p \in C^-$ , is

$$I(C) = \begin{cases} I(C^+) \lor I(C^-) & \text{if } L(p, C^+) = L(p, C^-) = a, \\ I(C^+) \land I(C^-) & \text{if } L(p, C^+) = L(p, C^-) = b, \text{ and } \\ (I(C^+) \lor p) \land (I(C^-) \lor \neg p) \text{ otherwise.} \end{cases}$$

(3)

The interpolation algorithms  $M_s$ , P, and  $M_w$  mentioned in the introduction can be obtained as special cases of LIS by providing a labeling function returning b, ab, and a for the shared variables, respectively.

In some applications it is useful to consider different interpolants constructed from a fixed interpolation instance, but using different interpolation algorithms [10]. For such cases the LIS framework provides a convenient tool for analyzing whether the interpolants generated by one interpolation algorithm always imply the interpolants generated by another algorithm. If we order the three labels so that  $b \leq ab \leq a$ , it can be shown that given two labeling functions L and L' resulting in the interpolants  $I_L$  and  $I_{L'}$  in LIS and having the property that  $L(p, C) \leq L'(p, C)$  for all occurrences (p, C), it is true that  $I_L \to I_{L'}$ . In this case we say that the interpolation algorithm obtained from LIS using the labeling L' is *weaker* than the interpolation algorithm that uses the labeling L.

We define here two concepts that will be useful in the next section: the class of *uniform* labeling functions, and the *internal size* of an interpolant.

**Definition 1.** A labeling function is uniform if for all pairs of clauses  $C, D \in R$  containing the variable p, L(p,C) = L(p,D), and no occurrence is labeled ab. Any interpolation algorithm with uniform labeling function is also called uniform.

An example of non-uniform labeling function is  $D_{min}$ , presented in [8].  $D_{min}$  is proven to produce interpolants with the least number of distinct variables.

**Definition 2.** The internal size IntSize(I) of an interpolant I is the number of connectives in I excluding the connectives contributed by the partial interpolants associated with the source clauses.

Typically, an interpolant constructed by a LIS-based algorithm will contain a significant amount of subformulas that are syntactically equivalent. The *structural sharing*, i.e., maintaining a unique copy of the syntactically equivalent subformulas, while completely transparent to the satisfiability, is of critical practical importance. Similarly important for performance is the *constant simplification*, consisting of four simple rewriting rules:  $\top \land \phi \rightsquigarrow \phi, \perp \land \phi \rightsquigarrow \perp, \top \lor \phi \rightsquigarrow \top$ , and  $\perp \lor \phi \rightsquigarrow \phi$ , where  $\phi$  is an arbitrary Boolean formula.

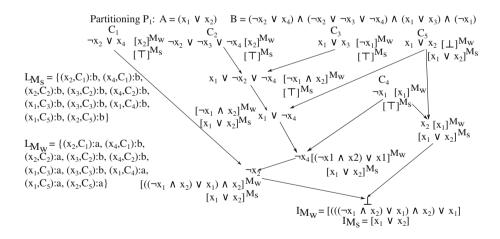

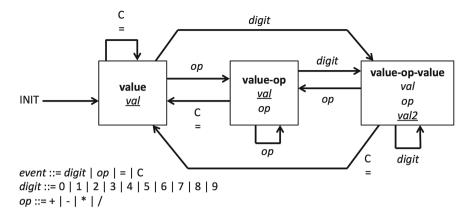

Fig. 1. Different interpolants obtained from the refutation using the partitioning  $P_1$ .

The following example illustrates the concepts discussed in this section by showing how LIS can be used to compute interpolants with two different uniform algorithms  $M_s$  and  $M_w$ .

Example 1. Consider the unsatisfiable formula  $\phi = A \wedge B$  where  $\phi$  is from Eq. (1) and  $A = (x_1 \vee x_2)$  and  $B = (\neg x_2 \vee x_4) \wedge (\neg x_2 \vee \neg x_3 \vee \neg x_4) \wedge (x_1 \vee x_3) \wedge (\neg x_1)$ . Figure 1 shows a resolution refutation for  $\phi$  and the partial interpolants computed by the interpolation algorithms  $M_s$  and  $M_w$ . Each clause in the refutation is associated with a partial interpolant  $\psi$  generated by labeling  $L_{M_s}$ (denoted by  $[\psi]^{M_s}$ ) and a partial interpolant  $\psi'$  generated by labeling  $L_{M_w}$ (denoted by  $[\psi']^{M_w}$ ). The generated interpolants are  $I_{M_s} = x_1 \vee x_2$  and  $I_{M_w} = (((\neg x_1 \wedge x_2) \vee x_1) \wedge x_2) \vee x_1$ . Now consider a different partitioning  $\phi' = A' \wedge B'$  for the same formula where the partitions have been swapped, that is, A' = B and B' = A. Using the same refutation (figure omitted for lack of space), we get the interpolants  $I'_{M_s} = (((x_1 \vee \neg x_2) \wedge \neg x_1) \vee \neg x_2) \wedge \neg x_1 = \neg I_{M_w}$ and  $I'_{M_w} = \neg (x_1 \vee x_2) = \neg I_{M_s}$  We use both structural sharing and constant simplification in the example. The internal size of  $I_{M_s}$  is 0, whereas the internal size of  $I_{M_w}$  is 4.

The two partitionings illustrate a case where the interpolation algorithm  $M_s$ , in comparison to  $M_w$ , produces a small interpolant for one and a large interpolant for another interpolation instance. Since the goal in this work is to develop LIS-based interpolation algorithms that consistently produce small interpolants, the labeling function of choice cannot be  $L_{M_s}$  or  $L_{M_w}$ . Note that while in this case the interpolants  $I_{M_s}$  and  $I_{M_w}$  are equivalent, the representation of  $I_{M_w}$  is considerably smaller than the representation of  $I_{M_s}$ . Since minimizing a propositional formula is an NP-complete problem, producing interpolants that are small in the first place is a very important goal.

#### 3 Labeling Functions for LIS

This section studies the algorithms based on the labeled interpolation system in an analytic setting. Our main objective is to provide a basis for developing and understanding labeling functions that construct interpolants having desirable properties. In particular, we will concentrate on three syntactic properties of the interpolants: the number of distinct variables; the number of literal occurrences; and the internal size of the interpolant. In most of the discussion in this section we will ignore the two optimizations on structural sharing and constraint simplification. While both are critically important for practicality of interpolation, our experimentation shows that they mostly have similar effect on all the interpolation algorithms we studied, and therefore they can be considered orthogonally (see Sect. 4.4). The exception is that the non-uniform labeling functions allow a more efficient optimization compared to the uniform labeling functions through constraint simplification. More specifically, the main results of the section are the following theorems.

(i) If an interpolation instance is not p-annihilable (see Definition 3), which in our experimentation turns out almost always to be the case, then all LIS interpolants constructed from the refutation have the same number of distinct variables (Theorem 1);

- (ii) For a given interpolation instance, the interpolants  $I_n$  obtained with any non-uniform labeling function and  $I_u$  obtained with any uniform labeling function satisfy  $IntSize(I_u) \leq IntSize(I_n)$ . (Theorem 2); and

- (iii) Among uniform labeling functions, the *proof-sensitive* labeling function (see Definition 4) results in the least number of variable occurrences in the partial interpolants associated with the source clauses (Theorem 3).

From the three theorems we immediately have the following:

**Corollary 1.** For not *p*-annihilable interpolation instances, the proof-sensitive labeling function will result in interpolants that have the smallest internal size, the least number of distinct variables, and least variable occurrences in the source partial interpolants.

The proof-sensitive interpolant strength can only be given the trivial guarantees: it is stronger than  $I_{M_w}$  and weaker than  $I_{M_s}$ . At the expense of the minimality in the sense of the above corollary, we introduce in Eqs. (6) and (7) the weak and strong versions of the proof-sensitive labeling functions.

#### 3.1 Analysing Labeling Functions

An interesting special case in LIS-based interpolation algorithms is when the labeling can be used to reduce the number of distinct variables in the final interpolant. To make this explicit we define the concepts of a p-pure resolution step and a p-annihilable interpolation instance.

**Definition 3.** Given an interpolation instance (R, A, B), a variable  $p \in var(A) \cup var(B)$  and a labeling function L, a resolution step in R is p-pure if at most one of the antecedents contain p, or both antecedents C, D contain p but L(p, C) = L(p, D) = a or L(p, C) = L(p, D) = b. An interpolation instance (R, A, B) is p-annihilable if there is a non-uniform labeling function L such that L(p, C) = a if  $C \in A$ , L(p, C) = b if  $C \in B$ , and all the resolution steps are p-pure.

The following theorem shows the value of p-annihilable interpolation instances in constructing small interpolants.

**Theorem 1.** Let (R, A, B) be an interpolation instance,  $p \in var(A) \cap var(B)$ , and I an interpolant obtained from (R, A, B) by means of a LIS-based algorithm. If  $p \notin var(I)$ , then (R, A, B) is p-annihilable.

*Proof.* Assume that (R, A, B) is not *p*-annihilable,  $p \in var(A) \cap var(B)$ , but there is a labeling *L* which results in a LIS-based interpolation algorithm that constructs an interpolant not containing *p*. The labeling function cannot have L(p, C) = b if  $C \in A$  or L(p, C) = a if  $C \in B$  because *p* would appear in the partial interpolants associated with the sources by Eq. (2). No clause *C* in *R* can have L(p, C) = ab since all literals in the refutation need to be used as a pivot on the path to the empty clause, and having an occurrence of *p* labeled *ab*  in an antecedent clause would result in introducing the literal p to the partial interpolant associated with the resolvent by Eq. (3) when used as a pivot. Every resolution step in the refutation R needs to be p-pure, since if the antecedents contain occurrences (p, C) and (p, D) such that  $L(p, C) \neq L(p, D)$  either the label of the occurrence of p in the resolvent clause will be ab, violating the condition that no clause can have L(p, C) = ab above, or, if p is pivot on the resolution step, the variable is immediately inserted to the partial interpolant by Eq. (3).

While it is relatively easy to artificially construct an interpolation instance that is p-annihilable, they seem to be rare in practice (see Sect. 4.4). Hence, while instances that are p-annihilable would result in small interpolants, it has little practical significance at least in the benchmarks available to us. However, we have the following practically useful result which shows the benefits of labeling functions producing p-pure resolution steps in computing interpolants with low number of connectives.

**Theorem 2.** Let (R, A, B) be an interpolation instance. Given a labeling function L such that the resolution steps in R are p-pure for all  $p \in var(A \land B)$ , and a labeling function L' such that at least one resolution step in R is not p-pure for some  $p \in var(A \land B)$ , we have  $IntSize(I_L) \leq IntSize(I_{L'})$ .

*Proof.* For a given refutation R, the number of partial interpolants will be the same for any LIS-based interpolation algorithm. By Eq. (3) each resolution step will introduce one connective if both occurrences in the antecedents are labeled a or b and three connectives otherwise. The latter can only occur if the labeling algorithm results in a resolution step that is not p-pure for some p.

Clearly, p-pure steps are guaranteed with uniform labeling functions. Therefore we have the following corollary:

**Corollary 2.** Uniform labeling functions result in interpolants with smaller internal size compared to non-uniform labeling functions.

The main result of this work is the development of a labeling function that is uniform, therefore producing small interpolants by Corollary 2, and results in the smallest number of variable occurrences among all uniform labeling functions. This *proof-sensitive labeling function* works by considering the refutation R when assigning labels to the occurrences of the shared variables.

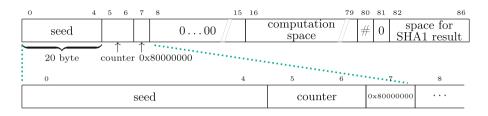

**Definition 4.** Let R be a resolution refutation for  $A \land B$  where A and B consist of the source clauses,  $f_A(p) = |\{(p,C) \mid C \in A\}|$  be the number of times the variable p occurs in A, and  $f_B(p) = |\{(p,C) \mid C \in B\}|$  the number the variable p occurs in B. The proof-sensitive labeling function  $L_{\text{PS}}$  is defined as

$$L_{\rm PS}(p,C) = \begin{cases} a & \text{if } f_A(p) \ge f_B(p) \\ b & \text{if } f_A(p) < f_B(p). \end{cases}$$

(4)

Note that since  $L_{PS}$  is uniform, it is independent of the clause C. Let  $Sh_A$  be the set of the shared variables occurring at least as often in clauses of A as in B and  $Sh_B$  the set of shared variables occurring more often in B than in A:

$$Sh_A = \{ p \in var(A) \cap var(B) \mid f_A(p) \ge f_B(p) \} \text{ and}$$

$$Sh_B = \{ p \in var(A) \cap var(B) \mid f_A(p) < f_B(p) \}$$

(5)

Theorem 3 states the optimality with respect to variable occurrences of the algorithm PS among uniform labeling functions.

**Theorem 3.** For a fixed interpolation instance (R, A, B), the interpolation algorithm PS will introduce the smallest number of variable occurrences in the partial interpolants associated with the source clauses of R among all uniform interpolation algorithms.

*Proof.* The interpolation algorithm PS is a uniform algorithm labeling shared variables either as a or b. Hence, the shared variables labeled a will appear in the partial interpolants of the source clauses from B of R, and the shared variables labeled b will appear in the partial interpolants of the source clauses from A of R. The sum of the number of variable occurrences in the partial interpolants associated with the source clauses by PS is

$$n_{\rm PS} = \sum_{v \in Sh_B} f_A(v) + \sum_{v \in Sh_A} f_B(v).$$

We will show that swapping uniformly the label of any of the shared variables will result in an increase in the number of variable occurrences in the partial interpolants associated with the source clauses of R compared to  $n_{\text{PS}}$ . Let v be a variable in  $Sh_A$ . By (4) and (5), the label of v in PS will be a. Switching the label to b results in the size  $n' = n_{\text{PS}} - f_B(v) + f_A(v)$ . Since v was in  $Sh_A$  we know that  $f_A(v) \ge f_B(v)$  by (5), and therefore  $-f_B(v) + f_A(v) \ge 0$  and  $n' \ge n_{\text{PS}}$ . An (almost) symmetrical argument shows that swapping the label for a variable  $v \in Sh_B$  to a results in  $n' > n_{\text{PS}}$ . Hence, swapping uniformly the labeling of PS for any shared variable will result in an interpolant having at least as many variable occurrences in the leaves. Assuming no simplifications, the result holds for the final interpolant.

*Example 2.* Figure 2 shows the interpolants that PS would deliver if applied to the same refutation R of  $\phi$  and partitionings  $A \wedge B$  and  $A' \wedge B'$  given in Example 1. Notice that PS adapts the labeling to the best one depending on the refutation and partitions, and gives small interpolants for both cases.

Because of the way  $L_{PS}$  labels the variable occurrences, we cannot beforehand determine the strength of PS relative to, e.g., the algorithms  $M_s$ , P, and  $M_w$ . Although it is often not necessary that interpolants have a particular strength, in some applications this has an impact on performance or even soundness [17]. To be able to apply the idea in applications requiring specific interpolant strength,

Fig. 2. Interpolants obtained by PS.

for example tree interpolation, we propose a weak and a strong version of the proof-sensitive interpolation algorithm,  $PS_w$  and  $PS_s$ . The corresponding labeling functions  $L_{PS_w}$  and  $L_{PS_s}$  are defined as

$$L_{\mathrm{PS}_{w}}(p,C) = \begin{cases} a & \text{if } p \text{ is not shared and } C \in A \text{ or } p \in Sh_{A} \\ b & \text{if } p \text{ is not shared and } C \in B \\ ab & \text{if } p \in Sh_{B} \end{cases}$$

(6)

$$L_{\mathrm{PS}_{s}}(p,C) = \begin{cases} a & \text{if } p \text{ is not shared and } C \in A \\ b & \text{if } p \text{ is not shared and } C \in B, \text{ or } p \in Sh_{B} \\ ab & \text{if } p \in Sh_{A} \end{cases}$$

(7)

Finally, it is fairly straightforward to see based on the definition of the labeling functions that the strength of the interpolants is partially ordered as shown in the diagram below.

$$\begin{array}{c|c} \mathcal{L} & & D_{min} & \mathcal{K} \\ \hline \mathbf{M}_s & \leq & \mathbf{PS}_s & \leq & \mathbf{PS}_w \\ \mathcal{K} & \mathbf{P} & \mathcal{L} & \mathbf{PS}_w & \leq & \mathbf{M}_w \end{array}$$

#### 4 Experimental Results

We implemented the three interpolation algorithms within the PERIPLO [17] toolset and compare them with the  $D_{min}$  algorithm, as well as with the popular algorithms  $M_s$ , P and  $M_w$  in the context of three different model-checking tasks: (i) incremental software model checking with function summarization using FUNFROG [20]; (ii) checking software upgrades with function summarization using EVOLCHECK [10]; and (iii) pre-image overapproximation for hardware model checking with PDTRAV [5]. The wide range of experiments permits the study of the general applicability of the new techniques. In experiments (i) and

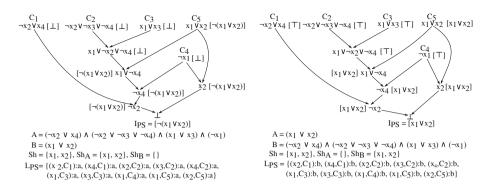

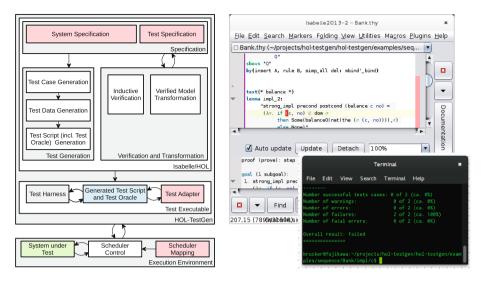

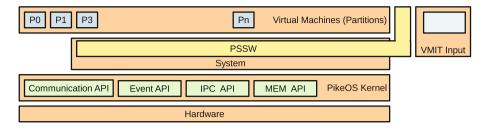

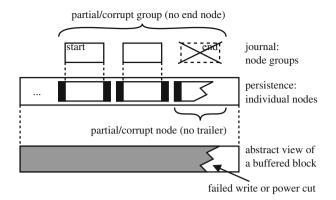

Fig. 3. Overall verification/interpolation framework.

(ii) the new algorithms are implemented within the verification process allowing us to evaluate their effect on the full verification run. Experiment (iii) focuses on the size of the interpolant, treating the application as a black box. Unlike in the theory presented in Sect. 3, all experiments use both structural sharing and constraint simplification, since the improvements given by these practical techniques are important. Experiments (i) and (ii) use a large set of benchmarks each containing a different call-tree structure and assertions distributed on different levels of the tree. For (iii), the benchmarks consisted of a set of 100 interpolation problems constructed by PDTRAV. All experiments use PERIPLO both as the interpolation engine and as the SAT solver.

Figure 3 shows a generic verification framework employing the new labeling mechanism for interpolation. Whenever the application needs an interpolant for the problem  $A \wedge B$ , it first requests the refutation from the SAT solver. After the refutation is generated, the application provides the partitioning to the proof analyser, which will generate functions  $f_A$  and  $f_B$  (Definition 4). The labeling engine then creates a labeling function based on the partitions A and B, the functions  $f_A$  and  $f_B$ , and a possible strength requirement from the application, and then passes it to the interpolator. The latter will finally construct an interpolant and return it to the application.

As mentioned in Sect. 1, different verification tasks may require different kinds of interpolants. For example, [17] reports that the FUNFROG approach works best with strong interpolants, whereas the EVOLCHECK techniques rely on weaker interpolants that have the tree-interpolation property. As shown in [18], only interpolation algorithms stronger than or equal to P are guaranteed to have this property. Therefore, we evaluated only  $M_s$ , P and PS<sub>s</sub> for (*ii*), and  $M_s$ , P,  $M_w$ , PS, PS<sub>w</sub> and PS<sub>s</sub> for (*i*) and (*iii*). D<sub>min</sub> was evaluated against the other algorithms for (*i*), but couldn't be evaluated for (*ii*) because it does not preserve the tree interpolation property. For (*iii*), D<sub>min</sub> was not evaluated due to its poor performance in (*i*).

In the experiments (i) and (ii), the overall verification time of the tools and average size of interpolants were analysed. For (iii) only the size was analysed. In all the experiments the size of an interpolant is the number of connectives in its DAG representation.

The tool and experimental data are available at http://verify.inf.usi.ch/periplo.

#### 4.1 Incremental Verification with Function Summarization

FUNFROG is a SAT-based bounded-model-checker for C designed to incrementally check different assertions. The checker works by unwinding a program up to some predefined bound and encoding the unwound program together with the negation of each assertion to a BMC formula which is then passed to a SAT solver. If the result is unsatisfiable, FUNFROG reports that the program is safe with respect to the provided assertion. Otherwise, it returns a counter-example produced from the model of the BMC formula.

Craig interpolation is applied in FUNFROG to extract function summaries (relations over input and output parameters of a function that over-approximate its behavior) to be reused between checks of different assertions with the goal of improving overall verification efficiency. Given a program P, and an assertion  $\pi$ , let  $\phi_{P,\pi}$  denote the corresponding BMC formula. If  $\phi_{P,\pi}$  is unsatisfiable, FUNFROG uses Craig Interpolation to extract function summaries. This is an iterative procedure for each function call f in P. Given f, the formula  $\phi_{P,\pi}$  is partitioned as  $\phi_{P,\pi} \equiv A_f \wedge B_{\pi}$ , where  $A_f$  encodes f and its nested calls,  $B_{\pi}$  the rest of the program and the negated assertion  $\pi$ . FUNFROG then calls PERIPLO to compute an interpolant  $I^{f,\pi}$  for the function f and assertion  $\pi$ .

While checking the program with respect to another assertion  $\pi'$ , FUNFROG constructs the new BMC formula  $\phi_{P,\pi'}$ ,  $\equiv I^{f,\pi} \wedge B_{\pi'}$ ; where  $I^{f,\pi}$  is used to over-approximate f. If  $\phi_{P,\pi'}$  is unsatisfiable then the over-approximation was accurate enough to prove that  $\pi'$  holds in P. On the other hand, satisfiability of  $\phi_{P,\pi'}$  could be caused by an overly weak over-approximation of  $I^{f,\pi}$ . To check this hypothesis,  $\phi_{P,\pi'}$  is refined to  $\phi_{P,\pi'}^{ref}$ , in which  $I^{f,\pi}$  is replaced by the precise encoding of f and the updated formula is solved again. If  $\phi_{P,\pi'}^{ref}$  is satisfiable, the error is real. Otherwise, the unsatisfiable formula  $\phi_{P,\pi'}^{ref}$  is used to create new function summaries in a similar manner as described above.

In our previous work [17,20] FUNFROG chooses the interpolation algorithm from the set {M<sub>s</sub>, P, M<sub>w</sub>} and uses it to create summaries for all function calls in the program. In this paper, we add the algorithms PS, PS<sub>w</sub> and PS<sub>s</sub> to the portfolio of the interpolation algorithms and show that in particular the use of PS and PS<sub>s</sub> improves quality of function summaries in FUNFROG and therefore makes overall model checking procedure more efficient.

*Experiments.* The set of benchmarks consists of 23 C programs with different number of assertions. FUNFROG verified the assertions one-by-one incrementally traversing the program call tree. The main goal of ordering the checks this way is to maximize the reuse of function summaries and thus to test how the labeling functions affect the overall verification performance. To illustrate our setting, consider a program with the chain of nested function calls

$$main() \{ f() \{ g() \{ h() \} assert_g \} assert_f \} assert_{main} \},\$$

where  $assert_F$  represents an assertion in the body of function F. In a successful scenario, (a)  $assert_g$  is detected to hold and a summary  $I^h$  for function h is

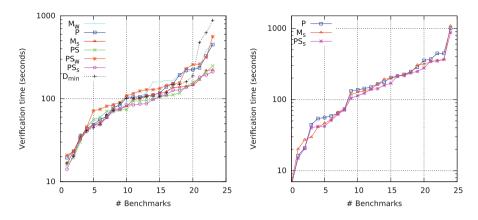

**Fig. 4.** Overall verification time of FUNFROG (*left*) and EVOLCHECK (*right*) using different interpolation algorithms.

**Table 1.** Sum of overall verification time and average interpolants size for the FUN-FROG (left) and EVOLCHECK (right) using the applicable labeling functions.

|               | FunFrog          |       |                  |               |                 |                 | eVolCheck |        |                 |        |

|---------------|------------------|-------|------------------|---------------|-----------------|-----------------|-----------|--------|-----------------|--------|

|               | $\mathbf{M}_{s}$ | Р     | $\mathbf{M}_{w}$ | $\mathbf{PS}$ | $\mathrm{PS}_w$ | $\mathrm{PS}_s$ | $D_{min}$ | $M_s$  | $\mathrm{PS}_s$ | Р      |

| Time (s)      | 2333             | 3047  | 3207             | 2272          | 3345            | 2193            | 3811      | 4867   | 4422            | 5081   |

| Increase %    | 6                | 39    | 46               | 3             | 52              | 0               | 74        | 10     | 0               | 16     |

| Avg size      | 48101            | 79089 | 86831            | 43781         | 95423           | 40172           | 119306    | 246883 | 196716          | 259078 |

| Increase $\%$ | 20               | 97    | 116              | 9             | 137             | 0               | 197       | 26     | 0               | 32     |

created; (b)  $assert_f$  is efficiently verified by exploiting  $I^h$ , and  $I^g$  is then built over  $I^h$ ; and (c) finally  $assert_{main}$  is checked against  $I^g$ .

Figure 4 (left) shows FUNFROG's performance with each interpolation algorithm. Each curve represents an interpolation algorithm, and each point on the curve represents one benchmark run using the corresponding interpolation algorithm, with its verification time on the vertical axis. The benchmarks are sorted by their run time. The PS and PS<sub>s</sub> curves are mostly lower than those of the other interpolation algorithms, suggesting they perform better. Table 1 (left) shows the sum of FUNFROG verification time for all benchmarks and the average size of all interpolants generated for all benchmarks for each interpolation algorithm. We also report the relative time and size increase in percents. Both PS and PS<sub>s</sub> are indeed competitive for FUNFROG, delivering interpolants smaller than the other interpolation algorithms.

#### 4.2 Upgrade Checking Using Function Summarization

EVOLCHECK is an Upgrade Checker for C, built on top of FUNFROG. It takes as an input an original program S and its upgrade T sharing the set of functions calls  $\{f\}$ . EVOLCHECK uses the interpolation-based function summaries  $\{I^{S,f}\}$ , constructed for S as shown in Sect. 4.1 to perform upgrade checking. In particular, it verifies whether for each function call f the summary  $I^{S,f}$  overapproximates the precise behavior of T. This local check is turned into showing unsatisfiability of  $\neg I^{S,f} \land A_{T,f}$ , where  $A_{T,f}$  encodes f and its nested calls in T. If proven unsatisfiable, EVOLCHECK applies Craig Interpolation to refine the function summary with respect to T.

*Experiments.* The benchmarks consist of the ones used in the FUNFROG experiments and their upgrades. We only experiment with  $M_s$ , P and  $PS_s$  since EVOLCHECK requires algorithms at least as strong as P. Figure 4 (right) demonstrates that  $PS_s$ , represented by the lower curve, outperforms the other algorithms also for this task. Table 1 (right) shows the total time EVOLCHECK requires to check the upgraded versions of all benchmarks and average interpolant size for each of the three interpolation algorithms. Also for upgrade checking, the interpolation algorithm  $PS_s$  results in smaller interpolants and lower run times compared to the other studied interpolation algorithms.

#### 4.3 Overapproximating Pre-image for Hardware Model Checking

PDTRAV [5] implements several verification techniques including a classical approach of unbounded model checking for hardware designs [13]. Given a design and a property, the approach encodes the existence of a counterexample of a fixed length k into a SAT formula and checks its satisfiability. If the formula is unsatisfiabile, proving that no counterexample of length k exists, Craig interpolation is used to over-approximate the set of reachable states. If the interpolation finds a fixpoint, the method terminates reporting safety. Otherwise, k is incremented and the process is restarted.

*Experiments.* For this experiment, the benchmarks consist of interpolation instances generated by PDTRAV. We compare the effect of applying different interpolation algorithms on the individual steps of the verification procedure.<sup>1</sup>

**Table 2.** Average size and increase relative to the winner for interpolants generated when interpolating over A (top) and B (bottom) in  $A \wedge B$  with PDTRAV.

|            | $M_s$  | Р      | $M_w$  | PS     | $\mathrm{PS}_w$ | $\mathrm{PS}_s$ |

|------------|--------|--------|--------|--------|-----------------|-----------------|

| Avg size   | 683233 | 724844 | 753633 | 683215 | 722605          | 685455          |

| Increase % | 0.003  | 6      | 10     | 0      | 6               | 0.3             |

| Avg size   | 699880 | 694372 | 649149 | 649013 | 650973          | 692434          |

| Increase % | 8      | 7      | 0.02   | 0      | 0.3             | 7               |

<sup>&</sup>lt;sup>1</sup> The forthcoming research question is how interpolants generated using PS affect the convergence. This study is however orthogonal to ours and left for future work.

Table 2 (top) shows the average size of the interpolants generated for all the benchmarks using each interpolation algorithm, and the relative size compared to the smallest interpolant. Also for these approaches the best results are obtained from  $M_s$ , PS and PS<sub>s</sub>, with PS being the overall winner. We note that  $M_s$ performs better than  $M_w$  likely due to the structure of the interpolation instances in these benchmarks: the partition B in  $A \wedge B$  is substantially larger than the partition A. This structure favors algorithms that label many literals as b, since the partial interpolants associated with the clauses in B will be empty while the number of partial interpolants associated with the partitions, interpolating this time over B in  $A \wedge B$  for the same benchmarks resulting in problems where the A part is large. Table 2 (bottom) shows the average size of the interpolants generated for these benchmarks and the relative size difference compared to the winner. Here  $M_w$  and PS<sub>w</sub> perform well, while PS remains the overall winner.

We conclude that the experimental results are compatible with the analysis in Sect. 3. In the FUNFROG and EVOLCHECK experiments,  $PS_s$  outperformed the other interpolation systems with respect to verification time and interpolant size. PDTRAV experiments confirm in addition that PS is very capable in adapting to the problem, giving best results in both cases while the others work well in only one or the other.

#### 4.4 Effects of Simplification

It is interesting to note that in our experiments the algorithm PS was not always the best, and the non-uniform interpolation algorithm PS<sub>s</sub> sometimes produced the smallest interpolant, seemingly contradicting Corollary 1. A possible reason for this anomaly could be in the small difference in how constraint simplification interacts with the interpolant structure. Assume, in Eq. (3), that  $I(C^+)$  or  $I(C^-)$ is either constant true or false. As a result in the first and the second case respectively, the resolvent interpolant size decreases by one in Eq. (3). However in the third case, potentially activated only for non-uniform algorithms, the simplification if one of the antecedents' partial interpolants is false decreases the interpolant size by two, resulting in partial interpolants with smaller internal size. Therefore, in some cases, the good simplification behavior of non-uniform algorithms such as PS<sub>s</sub> seems to result in slightly smaller interpolants compared to PS. We believe that this is also the reason why P behaves better than M<sub>s</sub> and M<sub>w</sub> in some cases.

We also observed (detailed data not shown) that in only five of the benchmarks a labeling function led to interpolants with less distinct variables, the difference between the largest and the smallest number of distinct variables being never over 3 %, suggesting that *p*-annihilable interpolation instances are rare. Finally, we measured the effect of structural sharing. The results (see Appendix A) show that there is no noticeable, consistent difference between any of the algorithms, suggesting that the theory developed in Sect. 3 suffices to explain the experimental observations.

## 5 Conclusion and Future Work

This paper studies the *labeled interpolation system* (LIS), a framework for constructing interpolation algorithms for propositional proofs. In particular, we study how different labeling functions influence the resulting interpolants by analyzing how the choice of labeling affects several size metrics. Based on the results we construct three new interpolation algorithms: the algorithm PS that decides the labeling based on the resolution refutation, and its strong and weak variants. We show that under certain practical assumptions PS results in the smallest interpolants among the framework. Experimentally, when fully integrated with two software model checkers, PS or its stronger variant outperforms widely used algorithms. The results are similarly encouraging when we overapproximate pre-image in unbounded model checking with PS. We believe that this result is due to the size reduction obtained by the new algorithms.

In the future we plan to study why *p*-annihilable proofs are rare and how to make them common. We also plan to integrate our framework more tightly with other model checkers through efficiently exchanging proofs and interpolants.

Acknowledgements. We thank our colleagues Professor Gianpiero Cabodi and Danilo Vendraminetto from the University of Turin, Italy for the benchmarks and instructions related to PDTRAV. This work was funded by the Swiss National Science Foundation (SNSF), under the project #200021\_138078.

### Appendix A Experiments on Simplifications by Structural Sharing

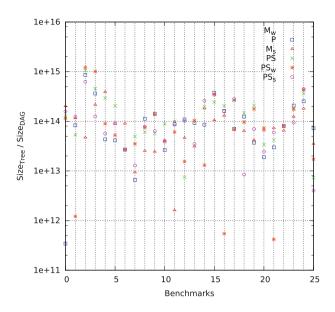

To investigate the effect of structural sharing on simplifications, we analysed two parameters: the number of connectives in an interpolant on its pure tree representation  $(Size_{Tree})$ , and the number of connectives in an interpolant on its DAG representation  $(Size_{DAG})$ , which is the result of the application of structural sharing. Thus, we believe that the ratio  $Size_{Tree}/Size_{DAG}$  is a good way to measure the amount of simplifications due to structural sharing.

Figure 5 shows the results of this analysis on FUNFROG benchmarks. Each vertical line represents a benchmark, and each point on this line represents the ratio  $Size_{Tree}/Size_{DAG}$  of the interpolant generated by each of the interpolation algorithms for the first assertion of that benchmark. The reason why only the first assertion is considered is that from the second assertion on, summaries (that is, interpolants) are used instead of the original code, and therefore it is not guaranteed that the refutations will be the same when different interpolation algorithms are applied.

It is noticeable that the existence of more/less simplifications is not related to the interpolation algorithms, since all of them have cases where many/few simplifications happen. Therefore, there is no difference between any of the algorithms with respect to structural sharing.

17

Fig. 5. Relation  $Size_{Tree}/Size_{DAG}$  on FUNFROG benchmarks for different interpolation algorithms

#### References

- Albarghouthi, A., McMillan, K.L.: Beautiful interpolants. In: Sharygina, N., Veith, H. (eds.) CAV 2013. LNCS, vol. 8044, pp. 313–329. Springer, Heidelberg (2013)

- Alberti, F., Bruttomesso, R., Ghilardi, S., Ranise, S., Sharygina, N.: Lazy abstraction with interpolants for arrays. In: Bjørner, N., Voronkov, A. (eds.) LPAR-18 2012. LNCS, vol. 7180, pp. 46–61. Springer, Heidelberg (2012)

- Bloem, R., Malik, S., Schlaipfer, M., Weissenbacher, G.: Reduction of resolution refutations and interpolants via subsumption. In: Yahav, E. (ed.) HVC 2014. LNCS, vol. 8855, pp. 188–203. Springer, Heidelberg (2014)

- Cabodi, G., Lolacono, C., Vendraminetto, D.: Optimization techniques for Craig interpolant compaction in unbounded model checking. In: DATE, pp. 1417–1422 (2013)

- Cabodi, G., Murciano, M., Nocco, S., Quer, S.: Stepping forward with interpolants in unbounded model checking. In: ICCAD, pp. 772–778 (2006)

- Cabodi, G., Palena, M., Pasini, P.: Interpolation with guided refinement: revisiting incrementality in SAT-based unbounded model checking. In: FMCAD, pp. 43–50 (2014)

- Chockler, H., Ivrii, A., Matsliah, A.: Computing interpolants without proofs. In: Biere, A., Nahir, A., Vos, T. (eds.) HVC. LNCS, vol. 7857, pp. 72–85. Springer, Heidelberg (2013)

- D'Silva, V.: Propositional interpolation and abstract interpretation. In: Gordon, A.D. (ed.) ESOP 2010. LNCS, vol. 6012, pp. 185–204. Springer, Heidelberg (2010)

- D'Silva, V., Kroening, D., Purandare, M., Weissenbacher, G.: Interpolant strength. In: Barthe, G., Hermenegildo, M. (eds.) VMCAI 2010. LNCS, vol. 5944, pp. 129– 145. Springer, Heidelberg (2010)

- Fedyukovich, G., Sery, O., Sharygina, N.: eVolCheck: incremental upgrade checker for C. In: Piterman, N., Smolka, S.A. (eds.) TACAS 2013 (ETAPS 2013). LNCS, vol. 7795, pp. 292–307. Springer, Heidelberg (2013)

- Fontaine, P., Merz, S., Woltzenlogel Paleo, B.: Compression of propositional resolution proofs via partial regularization. In: Bjørner, N., Sofronie-Stokkermans, V. (eds.) CADE 2011. LNCS, vol. 6803, pp. 237–251. Springer, Heidelberg (2011)

- Jancík, P., Kofron, J., Rollini, S.F., Sharygina, N.: On interpolants and variable assignments. In: FMCAD, pp. 123–130 (2014)

- McMillan, K.L.: Interpolation and SAT-based model checking. In: Hunt Jr. W.A., Somenzi, F. (eds.) CAV 2003. LNCS, vol. 2725, pp. 1–13. Springer, Heidelberg (2003)

- McMillan, K.L.: An interpolating theorem prover. In: Jensen, K., Podelski, A. (eds.) TACAS 2004. LNCS, vol. 2988, pp. 16–30. Springer, Heidelberg (2004)

- McMillan, K.L.: Lazy annotation revisited. In: Biere, A., Bloem, R. (eds.) CAV 2014. LNCS, vol. 8559, pp. 243–259. Springer, Heidelberg (2014)

- Pudlák, P.: Lower bounds for resolution and cutting plane proofs and monotone computations. J. Symbolic Logic 62(3), 981–998 (1997)

- Rollini, S.F., Alt, L., Fedyukovich, G., Hyvärinen, A.E.J., Sharygina, N.: PeRIPLO: a framework for producing effective interpolants in SAT-based software verification. In: McMillan, K., Middeldorp, A., Voronkov, A. (eds.) LPAR-19 2013. LNCS, vol. 8312, pp. 683–693. Springer, Heidelberg (2013)

- Rollini, S.F., Sery, O., Sharygina, N.: Leveraging interpolant strength in model checking. In: Madhusudan, P., Seshia, S.A. (eds.) CAV 2012. LNCS, vol. 7358, pp. 193–209. Springer, Heidelberg (2012)

- 19. Rümmer, P., Subotic, P.: Exploring interpolants. In: FMCAD, pp. 69-76 (2013)

- Sery, O., Fedyukovich, G., Sharygina, N.: FunFrog: bounded model checking with interpolation-based function summarization. In: Chakraborty, S., Mukund, M. (eds.) ATVA 2012. LNCS, vol. 7561, pp. 203–207. Springer, Heidelberg (2012)

- Vizel, Y., Ryvchin, V., Nadel, A.: Efficient generation of small interpolants in CNF. In: Sharygina, N., Veith, H. (eds.) CAV 2013. LNCS, vol. 8044, pp. 330–346. Springer, Heidelberg (2013)

## Recursive Games for Compositional Program Synthesis

Tewodros A. Beyene<sup>1(⊠)</sup>, Swarat Chaudhuri<sup>2</sup>, Corneliu Popeea<sup>1</sup>, and Andrey Rybalchenko<sup>3</sup>

> <sup>1</sup> TU München, Munich, Germany beyene@in.tum.de

>  <sup>2</sup> Rice University, Texas, USA

>  <sup>3</sup> Microsoft Research, Cambridge, UK

**Abstract.** Compositionality, i.e., the use of procedure summarization instead of code inlining, is key to scaling automated verification to large code bases. In this paper, we present a way to exploit compositionality in the context of *program synthesis*.

The goal in our synthesis problem is to instantiate missing expressions in a procedural program so that the resulting program satisfies a safety or termination requirement in spite of an adversarial environment. The problem is modeled as a game between two players — the program and the environment — that take turns changing the program's state and stack. The objective of the program is to ensure that all executions of this recursive game satisfy the requirement. Synthesis involves the modular computation of a strategy under which the program meets this objective. Our solution is based on the notion of *game summaries*, which generalize traditional procedure summaries, and relate program states in a procedural context with sets of states at which the game can return from that context. Our method for compositional reasoning about game summaries is embodied in a set of deductive proof rules. We prove these rules sound and relatively complete. We also show that a sound approximation of these rules can be automated using a Horn constraint solver that utilizes SMT-solving, counterexample-guided abstraction refinement, and interpolation. An experimental evaluation over a set of systems code benchmarks demonstrates the practical promise of the approach.

#### 1 Introduction

The last decade has seen remarkable advances in automated software verification [6,39]. An essential lesson from these developments is that to be scalable, techniques for reasoning about software need to be *compositional*. In other words, an analysis for a large program needs to be constructed from analyses for modules (commonly, procedures) in the program.

Specifically, successful software analysis tools like SLAM [6] and SATURN [39] use *procedure summarization* [32] to compositionally analyze large systems code bases. The idea here is to compute, for each procedure **p** in a program, a *summary*: a reachability relation between the input and output states of **p**. If **p** calls

<sup>©</sup> Springer International Publishing Switzerland 2016

A. Gurfinkel and S.A. Seshia (Eds.): VSTTE 2015, LNCS 9593, pp. 19–39, 2016. DOI: 10.1007/978-3-319-29613-5\_2

a procedure q, then the summary of q is used to compute the summary of p. The approach can handle recursion: if p and q are mutually recursive, then the relationship between the summaries of p and q is given by a system of recursive equations. To compute summaries of p and q, we find a fixpoint of this system.

The use of summaries in automated verification of programs is, by now, wellunderstood [2, 13]. Less is known about the use of summarization in the emerging setting of *automated program synthesis* [7, 25, 34, 35]. The goal in synthesis is to generate missing expressions in a partial program so that a set of requirements are satisfied. The problem is naturally framed in terms of a graph game [15]. This game involves two players — the program and its environment — who take turns changing the state and stack of the program. The program wins the game if all executions of the game satisfy a user-defined requirement, no matter how the environment behaves. Synthesis amounts to the computation of a strategy that ensures victory for the program.

There is a large literature, going back to the 1960s, on game-theoretic program synthesis [11,30,36]. However, most of these approaches are: (1) restricted to the synthesis of programs over finite data domains; and (2) do not support compositional reasoning about procedural programs. While a recent paper [7] offers a synthesis method that permits programs over unbounded data, it does not support compositional reasoning. An approach for *recursive infinite-state* games — games played on the configuration graphs of programs with recursion and unbounded data — has remained elusive so far.

In this paper, we present such an approach. The key idea here is a generalization of traditional summaries, called *game summaries*, that allow compositional reasoning about strategies in the presence of procedures and recursion. Our contributions include a set of sound and complete rules for compositional, deductive synthesis using game summaries, and a way to automate a sound approximation to these rules on top of an existing automated deduction system.

Concretely, a game summary sum for a program is a relation that relates states of the program to *sets of states*. For a state s and a set of states f, we have sum(s, f) whenever:

- 1. s is a reachable state.

- 2. Suppose the game starts from s in a certain procedural context. Then the program has a strategy to ensure that in all executions of game, the *first unmatched return state* the state to which the game returns from the initial context is in f.

The genereralization to game summaries is called for as the use of traditional summaries leads to incompleteness in the game setting. Game summaries were previously explored in branching-time model checking of pushdown systems [3–5], but their use in synthesis, or for that matter analysis of infinite-state programs, is new.

Our proof rules for compositional inference of game summaries utilize quantifier alternation: an existential quantifier is used to nondeterministically guess moves for the program, and a universal quantifier is used to capture the adversarial environment. The quantifiers are second-order because summaries are higher-order relations relating states to sets. As in the traditional verification setting, a summary sum is propagated across procedure calls and returns through inductive reasoning. The computation exploits compositionality: to generate the parts of sum involving states of a procedure **q**, the rule generates the parts of the summary that involve procedures that **q** calls, and adds these summaries to sum once and for all. Like the corresponding proof rules for verification, the rule is agnostic to whether the input transition relations encode recursion.

To verify that a safety property p is satisfied in all executions of the game, we show that for all s, f such that sum(s, f), s satisfies p. A winning strategy for the program is obtained as an instantiation of the existential quantifiers used in the deduction. Synthesis with respect to termination requirements necessitates the additional use of a disjunctively well-founded transition invariant [31].

We show that our rules are sound, meaning that if they derive a strategy, then the program actually wins under the strategy. They are also relatively complete, meaning that the rules can always derive a winning strategy when one exists, assuming a suitably powerful language of assertions over local and global program variables. Importantly, this completeness proof does not require an encoding of the stack using auxiliary program variables.

We present an implementation RECSYNTH of a sound approximation to our rules on top of an existing automated deduction engine. Specifically, our implementation RECSYNTH feeds our proof rules to the EHSF engine for solving constraints in the form of Horn-like clauses that permit existential quantification in clause heads [8]. Solving the repair problem now amounts to finding an interpretation to unknown sets and relations over program variables. EHSF performs this task with some guidance from user-provided templates, and by using a combination of counterexample-guided abstraction-refinement (CEGAR), interpolation and SMT-solving.

We evaluate RECSYNTH on an array of systems programs, including device driver benchmarks drawn from the SV-COMP software verification competition [9]. Some of our benchmarks contain up to 11 K lines of C code structured into up to 181 procedures. For each of these benchmarks, we set up a synthesis problem by starting with a device driver that satisfies its requirements and eliding certain expressions from the code. Our tool is now used to find values of these expressions so that the resulting code satisfies its specification.

The experimental results are promising: in most cases, RECSYNTH is able to return successfully within a minute, depending on amount of nondeterminism to be resolved. The exploitation of compositionality is essential to these results, as inlining procedures in these examples would lead to programs that are so large as to be beyond the reach of existing program verifiers, let alone known repair/synthesis techniques.

Now we summarize the main contributions of the paper:

- We present an approach to the compositional, deductive synthesis of programs with infinite data domains as well as recursion. The method is based on the use of the new notion of *game summaries*. We give a set of sound and complete proof rules for synthesis using game summaries under safety and termination requirements. - We offer an implementation (called RECSYNTH) of a sound but incomplete approximation of our inference rules on top of the EHSF deduction engine. We illustrate the promise of the system using an array of challenging benchmarks running into thousands of lines of code.

#### 2 Motivation

Our program synthesis problem can be viewed as a game [15] between two players: a program player, whose goal is to satisfy the program's correctness requirements, and an environment player, which aims to prevent the program player from doing so. The two players take turns changing the configuration (state and stack) of the program. The transitions of the program come from the user-supplied partial program, with nondeterminism used to capture our lack of knowledge of certain expressions. The environment's transitions model inputs that a hostile outside world feeds to the program. As the game is played on the configuration graph of a recursive program, we call it a recursive game. Our goal is to find a winning strategy for the program player, i.e., to reduce the nondeterminism in the program's transitions so that the resulting program satisfies the requirements no matter what the environment does.

Now we show that the standard notion of summaries, ubiquitous in verification of programs with procedures, can be inadequate when solving recursive games.

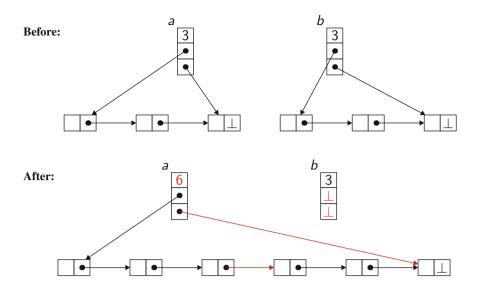

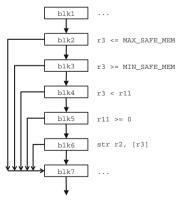

We consider the source code in Fig. 1 that describes an interaction between an environment player that controls all statement except at line P and the program player that only controls the non-deterministic assignment statement at line P. The goal of the program player is to find a strategy that resolves the non-determinism at line P such that regardless of how the environment player resolves the non-determinism at line E the assertion is always satisfied.

We observe that a standard summary for foo can only relate values of the variables in scope foo at the start and exit states of its execution. That is, if a triple (x, y, pc) represents a program state then we obtain the following summary for foo.

$$sum((x, y, pc), (x', y', pc)) = (pc = \mathbf{P} \land x' = x \land (y' = 0 \lor y' = 1) \land pc' = \mathbf{S})$$

```

void main(void) {

int x=-1, y=-1;

E:

if (env_nondet()) {

int foo() {

foo();

A :

P:

if (prog_nondet()) {

B:

x = 0;

Q:

y = 0;

} else {

} else {

C:

foo();

R:

y = 1;

D:

x = 1;

}

}

S: }

F :

assert( x == y );

}

```

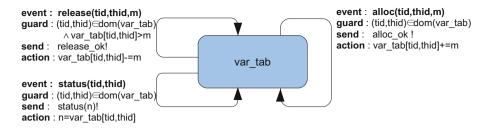

Fig. 1. Program that exhibits inadequacy of summaries used for verification purposes for solving games.

Hence, when reasoning about the (existence of) winning strategy for the program player we lack crucial information about the calling context in which foo is executed. As a result, the summary for foo cannot distinguish if the top of the stack stores the value A or C for the program counter of main. That is, when applying sum((x, y, pc), (x', y', pc)) in the calling context with pc = A, we obtain a state in which  $y = 0 \lor y = 1$ . Hence the subsequent assignment x = 1; leads to an assertion violation.

In contrast, when applying the notion of game summaries we relate each entry state of foo with states of main at the return sites A and C. Thus, the game summary can discriminate between the call site on the branch that executes x = 0; and the call site on the branch with x = 1;. As a result out method is able to identify a winning strategy for the program player.

#### **3** Preliminaries

In this section, we formally define programs, games, and our synthesis problem.

Procedural Programs. A program consists of a finite set of procedures P, where  $main \in P$  is a distinguished main procedure. For simplicity we assume that the program has no global variables (yet these can be easily added at the expense of lengthier presentation). Let v be a tuple of local variables that are in scope of each procedure.

We use an assertion init(v) to describe the initial valuation of the local variables of main, that is, we assume there is only one such evaluation. We use step(v, v') to represent intra-procedural transitions of all program procedures, i.e., the union of intra-procedural transition relations of all procedures. An assertion call(v, v') represents argument passing transitions of all call sites, i.e., the union of argument passing transition relations at all call sites in the program. The left diagram below shows how the valuation of the program variables in scope changes during a call transition. For simplicity, we assume that the valuation of global variables can be modified during the argument passing.

For return value passing we use the relation ret(v, v'', v') where v represents the callee state at the exit location, v'' represents caller's state at the corresponding call site, and v' is result of passing the return value (while keeping caller's local variables unchanged) and advancing the caller's program counter value beyond the call site. To model the fact that only local states are put on the stack, we assume that only the local variables of v'' occur in the return value passing relation. The right diagram above shows how the valuation of the program variables in scope changes during a return transition. We assume that an assertion safe(v) represents a set of safe valuations, and thus provides the means for specifying temporal safety properties.

Recursive Games. We model the interaction between the program and its environment as a recursive game: a game where two players  $\operatorname{Prog}$  and  $\operatorname{Env}$  (standing respectively for the program and the environment) take turns in performing computation steps<sup>1</sup>. In this paper, we assume that  $\operatorname{Env}$  executes call and return transitions, as well as some of the intra-procedural steps. We capture two-player games by modifying our definition of programs as follows. We assume that instead of the monolithic intraprocedural transition relation step(v, v'), we are given two separate transition relations, prog(v, v') and env(v, v'), respectively belonging to  $\operatorname{Prog}$  and  $\operatorname{Env}$ . Among the intra-procedural steps we assume a strict alternation between  $\operatorname{Prog}$  and  $\operatorname{Env}$ . That is, when considering an intraprocedural segment of the computation we assume that the first step executed in the environment, the second step is executed by the program, and so on.

Our partition of computation steps into program and environment steps is chosen to simplify the presentation in the following sections, however it does not restrict the applicability of our results. For example, in a similar way we can model the scenario where the roles of the program and the environment are exchanged, i.e., the program controls calls and returns while the environment controls some of the intra-procedural steps.