# Ahmet Bindal · Sotoudeh Hamedi-Hagh

# Silicon Nanowire Transistors

Silicon Nanowire Transistors

Ahmet Bindal • Sotoudeh Hamedi-Hagh

# Silicon Nanowire Transistors

Ahmet Bindal Computer Engineering Department San Jose State University San Jose, CA, USA Sotoudeh Hamedi-Hagh Electrical Engineering Department San Jose State University San Jose, CA, USA

ISBN 978-3-319-27175-0 ISBN 978-3-319-27177-4 (eBook) DOI 10.1007/978-3-319-27177-4

Library of Congress Control Number: 2015959712

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

This book is dedicated to my all-time mentor and friend Dr. Seiki Ogura whose constant encouragement to my well-being will never be forgotten.

Dr. Ahmet Bindal

I dedicate this book to my loving family who have always been a constant source of support and happiness.

Dr. Sotoudeh Hamedi-Hagh

## Preface

When we started exploring the possibility of using Silicon Nanowire Transistors (SNT) for the next-generation VLSI technology, we were initially quite uncertain in its outcome. The early device simulations did not reveal superior device performance compared to FinFETs. Besides, there was an issue of channel doping. Even high concentrations of Arsenic (and Boron) were able to replace only several dopant atoms in the MOSFET body. This created a serious problem in threedimensional device simulations. The sequence of failures and disappointing results motivated us to look at alternative device designs. We used intrinsic silicon for the body of the device and changed the gate material from conventional polysilicon to metal to be able to adjust the gate work function and the threshold voltage. This approach also helped to eliminate short channel effects of the transistor; however, it also made the device fabrication steps in simulations more difficult due to the metal gate. Previous annealing steps used after the gate deposition step could not be used once the metal gate was deposited. The heat management became a critical issue and required several changes in the fabrication in order to form the vertical gate structure.

It was not until we created the level 6 SPICE models for n- and p-channel SNTs and used them in basic digital gates, we could observe the real potential of SNTs in circuit performance and power consumption. Motivated primarily by the power consumption results, we subsequently replaced the level 6 models with the more accurate BSIMSOI models in the next phase of our research in designing analog and digital circuits.

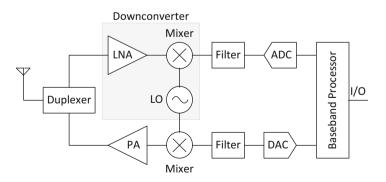

The organization of chapters pretty much follows the progression of our fiveyear long research. Chapters 1 and 2 examine the device design and characteristics of SNTs with dual and single work-function metal gates. Each of these chapters studies and measures the circuit performance and power consumption of basic digital gates with extrinsic device parasitics. The layout area of each gate is also included in each chapter and compared with various digital gates built with FinFETs. Chapter 3 examines the BSIMSOI SPICE model and all the intrinsic and extrinsic parasitic components of SNTs. High-speed analog applications are studied in Chapter 4 where SNTs are used in a single-stage amplifier, a differential pair, and a multi-stage operational amplifier. Chapter 5 examines the Radio Frequency (RF) applications. In this chapter, we presented the front end of an RF receiver and a Voltage-Controlled Amplifier (VGA). In Chapters 6 through 9, SNTs are used in various mega cells and complex digital systems. A complete Static Random Access Memory (SRAM) design and its layout are studied in Chapter 6. A Field-Programmable-Gate-Array (FPGA) architecture, circuit characteristics and layout in Chapter 7, an Integrate-and-Fire Spiking (IFS) neuron in Chapter 8, and a complete Direct Sequence Spread Spectrum (DSSS) baseband transmitter design in Chapter 9 are given to fully understand the implications of using SNTs in large-scale digital systems.

We firmly believe that SNTs are good candidates for the future of VLSI once the inherent complexities of device fabrication are overcome.

Dr. Ahmet Bindal Dr. Sotoudeh Hamedi-Hagh

# Contents

| 1 | Dua  | l Work   | Function Silicon Nanowire MOS Transistors     | 1  |

|---|------|----------|-----------------------------------------------|----|

|   | 1.1  | Device   | e Design                                      | 1  |

|   |      | 1.1.1    | Introduction to Design Process                | 1  |

|   |      | 1.1.2    | The Criteria for Low Static Power Dissipation | 3  |

|   |      | 1.1.3    | Device Structure                              | 4  |

|   |      | 1.1.4    | Physical Models Used in Device Simulations    | 4  |

|   |      | 1.1.5    | Determining Metal Gate Work Function Values   |    |

|   |      |          | for NMOS and PMOS Transistors                 | 5  |

|   |      | 1.1.6    | The OFF Current Requirement                   | 6  |

|   |      | 1.1.7    | Intrinsic Transient Time                      | 6  |

|   |      | 1.1.8    | DC Device Characteristics                     | 9  |

|   | 1.2  | Circui   | t Simulations and Performance                 | 13 |

|   |      | 1.2.1    | Parasitic Extraction and Post-layout Issues   | 13 |

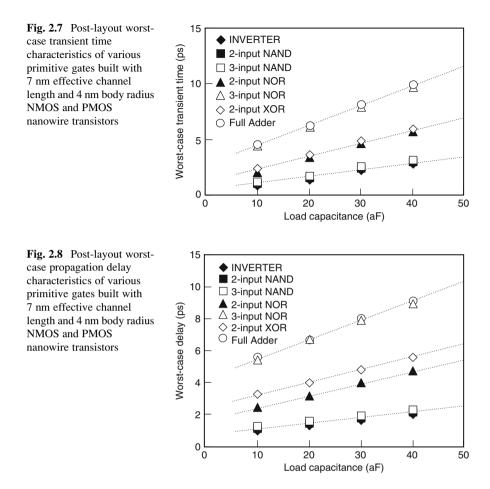

|   |      | 1.2.2    | Transient Performance                         | 15 |

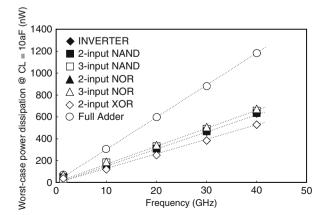

|   |      | 1.2.3    | Power Dissipation                             | 17 |

|   |      | 1.2.4    | Cell Layout and Gate Area Estimations         | 18 |

|   |      | 1.2.5    | Manufacturability                             | 20 |

|   | 1.3  | Summ     | ary                                           | 23 |

|   | Refe | erences. |                                               | 24 |

| 2 | Sing | le Wor   | k Function Silicon Nanowire MOS Transistors   | 27 |

|   | 2.1  | Device   | e Design                                      | 27 |

|   |      | 2.1.1    | Purpose                                       | 27 |

|   |      | 2.1.2    | The Criteria for Low Static Power Dissipation | 28 |

|   |      | 2.1.3    | Device Structure                              | 28 |

|   |      | 2.1.4    | Physical Models Used in Device Simulations    | 28 |

|   |      | 2.1.5    | Determining a Single Metal Gate Work Function | 29 |

|   |                                                | 2.1.6 The OFF Current Requirement for the Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                           |

|---|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   |                                                | 2.1.7 Transistor Transient Characteristics:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|   |                                                | Intrinsic Transient Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                                                                                           |

|   |                                                | 2.1.8 DC Characteristics of the Selected NMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|   |                                                | and PMOS Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32                                                                                           |

|   | 2.2                                            | Circuit Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33                                                                                           |

|   |                                                | 2.2.1 Parasitic Extraction and Post-layout Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                           |

|   |                                                | 2.2.2 Transient Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34                                                                                           |

|   |                                                | 2.2.3 Dynamic Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                           |

|   |                                                | 2.2.4 Cell Layout Area Estimations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                           |

|   |                                                | 2.2.5 Full Adder Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                                           |

|   | 2.3                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39                                                                                           |

|   | Refe                                           | prences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                           |

| 3 | SPI                                            | CE Modeling for Analog and Digital Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                                           |

|   | 3.1                                            | BSIMSOI Device Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                                                                           |

|   |                                                | 3.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43                                                                                           |

|   |                                                | 3.1.2 The Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                                                                           |

|   |                                                | 3.1.3 Intrinsic Modeling and Parasitic Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                                           |

|   |                                                | 3.1.4 Extrinsic Modeling and Parasitic Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                                                           |

|   | 3.2                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                                                                           |

|   | Refe                                           | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                                                                           |

| 4 | Higl                                           | h-Speed Analog Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                           |

| - | 4.1                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                                           |

|   | 4.2                                            | Brief Description of Transistor Design and Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61                                                                                           |

|   | 4.3                                            | Single-Stage CMOS SNT Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                                           |

|   |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 02                                                                                         |

|   |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

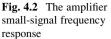

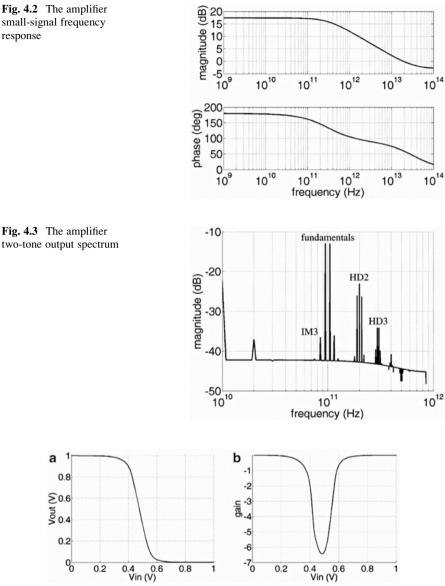

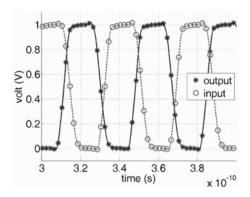

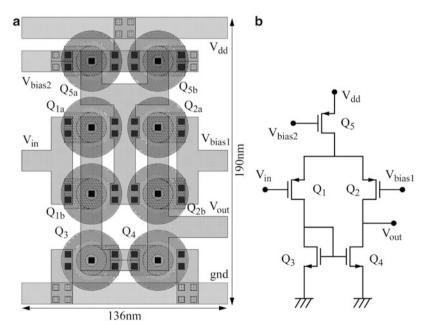

|   |                                                | 4.3.1 The CMOS Amplifier Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62<br>62<br>63                                                                               |

|   | 4.4                                            | <ul><li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                                           |

|   | 4.4                                            | <ul><li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62<br>63                                                                                     |

|   | 4.4                                            | <ul> <li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66                                                                               |

|   | 4.4<br>4.5                                     | <ul> <li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66<br>66                                                                         |

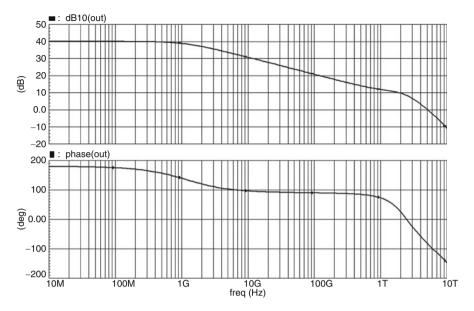

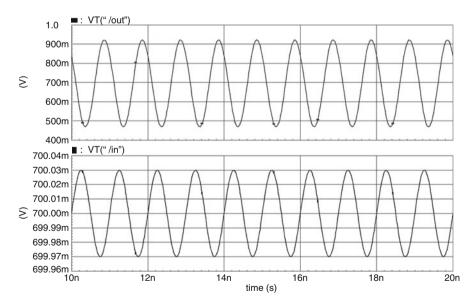

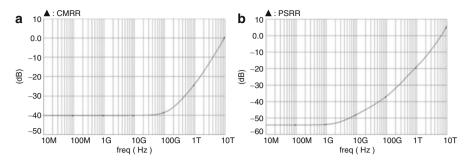

|   |                                                | 4.3.1The CMOS Amplifier Design4.3.2The Characteristics of the CMOS AmplifierDifferential SNT Amplifier4.4.1A Single-Stage Differential Amplifier Design4.4.2The Characteristics of the Differential AmplifierMulti-stage SNT Operational Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66<br>66<br>67                                                                   |

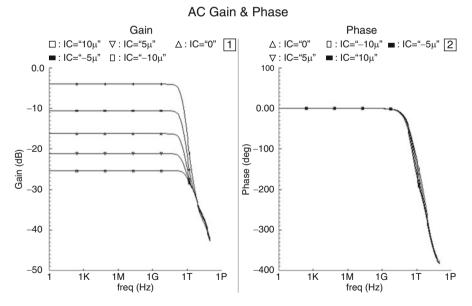

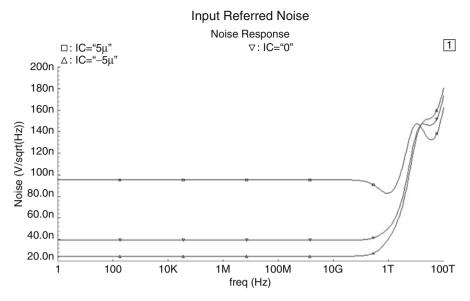

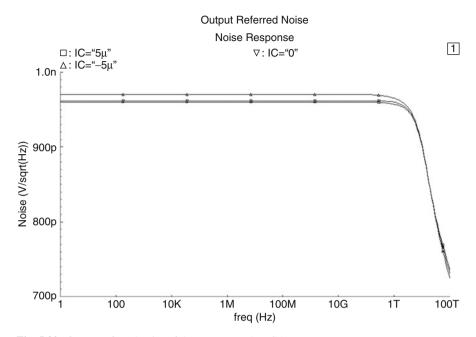

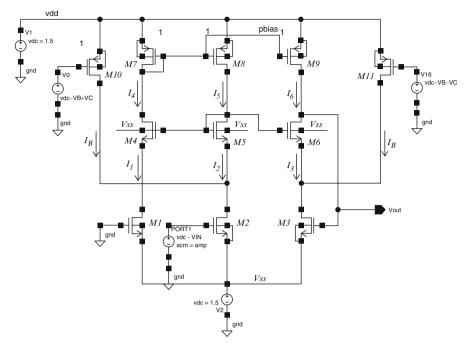

|   |                                                | <ul> <li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66<br>66<br>67<br>69                                                             |

|   |                                                | <ul> <li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66<br>66<br>67<br>69<br>69                                                       |

|   | 4.5<br>4.6                                     | <ul> <li>4.3.1 The CMOS Amplifier Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62<br>63<br>66<br>67<br>69<br>69<br>77                                                       |

| 5 | 4.5<br>4.6<br>Refe                             | 4.3.1The CMOS Amplifier Design4.3.2The Characteristics of the CMOS AmplifierDifferential SNT Amplifier4.4.1A Single-Stage Differential Amplifier Design4.4.2The Characteristics of the Differential Amplifier4.4.2The Characteristics of the Differential Amplifier4.5.1A Two-Stage Operational Amplifier Design4.5.2Characteristics of the Operational AmplifiersummarySummary                                                                                                                                                                                                                                                                                                                                                                                                                       | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81                                           |

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b>               | 4.3.1 The CMOS Amplifier Design         4.3.2 The Characteristics of the CMOS Amplifier         Differential SNT Amplifier         4.4.1 A Single-Stage Differential Amplifier Design         4.4.2 The Characteristics of the Differential Amplifier         Multi-stage SNT Operational Amplifier         4.5.1 A Two-Stage Operational Amplifier Design         4.5.2 Characteristics of the Operational Amplifier         Summary         erences         io Frequency (RF) Applications                                                                                                                                                                                                                                                                                                          | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83                                     |

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1        | 4.3.1 The CMOS Amplifier Design         4.3.2 The Characteristics of the CMOS Amplifier         Differential SNT Amplifier         4.4.1 A Single-Stage Differential Amplifier Design         4.4.2 The Characteristics of the Differential Amplifier         Multi-stage SNT Operational Amplifier         4.5.1 A Two-Stage Operational Amplifier Design         4.5.2 Characteristics of the Operational Amplifier         Summary         Summary         Introduction                                                                                                                                                                                                                                                                                                                            | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83                               |

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1<br>5.2 | 4.3.1       The CMOS Amplifier Design         4.3.2       The Characteristics of the CMOS Amplifier         Differential SNT Amplifier       Differential SNT Amplifier         4.4.1       A Single-Stage Differential Amplifier Design         4.4.2       The Characteristics of the Differential Amplifier         Multi-stage SNT Operational Amplifier       Multi-stage Operational Amplifier Design         4.5.1       A Two-Stage Operational Amplifier Design         4.5.2       Characteristics of the Operational Amplifier         Summary       Summary         berences       Introduction         Brief Description of Transistor Design and Modeling       Modeling                                                                                                                | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83<br>83                         |

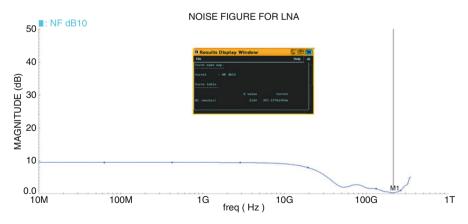

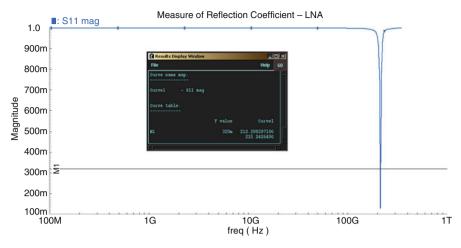

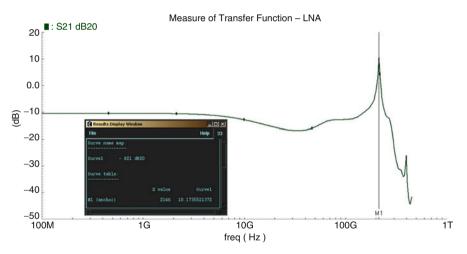

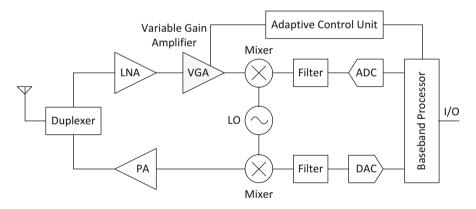

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1        | 4.3.1       The CMOS Amplifier Design         4.3.2       The Characteristics of the CMOS Amplifier         Differential SNT Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83<br>83<br>83<br>83             |

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1<br>5.2 | 4.3.1       The CMOS Amplifier Design         4.3.2       The Characteristics of the CMOS Amplifier         Differential SNT Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83<br>83<br>83<br>84<br>84       |

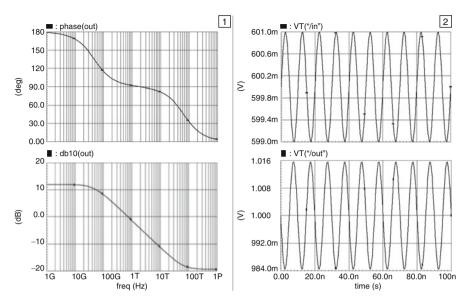

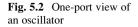

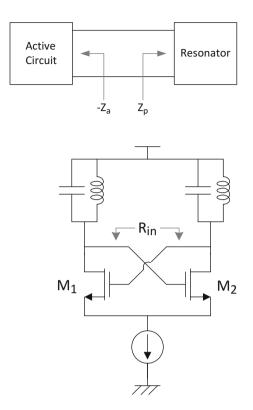

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1<br>5.2 | 4.3.1       The CMOS Amplifier Design         4.3.2       The Characteristics of the CMOS Amplifier         Differential SNT Amplifier       Differential SNT Amplifier         4.4.1       A Single-Stage Differential Amplifier Design         4.4.2       The Characteristics of the Differential Amplifier         Multi-stage SNT Operational Amplifier       Multi-stage SNT Operational Amplifier         4.5.1       A Two-Stage Operational Amplifier Design         4.5.2       Characteristics of the Operational Amplifier         Summary       Summary         erences       Introduction         Brief Description of Transistor Design and Modeling       RF Receiver Front End         5.3.1       Receiver Topology         5.3.2       LC Tank Voltage-Controlled Oscillator (VCO) | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83<br>83<br>83<br>84<br>84<br>84 |

| 5 | 4.5<br>4.6<br>Refe<br><b>Rad</b><br>5.1<br>5.2 | 4.3.1       The CMOS Amplifier Design         4.3.2       The Characteristics of the CMOS Amplifier         Differential SNT Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>63<br>66<br>67<br>69<br>69<br>77<br>80<br>81<br>83<br>83<br>83<br>83<br>84<br>84       |

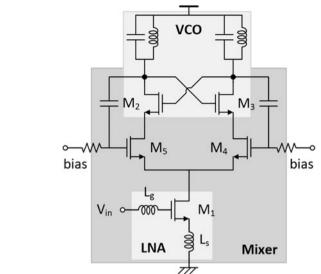

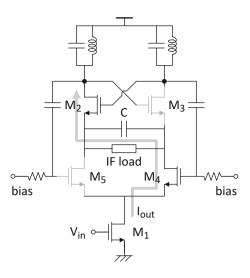

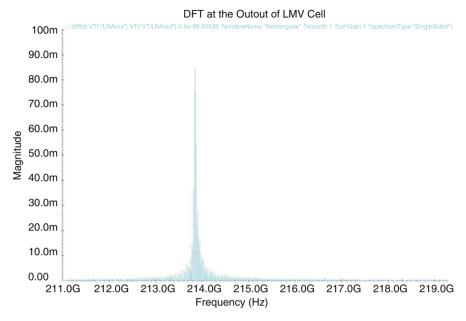

|   |      | 5.3.5   | LNA-Mixer-VCO (LMV) Cell                      | 88  |

|---|------|---------|-----------------------------------------------|-----|

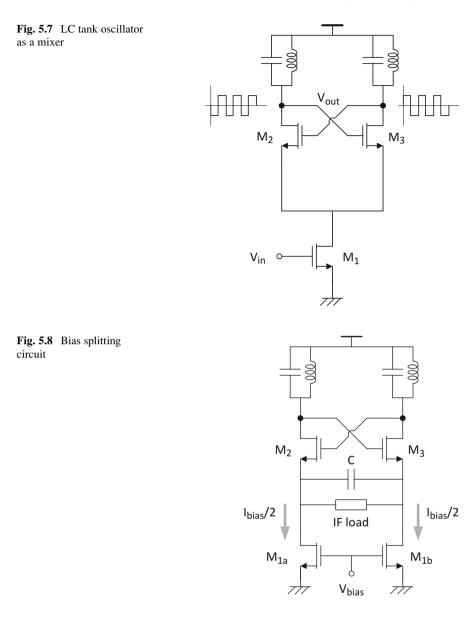

|   |      | 5.3.6   | LC Tank Oscillator as a Mixer                 | 89  |

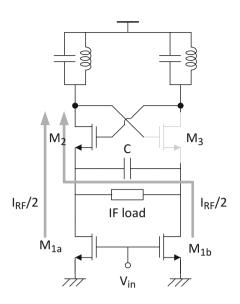

|   |      | 5.3.7   | Bias Splitting Self-Oscillating Mixer (SOM)   | 89  |

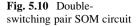

|   |      | 5.3.8   | Design of Double-Switching Self-Oscillating   |     |

|   |      |         | Degeneration LMV Cell Using SNTs              | 93  |

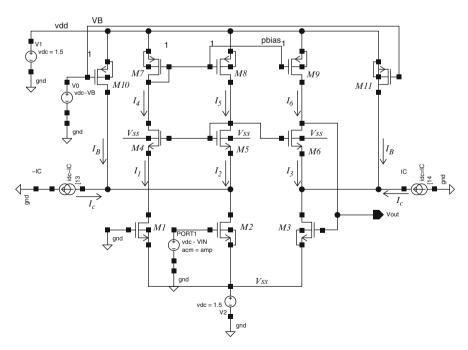

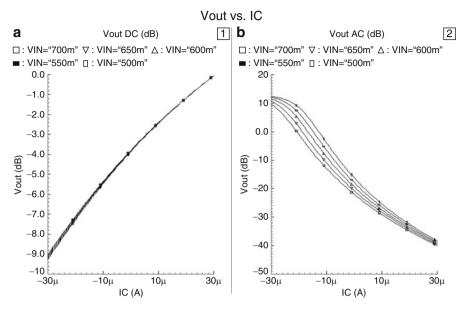

|   | 5.4  | Varial  | ble Gain Amplifier (VGA)                      | 94  |

|   |      | 5.4.1   | Introduction to VGA                           | 94  |

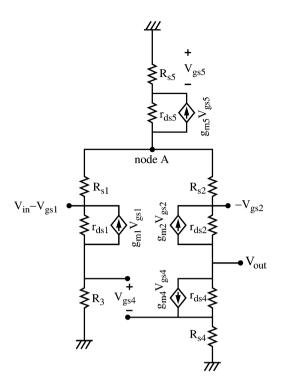

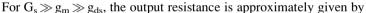

|   |      | 5.4.2   | Current-Mode Topology                         | 96  |

|   |      | 5.4.3   | Voltage-Mode Topology                         | 99  |

|   | 5.5  | Summ    | nary                                          | 104 |

|   | Refe | erences |                                               | 105 |

| 6 | SRA  | M Me    | ga Cell Design for Digital Applications       | 107 |

|   | 6.1  |         | luction                                       | 107 |

|   | 6.2  | Brief   | Description of Transistor Design and Modeling | 107 |

|   | 6.3  |         | / Design                                      | 108 |

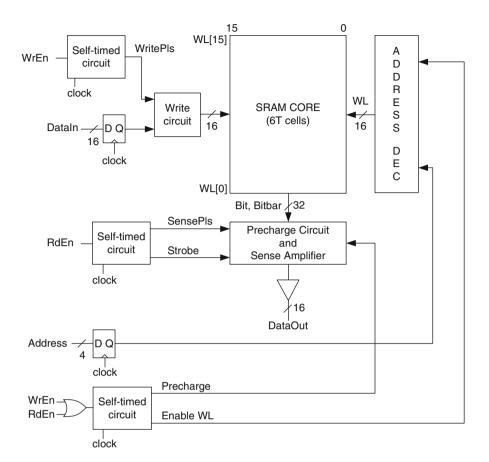

|   |      | 6.3.1   | SRAM Architecture                             | 108 |

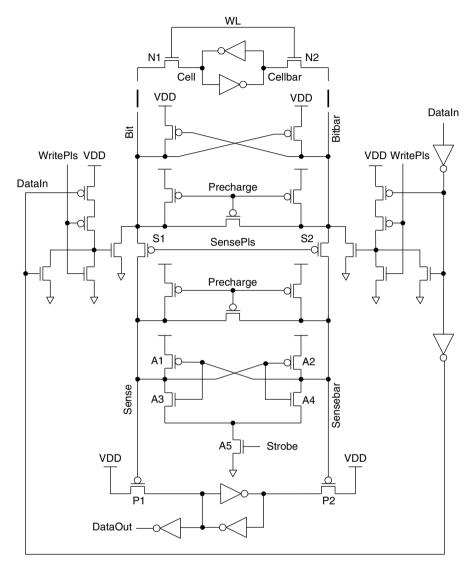

|   |      | 6.3.2   | SRAM Core                                     | 108 |

|   |      | 6.3.3   | Address Decoder                               | 111 |

|   |      | 6.3.4   | Self-Timed Circuits                           | 112 |

|   | 6.4  | SRAN    | A Characteristics                             | 116 |

|   |      | 6.4.1   | Parasitic Layout Extraction                   | 116 |

|   |      | 6.4.2   | Read and Write Access Times                   | 116 |

|   |      | 6.4.3   | Power Dissipation                             | 118 |

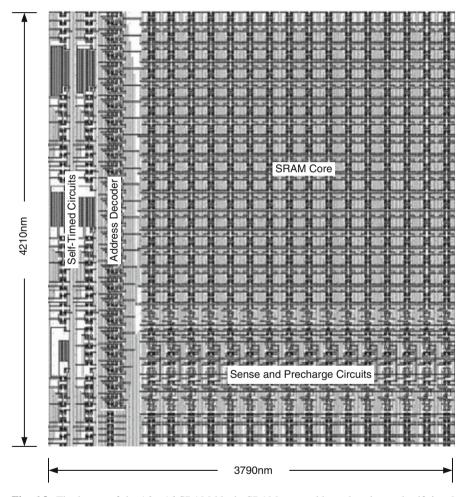

|   |      | 6.4.4   | SRAM Layout                                   | 119 |

|   | 6.5  | Summ    | nary                                          | 120 |

|   | Refe | erences |                                               | 120 |

| 7 | Fiel | d-Prog  | rammable-Gate-Array (FPGA)                    | 121 |

|   | 7.1  | Introd  | luction                                       | 121 |

|   | 7.2  | Brief   | Description of Transistor Design and Modeling | 121 |

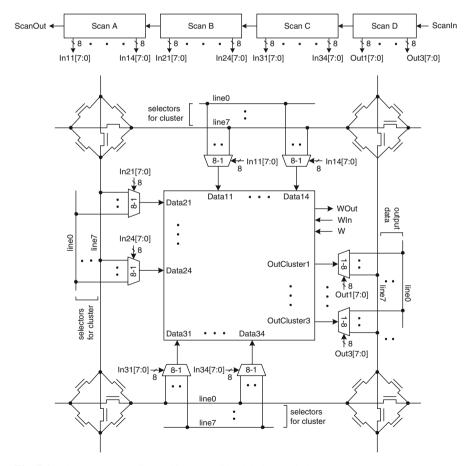

|   | 7.3  | FPGA    | Architecture                                  | 122 |

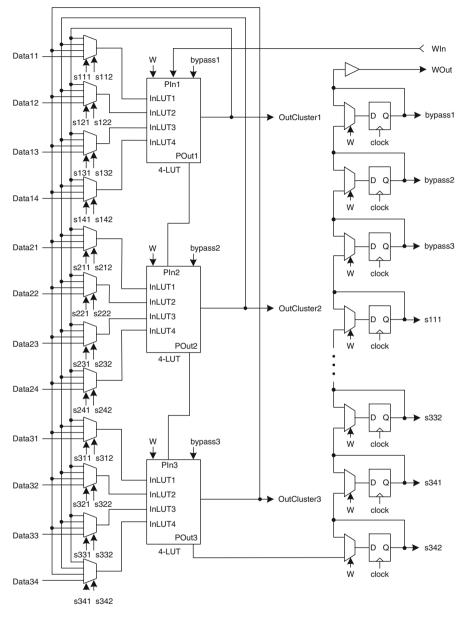

|   |      | 7.3.1   | Cluster Architecture                          | 122 |

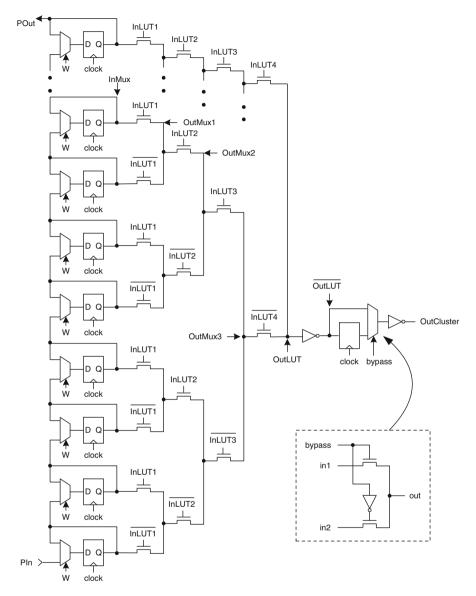

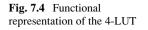

|   |      | 7.3.2   | 4-Input Look-Up-Table (4-LUT)                 | 123 |

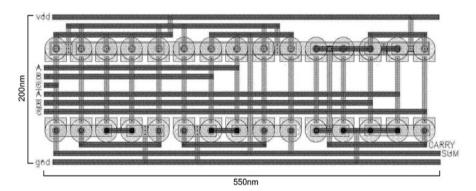

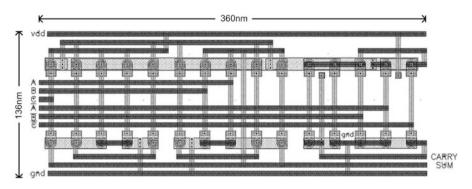

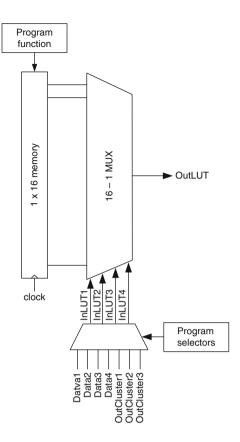

|   |      | 7.3.3   | An Example: A 3-bit Carry-Ripple Adder (CRA)  | 126 |

|   | 7.4  | FPGA    | Circuit Characteristics                       | 129 |

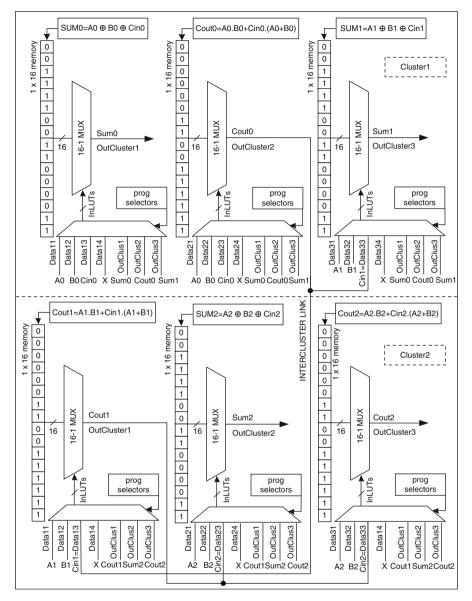

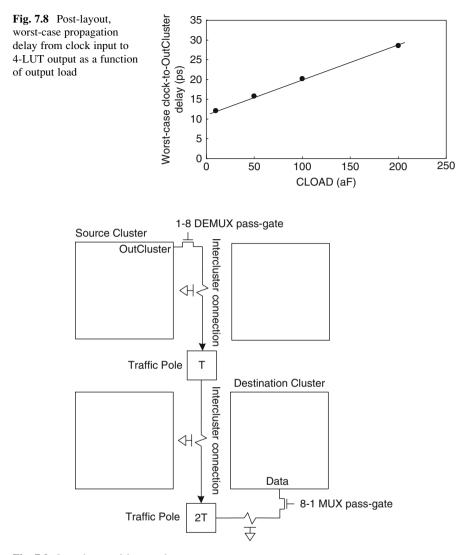

|   |      | 7.4.1   | 4-LUT Worst-Case Propagation Delays           | 129 |

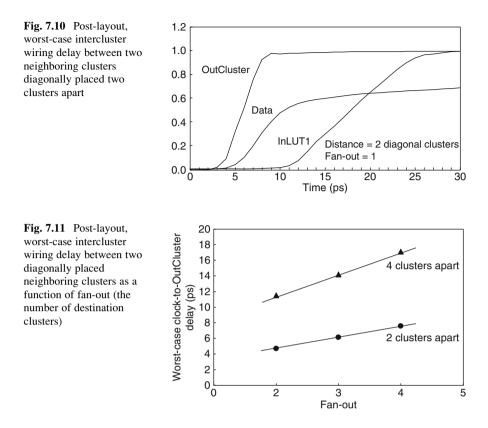

|   |      | 7.4.2   | Intercluster Propagation Delays               | 129 |

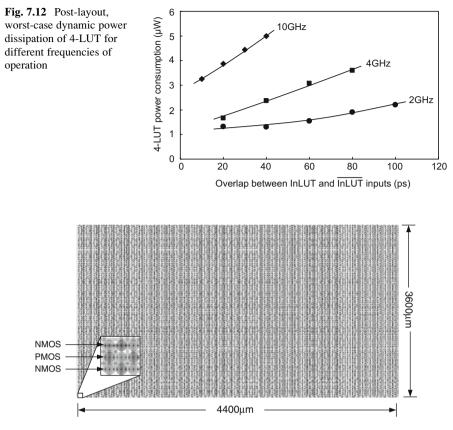

|   |      | 7.4.3   | 4-LUT Power Dissipation                       | 131 |

|   |      | 7.4.4   | Flip-Flop Characteristics                     | 132 |

|   |      | 7.4.5   | Cluster Layout                                | 132 |

|   | 7.5  | Summ    | 1ary                                          | 133 |

|   | Refe | erences | · · · · · · · · · · · · · · · · · · ·         | 133 |

| 8   | Inte | grate-and-Fire Spiking (IFS) Neuron                 | 135 |

|-----|------|-----------------------------------------------------|-----|

|     | 8.1  | Introduction                                        | 135 |

|     | 8.2  | Brief Description of Transistor Design and Modeling | 136 |

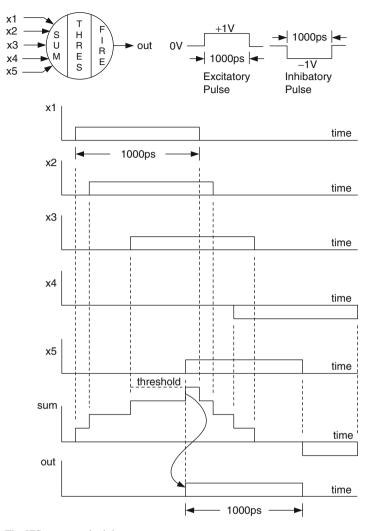

|     | 8.3  | IFS Neuron                                          | 136 |

|     |      | 8.3.1 IFS Neuron Firing Principle                   | 136 |

|     |      | 8.3.2 IFS Neuron Design                             | 136 |

|     |      | 8.3.3 Transient Response and Power Dissipation      | 141 |

|     |      | 8.3.4 IFS Neuron Cell Layout                        | 142 |

|     | 8.4  | Summary                                             | 143 |

|     | Refe | erences                                             | 144 |

| 9   | Dira | ect Sequence Spread Spectrum (DSSS)                 |     |

| ,   |      | eband Transmitter                                   | 145 |

|     | 9.1  | Introduction                                        | 145 |

|     | 9.2  | Brief Description of Transistor Design and Modeling | 145 |

|     | 9.3  | DSSS Baseband Transmitter                           | 146 |

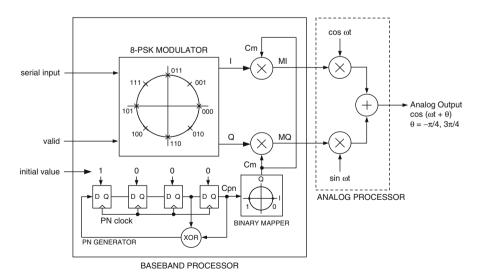

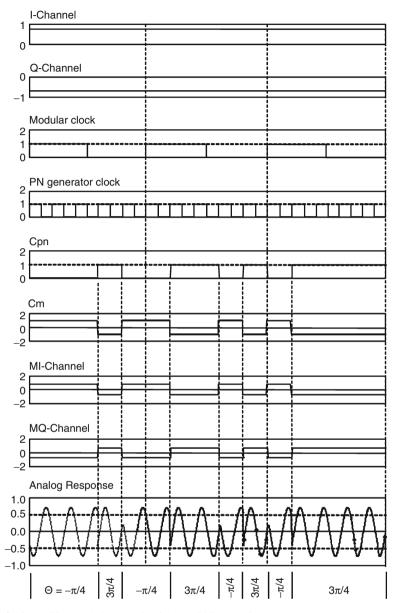

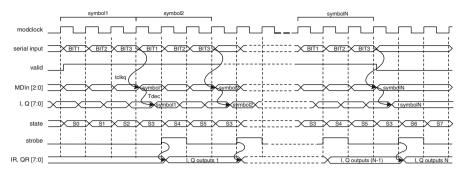

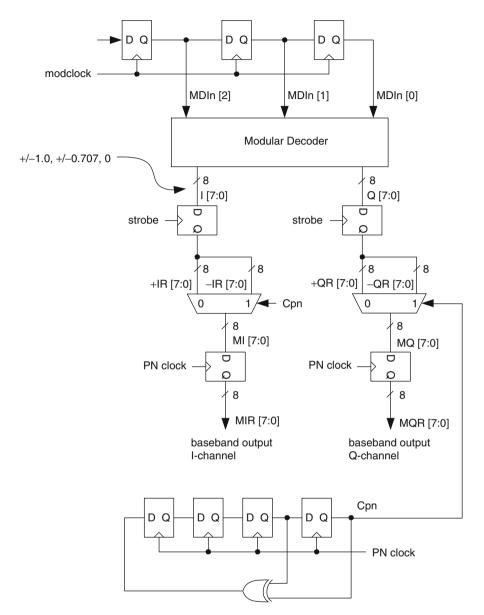

|     | 1.0  | 9.3.1 Overall Operation of the Transmitter          | 146 |

|     |      | 9.3.2 8-PSK Modulator                               | 148 |

|     |      | 9.3.3 PN Generator                                  | 148 |

|     |      | 9.3.4 Binary Mapper and Bit Multipliers             | 151 |

|     | 9.4  | Circuit Simulations                                 | 151 |

|     |      | 9.4.1 Clock Generation Circuits                     | 151 |

|     |      | 9.4.2 Maximum Critical Paths                        | 151 |

|     |      | 9.4.3 Minimum Critical Paths                        | 154 |

|     |      | 9.4.4 Parasitic RC Extraction                       | 154 |

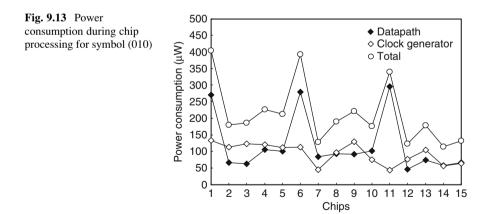

|     |      | 9.4.5 Power Consumption                             | 156 |

|     |      | 9.4.6 Layout                                        | 158 |

|     | 9.5  | Summary                                             | 159 |

|     | Refe | erences                                             | 159 |

|     |      |                                                     | -   |

| Ind | ex   |                                                     | 161 |

### **About the Authors**

Ahmet Bindal Ahmet Bindal received his M.S. and Ph.D. degrees in Electrical Engineering from the University of California, Los Angeles, CA. His doctoral research was on the material characterization and analysis of HEMT GaAs transistors. During his graduate studies, he was a research associate and technical consultant for Hughes Aircraft Co. In 1988, he joined the technical staff of IBM Research and Development Center in Fishkill, NY, where he worked as a device design and characterization engineer. He developed asymmetrical MOS transistors and ultra-thin Silicon-On-Insulator (SOI) technologies for IBM. In 1993, he transferred to IBM in Rochester, MN, as a senior circuit

design engineer to work on the floating-point unit for AS-400 main frame processor. He continued his circuit design career at Intel Corporation in Santa Clara, CA, where he designed 16-bit packed multipliers and adders for the MMX unit for Pentium II processors. In 1996, he joined Philips Semiconductors in Sunnyvale, CA, where he was involved in the designs of instruction and data caches, and various SRAM modules for the Trimedia processor. His involvement with VLSI architecture also started in Philips Semiconductors and led to the design of the Video-Out unit for the same processor. In 1998, he joined Cadence Design Systems as a VLSI architect and directed a team of engineers to design self-timed asynchronous processors. After approximately 20 years of industry work, he joined the Computer Engineering faculty at San Jose State University in 2002. His current research interests range from nano-scale electron devices to nano-scale architectures and robotics. Dr. Bindal has over 30 refereed scientific publications and 10 invention disclosures with IBM. He currently holds three U.S. patents with IBM and one with Intel Corporation.

**Sotoudeh Hamedi-Hagh** Dr. Hamedi-Hagh received his Ph.D. from the University of Toronto, Canada, in 2004. He joined the Electrical Engineering Department at San Jose State University (SJSU) in 2005. His areas of research and expertise include high frequency modeling of semiconductor device structures and design of Radio Frequency, Analog and Mixed-Signal integrated circuits for wireless and wireline communication systems. Dr. Hamedi-Hagh has developed the Radio Frequency Integrated Circuits laboratory and

curriculum at both graduate and undergraduate levels with over \$0.5 M research funding and through close collaborations with industries. He has received several California State University (CSU) professional development grants, CSU Research Funds, Research, Scholarship and Creative Activity (RSCA) grants, SJSU Planning Council Grants, College of Engineering professional development grants, and Junior Faculty Career Development Grants. He is a founding member of SJSU Smart Technology and Computing Center for Complex Systems (STCCS). In 2016, he was appointed as the Mixed-Signal endowed chair of the Electrical Engineering department. Dr. Hamedi-Hagh has over 30 refereed scientific journal and conference paper publications in prestigious national and international institutes and societies. He received the best paper award at the Micronet Symposium in Quebec, Canada, in 2001 and the IEEE International Symposium on Personal, Indoor and Mobile Radio Communications in Barcelona, Spain, in 2004. Dr. Hamedi-Hagh has advised several hundred projects on design of integrated circuits and systems. He holds seven US and world patents on wireless circuits, systems and cryptography. His latest patent introduces suspendance<sup>®</sup> and trajectance<sup>®</sup> laws as alternatives to Kirchhoff's laws for circuit analysis.

## Chapter 1 Dual Work Function Silicon Nanowire MOS Transistors

#### 1.1 Device Design

#### 1.1.1 Introduction to Design Process

In the past, there were several attempts to develop alternative technologies, including molecular technologies [1, 2], that were aimed to replace the current VLSI technology. However, conventional silicon-based technologies prevailed as solid choices over the newcomers for fabricating low power nano devices and circuits without sacrificing high performance. As today's chips require larger die areas to accommodate complex System-On-Chip (SOC) designs, reducing overall power dissipation has been accepted as the major design objective, replacing the need for faster circuit performance. Recent modeling studies in undoped, double-gated SOI MOS transistors revealed that these transistors could produce an order of magnitude less leakage current compared to conventional bulk silicon MOS transistors for achieving ultralow power consumption [3]. However, fabricating ultra-thin transistors sandwiched between two gates with adjustable work function is highly questionable in a production environment since both gates have to be made out of metal in order to produce proper threshold voltage and therefore to maintain a healthy circuit operation. Other studies on this device showed the effect of body thickness to alter the threshold voltage [4] and the variations of the back oxide thickness to decrease overall power dissipation [5]. Two-dimensional analytical modeling [6] and quantum mechanical modeling [7, 8] were also performed to better predict this device's performance and leakage current under different biasing conditions.

Another good candidate is a nano-scale, triple-gated SOI transistors or FINFETs. Theoretical studies conducted on these transistors explored the possibility of increasing transistor performance without increasing power consumption [9]. Recent experimental studies showed close-to-ideal subthreshold slope and Drain-Induced-Barrier-Lowering (DIBL) [10], both of which are important factors to reduce OFF current and power consumption [11]. Besides these promising

DOI 10.1007/978-3-319-27177-4\_1

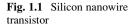

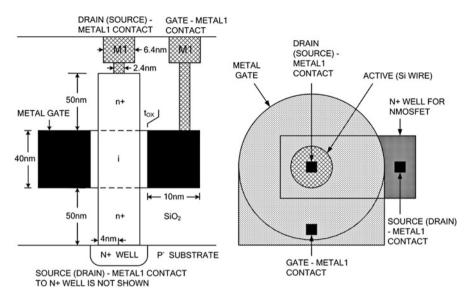

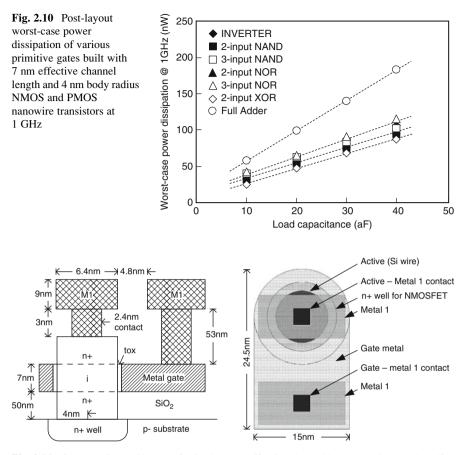

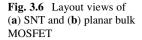

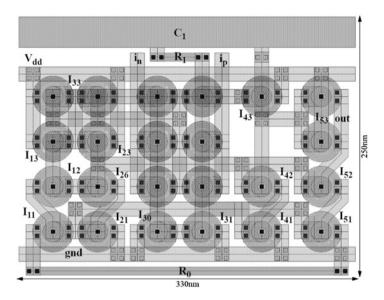

technologies, Silicon Nanowire MOS Transistors (SNT) also offers significant reduction in static and dynamic power consumption and compact layout area without sacrificing circuit performance. SNTs are vertically built on Silicon-On-Insulator (SOI) substrate and cylindrical in shape with a gate surrounding the entire perimeter of the transistor body as shown in Fig. 1.1. The source contact is placed at the bottom of the cylindrical body standing on the SOI substrate while the drain is placed at the top of the device interfacing the first metal layer. The primary objective of this chapter is to design SNTs with dual work function gates and use them in ultra-compact digital CMOS circuits that dissipate minimal static and dynamic power but perform equally or better than the state-of-the-art CMOS circuits.

The design criteria for each NMOS and PMOS SNT are outlined below:

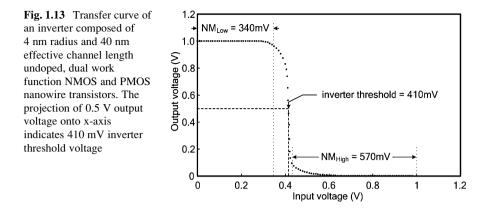

- NMOS and PMOS transistors need to have 300 mV threshold voltage for 1 V CMOS circuit operation for good noise immunity and low OFF current; therefore, different gate metals (dual work function) need to be used for each transistor.

- 2. The static OFF current has to be under 1 pA in each transistor.

However, to achieve these objectives requires changing the body geometry (channel length and radius) of both transistors and determining the device characteristics at each change.

This chapter also discusses the strengths and weaknesses of this technology. Low static and dynamic power dissipation, suppression of Short Channel Effects (SCE), and surface mobility enhancement may be considered as the advantages of SNTs. Alternative placement of NMOS and PMOS transistors as a crossbar configuration may also be counted as an advantage to simplify the layout; however, this method also increases the layout area. Other issues, such as source and drain contact resistances due to small body radius, source contact extension producing high source resistance, and fixed body dimensions resulting in non-adjustable ON currents (therefore limiting transient performance), are definite disadvantages of this technology.

One can trace the foundations of silicon nanowire technology in much earlier studies that investigate material properties and circuits. Silicon nanowires grown by Vapor–liquid–Solid (VLS) mechanism [12] and Chemical Vapor Deposition

#### 1.1 Device Design

(CVD) [13, 14] can be used to fabricate vertical SNTs. In fact, it was demonstrated that silicon nanowires could be used in Static Random Access Memory (SRAM) [15] and high-speed logic circuits [16]. Theoretical studies investigated the bulk and transport properties of silicon nanowires [17] and device properties as a function of wire diameter [18]. Circuit performance and power dissipation of SNTs were briefly studied in 3-D DNA architectures [19, 20].

#### 1.1.2 The Criteria for Low Static Power Dissipation

There are three major components that result in low static power dissipation:

- 1. Junction leakage

- 2. Subthreshold leakage

- 3. Gate-Induced-Drain-Leakage (GIDL) current

Junction leakage current primarily depends on DIBL factor as shown in Eq. 1.1.

$$DIBL = \left| \frac{V_{TSAT} - V_{TLIN}}{(V_{DS} = V_{DD}) - (V_{DS} = 50mV)} \right|$$

(1.1)

where  $V_{TLIN}$  and  $V_{TSAT}$  are the threshold voltages at  $V_{DS} = 50 \text{ mV}$  and  $V_{DS} = V_{DD}$ , respectively.

Subthreshold leakage current is a function of subthreshold slope, S, and saturation threshold voltage,  $V_{TSAT}$ , as expressed in Eq. 1.2.

$$\mathbf{I}_{\text{SUB}} = \text{Io.10}^{\frac{-V_{\text{TSAT}}}{8}} \tag{1.2}$$

Here, Io is the drain current at  $V_{GS} = V_{TLIN}$  and S is given in Eq. 1.3 [21].

$$S = \frac{kT}{q} \log \left( 1 + \frac{C_D}{C_{OX}} \right)$$

(1.3)

In this equation,  $C_D$  and  $C_{OX}$  are the channel depletion region and gate oxide capacitances, respectively.

The third component, GIDL current, is a strong function of transverse electric field, ES, at the semiconductor surface perpendicular to the device axis as given by Eq. 1.4 [22].

$$IGIDL = A.E_{s.exp}\left(-\frac{B}{E_{s}}\right)$$

(1.4)

where

$$E_{S} = \frac{V_{DG} - V_{FB} - 1.2}{3tox}$$

(1.5)

A is pre-exponential constant, B is a physically based exponential parameter suggested by [23],  $V_{DG}$  is the drain-to-gate potential,  $V_{FB}$  is the flat band voltage, and tox is the oxide thickness.

Therefore, the OFF current can be reduced by decreasing DIBL, tox, body doping concentration, and  $E_S$ . In this work, tox is set to minimum value of 1.5 nm to maintain the gate leakage current to a negligible level with respect to  $I_{OFF}$  as suggested by [3]; the body doping concentration is reduced to intrinsic level to minimize  $C_D$ , and  $E_S$  is also kept small due to non-overlapping gate-drain region and sub-10 nm wire radius [22].

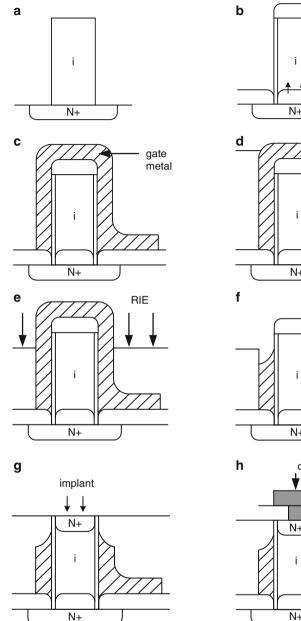

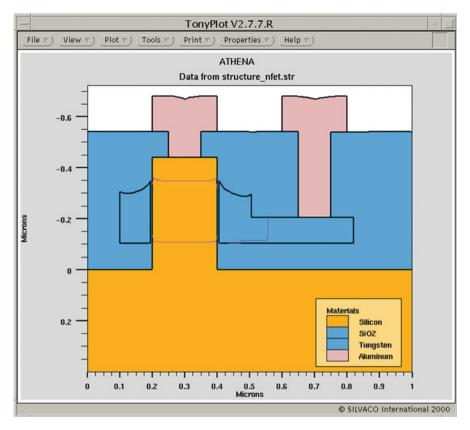

#### 1.1.3 Device Structure

Both NMOS and PMOS transistors are designed as enhancement type with uniform, undoped silicon bodies constructed perpendicular to the substrate. Both have the same body radius and effective channel length. Source/drain (S/D) contacts are assumed to have ohmic contacts. Both NMOS and PMOS transistors have metal gates and 1.5 nm thick gate oxide.

Device simulations are performed using Silvaco's 3-D ATLAS device simulation environment with a 1 V power supply voltage. Half of the device is constructed in a 2-D platform and then rotated around the y-axis to create a 3-D cylindrical structure for simulations. The device radius is changed from 1 nm to 25 nm while its effective channel length is varied between 5 nm and 250 nm.

#### 1.1.4 Physical Models Used in Device Simulations

Even though sub-100 nm device geometry requires inclusion of Schrödinger's equation to calculate effective electron/hole masses and density of states due to the perturbations in the silicon conduction and valance bands, ATLAS simulator is limited to the full usage of such quantum mechanical effects. Instead, this study follows a semiclassical approach in which the semiconductor surface potential and density of states are corrected using density gradient method [24].

Mobility models are composed of two parts to estimate the effects of low and high electric fields. Lombardi's vertical and horizontal electric field dependent mobility model is used for low electric field effects [25]. Velocity saturation and high electric field effects are estimated by Caughey's drift velocity model [26]. Mobility degradation due to lattice temperature is included using Arora's model [27].

Concentration-dependent Shockley–Read–Hall recombination and surface recombination models are included to estimate the recombination rates in the bulk and at the silicon/oxide interface, respectively. Serberherr's impact ionization model constitutes the only generation model in the simulations [28]. Gate oxide tunneling mechanisms and hot carrier injection are ignored because these mechanisms largely depend on oxide growth and composition, and change from one processing condition to another.

#### 1.1.5 Determining Metal Gate Work Function Values for NMOS and PMOS Transistors

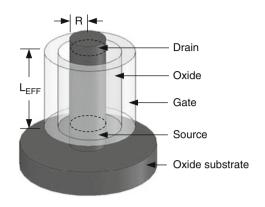

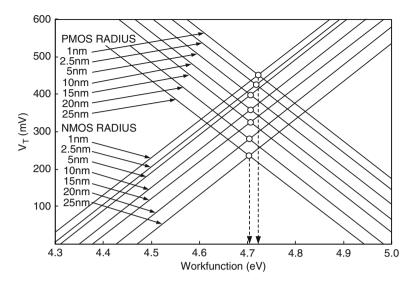

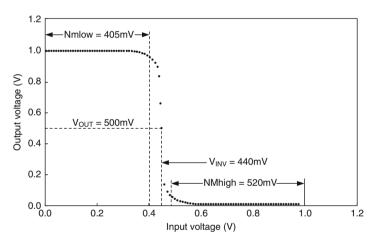

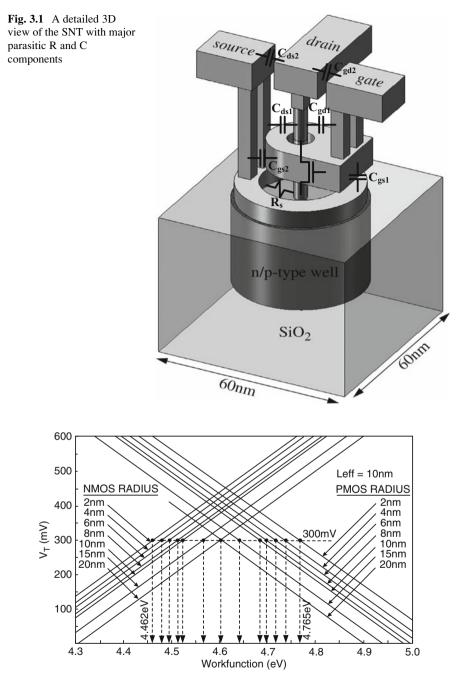

The first task in this design process is to determine an individual metal work function for each NMOS and PMOS transistor at a minimum channel length of 5 nm in order to produce a threshold voltage of approximately 300 mV. This value constitutes 30 % of the 1 V power supply voltage and provides sufficient noise immunity for any CMOS gate. Threshold voltage of each NMOS and PMOS transistor is measured as a function of work function for the body radius from 1 nm to 25 nm as shown in Fig. 1.2. Longer channel length devices yield marginally higher threshold voltage and improve noise margin slightly. The intersection of threshold voltage with 300 mV level in Fig. 1.2 is projected to the x-axis to yield an individual work function value for each NMOS and PMOS transistor at a different body radius. Threshold voltages are measured using two different methods: the first method extrapolates the maximum slope of  $I_D-V_{GS}$  curve towards  $V_{GS}$ -axis and

**Fig. 1.2** Threshold voltages of NMOS and PMOS nanowire transistors as a function of metal work function at a minimum effective channel length of 5 nm. Radius of both NMOS and PMOS transistors is changed between 1 and 25 nm

defines the intercept as the threshold voltage; the second method determines the threshold voltage from the gate voltage at  $I_{DS} = \zeta(W/L)$  for  $V_{DS} = 50$  mV, where  $\zeta$  is  $10^{-7}$ A for NMOS and  $10^{-8}$ A for PMOS transistors. This method is suggested by Liu et al. [29] and consistently produced 11 % and 3 % lower threshold voltages for NMOS and PMOS transistors, respectively.

#### 1.1.6 The OFF Current Requirement

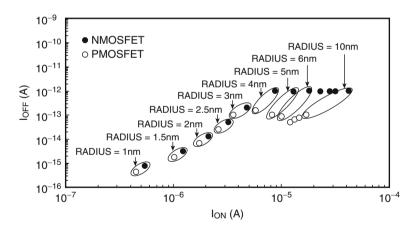

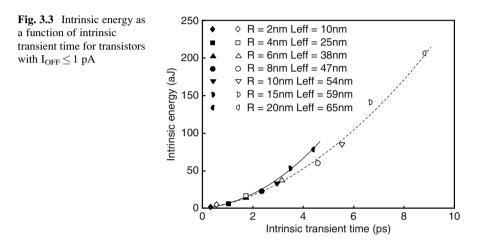

The leakage current is an important factor towards lowering overall standby power consumption; both NMOS and PMOS transistors are designed to have static leakage currents smaller than 1 pA, which is significantly smaller than SOI transistors in earlier modeling studies [3, 5, 9] and several orders of magnitude smaller than the technology trend predicted by Sery et al. [30]. Therefore, while most transistors with 1 nm to 5 nm radius produced  $I_{OFF}$  less than 1 pA and were considered as potential candidates for an optimum transistor design, transistors with larger radii were eliminated because their leakage currents exceeded 1 pA as shown in Fig. 1.3. In this figure, the transistor geometries closest to the dashed line are considered potential candidates since they produce higher ON currents for a given value of  $I_{OFF}$ .

#### 1.1.7 Intrinsic Transient Time

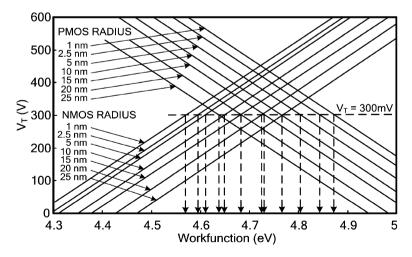

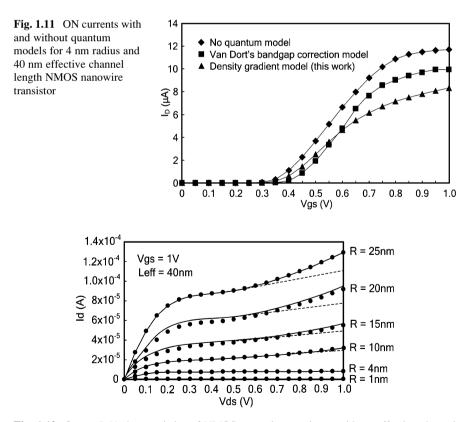

Following the device selection process for low power dissipation in Fig. 1.3, the intrinsic transient time,  $\tau$ , of each "selected" transistor is measured and then plotted as a function of  $I_{ON}$  in Fig. 1.4. Intrinsic transient time determines the time interval for a transistor to charge (or discharge) the gate capacitance of an identical transistor when it is fully on ( $V_{DS} = V_{GS} = 1$  V) and it is a quick way of understanding the transient characteristics of an individual transistor without building any circuitry. In Fig. 1.4, ON currents of the selected NMOS and PMOS transistors start diverging from each other after 4 nm radius and 40 nm effective channel length; larger wire radius provides higher  $I_{ON}$  values for NMOS transistors, but it reaches a saturation plateau for PMOS transistors. Therefore, the 4 nm radius and 40 nm effective channel length combination is considered an optimal choice to produce approximately equal drive currents and intrinsic transient times for both NMOS and PMOS transistors.

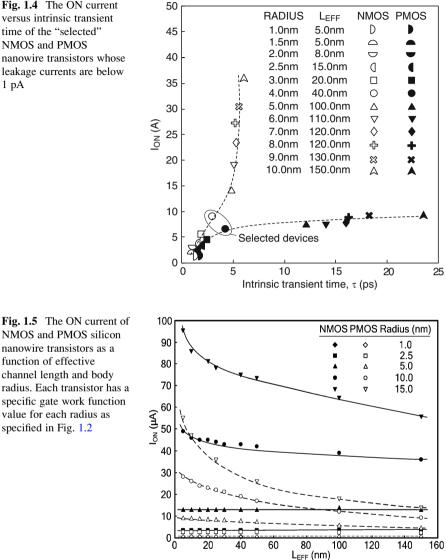

Figure 1.5 shows the ON currents for NMOS and PMOS transistors as a function of  $L_{EFF}$  for different wire radii and helps to explain the ON current behavior of each device in Fig. 1.4. For wire radius greater than 5 nm, ON currents of both NMOS and PMOS transistors increase with decreasing  $L_{EFF}$  as shown in Eq. 1.6 [31, 32].

**Fig. 1.3** The ON versus OFF current of NMOS and PMOS nanowire transistors. The radius of both transistors is changed between 1 and 25 nm while their effective lengths are varied between 5 and 250 nm. Each transistor has a specific gate work function value for each radius as specified in Fig. 1.2. Note that transistors with shorter effective channel lengths produce higher OFF currents

$$I_{ON} = \frac{\mu_{EFF}.\varepsilon ox.W}{2L_{EFF}.t'ox} \left\{ (V_{GS} - V_T)^2 - \frac{16k^2T^2}{q^2} \cdot \frac{t'ox.R.\varepsilon s}{\varepsilon ox} \cdot exp \left[ \frac{q}{kT} (V_{GS} - V_{TO} - V_{DS}) \right] \right\}$$

(1.6)

where

$$t'ox = R.ln\left(1 + \frac{tox}{R}\right)$$

(1.7)

$$V_{TO} = V_{FB} + \frac{kT}{q} ln \left( \frac{kT \epsilon s N}{q^2 n i^2} \right)$$

(1.8)

Here, N and R are the body doping concentration and radius of the SNT, respectively.

However, as the wire radius is further reduced from 5 nm to 1 nm, ON currents become independent of L<sub>EFF</sub>. This behavior is not supported by the expression in Eq. 1.6. If inversion charge concentration, Qi, and drift velocity of electrons (holes) are examined throughout the body of small radius devices, one observes that both charge distribution and velocity are uniform. For example, if  $V_{GS} = V_{DS} = 1$  V is applied to an NMOS transistor whose radius is smaller than 5 nm, the value of Qi approaches  $10^{19}$  cm<sup>-3</sup> and electron drift velocity becomes equal to  $10^7$  cm/s for device lengths between 5 and 150 nm. These observations suggest that electrons

Fig. 1.4 The ON current versus intrinsic transient time of the "selected" NMOS and PMOS nanowire transistors whose leakage currents are below 1 pA

travel with saturation drift velocity across the transistor body and becomes independent of  $L_{EFF}$  as given by Eq. 1.9 [21].

$$I_{ON} = \pi . R^2 vsatQi \tag{1.9}$$

The validity of this statement can be further verified by computing the ON current ratios of small radius devices in Fig. 1.5 and comparing them against the square of body radius ratios. For example,  $I_{ON}$  of 1 nm, 2.5 nm, and 5 nm radius NMOS transistors are 0.54  $\mu$ A, 3.3  $\mu$ A, and 13  $\mu$ A, respectively. When we compute the ratio of the ON currents of the R = 5 nm device to the R = 2.5 nm device, we obtain 3.94. If the same ratio is computed using Eq. 1.9, the result becomes equal to 4, assuming Qi in both devices is equal. Similarly, the ratio of ON currents of the R = 2.5 nm device to the R = 1 nm device produces 6.11 from Fig. 1.5 while the same ratio produces 6.25 according to Eq. 1.9.

For large wire radius shown in Fig. 1.5,  $I_{ON}$  follows Eq. 1.6 and the ratio of ON currents becomes equal to the ratio of effective electron and hole mobilities in NMOS and PMOS transistors if minor deviations in threshold voltages are ignored. For example, default effective electron and hole mobilities in Silvaco's ATLAS design simulation environment produce an ON current ratio of 3.9, whereas the ON current ratio extracted from Fig. 1.5 is equal to 3.38 for 10 nm radius NMOS and PMOS transistors. However, as the wire radius is reduced and the transistor bulk effect disappears, the ON current follows Eq. 1.9 and the ratio of ON currents becomes approximately proportional to the square of the NMOS and PMOS transistors produce 0.54  $\mu$ A and 0.48  $\mu$ A ON currents, respectively. The ratio of ON currents approaches unity rather than approaching to the ratio of effective electron to hole mobilities as in large radius devices.

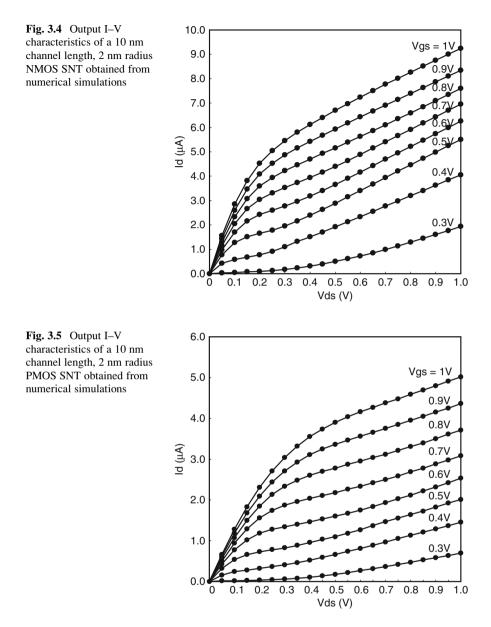

#### 1.1.8 DC Device Characteristics

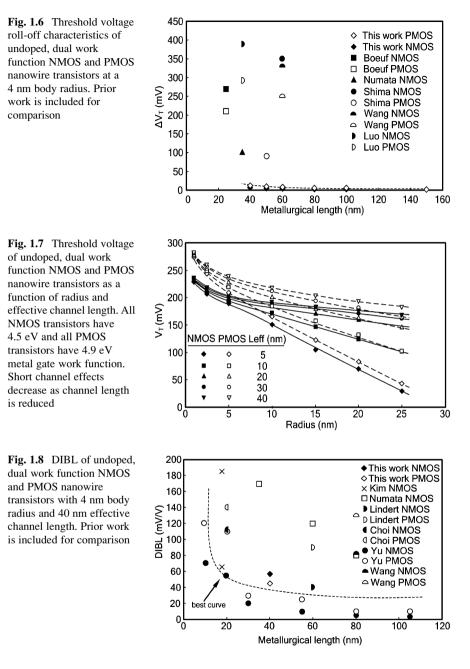

Figure 1.6 shows the threshold voltage roll-off of the 4 nm radius transistors with effective channel lengths ranging between 40 nm and 150 nm. The figure also includes earlier bulk and SOI transistor data for comparison [33–37]. The amount of  $\Delta V_T$  is 6 mV for the NMOS and 11 mV for the PMOS transistors. These results are more than an order of magnitude smaller than the values of bulk silicon transistors which require heavily doped substrates to prevent SCE but consequently suffer from early impact ionization and large leakage currents.

The threshold voltage behavior of SNTs in Fig. 1.6 is not surprising because the same trend can also be seen in Fig. 1.7. This figure illustrates that the SCE gradually disappears as wire radius decreases towards 1 nm; larger radius devices are affected by the SCE and exhibit in excess of 100 mV threshold voltage change. This shows that bulk transistors or transistors fabricated on an SOI substrate thicker than 5 nm are still susceptible to threshold voltage variations as a function of device geometry.

Silicon wire transistors, having a radial gate configuration, controls and suppresses SCE simply by reducing wire radius.

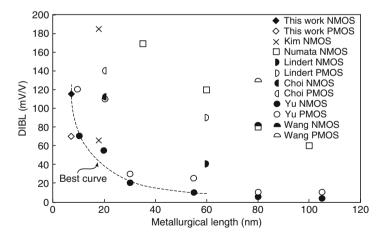

The amount of DIBL is 57 mV/V for the NMOS and 53 mV/V for the PMOS transistors with 4 nm radius and 40 nm effective channel length. These values are shown in Fig. 1.8 and compared with previously published data [3, 10, 34, 36, 38, 39].

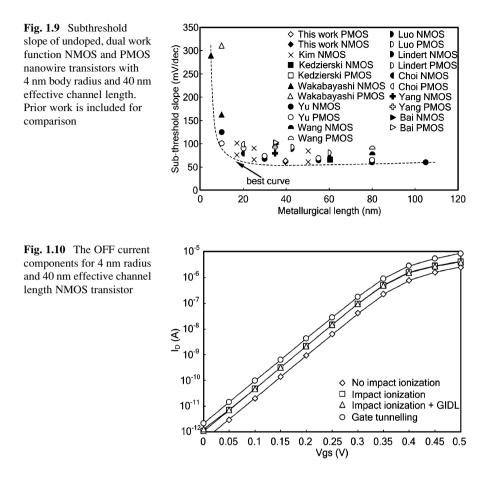

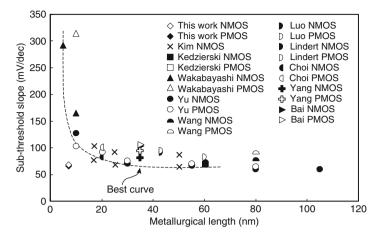

Subthreshold slope is 62 mV/dec for NMOS and 62.5 mV/dec for PMOS transistors at a drain voltage of 1 V. These results are plotted in Fig. 1.9 and show close-to-ideal characteristics in comparison with Kim's modeling results on double-gated SOI transistors [3] and previously published experimental data [10, 36–43].

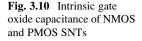

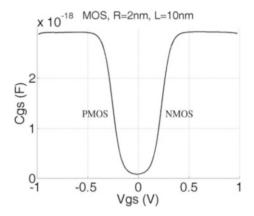

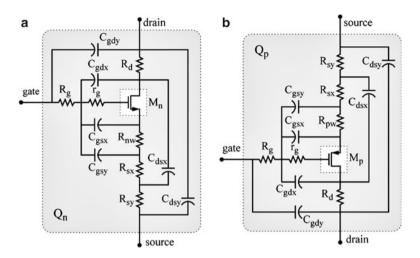

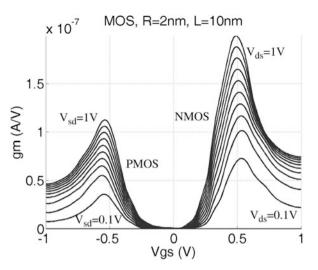

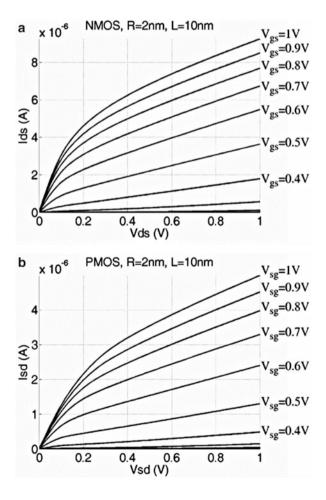

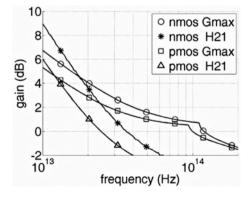

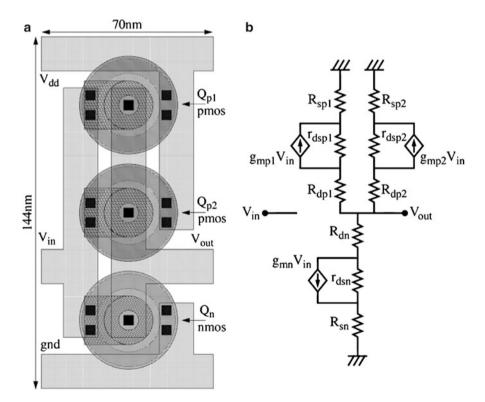

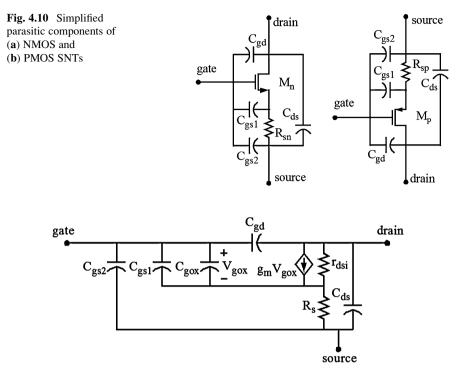

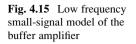

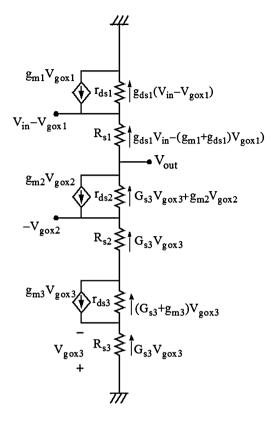

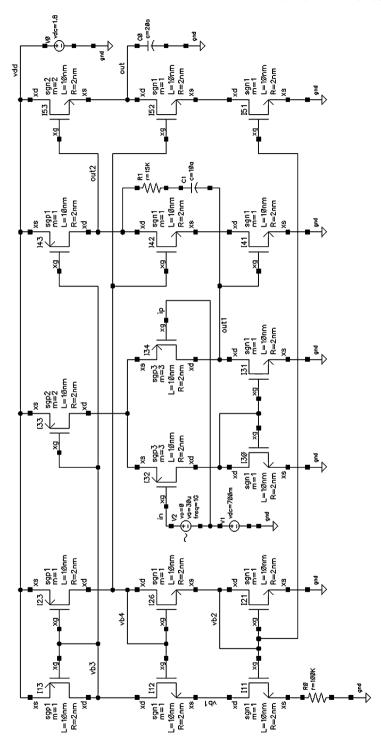

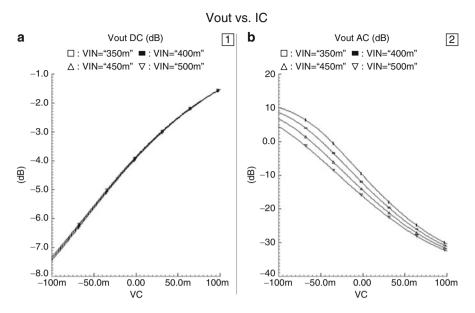

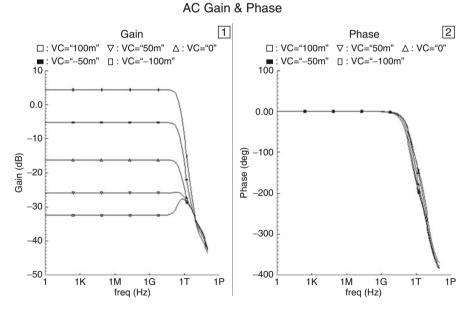

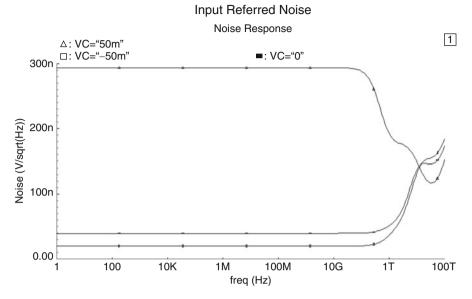

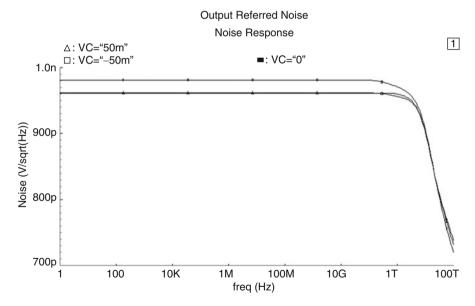

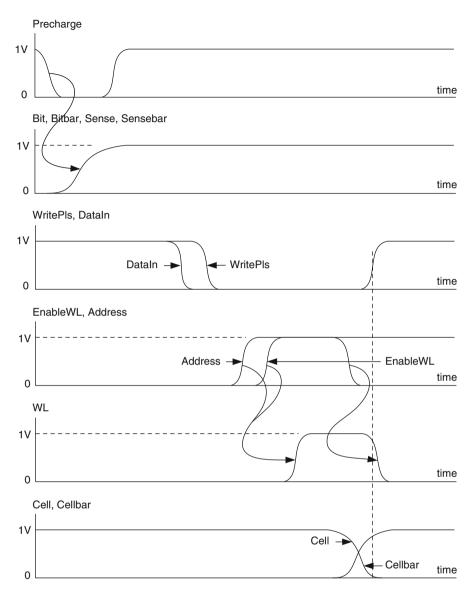

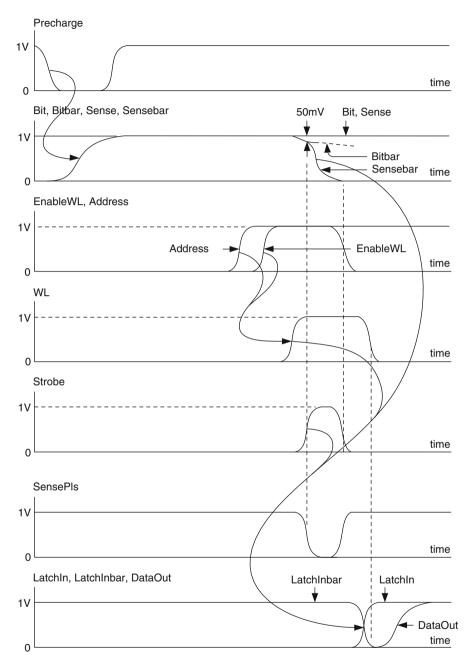

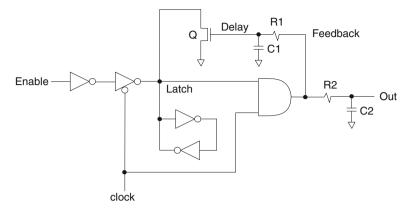

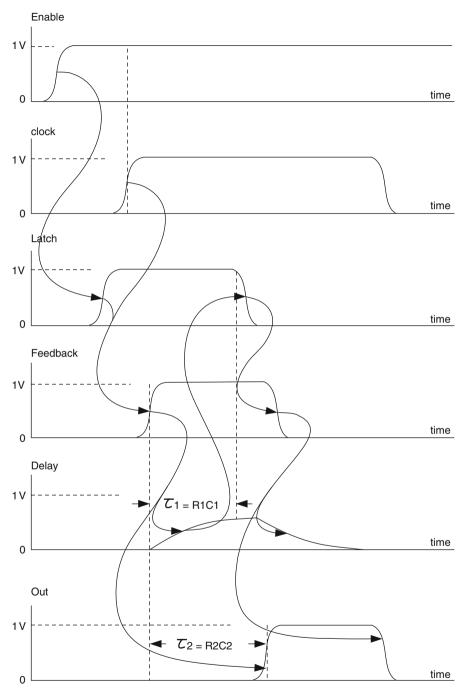

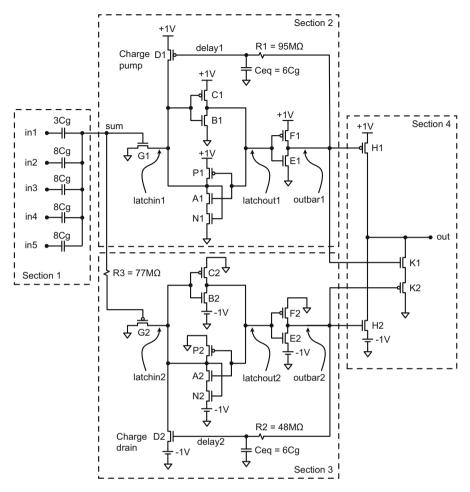

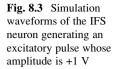

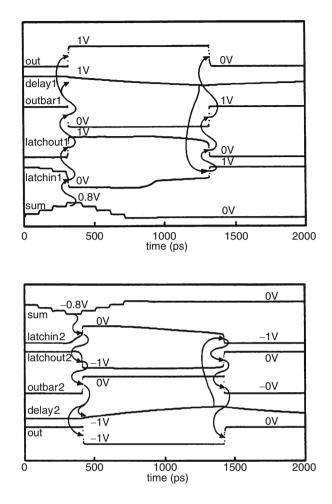

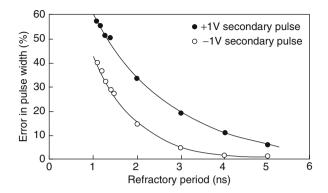

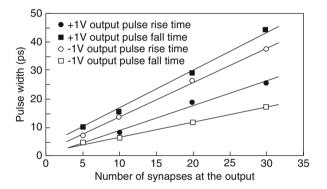

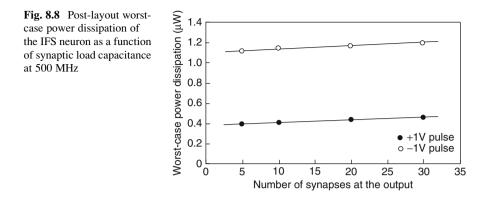

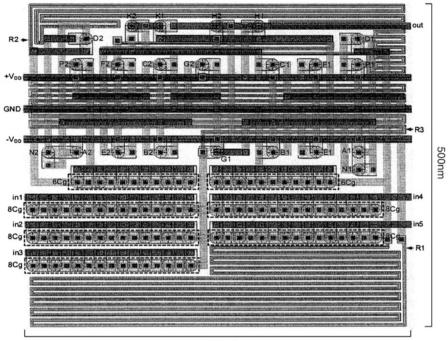

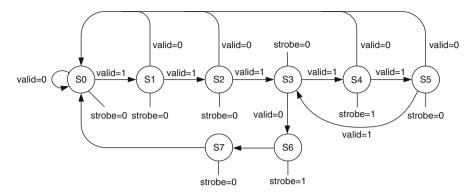

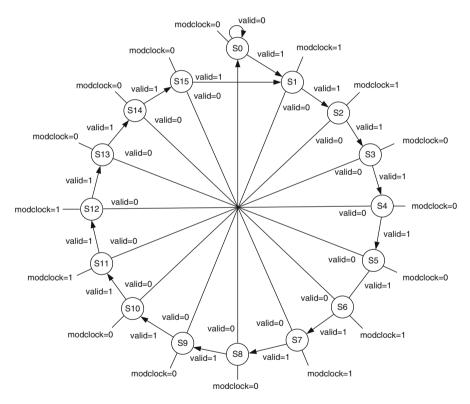

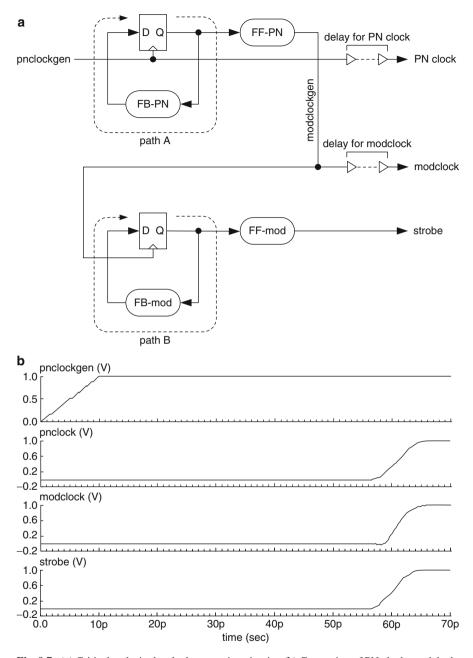

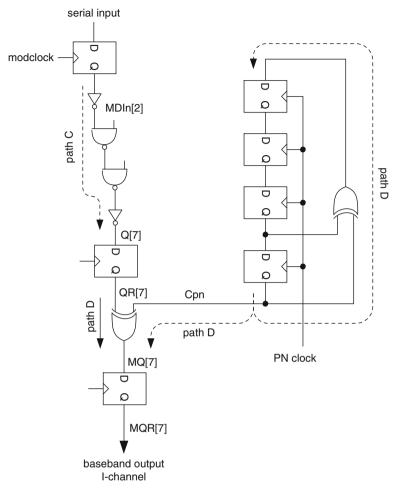

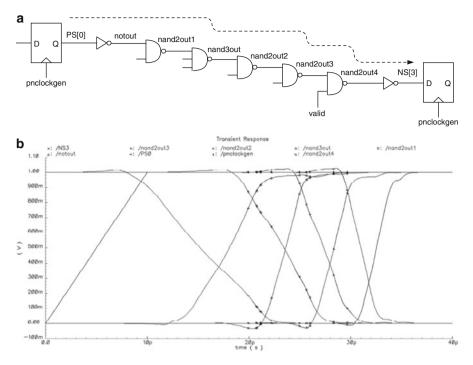

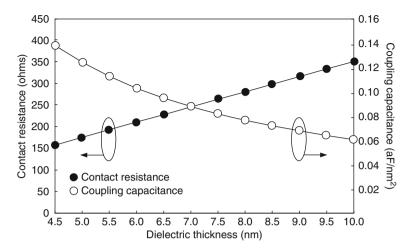

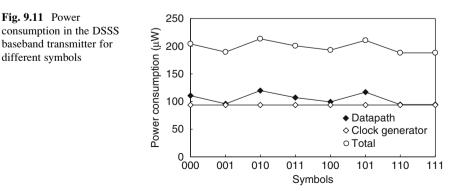

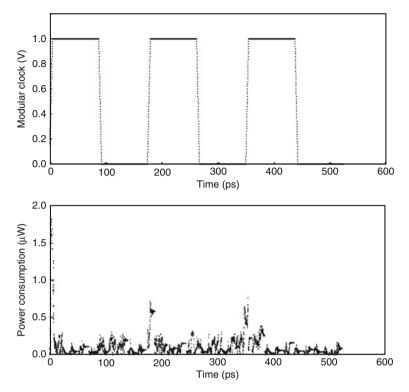

Figure 1.10 shows the three components of the OFF current for NMOS transistor. Subthreshold leakage is the first component when there is no impact ionization in the device body. Junction leakage is the result of impact ionization at high lateral electric fields and it doubles the total OFF current. Band-to-band leakage or GIDL component is small compared to junction leakage because of three factors. The first factor is the absence of a gate-drain overlap region in the proposed device structure: only fringing component of the transverse electric field emanating from the edge of the gate may induce GIDL. The second factor is the decrease in transverse electric field with respect to a bulk device with a single gate: surface potential in a bulk or partially depleted SOI device is appreciable to promote GIDL current generation [22]. The third factor is the magnitude of the power supply voltage: the drain-togate potential being less than the silicon band gap is not an effective way to create enough band-bending at the semiconductor surface to allow the valance band electrons to tunnel into the conduction band. Gate oxide tunneling using Concannon's model [44], on the other hand, may increase the OFF current beyond its designed limit as it almost doubles the total OFF current as shown in Fig. 1.10. However, the magnitude of this current primarily depends on processing conditions including gate oxide composition, quality and defect levels during growth, and it is not included in this study.