Mourad Fakhfakh Esteban Tlelo-Cuautle Patrick Siarry *Editors*

# Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design

Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design Mourad Fakhfakh · Esteban Tlelo-Cuautle Patrick Siarry Editors

## Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design

*Editors* Mourad Fakhfakh Department of Electronics ENET'Com, University of Sfax Sfax Tunisia

Esteban Tlelo-Cuautle Department of Electronics INAOE Tonantzintla, Puebla Mexico Patrick Siarry Laboratory LiSSi (EA 3956) Université Paris-Est Créteil Vitry-sur-Seine France

ISBN 978-3-319-19871-2 DOI 10.1007/978-3-319-19872-9 ISBN 978-3-319-19872-9 (eBook)

Library of Congress Control Number: 2015942631

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

## Preface

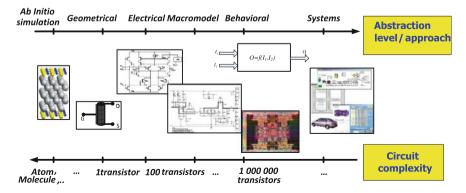

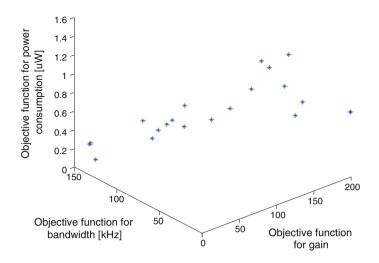

Computational intelligence has been an astounding success in the engineering domain, particularly in electronic design. Over the last two decades, improved techniques have raised the productivity of designers to a remarkable degree. Indeed, in the areas of digital, analog, radio-frequency, and mixed-signal engineering, there is a focused effort on trying to automate all levels of the design flow of electronic circuits, a field where it was long assumed that progress demanded a skilled designer's expertise. Thus, new computational-based modeling, synthesis and design methodologies, and applications of optimization algorithms have been proposed for assisting the designer's task.

This book offers the reader a collection of recent advances in computational intelligence—algorithms, design methodologies, and synthesis techniques—applied to the design of integrated circuits and systems. It highlights new biasing and sizing approaches and optimization techniques and their application to the design of high-performance digital, VLSI, radio-frequency, and mixed-signal circuits and systems.

As editors, we invited experts from related design disciplines to contribute overviews of their particular fields, and we grouped these into the following:

- Volume 1, "Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design," contains 17 chapters, divided into two parts: "Analog and Mixed-Signal Applications" (Chaps. 1–8) and "Radio-Frequency Design" (Chaps. 9–17).

- Volume 2, "Computational Intelligence in Digital and Network Designs and Applications," contains 12 chapters, divided into three parts: "Digital Circuit Design" (Chaps. 1–6), "Network Optimization" (Chaps. 7–8), and "Applications" (Chaps. 9–12).

Here, we present detailed descriptions of the chapters in both volumes.

## Volume 1—Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design

#### Part I—Analog and Mixed-Signal Applications

Chapter 1, "I-Flows: A Novel Approach to Computational Intelligence for Analog Circuit Design Automation Through Symbolic Data Mining and Knowledge-Intensive Reasoning," was written by Fanshu Jiao, Sergio Montano, Cristian Ferent, and Alex Doboli. It presents an overview of the authors' ongoing work toward devising a new approach to analog circuit synthesis. The approach computationally implements some of the facets of knowledge-intensive reasoning that humans perform when tackling new design problems. This is achieved through a synthesis flow that mimics reasoning using a domain-specific knowledge structure with two components: an associative part and a causal reasoning part. The associative part groups known circuit schematics into abstractions based on the similarities and differences of their structural features. The causal reasoning component includes the starting ideas as well as the design sequences that create the existing circuits.

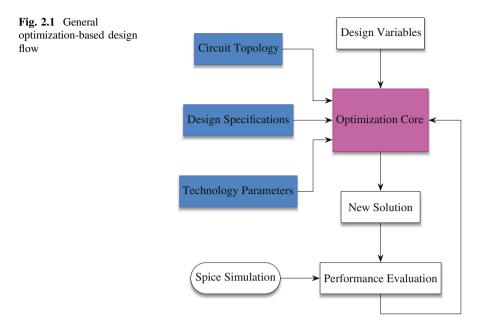

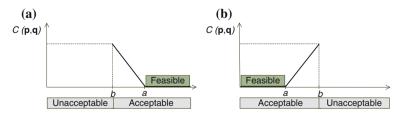

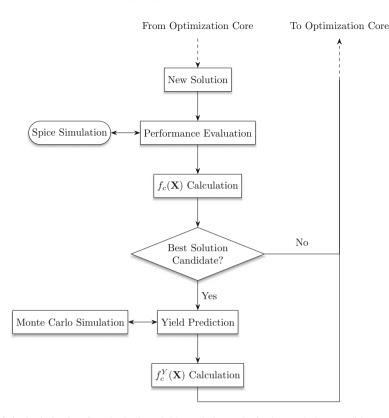

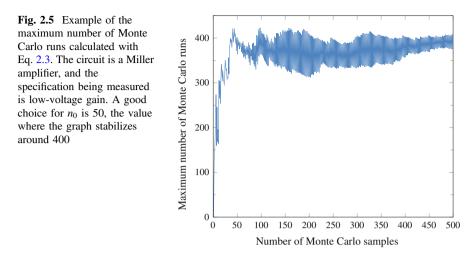

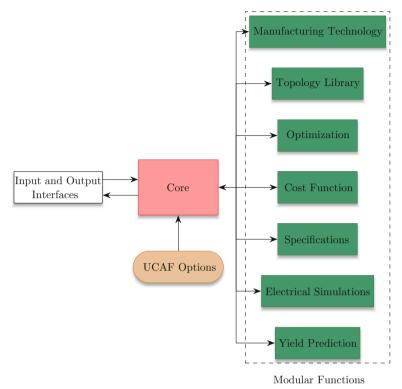

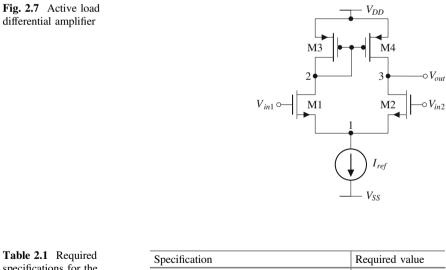

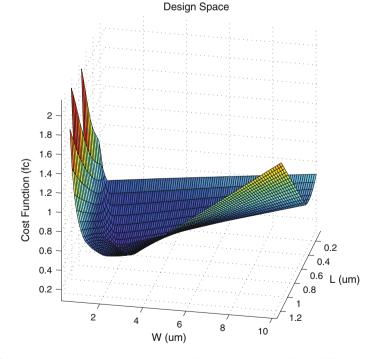

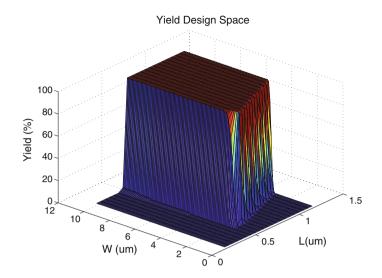

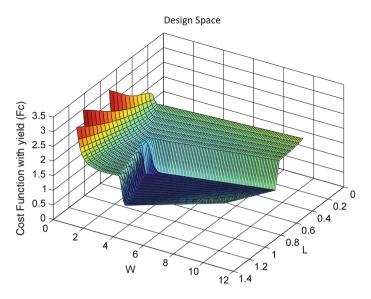

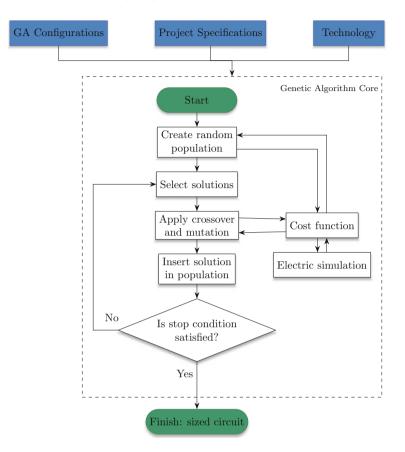

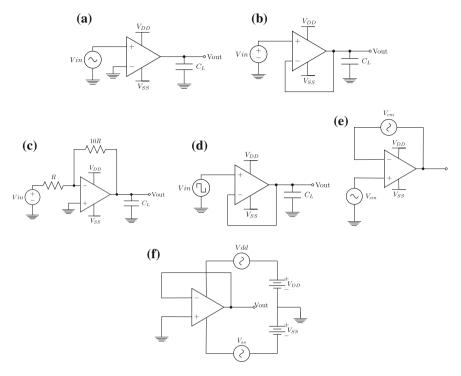

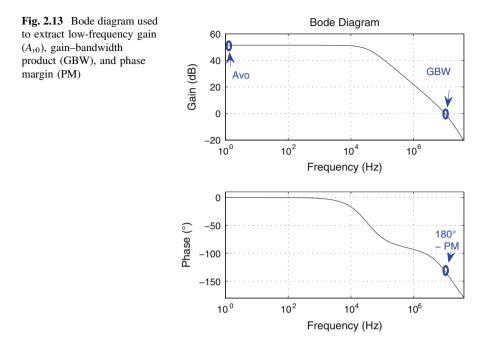

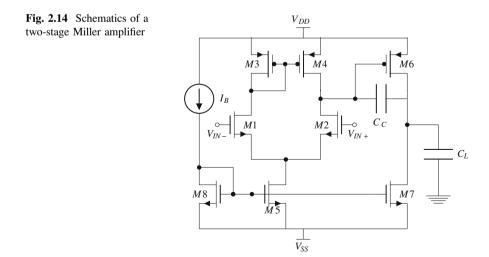

Chapter 2, "Automatic Synthesis of Analog Integrated Circuits Including Efficient Yield Optimization," was written by Lucas C. Severo, Fabio N. Kepler, and Alessandro G. Girardi. Here, the authors show the main aspects and implications of automatic sizing, including yield. Different strategies for accelerating performance estimation and design space search are addressed. The analog sizing problem is converted into a nonlinear optimization problem, and the design space is explored using metaheuristics based on genetic algorithms. Circuit performance is estimated by electrical simulations, and the generated optimal solution includes yield prediction as a design constraint. The method was applied for the automatic design of a 12-free-variables two-stage amplifier. The resulting sized circuit presented 100 % yield within a 99 % confidence interval, while achieving all the performance specifications in a reasonable processing time. The authors implemented an efficient yield-oriented sizing tool which generates robust solutions, thus increasing the number of first-time-right analog integrated circuit designs.

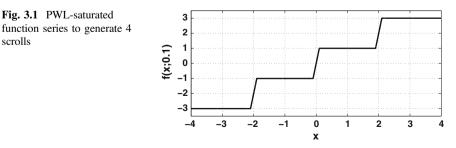

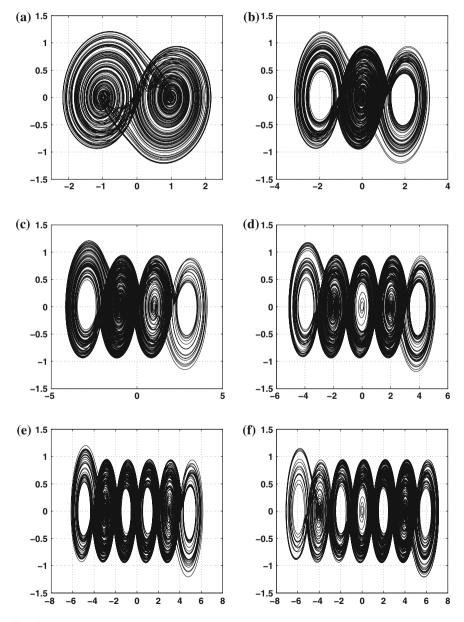

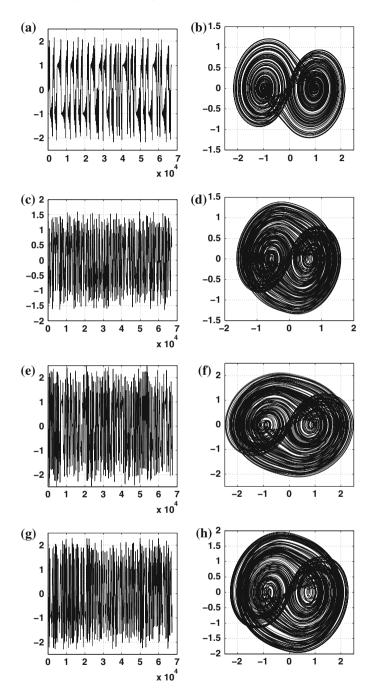

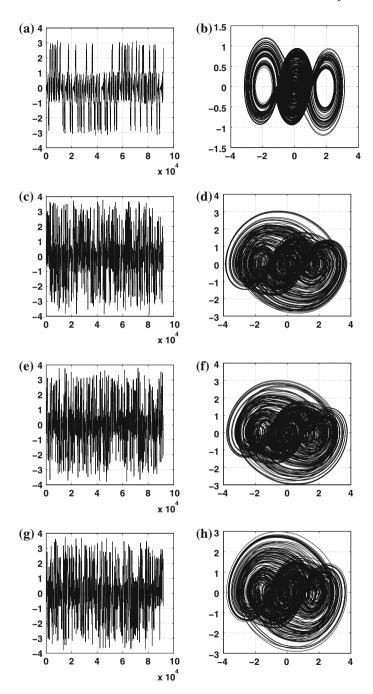

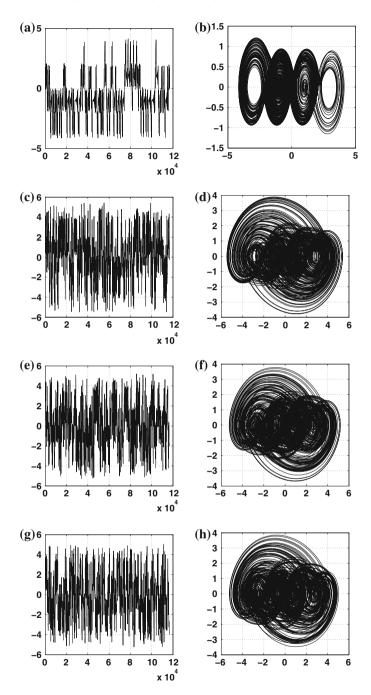

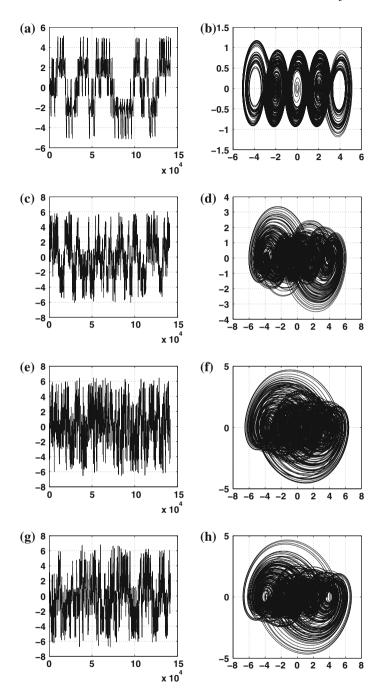

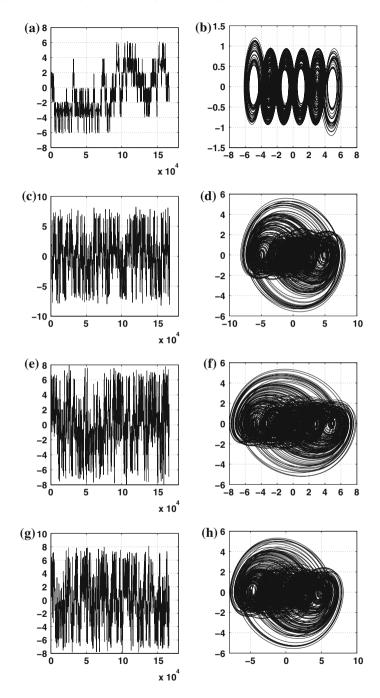

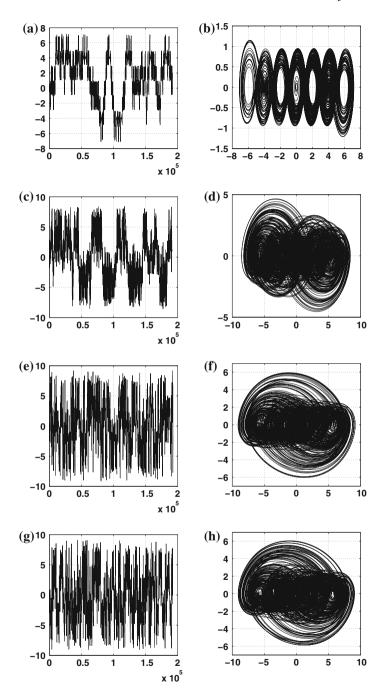

Chapter 3, "Application of Computational Intelligence Techniques to Maximize Unpredictability in Multiscroll Chaotic Oscillators," was written by Victor Hugo Carbajal-Gómez, Esteban Tlelo-Cuautle, and Francisco V. Fernández. It applies and compares three computational intelligence algorithms—the genetic algorithm (GA), differential evolution (DE), and particle swarm optimization (PSO)—to maximize the positive Lyapunov exponent in a multiscroll chaotic oscillator based on a saturated nonlinear function series based on the modification of the standard settings of the coefficient values of the mathematical description, and taking into account the correct distribution of the scrolls drawing the phase-space diagram. The experimental results show that the DE and PSO algorithms help to maximize the positive Lyapunov exponent of truncated coefficients over the continuous spaces.

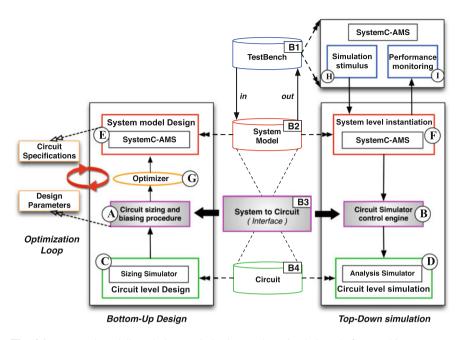

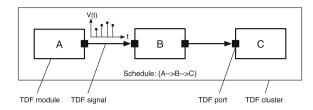

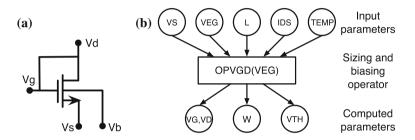

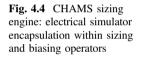

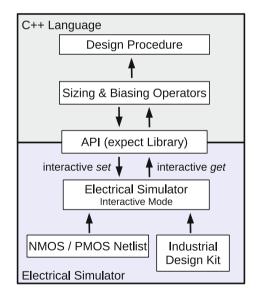

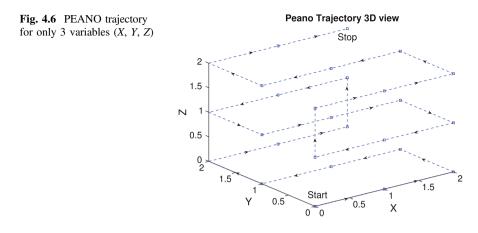

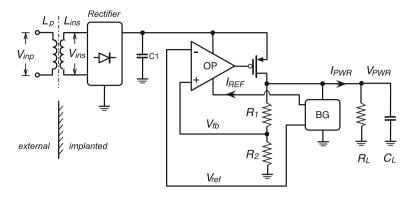

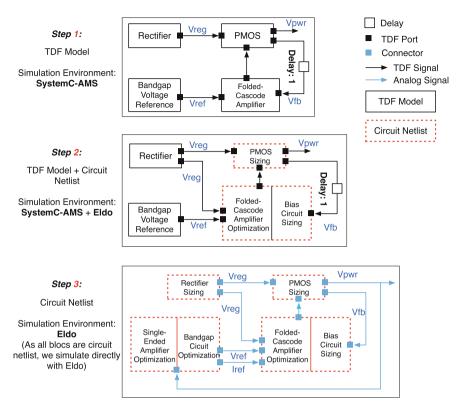

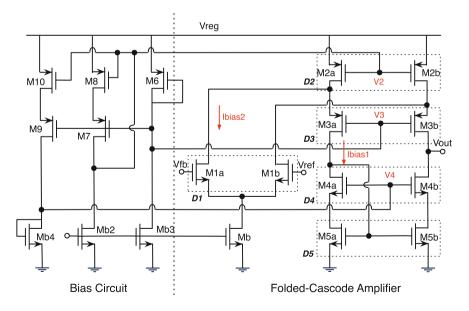

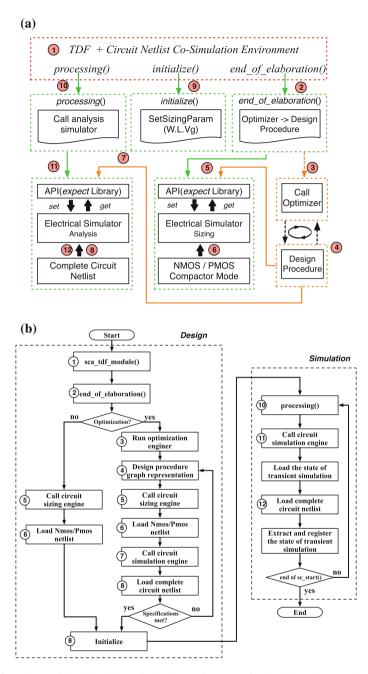

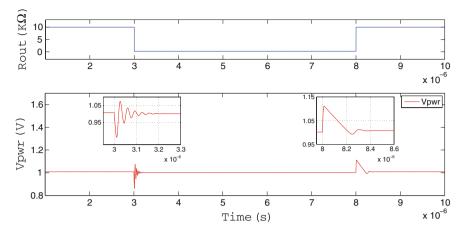

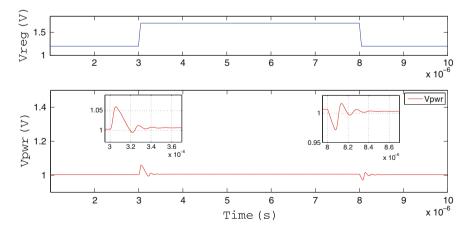

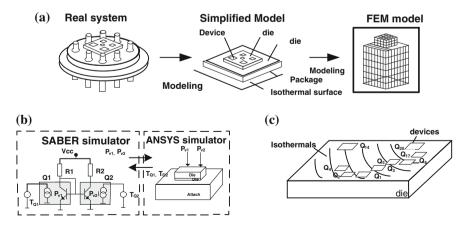

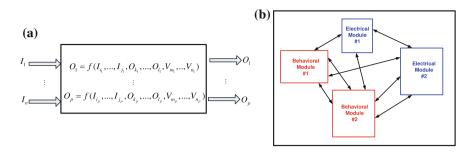

Chapter 4, "Optimization and Cosimulation of an Implantable Telemetric System by Linking System Models to Nonlinear Circuits," was written by Yao Li, Hao Zou, Yasser Moursy, Ramy Iskander, Robert Sobot, and Marie-Minerve Louërat. It presents a platform for modeling, design, optimization, and cosimulation of mixed-signal systems using the SystemC-AMS standard. The platform is based on a bottom-up design and top-down simulation methodologies. In the bottom-up design methodology, an optimizer is inserted to perform a knowledge-aware optimization loop. During the process, a Peano trajectory is applied for global exploration and the Nelder–Mead Simplex optimization method is applied for local refinement. The authors introduce an interface between system-level models and their circuit-level realizations in the proposed platform. Moreover, a transient simulation scheme is proposed to simulate nonlinear dynamic behavior of complete mixed-signal systems. The platform is used to design and verify a low-power CMOS voltage regulator for an implantable telemetry system.

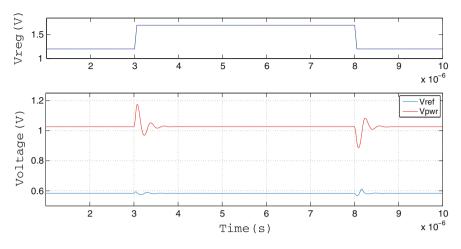

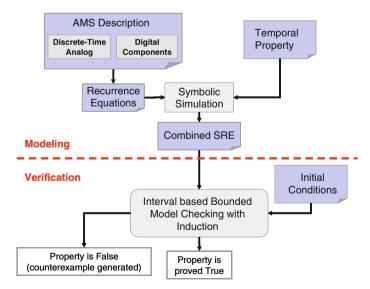

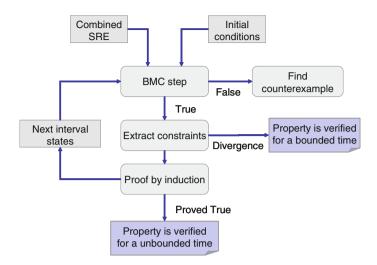

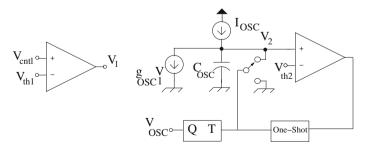

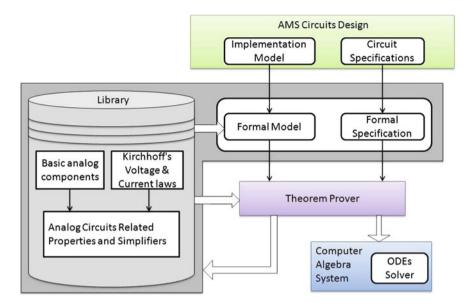

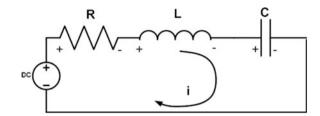

Chapter 5, "Framework for Formally Verifying Analog and Mixed-Signal Designs," was written by Mohamed H. Zaki, Osman Hasan, Sofiène Tahar, and Ghiath Al-Sammane. It proposes a complementary formal-based solution to the verification of analog and mixed-signal (AMS) designs. The authors use symbolic computation to model and verify AMS designs through the application of induction-based model checking. They also propose the use of higher order logic theorem proving to formally verify continuous models of analog circuits. To test and validate the proposed approaches, they developed prototype implementations in Mathematica and HOL and target analog and mixed-signal systems such as delta sigma modulators.

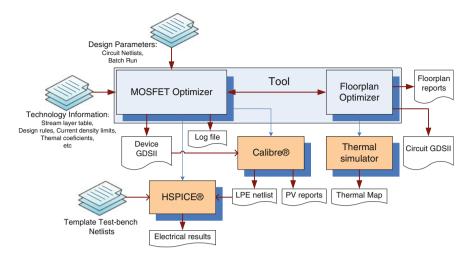

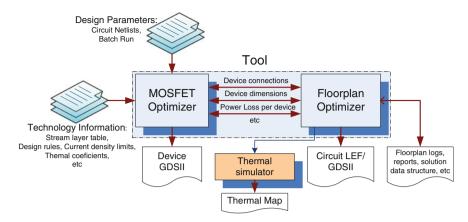

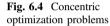

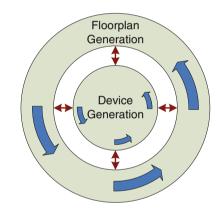

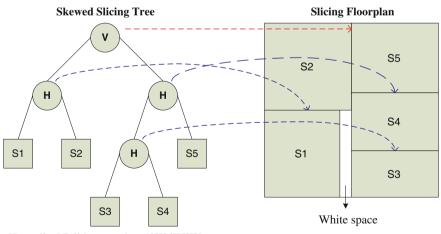

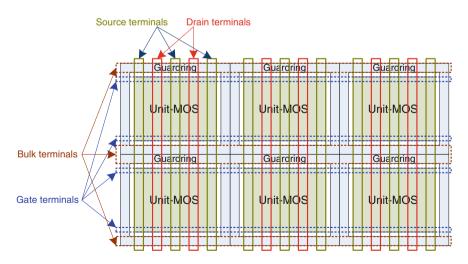

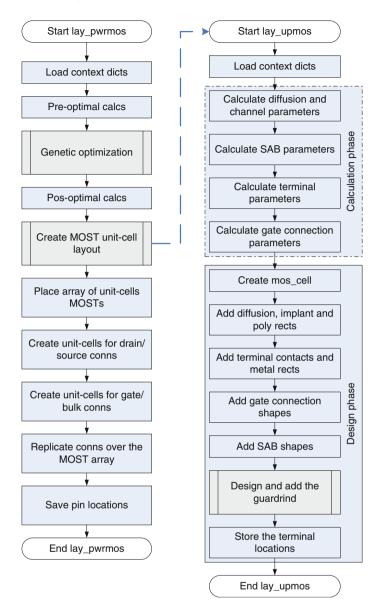

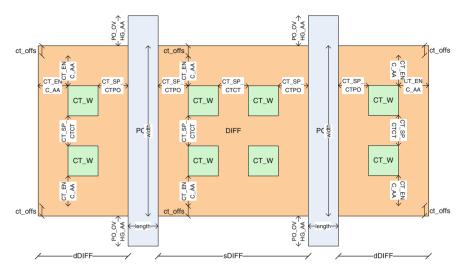

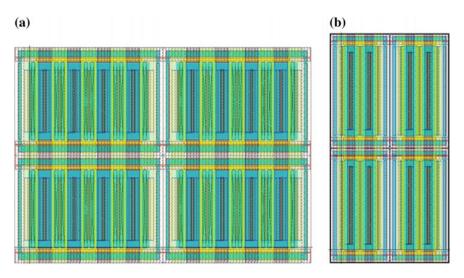

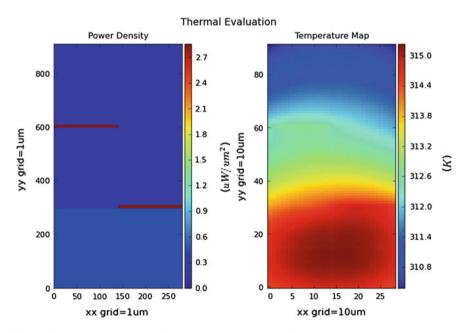

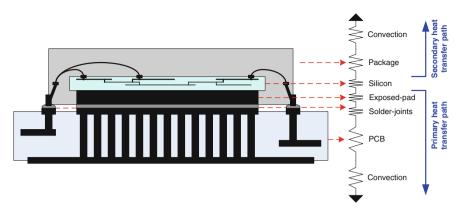

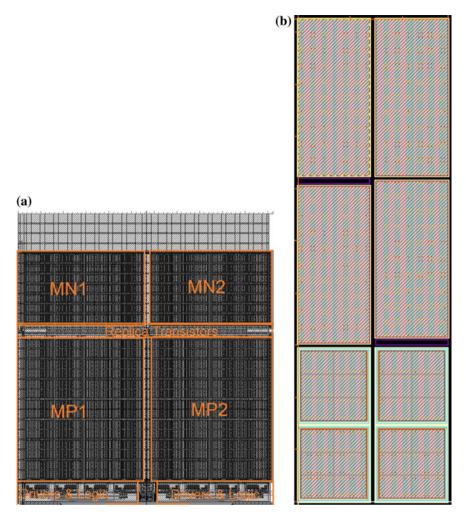

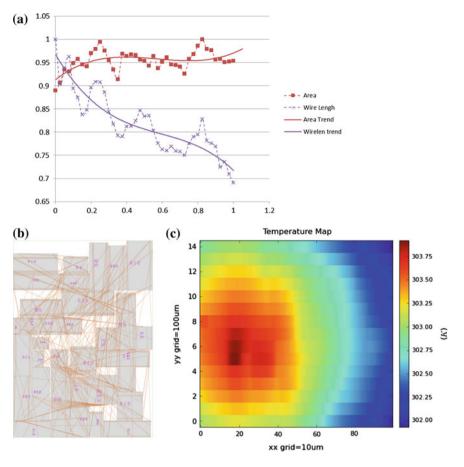

Chapter 6, "Automatic Layout Optimizations for Integrated MOSFET Power Stages," was written by David Guilherme, Jorge Guilherme, and Nuno Horta. It presents a design automation approach that generates automatically error-free area and parasitic optimized layout views of output power stages consisting of multiple power MOSFETs. The tool combines a multitude of constraints associated with DRC, DFM, ESD rules, current density limits, heat distribution, and placement. It uses several optimization steps based on evolutionary computation techniques that precede a bottom-up layout construction of each power MOSFET, its optimization for area and parasitic minimization, and its optimal placement within the output stage power topology network.

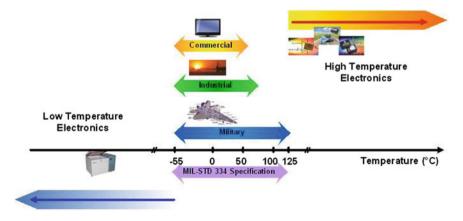

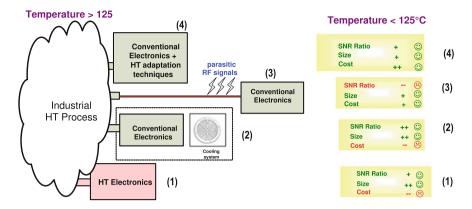

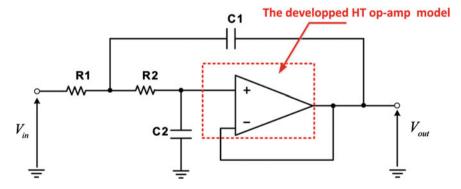

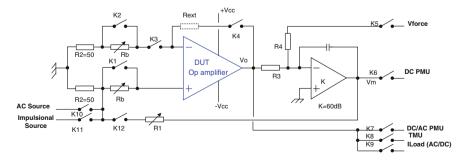

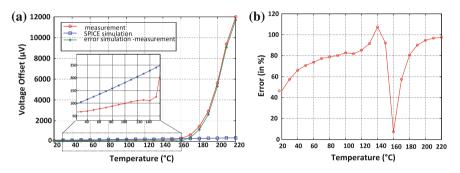

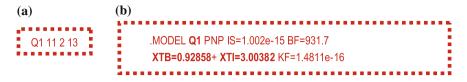

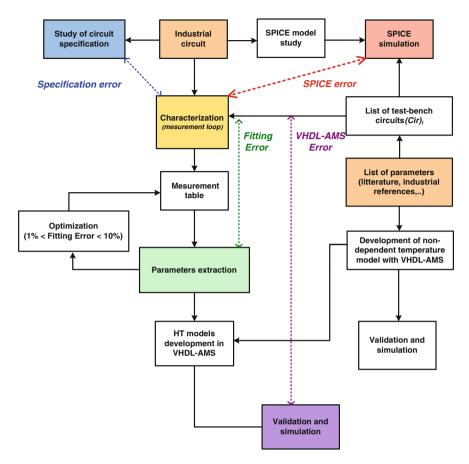

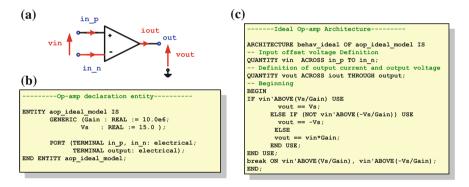

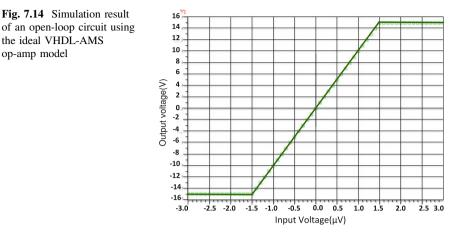

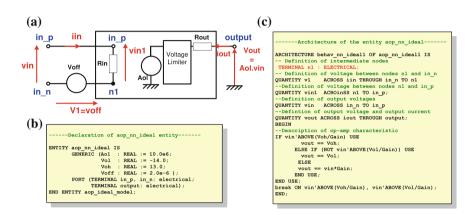

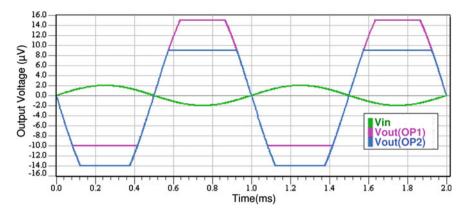

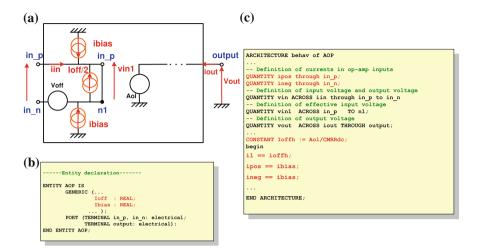

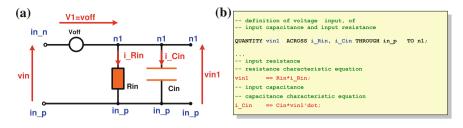

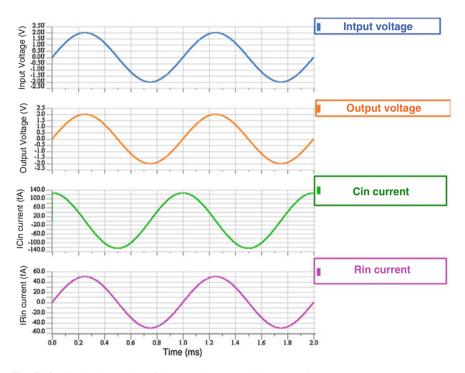

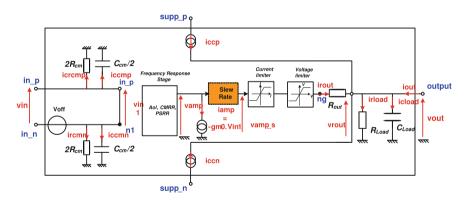

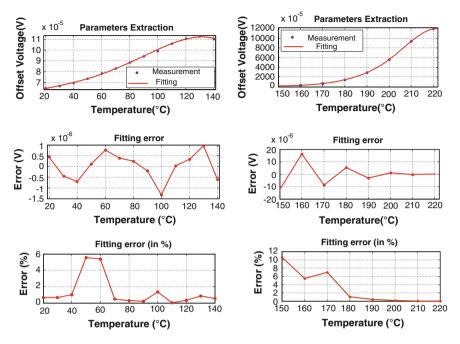

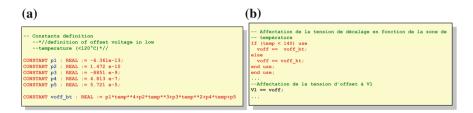

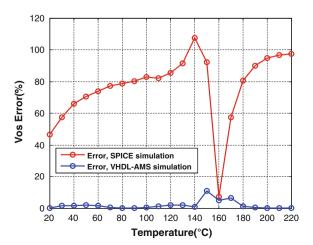

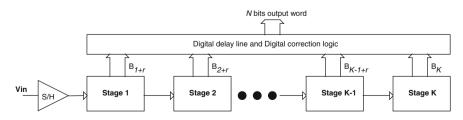

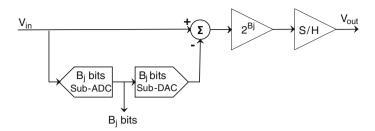

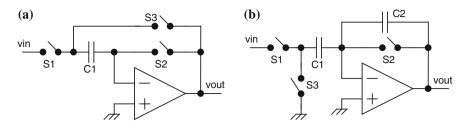

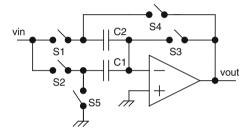

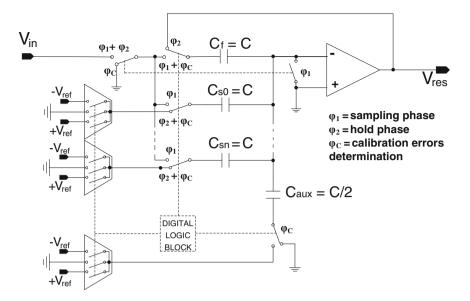

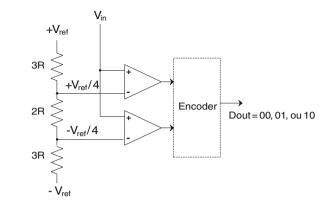

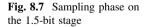

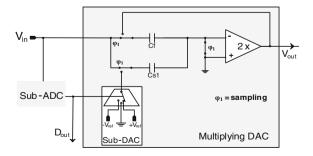

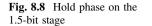

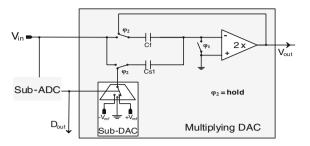

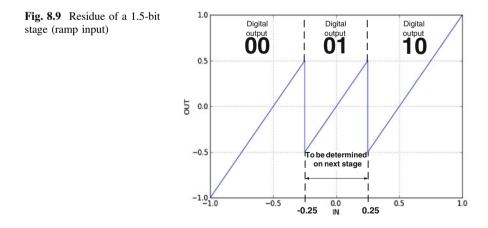

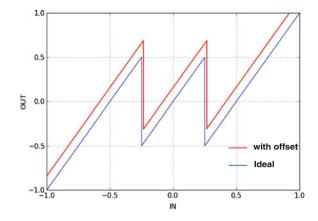

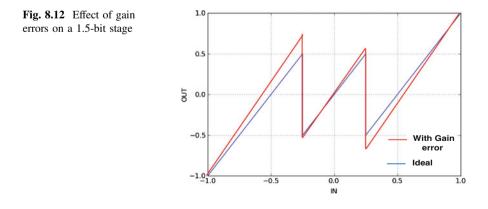

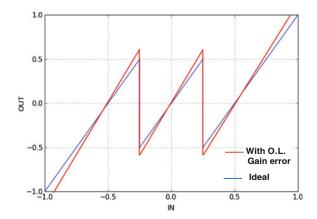

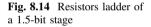

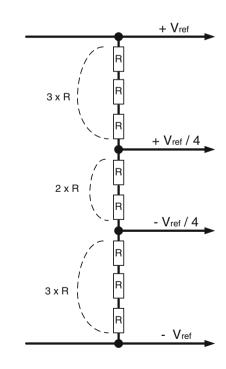

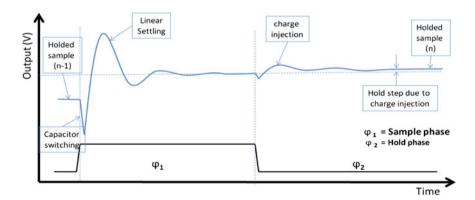

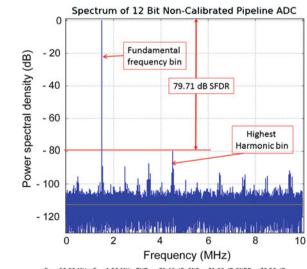

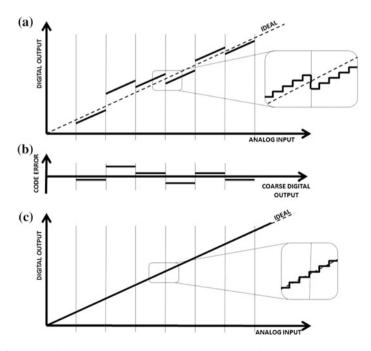

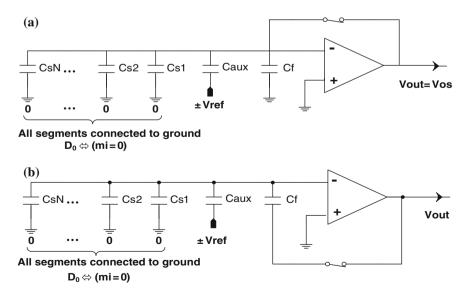

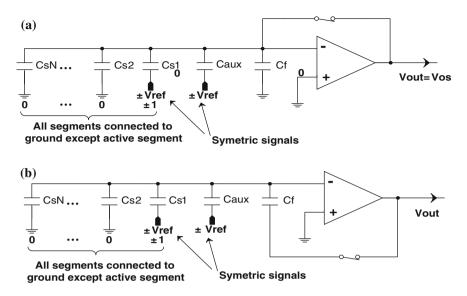

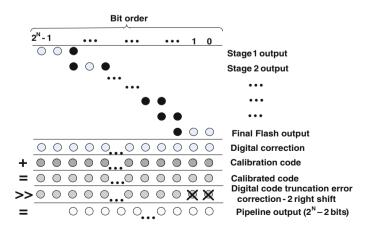

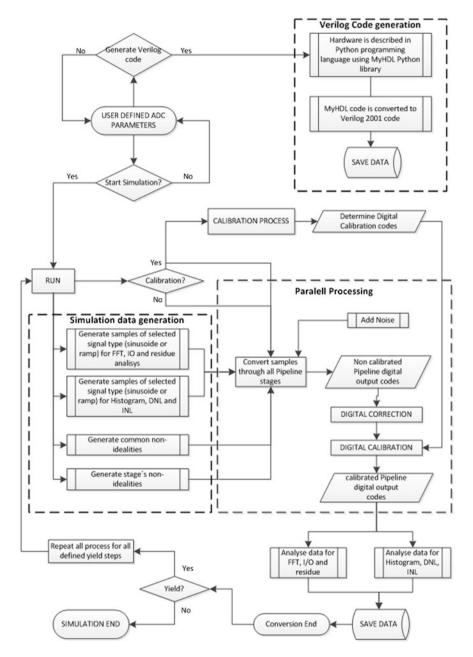

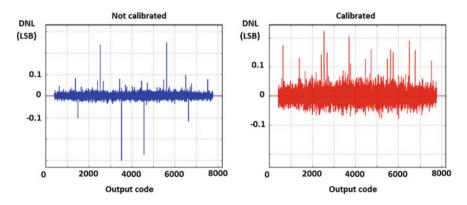

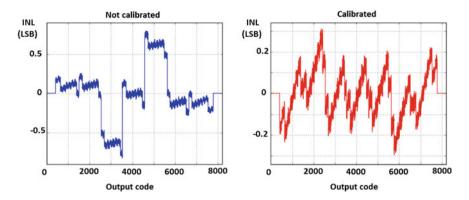

Chapter 7, "Optimizing Model Precision in High Temperatures for Efficient Analog and Mixed-Signal Circuit Design Using Modern Behavioral Modeling Techniques: an Industrial Case Study," was written by Sahbi Baccar, Timothée Levi, Dominique Dallet, and François Barbara. It deals with the description of a modeling methodology dedicated to simulation of AMS circuits in high temperatures (HT). A behavioral model of an op-amp is developed using VHDL-AMS in order to remedy the inaccuracy of the SPICE model. The precision of the model simulation in HT was improved thanks to the VHDL-AMS model. Almost all known op-amp parameters were inserted into the model which was developed manually. Future work can automate the generation of such a behavioral model to describe the interdependency between different parameters. This is possible by using modern computational intelligence techniques, such as genetic algorithms, or other techniques such as Petri nets or model order reduction. Chapter 8, "Nonlinearities Behavioral Modeling and Analysis of Pipelined ADC Building Blocks," was written by Carlos Silva, Philippe Ayzac, Nuno Horta, and Jorge Guilherme. It presents a high-speed simulation tool for the design and analysis of pipelined analog-to-digital converters implemented using the Python programming language. The development of an ADC simulator requires the behavior modeling of the basic building blocks and their possible interconnections to form the final converter. This chapter presents a Pipeline ADC simulator tool which allows topology selection and digital calibration of the frontend blocks. Several block nonlinearities are included in the simulation, such as thermal noise, capacitor mismatch, gain and offset errors, parasitic capacitances, settling errors, and other error sources.

#### Part II—Radio-Frequency Design

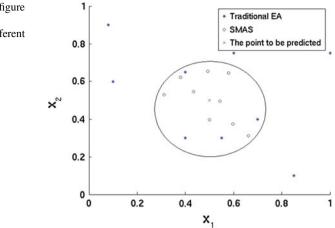

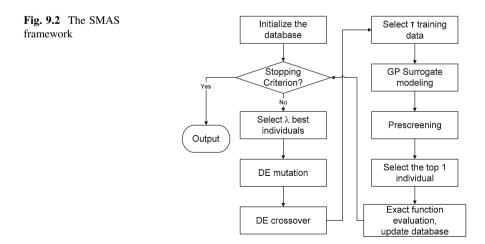

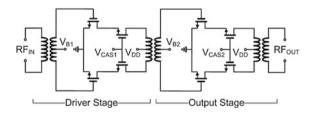

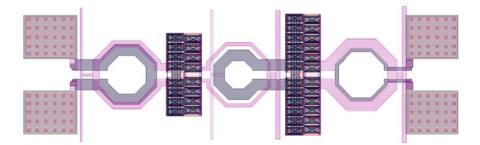

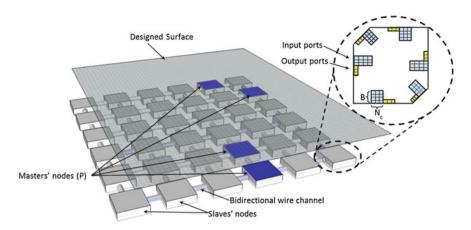

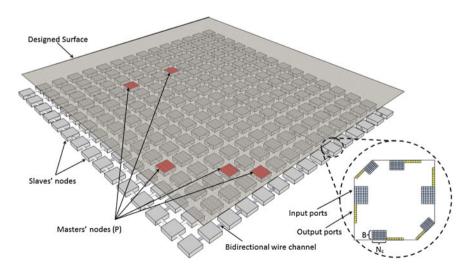

Chapter 9, "SMAS: A Generalized and Efficient Framework for Computationally Expensive Electronic Design Optimization Problems," was written by Bo Liu, Francisco V. Fernández, Georges Gielen, Ammar Karkar, Alex Yakovlev, and Vic Grout. Many electronic design automation (EDA) problems encounter computationally expensive simulations, making simulation-based optimization impractical for many popular synthesis methods. Not only are they computationally expensive, but some EDA problems also have dozens of design variables, tight constraints, and discrete landscapes. Few available computational intelligence methods can solve them effectively and efficiently. This chapter introduces a surrogate model-aware evolutionary search (SMAS) framework, which is able to use much fewer expensive exact evaluations with comparable or better solution quality. SMAS-based methods for mm-wave integrated circuit synthesis and network-on-chip parameter design optimization are proposed and are tested on several practical problems. Experimental results show that the developed EDA methods can obtain highly optimized designs within practical time limitations.

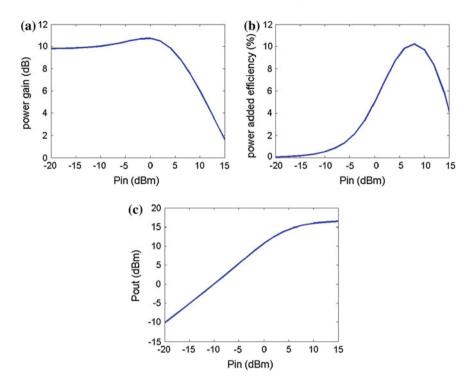

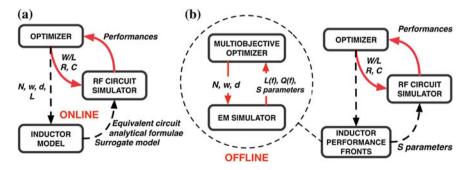

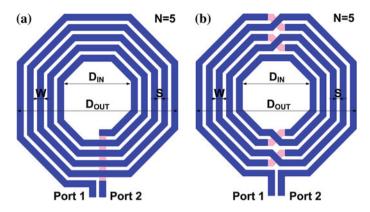

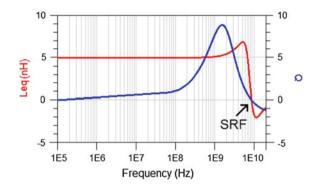

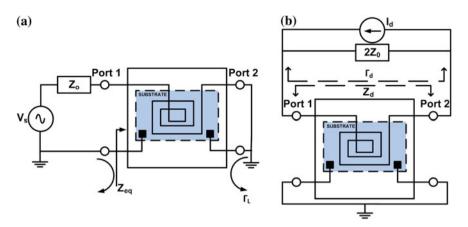

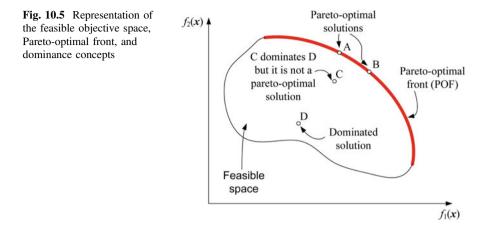

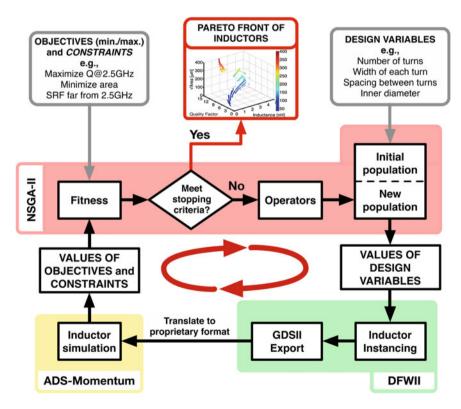

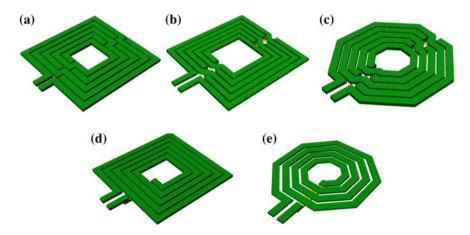

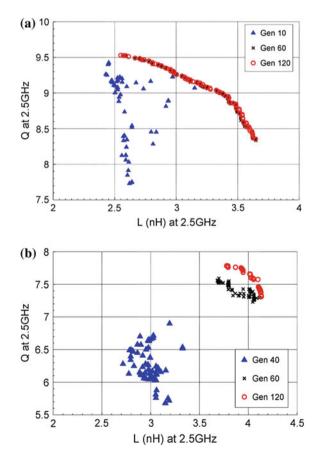

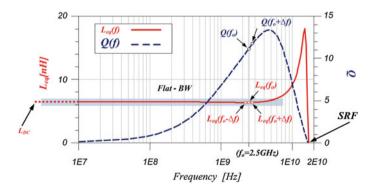

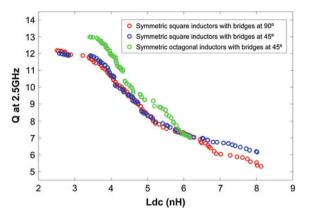

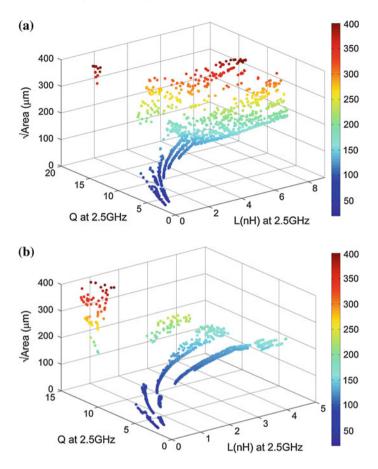

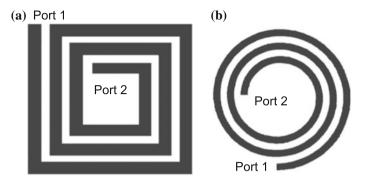

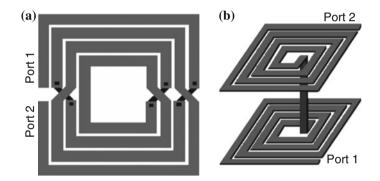

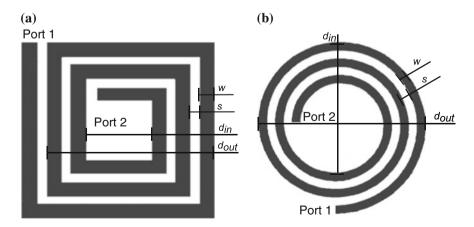

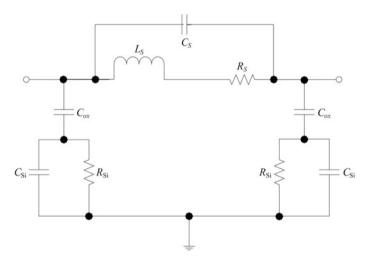

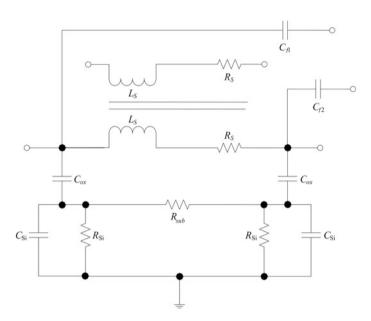

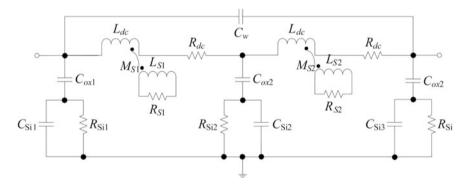

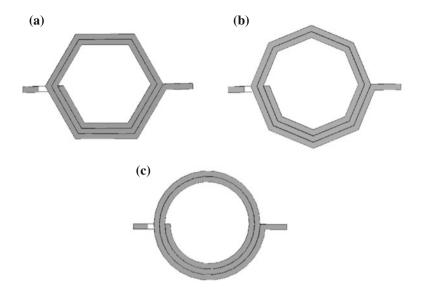

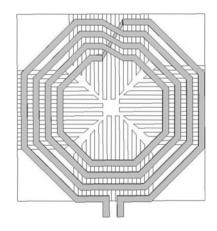

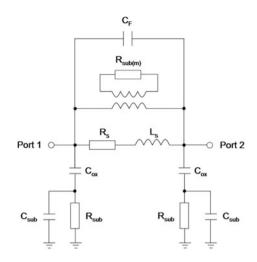

Chapter 10, "Computational Intelligence Techniques for Determining Optimal Performance Trade-offs for RF Inductors," was written by Elisenda Roca, Rafael Castro-López, Francisco V. Fernández, Reinier González-Echevarría, Javier Sieiro, Neus Vidal, and José M. López-Villegas. The automatic synthesis of integrated inductors for radio-frequency (RF) integrated circuits is one of the most challenging problems that RF designers have to face. In this chapter, computational intelligence techniques are applied to automatically obtain the optimal performance trade-offs of integrated inductors. A methodology is presented that combines a multiobjective evolutionary algorithm with electromagnetic simulation to get highly accurate results. A set of sized inductors is obtained showing the best performance trade-offs for a given technology. The methodology is illustrated with a complete set of examples where different inductor trade-offs are obtained.

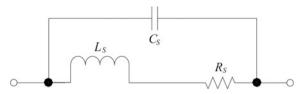

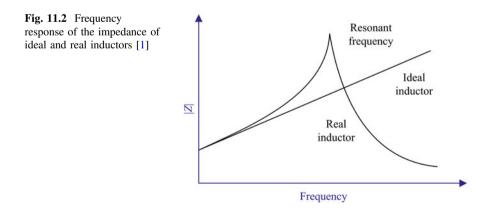

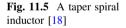

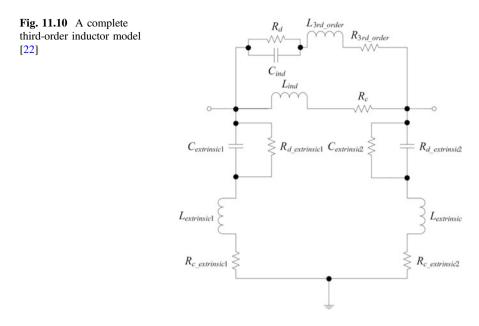

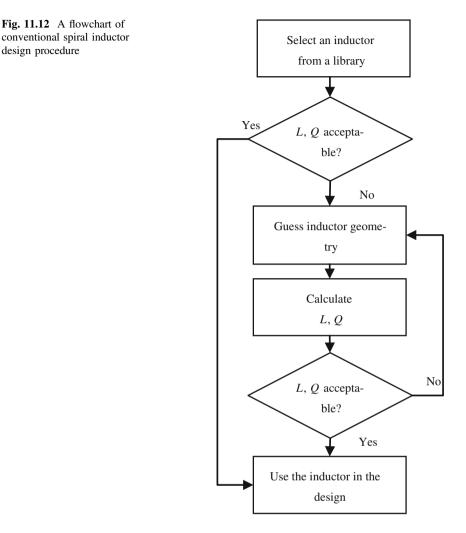

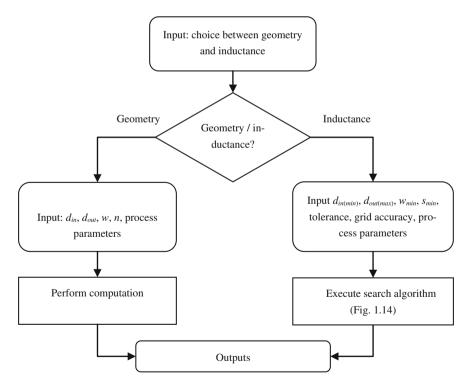

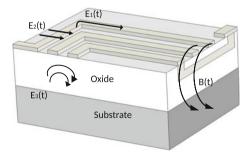

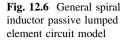

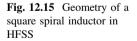

Chapter 11, "RF IC Performance Optimization by Synthesizing Optimum Inductors," was written by Mladen Božanić and Saurabh Sinha. It reviews inductor theory and describes various integrated inductor options. It also explains why integrated planar spiral inductors are so useful when it comes to integrated RF circuits. Furthermore, the chapter discusses the theory of spiral inductor design, inductor modeling, and how this theory can be used in inductor synthesis. In the central part of the chapter, the authors present a methodology for synthesis of planar spiral inductors, where numerous geometries are searched through in order to fit various initial conditions.

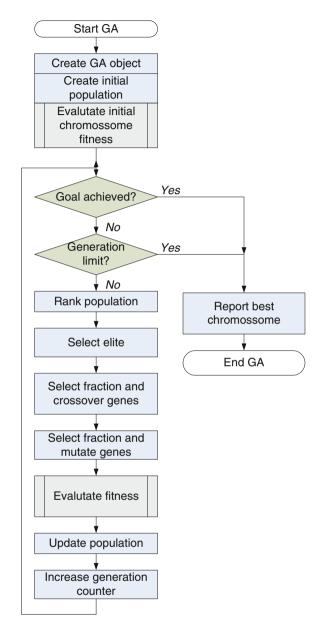

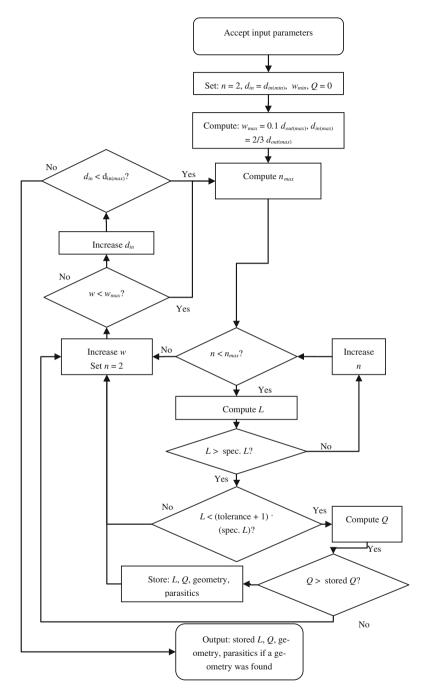

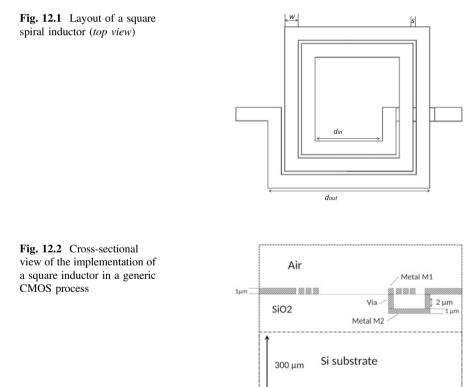

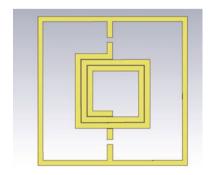

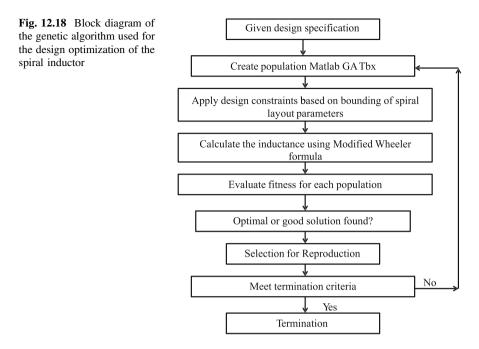

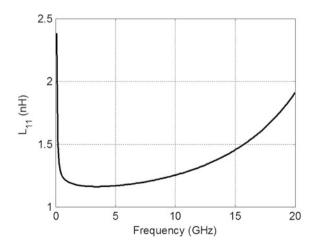

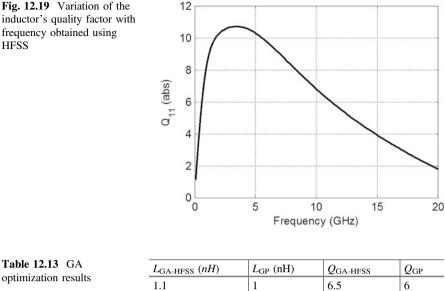

Chapter 12, "Optimization of RF On-Chip Inductors Using Genetic Algorithms," was written by Eman Omar Farhat, Kristian Zarb Adami, Owen Casha, and John Abela. It discusses the optimization of the geometry of RF on-chip inductors by means of a genetic algorithm in order to achieve adequate performance. Necessary background theory together with the modeling of these inductors is included in order to aid the discussion. A set of guidelines for the design of such inductors with a good quality factor in a standard CMOS process is also provided. The optimization process is initialized by using a set of empirical formulae in order to estimate the physical parameters of the required structure as constrained by the technology. Then automated design optimization is executed to further improve its performance by means of dedicated software packages. The authors explain how to use state-of-the-art computer-aided design tools in the optimization process and how to efficiently simulate the inductor performance using electromagnetic simulators.

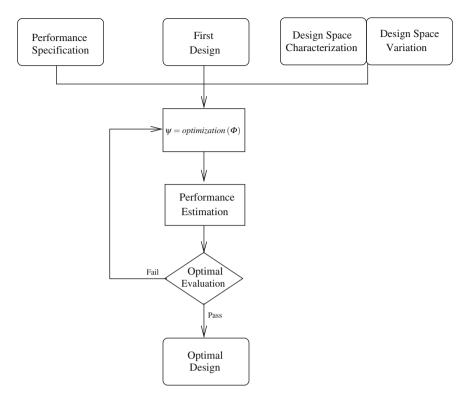

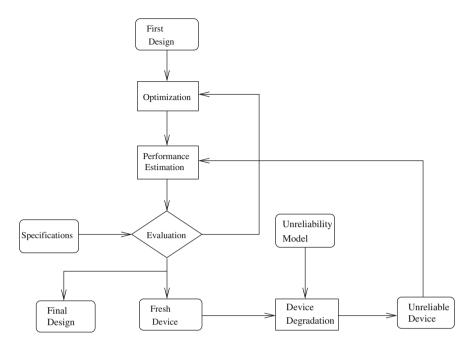

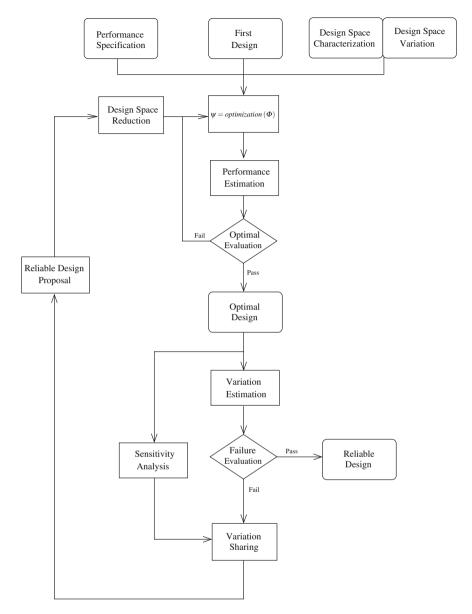

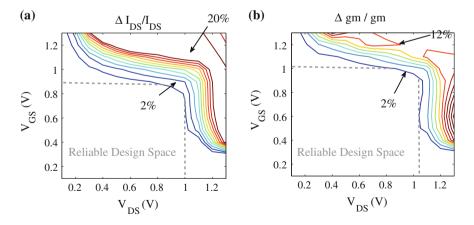

Chapter 13, "Automated System-Level Design for Reliability: RF Front-End Application," was written by Pietro Maris Ferreira, Jack Ou, Christophe Gaquière, and Philippe Benabes. Reliability is an important issue for circuits in critical applications such as military, aerospace, energy, and biomedical engineering. With the rise in the failure rate in nanometer CMOS, reliability has become critical in recent years. Existing design methodologies consider classical criteria such as area, speed, and power consumption. They are often implemented using post-synthesis reliability analysis and simulation tools. This chapter proposes an automated system design for reliability methodology. While accounting for a circuit's reliability in the early design stages, the proposed methodology is capable of identifying an RF front-end optimal design considering reliability as a criterion.

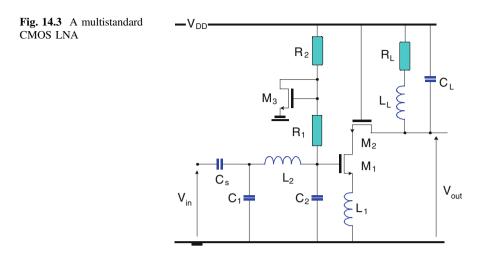

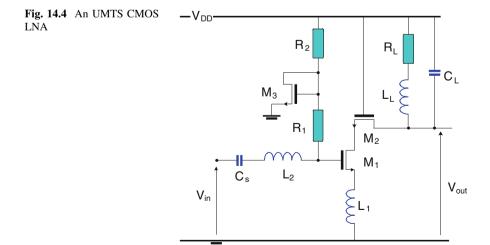

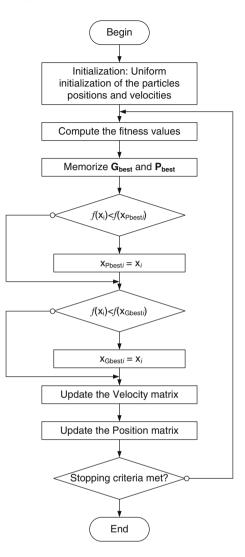

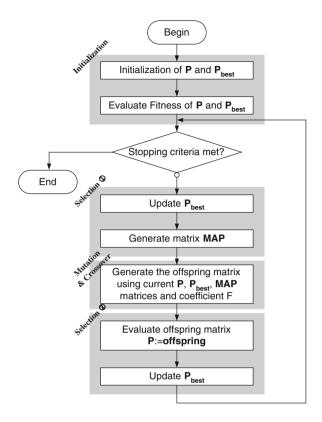

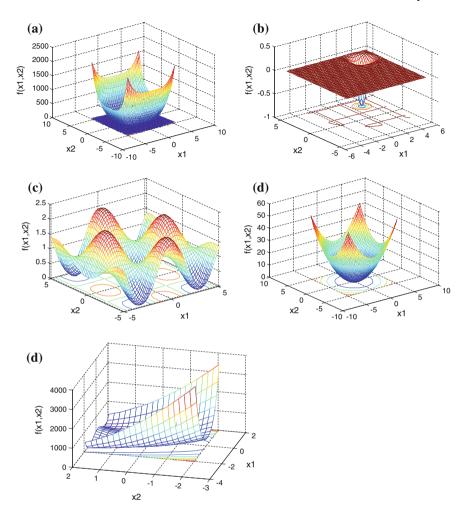

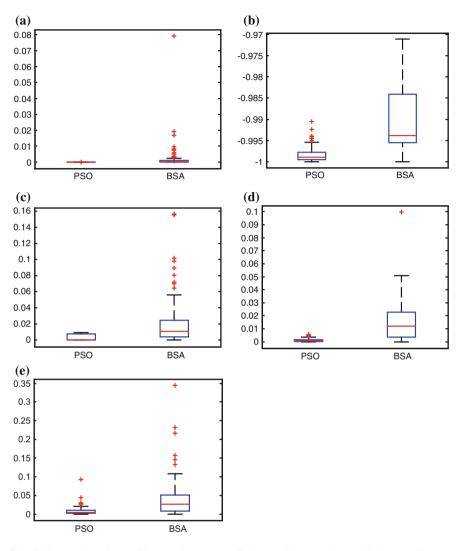

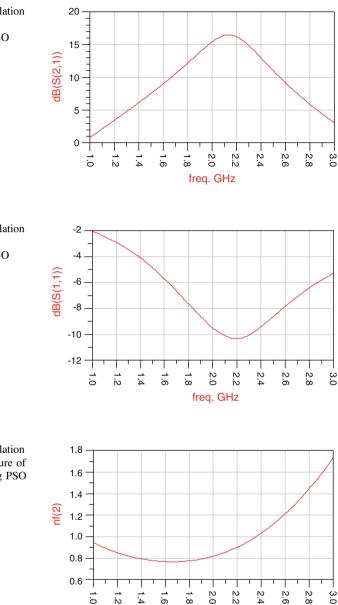

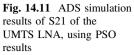

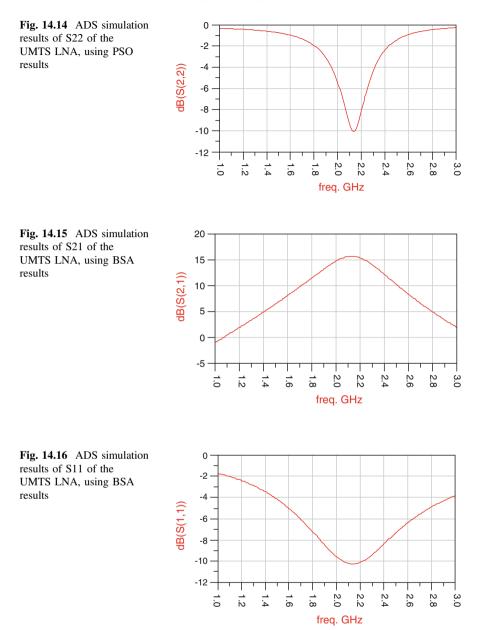

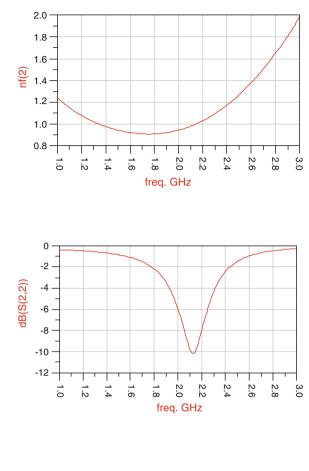

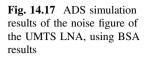

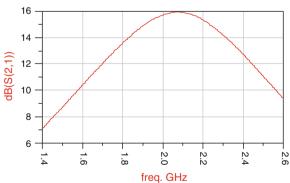

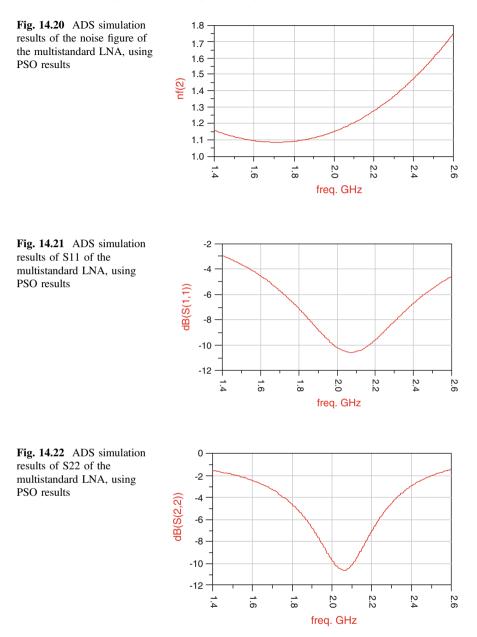

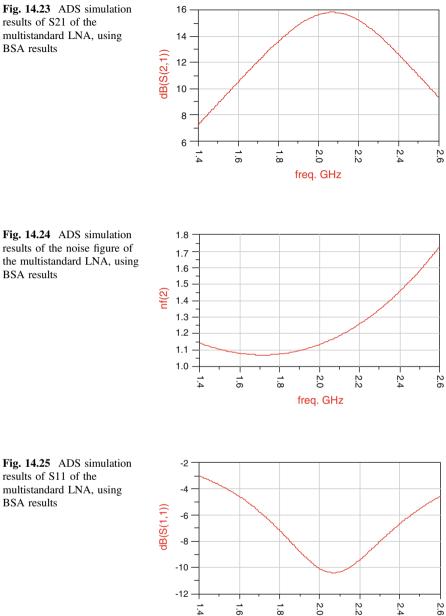

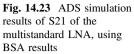

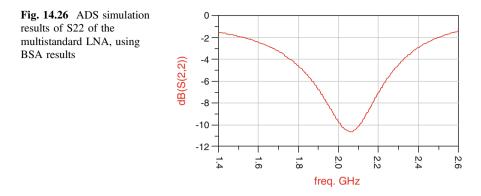

Chapter 14, "The Backtracking Search for the Optimal Design of Low-Noise Amplifiers," was written by Amel Garbaya, Mouna Kotti, Mourad Fakhfakh, and Patrick Siarry. The backtracking search algorithm (BSA) was recently developed. It is an evolutionary algorithm for real-valued optimization problems. The main feature of BSA vis-à-vis other known evolutionary algorithms is that it has a single control parameter. It has also been shown that it has a better convergence behavior. In this chapter, the authors deal with the application of BSA to the optimal design of RF circuits, namely low-noise amplifiers. BSA performances, viz. robustness and speed, are checked against the widely used particle swarm optimization technique, and other published approaches. ADS simulation results are given to show the viability of the obtained results.

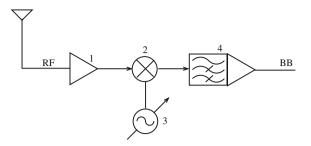

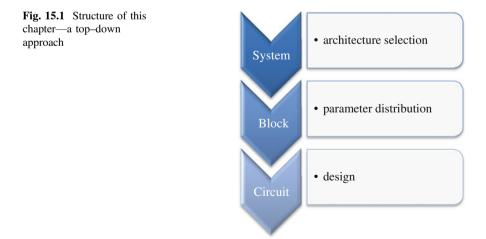

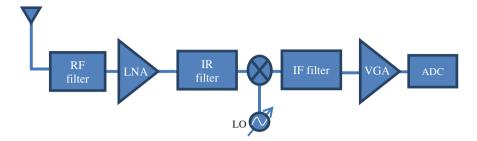

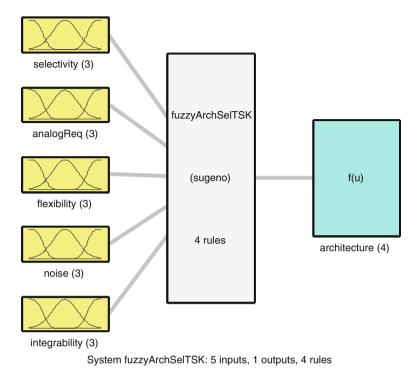

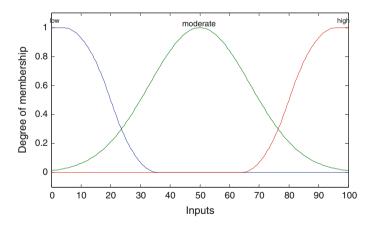

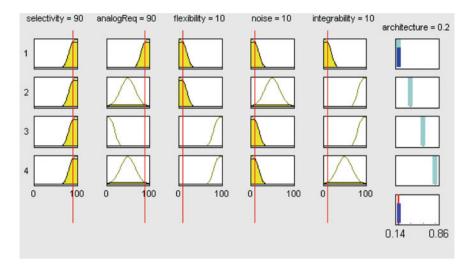

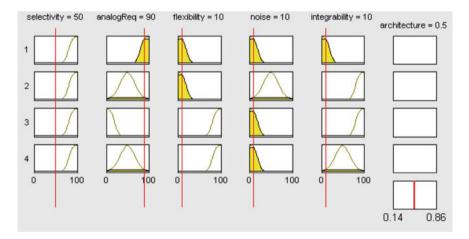

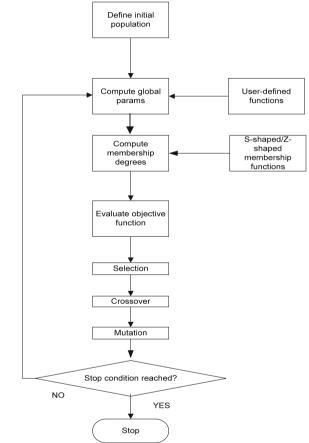

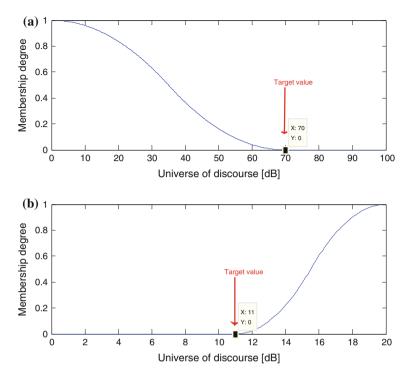

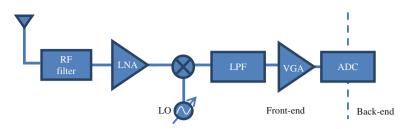

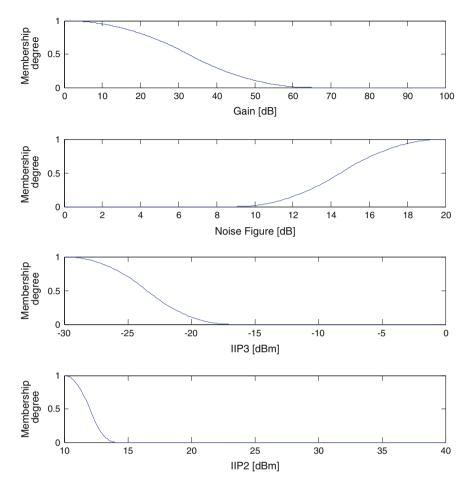

Chapter 15, "Design of Telecommunications Receivers Using Computational Intelligence Techniques," was written by Laura-Nicoleta Ivanciu and Gabriel Oltean. It proposes system-, block- and circuit-level design procedures that use computational intelligence techniques, taking into consideration the specifications for telecommunications receivers. The design process starts with selecting the proper architecture (topology) of the system, using a fuzzy expert solution. Next, at the block level, the issue of distributing the parameters across the blocks is solved using a hybrid fuzzy–genetic algorithms approach. Finally, multiobjective optimization using genetic algorithms is employed in the circuit-level design. The proposed methods were tested under specific conditions and have proved to be robust and trustworthy.

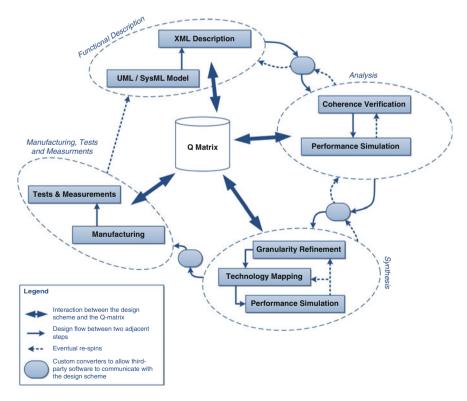

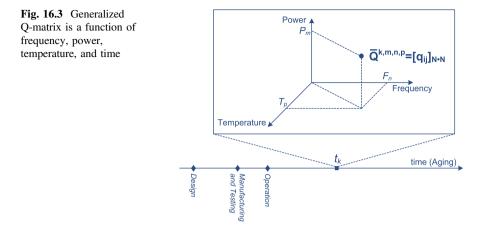

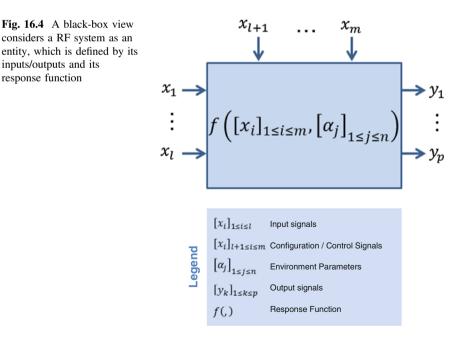

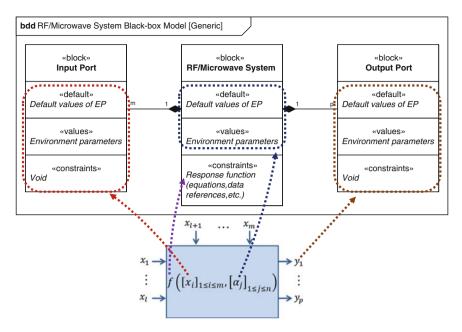

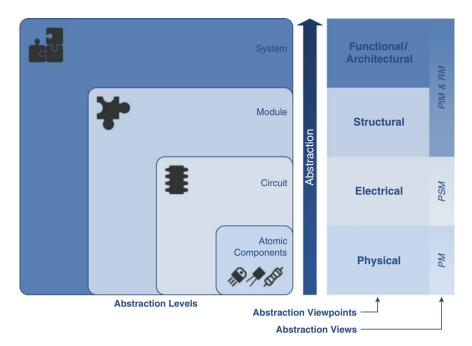

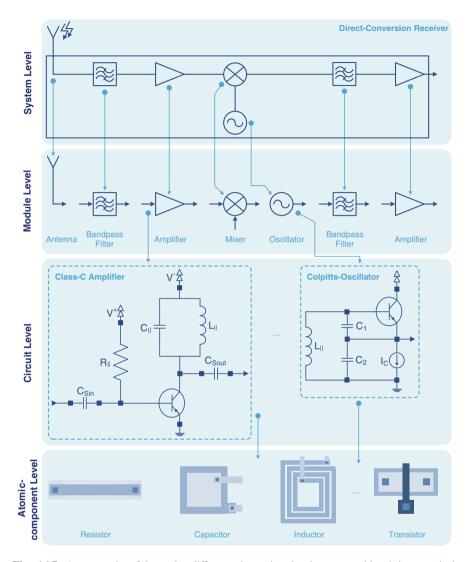

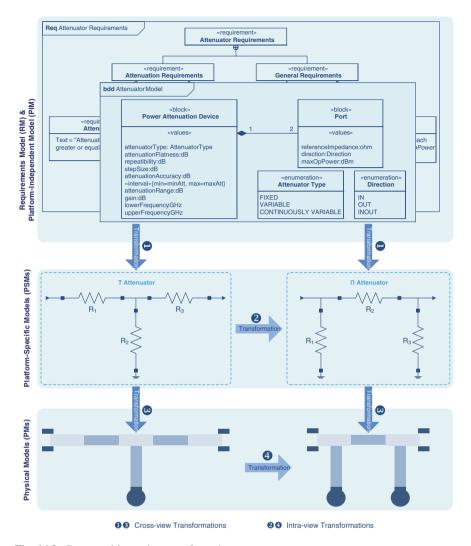

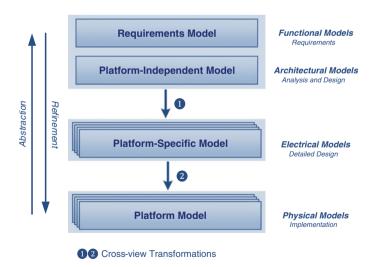

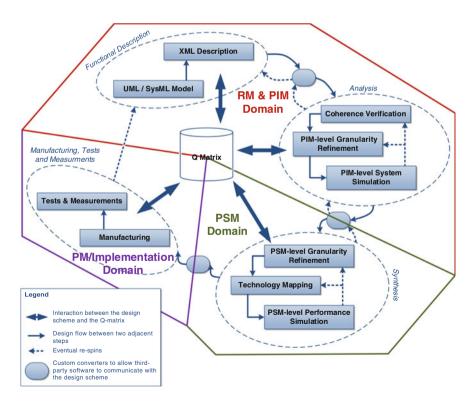

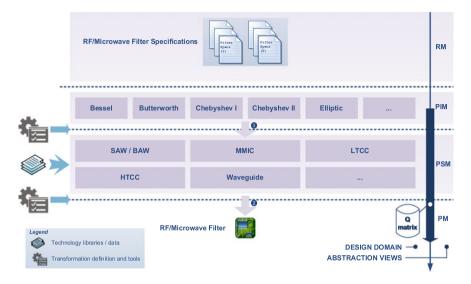

Chapter 16, "Enhancing Automation in RF Design Using Hardware Abstraction," was written by Sabeur Lafi, Ammar Kouki, and Jean Belzile. It presents advances in automating RF design through the adoption of a framework that tackles primarily the issues of automation, complexity reduction, and design collaboration. The proposed framework consists of a design cycle along with a comprehensive RF hardware abstraction strategy. Being a model-centric framework, it captures each RF system using an appropriate model that corresponds to a given abstraction level and expresses a given design perspective. It also defines a set of mechanisms for the transition between the models defined at different abstraction levels, which contributes to the automation of design stages. The combination of an intensive modeling activity and a clear hardware abstraction strategy through a flexible design cycle introduces intelligence, enabling higher design automation, and agility.

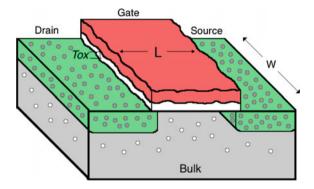

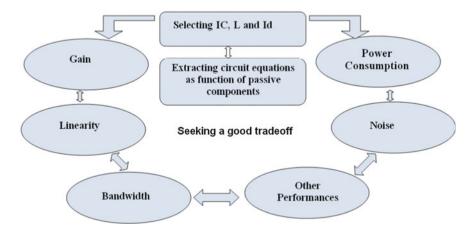

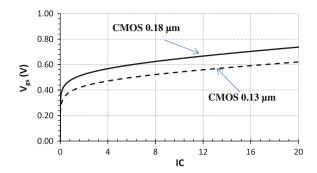

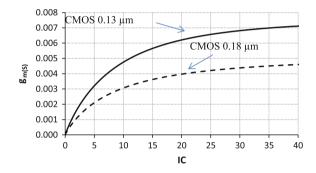

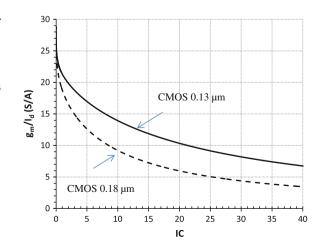

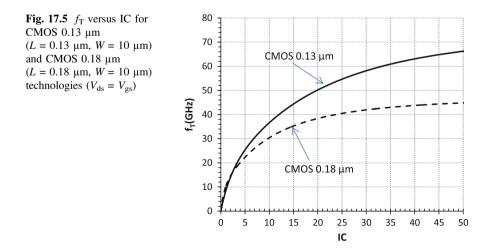

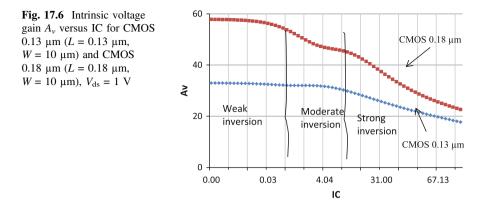

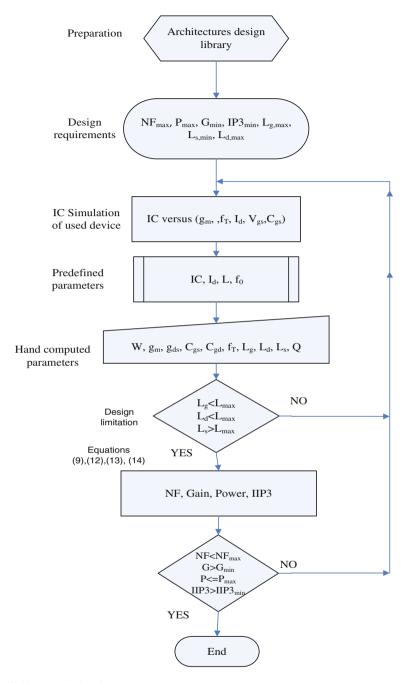

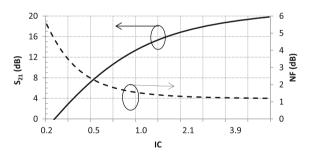

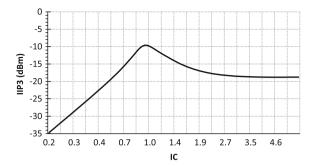

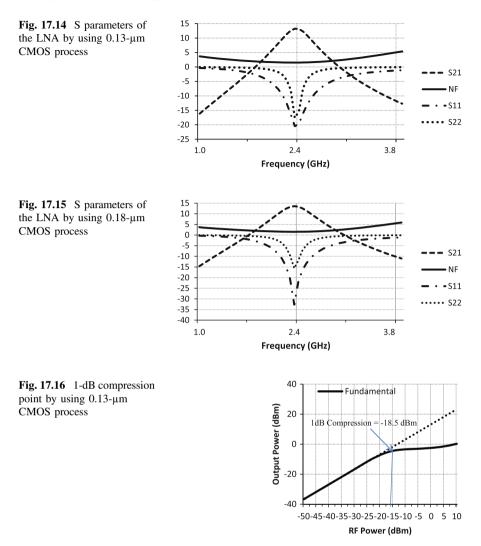

Chapter 17, "Optimization Methodology Based on IC Parameter for the Design of Radio-Frequency Circuits in CMOS Technology," was written by Abdellah Idrissi Ouali, Ahmed El Oualkadi, Mohamed Moussaoui, and Yassin Laaziz. It presents a computational methodology for the design optimization of ultra-low-power CMOS radio-frequency front-end blocks. The methodology allows us to explore MOS transistors in all regions of inversion. The power level is set as an input parameter before we begin the computational process involving other aspects of the design performance. The approach consists of trade-offs between power consumption and other radio-frequency performance parameters. This can help designers to seek quickly and accurately the initial sizing of the radio-frequency building blocks while maintaining low levels of power consumption. A design example shows that the best trade-offs between the most important low-power radio-frequency performances occur in the moderate inversion region.

## Volume 2—Computational Intelligence in Digital and Network Designs and Applications

#### Part I—Digital Design

Chapter 1, "Sizing Digital Circuits Using Convex Optimization Techniques," was written by Logan Rakai and Amin Farshidi. It collects recent advances in using convex optimization techniques to perform sizing of digital circuits. Convex optimization techniques provide an undeniably attractive promise: The attained solution is the best available. In order to use convex optimization techniques, the target optimization problem must be modeled using convex functions. The gate sizing problem has been modeled in different ways to enable the use of convex optimization techniques, such as linear programming and geometric programming. Statistical and robust sizing methods are included to reflect the importance of optimization techniques that are aware of variations. Applications of multiobjective optimization techniques that aid designers in evaluating the trade-offs are described.

Chapter 2, "A Fabric Component Based Approach to the Architecture and Design Automation of High-Performance Integer Arithmetic Circuits on FPGA," was written by Ayan Palchaudhuri and Rajat Subhra Chakraborty. FPGA-specific primitive instantiation is an efficient approach for design optimization to effectively utilize the native hardware primitives as building blocks. Placement steps also need to be constrained and controlled to improve the circuit critical path delay. Here, the authors present optimized implementations of certain arithmetic circuits and pseudorandom sequence generator circuits to indicate the superior performance scalability achieved using the proposed design methodology in comparison with the circuits of identical functionality realized using other existing FPGA CAD tools or design methodologies. The hardware description language specifications as well as the placement constraints can be automatically generated. A GUI-based CAD tool has been developed, that is integrated with the Xilinx Integrated Software Environment for design automation of circuits from user specifications.

Chapter 3, "Design Intelligence for Interconnection Realization in Power-Managed SoCs," was written by Houman Zarrabi, A.J. Al-Khalili, and Yvon Savaria. Here, various intelligent techniques for modeling, design, automation, and management of on-chip interconnections in power-managed SoCs are described, including techniques that take into account various technological parameters such as cross talk. Such intelligent techniques guarantee that the integrated interconnections, used in power-managed SoCs, are well-designed, energy-optimal and meet the performance objectives in all the SoCs operating states.

Chapter 4, "Introduction to Optimization Under Uncertainty Techniques for High-Performance Multicore Embedded Systems Compilation," was written by Oana Stan and Renaud Sirdey. The compilation process design for massively parallel multicore embedded architectures requires solving a number of difficult optimization problems, nowadays solved mainly using deterministic approaches. However, one of the main characteristics of these systems is the presence of uncertain data, such as the execution times of the tasks. The authors consider that embedded systems design is one of the major domains for which applying optimization under uncertainty is legitimate and highly beneficial. This chapter introduces the most suitable techniques from the field of optimization under uncertainty for the design of compilation chains and for the resolution of associated optimization problems.

Chapter 5, "Digital IIR Filter Design with Fix-Point Representation Using Effective Evolutionary Local Search Enhanced Differential Evolution," was written by Yu Wang, Weishan Dong, Junchi Yan, Li Li, Chunhua Tian, Chao Zhang, Zhihu Wang, and Chunyang Ma. Previously, the parameters of digital IIR filters were encoded with floating-point representations. It is known that a fixed-point representation can effectively save computational resources and is more convenient for direct realization on hardware. Inherently, compared with floating-point repre-

sentation, fixed-point representation may make the search space miss much useful gradient information and, therefore, raises new challenges. In this chapter, the universality of DE-based MA is improved by implementing more efficient evolutionary algorithms (EAs) as the local search techniques. The performance of the newly designed algorithm is experimentally verified in both function optimization tasks and digital IIR filter design problems.

Chapter 6, "Applying Operations Research to Design for Test Insertion Problems," was written by Yann Kieffer and Lilia Zaourar. Enhancing electronic circuits with ad hoc testing circuitry—so-called design for test (DFT)—is a technique that enables one to thoroughly test circuits after production. But this insertion of new elements itself may sometimes be a challenge, for bad choices could lead to unacceptable degradations of features of the circuit, while good choices may help reduce testing costs and circuit production costs. This chapter demonstrates how methods from operations research—a scientific discipline rooted in both mathematics and computer science, leaning strongly on the formal modeling of optimization issues—help us to address such challenges and build efficient solutions leading to real-world solutions that may be integrated into electronic design software tools.

#### Part II—Network Design

Chapter 7, "Low-Power NoC Using Optimum Adaptation," was written by Sayed T. Muhammad, Rabab Ezz-Eldin, Magdy A. El-Moursy, Ali A. El-Moursy, and Amr M. Refaat. Two power-reduction techniques are exploited to design a low-leakage-power NoC switch. First. the adaptive virtual channel (AVC) technique is presented as an efficient way to reduce the active area using a hierarchical multiplexing tree of VC groups. Second, power gating reduces the average leakage power consumption of the switch by controlling the supply power of the VC groups. The traffic-based virtual channel activation (TVA) algorithm is presented to determine traffic load status at the NoC switch ports. The TVA algorithm optimally utilizes virtual channels by deactivating idle VC groups to guarantee high-leakage-power saving without affecting the NoC throughput.

Chapter 8, "Decoupling Network Optimization by Swarm Intelligence," was written by Jai Narayan Tripathi and Jayanta Mukherjee. Here, the problem of decoupling network optimization is discussed in detail. Swarm intelligence is used for maintaining power integrity in high-speed systems. The optimum number of capacitors and their values are selected to meet the target impedance of the system.

#### Part III—Applications

Chapter 9, "The Impact of Sensitive Inputs on the Reliability of Nanoscale Circuits," was written by Usman Khalid, Jahanzeb Anwer, Nor H. Hamid, and Vijanth S. Asirvadam. As CMOS technology scales to nanometer dimensions, its performance and behavior become less predictable. Reliability studies for nanocircuits and systems become important when the circuit's outputs are affected by its sensitive noisy inputs. In conventional circuits, the impact of the inputs on reliability can be observed by the deterministic input patterns. However, in nanoscale circuits, the inputs behave probabilistically. The Bayesian networks technique is used to compute the reliability of a circuit in conjunction with the Monte Carlo simulations approach which is applied to model the probabilistic inputs and ultimately to determine sensitive inputs and worst-case input combinations.

Chapter 10, "Pin Count and Wire Length Optimization for Electrowettingon-Dielectric Chips: A Metaheuristics-Based Routing Algorithm," was written by Mohamed Ibrahim, Cherif Salama, M. Watheq El-Kharashi, and Ayman Wahba. Electrowetting-on-dielectric chips are gaining momentum as efficient alternatives to conventional biochemical laboratories due to their flexibility and low power consumption. In this chapter, we present a novel two-stage metaheuristic algorithm to optimize electrode interconnect routing for pin-constrained chips. The first stage models channel routing as a traveling salesman problem and solves it using the ant colony optimization algorithm. The second stage provides detailed wire routes over a grid model. The algorithm is benchmarked over a set of real-life chip specifications. On average, comparing our results to previous work, we obtain reductions of approximately 39 and 35 % on pin count and total wire length, respectively.

Chapter 11, "Quantum Dot Cellular Automata: A Promising Paradigm Beyond Moore," was written by Kunal Das, Arijit Dey, Dipannita Podder, Mallika De, and Debashis De. The quantum dot cellular automata (QCA) is a promising paradigm to overcome the ever-growing needs in size, power, and speed. In this chapter, we explore charge-confined low-power optimum logic circuit design to enhance the computing performance of a novel nanotechnology architecture, the quantum dot cellular automata. We investigate robust and reliable diverse logic circuit design, such as hybrid adders and other binary adder schemes, among them bi-quinary and Johnson–Mobius, in QCA. We also examine zero-garbage lossless online-testable adder design in QCA. Multivalued logic circuit design, with potential advantages such as greater data storage, fast arithmetic operation, and the ability to solve nonbinary problems, will be important in multivalued computing, especially in the ternary computing paradigm.

Chapter 12, "Smart Videocapsule for Early Diagnosis of Colorectal Cancer: Toward Embedded Image Analysis," was written by Quentin Angermann, Aymeric Histace, Olivier Romain, Xavier Dray, Andrea Pinna, and Bertrand Granado. Wireless capsule endoscopy (WCE) enables screening of the gastrointestinal tract by a swallowable imaging system. However, contemporary WCE systems have several limitations—battery, low processing capabilities, among others—which often result in low diagnostic yield. In this chapter, after a technical presentation of the components of a standard WCE, the authors discuss the related limitations and introduce a new concept of smart capsule with embedded image processing capabilities based on a boosting approach using textural features. We discuss the feasibility of the hardware integration of the detection–recognition method, also with respect to the most recent FPGA technologies. Finally, the editors wish to use this opportunity to thank all the authors for their valuable contributions, and the reviewers for their help for improving the quality of the contributions.

The editors are also thankful to Ronan Nugent, Springer Senior Editor, for his support, and for his continuous help.

Enjoy reading the book.

Sfax Puebla Paris December 2014 Mourad Fakhfakh Esteban Tlelo-Cuautle Patrick Siarry

## Contents

## Part I Analog and Mixed-Signal Applications

| 1 | <ul> <li>I-Flows: A Novel Approach to Computational Intelligence<br/>for Analog Circuit Design Automation Through Symbolic</li> <li>Data Mining and Knowledge-Intensive Reasoning</li> <li>Fanshu Jiao, Sergio Montano, Cristian Ferent and Alex Doboli</li> </ul> | 3   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Automatic Synthesis of Analog Integrated Circuits         Including Efficient Yield Optimization         Lucas C. Severo, Fabio N. Kepler and Alessandro G. Girardi                                                                                                | 29  |

| 3 | Application of Computational Intelligence Techniquesto Maximize Unpredictability in Multiscroll ChaoticOscillatorsOscillatorsVictor Hugo Carbajal-Gómez, Esteban Tlelo-Cuautleand Francisco V. Fernández                                                           | 59  |

| 4 | Optimization and Co-simulation of an ImplantableTelemetry System by Linking System Models to NonlinearCircuitsYao Li, Hao Zou, Yasser Moursy, Ramy Iskander,Robert Sobot and Marie-Minerve Louërat                                                                 | 83  |

| 5 | Framework for Formally Verifying Analog<br>and Mixed-Signal Designs<br>Mohamed H. Zaki, Osman Hasan, Sofiène Tahar<br>and Ghiath Al-Sammane                                                                                                                        | 115 |

| 6   | Automatic Layout Optimizations for Integrated MOSFET         Power Stages       David Guilherme, Jorge Guilherme and Nuno Horta                                                                                                                                 | 147 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7   | Optimizing Model Precision in High Temperatures<br>for Efficient Analog and Mixed-Signal Circuit Design<br>Using Modern Behavioral Modeling Technique:<br>An Industrial Case Study<br>Sahbi Baccar, Timothée Levi, Dominique Dallet<br>and François Barbara     | 177 |

| 8   | Nonlinearities Behavioral Modeling and Analysis<br>of Pipelined ADC Building Blocks                                                                                                                                                                             | 217 |

| Par | t II Radio-Frequency Design                                                                                                                                                                                                                                     |     |

| 9   | SMAS: A Generalized and Efficient Framework<br>for Computationally Expensive Electronic Design<br>Optimization Problems<br>Bo Liu, Francisco V. Fernández, Georges Gielen,<br>Ammar Karkar, Alex Yakovlev and Vic Grout                                         | 251 |

| 10  | Computational Intelligence Techniques for Determining<br>Optimal Performance Trade-Offs for RF Inductors<br>Elisenda Roca, Rafael Castro-López, Francisco V. Fernández,<br>Reinier González-Echevarría, Javier Sieiro, Neus Vidal<br>and José M. López-Villegas | 277 |

| 11  | <b>RF IC Performance Optimization by Synthesizing</b><br><b>Optimum Inductors</b>                                                                                                                                                                               | 297 |

| 12  | Optimization of RF On-Chip Inductors Using Genetic<br>Algorithms                                                                                                                                                                                                | 331 |

| 13  | Automated System-Level Design for Reliability:RF Front-End ApplicationPietro Maris Ferreira, Jack Ou, Christophe Gaquièreand Philippe Benabes                                                                                                                   | 363 |

| 14 | The Backtracking Search for the Optimal Design<br>of Low-Noise Amplifiers<br>Amel Garbaya, Mouna Kotti, Mourad Fakhfakh<br>and Patrick Siarry                                                           | 391 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 15 | <b>Design of Telecommunication Receivers</b><br><b>Using Computational Intelligence Techniques</b><br>Laura-Nicoleta Ivanciu and Gabriel Oltean                                                         | 413 |

| 16 | Enhancing Automation in RF Design Using Hardware<br>Abstraction<br>Sabeur Lafi, Ammar Kouki and Jean Belzile                                                                                            | 439 |

| 17 | Optimization Methodology Based on IC Parameter<br>for the Design of Radio-Frequency Circuits in CMOS<br>Technology<br>Abdellah Idrissi Ouali, Ahmed El Oualkadi, Mohamed Moussaoui<br>and Yassin Laaziz | 471 |

## Contributors

John Abela University of Malta, Msida, Malta

Kristian Zarb Adami University of Oxford, Oxford, UK

Ghiath Al-Sammane Concordia University, Montreal, Québec, Canada

Philippe Ayzac Thales Alenia Space, Toulouse, France

Sahbi Baccar IRSEEM Laboratory-ESIGELEC, Rouen, France

François Barbara Schlumberger Etudes et Productions, Schlumberger, France

Jean Belzile MEIE, Québec, Canada

**Philippe Benabes** Department of Electronic Systems, GeePs, UMR CNRS 8507, CentraleSupélec - Campus Gif, Gif-sur-Yvette, France

**Mladen Božanić** Department of Electrical and Electronic Engineering Science, Faculty of Engineering and the Built Environment, University of Johannesburg, Johannesburg, South Africa

Victor Hugo Carbajal-Gómez INAOE, Puebla, Mexico

Owen Casha University of Malta, Msida, Malta

**Rafael Castro-López** Instituto de Microelectrónica de Sevilla, IMSE-CNM, CSIC and Universidad de Sevilla, Seville, Spain

Dominique Dallet IMS-Laboratory, Bordeaux INP, Bordeaux, France

Alex Doboli Department of ECE, Stony Brook University, Stony Brook, NY, USA

Mourad Fakhfakh National School of Electronics and Telecommunications of Sfax, University of Sfax, Sfax, Tunisia

Eman Omar Farhat University of Malta, Msida, Malta

Cristian Ferent Department of ECE, Stony Brook University, Stony Brook, NY, USA

**Francisco V. Fernández** Instituto de Microelectrónica de Sevilla, IMSE-CNM, CSIC and Universidad de Sevilla, Seville, Spain

**Pietro Maris Ferreira** Department of Electronic Systems, GeePs, UMR CNRS 8507, CentraleSupélec - Campus Gif, Gif-sur-Yvette, France

Christophe Gaquière IEMN, UMR CNRS 8520, Department of DHS, Lille-1 University, Lille, France

**Amel Garbaya** National School of Electronics and Telecommunications of Sfax, University of Sfax, Sfax, Tunisia

Georges Gielen ESAT-MICAS, Katholieke Universiteit Leuven, Leuven, Belgium

Alessandro G. Girardi Alegrete Technology Campus, Federal University of Pampa, Alegrete-RS, Brazil

**Reinier González-Echevarría** Instituto de Microelectrónica de Sevilla, IMSE-CNM, CSIC and Universidad de Sevilla, Seville, Spain

Vic Grout Department of Computing, Glyndwr University, Wrexham, UK

David Guilherme Instituto de Telecomunicações, Lisbon, Portugal

Jorge Guilherme Instituto Politécnico de Tomar, Tomar, Portugal

**Osman Hasan** National University of Sciences and Technology, Islamabad, Pakistan

Nuno Horta Instituto de Telecomunicações, Lisbon, Portugal

Ramy Iskander Université Pierre et Marie Curie, Paris, France

Laura-Nicoleta Ivanciu Technical University of Cluj-Napoca, Cluj-Napoca, Romania

Fanshu Jiao Department of ECE, Stony Brook University, Stony Brook, NY, USA

Ammar Karkar School of Electrical Electronic and Computer Engineering, Newcastle University, Newcastle, UK

Fabio N. Kepler Alegrete Technology Campus, Federal University of Pampa, Alegrete, RS, Brazil

Mouna Kotti High School of Sciences and Technologies of Hammam Sousse, University of Sousse, Sousse, Tunisia

Ammar Kouki LACIME, ÉTS, Montréal, Canada

Yassin Laaziz LabTIC, National School of Applied Sciences of Tangier, Abdelmalek Essaadi University, ENSA Tanger, Tangier, Morocco

Sabeur Lafi LACIME, ÉTS, Montréal, Canada

Timothée Levi IMS-Laboratory, University of Bordeaux, Bordeaux, France

Yao Li Université Pierre et Marie Curie, Paris, France

Bo Liu Department of Computing, Glyndwr University, Wrexham, UK

Marie-Minerve Louërat Université Pierre et Marie Curie, Paris, France

José M. López-Villegas Departament d'Electrònica, Universitat de Barcelona, Barcelona, Spain

Sergio Montano Department of ECE, Stony Brook University, Stony Brook, NY, USA

Yasser Moursy Université Pierre et Marie Curie, Paris, France

Mohamed Moussaoui LabTIC, National School of Applied Sciences of Tangier, Abdelmalek Essaadi University, ENSA Tanger, Tangier, Morocco

Gabriel Oltean Technical University of Cluj-Napoca, Cluj-Napoca, Romania

Jack Ou Department of Electrical and Computer Engineering, California State University Northridge, Northridge, CA, USA

Abdellah Idrissi Ouali LabTIC, National School of Applied Sciences of Tangier, Abdelmalek Essaadi University, ENSA Tanger, Tangier, Morocco

Ahmed El Oualkadi LabTIC, National School of Applied Sciences of Tangier, Abdelmalek Essaadi University, ENSA Tanger, Tangier, Morocco

**Elisenda Roca** Instituto de Microelectrónica de Sevilla, IMSE-CNM, CSIC and Universidad de Sevilla, Seville, Spain

Lucas C. Severo Alegrete Technology Campus, Federal University of Pampa, Alegrete-RS, Brazil

**Patrick Siarry** Laboratoire LiSSi (EA 3956), Université Paris-Est Créteil, Créteil, France

Javier Sieiro Departament d'Electrònica, Universitat de Barcelona, Barcelona, Spain

Carlos Silva Portugal Telecom, Lisbon, Portugal

Saurabh Sinha Faculty of Engineering and the Built Environment, University of Johannesburg, Johannesburg, South Africa

**Robert Sobot** The University of Western Ontario, London, ON, Canada; ENSA/ETIS, University of Cergy-Pontoise, Cergy-Pontoise, France

Sofiène Tahar Concordia University, Montreal, QC, Canada

Esteban Tlelo-Cuautle INAOE, Puebla, Mexico

Neus Vidal Departament d'Electrònica, Universitat de Barcelona, Barcelona, Spain

Alex Yakovlev School of Electrical Electronic and Computer Engineering, Newcastle University, Newcastle, UK

Mohamed H. Zaki Concordia University, Montreal, QC, Canada

Hao Zou Université Pierre et Marie Curie, Paris, France

## Part I Analog and Mixed-Signal Applications

## Chapter 1 I-Flows: A Novel Approach to Computational Intelligence for Analog Circuit Design Automation Through Symbolic Data Mining and Knowledge-Intensive Reasoning

Fanshu Jiao, Sergio Montano, Cristian Ferent and Alex Doboli

**Abstract** This chapter presents an overview of the authors' ongoing work toward devising a new approach to analog circuit synthesis. The approach computationally implements some of the facets of knowledge-intensive reasoning that humans perform when tackling new design problems. This is achieved through a synthesis flow that mimics reasoning using a domain-specific knowledge structure with two components: an associative part and a causal reasoning part. The associative part groups known circuit schematics into abstractions based on the similarities and differences of their structural features. The causal reasoning component includes the starting ideas as well as the design sequences that create the existing circuits.

## 1.1 Introduction

Research in cognitive psychology suggests that human reasoning relies on organized knowledge structures to perform activities such as concept comparison and identification, concept learning, and problem solving through deduction and induction [1-4]. In particular, analog circuit design mainly depends on the designers' expertise and ability to create new designs by combining basic devices,

F. Jiao (🖂) · S. Montano · C. Ferent · A. Doboli

Department of ECE, Stony Brook University, Stony Brook, NY 11794-2350, USA e-mail: fanshu.jiao@stonybrook.edu

S. Montano e-mail: sergio.montano@stonybrook.edu

C. Ferent e-mail: cristian.ferent@stonybrook.edu

A. Doboli e-mail: alex.doboli@stonybrook.edu

© Springer International Publishing Switzerland 2015 M. Fakhfakh et al. (eds.), *Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design*, DOI 10.1007/978-3-319-19872-9\_1 sub-circuits, and ideas from similar solutions as the source for innovation. These activities are arguably hard to replicate through optimization-based methods, which have been traditionally popular in analog circuit EDA [5–9]. This limits the effectiveness of current EDA methods for activities such as circuit topology selection, topology refinement through feature reuse, design retargeting, topology design, and design verification.

Analog circuit design is knowledge intensive [10, 11]. Reasoning steps such as abstraction, instantiation, analogies (similarities), induction, concept combination, and constraint relaxation are utilized in complex design strategies (design plans) to tackle a new application. While this process might involve optimization and equation solving, it also includes pattern identification with respect to both the utilized design features and reasoning sequences. In fact, it has been suggested that the human brain is analogous to a sophisticated and effective pattern recognition machine [12]. This observation suggests that the circuit design process realizes an effective traversal of the design space by identifying, using, and reusing various design patterns (design steps). These patterns (or design features) include various topological circuit structures (e.g., differential input structures, cascode structures, buffers, and current sources) as well as specific constraints among circuit parameters (i.e., matched devices). Using certain features is justified by the functional and performance requirements of an application, and the performance trade-offs and bottlenecks of current solutions. Hence, the circuit design process can be seen as a collection of starting ideas (like ideas previously used in similar designs and new insight) followed by a sequence of design steps, in which every step adds a design feature that is causally justified by the need to address a given constraint of the design. We think that extending current analog circuit EDA methods by incorporating activities inspired by human reasoning can leverage the effectiveness and capabilities of automated tools by narrowing the gap between their solutions and human-devised circuits.

The analog circuit design space is complex, nonlinear, tightly coupled, and highly discontinuous. The traversal of the space to find new design features is challenging. As explained in the next section, diversification is a major activity in circuit design every time new structural (topological) features must be identified or invented as the current features cannot tackle well the existing performance bottlenecks. For example, addressing new performance challenges, such as ultrahigh frequencies, low power consumption, and high robustness to process parameter variations, required the creation of new structural features for more effective compensation and adaptation [13–16]. Novel features are a diversification from the current set of circuit features present in the knowledge domain. Effectively identifying the directions for diversification is difficult as traditional diversification approaches, such as focusing on the unexplored regions or introducing random changes into a solution, do not guarantee that an actual bottleneck is addressed. Moreover, such strategies might produce very complex circuit structures even though, often, there is a simpler solution.

This chapter presents an overview of our recent work toward devising a new approach to analog circuit EDA by computationally implementing some of the

facets of the knowledge-intensive reasoning tasks that humans perform when tackling new problems [17–21]. This is achieved through a synthesis mechanism that mimics reasoning on a domain-specific knowledge structure. The knowledge structure has two components: an associative part and a causal reasoning component. The associative part [17, 19] groups the known circuit schematics into abstractions based on the similarities and differences of their structural features. The associative part also characterizes the performance trade-offs (e.g., gain-bandwidth-noise) and bottlenecks of every circuit instance and abstraction [18] in the associative part. Each abstraction is a summary of the common symbolic expressions that describe the behavior of the related instances. Abstractions support a quick traversal of the solution space during synthesis, whenever a bottleneck must be addressed (e.g., if the abstraction does not include the symbolic expression of the bottleneck, then it includes an alternative topology that does not have the bottleneck).

The reasoning procedure for synthesis is based on operators such as abstractioninstantiation, induction, and concept combination [22, 23]. In addition, the synthesis flow reuses design sequences that have been previously used to solve similar design applications. Such sequences together with the starting design ideas are stored by the causal reasoning component of the knowledge structure. The starting ideas constitute the spark that initiated a design (or the aha moment [3]). A detailed presentation of the algorithms that mine the starting ideas and design sequence of an existing circuit is offered in [21]. This chapter offers a comprehensive yet intuitive presentation of the synthesis routines and the related knowledge structure. In addition, the experimental section gives detailed insight about the automated mining of the starting ideas and design sequences for four high-performance analog circuits.

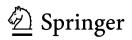

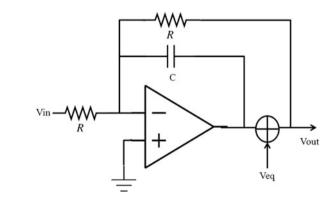

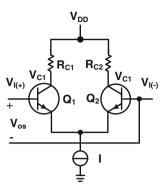

Figure 1.1 offers an intuitive description of the synthesis flow. It starts by identifying the initial features of the circuit, e.g., a circuit developed for a similar application. Circuit<sub>2</sub> is such a circuit in the figure. As the circuit includes a performance bottleneck (i.e., gain–noise) that prevents it from meeting the requirements, the synthesis approach uses the abstraction operator to move to node Abstraction, which collectively describes Circuit<sub>1</sub>, Circuit<sub>2</sub>, and Circuit<sub>3</sub>. The common features of an abstraction are denoted as set *I* (invariant) and the distinguishing features as set *U* (uniqueness). Then, the features of the abstraction are combined with some features of Circuit<sub>4</sub> (e.g., its adaptation scheme) to produce Circuit<sub>5</sub>, the final solution. The associative part of the knowledge structure includes the circuit instances and the abstractions. The causal reasoning part presents the reasoning steps (like abstraction followed by concept combination) that produced a new solution.

We think that the presented approach represents a new perspective on synthesis of analog circuits to extend the capabilities of current optimization- and solving-based techniques. Also, the approach is not similar to the older expert system-based synthesis techniques as it is not limited to a static set of built-in if-then rules. It automatically mines new design knowledge, such as in our ongoing work to mine knowledge in real time from electronic documents in databases, such as IEEE Xplore. While the overall synthesis flow is currently under development, encouraging progress has been made on devising the associative component and the

Fig. 1.1 Synthesis flow based on knowledge-intensive reasoning

causal reasoning part of the knowledge structure, including the examples discussed in this chapter. Finally, we think that this approach fits more naturally the way analog designers reason, hence creating a still very limited yet intriguing path toward computationally mimicking some facets of human creativity, a well-known challenge in computing.

The chapter has the following structure. Section 1.2 discusses the importance of diversification in analog circuit design and the challenges posed by two different types of diversification. Section 1.3 presents the reasoning-based synthesis method and the associative and causal reasoning components of the knowledge structure. References to the detailed presentation of the algorithms are also indicated. Section 1.4 presents new experimental results on mining the initial ideas and design sequences for four state-of-the-art circuits. Finally, conclusions end the chapter.

## **1.2 Motivation: The Importance of Effective** Diversification

Analog circuit design is knowledge intensive. It is well accepted that the expertise and experience of a designer are critical in deciding the quality of the final solution (e.g., its performance) [10, 11]. The solution space of a circuit design problem is complex, nonlinear, tightly coupled, and highly discontinuous. For example, a circuit design includes a large number of variables, such as the transconductances and capacitances of its devices. The variables are linked through complicated, nonlinear equations that express the DC, AC, and transient behavior of the circuit [8, 18, 24]. Moreover, the variables are tightly coupled with each other through symbolic (mathematical) expressions that describe a circuit's behavior and performance. Finally, strong discontinuities characterize the solution space as the transitions from a given circuit schematics (topology) to an incremental extension of it can introduce significant changes to the symbolic expressions of the circuit behavior and performance. This section explains that traditional optimization techniques, such as optimization-based methods, often experience difficulties in tackling the complex analog circuit design solution space. Instead, circuit designers use knowledge-intensive reasoning to find effective design plans and strategies to address the above challenges.

We classify the nature of divergence specific to analog circuit design into two types:

- *Closed-ended (or enumerable) diversification*: This diversification type corresponds to situations in which the enumeration of all diversification cases is possible, even though the number of resulting cases can be very large. Hence, the set of diversification situations is enumerable. For example, the solution space for optimizing the parameter values of a circuit includes many local optima. Each parameter sub-range that corresponds to a local optimum defines an area that is divergent (distinct) from another local optimum. The set of possible parameter sub-ranges is enumerable starting from the possible device sizes for a given fabrication process.

- Open-ended (or non-enumerable) diversification: This diversification type presents situations in which the diversification cases can be enumerated only with respect to a given set of building blocks and block connection rules. However, the resulting cases do not necessarily express all possible diversification situations as adding new building blocks and/or rules produces new diversification cases. For example, the solution space for the possible circuit topologies can be described using building blocks such as MOSFETs, resistors, and capacitors, as well as rules to connect the building blocks, i.e., series, parallel, and star. Note, however, that new diversifying cases can result by adding new building blocks, e.g., new devices. The resulting diversifications are open-ended as an unbounded (non-enumerable) number of new cases can be created through continuously connecting the building blocks into structures of growing complexity.

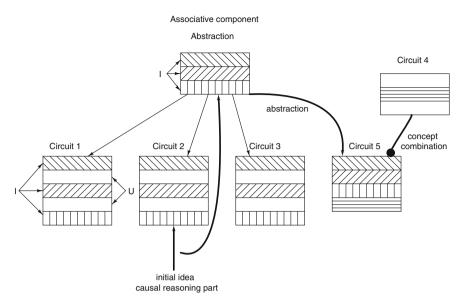

In our previous work, we studied optimization algorithms tackling closed-ended diversification [9]. The studied problem was to search for the circuit parameters that optimize the performance of a given analog system, e.g., high-frequency continuous-time filters or high-resolution  $\Delta\Sigma$  analog-to-digital converters (ADCs). As shown in Fig. 1.2, traditional optimization algorithms that exploit some form of gradient descendant methods, such as simulated annealing, have difficulties in finding good-quality parameter values mainly due to the hardness to systematically visit the divergent regions of a solution space. Diversification strategies, such as randomly accepting worse solutions at higher temperatures (in simulated annealing) or forcing the algorithm toward previously unexplored regions (in tabu

Fig. 1.2 Synthesis convergence with and without knowledge about variable domains [9]

search), did not significantly improve solution quality. This is mainly because interesting diversifying regions have characteristics that are hard to predict from those of the current regions; therefore, it is difficult to identify (compute) the search direction along which such diversifying regions are placed. The history of previously found good-quality regions might offer little insight about future good-quality regions unless insight similar to designer reasoning is mined from the former. However, knowledge about the parameter ranges that are likely to produce high-quality solutions results in a significant improvement of the cost function values as shown in Fig. 1.2.

This conceptual difficulty has been addressed by the proposed algorithm [9] by using three different diversification-related steps: (i) variable domain pruning, (ii) wave front expansion to cover all search directions, and (iii) identifying the parameter correlation patterns specific to the promising search directions. Variable domain pruning eliminates the parameter sub-domains for which the resulting values of the system behavior and performance vary in large ranges. Even though such parameter sub-domains can still produce constraint-satisfying solutions, finding the performance-optimizing parameter values is harder than for the parameter sub-domains for which the resulting behavior and performance presents a lesser variation. Interval arithmetic was used for parameter domain pruning [9]. The second step, wave front expansion, is called every time a convex subspace has been fully explored (using a descending gradient-based search) and diversification is needed. Wave front expansion is initially along all directions for changing the parameter values, but as the number of possible directions grows quickly, it reduces the search complexity by sampling the alternatives using orthogonal arrays. This way of sampling encourages that each parameter sub-range combination has equal chance of being searched. Otherwise, there is no guarantee that diversification

systematically explores all alternatives. Finally, the third step, identifying correlation patterns, further reduces the number of diversifying alternatives based on the observation that high-quality design solutions implement certain required constraints among the parameter values, e.g.,  $p_1 \gg p_2$  or  $p_3 \approx p_4$ . Even though such parameter correlations are probably unavailable at the start of an optimization algorithm (unless designer expertise is employed to find them), correlations can be automatically detected (learned) during wave front expansion. A search direction that embeds a useful parameter correlation produces a rapid drop of the cost function value, while less useful search directions are characterized by either oscillating or plateaulike cost function values [9]. The latter directions are quickly found and dropped during wave front expansion. Experiments for filter and  $\Delta\Sigma$ ADC synthesis showed that using the three steps for closed-ended diversification finds more constraint-satisfying designs as well as designs of better performance, i.e., the method found between 1.8 and 2.6 times more constraint-satisfying solutions than other state-of-the-art tools [9].

Open-ended (or non-enumerable) diversification represents situations in which the diversification cases are enumerated with respect to a given set of building blocks and connection rules, even though new building blocks and/or rules can be added to the set. Traditionally, such diversification situations have been tackled through two methods: template-based search and genetic algorithms. In template-based search [25–27], a structural template describes the characterizing features of the possible circuit topologies, e.g., the main signal flows through the contemplated circuit topologies. The diversification routine uses the set of building blocks and connection rules to generate different topologies but which all realize the same signal flow as the given template. Genetic algorithms (GA) [28-30] achieve diversification through the well-known operators' selection, mutation, and combination (and their extensions), which are sometimes extended with analog design-related steps or constraints. GAs can construct, potentially, an unlimited set of diversifying solutions. However, the arguably unsystematic traversal of the solution space does not guarantee that optimal solutions are found for a problem. Also, the search time might become very large for complex search problems. Moreover, the repeated applying of the three operators can result in very complex structures, which are less common to the topologies that a designer devises through knowledge-intensive reasoning [31]. As explained in [31], traditional topology synthesis, i.e., using GAs, might experience difficulties in producing circuits with novel (hence diversifying) yet useful structural features. The synthesized circuit topologies include unique features, but such features are rarely used by designers.

This chapter proposes a reasoning-based approach for tackling diversification during circuit design. The approach attempts to mimic at a very basic level the knowledge-intensive reasoning process conducted by a designer. The process starts with a set of initial design features which are the starting points (e.g., the initial ideas) for solving the problem. The performance bottlenecks of the initial features are found, i.e., the design features that prevent the design from meeting the needed performance. Then, a sequence of design steps attempts to remove the bottlenecks, such that every step is justified either by addressing an existing performance limitation or by relaxing constraints, so that future performance-enhancing design steps are possible (steps which are impossible without constraint relaxation). The reasoning-based approach includes two main components, which are discussed in the next section: (i) an *associative component* that presents the domain knowledge specific to analog circuit design and (ii) a *reasoning component* that expresses the various reasoning sequences that were used in creating a circuit solution. Reasoning sequences are reused during the devising of new circuit solutions.

## 1.3 Knowledge Structures

The proposed knowledge-intensive reasoning method for circuit synthesis is shown in Fig. 1.3. More details about the method can be also found in [32, 17]. It incorporates design knowledge-intensive diversification using the associative and reasoning components. As detailed next, the associative part includes *instances* (e.g., actual circuit designs) and *abstract concepts* that summarize the features of a set of instances. The first step of the methodology selects the initial features of the design solution by relating every node  $C_x$  (instance or abstract concept) of the associative part *St* to the desired design requirements and then finding the bottlenecks that prevent it from achieving the needed performance. Another way of

```

for each node Cx in structure St {

find bottlenecks and relate them to

the topological elements of the circuits

(i.e. variables, expressions, constraints);

C = select node in St;

while d(C, <f, p>) > acceptable {

if (bottleneck is due to unique features of C) {

find bottom-up in St first node Cn

but without expressions that cause the bottleneck;

if (not successful)

C = concept-combination (C, St, bottleneck);

if (not successful) {

add to bottleneck the features that condition

the expressions of the bottleneck;

find bottom-up in St first node Cn

but without expressions that cause the bottleneck;

else if (successful) {

find new bottlenecks and relate them to

the topological elements of the circuits

(i.e. variables, expressions, constraints);

}

}

```

Fig. 1.3 Conceptual description of knowledge-intensive reasoning method [32]

selecting the initial solution features is by selecting a previously solved problem that is most similar to the current requirements and then using its initial features as the starting point of the new design. As explained in the second part of this section, this requires reusing information stored by the reasoning component. Bottlenecks are related to the actual structural elements of a circuit, i.e., its design variables (like device sizes), the symbolic expressions describing the circuit behavior, and the constraints imposed for correct operation. A technique for finding circuit bottlenecks is presented in [18].

Next, the method selects node C, which is the most attractive candidate in implementing the new circuit design. The node describes the initial features used to develop the solution. The iterative process continues as long as the derived solution C does not meet the desired functional and performance requirements expressed as pair  $\langle f, p \rangle$ . Hence, distance *d* between the behavior of solution C and pair  $\langle f, p \rangle$  exceeds an acceptable value. Each step of the method attempts three subsequent reasoning steps:

- First, *abstraction* searches bottom up the associative part *St* to find an abstract concept corresponding to node C, so that the abstract concept does not include the performance-limiting bottleneck of node C. If the search is successful, it indicates that the bottleneck is specific only to node C but not the abstract concept to which node C corresponds to and for which node C is an implementation. Hence, the abstract concept can include alternative instances to node C (e.g., another circuit topology) without the bottleneck. This instance becomes the current design that is further extended into the final solution.

- Second, if abstraction was unsuccessful, *concept combination* attempts to remove the bottleneck by combining the features of node C with the features of a concept that does not include the bottleneck. For example, the combined features might include various adaptation or compensation mechanisms that are used to improve performances such as bandwidth and linearity.

- Third, if the previous two steps could not find a solution, then *constraint relaxation* tries to lighten up the constraints that guarantee the correct operation of the circuit, i.e., the constraints that set the right device operation regions or the constraints on the device parameter values. This step might then enable concept combinations that otherwise would not be feasible.

The detailed analysis used by the three steps utilizes an automated mechanism for systematically producing comparison data between two analog circuits [18]. The similar and distinguishing performance characteristics of circuits with respect to gain, bandwidth, common-mode gain, noise, and sensitivity are captured. The technique utilizes matching of both topologies and symbolic expressions of the compared circuits to find the nodes with similar behavior. The impact on performance of the unmatched nodes is used to express the differentiating characteristics of the circuits. The produced comparison data are important for getting insight into unique benefits and limitations of a circuit, selecting fitting circuit topologies for system design, and optimizing circuit topologies. The next two subsections present the two parts used to support knowledge-intensive reasoning by the proposed method, the associative component and the reasoning component.

### 1.3.1 Associative Component

The associative component clusters the existing circuit instances into higher-level descriptions, called abstractions [17, 19]. The clustering is based on the common features (called attributes) of the instances forming a concept as well as the features that offer unique expression of the specific attributes of each instance. These features form a set that is called set I (invariants) [17]. In addition, a second set, set U (uniqueness), presents the features that are unique to the abstraction as compared to other abstractions. Finally, set E (enabling) introduces all conditions and constraints that must be met during the operation of the design. All features are symbolic expressions over variables.

This description is important because the symbolic expressions in set I indicate the trade-offs and bottlenecks specific to an abstraction. Any instance of the abstraction will include them. Hence, the abstraction step of the reasoning method in Fig. 1.3 checks the existence or not of a bottleneck by analyzing set I of the abstraction. Moreover, set U indicates whether a bottleneck is unique for an abstraction, and therefore, diversifying toward other abstractions might result in removing the bottleneck. Finally, set E is used by the constraint relaxation step of the method to indicate the constraints that are candidates for removal.

*Example* Let us assume three design instances characterized by the following set of features:  $D_1 = \{x_o = x_1 * x_2; x_1 = 3 * x_i; x_2 = x_1 + x_i;\}, D_2 = \{x_o = x_1 * x_2; x_1 = 8 * x_i; x_2 = x_1 + x_i;\}, and <math>D_3 = \{x_o = x_1 * x_2; x_1 = 6 * x_i; x_2 = x_1 + x_i;\}.$  (For brevity, we did not use the symbolic expressions describing concrete circuit topologies, but the analogy holds.) Each expression is a feature of the design, e.g., it describes the behavior of the circuit. Variables  $x_i$  are the design variables, where  $x_i$  is the input and  $x_o$  is the output. The abstraction of the three instances is expressed by the following features  $D_a = \{x_o = x_1 * x_2; x_1 = A * x_i; x_2 = x_1 + x_i;\}$ . Set  $I = \{x_o = x_1 * x_2; x_1 = A * x_i; x_2 = x_1 + x_i;\}$ . Note that feature  $x_1 = A * x_i$ , with A being a symbolic constant, represents the specific features  $x_1$  of each design  $D_i$ . Finally, compared to another abstraction,  $D_b = \{x_o = x_1 * x_2; x_1 = B * x_i; x_2 = x_1 - x_i;\}$ , the set U of  $D_a$  is feature  $x_2 = x_1 + x_i$  as this feature does not occur for  $D_b$ . Set E might include constraints on the variables, e.g.,  $x_i \in (-1.0, 1.0)$ .

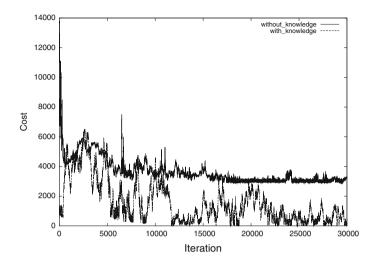

The description of similar instances as abstractions, of similar abstraction as higher-level abstractions, and so on, produces a hierarchical, graphlike associative component, as shown in Fig. 1.4. Arrows indicate instances of an abstraction, and arrows with bubbled heads represent combined features. Note that the representation is a graph (not a tree) as instances can belong to multiple abstractions.

The number of levels in the hierarchy depends on the sampling of the features of the available designs, e.g., the alternative symbolic expressions of similar features, the way in which one feature is combined with other features, and the function and purpose (goal) of a design.

**Example** Figure 1.4b presents the associative component built for the five circuits shown in Fig. 1.4a. Each circuit is described by its signal flow graph, in which the nodes are the circuit nodes, arcs indicate the coupling among nodes, and poles are attached to every node. Every arc is labeled by the symbolic expression of the coupling among nodes. The symbolic expressions of the poles and couplings are computed using the algorithm presented in [24, 33]. For brevity, the symbolic

Fig. 1.4 Associative component of the knowledge structure [19]

expressions were not shown in the figure. Nodes  $C_6-C_{11}$  in Fig. 1.4b are the abstractions computed for the five circuits. The invariant set (set *I*) of a circuit includes all the symbolic expressions of the circuit poles and couplings through the arcs. The unique features of the instances and abstractions (set *U*) correspond to the symbolic expressions of the node poles and arcs shown in bold. They represent the distinguishing elements of the instances or abstractions as compared to the other alternatives that have the same parent in the graph.

In addition to circuit comparison, the proposed concept structure includes three other symbolic operators: circuit concept instantiation–abstraction, circuit concept combination, and design feature induction [22, 23]. The operators algorithmically implement the steps of the method in Fig. 1.3. The first operator constructs the associative component for a set of known solutions, while the later two provide the mechanisms to extend the knowledge representation to find novel solutions. Instantiation–abstraction organizes the features at various levels by replacing signals or blocks in a design through clusters of signals or blocks with the same behavior [22]. The concept combination operator produces a new circuit concept for an application by mixing the features of two existing circuits, so that resulting performance is improved [20]. The generic concept induction operator uses the existing information on design feature variety from all concepts in the structure to create novel concepts that have not yet been explored, such as different connection patterns among signal nodes that can relax trade-offs [22, 23].

Our ongoing work attempts to update the associative component, so that it gets updated in real time every time a new circuit is published in the literature. A crawler continuously scans databases for scientific literature on analog circuit design, e.g., journals and conference proceedings published by IEEE Xplore, and downloads the papers presenting new circuits. The schematics of the circuit is automatically identified in the pdf file and then converted into its Spice description. After constructing its macromodel (based on the Spice netlist) as presented in [24], the circuit is then added to the associative component by using the clustering method proposed in [19] as well as the symbolic circuit comparison algorithm in [18].

### 1.3.2 Causal Reasoning Component

Each abstraction of the associative component is a *branching point* (BP) in a reasoning flow as the designer could have possibly adopted a different alternative to realize a solution. Obviously, a different alternative might produce different outcomes and performance. Each BP is characterized by a number of variables (e.g., the feature variables in sets I and U of the corresponding abstraction), the coupling between variables (e.g., the number of shared variables between the features), and performance values that can be achieved. The causal component of the knowledge structure indicates the reasons that justified the designer's selection of a particular alternative [21]. Reasons include improvement of the performance capabilities of a

design (e.g., by changing its bottlenecks), modifying the functionality (i.e., the performed processing of the input signals), and relaxing the design constraints of set E (enabling conditions).

As already explained, the knowledge-intensive reasoning method in Fig. 1.3 builds new design solutions starting from initial design features (e.g., initial ideas) and then employing a design sequence, which are a set of reasoning steps that ultimately produce a circuit design. Each step in a design sequence must be *justified*, meaning that it implements a structural feature of an abstraction or it enhances the performance of another circuit design. Design sequences are design plans (or reasoning strategies) that are reused by the method in Fig. 1.3 during circuit synthesis.

The causal component includes the initial design features and design sequences specific to the circuit instances that are stored by the associative component. A detailed presentation of the algorithms that mine initial ideas and design sequences for a given circuit is offered in [21]. We offer next a summary of the two algorithms. The experimental section illustrates the two mining algorithms for several modern, high-performance analog circuits.

The algorithm for mining the initial design features of an analog circuit attempts to identify what were reasonably the starting ideas (of the authors) when devising the circuit. While the complete, iterative process for devising a new circuit might be impossible to infer, we think that at least the ideas (of the last iteration) that lead to final solution can be automatically mined. The algorithm first identifies all the structural features of a given circuit by matching its device connections to the device connections present in the associative component. This set is denoted as set  $\Sigma$  (also called complete set). Next, the algorithm implements the observation that all features in set  $\Sigma$  should be justified by a design sequence starting from the set of initial features. Hence, the set of initial features are those that allow the finding of a design sequence of justified steps (hence, steps either which instantiate more abstract features or which improve the performance of the circuit). Moreover, the set of initial ideas includes (i) features that were previously used by the same authors in devising new circuits (called set  $\Lambda$ ), (ii) features that appear in the cited papers (called set  $\Gamma$ ), and (iii) features that indicate new insight by the authors. The features of the first two categories can be found by analyzing previously published designs as well as any cited circuits. They represent the tentative set of initial features. Then, the algorithm attempts to find whether all the features of the complete set  $\Sigma$  can be justified starting from the current set of initial features. If this is successful, then the current set is also the final set of initial features. However, if there are any unjustified features, then the algorithm finds the minimum subset among the unjustified features which then justify all the remaining structural features. The minimum set is added to sets  $\Lambda$  and  $\Gamma$  to represent the complete set of initial features.

The algorithm for constructing a design sequence takes as input the current set of initial features and then explores the maximal set of features in the complete set  $\Sigma$  that can be justified based on the initial features. It iteratively finds the features that

can be immediately justified from the initial set, and then, it finds the features that can be justified based on the features found by the previous step and so on until no more features in set  $\Sigma$  can be identified.

## 1.4 Experiments

This section presents four case studies to illustrate the mining of the initial features (ideas) and design sequences that were used in creating a circuit. The procedures use causal reasoning, e.g., understanding the cause—effect relations that produce the performance bottlenecks of a circuit topology and how the design steps of the sequence relax the performance trade-offs.

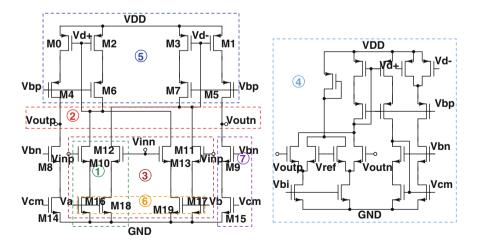

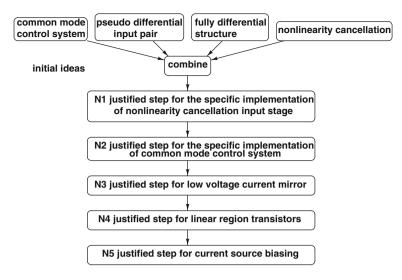

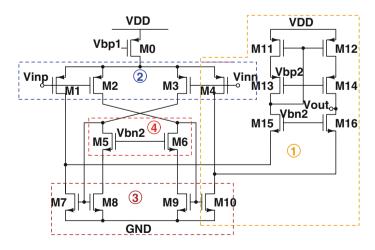

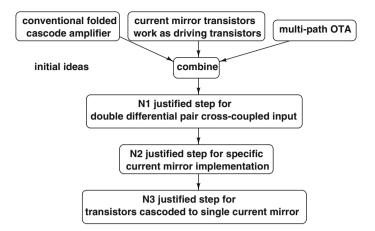

## 1.4.1 Circuit 1