# Cyrille Artho Peter Csaba Ölveczky (Eds.)

Communications in Computer and Information Science

476

# Formal Techniques for Safety-Critical Systems

Third International Workshop, FTSCS 2014 Luxembourg, November 6–7, 2014 Revised Selected Papers

# Communications in Computer and Information Science 476

#### Editorial Board

Simone Diniz Junqueira Barbosa Pontifical Catholic University of Rio de Janeiro (PUC-Rio), Rio de Janeiro, Brazil Phoebe Chen La Trobe University, Melbourne, Australia Alfredo Cuzzocrea ICAR-CNR and University of Calabria, Cosenza, Italy Xiaoyong Du Renmin University of China, Beijing, China Joaquim Filipe Polytechnic Institute of Setúbal, Setúbal, Portugal Orhun Kara TÜBİTAK BİLGEM and Middle East Technical University, Ankara, Turkey Igor Kotenko St. Petersburg Institute for Informatics and Automation of the Russian Academy of Sciences, St. Petersburg, Russia Krishna M. Sivalingam Indian Institute of Technology Madras, Chennai, India Dominik Ślęzak University of Warsaw and Infobright, Warsaw, Poland Takashi Washio Osaka University, Osaka, Japan Xiaokang Yang Shanghai Jiao Tong University, Shangai, China

More information about this series at http://www.springer.com/series/7899

# Formal Techniques for Safety-Critical Systems

Third International Workshop, FTSCS 2014 Luxembourg, November 6–7, 2014 Revised Selected Papers

*Editors* Cyrille Artho National Institute of Advanced Industrial Science and Technology Amagasaki Japan

Peter Csaba Ölveczky University of Oslo Oslo Norway

ISSN 1865-0929

ISSN 1865-0937 (electronic)

Communications in Computer and Information Science

ISBN 978-3-319-17580-5

ISBN 978-3-319-17580-5

ISBN 978-3-319-17581-2 (eBook)

DOI 10.1007/978-3-319-17581-2

Library of Congress Control Number: 2015937953

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

### Preface

This volume contains the proceedings of the *Third International Workshop on Formal Techniques for Safety-Critical Systems* (FTSCS 2014), held in Luxembourg on November 6–7, 2014, as a satellite event of the ICFEM conference.

The aim of FTSCS is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safetycritical computer systems. FTSCS strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics of the workshop include, but are not limited to:

- case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, medical, and other kinds of safety-critical and QoS-critical systems;

- methods, techniques, and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems;

- analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.);

- formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.; and

- code generation from validated models.

FTSCS 2014 received 40 regular paper submissions and two position/work-inprogress paper submissions. Each submission was reviewed by at least three reviewers; based on the reviews and extensive discussions, the program committee selected 14 of these regular papers and both position/work-in-progress papers for presentation at the workshop. This volume contains revised versions of those 14 regular papers, as well as invited papers by Klaus Havelund and Thomas Noll. As was the case for FTSCS 2012 and FTSCS 2013, a special issue of the *Science of Computer Programming* journal is devoted to extended versions of selected papers from FTSCS 2014.

Many colleagues and friends contributed to FTSCS 2014. We thank Klaus Havelund and Thomas Noll for accepting our invitations to give invited talks and the authors who submitted their work to FTSCS 2014 and who made this workshop an interesting event attracting more than 30 participants. We are particularly grateful to the members of the program committee, who all provided timely, insightful, and detailed reviews.

We also thank the editors of Springer's *Communications in Computer and Information Science* (CCIS) series for publishing the proceedings of FTSCS 2014, Bas van Vlijmen for accepting our proposal to devote a special issue of *Science of Computer Programming* to extended versions of selected papers from FTSCS 2014, Jun Pang and Magali Martin for their help with local arrangements, and Andrei Voronkov for the excellent EasyChair conference systems.

January 2015

Cyrille Artho Peter Csaba Ölveczky

# Organization

### Workshop Chair

Hitoshi Ohsaki

AIST, Japan

## **Program Committee**

| Erika Ábrahám                | RWTH Aachen University, Germany                |  |  |

|------------------------------|------------------------------------------------|--|--|

| Musab AlTurki                | King Fahd University of Petroleum and Minerals |  |  |

|                              | Saudi Arabia                                   |  |  |

| Toshiaki Aoki                | JAIST, Japan                                   |  |  |

| Farhad Arbab                 | Leiden University and CWI, The Netherlands     |  |  |

| Cyrille Artho (Chair)        | AIST, Japan                                    |  |  |

| Kyungmin Bae                 | Carnegie Mellon University, USA                |  |  |

| Saddek Bensalem              | Verimag, France                                |  |  |

| Armin Biere                  | Johannes Kepler University of Linz, Austria    |  |  |

| Ansgar Fehnker               | University of the South Pacific, Fiji          |  |  |

| Mamoun Filali                | IRIT, France                                   |  |  |

| Bernd Fischer                | Stellenbosch University, South Africa          |  |  |

| Klaus Havelund               | NASA JPL, USA                                  |  |  |

| Marieke Huisman              | University of Twente, The Netherlands          |  |  |

| Ralf Huuck                   | NICTA, Australia                               |  |  |

| Fuyuki Ishikawa              | National Institute of Informatics, Japan       |  |  |

| Takashi Kitamura             | AIST, Japan                                    |  |  |

| Alexander Knapp              | Augsburg University, Germany                   |  |  |

| Yang Liu                     | Nanyang Technological University, Singapore    |  |  |

| Robi Malik                   | University of Waikato, New Zealand             |  |  |

| Frédéric Mallet              | Université Nice Sophia Antipolis, France       |  |  |

| César Muñoz                  | NASA Langley, USA                              |  |  |

| Thomas Noll                  | RWTH Aachen University, Germany                |  |  |

| Peter Csaba Ölveczky (Chair) | University of Oslo, Norway                     |  |  |

| Charles Pecheur              | Université catholique de Louvain, Belgium      |  |  |

| Paul Pettersson              | Mälardalen University, Sweden                  |  |  |

| Camilo Rocha                 | Escuela Colombiana de Ingeniería, Colombia     |  |  |

| Ralf Sasse                   | ETH Zürich, Switzerland                        |  |  |

| Oleg Sokolsky                | University of Pennsylvania, USA                |  |  |

| Sofiène Tahar                | Concordia University, Canada                   |  |  |

| Carolyn Talcott              | SRI International, USA                         |  |  |

| Tatsuhiro Tsuchiya           | Osaka University, Japan                        |  |  |

| Chen-Wei Wang                | McMaster University, Canada                    |  |  |

|                              |                                                |  |  |

Mike Whalen Huibiao Zhu University of Minnesota, USA East China Normal University, China

#### **Additional Reviewers**

Dunchev, Cvetan Enoiu, Eduard Paul Fang, Huixing Gao, Sa Hatvani, Leo Huang, Yanhong Hung, Dang Van Jansen, Christina Jansen, Nils Johnsen, Andreas Kremer, Gereon Li, Qin Limbrée, Christophe Mentis, Anakreon Mu, Chunyan Siddique, Umair Soualhia, Mbarka Wu, Xi

# Contents

| Experience with Rule-Based Analysis of Spacecraft Logs                                                                                                                                                                                                 | 1   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Safety, Dependability and Performance Analysis of Aerospace Systems<br>Thomas Noll                                                                                                                                                                     | 17  |

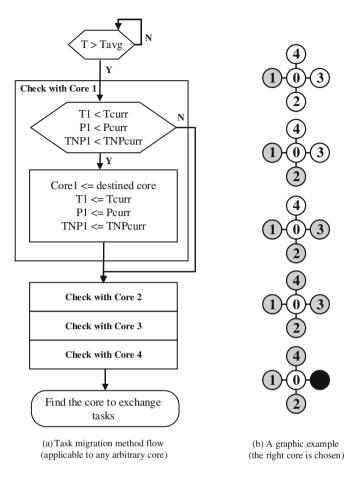

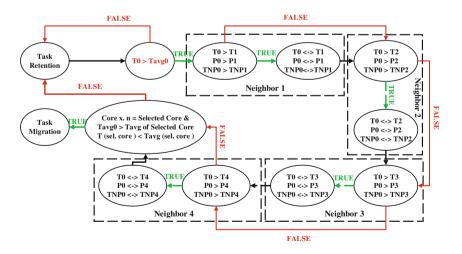

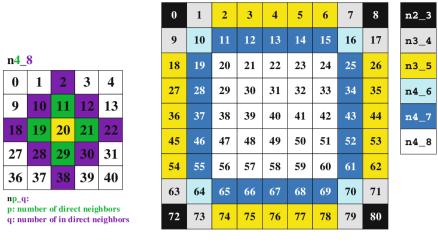

| Formal Verification of Distributed Task Migration for Thermal Management<br>in On-Chip Multi-core Systems Using nuXmv<br>Syed Ali Asadullah Bukhari, Faiq Khalid Lodhi, Osman Hasan,<br>Muhammad Shafique, and Jörg Henkel                             | 32  |

| Expression-Based Aliasing for OO–languages                                                                                                                                                                                                             | 47  |

| Checking Integral Real-Time Automata for Extended Linear<br>Duration Invariants<br><i>Changil Choe, Univan Ahn, and Song Han</i>                                                                                                                       | 62  |

| A Normalized Form for FIFO Protocols Traces, Application to the Replay<br>of Mode-based Protocols                                                                                                                                                      | 76  |

| Dynamic State Machines for Formalizing Railway Control<br>System Specifications<br>Roberto Nardone, Ugo Gentile, Adriano Peron, Massimo Benerecetti,<br>Valeria Vittorini, Stefano Marrone, Renato De Guglielmo,<br>Nicola Mazzocca, and Luigi Velardi | 93  |

| Checking the Conformance of a Promela Design to its Formal Specification<br>in Event-B<br><i>Dieu-Huong Vu, Yuki Chiba, Kenro Yatake, and Toshiaki Aoki</i>                                                                                            | 110 |

| A Formal Model of SysML Blocks Using CSP for Assured<br>Systems Engineering Jaco Jacobs and Andrew Simpson                                                                                                                                             | 127 |

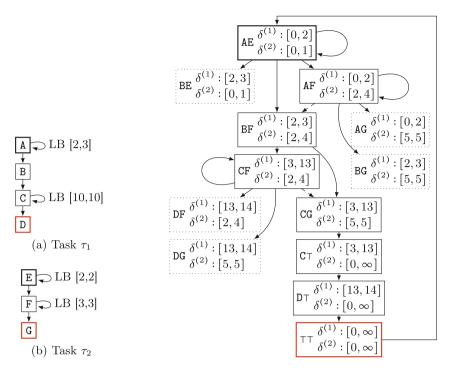

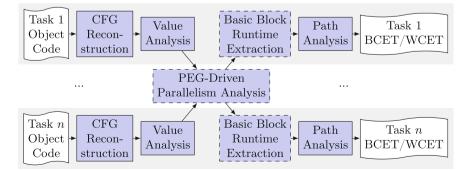

| Parallelism Analysis: Precise WCET Values for Complex<br>Multi-Core Systems<br><i>Timon Kelter and Peter Marwedel</i>                                                                                                                                  | 142 |

| Key-Secrecy of PACE with OTS/CafeOBJ                                                                                                                                                                                                                   | 159 |

#### X Contents

| Coalgebraic Semantic Model for the Clock Constraint<br>Specification Language<br><i>Frédéric Mallet and Grygoriy Zholtkevych</i>                                                              |     |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

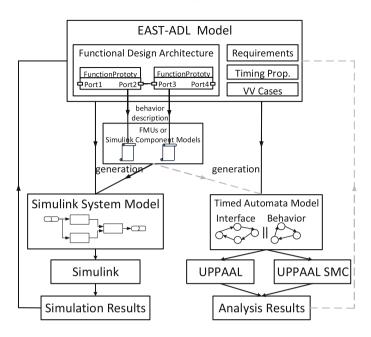

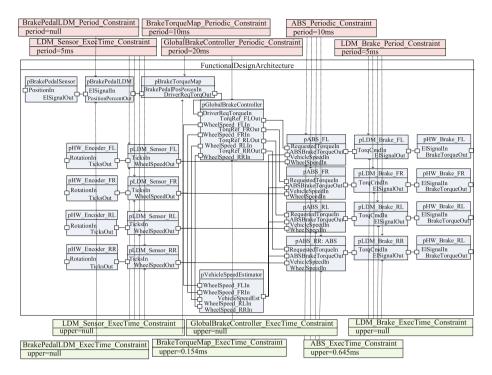

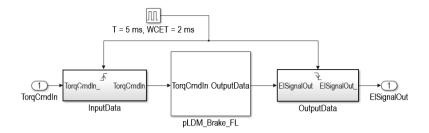

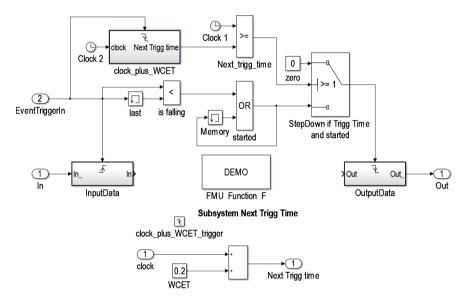

| Analyzing Industrial Architectural Models by Simulation<br>and Model-Checking<br>Raluca Marinescu, Henrik Kaijser, Marius Mikučionis,<br>Cristina Seceleanu, Henrik Lönn, and Alexandre David | 189 |  |  |

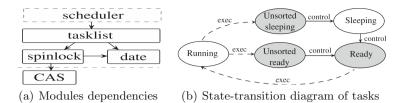

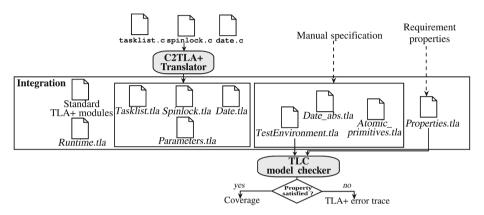

| Specifying and Verifying Concurrent C Programs with TLA+<br>Amira Methni, Matthieu Lemerre, Belgacem Ben Hedia,<br>Serge Haddad, and Kamel Barkaoui                                           | 206 |  |  |

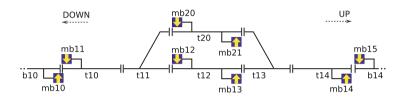

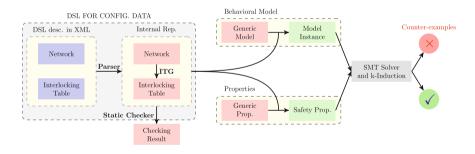

| Formal Modeling and Verification of Interlocking Systems Featuring<br>Sequential Release<br>Linh H. Vu, Anne E. Haxthausen, and Jan Peleska                                                   | 223 |  |  |

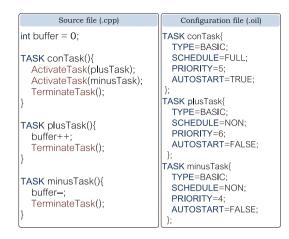

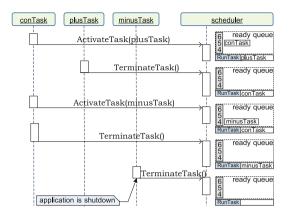

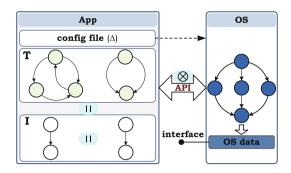

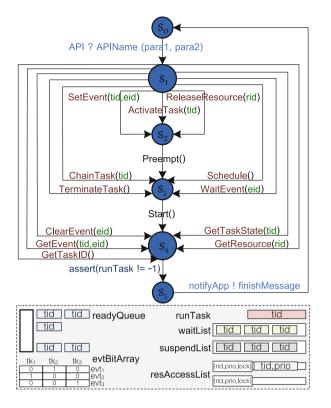

| A Spin-Based Approach for Checking OSEK/VDX Applications<br>Haitao Zhang, Toshiaki Aoki, and Yuki Chiba                                                                                       | 239 |  |  |

| Author Index                                                                                                                                                                                  | 257 |  |  |

# Experience with Rule-Based Analysis of Spacecraft Logs

Klaus Havelund $^{(\boxtimes)}$  and Rajeev Joshi

Jet Propulsion Laboratory, California Institute of Technology, Pasadena, USA havelund@gmail.com

Abstract. One of the main challenges facing the software development as well as the hardware communities is that of demonstrating the correctness of built artifacts with respect to separately stated requirements. Runtime verification is a partial solution to this problem, consisting of checking actual execution traces against formalized requirements. A related activity is that of humans attempting to understand (or *comprehend*) what the system does when it executes, for validation purposes, or for simply operating the system optimally. For example, a key challenge in operating remote spacecraft is that ground operators must rely on the limited visibility available through spacecraft telemetry in order to assess spacecraft health and operational status. In this paper we illustrate the use of the rule-based runtime verification system LogFire for supporting such log comprehension. Specifically, LogFire is used for generating abstract events from the concrete events in logs, followed by a visualization of these abstract events using the D3 visualization framework.

#### 1 Introduction

#### 1.1 Motivation

Demonstrating the correctness of a software or hardware artifact is a challenging problem. In the ideal case we want to prove the artifact correct for all possible input. Unfortunately, full verification is still cost-prohibitive for complex systems (especially those with tight deadlines), so practitioners typically use less formal, but cheaper, alternatives to build confidence in their systems. One such alternative is runtime verification, which checks a particular execution against a formal specification, which in this case becomes the test oracle. However, runtime verification systems can be used during deployment as well, to monitor the actual execution of the system in the field. Such monitoring can happen *online*, as the system executes, or *offline* by analyzing log files generated by the running system. Violations of the formal specification can be flagged by the runtime verification system, either leading to automated behavior modification in the case

The work described in this publication was carried out at Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

<sup>©</sup> Springer International Publishing Switzerland 2015

C. Artho and P.C. Ölveczky (Eds.): FTSCS 2014, CCIS 476, pp. 1–16, 2015. DOI: 10.1007/978-3-319-17581-2\_1

of online monitoring, or human driven systems modification in the case of offline monitoring (as examples).

In this paper we suggest yet a slightly different use of a runtime verification system: namely that of system comprehension. One of the key challenges in operating remote spacecraft is that the only knowledge ground operators have of the spacecraft behavior is the telemetry sent down to earth. Such telemetry typically consists of logs of system events and sensor measurements (such as battery voltage or probe temperature). A log may be viewed as a sequence of time-stamped records with named fields. Current practice at NASA's Jet Propulsion Laboratory (JPL) is to develop ad-hoc tools using various scripting languages, resulting in a growing collection of scripts that are hard to maintain and modify, which becomes a concern for long-running missions that last many years. A more desirable solution is a specification-based approach where *comprehension rules* are formulated in a human readable DSL (Domain Specific Language). In this paper, we present such an approach applied to the telemetry received from the Curiosity rover currently on Mars, and part of the MSL (Mars Science Laboratory) mission [31].

#### 1.2 Contribution

More concretely, we illustrate the application of the LOGFIRE runtime verification system [25] and the D3 visualization system [14] to support *human comprehension* of logs sent down to earth from Curiosity. Although illustrated on such logs, the approach is fully general. LOGFIRE is a rule-based monitoring framework, a concept extensively studied within the artificial intelligence community. It is implemented in the SCALA programming language as an internal DSL (essentially an API), and its core algorithm is a modification of the RETE algorithm [19], to support event processing as well as fast indexing, as described in [25]. RETE is one of the original algorithms for rule-based systems, optimizing rule-evaluation, and known for its complexity.

Rules have the form:  $condition_1, \ldots, condition_n \Rightarrow action$ . The state of a rule-system can abstractly be considered as consisting of a set of *facts*, referred to as the *fact memory*, where a fact is a mapping from field names to values. A condition in a rule's left-hand side can check for the presence or absence of a particular fact. A left-hand side matching against the fact memory usually requires unification of variables occurring in conditions. In the case that all conditions on a rule's left-hand side match (become true), the right-hand side action is executed, which can be any SCALA code, including adding and deleting facts, or generating error messages. The DSL allows domain specific constructs to be mixed with SCALA code, making the notation very expressive and convenient for practical purposes, one of the reasons that LOGFIRE is used daily on the MSL mission.

LOGFIRE was originally developed for verifying execution traces against formal specifications. A main focus was monitoring of events carrying data, what is also sometimes referred to as data parameterized monitoring. The purpose was to understand how well rule-based systems fare for this form of task. In the work presented here, we instead use LOGFIRE for generating abstract facts from low level events occurring in a log. Such facts are generated as a result of executing actions of rules triggered by lower-level events and facts. The rule-based approach is particularly suited for this form of fact generation, compared to other forms of runtime verification logics, such as temporal logics, regular expressions or state machines. The collection of facts built in this manner is then fed into a visualization tool implemented using the D3 library. The system is currently in use by the Curiosity operations team. A main core message of this work is that runtime verification as a field should embrace a wide range of technologies for not only verifying systems but also for learning and comprehending their behavior.

#### 1.3 Related Work

In [26] we describe an attempt to build a DSL on top of LOGFIRE in order to make it even easier to formulate abstraction rules for log comprehension and visualization. That work, however, is still a research prototype, and not (yet) used in mission operations, as is the case with the work presented here.

Numerous systems have been developed over the last decade for supporting monitoring of parameterized events, using various formalisms, such as state machines [2,5,11,21,32], regular expressions [1,32], variations over the  $\mu$ -calculus [4], temporal logics [4,5,8,9,15,22,32], grammars [32], and rule-based systems [7,25]. LOGFIRE itself was in part inspired by the RULER system [7]. Other rulebased systems include DROOLS [17], JESS [27] and CLIPS [13]. Standard rule systems usually enable processing of facts, which have a life span. In contrast, LOGFIRE additionally implements events, which are instantaneous. DROOLS supports a notion of events, which are facts with a limited life span, inspired by the concept of *Complex Event Processing* (CEP), described by David Luckham in [28].

Two other rule-based internal DSLs for SCALA exist: HAMMURABI [20] and ROOSCALOO [33]. HAMMURABI, which is not RETE-based, achieves efficient evaluation of rules by evaluating these in parallel, assigning each rule to a different SCALA actor. ROOSCALOO [33] is RETE based, but is not documented in any form other than experimental code. The DROOLS project has an effort ongoing, defining functional programming extensions to DROOLS [18]. In contrast, by embedding a rule system in an object-oriented and functional language, as done in LOGFIRE, we can leverage the already existing host language features.

TRACECONTRACT [5] and DAUT (Data automata) [23,24] are internal SCALA DSLs for trace analysis based on state machines. They allow for multi-transitions without explicitly naming the intermediate states, which allows for temporal logic like specifications, in addition to data parameterized state machines. TRACECON-TRACT was deployed throughout the LADEE mission [29], checking command sequences (similar format as logs) sent to the spacecraft, as documented in [6] at an early stage of that project.

#### 1.4 Contents

The paper is organized as follows. Section 2 introduces the rule-based system LOGFIRE, illustrating how it can be used for verifying the correctness of program/system executions. The example is that of general deadlock potential detection between any number of tasks, chosen since it illustrates the expressive power of rules. Section 3 presents the application of LOGFIRE to abstract and visualize telemetry from the Curiosity rover. Finally, Sect. 4 concludes the paper.

#### 2 The LogFire Runtime Verification System

LOGFIRE [25] is an API in the SCALA programming language, also here referred to as an internal DSL, created for writing rule-based runtime monitors. A monitor is specified as a set of rules, each of the form:  $lhs \Rightarrow rhs$ , which operate on a database of facts, called the *fact memory*. Rule left-hand sides test on incoming events, as well as presence or absence of facts in the fact memory. Right-hand sides (actions) can add facts to the fact memory, delete facts, issue error messages, and generally execute any SCALA code. A monitor takes as input a sequence of events, consumed one at a time, and for each event executes the actions of those rules whose left-hand sides evaluate to true. Monitors can be used to analyze the execution of a program as it executes or to analyze logs produced by the program. LOGFIRE is an implementation of the RETE algorithm [19], specifically as it is described in [16], modified to process instantaneous events (in addition to facts that have a life span), and to perform faster lookups in the fact memory. We will illustrate LOGFIRE using the example of detecting deadlock potentials [10] in a program by just analyzing a single execution trace generated by an instrumented version of the program. This example illustrates the flexibility of using a rule-based system. The reader is referred to [25] for more details about the implementation of LOGFIRE.

#### 2.1 The Deadlock Potential Detection Problem

Deadlock potentials in a program can very easily be detected by analyzing single execution traces generated by an appropriately instrumented program. We consider traces that only contain two kinds of events: lock(t, l), representing that task t takes the lock l; and unlock(t, l), representing that task t releases lock l. As described in [10], the standard technique for detecting deadlock potentials is to build a *lock graph*, where nodes are locks and where there is an edge between two nodes (locks)  $l_1$  and  $l_2$ , labelled with task id t, if task t at some point holds lock  $l_1$  while taking lock  $l_2$ . Nodes and edges are only added to the graph (never deleted). If at some point the graph contains a cycle it indicates the potential for deadlock, although not necessarily an actual deadlock. The algorithm can typically be made efficient in practice since it only needs to check for deadlock *potentials*, in contrast to, say, a model checker, which typically has to search the reachable state space for *actual* deadlocks.

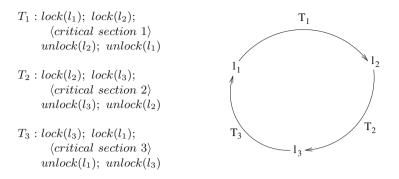

Fig. 1. Example illustrating three tasks  $T_1$ ,  $T_2$ , and  $T_3$ , taking three locks  $l_1$ ,  $l_2$ , and  $l_3$  in a cyclic manner, opening for a deadlock potential. This is detected as a cycle in the corresponding lock graph

Figure 1 shows an example illustrating how the algorithm works. The lefthand side shows three tasks (say, threads in a multi-threaded program), each taking two locks, then entering a critical section, and then releasing the locks. The locks are taken in a circular manner: a deadlock can occur if the tasks are scheduled such that each gets to take their first lock, but not the second. After that point none of the tasks can take the second lock since it is already held by one of the other tasks. Testing may not reveal this deadlock which only happens with certain schedules. For example, if we run these tasks in a sequential manner (first task  $T_1$ , then  $T_2$ , and then  $T_3$ ), no deadlocks will occur. However, we can record the lockings and unlockings in a graph, as shown on the right of Fig. 1. Each node is a lock, and an edge is drawn from a lock  $l_x$  to a lock  $l_y$ , labelled with task  $T_z$  if task  $T_z$  at some point holds lock  $l_x$  while taking lock  $l_y$ . If this graph ends up containing a cycle, as in this case, we have detected the potential for a deadlock.

Traditional implementations of such deadlock-potential checkers are coded as algorithms in a programming language [10]. An alternative is to formulate such a checker in a logic as a monitor specification, expressing that there must be no such cycles. The general case involves a cycle between any number n of tasks. It turns out, however, that traditional temporal logic is not expressive enough for the case where n is unknown (it can vary at execution time). Temporal logic solutions for exactly two tasks are shown in [3,34]. For example, the solution provided in [34] has the following form (with some minor changes for presentation purposes) expressed in linear temporal logic (LTL) extended with data, and stating the property that no cycles should exist between two tasks and locks:

$$\begin{array}{l} \forall t_1, t_2 : Task, l_1, l_2 : Lock \bullet \\ \mathbf{G} \ ( \\ \neg lock(t_1, l_2) \ \mathbf{U} \ (lock(t_1, l_1) \land (\neg unlock(t_1, l_1) \ \mathbf{U} \ lock(t_1, l_2))) \\ \rightarrow \\ \mathbf{G} \ \neg (\neg lock(t_2, l_1) \ \mathbf{U} \ (lock(t_2, l_2) \land (\neg unlock(t_2, l_2) \ \mathbf{U} \ lock(t_2, l_1)))) \\ ) \end{array}$$

This formula can be read as follows: always (**G**), if task  $t_1$  does not take lock  $l_2$  until (**U**) it takes lock  $l_1$ , and from then on does not release  $l_1$  until (**U**) it takes  $l_2$ , then always (**G**), it is not the case that task  $t_2$  follows the opposite pattern. Besides being cumbersome to read, it only captures the situation for two tasks and two locks. As we show in the next section, using a rule-based logic makes it possible to express the property for an arbitrary number of tasks.

#### 2.2 Formulating Deadlock Detection in LOGFIRE

Assume that our traces contain the two events: lock(t,l) and unlock(t,l). The cycle detection property (that no cycles should exist) is shown in Fig. 2. The main component of LOGFIRE is the **trait**<sup>1</sup> *Monitor*, which any user-defined monitor must extend to get access to the constants and methods provided by the rule DSL. The *events* lock and unlock are short-lived instantaneous observations about the system being monitored, those submitted to the monitor. In contrast, *facts*, in this case Locked and Edge, are long-lived pieces of information stored in the fact memory of the rule system, generated and deleted explicitly by the rules. The monitor contains five rules. Each rule has the form:

$$name -- condition_1 \& \dots \& condition_n \longmapsto action$$

Event and fact names, as well as parameter names are values of the SCALA type Symbol, which contains quoted identifiers such as 't. The rules read as follows. The first rule, named lock, states that on observation of a lock('t, 'l) event we insert a Locked('t, 'l) fact in the fact memory, representing the fact that task t holds the lock I. The second rule, named unlock, states that if a task t holds a lock I (represented by Locked('t, 'I)), and an unlock('t, 'I) event is observed, then that Locked fact is removed from the fact memory. The third rule, named edge, states that if a task t holds a lock 11 (represented by Locked('t, '11), and a lock('t, 'l2) event is observed, then an edge from l1 to l2 is drawn. The fourth rule, named close, performs the transitive closure of the edge-relation. Note that LOGFIRE for each event first evaluates all left-hand sides, recording which evaluate to true. Then it deletes the event from the fact memory, evaluates all the corresponding right-hand sides, and continues evaluating rules until a fixed point is reached (infinite loops are possible to program by a mistake). Only hereafter is the next event is consumed. This special handling of events is one difference wrt. the original RETE algorithm described in [16, 19]. The last rule, named cycle, detects cycles in the graph. It states that if there is an edge from a lock to itself then it is considered a deadlock potential. Symbols representing bindings of parameter values must be accessed with special get functions.

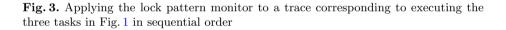

A monitor can be applied as shown in Fig. 3. Since the trace exposes a deadlock potential, an error trace is produced as shown in Fig. 4. Each entry in the error trace shows the number of the event, the event, the fact that it causes to be generated, and the rule that triggers.

<sup>&</sup>lt;sup>1</sup> A **trait** in SCALA is a module concept closely related to the notion of an *abstract class*, as for example found in JAVA.

```

class NoLockCycles extends Monitor {

val lock, unlock = event

val Locked, Edge = fact

"lock" -- lock('t,'l) → insert(Locked('t,'l))

"unlock" -- Locked('t,'l) & unlock('t,'l) → remove(Locked)

"edge" -- Locked('t,'l1) & lock('t,'l2) → insert(Edge('l1,'l2))

"close" -- Edge('l1,'l2) & Edge('l2,'l3) & not(Edge('l1,'l3)) →

insert (Edge('l1,'l3))

"cycle" -- Edge('l1,'l2) → {

if (get('l1) == get('l2)) fail ("cycle detected on " + get('l1))

}

}

```

Fig. 2. No-lock-cycles property in LOGFIRE

#### 2.3 Improving the Specification

The deadlock potential detection specification shown in Fig. 2 can be improved in three ways. Firstly, it can yield false positives. It will for example report a deadlock potential for a single task that accesses locks in a cyclic manner, although a single task cannot deadlock on its own (assuming reentrant locks). In order to exclude such false positives (although it can be argued that any cycles should be avoided), edges in the lock graph should be labelled with task ids, and a cycle is only reported in case all the task ids on the edges of the cycle are different. Secondly, the monitor will report the same deadlock potential multiple times due to the fact that different cycles (starting in different locks) represent the same problem. Thirdly, lock(t,l) and unlock(t,l) events are assumed to have exactly two arguments. Events in general may have many arguments, and instead of referring to them in a positional style as shown, we may want to pick out those arguments we are interested in by name, as for example with the notation  $unlock('task \rightarrow 't, 'lock \rightarrow 'l)$ . The alternative specification shown in Fig. 5 is an attempt to make these improvements and to illustrate additional features of LOGFIRE.

As can be seen, event arguments are referred to by name, as in unlock('task  $\rightarrow$  't,'lock  $\rightarrow$  'l). Each edge now also includes a set of task ids, namely those involved in forming the edge. A check in rule close is now performed that two edges can only be composed (transitive closure) if their task ids differ. We see here the use of set operations and sets as arguments to facts. Finally, in order to avoid a deadlock between a set of tasks to be reported multiple times, a

```

object ApplyMonitor {

def main(args: Array[String]) {

val m = new NoLockCycles

m.addEvent('lock)(1, "l1")

m.addEvent('lock)(1, "12")

m.addEvent('unlock)(1, "12")

m.addEvent('unlock)(1, "11")

m.addEvent('lock)(2, "12")

m.addEvent('lock)(2, "13")

m.addEvent('unlock)(2, "13")

m.addEvent('unlock)(2, "12")

m.addEvent('lock)(3, "13")

m.addEvent('lock)(3, "11")

m.addEvent('unlock)(3, "11")

m.addEvent('unlock)(3, "13")

}

}

```

variable is declared in the monitor, storing the sets of tasks that have so far been reported being involved in a deadlock potential. The rule cycle avoids to report a deadlock potential between a set of tasks in case a such has already been reported for those tasks. This illustrates how rules can be mixed with SCALA code, including declaration of variables and methods.

#### 3 Analyzing Telemetry from the Curiosity Rover

In this section, we describe how we have used LOGFIRE to process telemetry received from the Curiosity rover on Mars. Our focus here is on building tools based on LOGFIRE for processing telemetry in order to generate summaries that can be used for creating effective visualizations for use by the daily operations team. Our tools are integrated into the mission ground data system, and receive and automatically process telemetry from the rover several times a day. As this telemetry is processed, the tools generate summary files, typically in comma separated values (CSV) format. These summary files are in turn used by visualizations built using the D3 library [12]; these visualizations are used as part of a "dashboard" that is regularly monitored by mission operators and science planners.

```

[10] ' lock(3,"11") \implies 'Fail("ERROR cycle detected on 11")

rule: "cycle" -- 'Edge('l1,'l2) \mapsto \{...\}

```

Fig. 4. An error trace representing a lock cycle

In the following subsections, we give two examples of telemetry processing tools and show how they are used in building useful visualizations.<sup>2</sup>

#### 3.1**Monitoring Sequence Execution Status**

[1]

[2]

[5]

[6]

[6]

[9]

The first example shows a tool that monitors execution of spacecraft sequences. A sequence is a list of commands that perform specific spacecraft actions such as taking an image, or deleting a file, or possibly even invoking another sequence. The operations team typically uplinks a list of sequences every other day containing the commands that the rover should perform over the next two days.

$<sup>^{2}</sup>$  In the interests of readability, and to comply with NASA restrictions on publishing mission data, we have simplified the examples and modified the actual names and times from actual telemetry.

```

class NoLockCyclesImproved extends Monitor {

val lock, unlock = event

val Locked, Edge = fact

def getset(s: Symbol) = get[Set[Int ]](s)

var cycles : Set[Set[Int]] = Set()

"lock" -- lock('task \rightarrow 't,' lock \rightarrow 'l) \mapsto insert(Locked('t,'l))

"unlock" -- Locked('t,'l) & unlock('task \rightarrow 't,' lock \rightarrow 'l) \mapsto

remove(Locked)

"edge" -- Locked('t,'l1) & lock('task \rightarrow 't,' lock \rightarrow 'l2) \mapsto

insert (Edge(Set(get[Int]('t)),'l1,'l2))

"close" -- Edge('s1,'l1,'l2) & Edge('s2,'l2,'l3) & not(Edge(','l1,'l3)) →

ł

if (getset ('s1). intersect (getset ('s2)). isEmpty)

insert (Edge(getset ('s1). union(getset ('s2)), 'l1, 'l3))

"cycle" -- Edge('s,'l1,'l2) \mapsto

if (get('|1)) = get('|2) \& !cycles.contains(getset('s)))

fail ("cycle detected between tasks" + get('s))

cycles += getset('s)

}

}

```

Fig. 5. Improved no-lock-cycles property in LOGFIRE

This includes mobility requests (such as driving to a specific location), science requests (such as taking a panorama or firing a laser), as well as engineering requests (such as deleting old data files to free up space on flash memory).

Figure 6 shows the rules for processing telemetry related to sequence execution. These rules rely on processing an *event log* which is generated on board and sent to the ground periodically. The event log consists of a list of EVRs (short for "event reports"); each EVR has an associated timestamp (indicating the sclk, or *spacecraft clock* time when the event occurred), a unique identifier, and a text *message* describing the event. The SeqMonitor class extends the trait EvrMonitor, which itself extends trait Monitor, and in addition defines various utilities, such as the EVR event. The rule start\_seq is triggered by the log event EVR\_SEQ\_START and adds a fact SeqStart to the fact memory, recording the name and start time

11

```

class SegMonitor extends EvrMonitor {

val SeqStart, SeqDone = fact

def seq name(s:String) = words(s)(2) // Helper function

"start_seq" -- EVR('id \rightarrow "EVR_SEQ_START", 'sclk \rightarrow 'S, 'msg \rightarrow 'M) \longmapsto {

val w = words('M.s)

val seq name = w(15).slice(1, w(15).length-2)

insert (SeqStart(seq name, 'S.d))

}

"end_seq_ok" -- EVR('id \rightarrow "EVR_SEQ_SUCCESS", 'sclk \rightarrow 'E, 'msg \rightarrow 'M)

& 'SegStart('name, 'S) \mapsto {

if (seq name('M.s) == 'sname.s) {

replace (SeqStart)(SeqDone('name.s, 'S.d, 'E.d, "OK"))

}

}

"end_seq_fail" -- EVR('id \rightarrow "EVR_SEQ_FAILURE", 'sclk \rightarrow 'F, 'msg \rightarrow 'M)

& 'SeqStart('name, 'S) \mapsto {

if (seq_name('M.s) == 'name.s) {

replace(SeqStart)(SeqDone('name.s, 'S.d, 'F.d, "FAIL"))

}

}

"print" -- SeqDone('name, 'S, 'E, 'stat) \longmapsto {

updateCSV('name.s, 'S.d, 'E.d, 'stat.s)

remove(SeqDone)

}

}

```

Fig. 6. Rules for sequence execution

of the sequence. A sequence may terminate either successfully or unsuccessfully. A successful termination is denoted by the event EVR\_SEQ\_SUCCESS, which results in the SeqStart fact being replaced by a fact SeqDone, which records the name, start and end times of the sequence, along with the status OK, indicating that the sequence completed successfully. A sequence that terminates with failure results in the SeqStart fact being replaced by a fact SeqDone, which records the name, start and end times as before, along with the status FAIL. Finally, the print rule updates a CSV file containing a row for each sequence invocation, recording the start and end times and execution status.

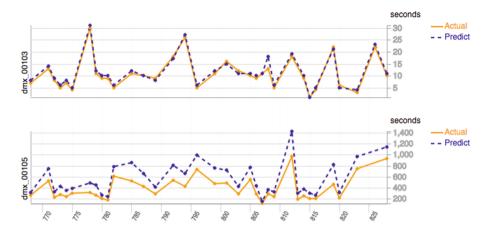

This CSV file is useful for building various visualizations that track how ground commands are being performed by the rover. As an example, Fig. 7 shows a visualization used by the data management operations team to compare the

Fig. 7. Visualization showing actual vs predicted sequence run times

actual onboard execution times across multiple days (shown on the x-axis) for two sequences ( $dmx_00103$  and  $dmx_00105$ ) against the times predicted by ground tools. As the figure shows, such a visualization makes it easy to see that the predictions for the  $dmx_00103$  sequence are much more accurate than the predictions for the  $dmx_00105$  sequence. This observation can then be used to further refine the models used by the ground tools to improve prediction times.

#### 3.2 Monitoring Communication Windows

Figure 8 shows the rules used for monitoring Curiosity's *communication windows* [30]. A communication window defines the periods when the spacecraft communicates either directly with Earth, or with one of several relay orbiting spacecraft. Due to the importance of communication, monitoring rover performance during a window is of great interest to the operations team. To aid this monitoring, we developed a set of rules that are used to generate summaries from rover telemetry; these summaries are in turn used to build useful visualizations that help the operational team monitor window performance.

A communication window consists of 3 phases – a prep phase, when on-board software configures the rover for the communication window (for instance, by turning on appropriate radios and retrieving from various cameras the images that will be sent to Earth); an active phase, during which the communication takes place; and a *cleanup* phase, for performing any cleanup actions (for instance, turning the radios off). Figure 8 shows four rules for processing telemetry for a communication window. The **prep** rule is triggered by the event **EVR\_BEGINS\_PREP** that indicates the start of a communication window; it adds the fact Prep(w, p) to the fact memory. Here w is the (unique) integer identifier associated with the window (this identifier is reported in the event message, and is extracted by the helper wid function shown in the example), and p is

```

13

```

```

class CommWindowMonitor extends EvrMonitor {

def wid(s: String, k: Int=5) = { val w = words(s)(k) ; w. slice (1, w. length). tolnt }

"prep" - EVR('id \rightarrow "EVR_BEGIN_PREP", 'sclk \rightarrow 'P, 'msg \rightarrow 'M) \longmapsto {

insert ('Prep(wid('M.s,4), 'P.d))

}

"active" -- EVR('id \rightarrow "EVR_BEGIN_ACTIVE", 'sclk \rightarrow 'A, 'msg \rightarrow 'M)

& 'Prep('W, 'P) \mapsto {

if (wid('M.s,2) == 'W.i) {

insert ('Active ('W.i, 'A.d))

}

}

"cleanup" -- EVR('id \rightarrow "EVR_CLEANUP", 'sclk \rightarrow 'C, 'msg \rightarrow 'M)

& 'Active('W, 'A) \mapsto {

if (wid('M.s,1) == 'W.i) {

insert ('Cleanup('W.i, 'C.d)

}

}

"print" -- 'Prep('W, 'P) & 'Active('W, 'A) & 'Cleanup('W, 'C) \mapsto {

updateCSV('W.i, 'P.d, 'A.d, 'C.d)

remove('Prep)

remove('Active)

remove('Cleanup)

}

}

```

Fig. 8. Rules for communication windows

the event timestamp (which indicates the time when prep started). Next, the **active** rule is used to detect when the active window begins; it is triggered by the EVR\_BEGINS\_ACTIVE event, and adds the fact Active(w, a) to the fact memory, where w is the window identifier and a is the event timestamp. In a similar fashion, the cleanup rule is triggered by the EVR\_CLEANUP event, and adds the Cleanup fact to the memory. Finally, the print rule updates a CSV file that defines all windows that have been performed on the rover; each row of this CSV file contains the window identifier and times when the prep, active and cleanup phases started.

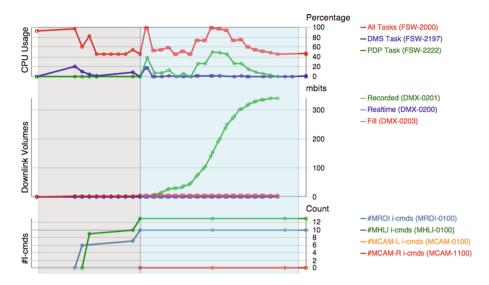

The CSV files are used to build the visualization shown in Fig. 9. This visualization uses the window definitions in the CSV file to provide context for assessing window performance. The top graph in the figure shows the percentage of CPU time taken up by various tasks, including the DMS and PDP tasks

Fig. 9. Visualization showing communication window performance

which respectively read files from flash memory and generate data packets for downlink. The middle graph shows the volume of data sent through the radio to an overhead orbiter; as the figure shows, the downlink rate varies over time, reaching a maximum rate when the orbiter is directly overhead (approximately halfway into the active session). Finally, the bottom graph shows the number of images fetched from each of the four cameras during window prep; in the example shown, the software fetched 13 images from the MHLI camera and 10 images from the MRDI camera (and no images from the other two cameras). Such visualizations are useful to the operations team, which can use them to determine, for instance, that the PDP task needs 40 % of the CPU for packet generation when the radio is communicating at its highest rates. This knowledge helps guide decisions on whether or not to schedule other processor-intensive activities during communication windows.

#### 4 Conclusion and Future Work

We have described the use of a rule-based engine, the LOGFIRE SCALA library, in building applications for processing telemetry. The applications are not limited to checking specific logical or temporal properties (as is common in runtime verification), but in addition generate summaries that are used to build effective visualizations supporting systems comprehension. We have described how these telemetry analysis applications are being deployed to process telemetry and build visualizations illustrating various aspects of the behavior of the Curiosity rover. The rule-based notation is shown to be sufficiently expressive and convenient for the task. The combination of a monitoring logic with a high-level programming language, in this case SCALA, has turned out to be a crucial advantage. Future work includes studying alternatives for defining the internal LOGFIRE DSL. LOGFIRE is a *deep embedding*, meaning that we have defined the abstract syntax for rules in SCALA, in contrast to a *shallow embedding* as in [23], where we would have used SCALA's own language constructs for writing rules. This again means that as a default there is no type checking of rules beyond what we program it to be. Another consequence is that user-defined names must be either strings or symbols (of the SCALA class Symbol), and to get to their values, in case they represent event/fact parameters, the user has to apply get functions. A more elegant solution could potentially be achieved by defining the DSL as a syntactic extension of SCALA, for example using the SUGARSCALA tool available at [35] (part of SUGARJ). Finally, the intention is to deploy LOGFIRE more broadly, within MSL, as well as within other missions, as a general approach to log analysis and comprehension at JPL.

#### References

- Allan, C., Avgustinov, P., Christensen, A.S., Hendren, L., Kuzins, S., Lhoták, O., de Moor, O., Sereni, D., Sittamplan, G., Tibble, J.: Adding trace matching with free variables to AspectJ. In: OOPSLA 2005. ACM Press (2005)

- Barringer, H., Falcone, Y., Havelund, K., Reger, G., Rydeheard, D.: Quantified event automata: towards expressive and efficient runtime monitors. In: Giannakopoulou, D., Méry, D. (eds.) FM 2012. LNCS, vol. 7436, pp. 68–84. Springer, Heidelberg (2012)

- Barringer, H., Goldberg, A., Havelund, K., Sen, K.: Program monitoring with LTL in eagle. In: Parallel and Distributed Systems: Testing and Debugging (PADTAD 2004), Santa Fee, New Mexico, USA, vol. 17. IEEE Computer Society, April 2004

- Barringer, H., Goldberg, A., Havelund, K., Sen, K.: Rule-based runtime verification. In: Steffen, B., Levi, G. (eds.) VMCAI 2004. LNCS, vol. 2937, pp. 44–57. Springer, Heidelberg (2004)

- Barringer, H., Havelund, K.: TRACECONTRACT: A scala dsl for trace analysis. In: Butler, M., Schulte, W. (eds.) FM 2011. LNCS, vol. 6664, pp. 57–72. Springer, Heidelberg (2011)

- Barringer, H., Havelund, K., Kurklu, E., Morris, R.: Checking flight rules with TraceContract: application of a scala DSL for trace analysis. In: Scala Days 2011, Stanford University, California (2011)

- Barringer, H., Rydeheard, D.E., Havelund, K.: Rule systems for run-time monitoring: from Eagle to RuleR. J. Log. Comput. 20(3), 675–706 (2010)

- Basin, D., Klaedtke, F., Müller, S.: Policy monitoring in first-order temporal logic. In: Touili, T., Cook, B., Jackson, P. (eds.) CAV 2010. LNCS, vol. 6174, pp. 1–18. Springer, Heidelberg (2010)

- Bauer, A., Küster, J.-C., Vegliach, G.: From propositional to first-order monitoring. In: Legay, A., Bensalem, S. (eds.) RV 2013. LNCS, vol. 8174, pp. 59–75. Springer, Heidelberg (2013)

- Bensalem, S., Havelund, K.: Dynamic deadlock analysis of multi-threaded programs. In: Ur, S., Bin, E., Wolfsthal, Y. (eds.) HVC 2005. LNCS, vol. 3875, pp. 208–223. Springer, Heidelberg (2006)

- Bodden, E.: MOPBox: a library approach to runtime verification. In: Khurshid, S., Sen, K. (eds.) RV 2011. LNCS, vol. 7186, pp. 365–369. Springer, Heidelberg (2012)

- Bostock, M., Ogievetsky, V., Heer, J.: D3: Data-driven documents. IEEE Trans. Vis. Comput. Graph. 17, 2301–2309 (2011)

- 13. Clips website. http://clipsrules.sourceforge.net

- 14. D3 website. http://d3js.org

- Decker, N., Leucker, M., Thoma, D.: Monitoring modulo theories. In: Ábrahám, E., Havelund, K. (eds.) TACAS 2014. LNCS, vol. 8413, pp. 341–356. Springer, Heidelberg (2014)

- Doorenbos, R.B.: Production matching for large learning systems, Ph.D. thesis, Carnegie Mellon University, Pittsburgh, PA (1995)

- 17. Drools website. http://www.jboss.org/drools

- Drools functional programming extensions website. https://community.jboss.org/ wiki/FunctionalProgrammingInDrools

- Forgy, C.: Rete: a fast algorithm for the many pattern/many object pattern match problem. Artif. Intell. 19, 17–37 (1982)

- Fusco, M.: Hammurabi a Scala rule engine. In: Scala Days 2011, Stanford University, California (2011)

- Goubault-Larrecq, J., Olivain, J.: A smell of ORCHIDS. In: Leucker, M. (ed.) RV 2008. LNCS, vol. 5289, pp. 1–20. Springer, Heidelberg (2008)

- Hallé, S., Villemaire, R.: Runtime enforcement of web service message contracts with data. IEEE Trans. Serv. Comput. 5(2), 192–206 (2012)

- Havelund, K.: Data automata in Scala. In: Leucker, M., Wang, J., (eds.) Proceedings of the 8th International Symposium on Theoretical Aspects of Software Engineering, TASE 2014, Changsha, China, 1–3 September. IEEE Computer Society Press (2014)

- Havelund, K.: Monitoring with data automata. In: Margaria, T., Steffen, B. (eds.) ISoLA 2014, Part II. LNCS, vol. 8803, pp. 254–273. Springer, Heidelberg (2014)

- Havelund, K.: Rule-based runtime verification revisited. Softw. Tools Technol. Transf. (STTT) 17(2), 143–170 (2015)

- Havelund, K., Joshi, R.: Comprehension of spacecraft telemetry using hierarchical specifications of behavior. In: Merz, S., Pang, J. (eds.) ICFEM 2014. LNCS, vol. 8829, pp. 187–202. Springer, Heidelberg (2014)

- 27. Jess website. http://www.jessrules.com/jess

- 28. Luckham, D. (ed.): The Power of Events: An Introduction to Complex Event Processing in Distributed Enterprise Systems. Addison-Wesley, Reading (2002)

- 29. Lunar Atmosphere Dust Environment Explorer (LADEE) mission website. http:// www.nasa.gov/mission\_pages/LADEE/main

- Makovsky, A., Ilott, P., Taylor, J.: Mars science laboratory telecommunications system design. Descanso Design and Performance Summary Series, Article 14 (2009)

- 31. Mars Science Laboratory (MSL) mission website. http://mars.jpl.nasa.gov/msl

- Meredith, P., Jin, D., Griffith, D., Chen, F., Rou, G.: An overview of the MOP runtime verification framework. Softw. Tools Technol. Transf. (STTT) 14(3), 249– 289 (2012)

- 33. Rooscaloo website. http://code.google.com/p/rooscaloo

- Stolz, V., Bodden, E.: Temporal assertions using AspectJ. In: Proceedings of the 5th International Workshop on Runtime Verification (RV 2005), vol. 144, no. 4, ENTCS, pp. 109–124. Elsevier (2006)

- 35. SugarJ website. http://www.student.informatik.tu-darmstadt.de/~xx00seba/ projects/sugarj

# Safety, Dependability and Performance Analysis of Aerospace Systems

Thomas  $\operatorname{Noll}^{(\boxtimes)}$

Software Modeling and Verification Group, RWTH Aachen University, Aachen, Germany noll@cs.rwth-aachen.de http://moves.rwth-aachen.de/

Abstract. The size and complexity of software in spacecraft is increasing exponentially, and this trend complicates its validation within the context of the overall spacecraft system. Current validation methods are labour-intensive as they rely on manual analysis, review and inspection. In this paper we give an overview of an integrated system-software co-engineering approach focusing on a coherent set of specification and analysis techniques for evaluation of system-level correctness, safety, dependability and performability of on-board computer-based aerospace systems. It features both a tailored modelling language and toolset for supporting (semi-)automated validation activities. Our modelling language is a dialect of the Architecture Analysis and Design Language, AADL, and enables engineers to specify the system, the software, and their reliability aspects. The COMPASS toolset employs state-of-the-art model checking techniques, both qualitative and probabilistic, for the analysis of requirements related to functional correctness, safety, dependability and performance.

#### 1 Introduction

Building modern aerospace systems is highly demanding. They should be extremely dependable, offering service without interruption (i.e., without failure) for a very long time – typically years or decades. Whereas "five nines" dependability, i.e., a 99.999 % availability, is satisfactory for most safety-critical systems, for aerospace on-board systems it is not. Faults are costly and may severely damage reputations. Dramatic examples are known. Fatal defects in the control software of the Ariane-5 rocket and the Mars Pathfinder have led to headlines in newspapers all over the world. Rigorous design support and analysis techniques are called for. Bugs must be found as early as possible in the design process while performance and reliability guarantees need to be checked

We thank all co-workers in the COMPASS project for their contributions, including the groups of Alessandro Cimatti (FBK, Trento, IT), Xavier Olive (Thales Alenia Space, FR), David Lesens (Airbus Defence and Space, FR) and Yuri Yushtein (ESA/ESTEC, NL). This research has been funded by the European Space Agency via several grants.

<sup>©</sup> Springer International Publishing Switzerland 2015

C. Artho and P.C. Ölveczky (Eds.): FTSCS 2014, CCIS 476, pp. 17–31, 2015. DOI: 10.1007/978-3-319-17581-2.2

whenever possible. The effect of fault diagnosis, isolation and recovery must be quantifiable.

Tailored effective techniques exist for specific system-level aspects. Peer reviewing and extensive testing detect most of the software bugs, performance is checked using queueing networks or simulation, and hardware safety levels are analysed using a profiled Failure Modes and Effects Analysis (FMEA) approach. Fine. But how is the consistency between the analysis results ensured? What is the relevance of a zero-bug confirmation if its analysis is based on a system view that ignores critical performance bottlenecks? There is a clear need for an integrated, coherent approach! This is easier said than done: the inherent heterogeneous character of on-board systems involving software, sensors, actuators, hydraulics, electrical components, etc., each with its own specific development approach, severely complicates this.

The COMPASS project [15] advances the system-software perspective by providing means for its validation in the early design phases, such that system architecture, software architecture, and their interfacing requirements are aligned with the overall functional intents and risk tolerances. Validation in the current practice is labour-intensive and consists mostly of manual analysis, review and inspection. We improve upon this by adopting a model-based approach using formal methods. In COMPASS, the system, the software and its reliability models are expressed in a single modelling language. This language originated from the need for a language with a rigorous formal semantics, and it is a dialect of the Architecture Analysis & Design Language (AADL). Models expressed in our AADL dialect are processed by the COMPASS toolset that automates analyses which are currently done manually. The automated analyses allow studying functional correctness of discrete, real-time and hybrid aspects under degraded modes of operation, generating safety & dependability validation artefacts, performing probabilistic risk assessments, and evaluating effectiveness of fault management. The analyses are mapped onto discrete, symbolic and probabilistic model checkers, but all of them are completely hidden away from the user by appropriate model-transformations. The COMPASS toolset is thus providing an easy-to-use push-button analysis technology.

The first ideas and concepts for the development of the COMPASS toolset emerged in 2007, due to a series of significant advances in model checking [2], and especially in its probabilistic counterpart [1]. These advances opened prospects for an integrated model-based approach towards system-software correctness validation, safety & dependability assessment and performance evaluation during the design phase. Its technology readiness level was estimated at level 1, i.e. basic principles were observed and reported. The European Space Agency (ESA) issued a statement of work to improve system-software co-engineering and this was commissioned to the COMPASS consortium consisting of RWTH Aachen University, Fondazione Bruno Kessler and Thales Alenia Space. Development started soon after, and in 2009 a COMPASS toolset prototype was delivered to the European space industry. Maturation was followed by subsystem-level case studies performed by Thales Alenia Space [10]. As of 2012, two large pilot projects took place in ESA for a spacecraft in development. This marked the maturation of the COMPASS toolset to early level 4, namely laboratory-tested. This paper summarises the background work. Altogether, it describes the current state of the art in system-software spacecraft co-engineering, ranging from the used techniques, to the tools and the conducted industrial projects.

The remainder is organised as follows. An introduction to the developed modelling language is given in Sect. 2, followed by an overview of the toolset and its supported analyses in Sect. 3. Section 4 draws a conclusion about the evaluation activities.

#### 2 Modelling Using an AADL Dialect

The Architecture Analysis and Design Language (AADL) [24,35] is an industry standard for modelling safety-critical system architectures and it is developed and governed by the Society of Automotive Engineers (SAE). Although standardized by the SAE, it is backed by the aerospace community as well. AADL provides a cohesive and uniform approach to model heterogeneous systems, consisting of software (e.g., processes and threads) and hardware (e.g., processors and buses) components, and their interactions. Our variant of AADL was designed to meet the needs of the European space industry. It extends a core fragment of AADL 1.0 [32] by supporting the following essential features:

- Modelling both the system's nominal and faulty behaviour. To this aim, AADL provides primitives to describe software and hardware faults, error propagation (i.e., turning fault occurrences into failure events), sporadic (transient) and permanent faults, and degraded operation modes (by mapping failures from architectural to service level).

- Modelling (partial) *observability* and the associated observability requirements. These notions are essential to deal with diagnosability and Fault Detection, Isolation and Recovery (FDIR) analyses.

- Specifying timed and hybrid behaviour. In particular, to analyze continuous physical systems such as mechanics and hydraulics, our modelling language supports continuous real-valued variables with (linear) time-dependent dynamics.

- Modelling *probabilistic* aspects. These are important to specify random faults and systems repairs with stochastic timing.

In the following, we present the capabilities of our AADL dialect using a running example. A complete AADL specification consists of three parts, namely a description of the nominal behaviour, a description of the error behaviour and a fault injection specification that describes how the error behaviour influences the nominal behaviour. These three parts are discussed below. Due to space constraints, we refer the interested reader to [12] for a description of the formal semantics.

#### 2.1 Nominal Behaviour

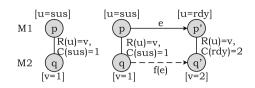

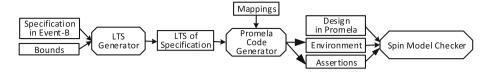

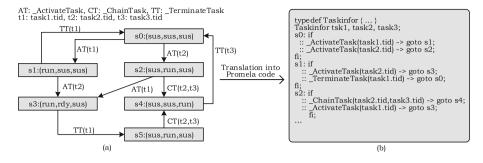

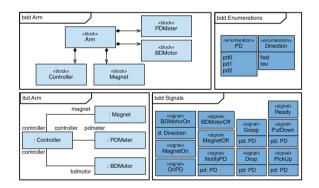

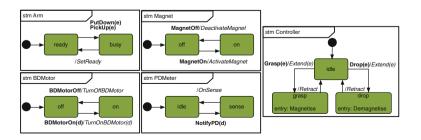

An AADL model is hierarchically organized into *components*, distinguished into software (processes, threads, data), hardware (processors, memories, devices, buses), and composite components (called *systems*). Components are defined by their *type* (specifying the functional interfaces as seen by the environment) and their *implementation* (representing the internal structure). An example of a component's type and implementation for a simple battery device [8] is shown in Fig. 1.

The component type describes the ports through which the component communicates. For example, the type interface of Fig. 1 features three ports, namely an outgoing event port empty which indicates that the battery is about to become discharged, an incoming data port tryReset which indicates that the battery device should (attempt to) reset, and an outgoing data port voltage which makes its current voltage level accessible to the environment.

A component implementation defines its subcomponents, their interaction through (event and data) port connections, the (physical) bindings at runtime, the operational behaviour via modes, the transitions between them, which are spontaneous or triggered by events arriving at the ports, and the timing and hybrid behaviour of the component. For example, the implementation of Fig. 1 specifies the battery to be in the charged mode whenever activated, with an energy level of 100% as indicated by the default value of 1.0. This level is continuously decreased by 2% (of the initial amount) per time unit (energy' denotes the first derivative of **energy**) until a threshold value of 20 % is reached, upon which the battery changes to the depleted mode. This mode transition triggers the empty output event, and the loss rate of energy is increased to 3%. Moreover, the voltage value is regularly computed from the energy level (ranging between 6.0 and 4.0 [volts]) and made accessible to the environment via the corresponding outgoing data port. In addition, the battery reacts to the tryReset port to decide when a reset operation should be performed in reaction to faulty behaviour (see the description of error models below).

In general, the mode transition system—basically a finite-state automaton describes how the component evolves from mode to mode while performing events. Invariants on the values of data components (such as "energy  $\geq 0.2$ " in mode charged) restrict the residence time in a mode. Trajectory equations (such as those associated with energy') specify how continuous variables evolve while residing in a mode. This is akin to timed and hybrid automata [28]. Here we assume that all invariants are linear. Moreover we constrain the derivatives occurring in trajectory equations to real constants, i.e., the evolution of continuous variables is described by simple linear functions.

A mode transition is given by m - [e when g then f] - > m'. It asserts that the component can evolve from mode m to mode m' upon occurrence of event e (the trigger event) provided that guard g, a Boolean expression that may depend on the component's (discrete and continuous) data elements, holds. Here "data elements" refers to (both incoming and outgoing) data ports and

```

device Battery

features

empty: out event port;

tryReset: in data port bool default false;

voltage: out data port real default 6.0;

end Battery;

device implementation Battery.Imp

subcomponents

energy: data continuous default 1.0;

modes

charged: initial mode while energy' = -0.02 and energy >= 0.2;

depleted: mode while energy' = -0.03 and energy >= 0.0;

transitions

charged -[then voltage := 2.0*energy+4.0]-> charged;

charged -[reset when tryReset]-> charged;

charged -[empty when energy = 0.2]-> depleted;

depleted -[then voltage := 2.0*energy+4.0]-> depleted;

depleted -[reset when tryReset]-> depleted;

end Battery.Imp;

```

Fig. 1. Specification of a battery component.

```

system Power

features

alert: out data port bool observable;

end Power:

system implementation Power.Imp

subcomponents

batt1: device Battery in modes (primary);

batt2: device Battery in modes (backup);

mon: device Monitor;

connections

data port batt1.voltage -> mon.voltage in modes (primary);

data port batt2.voltage -> mon.voltage in modes (backup);

data port mon.alert -> alert;

data port mon.alert -> batt1.tryReset in modes (primary);

data port mon.alert -> batt2.tryReset in modes (backup);

modes

primary: initial mode;

backup: mode;

transitions

primary -[batt1.empty]-> backup;

backup -[batt2.empty]-> primary;

end Power.Imp;

```

Fig. 2. The complete power system.

```

device Monitor

features

voltage: in data port real;

alert: out data port bool;

end Monitor;

device implementation Monitor.Imp

flows

alert := (voltage < 4.5);

end Monitor.Imp;</pre>

```

Fig. 3. Specification of the monitor.

data subcomponents of the respective component. On transiting, the effect f which may update data subcomponents or outgoing data ports (like voltage) is applied. The presence of event e, guard when g and effect then f is optional. If absent, e defaults to an internal event, g to true, and f to the empty effect.

Mode transitions may give rise to modifications of a component's configuration: subcomponents can become (de-)activated and port connections can be (de-)established. This depends on the in modes clause, which can be declared along with port connections and subcomponents. This is demonstrated by the specification in Fig. 2, which shows the usage of the battery component in the context of a redundant power system. It contains two instances of the battery device, namely batt1 and batt2, being respectively active in the primary and the backup mode. The mode switch that initiates reconfiguration is triggered by an empty event arriving from the battery that is currently active. The data ports are reconfigured too in this example. The voltage port of batt2 is connected to the overall power system once switched to the backup mode.

A similar reconfiguration is also performed for the alerts from the monitor component, which checks the current voltage level and raises an alarm if it falls below a critical threshold of 4.5 [volts]. Its specification is shown in Fig. 3; it employs another modelling concept, a so-called *flow*. A flow establishes a direct dependency between an outgoing data port of a component and (some of) its incoming data ports, meaning that a value update of one of the given incoming data ports immediately causes a corresponding update of the outgoing data port.

#### 2.2 Error Behaviour

*Error models* are an extension to the specification of nominal models [34] and are used to conduct safety and dependability analyses. For modularity, they are defined separately from nominal specifications. Akin to nominal models, an error model is defined by its type and its associated implementation.

An error model *type* defines an interface in terms of error states and (incoming and outgoing) error propagations. Error *states* are employed to represent the current configuration of the component with respect to the occurrence of errors. Error *propagations* are used to exchange error information between components. They are similar to input and output event ports, but differ in that error events

```

error model BatteryFailure

features

ok: initial state;

dead: error state;

resetting: error state;

batteryDied: out error propagation;

end BatteryFailure;

error model implementation BatteryFailure.Imp

events

fault: error event occurrence poisson 0.001;

works: error event occurrence poisson 0.2;

fails: error event occurrence poisson 0.8;

transitions

ok -[fault]-> dead;

dead -[batteryDied]-> dead;

dead -[reset]-> resetting;

resetting -[works]-> ok;

resetting -[fails]-> dead;

end BatteryFailure.Imp;

```

Fig. 4. Specification of the battery error model.

are matched by identifier rather than by an explicit declaration of an event port connection.

An error model *implementation* provides the structural details of the error model. It is defined by a (probabilistic) machine over the error states declared in the error model type. Transitions between states can be triggered by error events, reset events, and error propagations.

Figure 4 presents a basic error model for the battery device. It defines a probabilistic error event, fault, which occurs once every 1000 time units on average. Whenever this happens, the error model changes into the dead state. In the latter, the battery failure is signalled to the environment by means of the outgoing error propagation batteryDied. Moreover, the battery is enabled to receive a reset event from the nominal model to which the error behaviour is attached. It causes a transition to the resetting state, from which the battery recovers with a probability of 20 %, and returns to the dead state otherwise.

#### 2.3 Fault Injection

As error models bear no relation with nominal models, an error model does not influence the nominal model unless they are linked through *fault injection*.

A fault injection describes the effect of the occurrence of an error on the nominal behaviour of the system. More concretely, it specifies the value update that a data element of a component implementation undergoes when its associated error model enters a specific error state. To this aim, each fault injection has to be given by the user by specifying three parts: a state s in the error model

(such as dead in Fig. 4), an outgoing data port or subcomponent d in the nominal model (such as voltage in Fig. 1), and the fault effect given by the expression a (such as the value 0, indicating the collapse of power). Multiple fault injections between error models and nominal models are possible.

The automatic procedure that integrates both models and the given fault injections, the so-called *model extension*, works as follows. The principal idea is that the nominal and error models are running concurrently. That is, the state space of the extended model consists of pairs of nominal modes and error states, and each transition in the extended model is due to a nominal mode transition, an error state transition, or a combination of both (in case of a reset operation). The aforementioned fault injection becomes enabled whenever the error model enters state s. In this case the assignment d := a is carried out, i.e., the data subcomponent d is assigned with the fault effect a. This error effect is maintained as long as the error model stays in state s, overriding possible assignments to d in the nominal model. When s is left, the fault injection is disabled (though another one may be enabled). An example of an extended model can be found in [12].

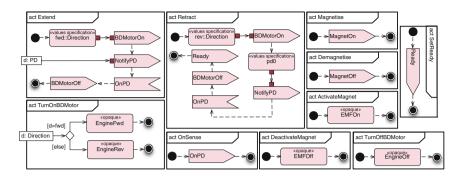

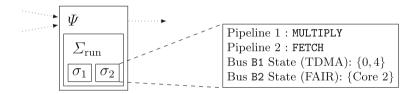

#### 3 The COMPASS Toolset

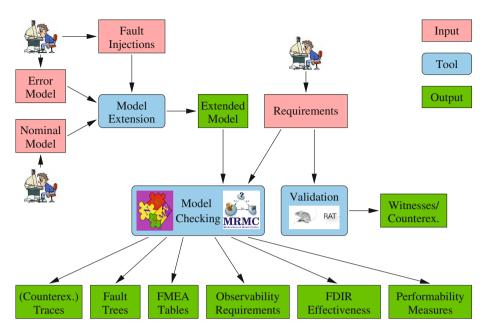

The COMPASS toolset is the result of a significant implementation effort carried out by the COMPASS Consortium. The GUI and most subcomponents are implemented in Python, using the PyGTK library. Pre-existing components, such as the NuSMV and MRMC model checker, are instead written in C. Overall, the core of the toolset consists of about 100,000 lines of Python code. Figure 5 shows the functionality of the toolset.

COMPASS takes as input one or more AADL models, and a set of properties. The latter are provided in the form of instantiated property *patterns* [17,25], which are templates containing placeholders that have to be filled in by the user. The COMPASS toolset provides templates for the most frequently used patterns, that ease property specifications by non-experts through hiding the details of the underlying temporal logic. The tool generates several outputs, such as traces, fault trees and FMEA tables, diagnosability and performability measures.

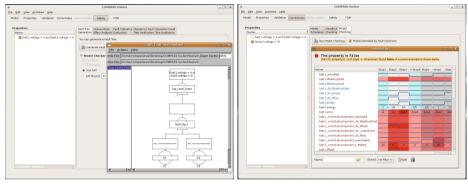

The toolset builds upon the following main components. NuSMV [14,23] (New Symbolic Model Verifier) is a symbolic model checker that supports stateof-the-art verification techniques such as BDD-based and SAT-based verification for CTL and LTL [2]. MRMC [30,31] (Markov Reward Model Checker) is a probabilistic model checker that supports the analysis of discrete-time and continuous-time Markov reward models. Specifications are written in PCTL (Probabilistic Computation Tree Logic) and CSL (Continuous Stochastic Logic [1], a probabilistic real-time version of CTL). SigRef [37] is used to minimize, amongst others, Interactive Markov Chains (IMC) [29] based on various notions of bisimulation. It is a symbolic tool using multi-terminal BDD representations of IMCs and applies signature-based minimization algorithms. A walkthrough of the toolset in terms of its screenshots in shown in Fig. 6.

Fig. 5. Functional view of the COMPASS platform.

The tool also supports a graphical notation of our AADL dialect, that is a derivation of the AADL graphical notation [33]. We developed a graphical drawing editor enabling engineers to construct models visually using the adopted graphical notation. The editor is called the COMPASS Graphical Modeller and is part of the COMPASS toolset.

#### 3.1 Functional Correctness

COMPASS supports random and guided *model-based simulation* of AADL models. Guided simulation can be performed by choosing either the next transition to be taken, or a target value for one or more variables. The generated traces can be inspected using a trace manager that displays the values of the model variables of interest (filtering is possible) for each step.

Property verification is based on model checking [2], an automated technique that verifies whether a property expressed in temporal logic, holds for a given model. Symbolic techniques [3, 4, 27] are used to tackle the problem of state space explosion. COMPASS relies on the NuSMV model checker, which supports both BDD-based and SAT-based verification for finite-state systems, and SMT-based verification techniques for timed and hybrid systems, based on the MathSAT solver [7, 22]. On refutation of a property, a counterexample is generated, showing an execution trace of the model violating the property. An example of this is shown in Fig. 6(d). Finally, it is possible to run *deadlock checking*, in order to pinpoint deadlocks (i.e., states with no outgoing transitions) in the model.

| + COMPASS To                                                                                                                           | ohet -                                      |    | +                                                      | COMPASS Toolset                |                       | _ O X  |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|--------------------------------------------------------|--------------------------------|-----------------------|--------|

| Bie Edit View Activities Help                                                                                                          |                                             |    | Bie Edit View Activities Help                          |                                |                       | _      |

| Hodel Properties Validation Correctness Performability Safety FCR                                                                      |                                             |    | Model Properties Validation Correctness Performability | Safety FDR.                    |                       |        |

| Loaded Files                                                                                                                           | Fault injections                            |    | Properties                                             |                                |                       |        |

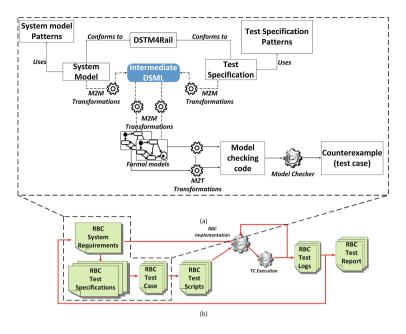

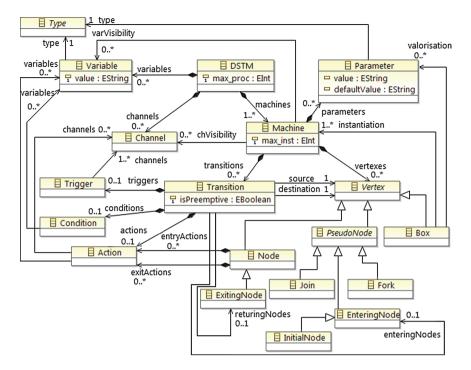

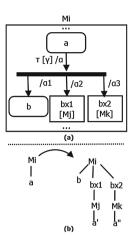

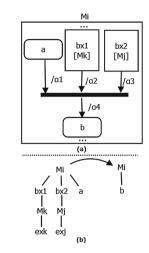

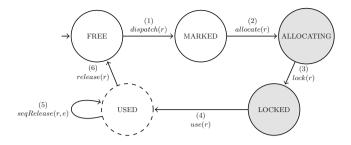

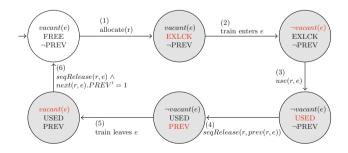

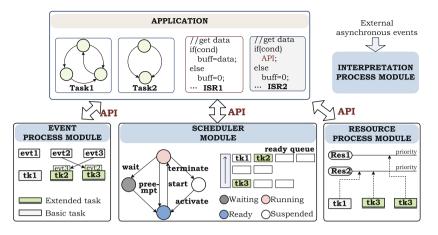

| Filename                                                                                                                               | Use Error Implementation Error State Effect |    | batt1.voltage < 4 and batt2.voltage < 4                |                                |                       |        |