Luís Miguel Pinho Wolfgang Karl Albert Cohen Uwe Brinkschulte (Eds.)

# Architecture of Computing Systems – ARCS 2015

28th International Conference Porto, Portugal, March 24–27, 2015 Proceedings

## Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zürich, Zürich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbrücken, Germany More information about this series at http://www.springer.com/series/7407

Luís Miguel Pinho · Wolfgang Karl Albert Cohen · Uwe Brinkschulte (Eds.)

## Architecture of Computing Systems – ARCS 2015

28th International Conference Porto, Portugal, March 24–27, 2015 Proceedings

*Editors* Luís Miguel Pinho CISTER/INESC TEC, ISEP Research Center Porto Portugal

Wolfgang Karl Karlsruher Institut für Technologie Karlsruhe Germany Albert Cohen Inria and École Normale Supérieure Paris France

Uwe Brinkschulte Goethe University Fachbereich Informatik und Mathematik Frankfurt am Main Germany

ISSN 0302-9743 Lecture Notes in Computer Science ISBN 978-3-319-16085-6 DOI 10.1007/978-3-319-16086-3 ISSN 1611-3349 (electronic) ISBN 978-3-319-16086-3 (eBook)

Library of Congress Control Number: Applied for

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

#### Preface

The 28th International Conference on Architecture of Computing Systems (ARCS 2015) was hosted by the CISTER Research Center at Instituto Superior de Engenharia do Porto, Portugal, from March 24 to 27, 2015 and continues the long-standing ARCS tradition of reporting top-notch results in computer architecture and related areas. It was organized by the special interest group on 'Architecture of Computing Systems' of the GI (Gesellschaft für Informatik e. V.) and ITG (Informationstechnische Gesellschaft im VDE), with GI having the financial responsibility for the 2015 edition. The conference was also supported by IFIP (International Federation of Information Processing).

The special focus of ARCS 2015 was on "Reconciling Parallelism and Predictability in Mixed-Critical Systems." This reflects the ongoing convergence between computational, control, and communication systems in many application areas and markets. The increasingly data-intensive and computational nature of Cyber-Physical Systems is now pushing for embedded control systems to run on complex parallel hardware. System designers are squeezed between the hammer of dependability, performance, power and energy efficiency, and the anvil of cost. The latter is typically associated with programmability issues, validation and verification, deployment, maintenance, complexity, portability, etc. Traditional, low-level approaches to parallel software development are already plagued by data races, non-reproducible bugs, time unpredictability, non-composability, and unscalable verification. Solutions exist to raise the abstraction level, to develop dependable, reusable, and efficient parallel implementations, and to build computer architectures with predictability, fault tolerance, and dependability in mind. The Internet of Things also pushes for reconciling computation and control in computing systems. The convergence of challenges, technology, and markets for highperformance consumer and mobile devices has already taken place. The ubiquity of safety, security, and dependability requirements meets cost efficiency concerns. Longterm research is needed, as well as research evaluating the maturity of existing system design methods, programming languages and tools, software stacks, computer architectures, and validation approaches. This conference put a particular focus on these research issues.

The conference attracted 45 submissions from 22 countries. Each paper was assigned to at least three Program Committee Members for reviewing. The Committee selected 19 submissions for publication with authors from 11 countries. These papers were organized into six sessions covering topics on hardware, design, applicatrions, trust and privacy, and real-time issues. A session was dedicated to the three best paper candidates of the conference. Three invited talks on "The Evolution of Computer Architectures: A View from the European Commission" by Sandro D'Elia, European Commission Unit "Complex Systems & Advanced Computing," Belgium, "Architectures for Mixed-Criticality Systems based on Networked Multi-Core Chips" by Roman Obermaisser, University of Siegen, Germany, and "Time Predictability in High-Performance Mixed-Criticality Multicore Systems" by Francisco Cazorla, Barcelona Supercomputing Center, Spain, completed the strong technical program. Four workshops focusing on specific sub-topics of ARCS were organized in conjunction with the main conference, one on Dependability and Fault Tolerance, one on Multi-Objective Many-Core Design, one on Self-Optimization in Organic and Autonomic Computing Systems, as well as one on Complex Problems over High Performance Computing Architectures. The conference week also featured two tutorials, on CUDA tuning and new GPU trends, and on the Myriad2 architecture, programming and computer vision applications.

We would like to thank the many individuals who contributed to the success of the conference, in particular the members of the Program Committee as well as the additional external reviewers, for the time and effort they put into reviewing the submissions carefully and selecting a high-quality program. Many thanks also to all authors for submitting their work. The workshops and tutorials were organized and coordinated by João Cardoso, and the poster session was organized by Florian Kluge and Patrick Meumeu Yomsi. The proceedings were compiled by Thilo Pionteck, industry liaison performed by Sascha Uhrig and David Pereira, and conference publicity by Vincent Nélis. The local arrangements were coordinated by Luis Ferreira. Our gratitude goes to all of them as well as to all other people, in particular the team at CISTER, which helped in the organization of ARCS 2015.

January 2015

Luís Miguel Pinho Wolfgang Karl Albert Cohen Uwe Brinkschulte

## Organization

## **General Co-Chairs**

| Luís Miguel Pinho<br>Wolfgang Karl    | CISTER/INESC TEC, ISEP, Portugal<br>Karlsruhe Institute of Technology, Germany |  |

|---------------------------------------|--------------------------------------------------------------------------------|--|

| Program Co-chairs                     |                                                                                |  |

| Albert Cohen<br>Uwe Brinkschulte      | Inria, France<br>Universität Frankfurt, Germany                                |  |

| Publication Chair                     |                                                                                |  |

| Thilo Pionteck                        | Universität zu Lübeck, Germany                                                 |  |

| Industrial Liaison Co-ch              | airs                                                                           |  |

| Sascha Uhrig<br>David Pereira         | Technische Universität Dortmund, Germany<br>CISTER/INESC TEC, ISEP, Portugal   |  |

| Workshop and Tutorial                 | Chair                                                                          |  |

| João M. P. Cardoso                    | University of Porto/INESC TEC, Portugal                                        |  |

| Poster Co-chairs                      |                                                                                |  |

| Florian Kluge<br>Patrick Meumeu Yomsi | University of Augsburg, Germany<br>CISTER/INESC TEC, ISEP, Portugal            |  |

| Publicity Chair                       |                                                                                |  |

| Vincent Nelis                         | CISTER/INESC TEC, ISEP, Portugal                                               |  |

| Local Organization Cha                | ir                                                                             |  |

| Luis Lino Ferreira                    | CISTER/INESC TEC, ISEP, Portugal                                               |  |

#### **Program Committee**

Michael Beigl Mladen Berekovic Simon Blindze Florian Brandner Jürgen Brehm Uwe Brinkschulte David Broman João M.P. Cardoso Luigi Carro Albert Cohen Koen De Bosschere Nikitas Dimopoulos Ahmed El-Mahdy Fabrizio Ferrandi Dietmar Fey Pierfrancesco Foglia William Fornaciari Björn Franke Roberto Giorgi Daniel Gracia Pérez Jan Haase Jörg Henkel Andreas Herkersdorf Christian Hochberger Jörg Hähner Michael Hübner Gert Iervan Ben Juurlink Wolfgang Karl Christos Kartsaklis Jörg Keller Raimund Kirner Andreas Koch Hana Kubátová

Olaf Landsiedel Paul Lukowicz

Karlsruhe Institute of Technology, Germany Technische Universität Braunschweig, Germany École Polytechnique Fédérale de Lausanne, Switzerland École Nationale Supérieure de Techniques Avancées. France Leibniz Universität Hannover, Germany Universität Frankfurt am Main, Germany KTH Royal Institute of Technology, Sweden, and University of California, Berkeley, USA University of Porto/INESC TEC, Portugal Universidade Federal do Rio Grande do Sul. Brazil Inria. France Ghent University, Belgium University of Victoria, Canada Egypt-Japan University of Science and Technology, Egypt Politecnico di Milano, Italy Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany Università di Pisa, Italy Politecnico di Milano, Italy University of Edinburgh, UK Università di Siena, Italy Thales Research and Technology, France University of the Federal Armed Forces Hamburg, Germany Karlsruhe Institute of Technology, Germany Technische Universität München, Germany Technische Universität Darmstadt, Germany Universität Augsburg, Germany Ruhr University Bochum, Germany Tallinn University of Technology, Estonia Technische Universität Berlin, Germany Karlsruhe Institute of Technology, Germany Oak Ridge National Laboratory, USA Fernuniversität in Hagen, Germany University of Hertfordshire, UK Technische Universität Darmstadt, Germany Czech Technical University in Prague, Czech Republic Chalmers University of Technology, Sweden Universität Passau, Germany

Erik Maehle Christian Müller-Schloer Alex Orailoglu Carlos Eduardo Pereira Thilo Pionteck Pascal Sainrat Toshinori Sato Martin Schulz Karsten Schwan Leonel Sousa Rainer Spallek Olaf Spinczyk Benno Stabernack

Walter Stechele Djamshid Tavangarian Jürgen Teich

Eduardo Tovar Pedro Trancoso Carsten Trinitis Martin Törngren Sascha Uhrig Theo Ungerer Hans Vandierendonck Stephane Vialle Lucian Vintan Klaus Waldschmidt Stephan Wong

#### **Additional Reviewers**

Ardeshiricham, Armaiti Backasch, Rico Blochwitz, Christopher Bradatsch, Christian Comprés Ureña, Isaías A. Eckert, Marcel Engel, Andreas Feng, Lei Gangadharan, Deepak Gottschling, Philip Grudnitsky, Artjom Guo, Qi Haas, Florian Universität zu Lübeck, Germany Leibniz Universität Hannover, Germany University of California, San Diego, USA Universidade Federal do Rio Grande do Sul, Brazil Universität zu Lübeck, Germany Université Toulouse III, France Fukuoka University, Japan Lawrence Livermore National Laboratory, USA Georgia Institute of Technology, USA Universidade de Lisboa, Portugal Technische Universität Dresden, Germany Technische Universität Dortmund, Germany Fraunhofer Institut für Nachrichtentechnik. Germany Technische Universität München, Germany Universität Rostock, Germany Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany CISTER/INESC TEC, ISEP, Portugal University of Cyprus, Cyprus Technische Universität München, Germany KTH Royal Institute of Technology, Sweden Technische Universität Dortmund, Germany Universität Augsburg, Germany **Oueen's University Belfast, UK** CentraleSupelec and UMI GT-CNRS 2958, France "Lucian Blaga" University of Sibiu, Romania Universität Frankfurt am Main, Germany Delft University of Technology, The Netherlands

> Habermann, Philipp Hassan, Ahmad Hempel, Gerald Hu, Sensen Huthmann, Jens Iacovelli, Saverio Jordan, Alexander Kantert, Jan Maia, Cláudio Meyer, Dominik Mische, Jörg Naji, Amine Nogueira, Luís

Pohl, Angela Preußer, Thomas Pyka, Arthur Sanz Marco, Vicent Schirmeier, Horst Shuka, Romeo Smirnov, Fedor Spiegelberg, Henning Westman, Jonas Yomsi, Patrick Zabel, Martin Zhang, Xinhai Zolda, Michael

## **Invited Talks**

## **Dr. Sandro D'Elia, European Commission Unit** "Complex Systems and Advanced Computing"

#### The Evolution of Computer Architectures: A view from the European Commission

Abstract of Talk: The changes in technology and market conditions have brought, in recent years, a significant evolution in the computer architectures. Multi-core chips force programmers to think parallel in any application domain, heterogeneous systems integrating different specialised processors are now the rule also in consumer markets, and energy efficiency is an issue across the entire computing spectrum from the wearable device to the high performance cluster. These trends pose significant issues: software development is a bottleneck because efficient programming for parallel and heterogeneous architectures is difficult, and application development remains a labour-intensive and expensive activity; non-deterministic timing in multicore chips poses a huge problem whenever a guaranteed response time is needed; software is typically not aware of the energy it uses, and therefore does not use hardware efficiently. Security is a cross-cutting problem, which in some cases is addressed through hardware-enforced "secure zones". This presentation discusses the recent evolution in computing architectures focusing on examples from European research and innovation projects, with a look forward to some promising innovations in the field like bio-inspired, probabilistic and approximate computing.

**Dr. Sandro D'Elia** is Project Officer at the European Commission Unit A/3 "Complex Systems & Advanced Computing". He spent a significant part of his career as IT project manager, first in the private sector and then in the IT service of the European Commission. In 2009 he moved to a position of research project officer. His role is evaluating, negotiating, controlling and supporting research and innovation projects financed by the European Commission, contributing to the drafting of the research and innovation work programme, and contributing to European policies on software, cyber-physical systems and advanced computing.

### Prof. Dr. Roman Obermaisser, University of Siegen

#### Architectures for Mixed-Criticality Systems Based on Networked Multi-Core Chips

Abstract of Talk: Mixed-criticality architectures with support for modular certification make the integration of application subsystems with different safety assurance levels both technically and economically feasible. Strict segregation of these subsystems is a key requirement to avoid fault propagation and unintended side-effects due to integration. Also, mixed-criticality architectures must deal with the heterogeneity of subsystems that differ not only in their criticality, but also in the underlying computational models and the timing requirements. Non safety-critical subsystems often demand adaptability and support for dynamic system structures, while certification standards impose static configurations for safety-critical subsystems. Several aspects such as time and space partitioning, heterogeneous computational models and adaptability were individually addressed at different integration levels including distributed systems, the chip-level and software execution environments. However, a holistic architecture for the seamless mixed-criticality integration encompassing distributed systems, multi-core chips, operating systems and hypervisors is an open research problem. This presentation discusses the state-of-the-art of mixed-criticality systems and presents research challenges towards a hierarchical mixed-criticality platform with support for strict segregation of subsystems, heterogeneity and adaptability.

**Prof. Dr. Roman Obermaisser** is full professor at the Division for Embedded Systems at University of Siegen in Germany. He has studied computer sciences at Vienna University of Technology and received the Master's degree in 2001. In February 2004, Roman Obermaisser has finished his doctoral studies in Computer Science with Prof. Hermann Kopetz at Vienna University of Technology as research advisor. In July 2009, Roman Obermaisser has received the habilitation ("Venia docendi") certificate for Technical Computer Science. His research work focuses on system architectures for distributed embedded real-time systems. He is the author of numerous conference and journal publications. He also wrote books on cross-domain system architectures for embedded systems, event-triggered and time-triggered control paradigms and time-triggered communication protocols. He has also participated in several EU research projects (e.g. DECOS, NextTTA, universAAL) and was the coordinator of the European research project DREAMS that will establish a mixed-criticality architecture for networked multi-core chips.

### Dr. Francisco Cazorla, Barcelona Supercomputing Center

#### Time Predictability in High-Performance Mixed-Criticality Multicore Systems

Abstract of Talk: While the search for high-performance will continue to be one of the main driving factors in computer design and development, there is an increasing need for time predictability across computing domains including high-performance (datacentre and supercomputers), handheld and embedded devices. The trend towards using computer systems to increasingly control essential aspects of human beings and the increasing connectivity across devices will naturally lead to situations in which applications - partially executed in handheld and datacentre computers, directly connect with more embedded critical systems such as cars or medical devices. The problem lies in the fact that high-performance is usually achieved by deploying aggressive hardware features (speculation, caches, heterogeneous designs) that negatively impact time predictability. The challenge lies on finding hardware/software designs that balance high-performance and time-predictability as needed by the application environment. In this talk I will focus on the increasing needs of time predictability in computing systems. I will present some of the main challenges in the design of multicores and manycores, widely deployed in the different computer domains, to provide increasing degrees of time predictability without significantly degrading average performance. I will present the work done in my research group in two different directions to reach this goal, namely, probabilistic multicore systems and the analysis of COTS multicore processors.

**Dr. Francisco J. Cazorla** is a researcher at the National Spanish Research Council (CSIC) and the leader of the CAOS research group (Computer Architecture - Operating System) at the Barcelona Supercomputing Centre (www.bsc.es/ caos). His research area covers the design for both high-performance and real-time systems. He has led several research projects funded by industry including several processor vendor companies (IBM, Sun microsystems) and the European Space Agency. He has also participated in European FP6 (SARC) and FP7 Projects (MERASA, parMERASA). He led the FP7 PROARTIS project and currently leads the FP7 PROXIMA project. He has co-authored over 70 papers in international refereed conferences and has several patents on the area.

## Contents

#### Hardware

| Parallel-Operation-Oriented Optically Reconfigurable Gate Array                                                                                                                                                                     | 3   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| SgInt: Safeguarding Interrupts for Hardware-Based I/O Virtualization<br>for Mixed-Criticality Embedded Real-Time Systems<br>Using Non Transparent Bridges<br>Daniel Münch, Michael Paulitsch, Oliver Hanka, and Andreas Herkersdorf | 15  |

| Design                                                                                                                                                                                                                              |     |

| Exploiting Outer Loops Vectorization in High Level Synthesis<br>Marco Lattuada and Fabrizio Ferrandi                                                                                                                                | 31  |

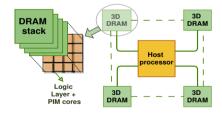

| Processing-in-Memory: Exploring the Design Space<br>Marko Scrbak, Mahzabeen Islam, Krishna M. Kavi, Mike Ignatowski,<br>and Nuwan Jayasena                                                                                          | 43  |

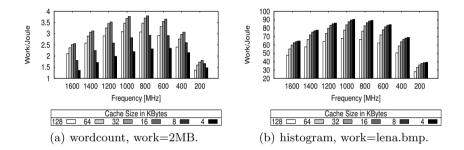

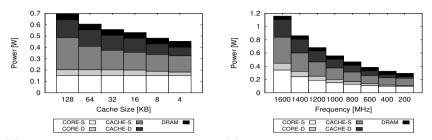

| Cache- and Communication-aware Application Mapping for Shared-cache<br>Multicore Processors                                                                                                                                         | 55  |

| Applications                                                                                                                                                                                                                        |     |

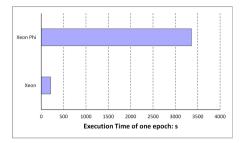

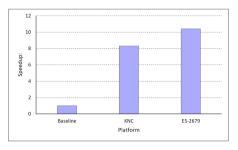

| Parallelizing Convolutional Neural Networks on Intel Many<br>Integrated Core Architecture<br>Junjie Liu, Haixia Wang, Dongsheng Wang, Yuan Gao, and Zuofeng Li                                                                      | 71  |

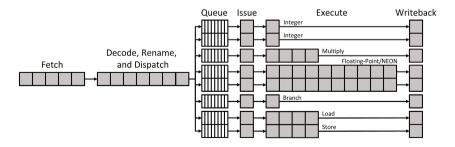

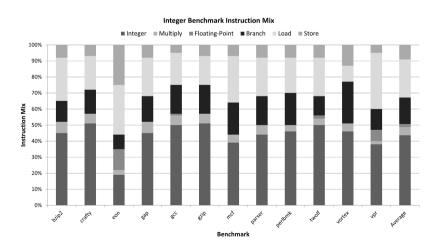

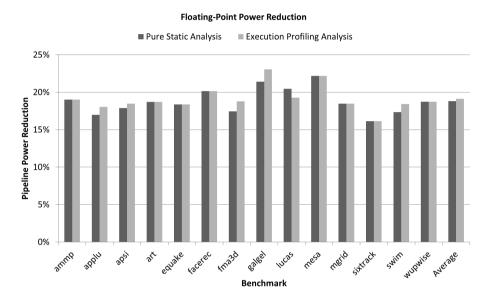

| Mobile Ecosystem Driven Dynamic Pipeline Adaptation for Low Power<br>Garo Bournoutian and Alex Orailoglu                                                                                                                            | 83  |

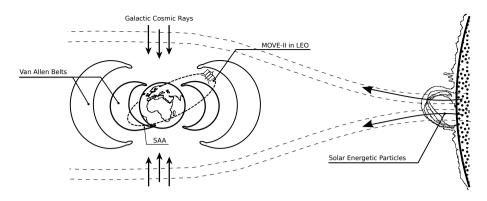

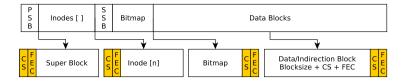

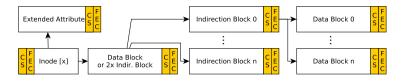

| FTRFS: A Fault-Tolerant Radiation-Robust Filesystem for Space Use<br>Christian M. Fuchs, Martin Langer, and Carsten Trinitis                                                                                                        | 96  |

| CPS-Xen: A Virtual Execution Environment for Cyber-Physical Applications                                                                                                                                                            | 108 |

Boguslaw Jablkowski and Olaf Spinczyk

#### **Trust and Privacy**

| Trustworthy Self-optimization in Organic Computing Environments<br>Nizar Msadek, Rolf Kiefhaber, and Theo Ungerer | 123 |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Improving Reliability and Endurance Using End-to-End Trust                                                        |     |

| in Distributed Low-Power Sensor Networks                                                                          | 135 |

| Jan Kantert, Sergej Wildemann, Georg von Zengen, Sarah Edenhofer,                                                 |     |

| Sven Tomforde, Lars Wolf, Jörg Hähner, and Christian Müller-Schloer                                               |     |

| Anonymous-CPABE: Privacy Preserved Content Disclosure                                                             |     |

| for Data Sharing in Cloud                                                                                         | 146 |

| S. Sabitha and M.S. Rajasree                                                                                      |     |

#### **Best Paper Session**

and Luís Miguel Pinho

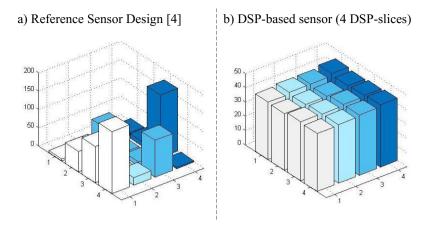

| A Synthesizable Temperature Sensor on FPGA Using DSP-Slices<br>for Reduced Calibration Overhead and Improved Stability<br><i>Christopher Bartels, Chao Zhang, Guillermo Payá-Vayá, and Holger Blume</i> | 161 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

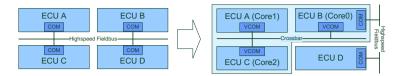

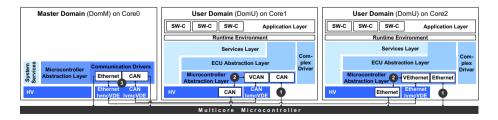

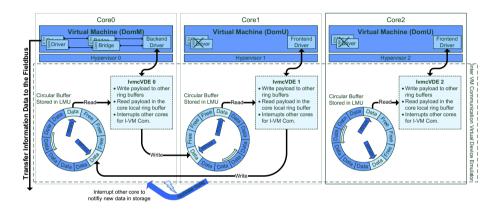

| Virtualized Communication Controllers in Safety-Related Automotive<br>Embedded Systems<br>Dominik Reinhardt, Maximilian Güntner, and Simon Obermeir                                                     | 173 |

| Network Interface with Task Spawning Support for NoC-Based DSM<br>Architectures                                                                                                                         | 186 |

| Real-Time Issues                                                                                                                                                                                        |     |

| Utility-Based Scheduling of $(m, k)$ -Firm Real-Time Task Sets Florian Kluge, Markus Neuerburg, and Theo Ungerer                                                                                        | 201 |

| MESI-Based Cache Coherence for Hard Real-Time Multicore Systems<br>Sascha Uhrig, Lillian Tadros, and Arthur Pyka                                                                                        | 212 |

| Allocation of Parallel Real-Time Tasks in Distributed Multi-core<br>Architectures Supported by an FTT-SE Network<br><i>Ricardo Garibay-Martínez, Geoffrey Nelissen, Luis Lino Ferreira,</i>             | 224 |

Speeding up Static Probabilistic Timing Analysis236Suzana Milutinovic, Jaume Abella, Damien Hardy, Eduardo Quiñones,<br/>Isabelle Puaut, and Francisco J. Cazorla236

| Author ] | Index | <br> | <br> | 249 |

|----------|-------|------|------|-----|

| Author ] | Index | <br> | <br> | 249 |

## Hardware

## Parallel-Operation-Oriented Optically Reconfigurable Gate Array

Takumi Fujimori and Minoru Watanabe<sup>(⊠)</sup>

Electrical and Electronic Engineering, Shizuoka University, 3-5-1 Johoku, Hamamatsu, Shizuoka 432-8561, Japan tmwatan@ipc.shizuoka.ac.jp

Abstract. Recently, studies exploring acceleration of software operations on a processor have been undertaken aggressively using field programmable gate arrays (FPGAs). However, currently available FPGA architectures present waste occurring with parallel operation in terms of configuration memory because the same configuration context corresponding to same-function modules must be programmed onto numerous configuration memory parts. Therefore, a parallel-operation-oriented FPGA with a single shared configuration memory for some programmable gate arrays has been proposed. Here, the architecture is applied for optically reconfigurable gate arrays (ORGA). To date, the ORGA architecture has demonstrated that a high-speed dynamic reconfiguration capability can increase the performance of its programmable gate array drastically. Software operations can be accelerated using an ORGA. This paper therefore presents a proposal for combinational architecture of the parallel-operation oriented FPGA architecture and a high-speed reconfiguration ORGA. The architecture is called a parallel-operationoriented ORGA architecture. For this study, a parallel-operation-oriented ORGA with four programmable gate arrays sharing a common configuration photodiode-array has been designed using  $0.18 \,\mu m$  CMOS process technology. This study clarified the benefits of the parallel-operationoriented ORGA in comparison with an FPGA having the same gate array structure, produced using the same process technology.

#### 1 Introduction

Recently, studies of acceleration of software operations on a processor have been executed aggressively using general-purpose computing on graphics processing units (GPGPUs) [1]–[3] and using field programmable gate arrays (FPGAs) [4]–[6]. Particularly, along with the increasing size of FPGAs, many FPGA hardware acceleration results have been reported. According to several reports, FPGA acceleration is suitable for fluid analysis, electromagnetic field analysis, image processing operation, game solvers, and so on. The importance of FPGA hardware acceleration of software operations therefore appears to be increasing.

Actually, FPGA programmability can be achieved based on a look-up table (LUT) and switching matrix (SM) architecture. For that architecture, FPGA performance is always inferior to that of custom VLSIs since a circuit implemented onto a LUT is always slower than the corresponding custom logic circuit

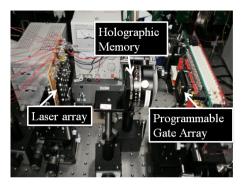

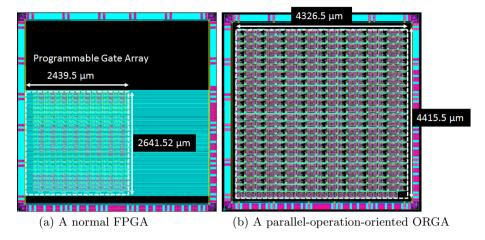

Fig. 1. Photograph of an optically reconfigurable gate array (ORGA) with 16 configuration contexts

and because the path delay of SMs on FPGA is greater than that of simple metal wires on custom VLSIs. When implementing processors, the clock frequency of the soft core processor on FPGA is always about a tenth of the frequency of custom processors having the same process technology as that of the FPGA [7][8][9].

Nevertheless, many high-performance FPGA implementations that are superior to the performance of the latest processors and the latest GPGPUs on personal computers have been reported. In such cases, the architecture invariably uses a massively parallel operation. Although the clock frequency of a single unit on an FPGA is lower than that of Intel's processors, the total performance of the parallel operation overcomes the processors. Therefore, when an FPGA is used as a hardware accelerator the architecture must become a parallel operation.

However, a main concern of a parallel operation on FPGA is that the same configuration context corresponding to the same-function modules must be programmed onto many parts of the configuration memory. Currently available FPGAs are designed as general-purpose programmable gate arrays so that all logic blocks, switching matrices, and so on can be programmed individually. Such an architecture is wasteful when functioning under parallel operation.

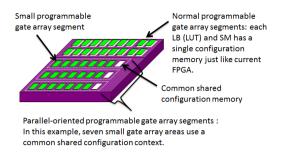

A better structure in the case of implementing a number of identical circuits onto LUTs and SMs is to share a common configuration memory for a parallel operation. Consequently, the amount of configuration memory can be decreased so that a larger programmable gate array can be realized on a die of the same size. Therefore, a parallel-operation-oriented FPGA that has a single shared configuration memory for some programmable gate arrays has been proposed [10]. The gate density can be increased by sharing configuration memory compared with general-purpose FPGAs.

Here, the parallel-operation-oriented FPGA architecture is applied for optically reconfigurable gate arrays (ORGAs). An ORGA consists of a holographic memory, a laser array, and an optically programmable gate array, as shown in Fig. 1 [11]–[15]. The ORGA can have over 256 reconfiguration contexts inside a holographic memory, which can be implemented dynamically onto an optically programmable gate array at every 10 ns. To date, ORGA architecture has

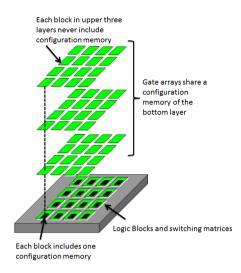

Fig. 2. Parallel-operation-oriented FPGA architecture including four common programmable gate arrays in which four parallel operations can be implemented

demonstrated that such high-speed dynamic reconfiguration capability can increase the performance of its programmable gate array drastically. Using the high-speed dynamic reconfiguration, simple circuits with a few functions can be implemented onto a programmable gate array. Change of the function can be accomplished using high-speed dynamic reconfiguration. Simple function requires only a small implementation area so that a large parallel computation can be realized. Therefore, a software operation can be accelerated drastically by exploiting the high-speed dynamic reconfiguration of ORGAs. Moreover, if the parallel-operation-oriented FPGA architecture is applied to ORGA, then the acceleration power or the number of parallel operation units is increased extremely.

This report therefore presents a proposal for a combined architecture of the parallel-operation oriented FPGA architecture and a high-speed reconfiguration ORGA. The architecture, called a parallel-operation-oriented ORGA architecture, includes a shared common configuration architecture. For this study, a parallel-operation-oriented ORGA with four programmable gate arrays sharing a common configuration photodiode-array has been designed using 0.18  $\mu$ m CMOS process technology. The benefits of the parallel-operation-oriented ORGA were clarified in comparison with an FPGA having the same gate array structure and the same process technology.

#### 2 Parallel-Operation-Oriented ORGA Architecture

#### 2.1 Parallel-Operation-Oriented FPGA Architecture

Under current general-purpose FPGA architectures, each logic block, switching matrix, I/O block, block RAM, and so on includes a configuration memory

6

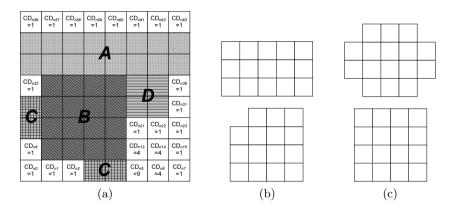

Fig. 3. Hybrid architecture including the parallel-operation-oriented FPGA architecture and current general-purpose FPGA architecture

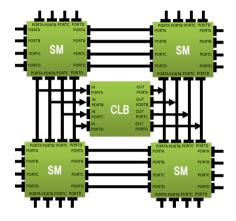

individually. However, in an FPGA accelerator, for example, in uses for fluid analysis, electromagnetic field analysis, image processing operation, and game solvers, numerous units with the same function are used. In this case, each function should use a shared configuration memory to increase the gate density of a programmable gate array. Therefore, a parallel-operation-oriented FPGA architecture with a common shared configuration memory has been proposed as shown in Fig. 2.

Figure 2 presents one example of a parallel-operation-oriented FPGA architecture including four common programmable gate arrays in which four parallel operations can be implemented. Of course, the number of common programmable gate arrays depends on the target application. For example, a game solver invariably uses numerous common evaluation modules. In this case, a programmable gate array partly including 10 common programmable gate array areas might be suitable for the application. As a result, the amount of configuration memory inside an FPGA can be decreased so that the gate array density can be increased.

Figure 3 shows that the parallel-operation-oriented FPGA architecture should be used along with a current general-purpose FPGA architecture. A suitable implementation is that a part is designed as parallel-operation-oriented FPGA architecture. The remainder should be current general-purpose FPGA architecture. Therefore, a system includes both a parallel operation part and a dedicated operation part. The ratio of a parallel operation part to a dedicated operation part also depends on the target application.

#### 2.2 Parallel-Operation-Oriented ORGA Architecture

To date, ORGA architecture has demonstrated that a high-speed dynamic reconfiguration capability can increase its programmable gate array performance drastically. If a high-speed reconfiguration is possible on a programmable gate array, then a single-function unit can be implemented. Multi-functionality can be achieved by reconfiguring the hardware itself. Such single-function unit works at the highest clock frequency. Numerous units can be implemented onto a small implementation area compared with a general-purpose multi-function unit with numerous functions because the complexity and size of units is smaller and

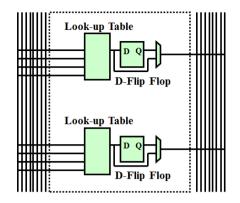

Fig. 4. Construction of a logic block

Fig. 5. Connection of logic blocks and switching matrices

simpler than those of multi-function units. Therefore, the performance can be increased compared with static uses of current FPGAs.

Moreover, an ORGA can support a high-speed dynamic reconfiguration. Its reconfiguration period is less than 10 ns. The number of reconfiguration contexts is at least 256. In the future, the number of configuration contexts on an ORGA will be increased to a million configuration contexts. For the goal of realizing numerous reconfiguration contexts, studies of new ORGAs have been progressing. Therefore, ORGA is extremely useful to accelerate a software operation on a processor. Additionally, the parallel-operation-oriented FPGA architecture is useful to increase the number of parallel operations on a gate array or the gate density of an ORGA under a parallel operation can be increased. In this study, a parallel-operation-oriented ORGA with four programmable gate arrays sharing a common configuration photodiode-array has been designed using 0.18  $\mu$ m CMOS process technology.

| Technology               | $0.18 \ \mu m$ double-poly       |

|--------------------------|----------------------------------|

|                          | 5-metal CMOS process             |

| Chip size                | $5.0 \times 5.0 \ mm^2$          |

| Supply Voltage           | Core 1.8V, I/O 3.3V              |

| Photodiode size          | $4.40 \times 4.45 \ \mu m^2$     |

| Photodiode response time | < 5  ns                          |

| Sensitivity              | $2.12 \times 10^{-14} \text{ J}$ |

| Distance between         |                                  |

| Photodiodes              | h.=30.08, v.= 20.16 $[\mu m]$    |

| Number of                |                                  |

| Photodiodes              | 25,056                           |

| Number of                |                                  |

| Logic Blocks             | 736                              |

| Number of                |                                  |

| Switching Matrices       | 828                              |

| Number of Wires          |                                  |

| in a Routing Channel     | 8                                |

| Number of                |                                  |

| I/O blocks               | 16 (64  bit)                     |

| Gate Count               | 25,024                           |

|                          |                                  |

Table 1. Specifications of a parallel-operation-oriented optically reconfigurable gate array

#### 3 VLSI Design of a Parallel-Operation-Oriented ORGA

#### 3.1 Entire VLSI Design

Here, a parallel-operation-oriented ORGA with four programmable gate array sharing a configuration architecture was designed using 0.18  $\mu$ m standard complementary metal oxide semiconductor (CMOS) process technology. The ORGA-VLSI specifications are shown in Table 1. In an ORGA, a configuration context is provided optically from a holographic memory. Therefore, an ORGA has numerous photodiodes to detect the configuration context, as shown in Table 1. The number of photodiodes corresponds to the number of configuration bits. In this design, 25,056 photodiodes were implemented for programming a programmable gate array. All blocks of the programmable gate array can be reconfigured at once. In this design, the ORGA has four programmable gate array planes which share the single configuration photodiode architecture of the 25,056 photodiodes. Each programmable gate array plane has 184 optically reconfigurable logic blocks and 207 optically reconfigurable switching matrices. The programmable gate array works along with the same configuration information based on a single photodiode configuration system.

#### 3.2 Optically Reconfigurable Logic Block

Figure 4 shows that each logic block on a programmable gate array plane has two four-input look-up tables (LUTs) and two delay-type flip flops. An optically

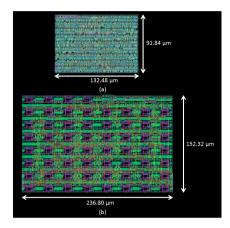

Fig. 6. CAD Layouts of logic blocks of (a) a comparison target design of a current general-purpose FPGA including a single programmable gate array and (b) a parallel-operation-oriented ORGA including four banks sharing a common configuration photodiode

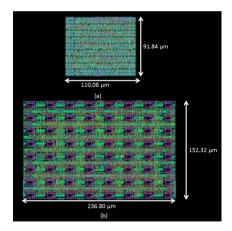

**Fig. 7.** CAD Layout of a switching matrix of (a) a comparison target design of a current general-purpose FPGA including a single programmable gate array and (b) a parallel-operation-oriented ORGA including four banks sharing a common configuration photodiode

reconfigurable logic block cell has four logic blocks. The four logic blocks share the same configuration context so that they can be reconfigured using 60 photodiodes. The CAD layout of the optically reconfigurable logic block is portrayed in Fig. 6(b). Therefore, all four logic blocks can be reconfigured at once and can function as the same circuit, although the input signals for logic blocks mutually differ. Figure 5 shows that the optically reconfigurable logic block cell has four output ports and four input ports for four programmable gate array planes.

**Fig. 8.** CAD Layouts of (a) a comparison design of a current general-purpose FPGA and (b) a parallel-operation-oriented ORGA including four programmable gate arrays sharing a common configuration context

#### 3.3 Optically Reconfigurable Switching Matrix

In addition, the optically reconfigurable switching matrix was designed as having four direction connections. Each switching matrix is connected for each direction to another one with eight wires. An optically reconfigurable switching matrix has 64 photodiodes for configuration procedures. The CAD layout of the optically reconfigurable switching matrix cell is portrayed in Fig. 7(b). The optically reconfigurable switching matrix cell has four switching matrices for four programmable gate arrays. Therefore, as shown in Fig. 5, each direction of the optically reconfigurable switching matrix cell has four ports for four programmable gate array planes.

#### 3.4 Gate Array Design

Each photodiode was designed to be  $4.40 \times 4.45\mu$ m. The photodiode sensitivity was estimated experimentally as  $2.12 \times 10^{-14}$  J. Even if reconfiguration can be executed constantly at 100 MHz, the necessary optical power for the configuration procedure is about 26.6 mW. Therefore, the configuration power consumption of the ORGA-VLSI can be estimated as low. Each logic block is surrounded by four switching matrices connecting eight wiring channels as an island style gate array. Since a parallel-operation-oriented ORGA has four of the same programmable gate arrays sharing a configuration architecture, in all, it has 736 logic blocks and 828 switching matrices. In this design, the number of I/O bits was limited to 64 bits because of chip package issues. The gate count reaches 25,024 gates. The CAD layout of the programmable gate array is presented in Fig. 8. The chip size is 5 mm × 5 mm. All gate array parts were designed using standard cells, except for a photodiode cell. The photodiode cell was designed

| Туре                                       | Current FPGA                    | Parallel-operation-oriented ORGA |

|--------------------------------------------|---------------------------------|----------------------------------|

| Number of functions                        | Single function                 | 4 functions                      |

|                                            | (368  LUTs)                     | (1,472  LUTs)                    |

| Size of a Logic Block                      | $132.48 \times 91.84 \ \mu m^2$ | $236.80 \times 152.32 \ \mu m^2$ |

| Size of a Switching Matrix                 | $110.08 \times 91.84 \ \mu m^2$ | $236.80 \times 152.32 \ \mu m^2$ |

|                                            | $106.88 \times 91.84 \ \mu m^2$ | $236.80 \times 152.32 \ \mu m^2$ |

| Size of a gate array (184 LBs and 207 SMs) | $6,443,988 \ \mu m^2$           | $19,103,661 \ \mu m^2$           |

| Number of LUTs / $mm^2$                    | 57.1                            | 77.1                             |

Table 2. Results of gate density comparisons

Table 3. Results of comparing the operating clock frequency of a seven-stage ring oscillator

| Туре                      | Current FPGA                       | Parallel-operation-oriented ORGA   |

|---------------------------|------------------------------------|------------------------------------|

| Number of functions       | Single function                    | 4 functions                        |

| Operating clock frequency | 43.71 MHz                          | 72.78 MHz                          |

| Gate array performance    | $2.50 \times 10^9$                 | $5.61 \times 10^9$                 |

| / second $\cdot mm^2$     | LUT operations / sec. $\cdot mm^2$ | LUT operations / sec. $\cdot mm^2$ |

| Performance ratio         | 1                                  | 2.24                               |

Table 4. Results of comparing the leakage power consumption

| Туре                | Current FPGA    | Parallel-operation-oriented ORGA |

|---------------------|-----------------|----------------------------------|

| Number of functions | Single function | 4 functions                      |

| Leakage Power       | $6.14 \ \mu W$  | $7.38 \ \mu W$                   |

as full-custom. The gate array design was synthesized using a logic synthesis tool (Design Compiler: Synopsys Inc.). In addition, as a place and route tool, IC compiler (Synopsys Inc.) was used. Voltages of the core and I/O are 1.8 V and 3.3 V, respectively. Currently, to facilitate optical experiments, the ORGA photodiode size and space between the photodiodes were designed as large. Therefore, since the ORGA-VLSI design has spaces and the density of the logic cells is not maximum, the cell sizes of the logic block and the switching matrix of the ORGA-VLSI were larger than those of the comparison-target FPGA.

#### 3.5 Comparison Target Design

Additionally, here, as a comparison target, a normal FPGA was also designed with the same 0.18  $\mu$ m standard CMOS process technology. The FPGA has a single programmable gate array, which is the same structure as the ORGA design and the configuration memory above. Since the FPGA has only one programmable gate array plane, the gate array has 184 logic blocks and 207 switching matrices. Of course, the logic block structure and switching matrix structure are also the same. The CAD layouts of a logic block and a switching matrix are shown respectively in Fig. 6(a) and Fig. 7(a).

### 4 Evaluation Results

#### 4.1 Gate Density

The implementation results of the parallel-operation-oriented ORGA and the comparison target FPGA are presented in Table 2. Figures 6, 7, and 8 show that the implementation area of the ORGA-VLSI is larger than that of the comparison target FPGA. The gate array's implementation area of the paralleloperation-oriented ORGA is 19.103.661  $\mu m^2$ . However, the ORGA-VLSI includes four-times the gate array or four planes of programmable gate arrays. Therefore, a single programmable gate array corresponding to the comparison target FPGA has been implemented on only  $4,775,915 \ \mu m^2$ . The implementation area is smaller than 6,443,988  $\mu$ m<sup>2</sup> of the comparison target FPGA. Estimating the gate density, the number of LUTs  $/ \text{ mm}^2$  of the parallel-operation-oriented ORGA and the comparison target FPGA are 77.1 and 57.1, respectively, because the programmable gate arrays of the parallel-operation-oriented ORGA and the comparison target FPGA respectively have 1,472 LUTs and 368 LUTs. Therefore, the gate density of the parallel-operation-oriented ORGA is higher than that of the comparison target FPGA, meaning that the ORGA-VLSI can execute larger operations than the comparison target FPGA.

#### 4.2 Propagation Delay

Next, the operation clock frequencies of the parallel-operation-oriented ORGA and the comparison target FPGA were measured as results show in Table 3. The results are based on IC compiler generated SDF information and the corresponding HDL simulation. Here, a seven-stage ring oscillator has been implemented onto both ORGA-VLSI and FPGA. The operating clock frequencies of the parallel-operation-oriented ORGA and the comparison target FPGA were 72.78 MHz and 43.71 MHz. The results show that the operation on an ORGA can be done faster than on the comparison target FPGA. Currently, the comparison target FPGA was designed to be as small as possible. Therefore, although FPGA is small, the gate array performance is lower. Of course, the performance of the comparison target FPGA can be improved through future development. However, even if the performance of an ORGA becomes lower than that of current FPGA design, a parallel-operation-oriented ORGA has advantages under parallel operation because the number of programmable gate array planes can be increased easily. Anyway, the performance of the parallel-operation-oriented ORGA is higher than that of current FPGAs. The total performance per square millimeter of the parallel-operation-oriented ORGA was 2.24 times higher than that of the comparison-target FPGA. In another example, the 4-bit multiplier circuit works at 80.13 MHz. The working speed can be regarded as sufficient under the current 0.18  $\mu$ m standard CMOS process technology.

#### 4.3 Power Consumption Estimation

The leakage power consumption generated by the IC compiler is presented in Table 4. The leakage power consumption of the parallel-operation-oriented ORGA is slightly higher than that of the comparison target FPGA. However, the leakage power consumption per single programmable gate array is decreased drastically compared with the comparison target FPGA because the ORGA-VLSI includes four programmable gate arrays. Considering a single programmable gate array, the leakage power consumption is estimated as  $1.85 \ \mu$ W. Therefore, the leakage power consumption per programmable gate array of the parallel-operation-oriented ORGA is sufficiently smaller than the comparison target FPGA. The major component of the latest VLSI's power consumption is leakage power consumption. The result implies that when the ORGA-VLSI chooses the latest VLSI technology in the future, the power consumption of the parallel-operation-oriented ORGA is sufficiently lower than that of currently available FPGAs.

#### 5 Conclusion

An accelerator using an FPGA must always use a massively parallel operation to constitute a high-performance system. The configuration memory of currently available FPGA architecture is wasted under parallel operation because the same configuration context corresponding to same-function modules must be programmed onto numerous parts of the configuration memory. Therefore, a parallel-operation-oriented FPGA with a single shared configuration memory has been proposed for some programmable gate arrays.

On the other hand, ORGA architecture has demonstrated that its high-speed dynamic reconfiguration capability can increase the number of parallel operations on its programmable gate array drastically. If both architectures could be implemented onto a single system, then numerous parallel operations would be realized.

This report has presented a proposal of a parallel-operation-oriented ORGA architecture including a shared common configuration photodiode architecture. In addition, a parallel-operation-oriented ORGA was designed using the same 0.18  $\mu$ m process technology. Results show that the parallel-operation-oriented ORGA architecture presents benefits in terms of performance and power consumption related to the leak current, compared with current general-purpose FPGAs, which was also designed with the same 0.18  $\mu$ m process technology and the same FPGA architecture. The performance per unit area of the parallel-operation-oriented ORGA is 2.24 times higher than that of a comparison-target FPGA. When using a parallel operation on an ORGA, the architecture is well-suited to realizing a high-performance system. The parallel-operation-oriented ORGA architecture is also well-suited to future three-dimensional VLSI technologies.

Acknowledgments. This research was partly supported by Nuclear Safety Research & Development Center of the Chubu Electric Power Corporation. The VLSI chip in this study was fabricated in the chip fabrication program of VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Rohm Co. Ltd. and Toppan Printing Co. Ltd.

#### References

- 1. Archirapatkave, V., Sumilo, H., See, S.C.W., Achalakul, T.: GPGPU acceleration algorithm for medical image reconstruction. In: IEEE International Symposium on Parallel and Distributed Processing with Applications, pp. 41–46 (2011)

- Unno, M., Inoue, Y., Asar, H.: GPGPU-FDTD method for 2-dimensional electromagnetic field simulation and its estimation. In: IEEE Conference on Electrical Performance of Electronic Packaging and Systems, pp. 239–242 (2009)

- Lezar, E., Jakobus, U.: GPU-acceleration of the FEKO electromagnetic solution kernel. In: International Conference on Electromagnetics in Advanced Applications, pp. 814–817 (2013)

- Sano, K., Hatsuda, Y., Yamamoto, S.: Multi-FPGA Accelerator for Scalable Stencil Computation with Constant Memory Bandwidth. IEEE Transactions on Parallel and Distributed Systems 25(3), 695–705 (2014)

- Saidani, T., Atri, M., Said, Y., Tourki, R.: Real time FPGA acceleration for discrete wavelet transform of the 5/3 filter for JPEG 2000. In: International Conference on Sciences of Electronics, Technologies of Information and Telecommunications, pp. 393–399 (2012)

- Durbano, J.P., Ortiz, F.E.: FPGA-based acceleration of the 3D finite-difference time-domain method. In: IEEE Symposium on Field-Programmable Custom Computing Machines, pp. 156–163 (2004)

- Sheldon, D., Kumar, R., Lysecky, R., Vahid, F., Tullsen, D.: Application-specific customization of parameterized FPGA soft-core processors. In: IEEE/ACM International Conference on Computer-Aided Design, pp. 261–268 (2006)

- Zhen, Z., Guilin, T., Dong, Z., Zhiping, H.: Design and realization of the hardware platform based on the Nios soft-core processor. In: International Conference on Electronic Measurement and Instruments, pp. 4–865-4-869 (2007)

- Hubner, M., Paulsson, K., Becker, J.: Parallel and flexible multiprocessor systemon-chip for adaptive automotive applications based on Xilinx MicroBlaze soft-cores. In: IEEE International Parallel and Distributed Processing Symposium, p. 149a (2005)

- Watanabe, M.: A parallel-operation-oriented FPGA architecture. In: International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies, pp. 123–126 (2014)

- 11. Kubota, S., Watanabe, M.: A four-context programmable optically reconfigurable gate array with a reflective silver-halide holographic memory. IEEE Photonics Journal **3**(4), 665–675 (2011)

- Nakajima, M., Watanabe, M.: Fast optical reconfiguration of a nine-context DORGA using a speed adjustment control. ACM Transaction on Reconfigurable Technology and Systems 4(2), 1–21 (2011). Article 15

- Seto, D., Nakajima, M., Watanabe, M.: Dynamic optically reconfigurable gate array very large-scale integration with partial reconfiguration capability. Applied Optics 49(36), 6986–6994 (2010)

- Morita, H., Watanabe, M.: Microelectromechanical Configuration of an Optically Reconfigurable Gate Array. IEEE Journal of Quantum Electronics 46(9), 1288–1294 (2010)

- Nakajima, M., Watanabe, M.: A four-context optically differential reconfigurable gate array. IEEE/OSA Journal of Lightwave Technology 27(20), 4460–4470 (2009)

## SgInt: Safeguarding Interrupts for Hardware-Based I/O Virtualization for Mixed-Criticality Embedded Real-Time Systems Using Non Transparent Bridges

Daniel Münch<sup>1( $\boxtimes$ )</sup>, Michael Paulitsch<sup>1</sup>, Oliver Hanka<sup>1</sup>, and Andreas Herkersdorf<sup>2</sup>

<sup>1</sup> Airbus Group Innovation, Munich, Germany {Daniel.Muench,Michael.Paulitsch,Oliver.Hanka}@airbus.com

<sup>2</sup> Institute for Integrated Systems, TU München, Munich, Germany herkersdorf@tum.de

Abstract. Safety critical systems and in particular higher functional integrated systems like mixed-criticality systems in avionics require a safeguarding that functionalities cannot interfere with each other. A notably underestimated issue are I/O devices and their (message-signaled) interrupts. Message-signaled interrupts are the omnipresent type of interrupts in modern serial high-speed I/O subsystems. These interrupts can be considered as small DMA write packets. If there is no safeguarding for interrupts, an I/O device associated with a distinct functionality can trigger any interrupt or manipulate any control register like triggering reset of all processing cores to provoke a complete system failure. This is a particular issue for available embedded processor architectures, since they do not provide adequate means for interrupt separation like an IOMMU with a granularity sufficient for interrupts.

This paper presents the SgInt concept to enable the safeguarding of interrupts for hardware-based I/O virtualization for safety-critical and mixed-criticality embedded real-time systems using non-transparent bridges in single (multi-core) processor systems and multi (multi-core) processor systems. The advantage of this SgInt concept is that it is an general and reusable interrupt separation solution which is scalable from a single (multi-core) processor to a multi (multi-core) processor system and builds on available COTS chip solutions. It allows to upgrade spatial separation for interrupts to available processors having no means for interrupt separation. A practical evaluation shows that the SgInt concept provides the required spatial separation and even slightly outperforms state-of-the-art doorbell interrupt handling in transfer time and transfer rate (by about 0.04%).

#### 1 Introduction

Driven by the demand for more and more functionality, there is a trend in avionics similar to other field of electronics to a higher functional integration. To save space, weight and power, functionalities are integrated onto one computing platform. This trend is pushed further by integrating functionalities of different criticality levels onto the same platform to so called mixed-criticality systems.

Functionalities of different criticality levels on one shared (multi-core) platform require that these functionalities cannot interfere with each other or with the entire system. To manage this interference issue, temporal separation and spatial separation are essential to grant a safe and secure system operation. The Input/Output (I/O) subsystem is a central part, because almost every function needs I/O for its operation. Since I/O is an often underestimated problem, this paper focuses on I/O. Temporal separation means having separation in the time domain. For example, it is guaranteed that an I/O device has a granted transfer rate or maximum transfer time [1]. Spatial separation means having separation in the address space domain. For example, it is assured that an I/O device only writes into a distinct address range or memory area belonging to a distinct functionality or application [2]. A particularly underestimated issue in I/O handling are (message-signaled) interrupts. Message-signaled interrupts are the ubiquitous type of interrupts in modern memory-mapped I/O subsystems and can be considered as small Direct Memory Access (DMA) write packets (e.g. with only 4 Byte payload). If there is no spatial separation for interrupts, an erroneous I/O device can trigger any interrupt of the system-on-chip of the processor or manipulate any memory-mapped control register like triggering reset of all processing cores. Such a situation could lead to a complete system failure [2] [3]. Therefore, it is common in today's avionics and similar highly safety-critical systems to effectively turn off all interrupts and handle I/O via polling. This is a very resource-consuming and ineffective, but a safe approach to solve the problem. Further constraints are the use of Commercial Of–The–Shelf (COTS) components, low complexity, determinism and predictability (cf. Section 3).

The challenge is that available embedded processor architectures do not offer spatial separation means for interrupts like an Input/Output Memory Management Unit (IOMMU) with sufficiently fine granularity (cf. Section 3 and [2]). Server or high-end workstation processor architectures providing such means (cf. Section 2 and [4] [5]) are not usable for embedded real-time systems because of size, weight, power, cooling, harsh environmental conditions, certification considerations, etc. Further constraints are the use of Commercial Off–The–Shelf (COTS) components. This is essential to keep costs low for products with low piece numbers / volume like aircraft. A fully customized design of a processor chip or system-on-chip is economically infeasible. For these reasons, this paper does not discuss the design of interrupt controllers or IOMMUs. Instead, it focuses on an approach to extend available embedded COTS processors or system-on-chip by additional means to provide spatial separation for interrupts with the least possible impact on performance.

The contribution of the Safeguarding Interrupts (SgInt) concept of this paper is an efficient, high-performance and safe interrupt handling approach for highly safety-critical systems. It enables spatial separation at interrupt level in systems that does not have already built-in means. This concept is a reusable and general solution, which is scalable from a single (multi-core) processor to a multi (multi-core) processor system and builds on available COTS chip solutions. The SgInt concept uses a source / origin ID check in the Non-Transparent Bridge (NTB) with an exclusive address range within the NTB aperture for interrupts of one distinct I/O device in combination with a dedicated alias page in the processor only containing the interrupt triggering register as mapping target. Furthermore, the paper contributes a implementation and an application of the SgInt concept in context of hardware-based I/O virtualization (cf. Section 2). The result of the presented practical evaluation is that the performance in terms of transfer time and transfer rate of the SgInt concept is by about 0.04% better than state-of-the-art doorbell interrupt handling.

To our best knowledge, we are the first to discuss an interrupt separation solution for single (multi-core) processor systems and multi (multi-core) processor systems in mixed-criticality embedded real-time systems that do not provide adequate means for interrupt separation.

#### 2 Related Work

The application context of this paper is hardware-based I/O virtualization (cf. [1,2,6]). This is the hardware-managed sharing of I/O in virtualized embedded systems. Virualized embedded systems are systems where multiple virtual machines or application partitions are running on a shared computing platform managed by virtual machine manager or hypervisor. The key point is that the sharing or virtualization management is offloaded to hardware. This hardware management provides a Physical Function (PF) (management interface) and several Virtual Functions (VFs) interfaces (application interfaces) [7]. A memory-mapped I/O like PCI Express (PCIe) serves as basic I/O technology. This allows to map the PF to a control partition or hypervisor. The VFs are mapped to the corresponding application partitions. Already available means for memory management and mapping like Memory Management Unit (MMU) and IOMMU ensure the spatial separation between the application partitions and I/O interfaces.

Non-transparent bridging in context of PCIe is the non-transparent connection of two dedicated tree-like (single-root) PCIe hierarchies or address spaces together to enable multiple processors to communicate and exchange data [8]. A (single-root) PCIe hierarchy or address space is a tree-like topology with maximally one Central Processing Unit (CPU), master or root. Therefore, a communication between two root or CPUs is originally not possible. To solve this issue, an NTB connects two PCIe hierarchies by presenting itself as an end-point to both PCIe hierarchies. An NTB is constructed by two end-points back to back with an address translation functionality. Each side of an NTB opens an address window (aperture) from one PCIe single root hierarchy to the other PCIe single root hierarchy. The behavior of an NTB is considered as non-transparent, since the NTB and its address translation feature has to be setup before it allows to exchange data. It is not checked if a device or function is allowed to transfer data to a distinct destination. Interrupts are transferred over an NTB by the so-called doorbell mechanism. This mechanism consumes the interrupt on the first side of the NTB and newly generates the interrupt on the second side and transmits it to the processing unit. It is not checked if a device or function is allowed to trigger an interrupt. The current concept uses NTB technology in a different way than formerly intended to enable multi-processor communication. It extends NTBs to enable spatial separation for interrupts of shared PCIe devices in a single (multi-core) processor or multi (multi-core) processor system.

[9] uses PCIe interconnect, NTB and Intel VT-d to share a PCIe Single Root I/O Virtualization (SR-IOV) network card among multiple Intel Xeon hosts in the IT-server domain. It is suggested to use a dedicated address window in the NTB to transfer interrupts from one NTB side to the other instead of using the doorbell mechanism to improve performance. The interrupt remapping feature of Intel VT-d – the Intel implementation of an IOMMU – is able to check if a device or function is allowed to trigger an interrupt [4] [10]. AMD provides a similar technology as part of AMD-Vi or AMD IOMMU [5] [11] [12]. In contrast to this, the current paper uses PCIe interconnect, NTB technology without an IOMMU – like Intel VT-d – to share a PCIe SR-IOV or PCIe multifunction device while still providing spatial separation for data transactions and interrupts in a mixed-criticality real-time embedded system. The current concept presents a more general interrupt separation solution, which does not rely on special interrupt separating features of Intel VT-d or AMD IOMMU.

[6] uses NTB technology to emulate an external IOMMU to provide spatial separation for data transactions of I/O devices like the separation feature of an IOMMU for a single (multi-core) computing host lacking an IOMMU. It is enforced that transactions (for example a DMA write) initiated by I/O device(s) flow over the NTBs. The control engine in the NTB checks the target address and source / origin ID (e.g. PCIe ID) of these transactions. A rule set in the control engine (e.g. white list) decides whether to block the transaction or pass the transaction and translate the target address to the defined target address in the (bus) address space on the other side of the NTB. [13] extends this idea to provide spatial separation for sharing I/O devices among multi (multi-core) processor systems which usually do not have means for separation like an IOMMU. The current paper extends this approach to increase the separation granularity further to provide spatial separation also for interrupts of I/O devices in a single (multi-core) processor system as well as a multi (multi-core) processor system, whose processors lack means to separate interrupts. In addition to the origin / source ID check in the NTB, the SgInt concept uses an exclusive address range (page) within the NTB aperture for the interrupts of each I/O device. Mapping target for this interrupt page is a dedicated page (alias page) in the processor that only contains the interrupt triggering register.

#### 3 SgInt (Safeguarding Interrupts)

A fundamental assumption is a static system configuration proving low complexity. This is prioritized over dynamic flexibility to obtain a predictable and deterministic system behavior. Determinism and predictability is an essential prerequisite to moderate the effort for the required assurance or certification process of a safety-oriented and security-oriented development project like in avionics [14]. Another assumption is the use of COTS components. This is essential to keep costs low for products with low piece numbers / volume and long life cycles like aircraft.

The SgInt concept enables the safeguarding of interrupts for hardware-based I/O virtualization for mixed-criticality embedded real-time systems using non-transparent bridges in single (multi-core) processor systems as well as in multi (multi-core) processor systems.

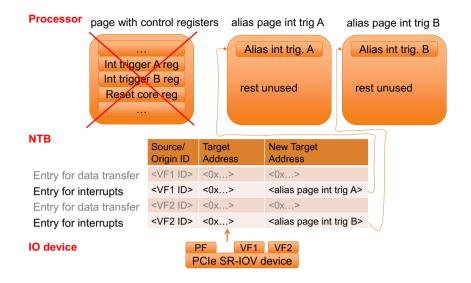

The already described separation mechanism (cf. [6] and [13]) using NTBs with additional checking of the target address and source / origin ID can also be extended to safeguard interrupts (cf. Figure 1). Message-signaled interrupts are the omnipresent type of interrupts in modern serial high-speed memory-mapped I/O standards, since dedicated interrupt wires are no longer available. Messagesignaled interrupts can be considered as small DMA write transactions (e.g. 4) Byte). The SgInt concept uses an exclusive entry in the rule set in the NTB per I/O device (or PCIe function or application interface) for its associated interrupts (cf. Figure 1). An entry represents an address window or memory page of a typical size of 4kB. The mapping target of this entry or page is a memory-mapped page containing the interrupt trigger register of the interrupt controller. The interrupt trigger register converts the message-signaled interrupt to an actual interrupt. The access to this NTB entry is controlled by the control engine in the NTB performing the origin/source ID check (cf. Figure 1). This means that only the message-signaled interrupt sent by a distinct I/O device (or PCIe function or application interface) can pass this special interrupt window over the NTB. However, the protection granularity at page level is still not sufficient for a safe and secure handling of interrupts. The mapping target of this interrupt entry or page is a page containing this interrupt trigger register and a variety of additional control registers. Since a message-signaled interrupt is a DMA write packet, it is able to manipulate any memory-mapped control register within the target page. For example, an interrupt can trigger interrupts associated with other devices or other system-on-chip interrupts or processor interrupts by targeting another interrupt trigger register (cf. Figure 1). In addition, an interrupt can manipulate any memory-mapped control register of the target page like triggering the reset of all processing cores (cf. Figure 1). This could lead to a complete system failure. To prevent this, the granularity or precision of the origin/source ID check needs to be increased. A possibility is to isolate the interrupt trigger register within a page. This means, a page only contains this single interrupt trigger register or an alias register to this interrupt trigger register. An I/O device (or PCIe function or application interface) that is allowed to access this page can only change this register and nothing else since the page does not contain more control registers. Such a page is called alias page or page with an alias to the interrupt trigger register (cf. Figure 1).

Fig. 1. SgInt (Safeguarding Interrupts): Origin/source ID check in combination with alias pages

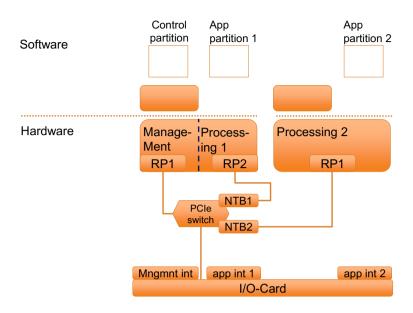

To demonstrate an application, we have implemented the SgInt concept in the context of sharing a DMA-capable multi-function PCIe I/O card in a mixedcriticality embedded processing platform. Figure 2 depicts the implemented system setup. A Xilinx VC709 FPGA evaluation board is used as PCIe I/O card. A PLX 8749 chip serves as PCIe switch containing the two non-transparent bridges. The two system hosts are built up by two Freescale QorIQ P4080 Development Systems (P4080DS). The P4080 platform is a PowerPC-based embedded multi-core processing platform and a reference model of the Freescale QorIQ series. Freescale's Software Development Kit (SDK) Version 1.2 is used as software foundation. The avionics industry considers the PowerPC architecturebased P4080 platform as a platform candidate for embedded avionics systems [1,2,6,14,15].

For simplicity reasons, the demonstration system considers only two multicore processors and one DMA-capable and bus-mastering capable PCIe card with two physical PCIe functions. Physical function (PF) 0 is used as management interface and application interface 1 and PF 1 servers as application interface 2. However, the SgInt concept is scalable from one application interface per processing host to multiple application interfaces per processing host with one NTB with multiple windows or multiple NTBs. An additional reason for using only two physical functions is that the SR-IOV capability of the Xilinx VC709 FPGA evaluation board is not compatible to the P4080DS. The Xilinx SR-IOV IP-core requires the optional PCIe Alternative Routing-ID Interpretation (ARI) extension to address VFs. The P4080DS does not support PCIe ARI [1]. Xilinx has

Fig. 2. Implementation of the Concept

confirmed this and we are in dialog with Xilinx to eliminate this limitation in the succeeding generation of Xilinx FPGAs.

The demonstration system encompasses two multi-core processors. If desired, the management part can be outsourced to a third management processor. The left multi-core processor runs the management section and one application section. One core and one dedicated (bus) address space or PCIe hierarchy or root port (RP) takes over the tasks of the management section. A second core and a second dedicated address space or PCIe hierarchy or root port runs one application section. This part of the demonstration system is representative to apply the concept in a single (multi-core) processing system. To be able to evaluate the concept also in multi (multi-core) processor systems, the additional second multiprocessor takes over the task of another application section. This management control partition sets up the system, controls the main address space and controls the NTBs and the management interface of the I/O card. Each of the dedicated address spaces of a application section is connected to the main address spaces by an NTB. Application partition 1 running on the first multi-core processor is directly mapped to application interface 1 of the I/O card whereas application partition 2 running on the second multi-core processor is mapped to application interface 2 of the I/O card. The IOMMU of the P4080 platform has no means to safeguard interrupts of multiple PCIe devices or PCIe devices with multiple functions [2] [16]. Therefore, the spatial separation of interrupts of the two application interfaces are performed by the SgInt concept.

## 4 Evaluation

#### 4.1 Evaluation Setup

The evaluation of the enforcement of the source / origin ID check for interrupts is analyzed with the following procedure:

The control partition sets up the NTB and the PCIe advanced error reporting (AER) registers. A DMA write transaction followed by a synchronization interrupt is triggered. The interrupt contains an allowed origin / source ID and target address, which complies to the rule set. Application partition 1 waits for the receiving of the interrupt while a time out timer is started. In this case, the receiving of the interrupt is expected and no time out should occur. The AER registers report no error. As a next step, another DMA write transaction with a synchronization interrupt is triggered. Here, the interrupt contains a target address associated to a disallowed origin / source ID. Application partition 1 waits for the receiving of the interrupt while a time out timer is started. The receiving of the interrupt is expected but does not occur and the time out occurs. The AER registers report the header and the first 32 data bits of the blocked packet.

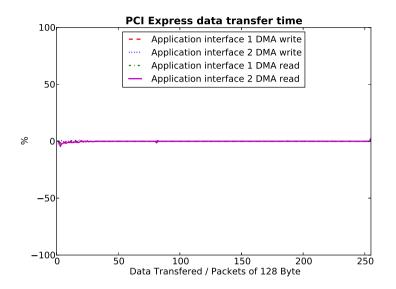

The evaluation of the performance overhead (transfer time, transfer rate) of the SgInt concept is investigated with the following procedure:

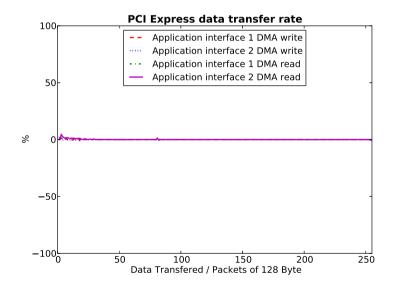

The control partition configures the NTB and the I/O card. It is defined by the management interface that application interface 1 is assigned 50% of the available transfer rate and application interface 2 is assigned 50% of the available transfer rate. DMA read and write transactions hit the two application partitions. The transfer time and transfer rate of transactions are measured including the low-level software overhead and synchronization interrupts. The DMA transactions are composed of a number of 128 Byte-sized packets sent back to back. The number of packets is increased from 1 to 255. For each packet count, the measurements are run 100 times. The described measurement procedure is executed twice. One time it is conducted using the presented SgInt concept with interrupt separation. The other time it is performed using the state-of-the-art doorbell interrupt mechanism without separation (cf. Section 2 and [8]). Then both results are compared.

#### 4.2 Evaluation Results

The evaluation result of the enforcement of the source / origin ID check for interrupts is given by the following output:

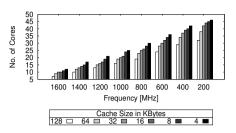

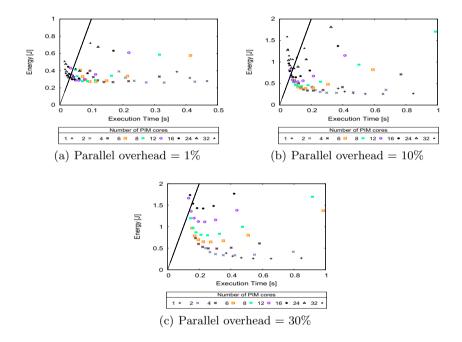

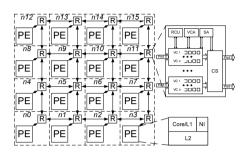

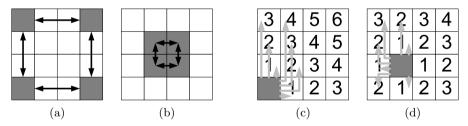

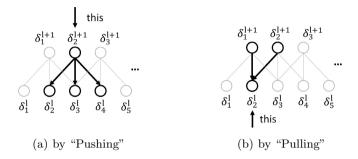

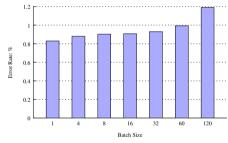

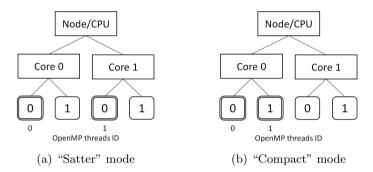

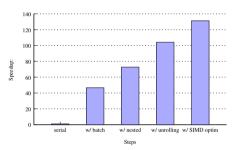

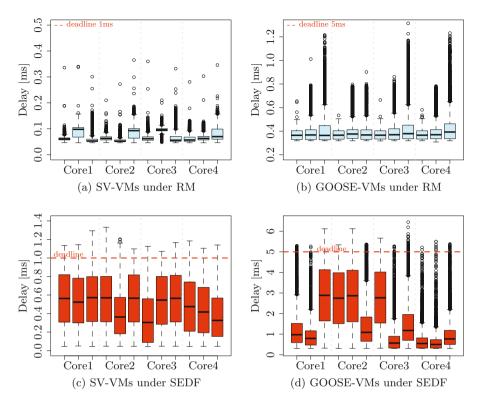

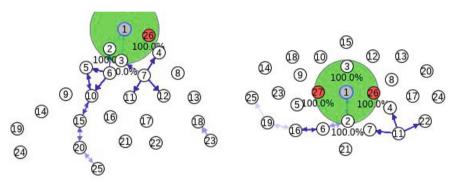

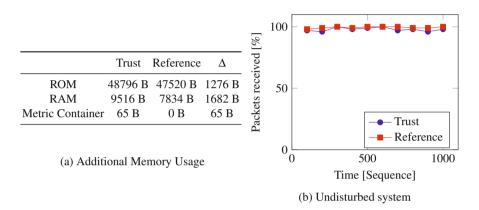

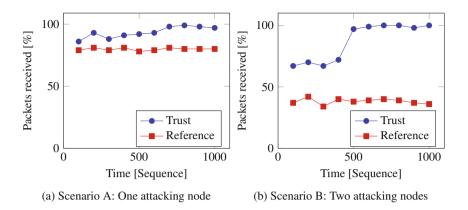

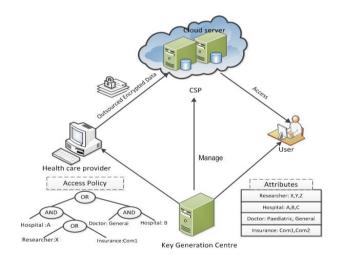

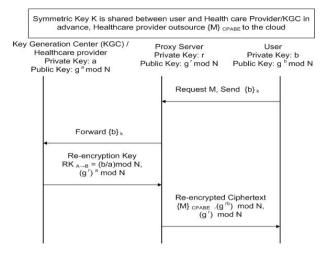

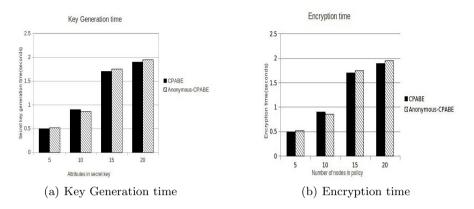

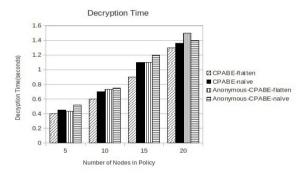

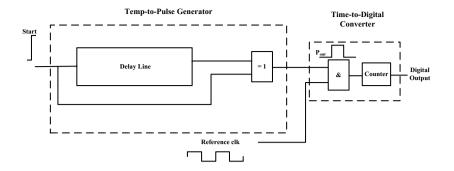

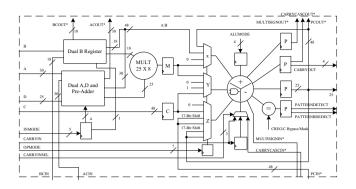

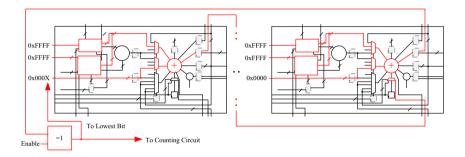

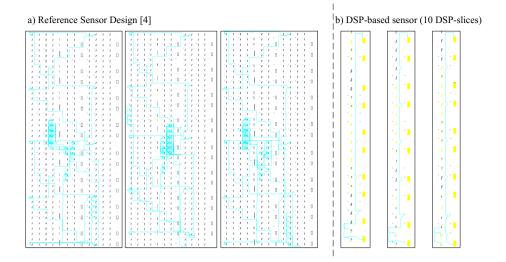

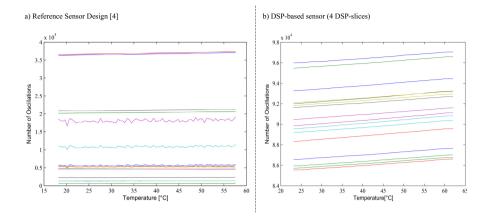

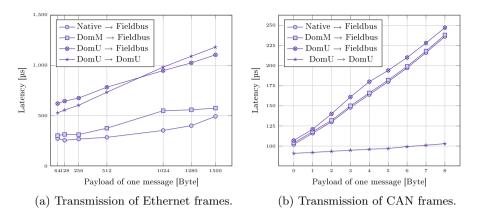

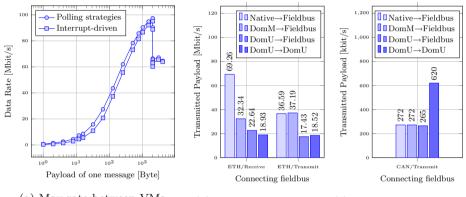

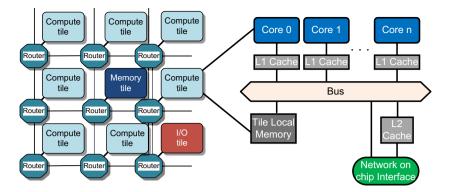

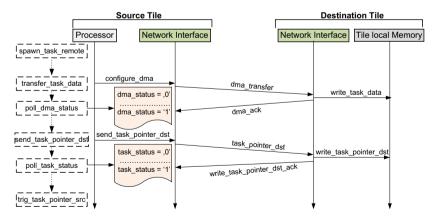

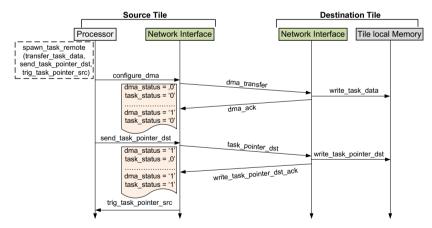

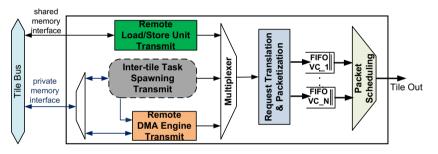

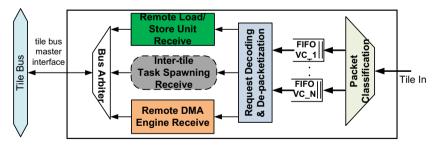

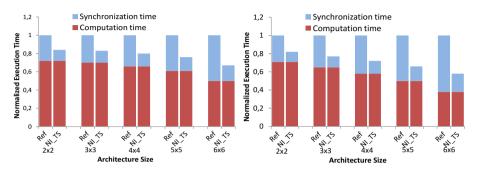

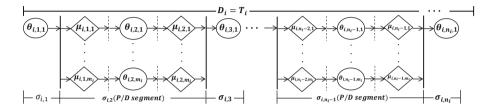

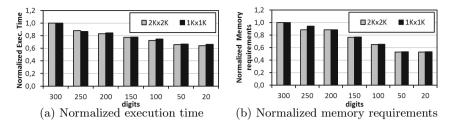

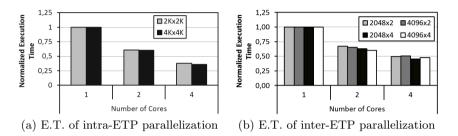

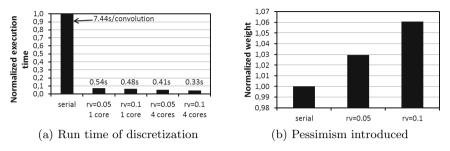

```