# Weisheng Zhao · Guillaume Prenat Editors

# Spintronics-based Computing

Spintronics-based Computing

Weisheng Zhao • Guillaume Prenat Editors

# Spintronics-based Computing

*Editors* Weisheng Zhao Spintronics Interdisciplinary Center Beihang University Beijing, China

Guillaume Prenat CEA Grenoble, France

ISBN 978-3-319-15179-3 ISBN 978-3-319-15180-9 (eBook) DOI 10.1007/978-3-319-15180-9

Library of Congress Control Number: 2015937624

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

## Foreword

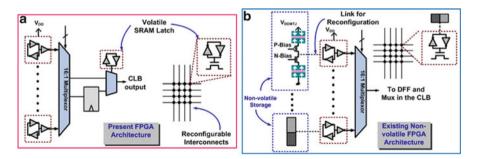

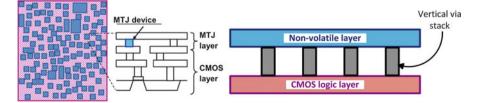

A major issue today for the development of the Information and Communication Technologies is the challenge of the "beyond CMOS," how to go beyond the physical limits of the semiconductor-based conventional electronics, how to continue the progress of the electronic components in terms of size, speed, and price reduction, with the additional challenge of treating and storing efficiently a continually increasing quantity of information while reducing the total energy consumption. If we look at the 2013 International Technology Roadmap for Semiconductors (ITRS), we can see that a major perspective for the "beyond CMOS" comes from spintronic technologies exploiting not only the charge of the electrons but also their magnetism, their spin. The book "Spintronics Based Computing" edited by Prof. Weisheng Zhao and Dr. Guillaume Prenat is particularly timely as it describes some of these spintronic technologies: Spin Transfer Torque-Random Access Memory (STT-RAM) and several types of logic or communication devices based on Magnetic Tunnel Junctions, STT-RAM, or Spin Torque Nano-Oscillators.

The STT-RAM nonvolatile memories, owing mainly to their potential for the highly desirable reduction the energy consumption of computing, are included in

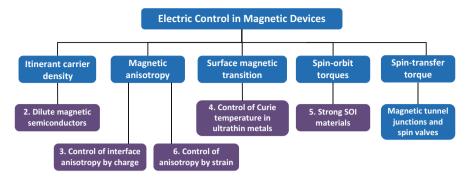

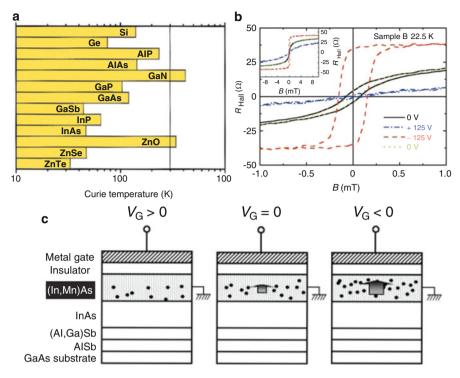

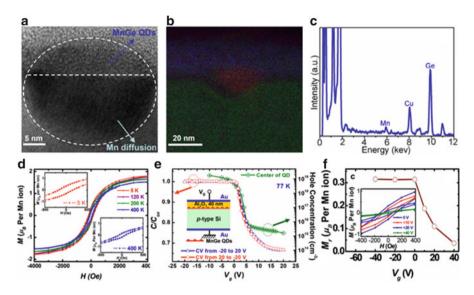

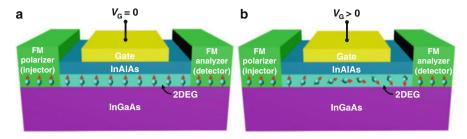

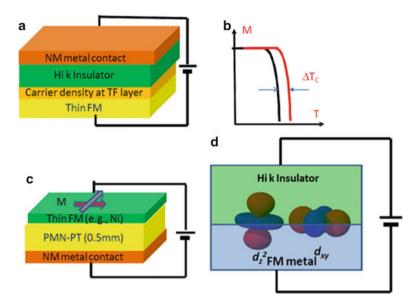

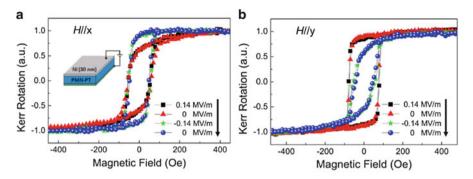

the ITRS roadmap into a category of "Memory and Logic Technologies Highlighted for Accelerated Development." The recent advances in the technology of the STT-RAMs are described in the chapter by Dr. Naoharu Shimomura, the associated critical issue of the current-induced switching of magnetic tunnel junctions (MTJ) is discussed in the chapter written by Prof. Weisheng Zhao and coworkers, and we can learn about the perspective for electric control of magnetic devices in the chapter by Prof. Kang L. Wang.

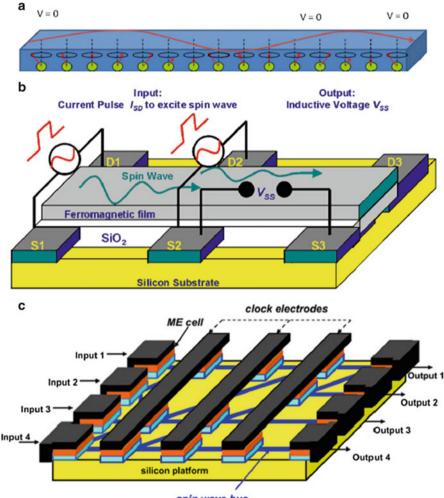

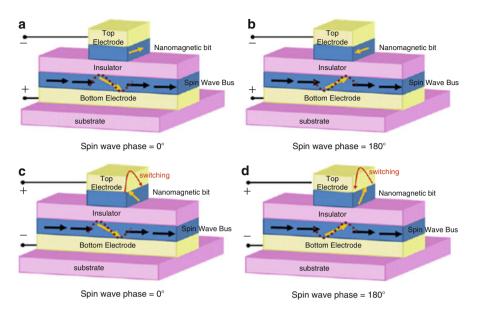

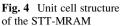

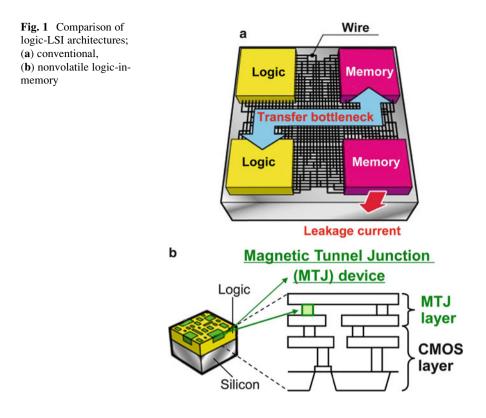

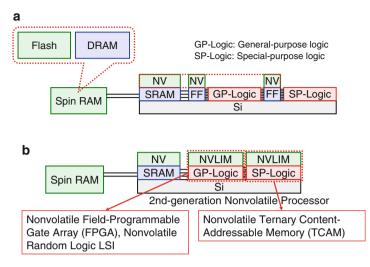

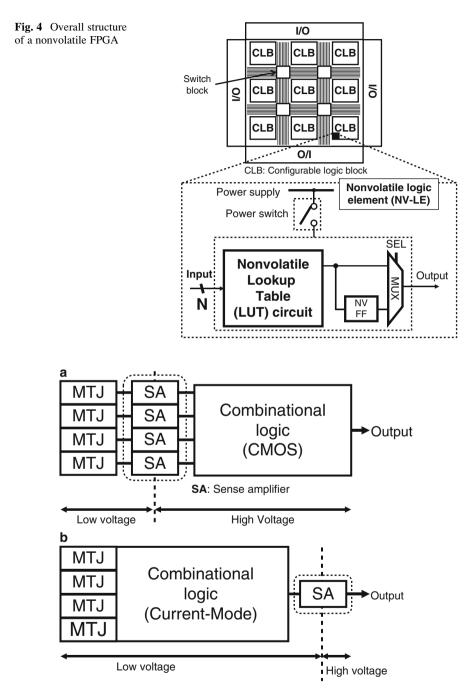

The MTJ and STT-MRAM can be used to replace the DRAM of the today computers but can also be integrated more deeply into the logic circuits to obtain a new generation of processors of enhanced speed and higher density. These new architectures are discussed in the two chapters written by Prof. Lionel Torres and Prof. Takahiro Hanyu. Finally, as computing cannot be strictly separated from RF communication, I want to point out the particular interest of the last chapter by Prof. Mircea Stan on the Spin Torque Nano-Oscillators and their synchronization.

I can conclude that Spintronics Based Computing, by presenting several expected next steps in the development of computing technology together with the associated problems of fundamental research, can be extremely useful for the researchers in both the academic and industry communities.

Albert Fert

Emeritus Professor at Université Paris-Sud 2007 Nobel Laureate in Physics

# Contents

| Current-Induced Magnetic Switching for High-Performance                                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

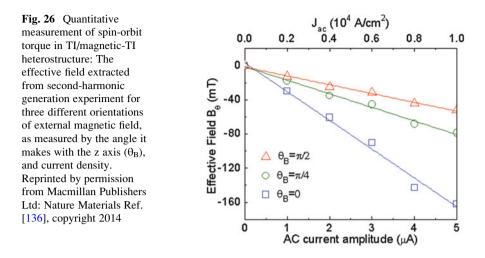

| <b>Computing</b>                                                                                                                              | 1   |

| Electric Control of Magnetic Devices for Spintronic<br>Computing                                                                              | 53  |

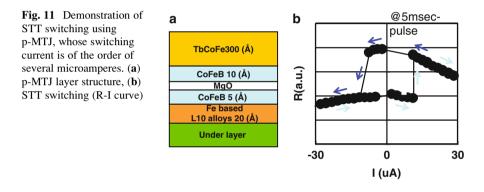

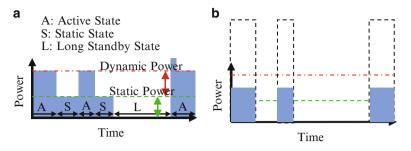

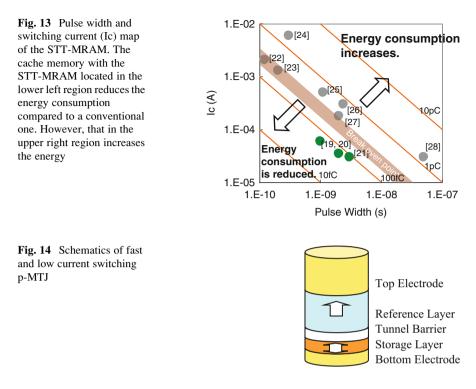

| Advanced Perpendicular STT-MRAM Technologies<br>for Power Reduction of High-performance Processors                                            | 113 |

| Beyond STT-MRAM, Spin Orbit Torque RAM SOT-MRAM<br>for High Speed and High Reliability Applications                                           | 145 |

| Challenge of Nonvolatile Logic LSI Using MTJ-Based<br>Logic-in-Memory Architecture                                                            | 159 |

| Logic Circuits Design Based on MRAM: From Single<br>to Multi-States Cells Storage<br>Bojan Jovanović, Raphael Martins Brum, and Lionel Torres | 179 |

| Statistical Reliability/Energy Characterization        |     |

|--------------------------------------------------------|-----|

| in STT-RAM Cell Designs                                | 201 |

| Wujie Wen, Yaojun Zhang, and Yiran Chen                |     |

| Synchronized Spin Torque Nano-Oscillators: From Theory |     |

| to Applications                                        | 231 |

| Mehdi Kabir and Mircea Stan                            |     |

| Index                                                  | 251 |

## **About the Editors**

Weisheng Zhao received the Ph.D. degree in physics from the University of Paris-Sud, France, in 2007. From 2004 to 2008, he investigated Spintronic devices-based logic circuits. Since 2009, he joined the CNRS as a tenured research scientist and his interest includes the hybrid integration of nanodevices with CMOS circuit and new nonvolatile memory (40 nm technology node and below) like MRAM circuit and architecture design. Weisheng has authored or co-authored more than 120 scientific papers (e.g., Advanced Material, Nature Communications, >40 I.E. Transactions); he is also the principal inventor of 4 international patents. Since 2014, he becomes "Youth 1000 plan" distinguished

professor in Beihang University, Beijing, China where he leads the Spintronics Interdisciplinary Center. He is a senior member of IEEE.

**Guillaume Prenat** (36 years old) is a researcher in microelectronics now in charge of the design activity for Spintec Lab. He graduated from Grenoble Institute of Technology in France, in 2002. He obtained a Ph.D. degree in the field of analog and mixed signal testing in 2005. He joined the spintronics laboratory SPINTEC in November 2006 to take in charge the design activity. He holds 6 international patents and has authored or co-authored 45 scientific publications in this field.

## **Current-Induced Magnetic Switching for High-Performance Computing**

Yue Zhang, Weisheng Zhao, Wang Kang, Eyra Deng, Jacques-Olivier Klein, and Dafiné Revelosona

#### 1 Introduction

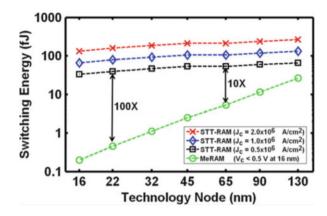

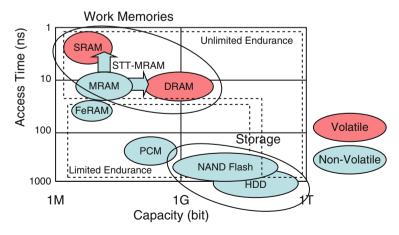

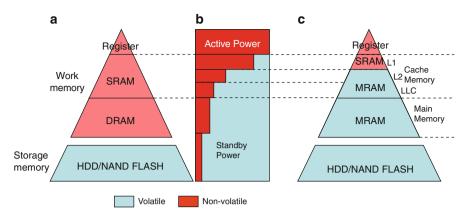

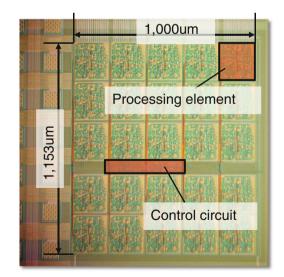

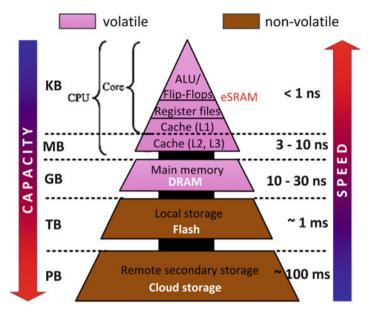

The shrinking of complementary metal oxide semiconductor (CMOS) fabrication node below 90 nm leads to high static power in memories and logic circuits due to the increasing leakage currents [1]. This power issue limits greatly the miniaturization and improvement of electronic devices. For example, the design of multicore microprocessors for CPU in computer is a proof for this point. In this background, novel technologies to replace the mainstream charge-based electronics are hot topics for both academics and industries. Beyond the electrical charge, the devices based on the spintronics attract a broad attention and show the performance advantages in many aspects [2].

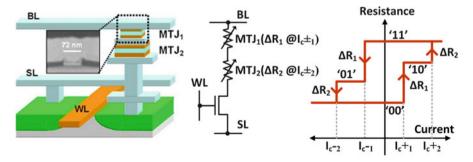

Magnetic tunnel junction (MTJ), one of the most important spintronic devices, is the basic element of magnetoresistance random access memory (MRAM) which becomes a most promising candidate for the next generation of universal nonvolatile memory. Among its various features, the magnetization switching in MTJ is a crucial point. Much of the academic and industrial research efforts are presently focused on developing efficient switching strategies. One promising method relies on using spin transfer torque (STT) [3, 4], which involves low threshold currents and well-understood mechanisms. Furthermore, only a bi-directional current is

W. Zhao (🖂)

Y. Zhang • W. Kang

Spintronics Interdisciplinary Center, Beihang University, Beijing 100191, China

IEF, Univ. Paris-Sud 11, UMR8622, CNRS, Orsay 91405, France

Spintronics Interdisciplinary Center, Beihang University, Beijing 100191, China e-mail: weisheng.zhao@buaa.edu.cn

E. Deng • J.-O. Klein • D. Revelosona IEF, Univ. Paris-Sud 11, UMR8622, CNRS, Orsay 91405, France

<sup>©</sup> Springer International Publishing Switzerland 2015 W. Zhao, G. Prenat (eds.), *Spintronics-based Computing*, DOI 10.1007/978-3-319-15180-9\_1

needed in this approach, which simplifies greatly the CMOS switching circuits and thereby allows for higher density than the other approaches.

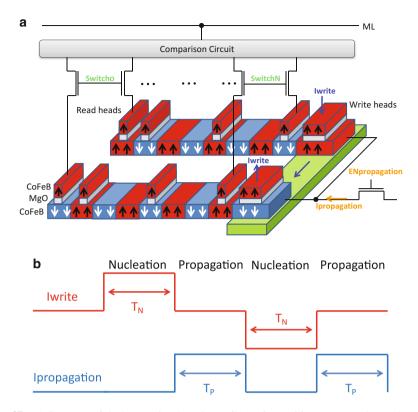

On the other hand, racetrack memory is an emerging spintronic concept based on current-induced domain wall (CIDW) motion in magnetic nanowires [5, 6]. Combining with MTJs as write and read heads, CMOS integrability and fast data access speed can be achieved. In this concept, the data are stored via the magnetizations of magnetic domains separated by domain walls (DWs). Due to STT mechanism, the DWs can be propagated consecutively in a direction by a spin-polarized current, which makes the racetrack memory possible to be widely applied for logic and memory designs.

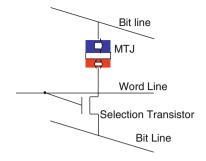

However, some unexpected effects have been discovered using current-induced approach in the devices with small size (e.g., lateral size of 40 nm), such as erroneous state switching with reading currents and short retention times. These problems are mainly related to the in-plane magnetic anisotropy, which cannot provide a sufficiently high energy barrier to ensure thermal stability [7]. This issue limits greatly the potential for future miniaturization of spintronic devices. One compelling solution addressing this issue involves the perpendicular magnetic anisotropy (PMA) in certain materials (e.g., CoFeB/MgO), because it allows high energy barrier to be attained for small-size structures (<40 nm) while maintaining the possibility of fast-speed operations, high TMR ratios and low threshold currents [8, 9].

Thanks to the diverse advantages demonstrated by spintronics as well as various milestone breakthroughs of its related materials and techniques, hybrid spintronics/ CMOS logic and memory circuits open a novel route to manipulate information more efficiently. Taking advantages of spintronic devices, the emerging circuits or systems can also realize low power, high density and high speed. For the past decade, many spintronics based logic and memory circuits and their prototypes have been designed and presented. From the relatively mature spin valve for HDDs [10–12] to recently commercialized STT-MRAM [13–17], from magnetic full adder (MFA) and Magnetic Flip-Flop (MFF) for magnetic processors [18–20] to magnetic content addressable memory (CAM) for internet router and search engines [21, 22], spintronics or concepts based on it has seeped into a majority of the advanced logic and memory systems.

One of the beneficial applications is the computing: the structural and technological limitations of conventional computing systems prevent them from reaching high frequency (~4 GHz) and limit power efficiency [23]. In this chapter, we describe an overview of the devices and circuits for high-performance computing, which are particularly based on current-induced magnetic switching. From the compact modeling to the circuit design and the optimization, the contributions of this chapter have been made at a series of levels.

Firstly we introduce the concepts of PMA STT MTJ and racetrack memory. Their fundamental physics, structures and performances, promising to achieve high performance computing, will be involved. In the following, we present spintronics based computing designs under intense R&D. MFA (1-bit one based on PMA STT MTJ and multi-bit one based on racetrack memory) and CAM are particularly investigated. They demonstrate the performance advantages in terms of area and/or speed and/or energy, compared with the CMOS based conventional ones.

#### 2 Current-Induced Magnetic Switching Spintronic Devices

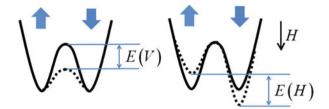

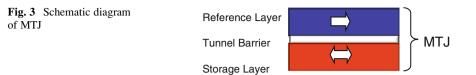

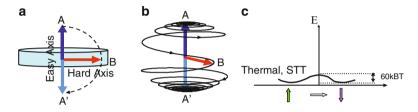

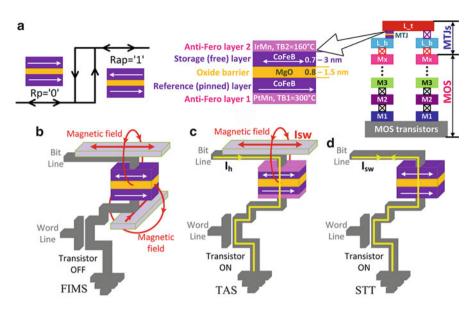

#### 2.1 Perpendicular Magnetic Anisotropy Spin Transfer Torque Magnetic Tunnel Junction (PMA STT MTJ)

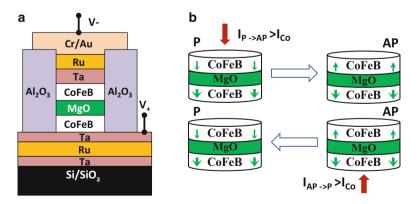

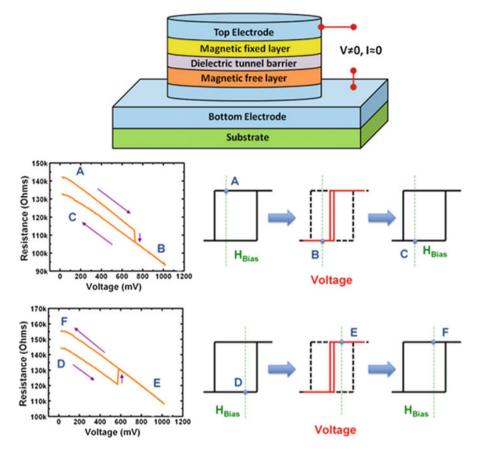

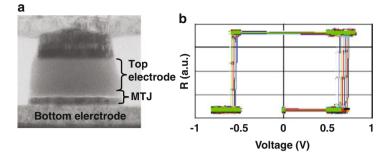

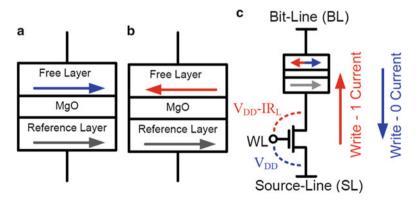

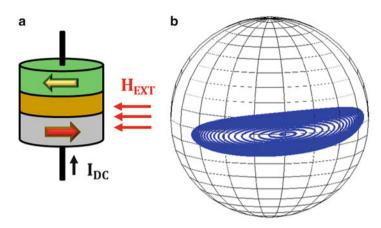

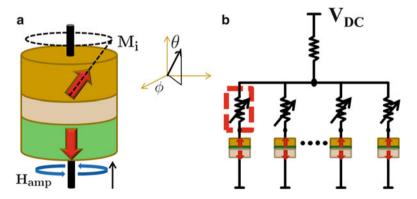

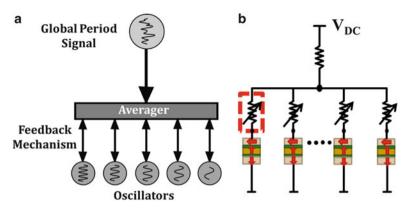

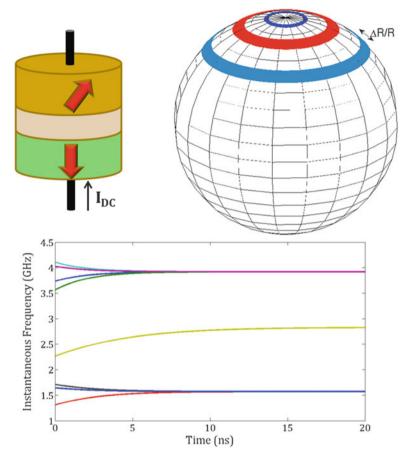

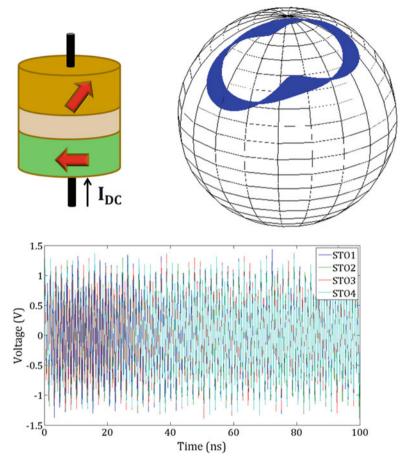

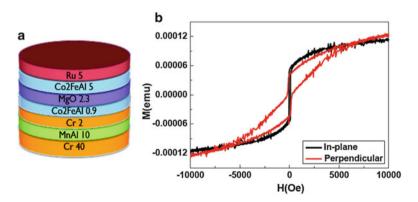

The MTJ nanopillar, as shown in Fig. 1a, is one of the important devices for current spintronics based integrated circuits. Particularly, it is the basic element of MRAM. According to the different switching mechanisms, MTJs can be categorized into certain generations. Field-induced magnetic switching (FIMS) [24, 25] and thermally-assisted switching (TAS) [26, 27] are two achievable and mainstream approaches. Some prototypes or even commercialized products are based on these mechanisms. However, the mandatory utilization of magnetic field in these approaches leads to drawbacks on speed, density and power consumption, which hinder the integration of MRAM for advanced computing or memory applications.

In this context, the current-induced magnetic switching comes into view. STT was proposed independently by Berger and Slonczewski in 1996 [3, 4]. They found that a spin-polarized current injected perpendicularly to the plane could equally influence the magnetizations. This interaction is attributed to angular momentum transferred from the polarized electrons to the local magnetization of the ferromagnetic (FM) layer. Once the amount of electrons exceeding the threshold value (often represented by critical current or critical current density), the STT exerted by the current will switch the magnetization of the free layer of MTJ [13, 28]. The STT switching approach was initially researched on giant magnetoresistance (GMR) effect based spin valve [29, 30], and then focused on the MTJ providing a significantly higher magnetoresistance [31, 32]. In MTJ, one FM layer acts as a polarizer for an electric current, which then transfers angular momentum by exerting a torque on the magnetization of the other FM layer. This current-only approach simplifies

**Fig. 1** (a) Vertical structure of an MTJ nanopillar composed of CoFeB/MgO/CoFeB thin films. (b) STT switching mechanism: the MTJ state changes from parallel (P) to anti-parallel (AP) as the positive direction current  $I_{P\to AP} > I_{C0}$ , on the contrast, its state will return to P state with the negative direction current  $I_{AP\to P} > I_{C0}$

greatly the switching process as it only requires a bi-directional current (see Fig. 1b). Moreover, the magnitude of current for STT is normally less by an order than that for generating a large magnetic field. As a consequence, STT switching approach is widely considered the most promising one to be applied in the future MRAM applications [33].

The effect of STT on the free layer of MTJ can be described by the extra STT term in the Landau-Lifshitz-Gilbert (LLG) equation [34, 35] given by

$$\frac{d\vec{m}}{dt} = -\gamma \vec{m} \times \vec{H}_{eff} + \alpha \vec{m} \times \frac{d\vec{m}}{dt} - \beta J \left(\vec{m} \times \vec{m} \times \vec{M}\right) \tag{1}$$

where  $\vec{m}$  and M are the unit vectors of the free and pinned layers' magnetizations,  $\alpha$  is the damping constant,  $\gamma$  is the gyromagnetic ratio,  $\beta$  is the STT coefficient depending on both the spin polarization and the geometric configuration of the spin torque efficiency.  $\vec{H}_{eff}$  is the effective field that includes the external field, the anisotropy field, the magnetostatic field, the Oersted field and the exchange coupling field.

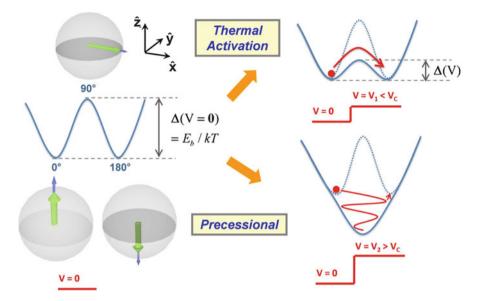

In this equation, the first term on the right is to describe the precession of the field-induced magnetization. The second term describes the intrinsic damping process that results in a decrease of the precessional angle as a function of time. The last term on the right is the STT term whose vector direction is opposite to the damping direction. In the current-induced system, the magnetization switching on the free layer can be considered the competition between the damping term and the STT term (see Fig. 2). When the current density is small, the STT term is weaker than the damping term, then the magnetization dynamics maintain in an equilibrium state. In contrast, if the current density is high enough to make STT term stronger than damping term, the magnetization can be excited to larger precessional angles and further be switched. The critical current is defined as the threshold current to distinguish these two regimes, which is described by STT switching static model presented as follows.

The threshold for excitations driven by STT is given by the critical current. The static behavior to describe STT switching in PMA MTJ is mainly based on the calculation of threshold or critical current  $I_{C0}$ , which can be expressed by the Eqs. (2) and (3) [8].

$$E_p = \frac{\mu_0 M_S \times Vol \times H_K}{2} \tag{2}$$

$$I_{C0p} = \alpha \frac{\gamma e}{\mu_B g} (\mu_0 M_S) H_K Vol \tag{3}$$

where  $H_K$  is the perpendicular magnetic anisotropy field.

Note that the spin accumulation effects are neglected and the spin polarization efficiency factor g is firstly obtained with the following equation to describe the

Fig. 2 Diagram of the LLG equation.  $N_D$  is the damping term,  $N_{STT}$  is the STT term and  $N_H$  is the field precession term

asymmetric current case [36]. It provides the best agreement with the experimental results illustrated in [8],

$$g = g_{SV} \pm g_{Tunnel} \tag{4}$$

where the sign depends on the free-layer alignment.  $g_{SV}$  and  $g_{Tunnel}$  are respectively the spin polarization efficiency in a spin valve and tunnel junction nanopillars. They are both predicted by Slonczewski,

$$g_{SV} = \left[ -4 + \left( P^{-1/2} + P^{1/2} \right)^3 (3 + \cos \theta) / 4 \right]^{-1}$$

(5)

$$g_{Tunnel} = (P/2)/(1 + P^2 \cos \theta) \tag{6}$$

where *P* is the spin polarization percentage of the tunnel current,  $\theta$  is the angle between the magnetization of the free and the pinned layers [3, 37].

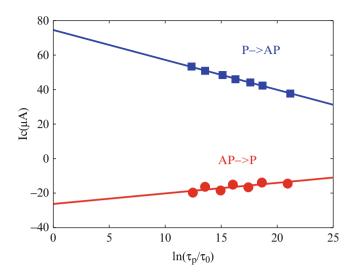

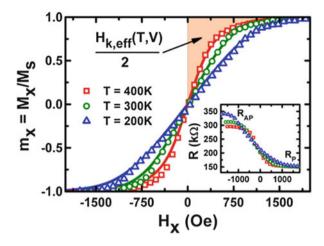

The good agreement between the physical model and experimental measurement has been verified. Figure 3 shows the verification of static model with the measured data reproduced by Ohno group [8]. The blue and red solid lines represent the STT switching static model for parallel to anti-parallel process and anti-parallel to parallel process, respectively. The blue squares and red points represent the experimental results. From Fig. 3, the overlaps between the lines and the squares (or points) show the good agreement and the feasibility of this physical model to describe the STT switching static behavior.

On the other hand, more recent experimental progress of IBM shows that an MTJ involving symmetric electrodes provides a single spin polarization efficiency factor g for both state change processes (anti-parallel state to parallel state process or parallel state to anti-parallel state process) of MTJ [38], which allows the same critical current for both parallel and anti-parallel states. In this mechanism, g is only related to TMR ratio and described as follows:

Fig. 3 Verification of the static model with measured data reproduced by [8]. Solid lines represent the STT static model, the red points and blue squares represent the experimental results

$$g = (TMR(TMR+2))^{1/2}/2(TMR+1)$$

(7)

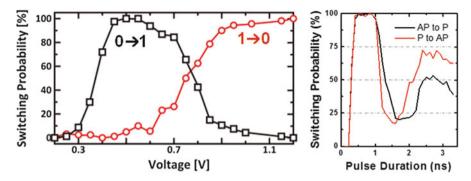

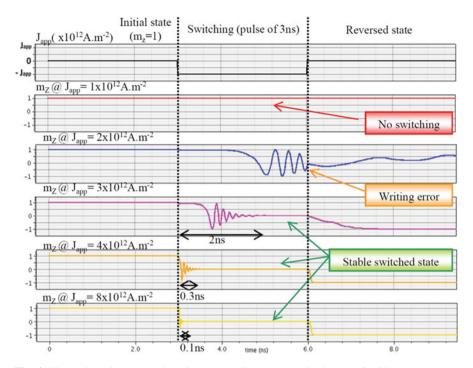

The dynamic switching behavior of STT in PMA MTJ shows the dependence of switching current on switching duration. It is considered to be a complex process as it can be categorized into two regimes depending on the relative magnitude between switching current (I) and critical current ( $I_{C0}$ , calculated by Eq. (3) for static behavior): thermally assisted ( $I < 0.8 I_{C0}$ ) and precessional ( $I > I_{C0}$ ) switching regimes. Thermally assisted regime can be described by Néel-Brown model and precessional regime can be described by Sun model [39–41]. Note that there are no clear experimental results and theories related to the range from  $0.8I_{C0}$  to  $I_{C0}$ , we thus neglect this range and consider no effect occurs in this range.

For each model, the relationship between current and duration follows different laws. For practical applications, the two regimes have their own specific interest: the thermally assisted regime corresponds to low current density but slower switching, which is usually used for the sensing operation; the precessional regime corresponds to fast switching (sub 3 ns) but high current density, which is usually used for the writing operation.

In the sub-threshold condition where the current remains below the critical current (I < 0.8Ico), the switching can still occur thanks to thermal activation above the voltage/current-dependent barrier. In this case, the switching behavior can be described by Néel-Brown model [42]:

$$\frac{d\Pr(t)}{(1-\Pr(t))dt} = \frac{1}{\tau_1}$$

(8)

$$\tau_1 = \tau_0 \exp\left(\frac{E}{k_B T} \left(1 - \frac{I}{I_{c0}}\right)\right) \tag{9}$$

where  $\tau_0$  is the attempt period, Pr(t) is the switching probability. Eq. (8) can be transformed to a simple formula:

$$t = -\tau_1 \ln(1 - \Pr(t)) \tag{10}$$

These equations demonstrate that the STT dynamic switching behavior is probabilistic or stochastic. However, from Eq. (10), it can convert this stochastic behavior to be deterministic by determining the switching probability. That means ones should apply a specifically long current pulse to get the determined switching probability. This assumption would greatly simplify the description and analyses of the thermally assisted regime. Meanwhile, the stochastic effect is still the key point for this regime, which will be described and integrated in the following part.

In the case that the switching current is near or exceeding the critical one, the STT excitation becomes more obvious and deterministic. The high current pulse drives the magnetization to process, then after reaching the switching time, a magnetization reversal occurs suddenly and quickly [9]. Considering a small thermal fluctuation in this regime with a relatively high thermal stability, the average switching time is given by

$$\frac{1}{\langle \tau \rangle} = \left[ \frac{2}{C + \ln\left(\frac{\pi^2 \xi}{4}\right)} \right] \frac{\mu_B P_{pin}}{em_m \left(1 + P_{pin} P_{free}\right)} (I - I_{c0}) \tag{11}$$

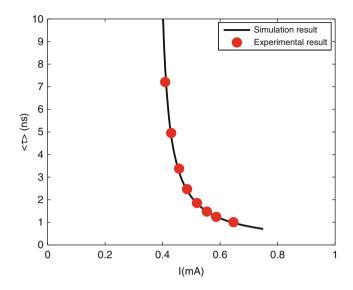

where *C* is the Euler's constant,  $\xi = E/k_{BT}$  is the activation energy in units of  $k_{BT}$ ,  $P_{pin}$ ,  $P_{free}$  are the tunneling spin polarizations of the pinned and free layers, we assume here that  $P_{pin} = P_{free} = P$ ,  $m_m$  is the magnetic moment of free layer. Figure 4 shows the good agreement of this dynamic model with the experimental data extracted from [9]. From this figure, the increase of *I* and decrease of  $I_{C0}$  both contribute to scale down the switching latency. Considering the high currents are always ensured by the large-size transistors, this physical model also implies the alternatives to optimize the tradeoff between the overall area and the speed of hybrid spintronic/CMOS circuits.

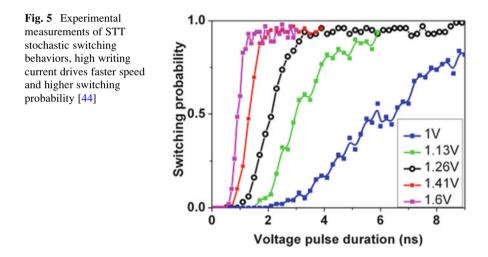

Recently, a lot of experimental and theoretical results have shown that, although STT switching may allow sub-nanosecond switching duration, the switching process of STT is intrinsically stochastic, which results from the unavoidable thermal fluctuations of magnetization (see Fig. 5) [43–46]. They are responsible for large fluctuation in the switching duration, which can be proven by the Eqs. (8)–(11) describing the dynamic behavior. Moreover, the stochastic behavior can also be

Fig. 4 Comparison of the dynamic model with measured data

divided into two regimes: thermally assisted (I < 0.8  $I_{C0}$ ) and precessional (I >  $I_{C0}$ ) switching regimes.

For the thermally assisted regime, we can transform Eq. (10) to another form:

$$\Pr(t) = 1 - \exp(-t/\tau_1)$$

(12)

It describes the probability density function (PDF) of the switching duration for this regime, which follows an exponential distribution with characteristic time  $\tau_1$  decreasing with the current density.

In the super-threshold region described as precessional regime, the stochastic switching is triggered by a thermal fluctuation which creates an initial angle between the current spin-polarization and the magnetization of magnetic layer. The switching duration then follows a specific exponential-like distribution centered on the average switching delay time calculated by Eq. (11) [47].

From the above expressions, it shows that, in both regions, increasing the switching probability requires to increase either the write current or the current pulse duration. It could also be of great benefit for tolerating the high mismatch and process variations [48, 49].

To address the requirement of high-performance MTJ for the future logic and memory applications, there are usually five criteria to evaluate: small area, high TMR ratio, low STT switching current, capacity to withstand the standard semiconductor processing and high thermal stability. With the shrinking of size, the conventional MTJ with in-plane magnetic anisotropy becomes more and more difficult to satisfy these criteria. Recent material progress showed that the MTJ with PMA could offer lower switching critical current, higher switching speed and higher thermal stability compared with that with in-plane magnetic anisotropy [7]. These can be explained by the following theories.

The barrier energy and critical current of STT switching in the materials with in-plane magnetic anisotropy can be expressed as:

$$E_i = \frac{\mu_0 M_S \times Vol \times H_C}{2} \tag{13}$$

$$I_{C0i} = \alpha \frac{\gamma e}{\mu_B g} (\mu_0 M_S) \left( H_{ext} \pm H_{ani} \pm \frac{H_d}{2} \right) Vol \tag{14}$$

where  $H_C$  is the coercive field,  $H_{ext}$  is the external field,  $H_{ani}$  is the in-plane uniaxial magnetic anisotropy field,  $H_d$  is the out-of-plane magnetic anisotropy induced by the demagnetization field,  $\mu_0$  is the permeability in the free space,  $M_s$  is the saturation magnetization, Vol is the volume of the free layer,  $\mu_B$  is the Bohr magneton,  $\gamma$  is the gyromagnetic ratio, e is the electron charge, m is the electron mass.

By comparing Eqs. (2) and (13), as  $H_K$  is higher than  $H_C$ , PMA allows obtaining relatively high barrier energy with a small size. By comparing Eqs. (3) and (14), as  $H_K$  is much lower than  $H_d$ , the critical current for PMA materials can be significantly reduced.

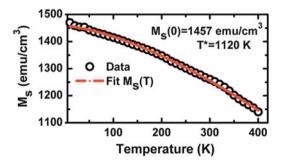

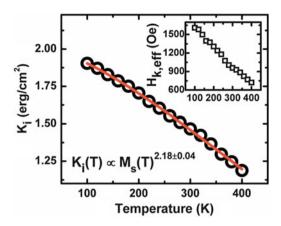

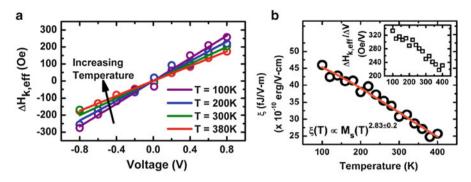

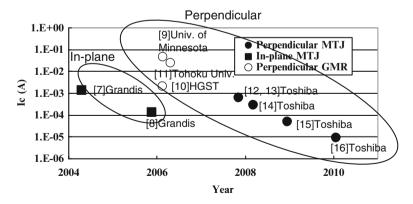

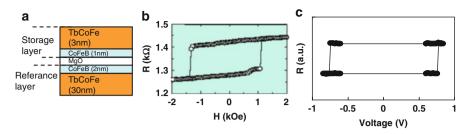

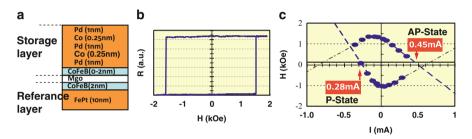

From 2002, when the first MTJ with PMA was reported, this advantageous structure attracts a great deal of attentions from academics and industries [50]. A variety of material systems has been attempted, for example, rare-earth/transition metal alloys, multilayers and other alloy materials. However, they have not been able to truly realize low critical current and high thermal stability at the same time. This situation didn't change until the Ta/CoFeB/MgO structure was revealed in 2010 [8, 9]. Figure 6 demonstrates the excellent performances of this structure. It takes advantages of CoFeB-MgO interface anisotropy to provide a good tradeoff

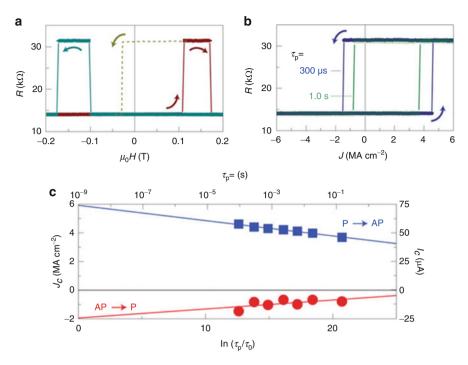

Fig. 6 TMR and current-induced magnetization switching for Ta/CoFeB/MgO structure MTJ with PMA. (a) Perpendicular R-H curve. (b) Typical results of current-induced magnetization switching at current pulse duration of 300  $\mu$ s and 1.0 s. (c) Critical current density as a function of pulse duration [8]

among the area (40 nm), critical current (~50  $\mu$ A), thermal stability (40 k<sub>B</sub>T) and TMR ratio (>100 %). Thanks to the material and technical improvement of MTJ, especially MgO based PMA STT MTJ, a lot of persistent and intensive efforts have been made for the past years to develop the high-performance spintronic systems [51, 52].

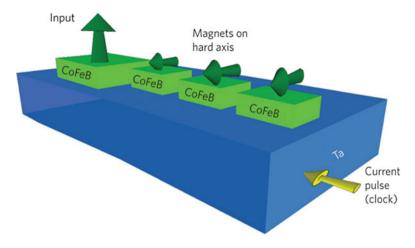

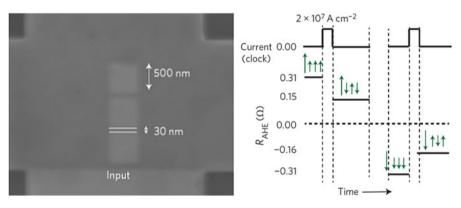

#### 2.2 Racetrack Memory

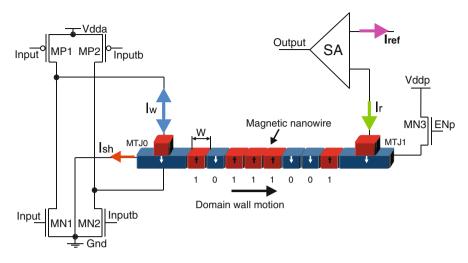

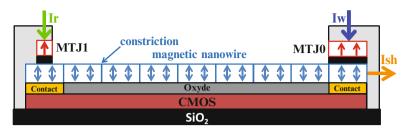

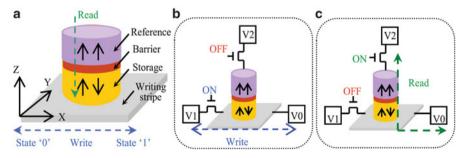

The observation of electrical CIDW motion in magnetic nanowires promises numerous perspectives [2, 53, 54] and the most interesting one is to build a novel ultra-dense non-volatile storage device, called "racetrack memory" (see Fig. 7).

The term "racetrack memory" was firstly proposed by Parkin in 2008 [5, 6]. In the concept that he proposed, write head nucleates a local domain in the magnetic nanowire and a current pulse drives the domain to move sequentially from write head to read head. Data or magnetization direction is stored between two artificial potentials or constrictions, which pin the DW as no current pulse is applied. The distance between two constrictions can be extremely small to some nanometers and

**Fig. 7** Racetrack memory based on CIDW motion, which is composed of one write head (MTJ0), one read head (MTJ1) and one magnetic nano-stripe. Iw nucleates data or magnetic domain in the magnetic stripe through STT approach, Ish induces DW motion along the magnetic stripe and Ir detects the magnetization direction through TMR effect

this allows an enormous storage (>GB) in a small die area. Compared with other non-volatile memory candidates, the scalability potential of racetrack memory is evident. By using MTJ as write and read heads, its operations, such as DW motion, domain nucleation and detection, can be addressed directly by CMOS circuits [55]. This hybrid integration makes racetrack memory promise high performance like high speed (>100 MHz) and low power beyond classical STT-MRAM. The nanowire can be built in 3D or 2D, the latter one is easier to be fabricated and become the mainstream solution for the current research on this topic. Based on in-plane magnetic anisotropy, the first racetrack memory prototype was presented in 2011 by IBM despite of its small capacity 256 bits [56]. However the intrinsic low energy barrier separating the two in-plane magnetization directions of storage layer leads to short data retention in advanced technology node (e.g., 22 nm) [51]. This drawback limits its use for high-density racetrack memory. PMA in some structures (e.g., CoFeB/MgO) providing a high energy barrier [8, 57, 58] were demonstrated and PMA MTJ become one of the most promising candidates to realize a read head. Advantageous domain wall nucleation current and speed with PMA MTJ were also observed recently [9] and this makes it be a better write head than in-plane MTJ.

The Cross-section structure of racetrack memory is shown in Fig. 8, which includes mainly three parts: a magnetic stripe separated by constrictions to store data, two MTJs as write and read heads. The number of constrictions equals to the number of stored bits. It is noteworthy that the CMOS circuits dominate the whole area of this racetrack memory as the magnetic stripe is implemented at the back-end through 3D integration as MRAM.

Fig. 8 Cross-section structure of racetrack memory. At the back-end process, the magnetic nanowire is implemented above the CMOS/MTJ interfacing circuits, which generate Ir for reading, Iw for DW nucleation and Ip for DW propagation

Figure 7 shows simultaneously one example of CMOS circuits to generate Iw and Ish, which are respectively bi-directional and uni-directional at the side of write head. Ir is driven by a sense amplifier [59] and it can convert the stored data from different magnetization directions to digital signal "0" or "1". In order to achieve the best write and read reliability, the width of write and read heads are different. For writing, a lower resistance of MTJ0 with larger width can reduce the rate of oxide barrier breakdown, which is one of the most significant constraints of the high-speed STT switching mechanism. On the contrary, high resistance of the MTJ1 with smaller width for reading can greatly improve the sensing performance.

For the racetrack memory, the speed performance is governed by the velocity of DW motion. The physical model to calculate DW velocity is indispensable for the compact modeling of racetrack memory. According to the previous literatures, the dependence of DW velocities on current and magnetic field can be described by the one dimensional (1D) model. This 1D model is deduced from the LLG equation in a 1D system [60], which can be described as:

$$\dot{\phi}_0 + \alpha \dot{X}/\lambda = \gamma H + \beta u/\lambda + f_{pin} \tag{15}$$

$$\dot{X} - \alpha \lambda \phi_0 = v_\perp \sin 2\phi_0 + u \tag{16}$$

where *X* is the position of a DW, and  $\phi_0$  is the angle that the DW magnetization forms with the easy plane.  $\lambda$  is the width of DW,  $\alpha$  is the Gilbert damping constant,  $\beta$  is the dissipative correction to the STT, *H* is the external field,  $\gamma$  is the gyromagnetic ratio,  $f_{pin}$  is the pinning force. The velocity constant  $v_{\perp}$  comes from the hard-axis magnetic anisotropy  $K_{\perp}$  (~  $K_{\perp}\lambda/\hbar$ ). *u* is spin current velocity. These two equations can describe a lot of qualitative features of DW motion driven by the field and the current. The field acts as a "force" to drive  $\phi_0$ , the current acts as a "torque" to drive *X*. In addition, as the "torque" is also contributed from the hard-axis magnetic anisotropy, the state of  $\phi_0$  can determine whether there is intrinsic pinning or pure STT. Considering only the process after depinning, Eqs. (15) and (16) can be solved analytically and described in the forms of the influence of field and current on the velocity:

$$V = V_H + V_j \tag{17}$$

The velocity is the vector sum of field-induced  $(V_H)$  and current-induced velocities  $(V_j)$ . Above the Walker breakdown field, the field-induced velocity contribution is given by

$$V_H = \alpha^2 \mu H \left\{ 1 - \frac{1}{1 + \alpha^2} \sqrt{1 - \left(\frac{H_W}{H}\right)^2} \right\}$$

(18)

where the mobility  $\mu = \gamma \lambda / \alpha$ ,  $H_w$  is the Walker breakdown field.

The general racetrack memory is based on CIDW motion, which means there is normally no magnetic field. Hence, the dependence of DW velocity on current is the key point. Regarding the relationship between  $\alpha$ , the damping constant, and  $\beta$ , the nonadiabatic coefficient, the dependence can be categorized into three cases. Before introducing these three cases, we should indicate the definition of the spin current velocity [60], which is given by Eq. (19).

$$u = \frac{\mu_B P j_p}{eM_S} \tag{19}$$

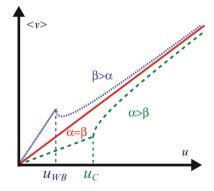

where  $j_p$  is the propagation current density. Figure 9 shows the dependence of DW velocity on current according to different configurations of  $\alpha$  and  $\beta$ , which depends on the material of the magnetic nanowire.

When  $\beta > \alpha$ ,

$$u_{WB} = \frac{1}{2} \gamma H_K \Delta \frac{\alpha}{\beta - \alpha} \tag{20}$$

$$\langle v \rangle = \frac{\beta}{\alpha} u \qquad (u < u_{WB})$$

(21)

$$\langle v \rangle = \frac{\beta}{\alpha} u - \frac{\sqrt{\left(1 - \frac{\beta}{\alpha}\right)^2 u^2 - \left(\frac{1}{2}\gamma\Delta H_K\right)^2}}{1 + \alpha^2} \qquad (u > u_{WB})$$

(22)

Fig. 9 Dependence of DW velocity on current described by 1D model

When  $\alpha > \beta$ ,

$$u_C = \frac{1}{2} \gamma H_K \Delta \frac{\alpha}{\alpha - \beta} \tag{23}$$

$$\langle v \rangle = \frac{\beta}{\alpha} u \qquad (u < u_C)$$

(24)

$$\langle v \rangle = \frac{\beta}{\alpha} u + \frac{\sqrt{\left(1 - \frac{\beta}{\alpha}\right)^2 u^2 - \left(\frac{1}{2}\gamma\Delta H_K\right)^2}}{1 + \alpha^2} \qquad (u > u_C)$$

(25)

When  $\alpha = \beta$ ,

$$\langle v \rangle = u \tag{26}$$

where  $u_{WB}$  is the Walker breakdown velocity,  $u_C$  is the critical velocity corresponding to the critical current density of DW motion. In order to achieve a high speed racetrack memory, the current density should be more or far more than the critical one. In both cases, when applying a much higher current, the DW velocity approaches to spin current velocity. Therefore, we take this assumption into account, which means we use the spin current velocity to directly represent DW velocity. Thus,

$$V_j = u = \frac{\mu_B P j_p}{eM_S} \tag{27}$$

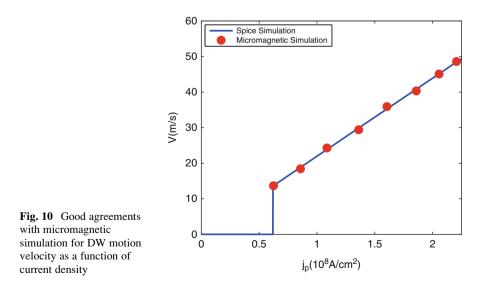

We verified this physical model by comparing with the micromagnetic simulations done by Ohno group (see Fig. 10) [61]. In this case, we suppose that the DWs are definitely pinned when the current density is lower than the critical one, the velocity is thus kept to zero in this condition. From the figure, a current density of

$\sim 2 \times 10^8$  A/cm<sup>2</sup> can trigger a DW motion in 50 m/s, which is beneficial for the logic and embedded memory circuits.

By considering the distance W between two adjacent constrictions (see Fig. 7), we can calculate the necessary pulse duration for current to move one storage element by the Eq. (28). For example, when W is 40 nm, the DW velocity is 50 m/s, the pulse duration can be as small as 0.8 ns. If neglecting the nucleation process, the frequency of racetrack memory can thus be as high as 1 GHz. If considering the nucleation process time (e.g., 1–2 ns), the frequency can still be 500 MHz.

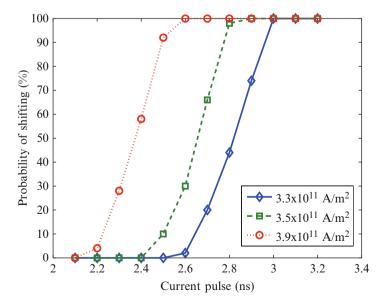

$$D = W/V_{i} \tag{28}$$

Caused by the thermal activation, stochastic nature has been found for DW motion in diverse structures and materials. With the reduction of the applied current or field by optimizing the techniques and the materials, the stochasticity of DW motion will be further enhanced [62]. DW velocity and displacement are susceptible to stochastic effect, which exerts a considerable influence to the feasibility and reliability of DW-based devices, not only racetrack memory. However, as there have not been some coherent experimental results or physical theories concerning the pure CIDW in PMA materials, we refer to the measurements of DW motions in spin valve induced simultaneously by current and field. Under this condition, after depinning, the DW motion velocity is found to follow a Gaussian-like specific distribution centered with the value calculated by Eq. (27) [63]. We analyze the dependence of cumulative probability of DW motion versus different current pulse durations and magnitudes in Fig. 11. It illustrates a coherent functionality of stochastic behavior where we can also find that higher and longer current pulse yields a more probable DW motion.

Fig. 11 Dependence of cumulative probability of DW motion versus shifting current pulse duration and magnitude

#### 3 Current-Induced Magnetic Switching Based Hybrid Spintronics/CMOS Circuits for High-Performance Computing

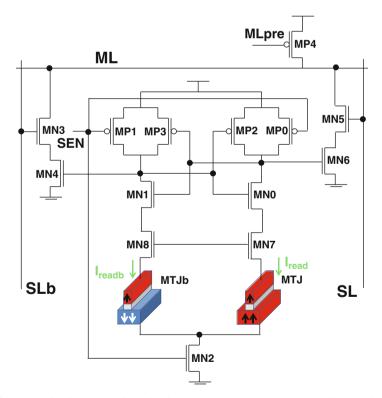

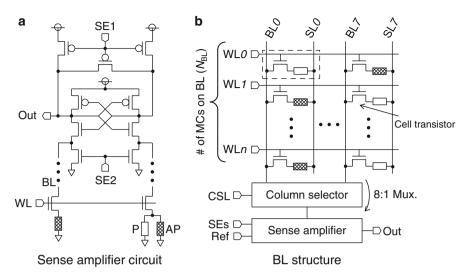

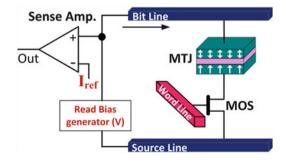

#### 3.1 Sensing Circuit

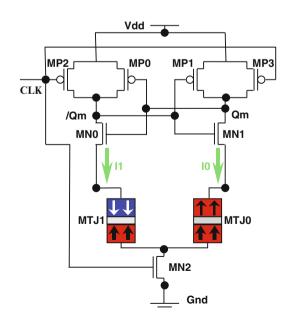

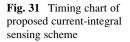

Due to the TMR effect, MTJ presents the property of resistance difference for different states. This resistance property allows MTJ to be compatible with CMOS sense amplifier circuit that detects the MTJ's configuration and amplifies them to logic level. Among various sense amplifiers [64–66], pre-charge sense amplifier (PCSA) is proposed to provide not only the best tradeoff between sensing reliability and power efficiency, but also high-speed performance [59]. Thereby we focus on PCSA and apply it for the hybrid logic circuits involved in this chapter.

The PCSA circuit (see Fig. 12) consists of a pre-charge sub-circuit (MP2-3), a discharge sub-circuit (MN2) and a pair of inverters (MN0-1 and MP0-1), which act as an amplifier. Its two branches are normally connected to a couple of MTJs with complementary states. It operates in 2 phases: "Pre-charge" and "Evaluation". During the first phase, "CLK" is set to "0" and the outputs ("Qm" and "/Qm") are pulled-up to "Vdd" or logic "1" through MP2-3 while MN2 remains off. During the second phase, "CLK" becomes "1", MP2-3 are turned off and MN2 on. Due to the resistance difference between the two branches, discharge currents are different. The lower resistance branch will be pulled-down to reach more quickly the threshold voltage of the transistor (MP0 or MP1), at that time, the other branch will be pulled up to "Vdd" or logic "1" and this low-resistance branch will continue to drop to "Gnd" or logic "0".

**Fig. 12** Pre-charge sense amplifier (PCSA) for MTJ state detection and amplification to logic level

Fig. 13 PCSA sensing operation in the case of MTJ0 with "parallel" state and MTJ1 with "antiparallel" state

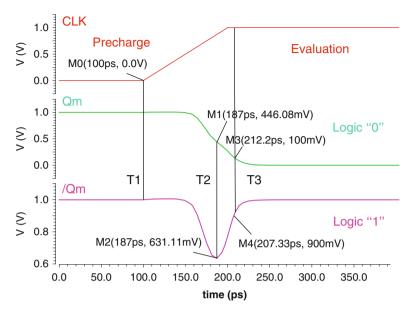

Figure 13 shows a sensing operation of PCSA in the case of MTJ0 with "parallel" state and MTJ1 with "anti-parallel" state. Before the moment "T1", it is "Precharge" phase. Both outputs are pulled up to 1 V. Then the "Evaluation" phase starts from "T1", two branches begin to discharge after a small delay considering the rising time of "CLK" signal. At the time "T2", the branch "Qm" reaches the threshold firstly and this branch will continue to decrease to "0". At the same time, MP0 begin to work and recharge the complementary branch "/Qm" back to "1". This sensing operation is so speedy. From the figure, we can find the whole process costs a sensing delay less than 100 ps. From the point of view of consumption energy, a sensing operation can only cost as low as 10 fJ. This high-speed and low-power feature makes PCSA suitable for the logic applications.

We use PCSA circuit in the hybrid MTJ/CMOS design for the other reason: the read disturbance induced by sensing operations can be significantly decreased. It is important for embedded STT-MRAM as it is an intrinsic nature and difficult to correct in logic circuit where complex error correction circuit (ECC) is prevent to ensure fast computing speed (e.g., 1 GHz). The read disturbance can be regarded as the unexpected switches during the sensing operation. As the sensing current is usually much lower than the critical current, the switch probability can be described by Néel-Brown model. If there are N bits of MTJs in the chip, the chip failure rate  $F_{chip}$  can be calculated by Eq. (29).

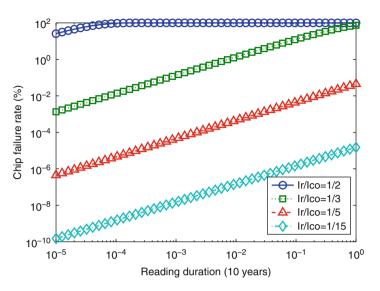

Fig. 14 Dependence of chip failure rate on reading duration for different reading current

$$F_{chip} = 1 - \exp\left[-N\frac{\tau}{\tau_0} \exp\left(-\Delta\left(1 - \frac{I_r}{I_{C0}}\right)\right)\right]$$

(29)

where N is the number of bits per word,  $I_r$  is sensing current,  $I_{C0}$  is the critical current,  $\tau$  is the read duration and  $\tau_0$  is the attempt period. As shown in Fig. 14, lower  $I_r$  and shorter  $\tau$  can reduce greatly the chip failure rate for the STT-MRAM with the same thermal stability factor  $\Delta = 40$ .

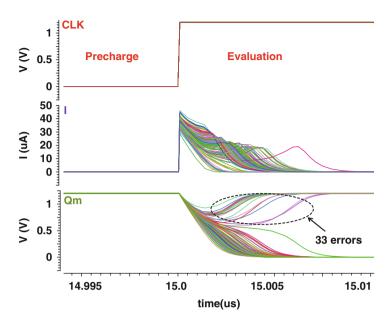

In reality, numbers of words of memories (e.g., 1 k) normally share a sense amplifier. As shown in Fig. 15, a 16 k-bit (1 k words of 16 bits) PCSA sensing circuit has been studied. This enormous parallel structure leads to a huge capacitance, which drives the current pulse through the MTJ. As a result, an evaluation phase lasts almost 10 ns. By taking the effect of stochastic behavior into account, Monte-Carlo simulations after 1  $\mu$ s of sensing duration (i.e., 1,000-time sensing operations) has been performed (see Fig. 16). We found that the 33 errors occurred among 100 simulations. They are caused by either mismatch and process variations of CMOS part or STT stochastic behaviors of MTJ, or sometimes by both of them.

To identify the impact from each of them, we also performed Monte-Carlo simulations for sensing circuit with only mismatch and process variations. We found that the read disturbance was ~11 %. Compared with the result presented in Fig. 16, we can conclude that the stochastic behavior of MTJ greatly increases the error probability for a long-pulse current, and that this PCSA is not suitable for very large memory systems.

Fig. 15 Schematic for 16 k-bits PCSA sensing circuit (m = 16, n = 1 k)

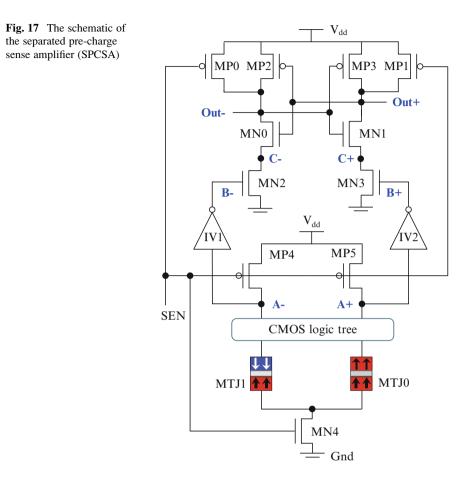

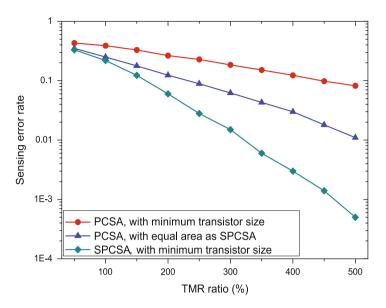

To improve further the sensing reliability, a separated PCSA (SPCSA) was proposed, as shown in Fig. 17 [67]. The basic structure as well as the operation of SPCSA is similar to that of the PCSA. The main difference is that SPCSA separates the discharging and evaluation stages with two different paths, which alleviate greatly the voltage headroom problem, enabling it to operate at a relatively lower supply voltage. Meanwhile, thanks to the separated discharge and evaluation stages, we can amplify the input signals before entering the evaluation stage so as to tolerate the input-offset. In addition, two inverters (IV1 and IV2) and two NMOS transistors (MN2 and MN3) are added connecting between the discharging and evaluation stages, to amplify the limited current or voltage difference (due to the limited TMR ratio) between the two discharging paths flowing through MTJ0 and MTJ1, thus tolerating significantly the process variations and increasing greatly the sensing margin. Figure 18 shows the statistical sensing error rate of SPCSA compared to PCSA. As can be seen, SPCSA provides a much higher sensing reliability with the same hardware.

Fig. 16 Monte-Carlo simulation of a 16 k-bit PCSA circuit

#### 3.2 Writing Circuit

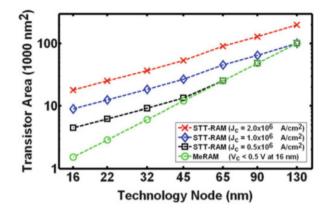

According to STT switching mechanism, a bi-directional current is required to switch the magnetization in free layer of MTJ. In order to achieve high-speed logic design, high current is required to ensure the speed. In contrast to the low power and low area of the sensing circuit, the writing circuit for PMA STT MTJ occupies the main area and power of the whole circuit. As a result, the study on writing circuit is of importance to hybrid MTJ/CMOS circuit design.

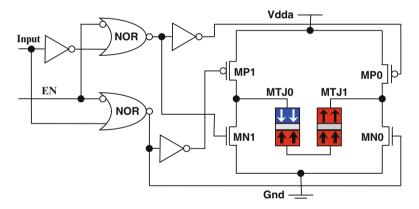

In concert with the sensing circuit for a couple of MTJs with complementary states, a writing circuit to generate the bi-directional current for switching a couple of MTJs is designed as Fig. 19. Two NMOS (MN0-1) and two PMOS (MP0-1) transistors construct the main circuit. Each time one NMOS and one PMOS are always left open and the others closed, which creates a path to make the current pass from "Vdda" to "Gnd". Through two NOR and three NOT logic gates, the signals "Input" and "EN" control respectively the current direction and activation. Normally, it requires a "Vdda" higher than "Vdd" for logic operations to avoid the area overhead in the write circuit.

In order to generate the maximum current flowing through the couple of MTJs, both the transistors (one PMOS and one NMOS) should operate in their linear region above the threshold voltage  $V_{TH}$  to obtain the relatively lower resistances. In this case, they should satisfy the conditions:  $V_{DS} \ll 2(V_{GS}-V_{TH})$  for NMOS and  $V_{DS} \gg 2(V_{GS}-V_{TH})$  for PMOS. Their resistances,  $R_{on}$  and  $R_{op}$ , can be

approximately expressed by Eqs. (30) and (31), and the generated current can be obtained through the Eq. (32),

$$R_{on} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

(30)

$$R_{op} = \frac{1}{\mu_p C_{ox} \frac{W}{L} \left( V_{SG} - |V_{TH}| \right)}$$

(31)

$$I_{write} = \frac{V dda}{R_p + R_{ap} + R_{on} + R_{op}}$$

(32)

where  $\mu_n$  is the electron mobility,  $\mu_p$  is the hole mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the channel width, L is the channel length,  $V_{GS}$  is the gate-source voltage.

Fig. 18 Sensing error rate of the SPCSA circuit with Monte-Carlo simulations

Fig. 19 Full writing schematic for STT writing approach, which is composed of two modified inverters and logic control circuits

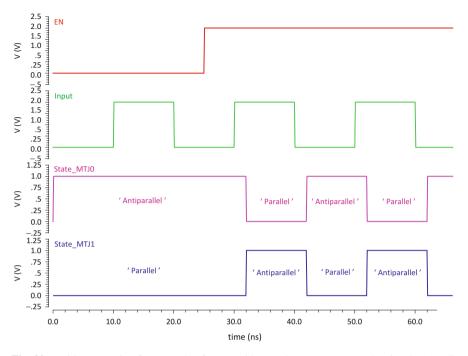

By simulating a writing operation including anti-parallel to parallel switching and parallel to anti-parallel switching (see Fig. 20). We can find that the writing operation is not activated until the signal "EN" is set to "1". The states of the couple of MTJs remain always opposite and the switching direction follows the signal "Input".

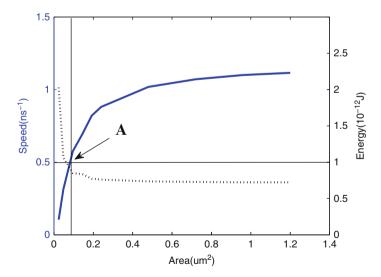

From Eqs. (30)–(32), we find that the most efficient method to improve the current value is by increasing *W*, but this leads to significant area overhead. Figure 21 shows a study of area, speed and energy performance for this circuit. Here, only the area of four transistors (MN0-1, MP0-1) has been taken into account as the area of logic control circuit is the same for different simulation and is often in

Fig. 20 Writing operation for a couple of MTJs with complementary states. The signals "Input" and "EN" control respectively the current direction and activation

Fig. 21 Dependence of circuit switching speed (*solid line*) and energy dissipation (*dotted line*) versus die area with four transistors (MN0-1, MP0-1)

the minimal size. A strong dependence between area and speed can be found, especially when the area is smaller than  $0.2 \ \mu m^2$ . The speed improvement becomes less significant for larger areas and saturates at ~1.1 GHz, which is different from the 2 GHz obtained with a single cell. There are two reasons for explaining this: first, "Vdda" is set to 2 V as 2.2 V is the breakdown limit for CMOS technology node [68]; second, there are a couple of MTJs, so the bias-voltage for each one cannot be larger than 1 V as there is also bias on the transistors in the circuit.

The energy of each switching operation has been calculated with Eq. (33). We also find a turning point, ~0.1  $\mu$ m<sup>2</sup>, below which the energy will be increased rapidly with a smaller area due to the extremely long switching duration as the current  $I_{write}$  approaching to the threshold  $I_{C0}$ . Contrarily, the energy is nearly the same for whatever the size larger than ~0.1  $\mu$ m<sup>2</sup>. This is firstly because that the writing current and speed approach to be saturated. Even if the writing current can increase continuously, from Eq. (11), the current is inversely proportional to the switching duration when the current is much higher than the critical one. Therefore the energy will inevitably be saturated for a high writing current.

$$E_{operation} = V dda \times I_{write} \times Duration \tag{33}$$

The region around the crossing point of the two curves (point "A" in Fig. 21) can be localized. It can be considered as a good tradeoff among the area ( $\sim 0.096 \,\mu\text{m}^2$  or 30 F<sup>2</sup>), power (1 pJ) and speed ( $\sim 500 \text{ MHz}$ ) performance of this switching circuit, and be suitable to build up both logic chip and memory. This analysis can also help to investigate the circuits with special requirements like 800 MHz operating frequency.

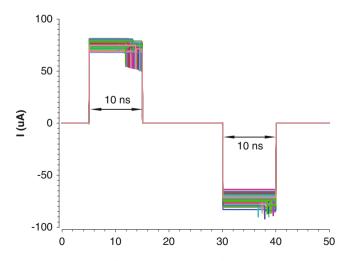

For the advanced node below 90 nm, high reliability is becoming more and more crucial for the IC design [69–72]. Thanks to the integration of STT stochastic behavior into this model, an overall reliability investigation becomes possible. Figure 22 shows the statistical Monte-Carlo simulations of 100 complete writing

Fig. 22 Monte-Carlo simulation of a whole writing operation implemented by the writing circuit

operations using the writing circuit shown in Fig. 19 (however, instead of a couple of MTJs, there is only one MTJ connected in the circuit for this part of study). The complete writing operation includes the switching from parallel to anti-parallel and from anti-parallel back to parallel. Similarly to the case of the sensing circuit, the writing current at each write event is different because of the mismatch and process variation of CMOS part. The switching delay times vary randomly due to the stochastic behavior of MTJ cell. Since writing current is normally larger than sensing current, the stochastic effect in writing operation is relatively weaker than that in sensing operation. This can be proven by Fig. 22, the variation of every event is not so enormous.

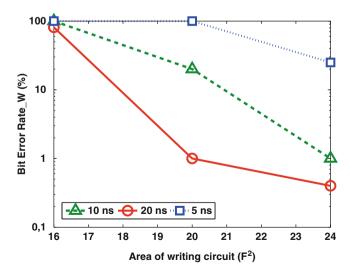

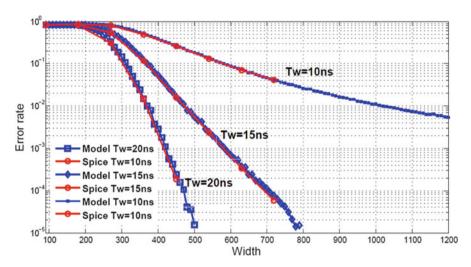

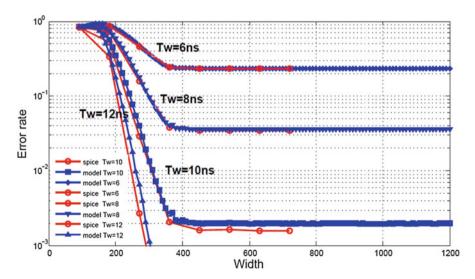

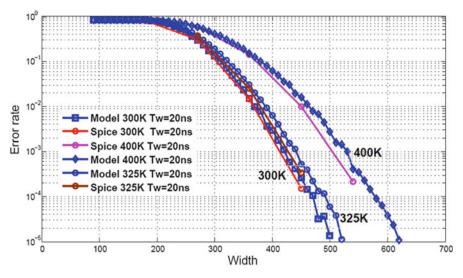

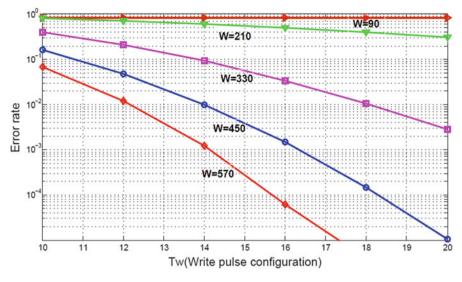

Writing current magnitude and pulse duration are two key factors for the writing operation. As mentioned above, the writing current magnitude is dependent on the die area of writing circuit. We then perform the Monte-Carlo simulations for different writing pulse durations (5, 10 and 20 ns) to observe the dependence of writing Bit Error Rate (BER\_W) versus die area of writing circuit (four main transistors: MP0-1 and MN0-1). The simulation results shown by Fig. 23 demonstrate their tradeoff relation: the increase of area can improve the BER performance. The reason is that a larger circuit allows larger write current, which in average reduces the time required to switch. For a given pulse duration, this increases the switching probability. Correlatively, it is observed that a longer pulse can also increase the reliability, which confirms the explanation mentioned above.

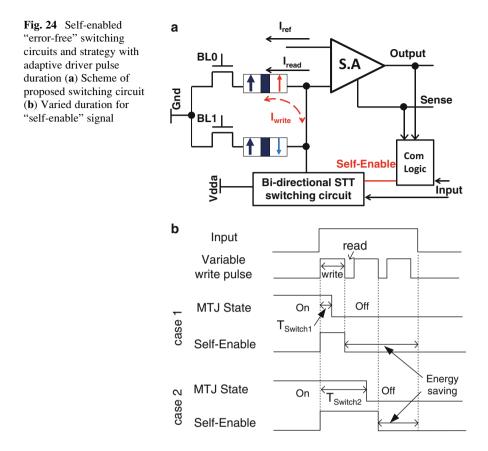

On the other hand, in order to overcome both power and reliability issues of conventional switching circuits due to the STT stochastic behavior, a self-enabled "error-free" strategy was proposed [73]. The corresponding circuit schematic is shown in Fig. 24. A sense amplifier (S.A) associated to the MTJ detects its state and outputs the data in logic level. The "self-enable" signal depends on the comparison

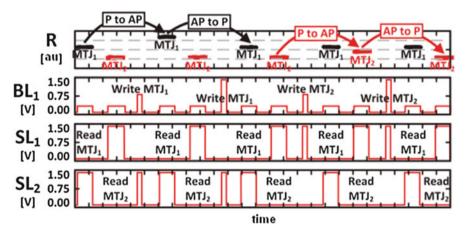

Fig. 23 Dependence of writing Bit Error Rate (BER\_W) versus die area of writing circuit

result between output and "Input" data. For instance, it becomes "ON" as output is different from "Input" data. The fixed long writing pulse is replaced by a sequence of short duration  $T_{SS}$  including both switching and sensing operations. Thanks to the stochastic behaviors of STT magnetic switching, the state of MTJ can be changed just after one short write pulse, as shown in Fig. 24b. After that, "self-enable" is set to "OFF" and no current flows through the MTJ. Different from a self-adaptive write circuit designed for memristor, the proposed circuit takes benefits from the stochastic behaviors of STT switching. Moreover, periodic sensing is used to obtain the STT-MRAM storage in logic level for the comparison with "Input" data. This is due to the relatively low TMR or  $R_{Off}/R_{on}$  ratio of MTJ (e.g., 150–250 %). The frequency of read operations equals normally to the global clock (e.g., 500 MHz).

This switching circuit with self-enable mechanism presents a number of advantages. Firstly, it allows "error-free" as the switching operation becomes fully deterministic instead of stochastic behaviors caused by the intrinsic STT and PVT variations. As the write pulse duration is shortened and the number of switching operation is also reduced, the lifetime of oxide barrier can be greatly improved. As mentioned above, the state of MTJ may be erroneously changed by a read current, "self-enable" becomes automatically "ON" to correct this error. Thereby, this proposed circuit provides evident high reliability.

Secondly, high power efficiency can be achieved by eliminating completely the additional power to tolerate the process voltage temperature (PVT) variations and stochastic behaviors. Another power saving comes from the reduced switching numbers as the "self-enable" signal is activated only while the stored data is different from "Input" data. On average, half of the switching operations can be economized, but exact power saving depends greatly on applications. Note that, for asynchronous applications, in addition to power saving, better operating speed could also be expected.

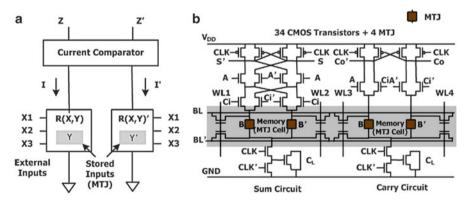

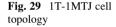

#### 3.3 Magnetic Full Adder

Aiming to overcome the issue of rising standby and dynamic power, magnetic processor based on spintronic devices is thus expected. Since addition is the basic operation of the arithmetic/logic unit of any processors, MFAs attract a lot of attention and several designs based on diverse technologies are proposed in the last years [18, 19]. Here, we present a 1-bit MFA based on PMA STT MTJ (STT-MFA) [74] and a multi-bit MFA based on PMA racetrack memory [75].

#### 3.3.1 1-Bit MFA Based on PMA STT MTJ

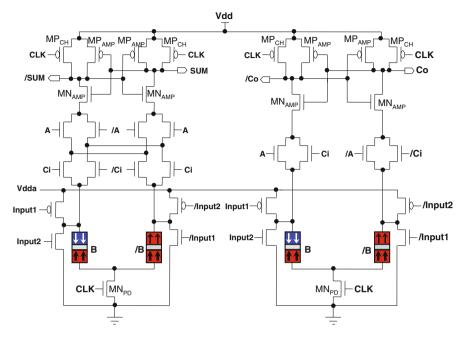

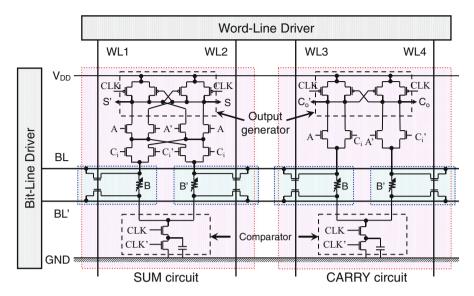

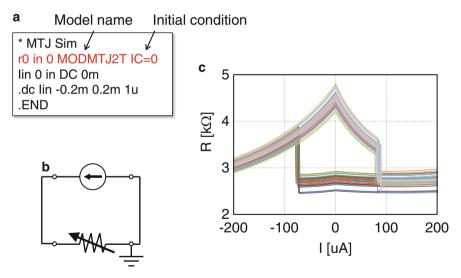

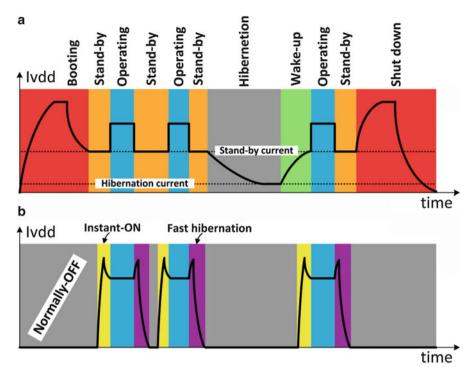

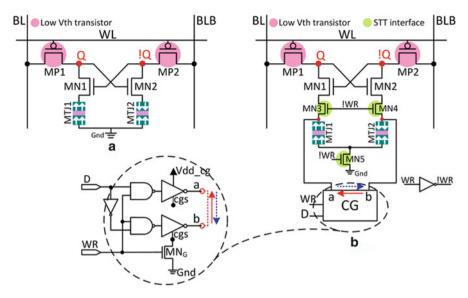

Figure 25 shows a 1-bit STT-MFA circuit, which is based on the generic logic-inmemory structure [74]. To evaluate the logic function, PCSA circuit is used. The inputs are "A", " $C_i$ " and "B", and the outputs are "SUM" and " $C_o$ ". Among them, the input "B" relates to non-volatile storage PMA STT MTJ. The MOS tree is designed according to Eqs. (34)–(37) and the truth table shown in Table 1.

$$SUM = A \oplus B \oplus C_i = ABC_i + A\overline{BC_i} + \overline{ABC_i} + \overline{ABC_i}$$

(34)

$$\overline{SUM} = AB\overline{C_i} + \overline{ABC_i} + \overline{ABC_i} + \overline{ABC_i}$$

(35)

$$C_o = AB + AC_i + BC_i \tag{36}$$

$$\overline{C_o} = \overline{AB} + \overline{AC_i} + \overline{BC_i}$$

(37)

For "SUM" logic, the MOS tree corresponds directly to the logic relationship among the inputs "A", " $C_i$ " and "B", we can simply adapt it to the general structure with a couple of complementary PMA STT MTJ. However, it is a little difficult for " $C_o$ " logic as there is the term  $AC_i$  in the logic function Eq. (36) and we cannot adapt the schematic to the general "logic-in-memory" structure. It can be inferred that the impact of the term  $AC_i$  on the resistance is equivalent to a sub-branch

Fig. 25 STT-MFA architecture with "SUM" (*left*) and output carry " $C_o$ " (*right*) sub-circuits, "A" is volatile data for computing, "B" is non-volatile data using as quasi-constant [74]

| table of<br>"logic gate | Α | B | С | SUM | Co |

|-------------------------|---|---|---|-----|----|

|                         | 0 | 0 | 0 | 0   | 0  |

|                         | 0 | 0 | 1 | 1   | 0  |

|                         | 0 | 1 | 0 | 1   | 0  |

|                         | 0 | 1 | 1 | 0   | 0  |

|                         | 1 | 0 | 0 | 1   | 0  |

|                         | 1 | 0 | 1 | 0   | 1  |

|                         | 1 | 1 | 0 | 0   | 1  |

|                         | 1 | 1 | 1 | 1   | 1  |

**Table 1** Truth table of "*SUM*" and " $C_o$ " logic gate for MFA

connecting PCSA and the discharging transistor (*MN2* in Fig. 12). Table 2 exhibits the true table and the resistance configuration of " $C_o$ " logic.  $R_{OFF}$  and  $R_{ON}$  are respectively the close and open resistances of MOS transistor.  $R_L$  and  $R_R$  are respectively the whole resistance of the left and right branch of PCSA. We can find that whatever the value of "A" and " $C_i$ ", the sub-branches  $AC_i$  and  $\overline{AC_i}$  have no impact on the output. If "A" and " $C_i$ " are different, the resistances of the two subbranches are the same. If they are the same, their comparison corresponds to that of  $R_L$  and  $R_R$  in the condition of  $R_{ON} > R_{AP}$ , which is always true for PMA STT MTJ under present technology condition. This allows the term  $AC_i$  to be deleted from Eq. (36) and we can obtain the " $C_o$ " logic circuit shown in Fig. 25.

| Α | B | C | Resistance comparison | Co | Sub-branch AC <sub>i</sub> | Sub-branch $\overline{AC}_i$ |

|---|---|---|-----------------------|----|----------------------------|------------------------------|

| 0 | 0 | 0 | $R_L > R_R$           | 0  | $2R_{OFF}$                 | $2R_{ON}$                    |

| 0 | 0 | 1 | $R_L > R_R$           | 0  | $R_{OFF} + R_{ON}$         | $R_{OFF} + R_{ON}$           |

| 0 | 1 | 0 | $R_L > R_R$           | 0  | $2R_{OFF}$                 | $2R_{ON}$                    |

| 0 | 1 | 1 | $R_L < R_R$           | 0  | $R_{OFF} + R_{ON}$         | $R_{OFF} + R_{ON}$           |

| 1 | 0 | 0 | $R_L > R_R$           | 0  | $R_{OFF} + R_{ON}$         | $R_{OFF} + R_{ON}$           |

| 1 | 0 | 1 | $R_L < R_R$           | 1  | $2R_{ON}$                  | $2R_{OFF}$                   |

| 1 | 1 | 0 | $R_L < R_R$           | 1  | $R_{OFF} + R_{ON}$         | $R_{OFF} + R_{ON}$           |

| 1 | 1 | 1 | $R_L < R_R$           | 1  | $2R_{ON}$                  | $2R_{OFF}$                   |

**Table 2** Truth table and resistance configuration of " $C_a$ " for MFA

The PMA STT MTJs connect serially with a common central point. In order to program MTJs, we use a writing circuit composed of pass transistors, which are connected respectively to the bottom and top electrodes of the serial branch. In such a manner, as a control signal ("*Input1*" or "*Input2*") is activated, the first PMA STT MTJ noted "*B*" is put in high resistance state ( $R_{AP}$ ) or low resistance state ( $R_P$ ) while the second PMA STT MTJ noted "/*B*" is put in the complementary state  $R_P$  or  $R_{AP}$ .

It is noteworthy that there is neither capacitance for the data sensing and nor magnetic field for data programming in this new structure beyond the previous structures [18, 19]. Therefore, this design allows efficient area minimization and is suitable for advanced fabrication nodes below 65 nm.

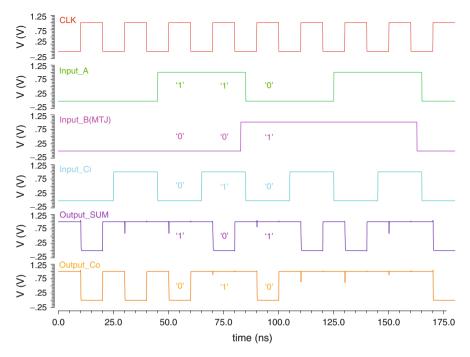

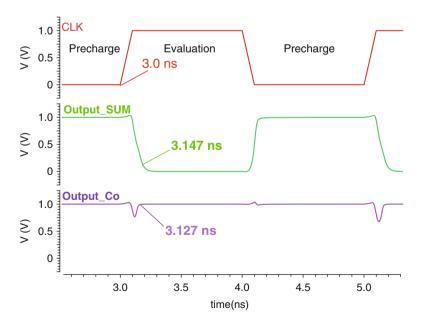

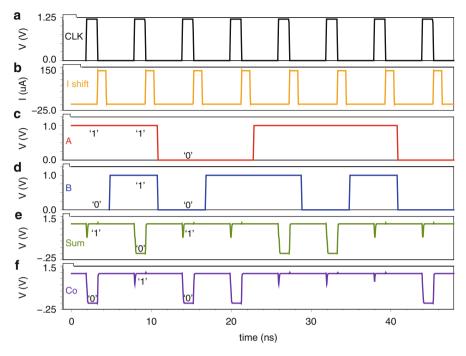

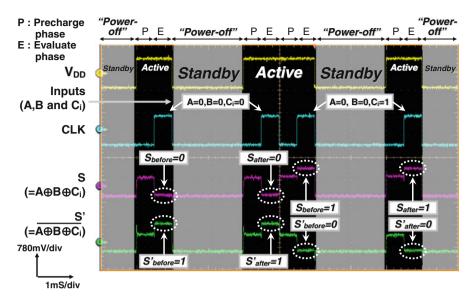

Figure 26 illustrates the transient simulation of 1-bit STT-MFA shown in Fig. 25. It is performed by using PMA STT MTJ compact models introduced above and CMOS 40 nm design kit. The time-dependent behaviors of outputs ("*SUM*" and " $C_o$ ") confirm the logic functionality of full addition. For instance, for the operation "A" = "1", "B" = "0", " $C_i$ " = "0", the result is "1" and no carry yields; for the operation "A" = "1", "B" = "0", " $C_i$ " = "1", the result is "0" and the carry is "1".

Figure 27 emphasizes one sensing operation of this STT-MFA and shows the analog behaviors. It confirms the pre-charge, evaluation and amplification process described previously. Moreover, we find that the sensing delay of " $Output_C_o$ " (~127 ps) is shorter than that of " $Output_SUM$ " (~147 ps). This is due to the higher resistance of the branch associated with " $Output_SUM$ ", leading to lower current and slower amplification.

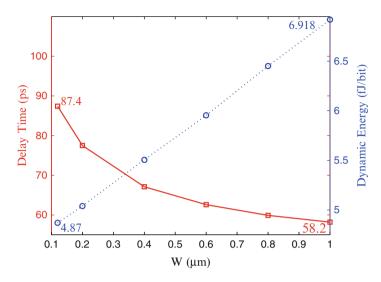

The delay time and dynamic energy are generally two crucial parameters to evaluate the performance of computation system. We have studied the effects of three possible factors: the size of discharge transistor ( $MN_{PD}$  in Fig. 25), PMA STT MTJ resistance-area product (RA) and TMR ratio. Figure 28 demonstrates the performance dependence of this STT-MFA in terms of delay time and dynamic power on the size of discharge transistor. We can find a tradeoff between the speed and power performance by varying the die area. A larger discharge transistor can drive a higher sensing current and faster amplification of PCSA circuit, but cost more energy.

Fig. 26 Transient simulations of 1-bit STT-MFA in 40 nm node

Fig. 27 One sensing operation of the PCSA based STT-MFA: outputs are pre-charged as CLK is set to "0" and are evaluated as CLK is set to "1"

Fig. 28 Dependence of delay time (*red solid line*) and dynamic energy (*blue dotted line*) on the width of discharge transistor for STT-MFA

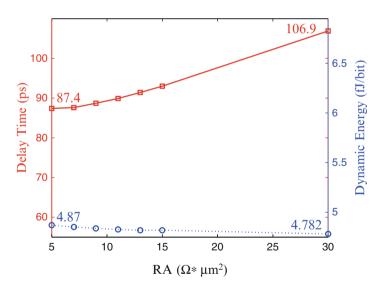

Fig. 29 Dependence of delay time (*red solid line*) and dynamic energy (*blue dotted line*) on the resistance-area product (*RA*) of PMA STT MTJ

Figure 29 shows the RA dependence for this STT-MFA. By decreasing RA, the delay time becomes shorter while keeping a relatively steady dynamic power performance. This confirms that the speed advantage of using low RA.

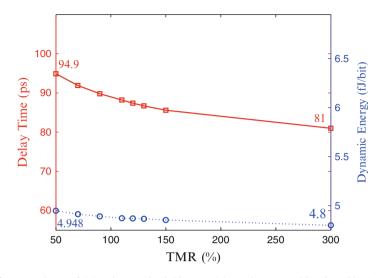

We also investigate the dependence between TMR ratio of PMA STT MTJ and STT-MFA performance. Figure 30 shows that faster speed is possible by increasing the TMR ratio while the dynamic energy changes slightly.

Fig. 30 Dependence of delay time (*red solid line*) and dynamic energy (*blue dotted line*) on PMA STT MTJ TMR ratio for 1-bit STT-MFA

| Performance            | CMOS full adder (40 nm) | STT-MFA         |

|------------------------|-------------------------|-----------------|

| Delay time             | 75 ps                   | 87.4 ps         |

| Dynamic power @500 MHz | 2.17 μW                 | 1.98 μW         |

| Standby power          | 71 nW                   | <1 nW [31]      |

| Data transfer energy   | >1 pJ/bit               | <1 fJ/bit       |

| Die area               | 46 MOS                  | 38 MOS + 4 MTJs |

Table 3 Comparison of 1-bit STT-MFA with CMOS only full adder

According to the above analyses, a PMA STT MTJ with lower *RA* and higher TMR ratio is expected to perform fast computation while keeping nearly the same dynamic energy. In the recent experimental demonstration of the MTJ, a low *RA* (e.g., 5  $\Omega \mu m^2$ ) and high TMR ratio (e.g., 200 %) can be achieved in PMA STT MTJ [51, 76, 77].

We compare the STT-MFA with conventional CMOS only full adder in terms of delay time, dynamic power, standby power, data transfer energy and die area (see Table 3). The CMOS-only full adder is taken from the standard cell library of STMicroelectronics 40 nm design kit. Two full latches are added to synchronize the outputs with clock signal.

In conventional computing architectures, logic and memory are completely separated [78]. In order to perform a logic operation, both the instruction and data need to be read from memory units (i.e., cache and main memories), and then moved to logic unit. The results are transferred back to the memory units after the computing. In the STT-MFA circuit based on "logic-in-memory" architecture, logic operations are processed directly with the magnetic data stored in MTJs and

the addition result is written to other MTJs for the next operations. Long latency and high dynamic power due to data moving can be significantly economized. For example, the data transfer energy (~1 pJ/mm/bit @22 nm [1]) becomes much lower thanks to the shorter distance between memory and computing unit, which is about some  $\mu$ m or below in STT-MFA instead of some mm for CMOS only logic circuit.

Furthermore, thanks to the 3D integration of STT-MRAM, the die area of this design (38 MOS + 4 MTJs) is advantageous compared to those of the CMOS full-adder (46 MOS). However, its energy-delay product (EDP) exceeds that of a CMOS full-adder by approximately 10 % since it takes more time for PCSA amplification process. Due to the non-volatility of PMA STT MTJ, the new chip can be powered off completely and this allows the standby power to be reduced significantly down to 0.75 nW [77]. Thereby, the STT-MFA can greatly reduce the consumption in a full computing system, especially for those normally in OFF state.

Another critical idea of this design is to use a programming frequency (e.g., 1 kHz) of STT-MRAM much lower than the computing frequency. Thereby, the switching power for non-volatile storage becomes insignificant to other power consumption in a full system. We can continue to reduce it by shortening the non-volatile data retention (e.g., 1 day). Moreover, the programming energy for the non-volatile data (bit "B" in Fig. 25) can be reduced, following the area minimization [79] and new material development for MTJs (e.g., ~0.1 pJ/bit).

#### 3.4 Multi-Bit MFA Based on Racetrack Memory

PMA racetrack memory is distinguished as it can store and shift multiple bits of data through CIDW motion along a magnetic nanowire. This advantageous feature makes it possible to design a high speed and compact multi-bit serial MFA.

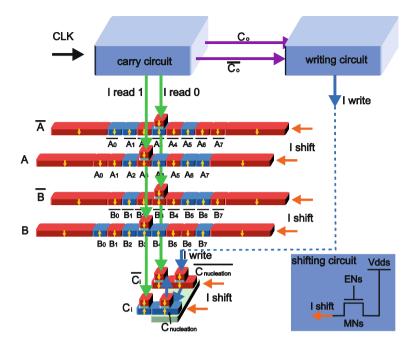

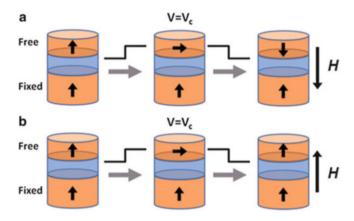

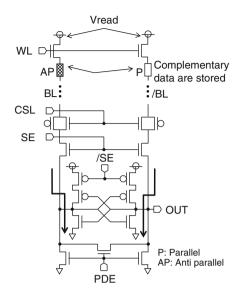

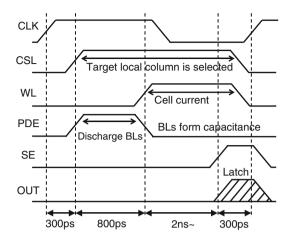

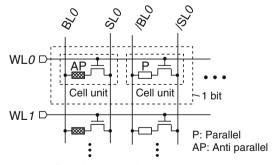

Figure 31 shows the detailed schematic of CARRY circuit of the multi-bit MFA based on PMA racetrack memory including MTJ writing circuit [75]. "A" and "B" are multi-bit input data stored in different nanowires. Each data is designed to be stored in dual magnetic nanowires with exactly opposite configuration to minimize the variation between two complementary data (e.g., "A" and "Å") as the same  $I_{shift}$  is used in the dual nanowires to move the DWs [3]. At each rising edge of CLK, " $C_o$ " and " $\overline{C}_o$ " are evaluated through the PCSA circuit and become inputs of a writing circuit, which generates writing current  $I_{write}$  to reverse or just conserve the state of nucleation MTJs (" $C_{nucleation}$ " and " $\overline{C}_{nucleation}$ "). At each falling edge of CLK, propagating current  $I_{shift}$  induces the DW motion of all magnetic nanowires ("A", " $\overline{A}$ ", " $\overline{B}$ ", " $\overline{C}$ ", " $\overline{C}$ ") simultaneously, moves next magnetic domains under the read MTJ for next adding operation.

The operation of SUM circuit is similar to that of CARRY: the SUM output and its complement are evaluated through the SUM PCSA circuit and become inputs of SUM writing circuit, which generates the writing current to write these values into

Fig. 31 CARRY circuit of multi-bit MFA based on PMA racetrack memory including MTJ writing circuit

the most significant bits of SUM nanowire. These bits are then shifted in the way that at the end of all additions, the sooner the bit is calculated, the greater its weight is.

The transient simulation of this multi-bit MFA shows the addition operation of two random 8-bit words: "A" = "01110011" (Fig. 32c) and "B" = "01011010" (Fig. 32d). "CLK" (Fig. 32a) drives PCSA circuit and "Ishift" (Fig. 32b) induces DW motion in the magnetic nanowire. The outputs "SUM" (Fig. 32e) and " $C_o$ " (Fig. 32f) are firstly precharged to logic "1" when "CLK" = "0" and are evaluated when "CLK" is set to "1". The DW motions are implemented in the pre-charge phase in order to avoid the disturbance to the output evaluation. The serial addition is performed from the least "SUM" = "11001101" and simulation result significant bit the and " $C_o$ " = "01110010" confirms the correct operation of MFA.

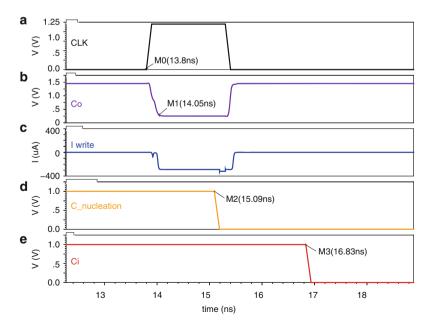

Between two addition evaluations, there is a data transition process to achieve multiple bits operation. Figure 33 demonstrates the CARRY transition including DW nucleation and motion. Carry-out " $C_o$ " (Fig. 33b) is firstly pre-charged to "Vdd" before the time "M0", after the rising edge of "CLK" (Fig. 33a), " $C_o$ " is evaluated by the PCSA and becomes the input signal of writing circuit (Fig. 33b).  $I_{write}$  is generated to nucleate DW in the magnetic nanowire (Fig. 33c, d).  $I_{shift}$  is in the following activated to propagate the DW and replace the value of carry-in " $C_i$ " with " $C_o$ " at the time "M3" for next cycle of addition (Fig. 33e).

**Fig. 32** Transient simulation of the multi-bit MFA. (a) CLK signal (b) Data shifting current pulse  $I_{shift}$  (c) Input data "A" (d) Input data "B" (e) "SUM" (f) " $C_o$ "

Fig. 33 Transient simulation of CARRY storage (a) CLK signal (b) " $C_o$ " (c) DW nucleation current  $I_{write}$  (d) State of DW nucleation MTJ (e) Carry in for next adding operation

We then analyze the performance of this multi-bit MFA in terms of delay and power dissipation. Indeed, several parameters, such as the size of transistors and "Vdd", can affect greatly on them. A first look at the repartition of consumed energy in this MFA shows that the energy for nucleation and propagation is of the same order of magnitude, and higher than that of data sensing or logic computing.

In order to propagate the magnetic domains to their next positions (shift 1 bit), we must supply a current  $I_{shift}$  in a period  $t_{pulse}$ . The period  $t_{pulse}$  is the necessary time for all magnetic domains to move from their current positions to their next positions. It corresponds to the propagation delay, which is inversely proportional to  $I_{shift}$ . Consequently, the propagation energy does not vary much (seeing that this energy is the integral of the product  $V_{pulse} \times I_{shift} \times t_{pulse}$  and the power supply voltage  $V_{pulse}$  is kept invariable). Simulations show that energy needed for shifting all racetrack memories 8 bits is about 29 pJ.

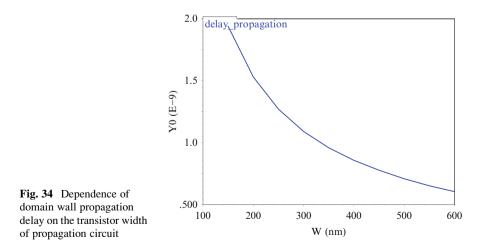

Since the energy needed for propagation is almost invariable, we can reduce the propagation delay by increasing  $I_{shift}$ . Normally, one transistor based current source is used to generate the DW propagation current, thus the size of transistor determines the generated current in propagation circuit. Figure 34 shows the tradeoff dependence of propagation delay on the width of transistor MN2: the reduction of propagation delay at the cost of satisfying the area.

The writing circuit nucleates domain walls under the MTJ write head (e.g., MTJ0 in Fig. 7) by passing through a bi-directional current  $I_{write}$ .  $I_{write}$  is proportional to both supply voltage  $V_{write}$  and transistors' size.  $V_{write}$  will be set as high as possible in order to minimize the size of transistors (MN0-1 and MP0-1) while keeping the switching current at fixed value. In this setup,  $V_{write}$  is set to 2 V to avoid the breakdown of oxide barrier at 65 nm technology node. A higher  $I_{write}$  can reduce the switching delay, but increase the power consumption.

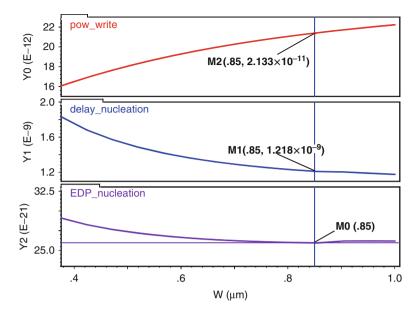

A study of the tradeoff among the width of transistors, switching speed and power dissipation have been made to find out optimal operation point (see Fig. 35). In this analysis, the width of transistors W is started at 0.35  $\mu$ m because  $I_{write}$  is not

Fig. 35 Dependence of energy consumption (pow\_write), switching speed (delay\_nucleation) and the energy-delay product (EDP\_nucleation) versus the width of four transistors using in writing circuit

Table 4 Comparison of 8-bit MFA based on racetrack memory with CMOS only full adder included transferring and writing data

| Performance     | CMOS full adder (65 nm) | MFA                  |

|-----------------|-------------------------|----------------------|

| Write time      | 200 ps                  | 2 ns                 |

| Write energy    | 16 fJ/8 bits            | (21.39+29) pJ/8 bits |

| Transfer time   | ~ns                     | 0                    |

| Transfer energy | 8 pJ/mm (for 8 bits)    | ~0                   |

| Die area        | 310 MOS                 | 23 MOS + 18 MTJs     |

high enough to switch the state of MTJ below this value. This curve shows that one can increase W to reduce the factor of merit EDP until the point "M0"  $(W = 0.85 \ \mu\text{m})$  and then it slightly goes up. Thereby the operating points should be chosen around the optimum (e.g.,  $W = 0.75-1.0 \ \mu\text{m}$ ) to address different applications. For instance, the two markers "M1" and "M2" show that when  $W = 0.85 \ \mu\text{m}$ , the switching power and latency are 21.33 pJ and 1.22 ns, respectively. The switching current  $I_{write}$  equals to 291  $\mu$ A in this case.

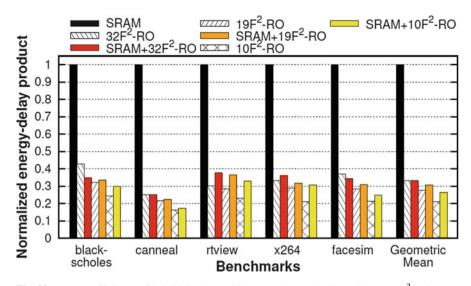

In order to understand the advantages and disadvantages of this multi-bit MFA based on PMA racetrack memory, we compare its performance with that of a CMOS-only series adder (see Table 4), which uses a full adder taken from the library of STMicroelectronics 65 nm design kit.

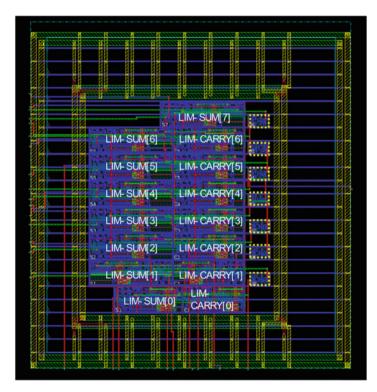

For the comparison with CMOS only multiple bits full adder regarding writing and transferring data, we see that the chip area of the MFA based on PMA racetrack memory is significantly reduced. The 8-bit MFA uses only 23 MOS transistors, 18 MTJs and 8 magnetic nanowires instead of 22 MOS plus  $8 \times 3$  Flip-Flops (310 MOS transistors totally) for an 8-bit series CMOS full adder. Although the number of transistors decrease 13 times, the area reduction is about 4.5 times since the writing circuit and propagating circuit requires the transistors with 6.3 times and 3.3 times minimum width (0.135 µm@65 nm technology node), respectively. The total delay of one operation of the new MFA is ~2.1 ns, composed of DW nucleation (~1.2 ns), motion (~0.7 ns) and detection (~180 ps). It can be thus driven by a CLK frequency up to 470 MHz, which can be further increased with the feature size shrinking. This latency is of the same order with that of CMOS circuit (read time + transfer time + operate time + transfer time + write time). On the contrary, the MFA consume six times dynamic energy more than the CMOS only full adder since energy needed for nucleation and propagation is still too large with current technology. However, we have not yet addressed the static energy in this comparison. Regarding that power must be supplied in order to maintain stored data in CMOSonly storage circuit, the MFA does not require energy to conserve information thanks to its total non-volatility. This allows the circuit to be turned off safely in "idle" mode without data backup. All the operations can be retrieved instantly after power-on. This instant on/off capability promises to overcome completely the rising standby power issue due to leakage currents and could be very useful for normally-off systems [77].

It is important to note that for this non-volatile MFA, operations are performed directly with the data ("A", " $\overline{A}$ ", "B", " $\overline{B}$ ") stored in magnetic nanowires, which plays the role of shift registers. We do not take into account the writing circuits of "A" and "B" to keep the same comparison condition as the writing circuits of data are considered in the CMOS shift register part, not in the adder. The number of writing circuit is then reduced to two for respectively SUM and CARRY circuits, which are shared by the eight bits.

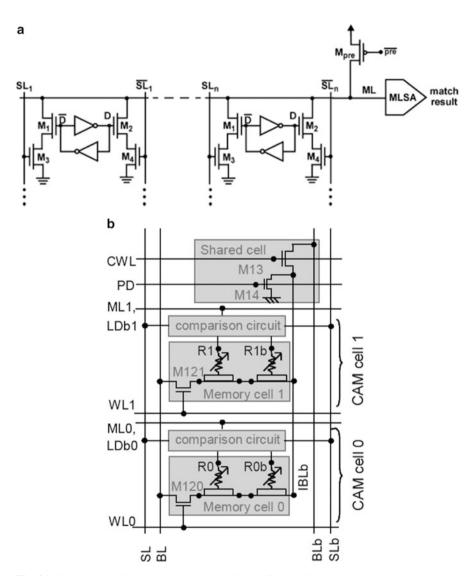

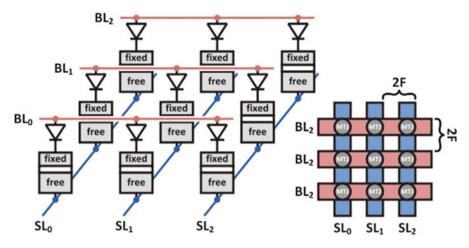

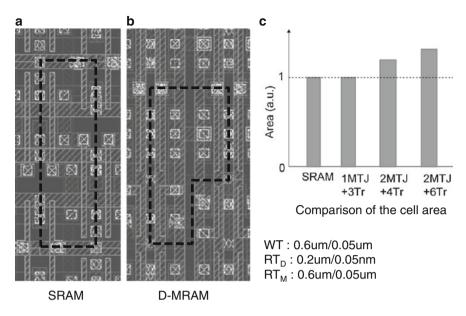

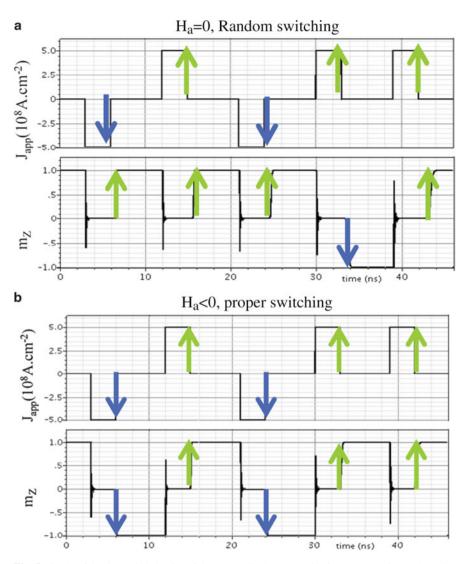

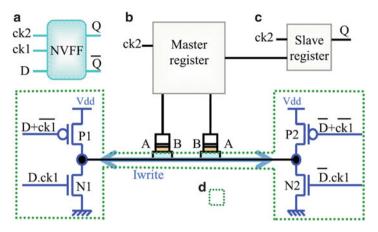

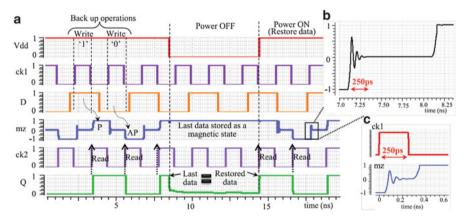

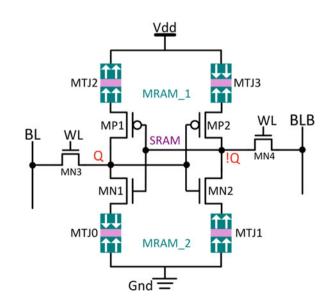

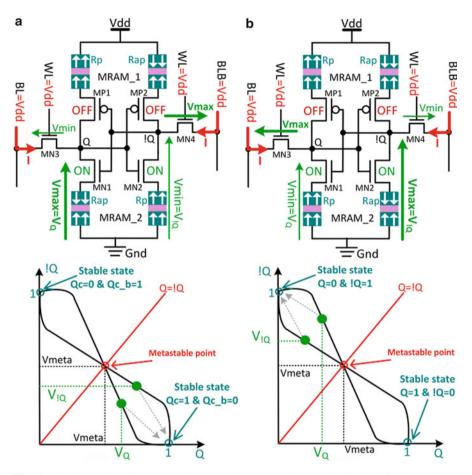

# 3.5 Content Addressable Memory (CAM) Based on Racetrack Memory

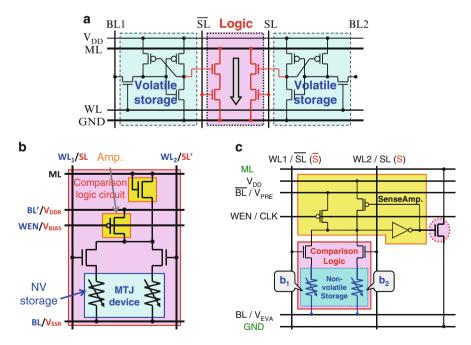

CAM is a computer memory that can output the address of search data. It compares search data with stored data and returns the match location with its high-speed fully-parallel manner. Therefore it is widely used in mobile, internet routers and processors to provide fast data access and ultra-high density [21]. The mainstream CAMs are composed of large-capacity volatile SRAM blocks (see Fig. 36a), which lead to high static power and large die area [80]. These become the key challenges for the future R&D of CAM. Replacing volatile memories by non-volatile memories or applying hybrid non-volatile logic-in-memory circuits is a promising

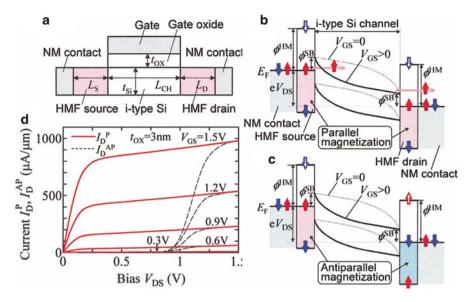

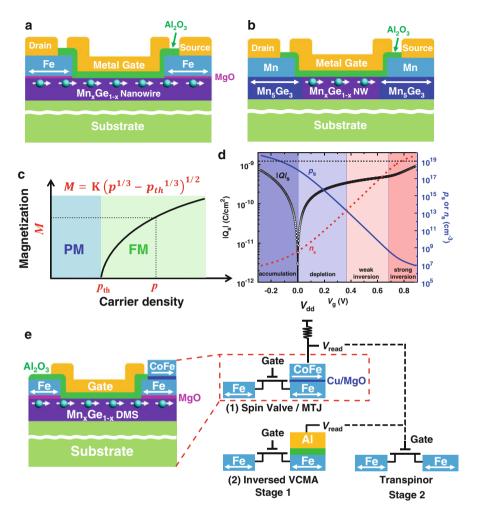

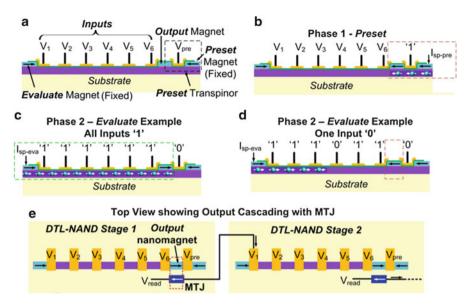

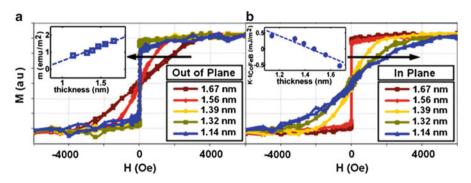

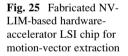

Fig. 36 Conventional CAM. (a) SRAM based CAM. (b) DW-CAM [21, 22]

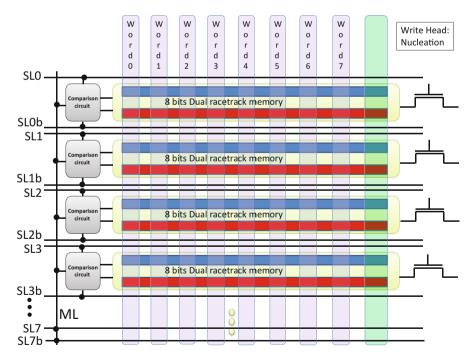

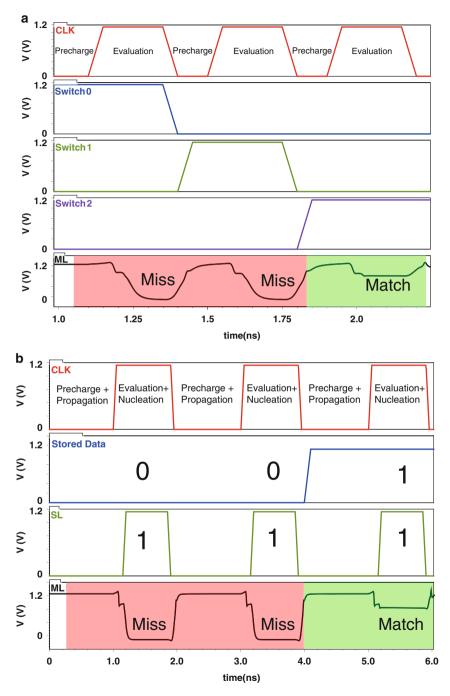

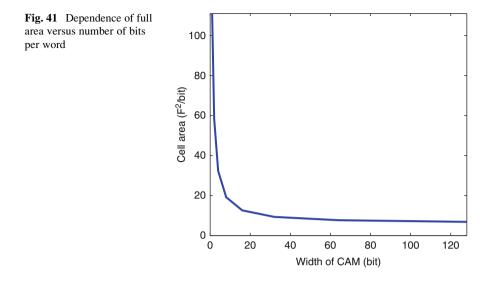

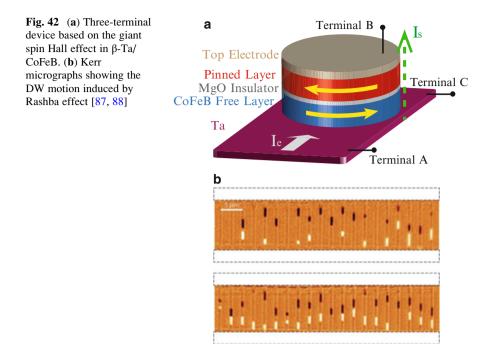

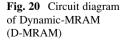

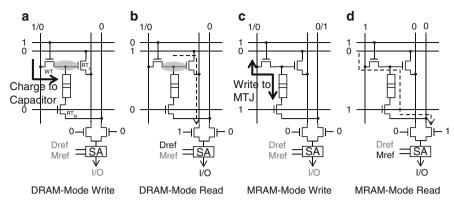

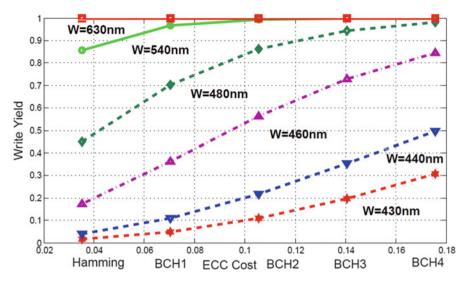

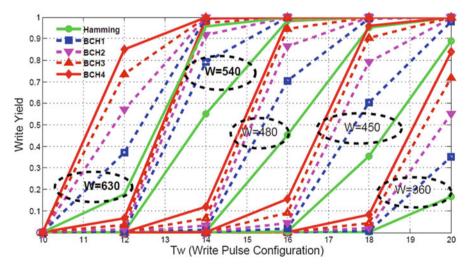

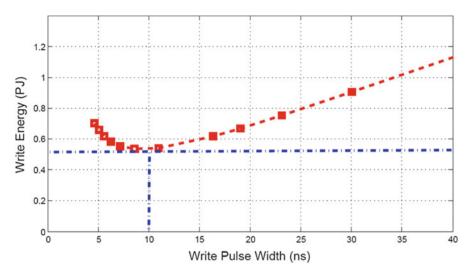

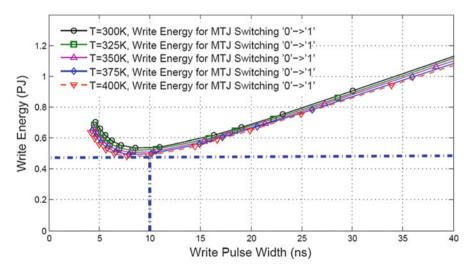

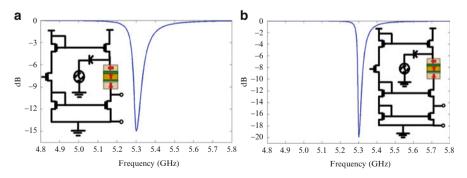

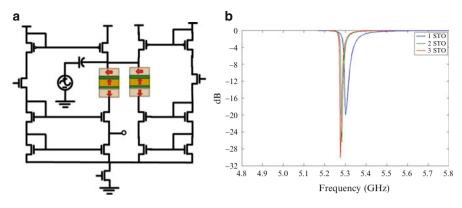

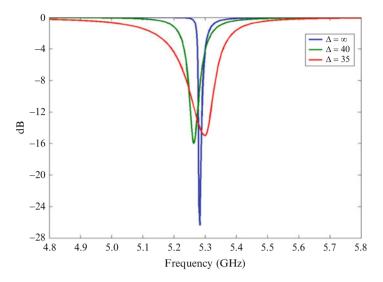

solution to build non-volatile CAM and overcome both these drawbacks. This topic is currently under intense investigation. For instance, a DW motion MRAM based CAM (DW-CAM) was prototyped recently (see Fig. 36b), which demonstrated important progress in terms of power and density [22]. However, this DW-CAM used a three-terminal MTJ as storage element and every memory cell had one comparison circuit and one selected transistor, which lead to a high bit-cell cost and cannot allow the expected ultra-high density.