**Engineering Materials**

Alexei Nazarov Francis Balestra Valeriya Kilchytska Denis Flandre *Editors*

Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting

**Engineering Materials**

More information about this series at http://www.springer.com/series/4288

Alexei Nazarov · Francis Balestra Valeriya Kilchytska · Denis Flandre Editors

# Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting

*Editors* Alexei Nazarov Lashkaryov Institute of Semiconductor Physics National Academy of Science of Ukraine Kyiv Ukraine

Francis Balestra Sinano Institute IMEP-LAHC, CNRS Grenoble IMEP-LAHC Grenoble France Valeriya Kilchytska Microelectronics Laboratory, ICTEAM Institute Université catholique de Louvain Louvain-la-Neuve Belgium

Denis Flandre Electrical Engineering (ELEN), ICTEAM Institute Université catholique de Louvain Louvain-la-Neuve Belgium

ISSN 1612-1317 ISSN 1868-1212 (electronic) ISBN 978-3-319-08803-7 ISBN 978-3-319-08804-4 (eBook) DOI 10.1007/978-3-319-08804-4

Library of Congress Control Number: 2014946761

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Preface

This book is devoted to fast the evolving field of modern material science and nanoelectronics, and more particularly to physics and technology of functional nanomaterials and devices. The book focuses on nanodevices for electronics, sensors, and energy harvesting, considering as main device structure—the semiconductor-on-insulator (SemOI) one. The book reports the recent achievements in this field from leading companies and universities in Europe, Russia, and Ukraine. It is articulated around four main topics: (1) Nanoscale CMOS materials and devices; (2) Beyond CMOS materials, devices and their diagnostics; (3) New functional nanomaterials and nanoscaled devices for energy harvesting, light emission, optoelectronics and THz range: (4) NanoSensors and MEMS/NEMS.

Part I is focused on new SemOI materials for More Moore and More-than-Moore applications. Ultrathin silicon SOI structures are necessary for production of fully depleted SOI devices of the 22 nm technology node and beyond. The materials innovation for RF electronics, Si-based photonics, and 3D integration are presented. Device solutions for very low-energy computing, high-performed tunnel FETs, 3D nanowire RAM cells, and mechanical flexible CMOS devices on plastics are described.

Part II of the Book deals with the physics of novel "beyond CMOS" devices such as IR memory cells on basis of Si/Ge nanoheterostructures, nonvolatile memory based on graphene on ferroelectric substrate, Si spintronic devices and the AFM diagnostics for different functional nanostructurated material and devices.

In Part III, we focus on functional nanomaterials and structures regarding selfpowered systems, solar energy harvesting structures, and THz electronics. Also nanocomposite dielectric materials for light-emitting materials and other optoelectronics applications are also discussed.

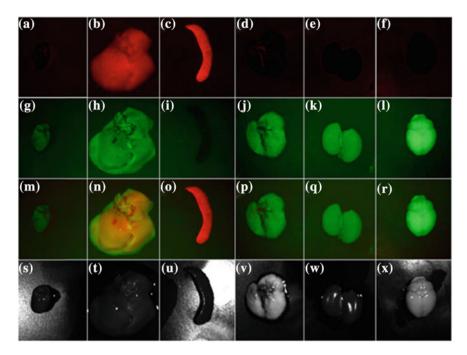

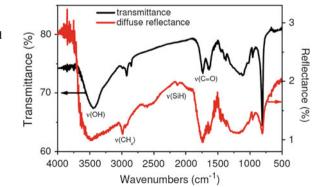

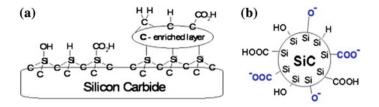

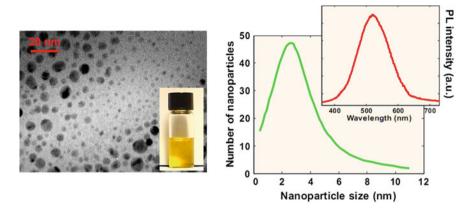

Part IV considers the application of SemOI nanowire structures for radiation sensors, biosensors, chemical sensors, and MEMS. The use of SemOI substrates allows a considerable increase of the sensitivity of the sensors, as well as the fabrication of MEMS compatible with CMOS technology. Additionally, Si and SiC nanodot materials are considered as fluorescent markers in different biomedical applications.

This book will be useful not only to specialists in nano, microelectronics, and functional nanomaterials but also to students and to the wider audience of readers who are interested by new directions in modern material science, electronics, and optoelectronics.

> Alexei Nazarov Francis Balestra Valeriya Kilchytska Denis Flandre

## Contents

| Engineered Substrates for Advanced CMOS Technology<br>Nodes and More-Than-Moore Applications                                                                                                                                                                                                                              | 3   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Perspectives of UTBB FD SOI MOSFETs for Analog<br>and RF Applications                                                                                                                                                                                                                                                     | 27  |

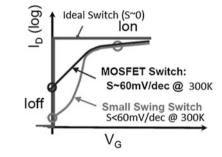

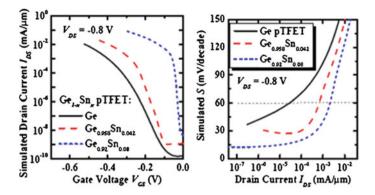

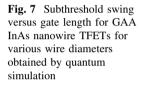

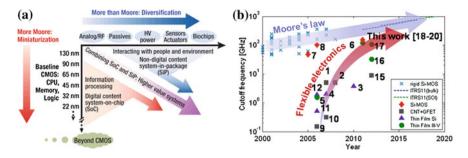

| <b>Challenges and Solutions for Very Low Energy Computation</b> Francis Balestra                                                                                                                                                                                                                                          | 47  |

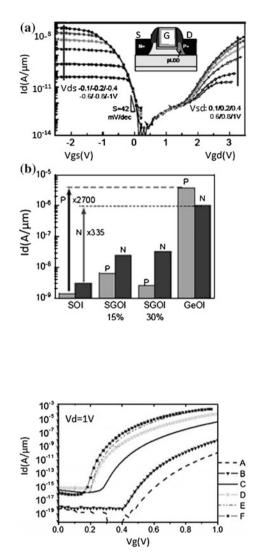

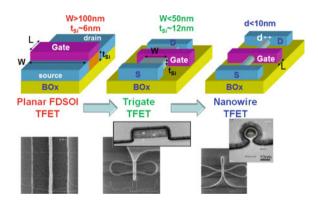

| <b>High-Performance Tunnel FETs on Advanced FDSOI Platform</b><br>Cyrille Le Royer, Anthony Villalon, Mikaël Cassé, David Cooper,<br>Jean-François Damlencourt, Jean-Michel Hartmann, Claude Tabone<br>and Sorin Cristoloveanu                                                                                            | 59  |

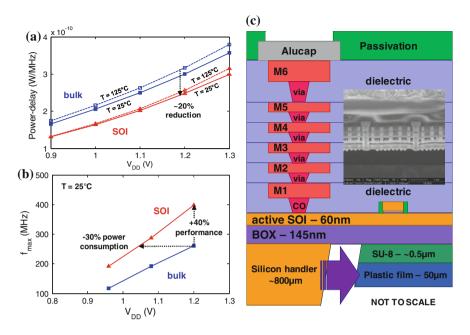

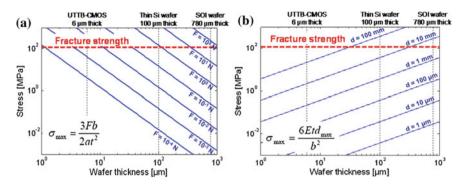

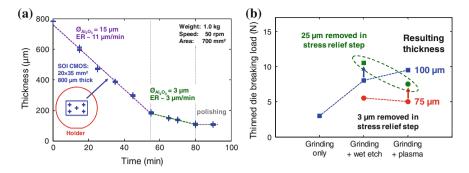

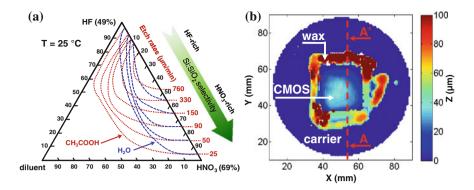

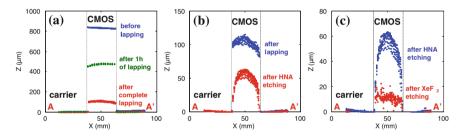

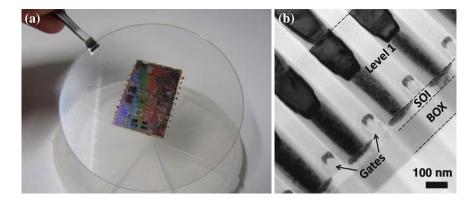

| Invariance of DC and RF Characteristics of Mechanically<br>Flexible CMOS Technology on Plastic<br>Aurelien Lecavelier des Etangs-Levallois, Justine Philippe,<br>Sylvie Lepilliet, Yoann Tagro, François Danneville,<br>Jean-François Robillard, Christine Raynaud, Daniel Gloria,<br>Jacek Ratajczak and Emmanuel Dubois | 81  |

| Tri-Dimensional A2-RAM Cell: Entering the Third Dimension<br>Francisco Gámiz, Noel Rodriguez, Carlos Navarro,<br>Carlos Marquez and Sorin Cristoloveanu                                                                                                                                                                   | 105 |

Part I Nanoscale CMOS Materials and Devices

#### Part II Beyond CMOS Materials, Devices and Their Diagnostic

| Uniaxial Shear Strain as a Mechanism to Increase Spin Lifetime<br>in Thin Film of a SOI-Based Silicon Spin FETs<br>Dmitri Osintsev, Viktor Sverdlov and Siegfried Selberherr                                                                                                                            | 127 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Quantum Noise in Nanotransistors                                                                                                                                                                                                                                                                        | 151 |

| Non-volatile Memory of New Generation and Ultrafast<br>IR Modulators Based on Graphene on Ferroelectric Substrate<br>Maksym V. Strikha                                                                                                                                                                  | 163 |

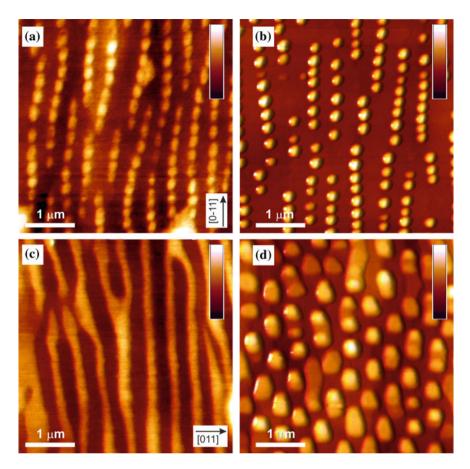

| Scanning Probe Microscopy in Practical Diagnostic:<br>3D Topography Imaging and Nanometrology                                                                                                                                                                                                           | 179 |

| Part III New Functional Nanomaterials and Nanoscaled<br>Devices for Energy Harvesting, Light Emission, Optoelectronics<br>and THz Range                                                                                                                                                                 |     |

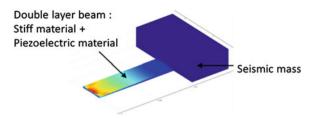

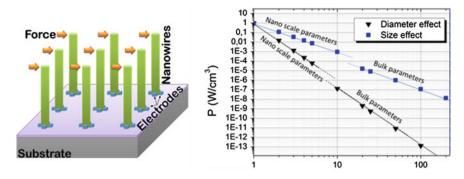

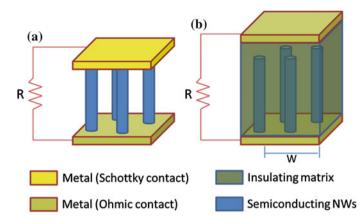

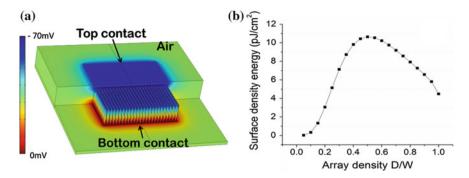

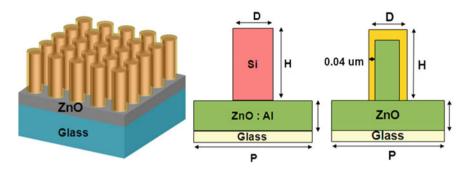

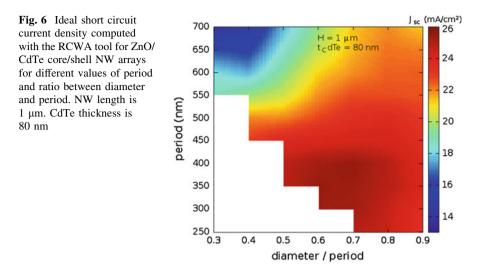

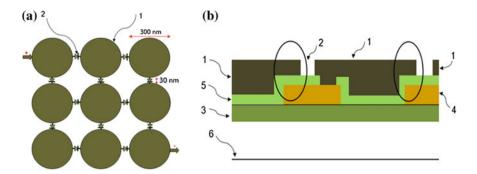

| Towards Self-Powered Systems: Using Nanostructures<br>to Harvest Ambient Energy<br>Gustavo Ardila, Anne Kaminski-Cachopo, Marco Pala,<br>Alessandro Cresti, Laurent Montès, Vincent Consonni,<br>Ronan Hinchet, Jérôme Michallon, Mehdi Daanoune,<br>Mauro Zanuccoli, Claudio Fiegna and Mireille Mouis | 223 |

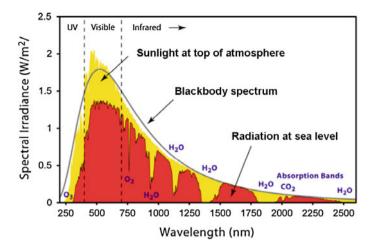

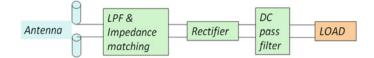

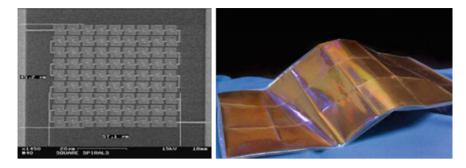

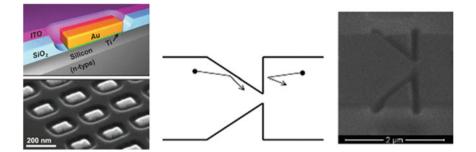

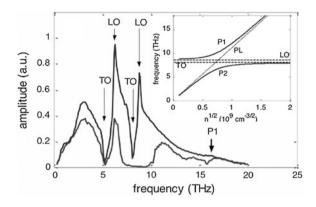

| <b>Energy Harvesting Using THz Electronics</b>                                                                                                                                                                                                                                                          | 241 |

| Uncooled Detector Challenges for mm/sub-mm Range<br>Fedor Sizov, Mykola Sakhno and Alexandr Golenkov                                                                                                                                                                                                    | 267 |

| Structural and Luminescent Properties of Carbonized Silicon<br>Oxide Thin Layers<br>Andrii V. Vasin                                                                                                                                                                                                     | 297 |

Contents

| <b>Preparation, Luminescent Properties and Bioimaging</b><br><b>Application of Quantum Dots Based on Si and SiC</b><br>Valeriy A. Skryshevsky, Tetiana Serdiuk, Yuriy E. Zakharko,<br>Sergei A. Alekseev, Alain Géloën and Vladimir Lysenko         | 323 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

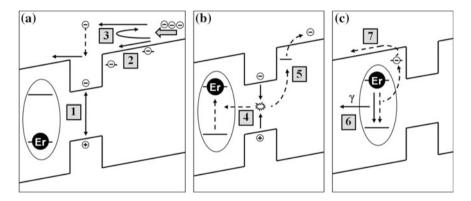

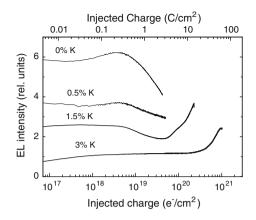

| Rare Earth Implanted MOS Structures: Advantagesand Drawbacks for Optoelectronic ApplicationsLars Rebohle                                                                                                                                            | 349 |

| Part IV NanoSensors and MEMS/NEMS                                                                                                                                                                                                                   |     |

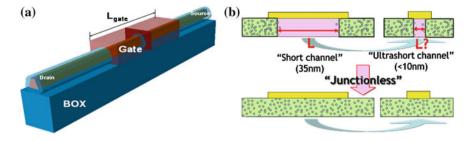

| Silicon and Germanium Junctionless Nanowire Transistors<br>for Sensing and Digital Electronics Applications                                                                                                                                         | 367 |

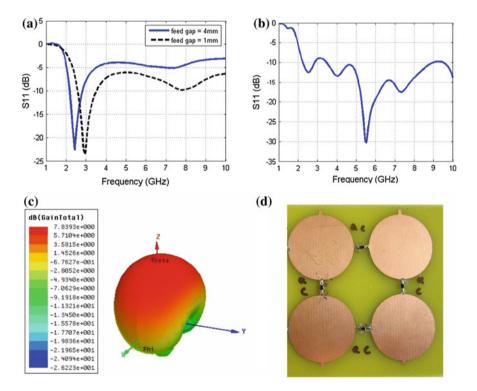

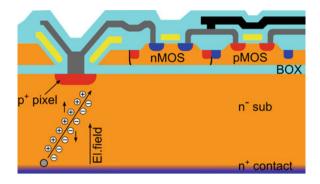

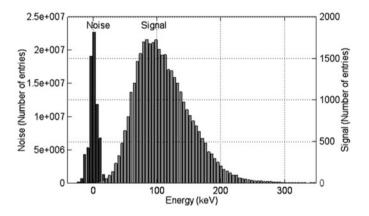

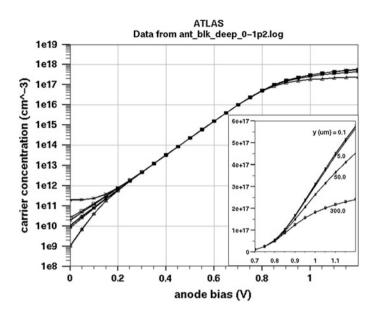

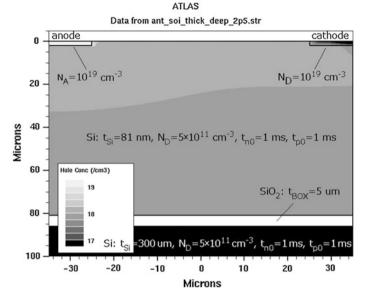

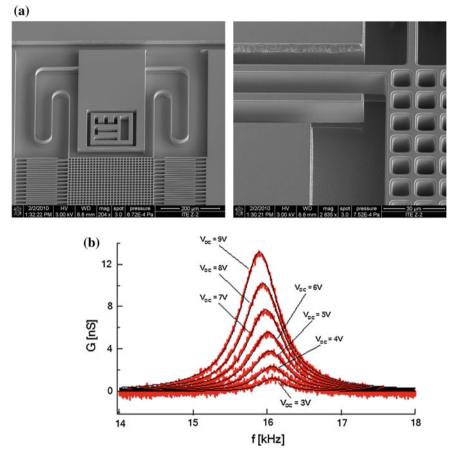

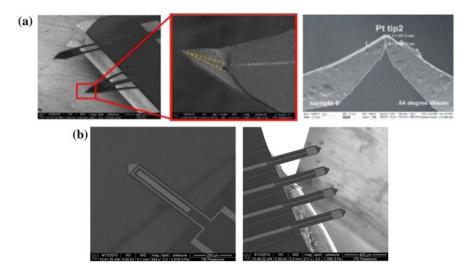

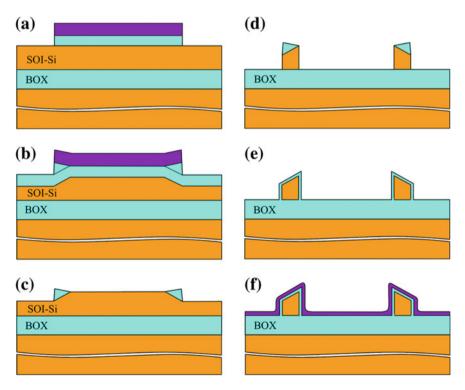

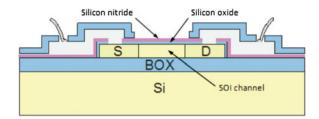

| <b>SOI-Based Microsensors</b><br>Daniel Tomaszewski, Michał Zaborowski, Krzysztof Kucharski,<br>Jacek Marczewski, Krzysztof Domański, Magdalena Ekwińska,<br>Paweł Janus, Tomasz Bieniek, Grzegorz Głuszko,<br>Bohdan Jaroszewicz and Piotr Grabiec | 389 |

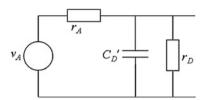

| Photoexcitation and Recombination of Charge Carriers<br>in Si/Ge Nanoheterostructures                                                                                                                                                               | 417 |

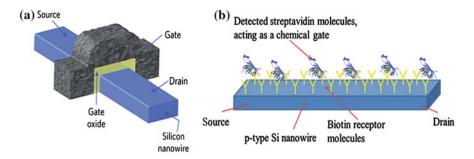

| SOI-Nanowire Biosensors for High-Sensitivity Protein<br>and Gene Detection                                                                                                                                                                          | 445 |

| <b>Erratum to: Energy Harvesting Using THz Electronics</b><br>Stephen Hall, Ivona Z. Mitrovic, Naser Sedghi, Yao-Chun Shen,<br>Yi Huang and Jason F. Ralph                                                                                          | E1  |

## Part I Nanoscale CMOS Materials and Devices

## **Engineered Substrates for Advanced CMOS Technology Nodes and More-Than-Moore Applications**

#### Konstantin K. Bourdelle

Abstract Traditional planar bulk or partially depleted SOI (PDSOI) CMOS transistor architectures at present leading edge of miniaturization are plagued by limitations due to unacceptably high current leakages and variability. To cope with these intrinsic limitations there is a need to introduce innovative technologies which take advantage of the benefits of Fully Depleted (FD) devices. There are two main architectures for the undoped channel FD device: 3D FinFETs (SOI or bulk-based) and 2D FDSOI-based transistors. Both of them are being introduced in high volume manufacturing (HVM). A pioneer of SOI concept, silicon on sapphire (SOS) substrates, have recently entered a mainstream radio frequency (RF) application market. Other flavors of engineered substrates, e.g. for photonics or 3D-based applications, have moved from research to industrial development phase. In this work an overview of the recent advances in the development of the engineered substrates for More Moore and More-than-Moore applications will be presented.

#### **1** Introduction

Over past decades, exponential gains in computational power have fuelled unprecedented progress in innovation and economical growth which has provided considerable benefits to society and has also enabled entirely new businesses such as e-commerce, social networking and mobile devices. This expected progress, however, now becomes threatened: an end to the gains in computing power and the raise of power consumption. The purely dimensional scaling era worked well down to 130 nm node. Since then such model of scaling has become less productive in improving CMOS performance due to increases short-channel effects (SCE). The local strain technologies were then introduced as mobility boosters.

K.K. Bourdelle (🖂)

Soitec, Parc Technologique Des Fontaines, 38190 Bernin, France e-mail: konstantin.bourdelle@soitec.com

<sup>©</sup> Springer International Publishing Switzerland 2014

A. Nazarov et al. (eds.), Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting, Engineering Materials, DOI 10.1007/978-3-319-08804-4\_1

These boosters, however, have started to run out of steam in the recent years mostly due to the bottleneck issues related to the leakage and device/circuit variability. That prompted the leading industry players to adopt FD device architectures: ultra-thin body and buried oxide (BOX) UTBB SOI (at 28 nm node) [1] and FinFET (at 22 nm node) [2]. Most important these two innovations feature new device geometry as compared to their planar bulk or PDSOI predecessors.

The limitations of Si-based CMOS, including FD devices in reaching high performance requirement are mostly due to reduction of the efficiency of uniaxial strain at 14 nm node and beyond. High mobility channel/substrate engineering is essential to boost performance especially for NMOSFETs. The corresponding innovative solutions must be: (i) Compatible with large diameter Si substrates to fully utilize existing platform therefore necessitating co-integration of Ge and III–V materials; (ii) Multigate devices will be needed to address the SCE issues; (iii) The solutions must meet defectivity as well as multi- $V_T$  requirements. They also must assure functional system on chip (SOC) circuits with high yield in HVM and be "economically affordable" based on the criteria of a broad consumer electronics market. Using Smart Cut<sup>TM</sup> technology SOI/UTBB-like devices with undoped and high mobility channels on thin insulator film can be fabricated in the heterogeneous integration concept. The technology is capable to address lattice mismatch challenges and transfer high quality ultra-thin (15–25 nm) Ge/III–V films on Si substrates.

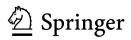

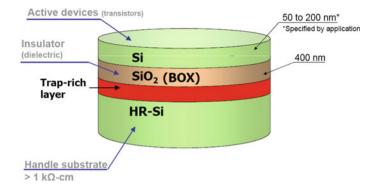

The definition of the substrates for More than Moore applications is rather broad and varies from source to source. Such applications would/might incorporate RF, power, photonics, imagers and micro electro mechanical systems (MEMS) devices. Soitec SOI product line to address some of these applications is depicted in Fig. 1. In addition, in the recent years 3D integration has appeared is a promising solution to overcome the limitations of size reduction and to increase circuit performances and functionality. By offering heterogeneous integration, shorter interconnection lengths and lower cost, this technology can address both More Moore and More than Moore applications.

#### 2 Engineered Substrates for More Moore Applications

In this section the emphasis will be made on FD device architectures (2D and 3D) with Si channels. In addition the new channel materials, strained Si (sSi), Ge and III–V alloys, and corresponding substrates requirements will be reviewed in the context of the potential introduction of the nanowire (NW) devices for sub-10 nm technology nodes.

Fig. 1 SOI product line. The *top* Si layers with *thickness* larger than 1 µm are obtained with the additional epitaxial step

#### 2.1 Planar FDSOI Technology

2D FDSOI-based devices have been extensively studied for more than 20 years. Their benefits are well documented: e.g. better immunity to SCEs and to random dopant fluctuations [1]. In addition, FDSOI substrates with thin, <25 nm, BOX (UTBOX) address a major challenge of undoped channel devices, i.e. fabrication of multiple threshold voltage,  $V_T$ , devices with dynamic  $V_T$  modulation. That is done by formation of different ground planes (GP) below the BOX and back biasing  $(V_B)$ . Such strategy is also attractive due to the possibility to reuse the bulk forward (FBB) and reverse (RBB) biasing techniques historically developed for planar bulk CMOS technologies. Top Si layer thickness (typical thickness <15 nm) non-uniformity was a formidable challenge to overcome before considering industrialization of 2D FDSOI technology for mainstream SOC applications. In FDSOI devices the Si thickness is strongly coupled to the MOSFET parameters, e.g. significant thickness non uniformity results in non acceptable  $V_T$ fluctuation. Typical uniformity requirements include within-the-wafer and waferto-wafer uniformity. Their combination is defined as layer total thickness variation (LTTV) and determines the overall manufacturing process window. LTTV of top Si has to be in the nanometer range for all wafers and all sites in order to meet the FD specifications.

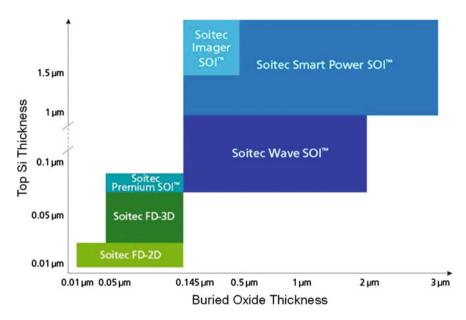

Fig. 2 Schematics of smart cut process flow used in the fabrication of UTBOX wafers [3]

Fabrication of UTBOX substrates is based on the conventional Smart Cut process depicted in Fig. 2. Uniformity of thin BOX thickness is defined by the donor wafer oxidation process step. Top Si thickness control is determined by ion implantation, splitting and finishing steps. Figure 3a shows that via thorough optimization of these steps within the wafer thickness uniformity  $\pm 4$  Å is achieved, as measured by optical ellipsometry with 41 points mapping [3]. To address wafer to wafer uniformity challenge the Advanced Process Control (APC) was implemented at post-split process module [4]. APC includes a specific tailored clean, which reduces a wafer to wafer SOI thickness variation from a standard  $\pm 10$  Å (as obtained through usual tool to tool matching) down to less than  $\pm 2$  Å. The LTTV performance for UTBOX (12 nm top Si and 25 nm BOX) substrates currently available for HVM is currently as follows: top Si thickness maximum variation of  $\pm 5$  Å (6 $\sigma$  value, all sites, all wafers), corresponding to an overall 1.6 % 1 $\sigma$  thickness control (Fig. 3b).

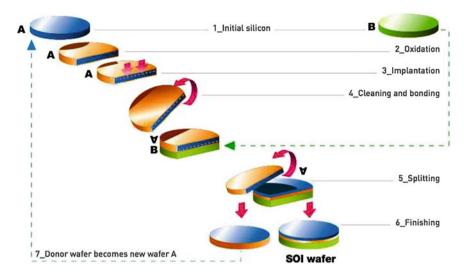

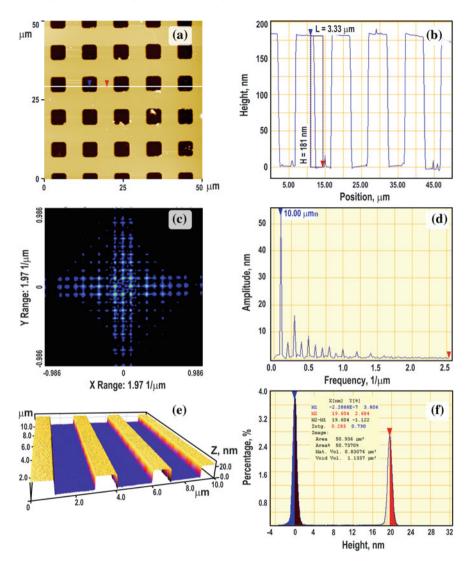

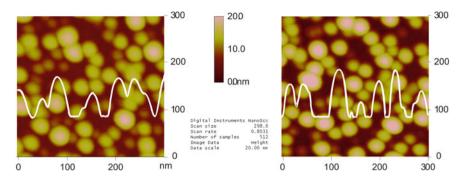

Device scale thickness variation is monitored by micro-roughness measurements using Atomic Force Microscopy (AFM) technique. Optimization of the thermal smoothing step in the finishing module (the step is driven by the surface diffusion of Si atoms) has lead to significant improvement in surface roughness of the fully processed UTBOX wafers. As a result the surface quality of the UTBOX family of substrates is currently very close to that of the polished bulk wafers. That is confirmed by the comparison of Power Spectral Density (PSD) curves obtained from  $30 \times 30 \ \mu\text{m}^2$  AFM scans (see Fig. 4). The corresponding root mean square (RMS) values have been reduced from the previously reported 2.0 Å [4] down to current 0.8 Å. Peak to valley (PV) local thickness variation has improved from 20 to 8 Å. The reported 8 Å PV measured performance is close to the theoretical minimum of 7 Å [3].

Fig. 3 a Ellipsometry map of within the wafer thickness uniformity; b UTBOX 12/25 nm all wafers all points top Si thickness distribution [3]

Fig. 4 Power spectral distribution from AFM  $30 \times 30 \ \mu\text{m}^2$  scans for polished bulk, PDSOI and current generation of FDSOI/UTBOX25 substrates [3]

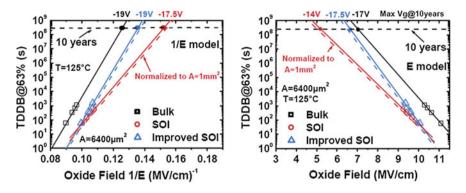

As mentioned above ultrathin Si films are today combined with ultrathin BOX layers to fabricate multi-*Vt* devices for low power (LP) and SOC applications [1]. Thinning of the BOX leads to increase of the electrostatic coupling with the substrate via GP contact. This results in effective dynamic *Vt* modulation of more than 100 mV for a back gate (BG) biasing in the range of  $\pm 1$  V (with BOX thickness of 25 nm). However, to replace 145 nm thick BOX, industry standard PDSOI technologies, these ultrathin BOX layers must exhibit the same high quality and reliability. It is of importance therefore to verify that the presence of many critical steps within Smart Cut flow does not degrade the intrinsic reliability of ultrathin BOX. In [5] the BOX breakdown reliability of UTBOX25 substrates was investigated using simple MOS capacitors. Figure 5 shows time dependent dielectric breakdown (TDDB) distributions obtained for UTBOX25 wafers

Fig. 5 (*left*) 10-years extrapolation results reported through 1/E model. (*right*) 10-years extrapolation results reported through E model [5]

fabricated with two different process flows (denoted as "SOI" and "improved SOI") compared with that for the oxide grown on bulk Si wafers. For this range of oxide thicknesses (>10 nm), TDDB is driven by the oxide electric field,  $E_{OX}$ , rather than by the maximum gate voltage  $V_G$ . Therefore authors [5] used the "E" and "1/E" models to extrapolate the TDDB lifetime at 10 years. It is seen in Fig. 5 that "improved SOI" and bulk oxide exhibit similar 10 years breakdown lifetimes. By using the "1/E" model, the maximum gate voltage is estimated to 19 V. The "E" model itself is more pessimistic than the "1/E" model consistently with literature data that lead to lower values. For the standard "SOI" oxide, the lifetime margin is reduced. Nevertheless, the extracted maximum voltages are 3–6 times larger than typical back-biases used for the 28 nm node [5].

#### 2.2 3D Multiple Gate Devices

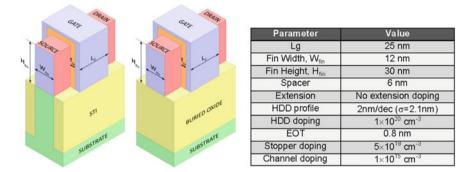

Device and circuit variability has become a major concern, forcing the industry to consider new transistor architectures for the 28 nm technology generation and below [1, 2]. Multiple gate devices like FinFETs or Tri-Gate can be fabricated using either bulk [2] or SOI substrates (see [6] for the recent reference). In FD architectures the electrostatic integrity and electrical characteristics are controlled by the thickness of the channel and, in the 3D case, its height and shape. The process control of these dimensions will play a critical role in the variability of the new technologies. In [7] the process-induced variability in a FinFET suitable for the 16 nm technology generation and built on SOI or bulk substrates was studied. Authors [7], using extensive numerical simulations, have compared the process sensitivity of key figures of merit including  $V_T$ , subthreshold slope (*SS*), drain induced barrier lowering (*DIBL*) and fixed overdrive drive current ( $I_{ODSAT}$ ). The structures of the simulated n-channel FinFETs (FF) are schematically illustrated in Fig. 6 (left) and main device design parameters are listed in Fig. 6 (right).

Fig. 6 Schematics of the bulk (*left*) and SOI (*center*) FinFETs. Device design used in the simulations (*right*) (from [7])

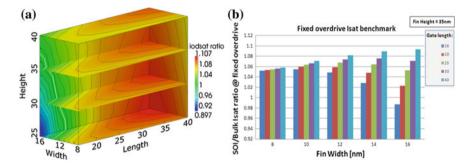

Fig. 7 a Colour and contour map of  $I_{ODSAT}(SOI)/I_{ODSAT}(bulk)$  in the experiment space. The *white* contour marks the unity ratio where bulk performance is equal to that of SOI. **b** Detailed comparison for  $H_{fin} = 35$  nm of this  $I_{ODSAT}$  boost for SOI [7]

The map of the  $I_{ODSAT}(\text{SOI})/I_{ODSAT}(\text{bulk})$  ratio in the  $H/W/L_G$  space is shown in Fig. 7a. It indicates a performance advantage for the SOI-FF which is typically 5 % over the parameter space. Figure 7b provides a more detailed comparison for  $H_{Fin} = 35$  nm of this  $I_{ODSAT}$  boost for SOI, showing improved current for narrower Fins, especially when the gate length is short. These data are of interest when used to assess the performance corners resulting from process variability. SOI-FF will benefit from a better Fin definition which is defined by the top Si thickness uniformity of the starting wafers [8]. The process-induced variations scenarios for bulk-FF and SOI-FF are summarized in Table 1. SOI-FF does have  $V_T$  corner range improved by factor two. In addition the range of  $I_{SAT}$  variation is reduced from 28.7 % in the bulk case down to 7.3 % for the SOI. That proves that better Fin height control directly translates into reduced  $I_{SAT}$  variability [7].

| Table 1 P | Table 1         Process-induced va | variation assumptions and process corners for device electrostatics [7] | ns and process         | corners for dev        | rice electrostatics | [ <b>7</b> ] s                                                                                                                                                                                                                                                                                                                                                                             |      |                      |              |

|-----------|------------------------------------|-------------------------------------------------------------------------|------------------------|------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|--------------|

|           | H control (Å)                      | W control (Å)                                                           | $V_T \min(\mathbf{V})$ | $V_T \max(\mathbf{V})$ | $V_T$ range (V)     | $W \text{ control } (\text{\AA})  \left  \begin{array}{c c} V_T \min \left( V \right) & \left  \begin{array}{c c} V_T \max \left( V \right) & \left  \begin{array}{c c} V_T \operatorname{range} \left( V \right) & SS \min \left( \operatorname{mV/dec} \right) & SS \max \left( \operatorname{mV/dec} \right) \\ \end{array} \right  \\ (\operatorname{mV/dec} ) \\ \end{array} \right $ |      | SS range<br>(mV/dec) | SS range (%) |

| Bulk fin  | 土5                                 | <b>±</b> 2                                                              | 0.147                  | 0.212                  | 0.065               | 69.5                                                                                                                                                                                                                                                                                                                                                                                       | 77.6 | 8.1                  | 11.05        |

| SOI fin   | <b>±</b> 2                         | ±2                                                                      | 0.167                  | 0.229                  | 0.062               | 71.9                                                                                                                                                                                                                                                                                                                                                                                       | 80.3 | 8.5                  | 11.2         |

| SOI fin   | 土1                                 | ±1.5                                                                    | 0.175                  | 0.221                  | 0.046               | 72.8                                                                                                                                                                                                                                                                                                                                                                                       | 79.2 | 6.33                 | 8.37         |

|           |                                    |                                                                         |                        |                        |                     |                                                                                                                                                                                                                                                                                                                                                                                            |      |                      |              |

| F                                         |

|-------------------------------------------|

| ن                                         |

| device electrostatics                     |

| or d                                      |

| corners for                               |

| process                                   |

| and                                       |

| ttion assumptions and process corners for |

| iation                                    |

| variat                                    |

| uced                                      |

| indu                                      |

|                                           |

| <b>Process</b> .                          |

| -                                         |

| e                                         |

| able                                      |

| Table                                     |

#### 2.3 New Channel Materials and New Device Architectures

Carrier mobility improvement becomes necessary to enhance device performance for the advanced nodes. The combination of high mobility channel and FD devices architectures is most appealing for high density, high performance, and low leakage applications. The challenges of scaling of Si-based devices below 11 nm node (using local strain options) have prompted researchers in recent years to consider fundamental paradigm change, i.e. replacement of the conventional Si channel by materials with much higher carrier mobilities: wafer scale strain Si (sSi), Ge and III–V (see Table 2 below). That would advance CMOS beyond traditional Si (SOI or bulk), and as a consequence open a new path to performance increase while still leveraging mature CMOS technology for large diameter Si wafers.

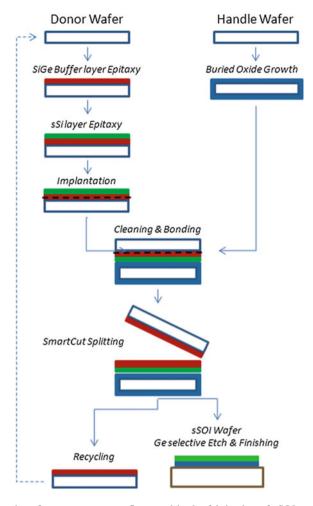

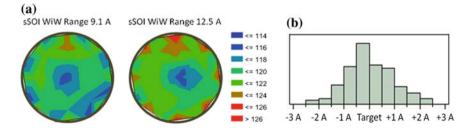

(a) Tensile strained silicon on insulator (sSOI) substrates represent a promising option to improve the carrier mobility of NMOS devices, without significant degradation of PMOS performance (with proper process integration knowhow). Technical details of fabrication of 300 mm sSOI substrates with top Si thickness of 12 nm, BOX thickness of 25 nm, and stress level of 1.3 GPa are described in [9]. Schematics of corresponding Smart Cut process flow is shown in Fig. 8. Within the wafer sSi thickness uniformity is determined by donor wafer epitaxy and finishing process steps. Figure 9a shows typical sSi thickness uniformity maps (at the thickness range levels at 12 Å and down to 9 Å, measured by optical ellipsometry technique with 41 points). Note: to get the industrial acceptance within the wafer sSi layer uniformity is required to be at the level of more mature UTBOX family of substrates (described in previous section). Wafer to wafer sSi thickness control is largely determined by the epitaxy step and is currently at par with that of UTBOX substrates due to implementation of the APC module (see Fig. 9b) [9]. Stress uniformity measurements are usually performed using well established Raman spectroscopy technique [10]. Figure 10a shows typical stress maps (with 41 measurement points) for an sSOI wafer (sSi thickness of 12 nm and BOX thickness of 25 nm). Device scale stress variation results obtained with the same technique (scan size of  $80 \times 80 \ \mu\text{m}^2$ ) are shown in Fig. 10b. The stress variation of typically 0.02 GPa RMS is observed (related to the SiGe buffer layer local relaxation conditions) [9].

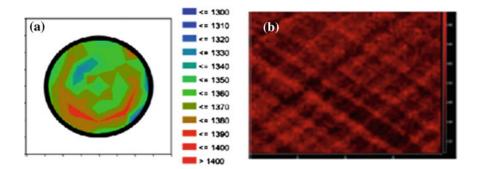

The devices fabricated on such substrates showed the gain in performance of at least 20 % for NMOS as compared to the standard SOI substrate [11, 12]. The efficiency of back gate bias for  $V_T$  modulation has been confirmed as well as an additional performance booster [11]. Figure 11 illustrates main results published recently for the devices fabricated on the sSOI substrates (stress level of 1.3 GPa and BOX thickness of 25 nm).

The sSOI substrates are also considered as potential candidates for sub-10 nm nodes with NW-based devices architectures. The reader is referred, e.g., to [13, 14] for recent advances. In [13] top-down Si NWs under tensile elastic uniaxial strain up to 4.5 % were demonstrated. Authors of [14] fabricated inverters based on

| Parameter                                                                                         | Si                    | Ge                    | GaAs                 | InP                  | $In_{0.53}Ga_{0.47}As$ | In <sub>0.7</sub> Ga <sub>0.3</sub> As | InAs                 | GaSb                 | InSb                 |

|---------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|------------------------|----------------------------------------|----------------------|----------------------|----------------------|

| Lattice<br>constant<br>(Å)                                                                        | 5.431                 | 5.658                 | 5.653                | 5.869                | 5.8687                 | 5.937                                  | 6.058                | 6.09593              | 6.4793               |

| Band gap<br>(eV)                                                                                  | 1.12                  | 0.66                  | 1.42                 | 1.34–1.35            | 0.74                   | 0.58                                   | 0.35-0.36            | 0.726                | 0.17                 |

| Electron<br>mobility<br>(cm <sup>2</sup> /Vs)                                                     | 1500–1600             | 3900                  | 8500–9200            | 4600–5400            | 12000                  | 20000                                  | 33000-40000          | ≤3000                | 77000-80000          |

| Hole<br>mobility<br>(cm <sup>2</sup> /Vs)                                                         | 430-450               | 1900                  | 400                  | 150-200              | 300                    | 400                                    | 460–500              | ≤1000                | 850-1250             |

| Effective<br>density of<br>states in<br>conduction<br>band, N <sub>c</sub><br>(cm <sup>-3</sup> ) | $2.8 \times 10^{19}$  | $1.04 \times 10^{19}$ | $4.7 \times 10^{17}$ | $5.7 \times 10^{17}$ | $2.1 \times 10^{17}$   | $1.6 \times 10^{17}$                   | $8.7 \times 10^{16}$ | $2.1 \times 10^{17}$ | $4.2 \times 10^{16}$ |

| Effective density of states in valence band, $N_v$ (cm <sup>-3</sup> )                            | $1.04 \times 10^{19}$ | $6.0 \times 10^{18}$  | $7.0 \times 10^{18}$ | $1.1 \times 10^{19}$ | $5.5 \times 10^{18}$   | $5.9 \times 10^{18}$                   | $6.6 \times 10^{18}$ | $1.8 \times 10^{19}$ | $7.3 \times 10^{18}$ |

| Dielectric<br>constant, k                                                                         | 11.9                  | 16                    | 13.1                 | 12.4                 | 13.9                   | NA                                     | 15.5                 | 15.7                 | 17.7                 |

| Melting<br>point, T <sub>m</sub><br>(°C)                                                          | 1412                  | 937                   | 1240                 | 1060                 | NA                     | NA                                     | 942                  | 712                  | 527                  |

12

Fig. 8 Schematics of smart cut process flow used in the fabrication of sSOI wafers [9]

Fig. 9 a Typical sSOI within the wafer thickness uniformity mapping. b sSOI wafer to wafer mean thickness distribution [9]

Fig. 10 a Within the wafer stress variation for a sSOI wafer. b  $80 \times 80 \ \mu\text{m}^2$  local strain mapping [9]

Fig. 11 XTEM micrograph of sSOI NMOS device with  $L_G = 30 \text{ nm}$  (*left*). NMOS  $I_{ON}/I_{OFF}$  ratio for sSOI and SOI wafers (*center*). NMOS and PMOS linear  $V_T$  evolution on back bias voltage in RBB and FBB modes (*right*) (from [11])

uniaxially tensile sSi NW tunnelling field-effect transistors (TFETs). These first sSi NW complementary TFET inverters show sharp transitions and fairly high static gain even at very low  $V_{DD} = 0.2$  V [14].

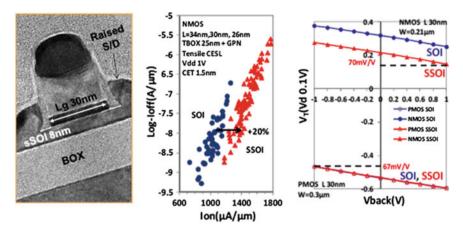

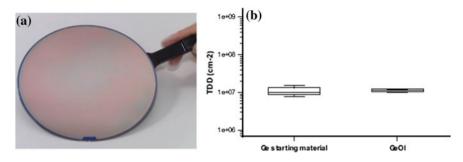

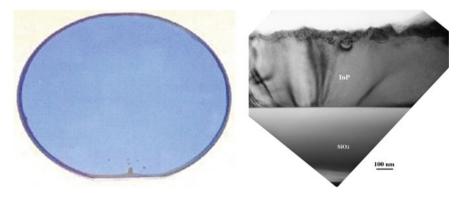

(b) In the last years, the semiconductor industry was re-introducing Ge to the front end process flows with a steady increase of Ge content in critical device areas. Pure Ge nowadays (despite limitations related to band-to-band tunnelling) is considered one of the promising channel materials to replace Si in future PMOS devices due to its high hole mobility. Technical details of fabrication of 200 mm GeOI substrates using Smart Cut technology are described in [15]. Figure 12a shows the picture of fully processed 200 mm GeOI wafer. Since GeOI-based devices are considered for sub-10 nm nodes such solution must be compatible with 300 mm and potentially 450 mm production environment. That defines the structure of the donor wafer, i.e. Ge layer epitaxially grown on the bulk Si

Fig. 12 a Picture of fully processed 200 mm GeOI wafer. b TDD in Ge epitaxial film before and after smart cut layer transfer [15]

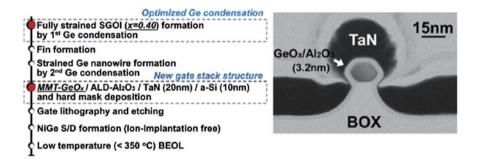

Fig. 13 (*left*) Fabrication process of strained-Ge nanowire MOSFETs with GeOx /ALD-Al<sub>2</sub>O<sub>3</sub> gate stack. (*right*) Cross-sectional TEM image of the fabricated device [16]

substrate. The crystal quality of the transferred Ge layer is of importance for the device fabrication. The main figure of merit is threading dislocation density, TDD. Figure 12b shows the current level of TDD in starting material and illustrates the fact that Smart Cut technology does not degrade the crystal quality obtained in the donor substrate.

Another way to fabricate the GeOI substrates is condensation technique which uses SOI wafers as starting material (see [16] for details). Authors of [16] reported uniaxially strained-Ge nanowire channel formed by improved two-step Ge condensation technique, which induced uniaxial stress along the channel direction. To improve the gate interface characteristics, a GeOx layer was formed by using the modified magnetron typed plasma at 300 °C on the strained-Ge nanowire surface. A 3.2 nm Al<sub>2</sub>O<sub>3</sub> layer was then grown by using an atomic layer deposition (ALD) system. NiGe-metal source-drain, S/D, structures were formed by salicide-like process on the unintentionally doped Ge wire. The fabrication process flow and cross-section of PMOS device are shown in Fig. 13. Authors of [16] demonstrated a record-high hole mobility ( $\mu_{eff} = 1922 \text{ cm}^2/\text{Vs}$ ) of a Ge nanowire MOSFET. High intrinsic transconductance  $G_{msat}$  of 1.21 mS/µm and low off-current of

<sup>(b)</sup> 1x10<sup>-3</sup> (a) 10<sup>-3</sup> -50mV, -0.5V = 40nm 10 15nm Drain current, I<sub>d</sub> (A/µm) 8x10 Drain current |/<sub>d</sub>| (A/µm) 10.3 = 0 to -2 V -0.5V step 10. 6x10<sup>-4</sup> 10.7 4x10 10-8 10. 2x10 10<sup>-10</sup> 10-11 0 0 -1 -0.6 .1.2 -2 Gate voltage,  $V_{g}$  (V) Drain voltage, V (V)

Fig. 14 a  $I_D$ - $V_G$  and b  $I_D$ - $V_D$  characteristics of fabricated strained Ge nanowire MOSFET with  $W_{wire} = 15 \text{ nm}, L_G = 40 \text{ nm} [16]$

Fig. 15 (*left*) Picture of 3" GaAs thin film transferred onto Si [18]. (*right*) XTEM cross section of InP film transferred on Si wafer covered with oxide [19]

$2.7 \times 10^{-9}$  A/µm at  $V_D = -0.5$  V were achieved for the device with the  $L_G$  of 45 nm due to the reduced interface state density.  $I_D - V_G$  and  $I_D - V_D$  characteristics of fabricated strained Ge nanowire MOSFETs with  $L_G = 40$  nm and  $W_{wire} = 15$  nm are shown in Fig. 14.

(c) III–V channel materials, particularly InGaAs alloys, are considered to address the challenges of NMOS performance boost. That would necessitate cointegration of III–V and Ge materials: proof of concept was recently reported in [17]. The transfer of GaAs and InP layer onto Si substrates using Smart Cut technology has been described in [18–20]. The pictures of GaAsOI and InPOI

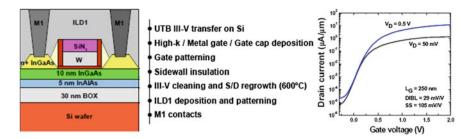

**Fig. 16** (*left*) Process flow and schematic for gate-first implant-free UTB InGaAs/InAlAs MOSFETs on silicon. (*right*)  $I_D$ - $V_G$  characteristic of a short-channel MOSFET as described in Fig. 16a with an EOT of 17.5 Å, 10 nm InGaAs channel and 5 nm InAlAs back barrier. Good electrostatic integrity and  $I_{ON}/I_{OFF}$  ratio are obtained due to the thin-body structure. The on-current is limited by the high access resistance *below* the sidewalls [21]

Fig. 17 a Picture of 6" fully processed SOS wafer. b Comparison of effective electron mobility for BSOS and SOS [24]

substrates are shown in Fig. 15. Recently, IBM-Zurich team has reported high quality InGaAs/InAlAs heterostructure devices (channel thickness <10 nm) fabricated on Si substrates using Smart Cut approach [21]. The thermal stability of the bonded layer enabled to integrate III–V MOSFETs at 500 nm pitch using a gate-first flow featuring raised S/D grown at 600 °C [21]. The process flow and  $I_D$ – $V_G$  curves are show in Fig. 16. The authors of [21] have stated that the donor wafer can be recycled for a cost-effective process. This publication proves the fact that Smart Cut implants do not degrade the electrical quality of InGaAs/InAlAs layers. The fabrication of strained [22] and high performance (with  $L_G = 20$  nm) [23] InGaAs-OI devices on Si substrates using bonding and etchback (BESOI) technique has been reported recently by the University of Tokyo team.

Fig. 18 Wafers commercially available from Soitec for RF and mixed-mode integration [27]

#### **3** Engineered Substrates for More-Than-Moore Applications

As mentioned above the definition of the engineered Substrates for More-than-Moore applications is rather broad. In this section the author will focus in on the RF, photonics and 3D applications.

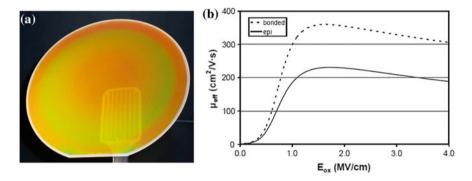

#### 3.1 RF Applications: SOS and HR-SOI Substrates

Modern engineered substrates technologies are currently successfully used to fabricate silicon on sapphire (SOS) and Si layers on the high resistivity (HR) substrate (HR-SOI) to reduce parasitic capacitance and improve RF performance. SOS substrates feature base wafer resistivity above 10 k $\Omega$ -cm, when for HR-SOI this value is typically around 1–2 k $\Omega$ -cm. SOS, historically developed via heteroepitaxial Si growth on a crystalline Al<sub>2</sub>O<sub>3</sub>, has become a first commercial SOI-based technology. The high crystal defectivity levels inherent to the heteroepitaxial technique did limit, however, industrial adaptation of SOS substrates. An alternative, SOS wafers fabricated with BESOI technique (BSOS), has emerged recently as a substrate solution to address the growing market needs. The photograph of 6" fully processed BSOS substrate is shown in Fig. 17a. The data, published by Peregrine and Soitec team, confirm that BSOS shows >50 % higher electron mobility as compared to conventional SOS fabricated by direct epitaxy (see Fig. 17b). These technical results have helped to open new market opportunities for "first-of-a-kind" SOI-based technology.

The availability of CMOS foundry technologies on 200 mm HR-SOI wafers has made possible high volume fabrication of RF systems, including high quality passive devices and RF switches [25–27]. The achieved performance was sufficient to integrate wireless and RF multi-standard multi-band functionalities in Si-based

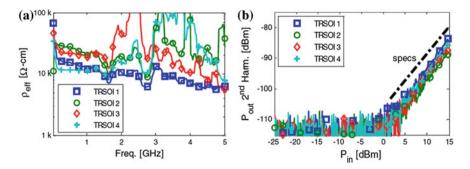

**Fig. 19 a** Effective resistivity versus frequency of CPWs on different TR HR-SOI wafers. **b** Harmonic distortion of CPWs on different trap-rich HR-SOI wafers. The specification (specs *straight line*) for the harmonic distortion corresponds to that of RF switches for GSM/EDGE transmitter modules (from [27])

SOCs. The inherent transmission line losses, due to the presence of parasitic surface conduction (PSC), however, limit RF performance of standard HR-SOI substrates [27]. The non-linear behavior of HR-SOI substrates is also increased due to PSC, and the generated harmonics at the passive components can have higher power levels than those from RF switches or other active devices fabricated on HR-SOI. The increase of BOX thickness provides better isolation, but does not reduce the parasitic effects. These effects are characterized by a threshold limit in the substrate losses reduction when increasing Si HR and high harmonic distortion levels introduced by the substrate itself [26]. Several methods were developed in the last years to reduce these parasitic effects and to enhance the HR properties of the base substrate [27]. The introduction of a trap-rich (TR) layer has proved to be an effective technique to reach the industry standards for transmission line performance. The Smart Cut technology used in the fabrication TR HR-SOI substrates has a moderate cost impact and is compatible with the thermal budgets of typical CMOS process flows [27]. Figure 18 shows schematics of TR HR-SOI wafer commercially available from Soitec. TR HR-SOI wafers manufactured with different process flavours were RF-characterized after fabrication of coplanar waveguides (CPW): for the details the reader is referred to Ref. [27]. Figure 19a depicts the effective resistivity versus frequency of CPWs. It confirms the effective resistivity higher than 4 k $\Omega$ -cm for all wafers being tested. Regarding the linear behaviour parameter, CPW harmonic distortion was always found to be lower than -81 dBm (for an input power of +15 dBm (Fig. 19b), i.e. more than 95 dBc).

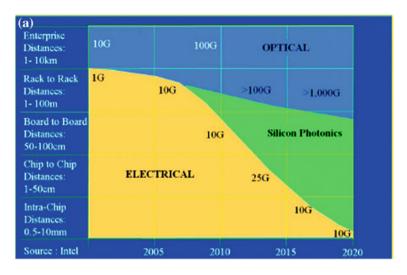

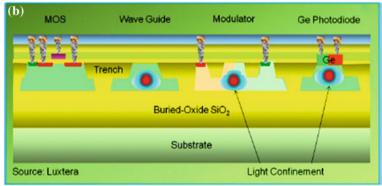

#### 3.2 Substrates for Photonics Applications

The push towards ever increasing data rates coupled with requirement for LP consumption suggests integration of optical components together with Si-electronics, i.e. development and industrialization of silicon photonics technology. Figure 20a

Fig. 20 a Electrical data rate limits for different data communication distances. b CMOS silicon photonics device cross-section [28]

depicts the foreseen electrical limits versus data communication distances [28]. A typical silicon photonics CMOS process flow starts from an SOI wafer (see Fig. 20b). SOI is required for the confinement of the light in the optical waveguides. The light is confined and guided into the silicon strip layer due to the difference of the two refractive indexes, *n*: top Si (n = 3.48) and BOX (n = 1.45 for SiO<sub>2</sub>). The thicknesses of top Si and BOX layers are chosen accordingly to the selected range of the operating wavelengths. The top Si thickness is typically in the range of about 0.2–0.5 µm, whereas for the BOX it is >1 µm. To support today's R&D efforts top Si thickness uniformity is currently about ±10 nm. In order to gain wide-range industrial adoption the ultimate uniformity is targeted at the level of ±1 nm.

Fig. 21 Process schematics of the smart stacking technology [30]

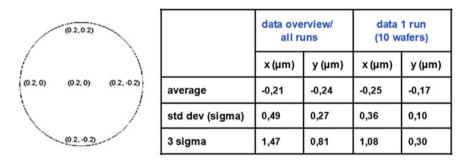

Fig. 22 W2W alignment accuracy across 300 mm wafer [31, 32]

Another potential application of Smart Cut technology in photonics is related to the fabrication of Bragg reflectors with top crystalline Si layer. Such reflectors provide high coupling efficiency, represent a fundamental building block for a number of devices (such as optical microcavities), and increase the quantum efficiency in resonant cavity enhanced photodetectors (while preserving highspeed operation) [29]. The proof of concept was demonstrated in [29] where conventional BOX was replaced with alternating multi-layer Si/SiO<sub>2</sub> stack.

#### 3.3 Substrates for 3D Integration

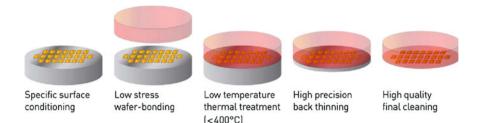

The emerging field of 3D integration aims at providing highly integrated systems by vertical stacking, connecting various materials and functional components together. Due to stringent reliability standards, a fundamental challenge of direct bonding technology is to achieve a mechanical bond between the face-to-face bonded wafers without intermediate materials. To address these challenges, Soitec and CEA-LETI have developed two wafer-to-wafer (W2W) stacking technologies: Smart Stacking<sup>TM</sup> and low-temperature Smart Cut<sup>TM</sup>. These technologies provide reduction of process cost and sub-micron alignment capability. Smart Stacking is a W2W stacking platform for partially or fully processed wafers (see Fig. 21).

Fig. 23 Process schematics of the smart cut technology for 3D stacking [33]

Fig. 24 Uniform thin Si film with low roughness transferred at low temperatures [33]

The technology incorporates surface conditioning, room temperature (RT) low stress bonding with precision alignment, low-temperature post-bond anneal, grinding and thinning. RT bonding ensures low thermal expansion mismatch, less stress and mechanical deformation, which are critical to achieve required level of alignment accuracy. W2W alignment accuracy of ~0.2  $\mu$ m across 300 mm wafers was demonstrated (see Fig. 22). To address the thermal budget constraint imposed by stacking of the backend of the line (BEOL) processed wafers (i.e. <400 °C), specific pre-bonding surface conditioning and a post-bonding thermal treatment were developed with the aim to increase the bonding strength. High bonding energies were achieved, providing compatibility with following wafer grinding and thinning processes [31, 32].

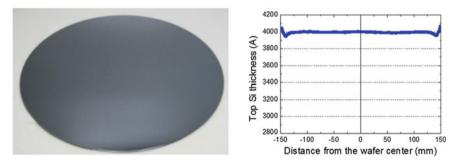

Fig. 25 Uniform thin Si film with low roughness transferred at low temperatures. The shown results are obtained with  $5 \times 5 \ \mu m^2$  AFM scan [30, 33]

(a) Well established oxide-oxide bonding technology is a promising way for Smart Stacking 3D integration. Direct bonding of two oxide surfaces, however, requires thorough control of surface preparation. The Smart Stacking technology was demonstrated on 300 mm wafers with more than 10 layers of backend metal and a deposited oxide layer on top acting as the bonding layer. Wafer topology was controlled by a chemical-mechanical polishing process that maintains wafer edge quality and wafer micro-roughness <5 Å RMS. This process is fully compatible with common interconnect planarization technologies [32].

(b) Smart Stacking based on low-temperature patterned metal bonding enables the formation of electrical contacts during the stacking process: a promising path for high-density 3D interconnects. Non-thermo compression bonding, unlike thermo compression option, is performed RT under atmospheric pressure and is based on molecular adhesion between surfaces in contact. The bonding process does not require any additional processing steps: standard dual-damascene processes and surface treatment techniques are optimized to ensure smooth hydrophilic surfaces [31]. The bonding can be done directly after standard backend processes and can be adapted for via middle and via last integration schemes. Authors [31] investigated this bonding option for copper pad sizes varying from 5 to 500  $\mu$ m with a pitch of 10 and 40  $\mu$ m; excellent bonding interface defectivity was demonstrated.

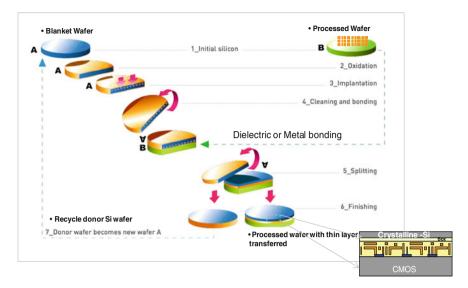

(c) Smart Cut technology is a promising option for monolithic 3D integration. E.g. blanket single-crystal Si layers can be transferred on a processed wafer and "second level" of devices and circuits will be fabricated afterwards in the Si film (see Fig. 23). This approach is based on the optimization of the bonding energy with the reduction of the overall thermal budget (as done for Smart Stacking) as well as optimizing the splitting kinetics to achieve layer transfer at low temperature (<350 °C) [32]. The W2W direct bonding used in Smart Cut technology could include oxide-oxide or metal-metal bonding [33]. The later option allows the formation of electrical connections during the bonding process. Figures 24 and 25 illustrates the recent results (demonstrated on 300 mm wafers) for the transfer of the 200–400 nm Si layers (with typical uniformity range of  $\pm 15$  nm) with low surface micro-roughness [33].

#### **4** Conclusions and Perspectives

In the last 2–3 years, the application domain of the engineered substrates has gone through fundamental paradigm change. The ultra-thin-body SOI-based devices/ circuits with undoped channels are entering the advanced phase of industrialization. Such SOCs feature good performance, high circuit density, competitive overall cost with completion solutions and low power consumption. The later is of critically importance for rapidly growing market of portable consumer electronics. In addition, engineered substrates enable the applications that represent formidable technical challenge for bulk Si: RF devices with high resistivity substrates, Sibased photonics, 3D integration, as well as backside imagers and MEMS devices.

Acknowledgments Fruitful discussions and advices provided by B.-Y. Nguyen, W. Schwarzenbach, C. Aulnette, N. Daval, O. Bonnin, F. Allibert, L. Ecarnot, P. Nguyen, X. Cauchy, I. Radu, M. Sadaka, E. Desbonnets, C. Cailler, A. Rigny, and many other colleagues at Soitec, CEA-LETI, IMEP-LAHC, and STMicroelectronics are gratefully acknowledged.

#### References

- 1. Skotnicki, T., Arnaud, F., Faynot, O.: UTBB SOI: a wolf in sheep's clothing. Fut. Fab Int. 42, 72–79 (2012)

- Auth, C., et al.: A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In: Symposium on VLSI Technology. Digest of Technical Papers, pp. 131–132 (2012)

- Schwarzenbach, W., Daval, N., Barec, V., Bonnin, O., Acosta-Alba, P., Maddalon, C., Chibko, A., Robson, T., Nguyen, B.Y., Maleville, C.: Atomic scale thickness control of SOI wafers for fully depleted applications. ECS Trans. 53(5), 39–46 (2013)

- Schwarzenbach, W., Cauchy, X., Boedt, F., Bonnin, O., Butaud, E., Girard, C.B.-Y., Nguyen, B.Y., Mazure, C., Maleville, C.: Excellent silicon thickness uniformity on ultra-thin SOI for controlling Vt variation of FDSOI. In: IEEE International Conference on ICICDT 2012– Paper B3 (2011)

- Besnard, G., Garros, X., Nguyen, P., Andrieu, F., Reynaud, P., Van Den Daele, W., Bourdelle, K.K., Schwarzenbach, W., Reimbold, G., Cristoloveanu, S.: Reliability of ultrathin buried oxides for multi-V<sub>T</sub> FDSOI technology. In: EuroSOI Conference 2013–Paper 3.3 (2013)

- 6. Hashemi, P., et al.: High-performance Si<sub>1-x</sub>Ge<sub>x</sub> channel on insulator tri-gate PFETs featuring an implant-free process and aggressively-scaled fin and gate dimensions. In: Symposium on VLSI Technology. Digest of Technical Papers–Paper 2.2 (2013)

- Brown, A.R., Daval, N., Bourdelle, K.K., Nguyen, B.Y., Asenov, A.: Simulation analysis of process-induced variability in nanoscale SOI and bulk FinFETs. In: IEEE International SOI Conference–Paper 11.4 (2012)

- Dobrovolný, P., Zuber, P., Miranda, M., Garcia Bardon, M., Chiarella, T., Buchegger, P., Mercha, K., Verkest, D., Steegen, A., Horiguchi, N.: Impact of fin height variations on SRAM yield. In: Symposium on VLSI-TSA. Digest of Technical Papers–Paper T45 (2012)

- Schwarzenbach, W., Daval, N., Kerdilès, S., Chabanne, G., Figuet, C., Guerroudj, S., Bonnin, O., Cauchy, X., Nguyen, B.Y., Maleville, C.: Strained silicon on insulator substrates for fully depleted application. In: IEEE International ICICDT Conference–Paper H3 (2012)

- Tiberj, A., Paillard, V., Aulnette, C., Daval, D., Bourdelle, K.K., Moreau, M., Kennard, M., Cayrefourcq, I.: Stress metrology: the challenge for the next generation of engineered wafers. In: Proceedings of Materials Research Society Symposium–Paper B3.1.1, vol. 809 (2004)

- Fenouillet-Beranger, C., Perreau, P., Weber, O., Ben-Akkez, I., Cros, A., Bajolet, A., Haendler, S., Fonteneau, P., Gouraud, P., Richard, E., Abbate, F., Barge, D., Pellissier-Tanon, D., Dumont, B., Andrieu, F., Passieux, J., Bon, R., Barral, V., Golanski, D., Petit, D., Planes, N., Bonin, O., Schwarzenbach, W., Poiroux, T., Faynot, O., Haond, M., Boeuf, F.: Enhancement of devices performance of hybrid FDSOI/Bulk technology by using UTBOX sSOI substrates. In: Symposium on VLSI Technology. Digest of Technical Papers, pp. 115–116 (2012)

- Allibert, F., Cheng, K., Schwarzenbach, W., Khakifirooz, A., Ecarnot, L., Nguyen, B.Y., Doris, B.: Evaluation of sSOI wafers for 22 nm node and beyond. In: SOI Conference–Paper 7.2 (2012)

- Minamisawa, R.A., Süess, M.J., Spolenak, R., Faist, J., David, C., Gobrecht, J., Bourdelle, K.K., Sigg, H.: Top-down fabricated silicon nanowires under tensile elastic strain up to 4.5 %. Nat. Commun. 3, 1096 (2012). doi: 10.1038/ncomms2102

- Knoll, L., Zhao, Q.T., Nichau, A., Trellenkamp, S., Richter, S., Schäfer, A., Esseni, D., Selmi, L., Bourdelle, K.K., Mantl, S.: Inverters with strained Si nanowire complementary tunnel field-effect transistors. Electron Device Lett. IEEE 34, 813–815 (2013)

- Daval, N., Figuet, C., Aulnette, C., Landru, D., Drazek, C., Bourdelle, K.K., Guiot, E., Letertre, F., Nguyen, B.Y., Mazure, C.: SiGe and Ge on insulator wafers. ECS Trans. 35(5), 29–38 (2011)

- 16. Ikeda, K., Kamimuta, Y., Moriyama, Y., Ono, M., Koji, U., Oda, M., Irisawa, T., Furuse, K., Tezuka, T.: Enhancement of hole mobility and cut-off characteristics of strained Ge nanowire pMOSFETs by using plasma oxidized GeOx inter-layer for gate stack. In: Symposium on VLSI Technology. Digest of Technical Papers–Paper 3.3 (2013)

- Ivana Subramanian, S., Owen, M.H.S., Tan, K.H., Loke, W.K., Wicaksono, S., Yoon, S.F., Yeo, Y.C.: N-channel InGaAs field-effect transistors formed on Germanium-on-insulator substrates. Appl. Phys. Express 5(116502), 1–3 (2012)

- Jalaguier, E., Aspar, B., Pocas, S., Michaud, J.F., Zussy, M., Papon, A.M., Bruel, M.: Transfer of 3in GaAs film on silicon substrate by proton implantation process. Electron. Lett. 34, 408–409 (1998)

- Jalaguier, E., Aspar, B., Pocas, S., Michaud, J.F., Papon, A.M., Bruel, M.: Transfer of thin InP films onto silicon substrate by proton implantation process. In: Proceedings of the 11th International Conference on Indium Phosphide and Related Materials, pp. 26–27 (1999)

- Di Cioccio, L., Jalaguier, E., Letertre, F.: III–V layer transfer onto silicon and applications. Phys. Status Solidi A 202, 509–515 (2005)

- Czornomaz, L., Daix, N., Caimi, D., Sousa, M., Erni, R., Rossell, M.D., El-Kazzi, M., Rossel, C., Marchiori, C., Uccelli, E., Richter, M., Siegwart, H., Fompeyrine, J.: An integration path for gate-first UTB III–V-on-insulator MOSFETs with silicon, using direct wafer bonding and donor wafer recycling. In: Proceedings of the IEEE International Conference on Electron Devices Meeting, IEDM 2012. Technical Digest, pp. 517–520 (2012)

- Kim, S.H., Yokoyama, M., Nakane, R., Ichikawa, O., Osada, T., Hata, M., Takenaka, M., Takagi, S.: Strained extremely-thin body In<sub>0.53</sub>Ga<sub>0.47</sub>As-on-insulator MOSFETs on Si substrates. In: Symposium on VLSI Technology. Digest of Technical Papers–Paper 5-1 (2013)

- 23. Kim, S.H., Yokoyama, M., Nakane, R., Ichikawa, O., Osada, T., Hata, M., Takenaka, M., Takagi, S.: High performance extremely-thin body InAs-on-insulator MOSFETs on Si with Ni-InGaAs metal S/D by contact resistance reduction technology. In: Symposium on VLSI Technology. Digest of Technical Papers–Paper 5-2 (2013)

- Imthurn, G.P., Miscione, A.M., Landry, K., Vaufredaz, A., Barge, T., Lagahe-Blanchard, C.: Strain reduction in silicon-on-sapphire by wafer bonding. In: SOI Conference–Paper 6.2 (2011)

- 25. Ben Ali, K., Roda Neve, C., Gharsallah, A., Raskin, J.P.: RF SOI CMOS technology on commercial trap-rich high resistivity SOI wafer. In: SOI Conference–Paper 9.2 (2012)

- Roda Neve, C., Raskin, J.P.: RF harmonic distortion of CPW lines on HR-Si and trap-rich HR-Si substrates. Electron. Devices IEEE Trans. 59, 924–932 (2012)

- 27. Roda Neve, C., Ben Ali, K., Malaquin, C., Allibert, F., Desbonnets, E., Bertrand, I., Van Den Daele, W., Raskin, J.P.: RF and linear performance of commercial 200 mm trap-rich HR-SOI wafers for SoC applications. In: Proceedings of the 13th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems–SiRF'13–Paper MO2B-2 (2013)

- Zuffada, M.: The industrialization of the silicon photonics: technology road map and applications. In: 42nd European Solid-State Device Research Conference, ESSDERC 2008, pp. 7–13 (2012)

- Akiyama, S., Grawert, F.J., Liu, J., Wada, K., Celler, G.K., Kimerling, L.C., Kaertner, F.X.: Fabrication of highly reflecting epitaxy-ready Si/SiO<sub>2</sub> Bragg reflectors. Photonics Technol. Lett. IEEE 17, 1456–1458 (2005)

- Sadaka, M., Radu, I., Lagahe-Blanchard, C., Di Cioccio, L.: Stacking<sup>TM</sup> and smart cut<sup>TM</sup> technologies for wafer level 3D integration. In: ICICDT Conference–Paper L4 (2012)

- Radu, I., Landru, D., Gaudin, G., Riou, G., Tempesta, C., Letertre, F., Di Cioccio, L., Gueguen, P., Signamarcheix, T., Euvrard, C., Dechamp, J., Clavelier, L., Sadaka, M.: Recent developments of Cu-Cu non-thermo compression bonding for wafer-to-wafer 3D stacking. In: Proceedings of the IEEE International Conference on 3D Systems Integration (3DIC) 2010, pp. 1–6 (2010)

- 32. Gaudin, G., Riou, G., Landru, D., Tempesta, C., Radu, I., Sadaka, M., Winstel, K., Kinser, E., Hannon, R.: Low temperature direct wafer to wafer bonding for 3D integration: Direct bonding, surface preparation, wafer-to-wafer alignment. In: Proceedings of the IEEE International Conference on 3D Systems Integration (3DIC) 2010, pp. 1–4 (2010)

- 33. Di Cioccio, L., Radu, I., Baudin, F., Mounier, A., Lacave, T., Delaye, V., Imbert, B., Chevalier, N., Mariolle, D., Thieffry, S., Mazen, F., Gaudin, G., Signamarcheix, T.: Wafer level 3D stacking using smart cut<sup>TM</sup> and metal-metal direct bonding technology. ECS Trans. 50(7), 169–175 (2012)

## Perspectives of UTBB FD SOI MOSFETs for Analog and RF Applications

Valeriya Kilchytska, Sergej Makovejev, Mohd Khairuddin Md Arshad, Jean-Pierre Raskin and Denis Flandre

Abstract Ultra-thin body and buried oxide (UTBB) fully depleted (FD) siliconon-insulator (SOI) MOSFETs are widely recognized as a promising candidate for 20 nm technology node and beyond, due to outstanding electrostatic control of short channel effects (SCE). Introduction of a highly-doped layer underneath thin buried oxide (BOX), so called ground-plane (GP), targets suppression of detrimental parasitic substrate coupling and opens multi-threshold voltage  $(V_{Th})$  and dynamic- $V_{Th}$  opportunities within the same process as well as the use of back-gate control schemes [1, 2]. Electrostatics, scalability and variability issues in UTBB MOSFETs as well as their perspectives for low power digital applications are widely discussed in the literature [1-5]. At the same time assessment of UTBB FD SOI for analog and RF applications received less attention. This *chapter* will discuss Figures of Merit (FoM) of UTBB MOSFETs of interest for further analog/ RF applications summarizing our original research over the last years [6-15]. Device analog/RF performance is assessed through the key parameters such as the transconductance,  $g_m$ , the output conductance,  $g_d$ , the intrinsic gain,  $A_v$  and the cutoff frequencies,  $f_T$  and  $f_{max}$ . Particular attention is paid to (1) a wide-frequency band assessment, the only approach that allows fair performance prediction for analog/RF applications; (2) the effect of parasitic elements, whose impact on the device performance increases enormously in deeply downscaled devices, in which they can even dominate device performance. Whenever possible, we will compare FoM achievable in UTBB FD SOI devices with those reported for other advanced devices.

V. Kilchytska (🖂) · S. Makovejev · J.-P. Raskin · D. Flandre

ICTEAM Institute, Université Catholique de Louvain, 1348 Louvain-la-Neuve, Belgium e-mail: valeriya.kilchytska@uclouvain.be

M.K. Md Arshad Institute of Nanoelectronic Engineering, Universiti Malaysia Perlis, 01000 Kangar, Perlis, Malaysia

<sup>©</sup> Springer International Publishing Switzerland 2014

A. Nazarov et al. (eds.), Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting, Engineering Materials, DOI 10.1007/978-3-319-08804-4\_2

# **1** Introduction

Enormous progress of the semiconductor technology during the last decade is mostly driven by the continuous demand for the increase of the operation speed and the integration density of complex digital circuits. In order to be able to continue device scaling down to 20 nm and beyond, both new materials and new device architectures are unavoidably employed. Therefore, nowadays we deal not simply with proportional shrinking of respective device dimensions, but as well as with new architectures and materials in both channel and gate oxide. Both these factors will evidently affect analog/RF device features. From the device architecture point of view, two main contenders clearly appear as able to satisfy ITRS requirements for device downscaling: planar FD SOI with ultra-thin body and ultra-thin BOX (so-called UTBB, or UTBOX, or UT2B or ETSOI) and multiple-gate devices or MuGFET.

Focus of this chapter is UTBB FD SOI MOSFETs, while some benchmarking with other devices is provided whenever possible. Main features which allow UTBB FD SOI withstanding ITRS requirements for 20 nm-node and beyond are the following:

- outstanding electrostatic integrity;

- effective suppression of fringing fields through the BOX (by BOX thinning);

- ease of heat exhaust through the thin BOX and thus attenuated self-heating (SH) is expected;

- possibility of back-gate control schemes implementation.

However, lateral coupling of source and drain through the substrate is enhanced in the case of thin-BOX devices. This calls for realization of highly-doped layer just under the BOX, or so-called Ground Plane (GP), which screens or prevents electric field lines penetration into the substrate and thus coupling through the substrate. Furthermore, GP opens a practical way for multi- $V_{Th}$  and back-gate biasing schemes realization.

Technological aspects, electrostatics, scalability and variability issues in UTBB FD SOI MOSFETs as well as their perspectives for low power digital applications are widely discussed and shown to be excellent [1-5]. However, till now almost no attention has been paid to analog and RF performance of these devices. Similarly, UTBB MOSFET small-signal behavior in a wide frequency range is rarely discussed except in our works issued during last 3 years [6–15].

## 2 Devices

UTBB FD SOI MOSFETs discussed in this chapter have been processed at CEA-Leti on UNIBOND<sup>TM</sup> SOI wafers with either 25 or 10 nm-thick BOX. Wafers without GP, with n- and p-type GP are considered. The Si film in the channel region is thinned down to 7–8 nm, depending on the wafer, and left undoped. Elevated source-drain structures are employed to reduce parasitic resistance. The gate stack is formed by a HfSiON dielectric with the equivalent oxide thickness of  $\sim 1.3$  nm and a TiN electrode. More process details can be found e.g. in [1, 2].

The studied devices are n-channel MOSFETs with the gate length L ranging from 30 nm to 10  $\mu$ m and the channel width W from 80 nm to 10  $\mu$ m. Multifingers devices are used and embedded in coplanar waveguide access pads for performing RF characterization.

## **3 MOSFET's Key Parameters and Methodology Applied**

It is worth firstly to list the key device parameters and FoM of interest for analog/ RF applications and describe the methodological approach, which allows a fair comparison of different devices under different bias conditions.

Main key-factors of any MOSFET are: cut-off frequencies ( $f_T$  and  $f_{max}$ ) and intrinsic voltage gain ( $A_{\nu 0}$ ), which itself varies in a frequency range (as will be discussed in Sect. 5):

$$f_T = \frac{g_m}{2 \cdot \pi \cdot C_{gg}},\tag{1}$$

$$A_{\nu 0} = \frac{g_m}{g_d} = \frac{g_m}{I_d} \cdot V_{EA} \neq const(f)$$

<sup>(2)</sup>

These key factors in turn depend on such device parameters as transconductance  $(g_m)$ , drive/drain current  $(I_d)$ , output conductance  $(g_d)$ , Early voltage  $(V_{EA} = I_d/g_d)$ ,  $g_m/I_d$ , gate capacitance  $(C_{gg})$ , etc. One should not forget as well about parasitic capacitance and resistance elements (as will be discussed below).

If one considers the application circuit level (e.g. amplifier), then it involves gain bandwidth product, *GBW*, which depends in turn on the same device parameters  $(g_m/I_d \text{ and } I_d)$ :

$$GBW = \frac{g_m}{2 \cdot \pi \cdot C_L} = \frac{g_m}{I_d} \cdot \frac{I_d}{2 \cdot \pi \cdot C_L},\tag{3}$$

where  $C_L$  is load capacitance.

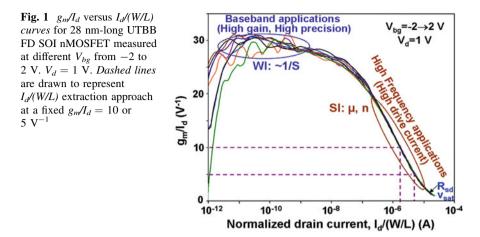

From methodological point of view, a very useful approach for analog performance assessment of different devices is calculating  $g_m/I_d$  as a function of normalized drain current [16, 17]. Firstly, because such plot gives a complete picture of studied device, which is valid for different applications: from base-band applications, where high gain, high precision is needed, to high frequency application where high drive current is requested (Fig. 1). Secondly, as  $g_m/I_d$  is inversely proportional to the subthreshold swing, S in weak inversion regime and proportional to  $\mu \cdot C_{ox}/n$  (where  $\mu$  is mobility,  $C_{ox}$  is oxide capacitance and n is body factor) in strong inversion, such plot is independent of threshold voltage,  $V_{Th}$ , of substrate/back gate (or body) bias,  $V_{bg}$  and to the first order is also independent of

*L*. In practice, one may fix  $g_m/I_d$  value and extract corresponding  $I_d/(W/L)$  values as shown in Fig. 1. This allows assessment of device performance purely related to physical parameters as  $\mu$  or body factor, thus providing a fair comparison of devices issued from different technologies, featuring different dimensions and operated at different conditions.

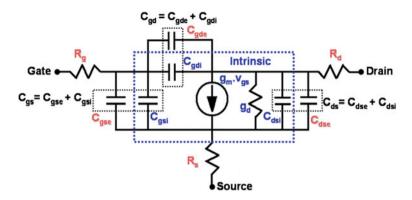

Figure 2 presents the complete small-signal equivalent circuit of a MOSFET. It is important to clearly distinguish between intrinsic elements, i.e. related to the device itself and extrinsic (or parasitic) elements, as access resistances, fringing and overlap capacitances. Parasitic capacitive components (for instance, capacitive coupling between source and drain through the BOX and substrate, fringing gate-to-source and gate-to-drain coupling, etc.) attain particular importance at high/RF frequencies.

With device length scaling down, importance of parasitic components increases enormously. Parasitic elements can even dominate the device performance (as will be shown in Sect. 6). Thus, ability of separate extraction of "intrinsic" and "extrinsic" elements in advanced nowadays technologies becomes crucial. Firstly, this allows for predicting "intrinsically" achievable idealistic or target values one can reach with optimization of parasitics. Secondly, for the process/configuration optimization, it is important to know wherefrom the problem comes (either intrinsic or extrinsic part). Indeed, if extrinsic part limits device performance, any innovations introduced to boost intrinsic performance (e.g. strain, orientation, etc.) will give negligible improvement to the final device performance.

Considering equivalent circuit shown in Fig. 2, MOSFET expressions for cutoff frequencies (Eq. 1) become more complex, accounting for parasitic elements and clearly reflecting SCE (through  $C_{gs}/C_{gd}$  ratio):

$$f_T \approx \frac{g_m}{2 \cdot \pi \cdot C_{gs}} \cdot \frac{1}{\left(1 + \frac{C_{gd}}{C_{gs}}\right) + (R_s + R_d) \cdot \left(\frac{C_{gd}}{C_{gs}} \cdot (g_m + g_d) + g_d\right)}$$

(4a)

Fig. 2 MOSFET complete small-signal equivalent circuit, including both intrinsic (denoted 'i') and extrinsic (denoted 'e') elements

$$f_{\max} \approx \frac{g_m}{4 \cdot \pi \cdot C_{gs}} \cdot \frac{1}{\left(1 + \frac{C_{gd}}{C_{gs}}\right) \sqrt{g_d \left(R_g + R_s\right) + \frac{1}{2} \cdot \frac{C_{gd}}{C_{gs}} \left(R_s \cdot g_m + \frac{C_{gd}}{C_{gs}}\right)}}$$

(4b)

With length shrinkage,  $C_{gd}/C_{gs}$  ratio increases indicating the lost of a gate control over the channel and dominance of control from the drain (increase of capacitive coupling between gate and drain). Comparing Eqs. 4a, 4b and 1 one can see that this effect can strongly degrade 'intrinsic' cut-off frequency. Next to that,  $f_T$  and  $f_{max}$  are degraded by the parasitic access resistances,  $R_s$  and  $R_d$ . Gate resistance,  $R_g$ , however, affects only  $f_{max}$  (see Eq. 4b). According to Eq. 1, as  $g_m$  is inversely proportional to L and proportional to W, while  $C_{gg}$  is proportional to the area,  $f_T$  is expected to increase with L and be independent of W. However, this does not hold in experiments due to strong parasitic effects (as will be shown in Sect. 6).

Extraction of a complete equivalent circuit demands S-parameter measurements in a wide frequency range. Therefore, adequate structures with RF access pads must be included in the layout from a very beginning of the technology development. Details on the extraction procedure can be found for instance in [18].

# 4 UTBB FD SOI MOSFET Analog FoM

### 4.1 Benchmarking with Other MOSFETs

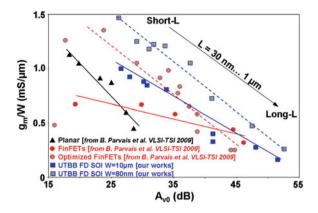

Extended benchmarking of analog FoM of UTBB FD SOI MOSFETs with respect to other both planar FD SOI MOSFETs and multiple-gate SOI-based FinFETs was performed in [6]. Table 1 summarizes analog FoM achievable in UTBB FD SOI with different geometries and compares them with SOI FinFET ones. One can see that UTBB FD SOI devices feature rather high values of  $I_d$ ,  $V_{EA}$ ,  $A_{v0}$ ,  $g_{m\_max}$ , which are comparable and in certain cases can be even higher than in another

|                                            | $g_m \max_{(\mu S/\mu m)}$ | $\begin{bmatrix} I_d / (W/L) g_m / I_d = \\ 10 V^{-1} (\mu A) \end{bmatrix}$ | $\begin{bmatrix} I_d (W/L) & g_m M_d \\ 5 & V^{-1} & (\mu A) \end{bmatrix}$ | $V_{EA} V_g \sim V_{Th} (V)$ | $\frac{I_d(WLL)}{10 V^{-1}} \frac{g_m/I_d}{(\mu A)} = \frac{I_d(WL)}{5 V^{-1}} \frac{g_m/I_d}{(\mu A)} = \frac{V_{EA} V_g \sim V_{Th} (V)}{V_{EA} V_g \sim V_T} \frac{V_{EA} V_g \sim 1 V (V)}{V_{EA} V_g \sim 1 V (V)} \frac{A_{\nu 0\_max} (dB)}{A_{\nu 0\_max} (dB)}$ | $A_{\nu 0\_\mathrm{max}} \ \mathrm{(dB)}$ |

|--------------------------------------------|----------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

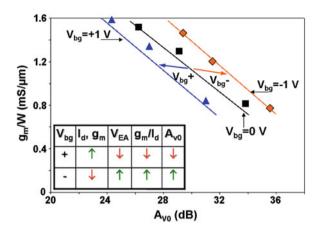

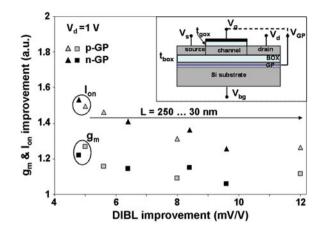

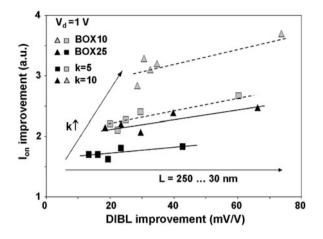

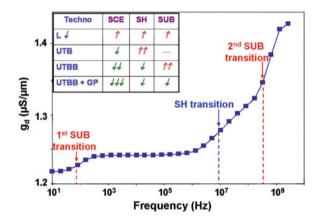

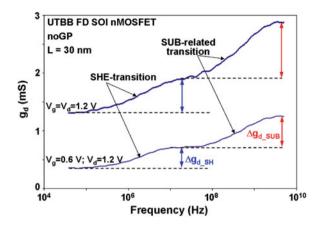

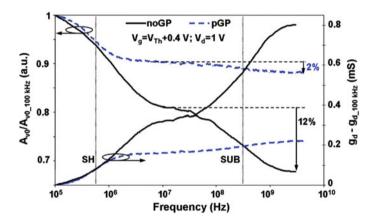

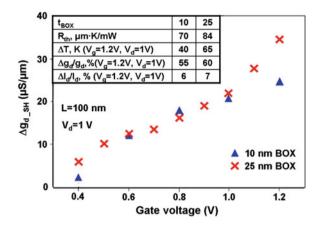

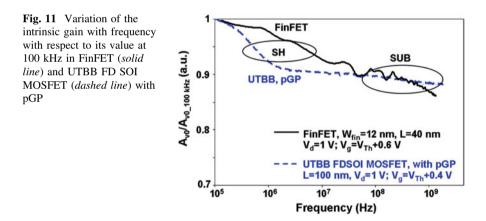

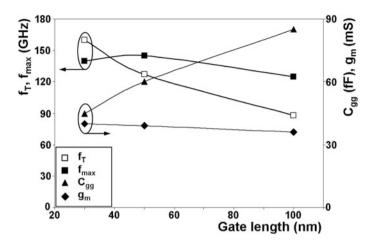

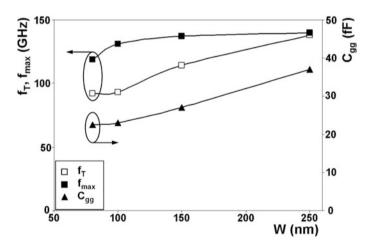

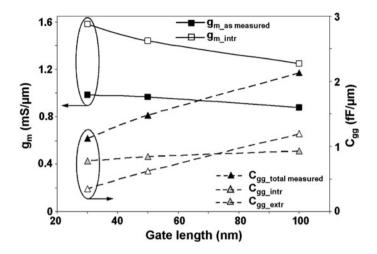

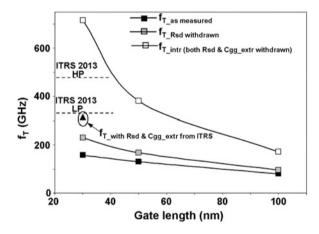

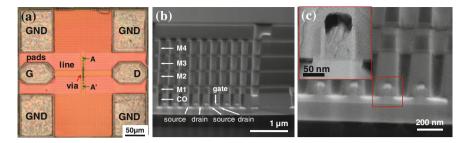

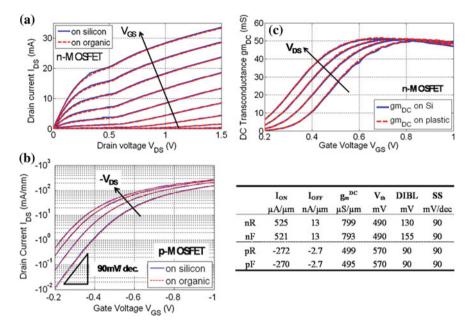

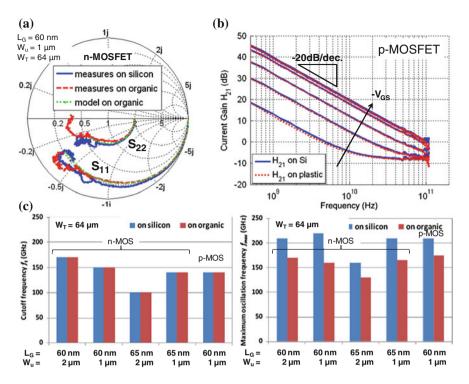

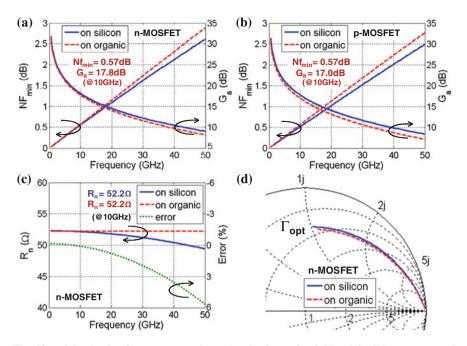

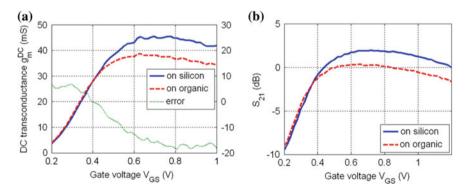

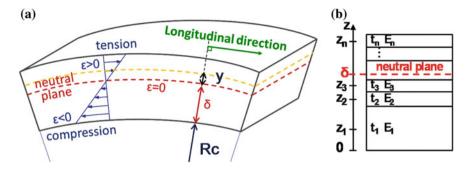

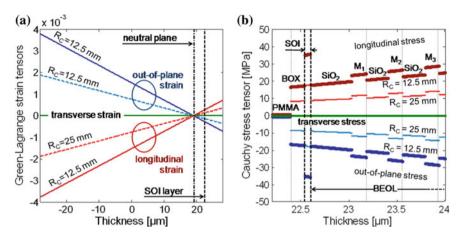

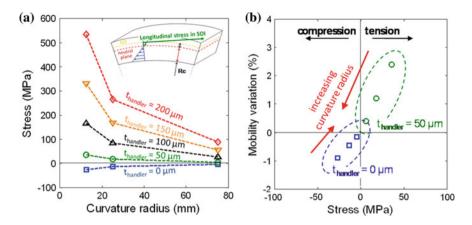

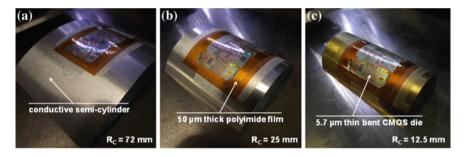

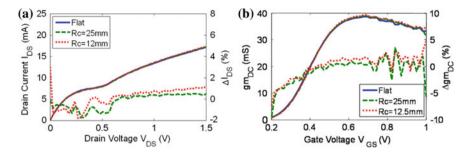

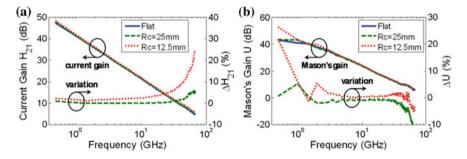

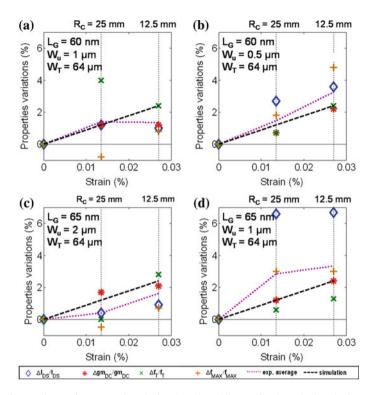

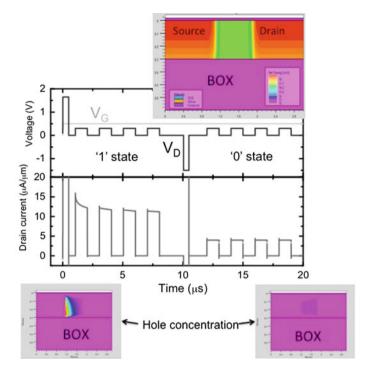

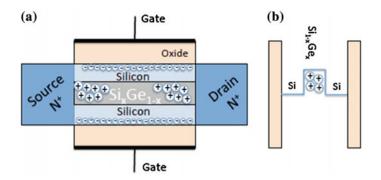

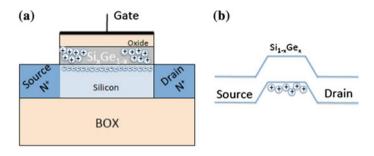

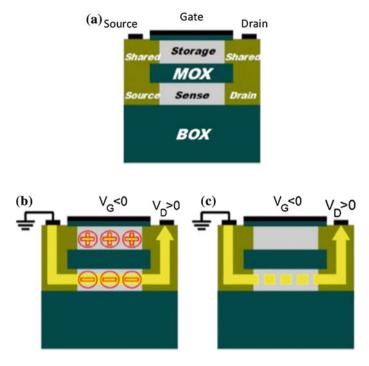

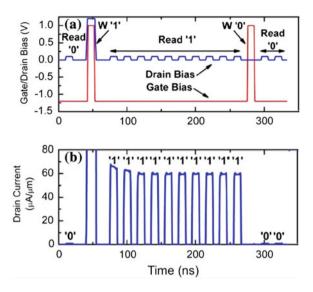

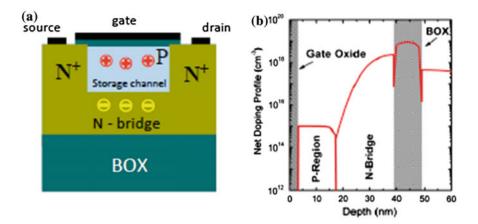

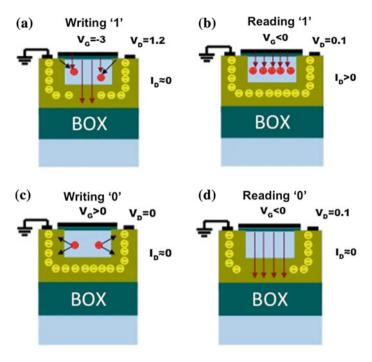

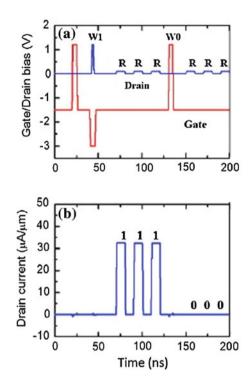

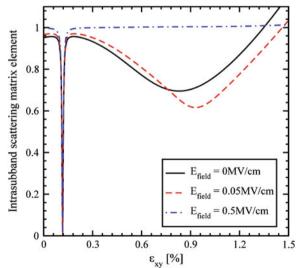

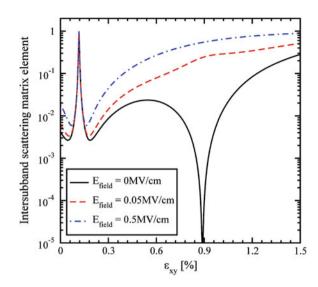

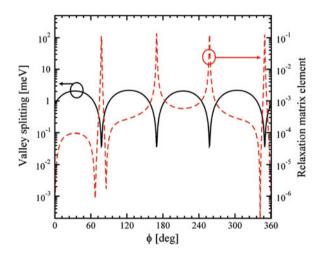

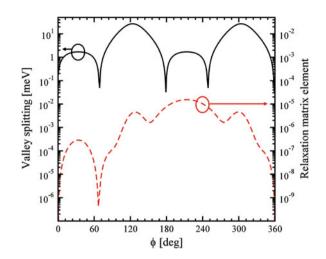

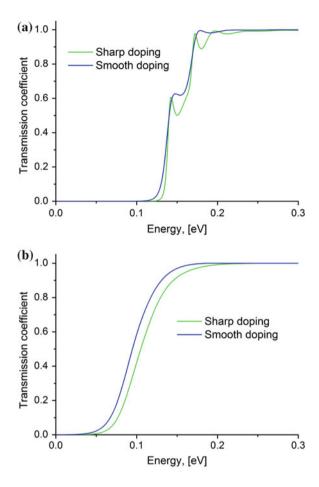

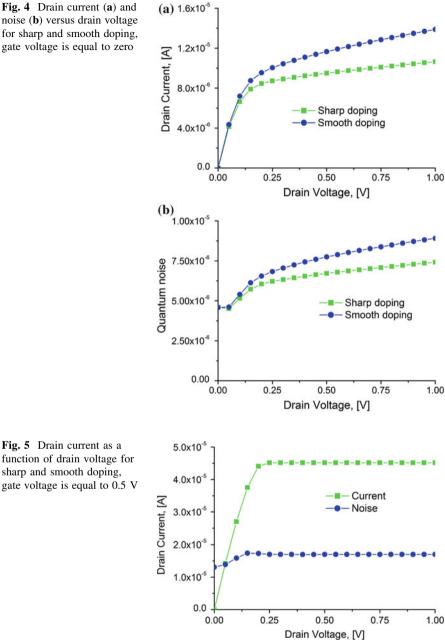

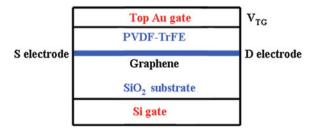

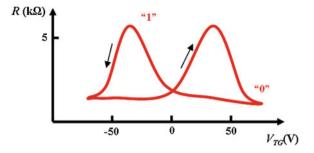

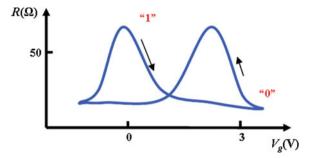

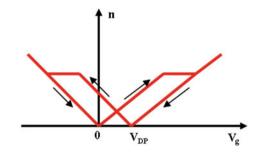

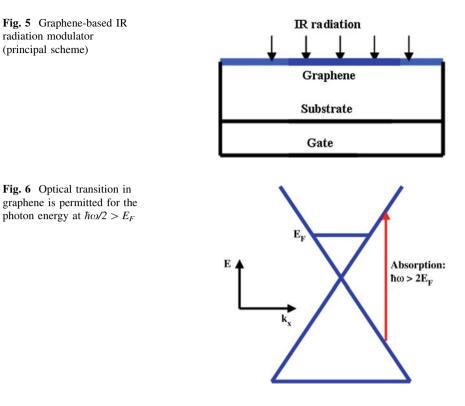

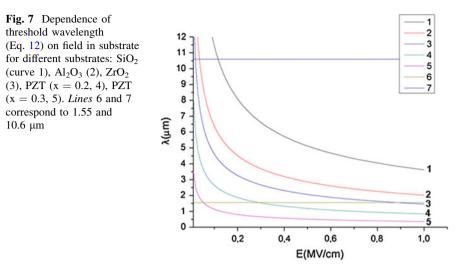

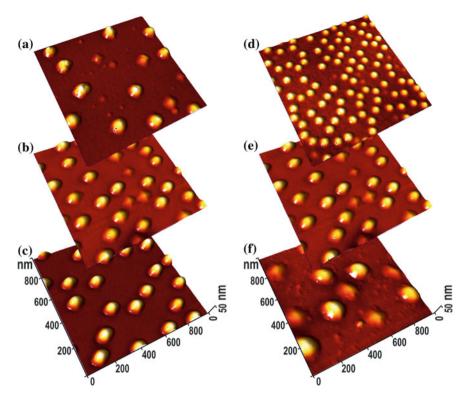

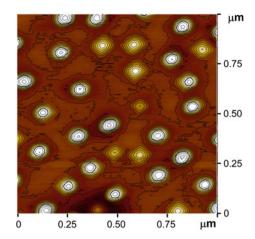

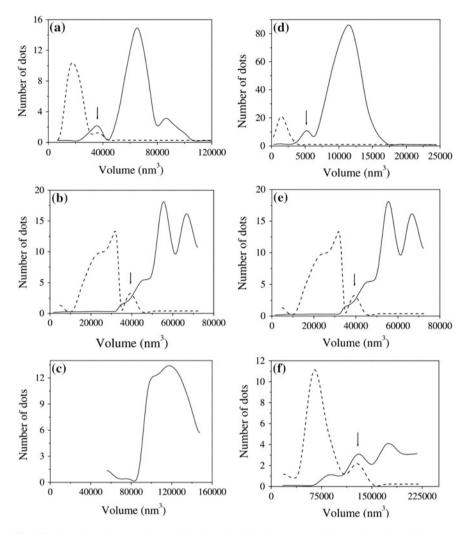

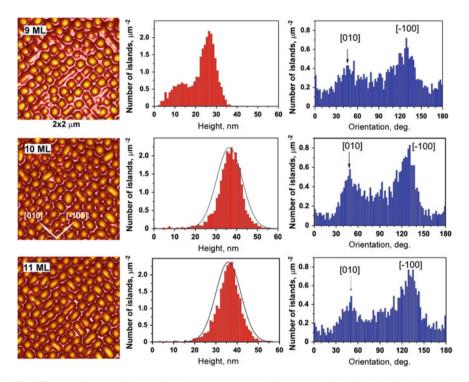

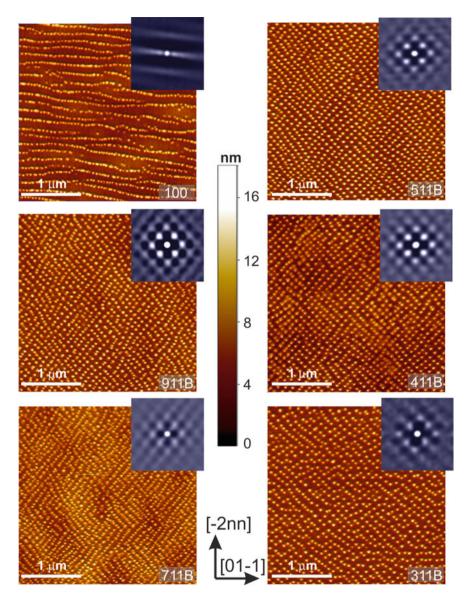

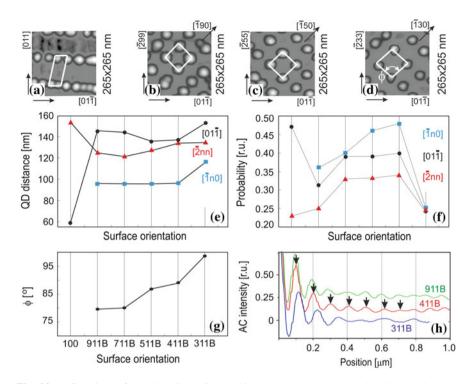

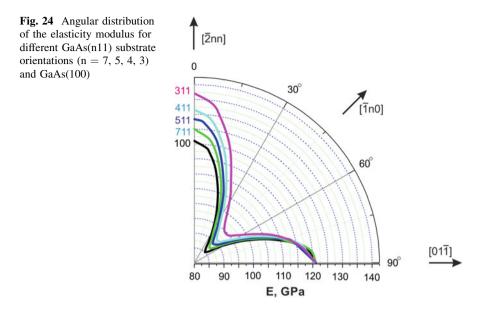

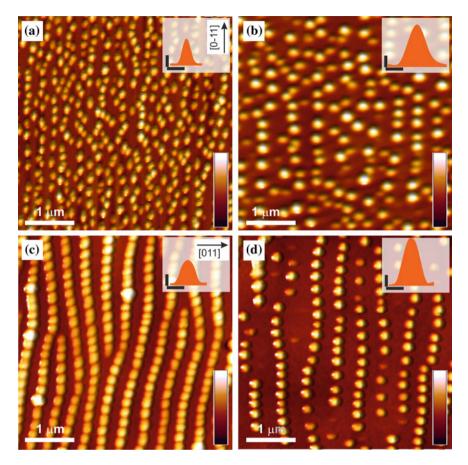

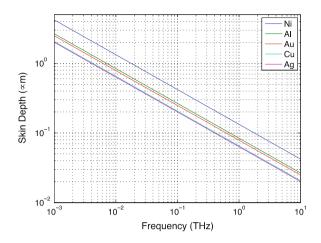

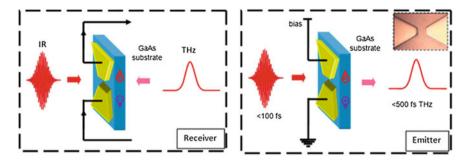

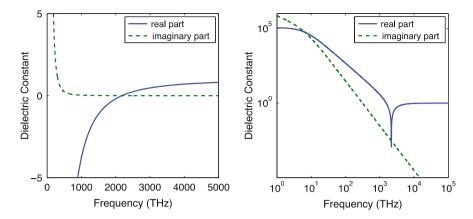

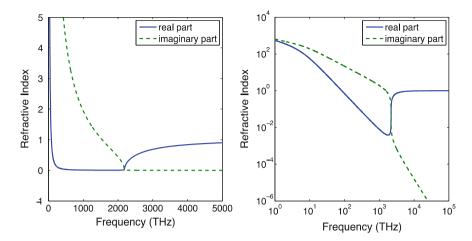

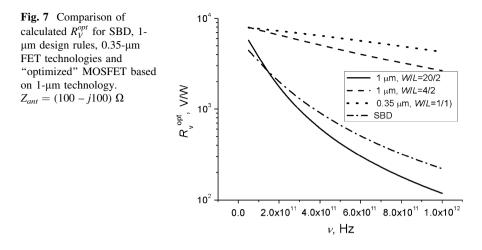

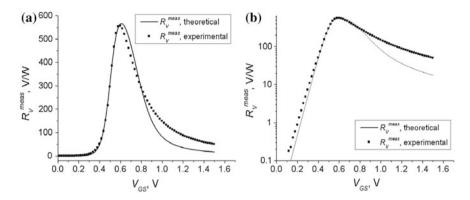

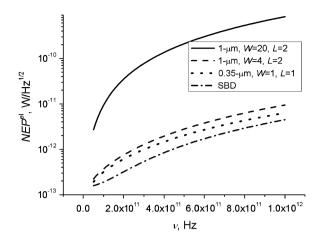

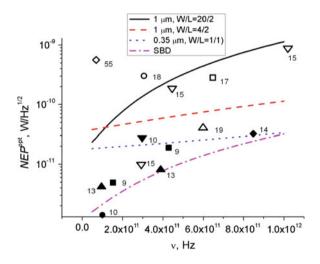

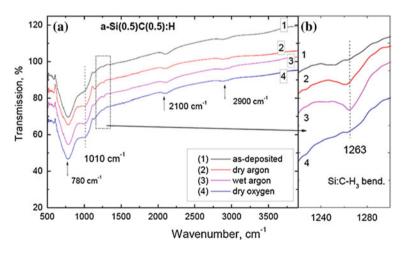

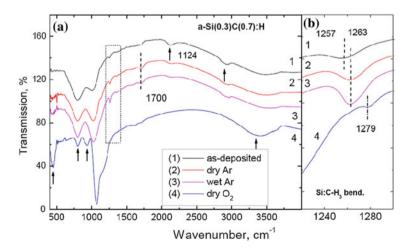

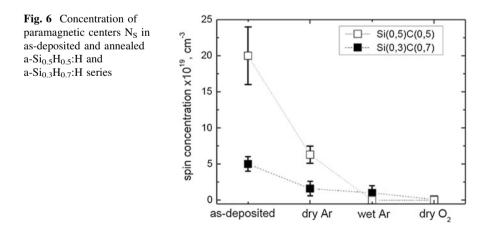

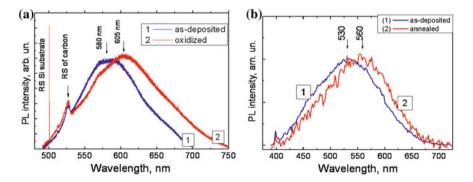

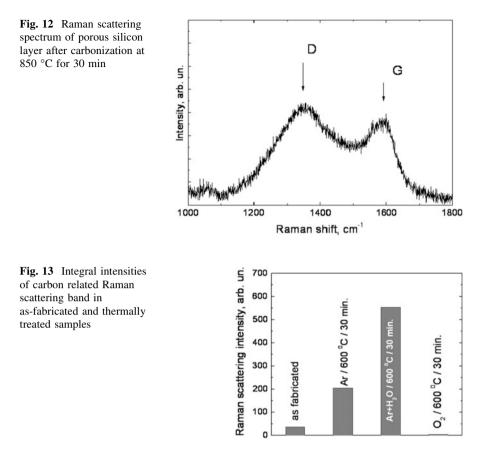

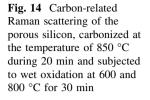

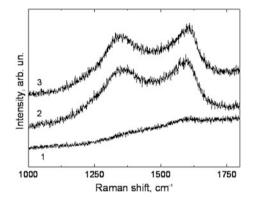

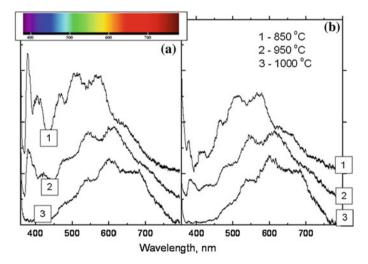

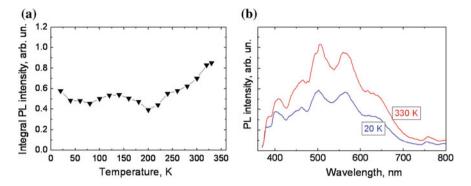

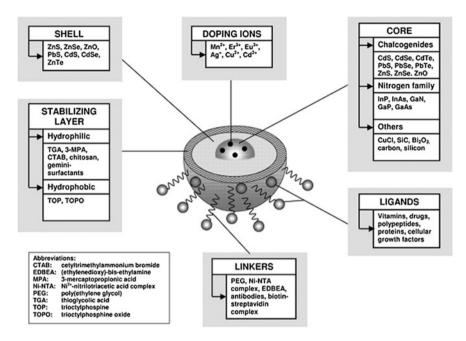

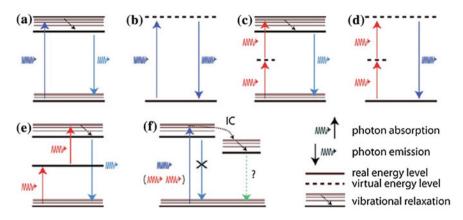

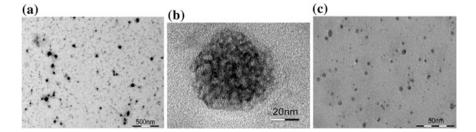

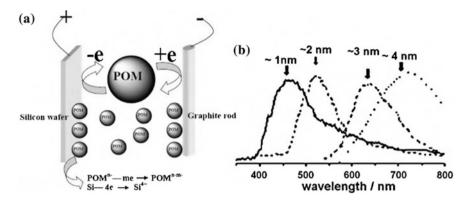

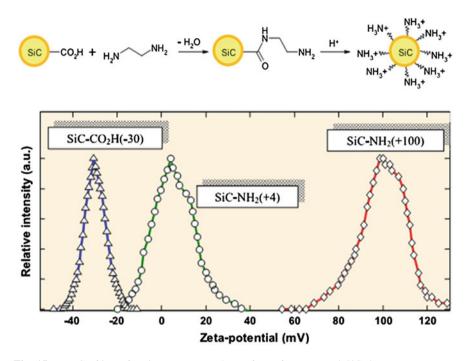

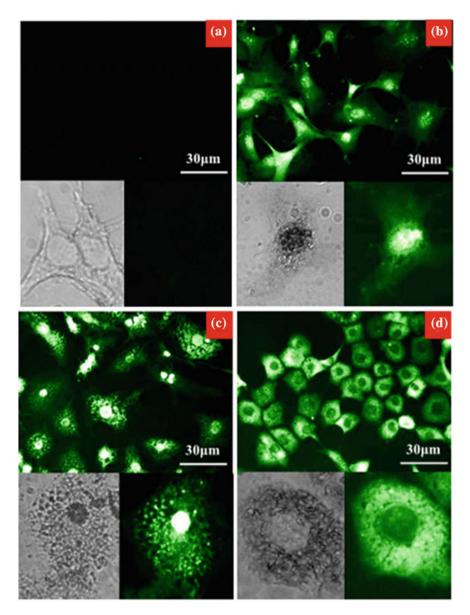

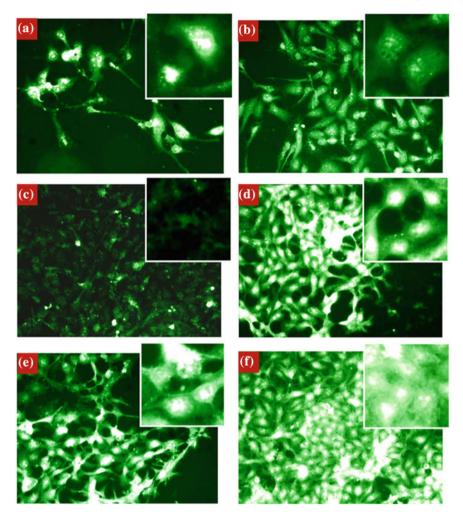

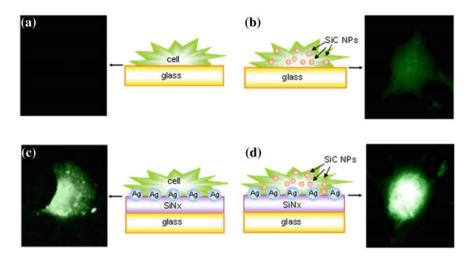

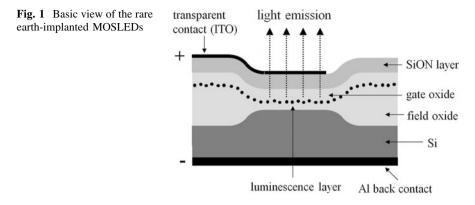

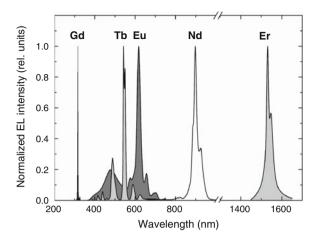

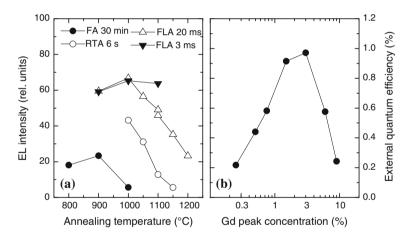

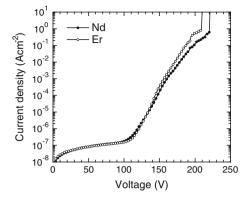

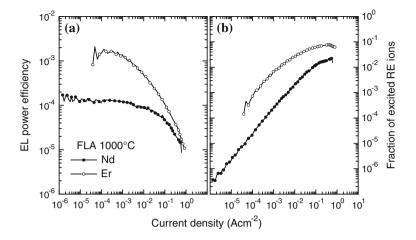

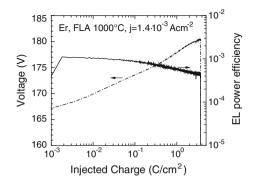

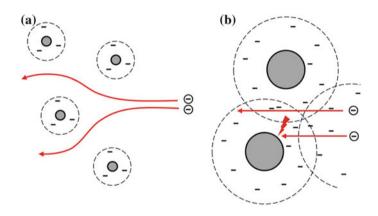

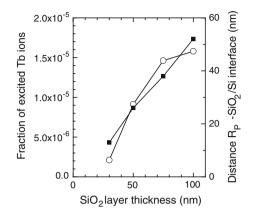

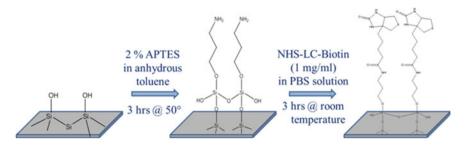

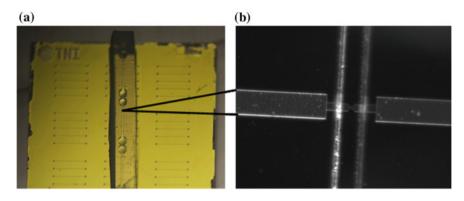

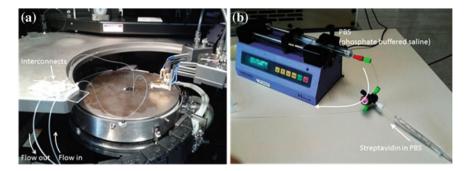

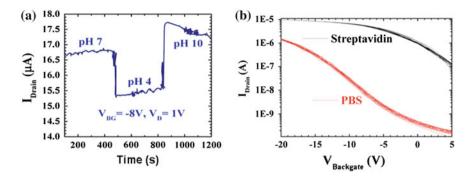

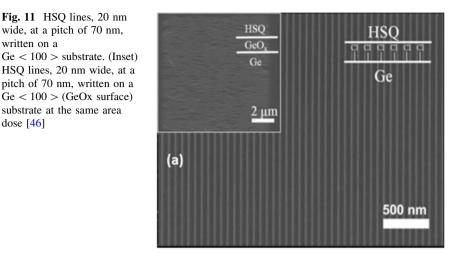

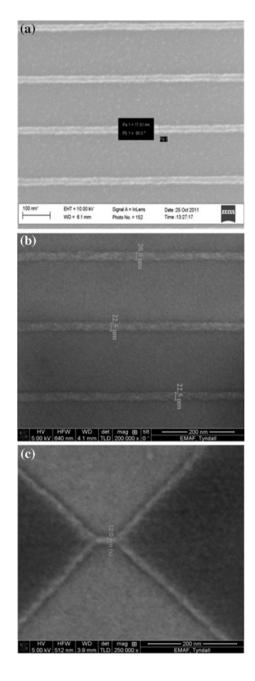

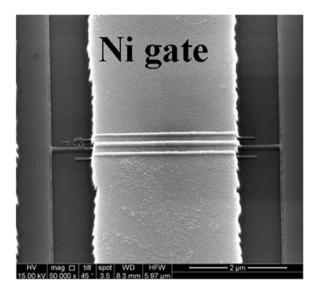

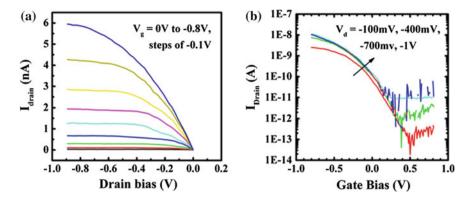

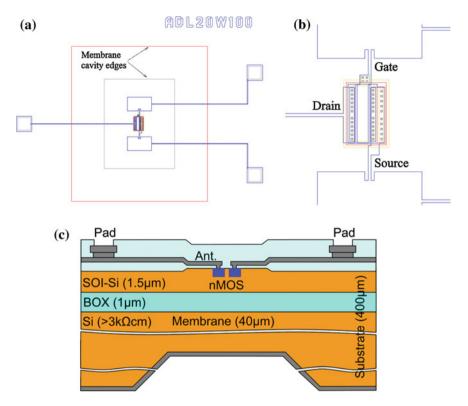

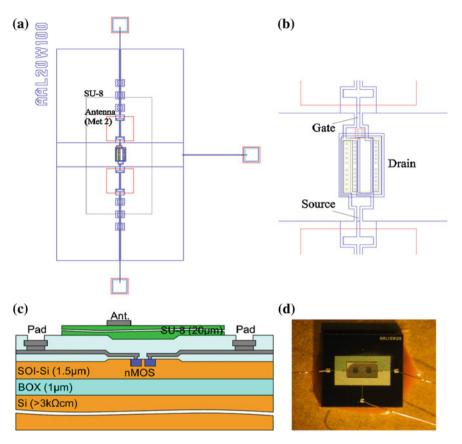

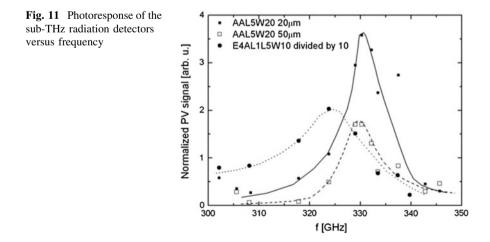

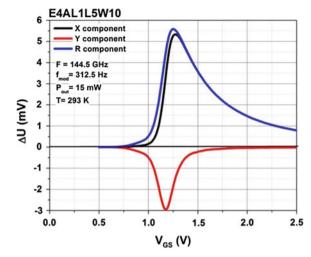

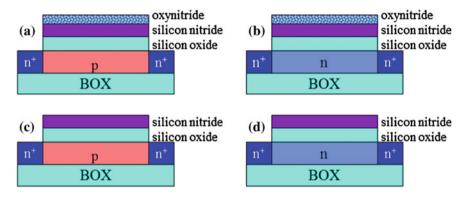

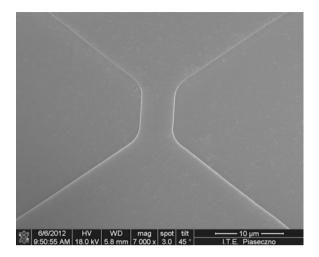

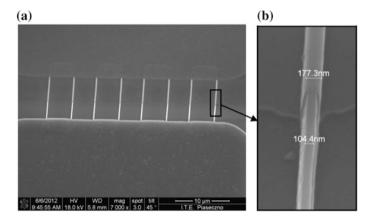

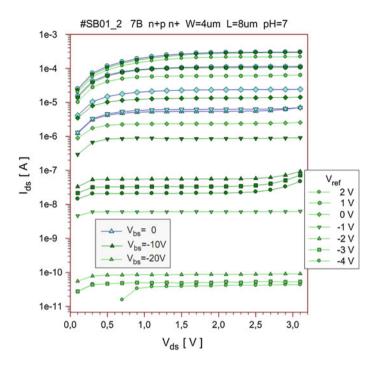

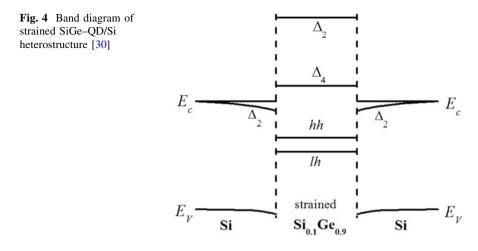

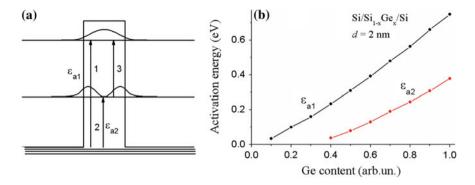

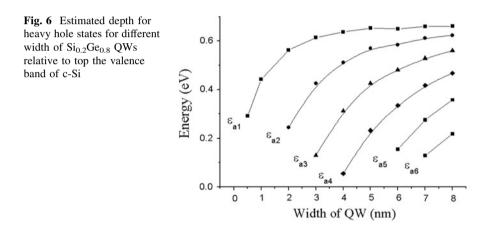

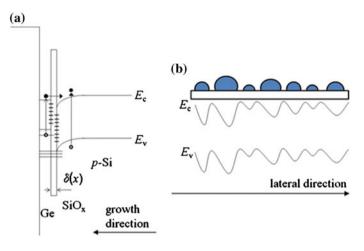

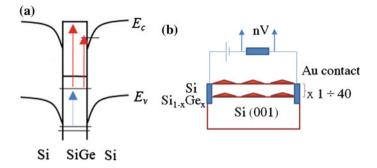

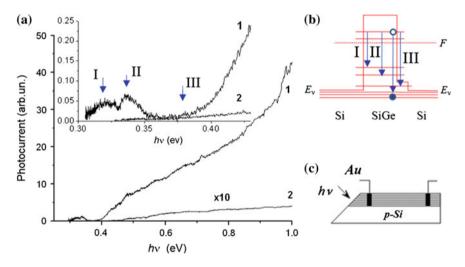

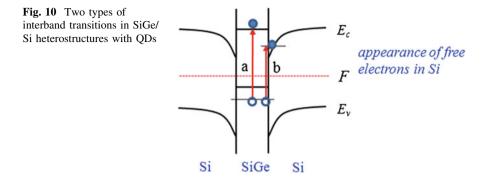

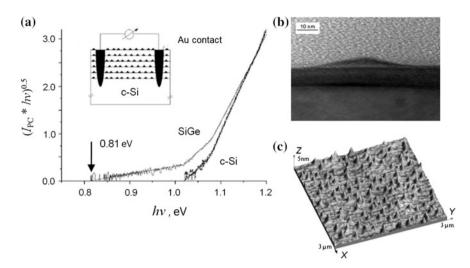

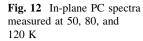

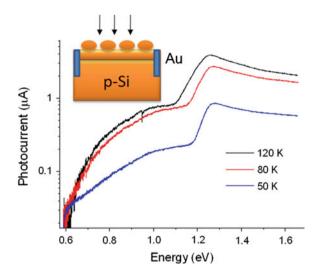

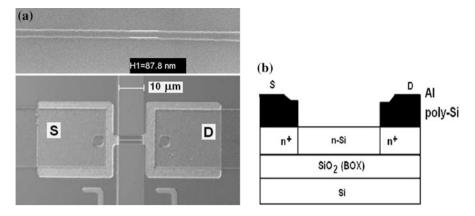

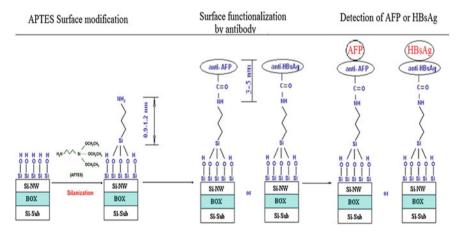

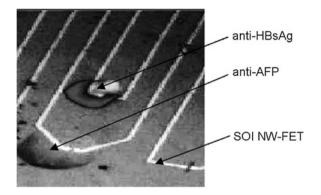

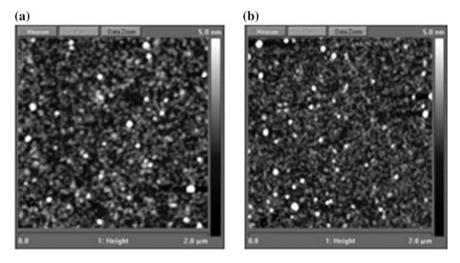

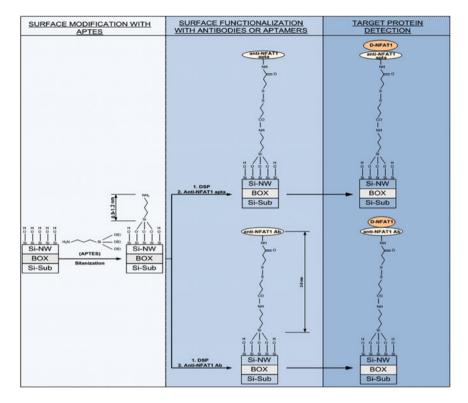

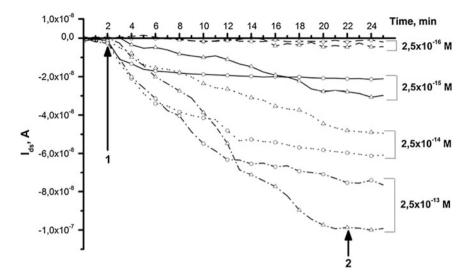

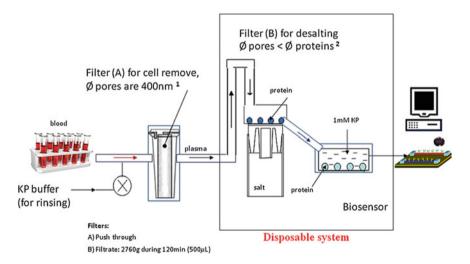

| L = 30  nm                                 |                            |                                                                              |                                                                             |                              |                                                                                                                                                                                                                                                                          |                                           |