Erik Maehle Kay Römer Wolfgang Karl Eduardo Tovar (Eds.)

# Architecture of Computing Systems – ARCS 2014

27th International Conference Lübeck, Germany, February 25-28, 2014 Proceedings

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Germany Madhu Sudan Microsoft Research, Cambridge, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany Erik Maehle Kay Römer Wolfgang Karl Eduardo Tovar (Eds.)

# Architecture of Computing Systems – ARCS 2014

27th International Conference Lübeck, Germany, February 25-28, 2014 Proceedings

#### Volume Editors

Erik Maehle Universität zu Lübeck, Institut für Technische Informatik Lübeck, Germany E-mail: maehle@iti.uni-luebeck.de

Kay Römer Graz University of Technology, Institute of Technical Informatics Graz, Austria E-mail: roemer@tugraz.at

Wolfgang Karl Karlsruhe Institute of Technology (KIT) Institute of Computer Science and Computer Engineering Karlsruhe, Germany E-mail: karl@kit.edu

Eduardo Tovar CISTER-ISEP, Polytechnic Institute of Porto Porto, Portugal E-mail: emt@isep.ipp.pt

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-319-04890-1 e-ISBN 978-3-319-04891-8 DOI 10.1007/978-3-319-04891-8 Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014930986

CR Subject Classification (1998): C.2, C.5.3, D.4, D.2.11, H.3.5, H.4, H.5.4

#### LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

© Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in ist current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

The 27th International Conference on Architecture of Computing Systems (ARCS 2014) was hosted by the Institute of Computer Engineering at the University of Luebeck, Germany, from February 25 to 28, 2014 and continued the long-standing ARCS tradition of reporting top-notch results in computer architecture and related areas. It was organized by the special interest group on Architecture of Computing Systems of the GI (Gesellschaft für Informatik e.V.) and ITG (Informationstechnische Gesellschaft im VDE), where the latter held the organizational and financial responsibility for the 2014 edition. The conference was also supported by IFIP (International Federation of Information Processing), Working Group 10.3 on Concurrent Systems.

The special focus of ARCS 2014 was on connecting computing with the physical world. This reflects the fact that more and more computing systems are deeply embedded into the real world, closely interacting with their physical environment as well as with human users, forming large and dynamic distributed embedded systems. These cyber-physical systems provide new opportunities and challenges for computer and systems architecture, such as ultra-low power consumption, while at the same time meeting real-time constraints and dependability requirements. Novel concepts for self-organization and adaptation are required to address highly dynamic environments, networks, and changing user requirements. Traditional topics of computer architecture, in particular in the area of parallel and high performance computing, are also advancing rapidly, driven mainly by new multi/many-core systems and accelerators.

The conference attracted 44 submissions from 23 countries. Each paper was assigned to at least three Program Committee members for reviewing. The Committee selected 20 submissions for publication with authors from 14 countries. These papers were organized in six sessions covering topics like parallelization methods, self-organization and trust, system design, sensor systems, virtualization or dependability aspects. Three invited talks on "Control of Cyber-physical Systems" by Karl H. Johansson, KTH Royal Institute of Technology, Sweden; "Approximate Computing" by Ravi Nair, IBM Thomas J. Watson Research Center, Yorktown Heights, USA; and "High Performance Computers for Earth System Science" by Thomas Ludwig, German Climate Computing Centre, Hamburg, Germany, completed the strong technical program. Four workshops focusing on specific sub-topics of ARCS were organized in conjunction with the main conference, one on dependability and fault tolerance, one on multi-objective many-core design, one on parallel systems and algorithms, as well as one on self-optimization in organic and autonomic computing systems.

We would like to thank the many individuals who contributed to the success of the conference, in particular the members of the Program Committee as well as the additional external reviewers, for the time and effort they put into reviewing the submissions carefully and selecting a high-quality program. Many thanks also to all authors for submitting their work. The workshops were organized and coordinated by Walter Stechele and Thomas Wild, the proceedings were compiled by Thilo Pionteck, and the financial issues managed by Karl-Erwin Großpietsch. The local arrangements were coordinated by Christian Renner, and the website was maintained by Steffen Prehn. Our gratitude goes to all of them as well as all of the other people, in particular the ITG office team, who helped in the organization of ARCS 2014.

December 2013

Erik Maehle Kay Römer Wolfgang Karl Eduardo Tovar

# Organization

## General Co-chairs

| Erik Maehle<br>Kay Römer                          | Universität zu Lübeck, Germany<br>Graz University of Technology, Austria                                                                            |  |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Program Co-chairs                                 |                                                                                                                                                     |  |  |  |  |

| Wolfgang Karl<br>Eduardo Tovar                    | Karlsruhe Institute of Technology, Germany<br>ISEP-IPP Porto, Portugal                                                                              |  |  |  |  |

| Workshop and Tutorial                             | Co-chairs                                                                                                                                           |  |  |  |  |

| Walter Stechele<br>Thomas Wild                    | Technische Universität München, Germany<br>Technische Universität München, Germany                                                                  |  |  |  |  |

| Publication Chair                                 |                                                                                                                                                     |  |  |  |  |

| Thilo Pionteck                                    | Hamburg University of Technology, Germany                                                                                                           |  |  |  |  |

| Finance Chair                                     |                                                                                                                                                     |  |  |  |  |

| Karl-Erwin Großpietsch                            | St. Augustin, Germany                                                                                                                               |  |  |  |  |

| Local Organization                                |                                                                                                                                                     |  |  |  |  |

| Christian Renner                                  | Universität zu Lübeck, Germany                                                                                                                      |  |  |  |  |

| Program Committee                                 |                                                                                                                                                     |  |  |  |  |

| Michael Beigl<br>Mladen Berekovic<br>Koen Bertels | Karlsruhe Institute of Technology, Germany<br>Technische Universität Braunschweig,<br>Germany<br>Delft University of Technology,<br>The Netherlands |  |  |  |  |

Jürgen Brehm Uwe Brinkschulte Kaan Bur João M.P. Cardoso Luigi Carro Alfons Crespo Martin Daněk Koen De Bosschere Nikitas Dimopoulos Arvind Easwaran Ahmed El-Mahdy Tullio Facchinetti Fabrizio Ferrandi Dietmar Fev Pierfrancesco Foglia William Fornaciari Björn Franke Roberto Giorgi Daniel Gracia Pérez Jan Haase Jörg Hähner Jörg Henkel Andreas Herkersdorf Christian Hochberger Michael Hübner Gert Jervan Ben Juurlink Shinpei Kato Jörg Keller Andreas Koch Anis Koubaa Hana Kubátová

Olaf Landsiedel Paul Lukowicz Pedro José Marrón

Alejandro Masrur

Leibniz Universität Hannover, Germany Goethe University Frankfurt am Main, Germany Lund University, Sweden FEUP/University of Porto, Portugal Universidade Federal do Rio Grande do Sul, Brazil Universitat Politècnica de València, Spain daiteq, Czech Republic Universiteit Gent, Belgium University of Victoria, Canada Nanyang Technological University, Singapore Egypt-Japan University for Science and Technology, Egypt University of Pavia, Italy Politecnico di Milano, Italy Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany Università di Pisa, Italy Politecnico di Milano, Italy University of Edinburgh, UK Università di Siena, Italy Thales Research & Technology, France Technische Universität Wien. Austria Universität Augsburg, Germany Karlsruhe Institute of Technology, Germany Technische Universität München. Germanv Technische Universität Darmstadt, Germany Ruhr-Universität Bochum, Germany Tallinn University of Technology, Estland Technische Universität Berlin, Germany Nagoya University, Japan Fernuniversität Hagen, Germany Technische Universität Darmstadt, Germany Prince Sultan University, Saudi Arabia/CISTER Research Unit, Portugal Czech Technical University in Prague, Czech Republic Chalmers University of Technology, Sweden DKFI, Kaiserslautern, Germany University of Duisburg-Essen and Fraunhofer FKIE, Germany Technische Universität Chemnitz, Germany

Christian Müller-Schloer Thomas Nolte Roman Obermeisser Alex Orailoglu Luigi Palopoli Carlos Eduardo Pereira

Pascal Sainrat Luca Santinelli Silvia Santini Toshinori Sato Martin Schulz Karsten Schwan Bernhard Sick Leonel Sousa

Rainer G. Spallek Olaf Spinczyk Benno Stabernack Walter Stechele Djamshid Tavangarian Jürgen Teich

Martin Törngren Pedro Trancoso Carsten Trinitis Theo Ungerer Hans Vandierendonck Stephane Vialle Lucian Vintan Thiemo Voigt Klaus Waldschmidt

Stephan Wong

Leibniz Universität Hannover, Germany Mälardalen University, Sweden Universität Siegen, Germany University of California, San Diego, USA University of Trento, Italy Universidade Federal do Rio Grande do Sul. Brazil IRIT - Université de Toulouse, France **Onera**, France Technische Universität Darmstadt, Germany Fukuoka University, Japan Lawrence Livermore National Laboratory, USA Georgia Institute of Technology, USA Universität Kassel, Germany INESC-ID, IST, Universidade de Lisboa, Portugal Technische Universität Dresden, Germany Technische Universität Dortmund, Germany Fraunhofer HHI, Germany Technische Universität München, Germany Universität Rostock, Germany Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany KTH Royal Institute of Technology, Sweden University of Cyprus, Cyprus Technische Universität München, Germanv Universität Augsburg, Germany Queen's University Belfast, UK SUPELEC, France Lucian Blaga University of Sibiu, Romania SICS and Uppsala University, Sweden Goethe University Frankfurt am Main, Germany Delft University of Technology, The Netherlands

### Additional Reviewers

Hussam Amrouch Kostiantyn Berezovskyi Anthony Brandon Chi Ching Chi Ahmed Elhossini Florian Haas Reinier van Kampenhout Mikael Åsberg Yvonne Bernard David de La Chevallerie Andreas Diavastos Lei Feng Uwe Jaenen Nima Moghaddami Khalilzad Erol Koser Björn Lisper Jörg Mische Julian Oppermann Johny Paul Sebastian Schlingmann Matthias Sommer Ericles Sousa Volker Wenzel Xinhai Zhang Tilman Küstner Pedro Miguens Nuno Neves Ahsan Qamar Rafael Rosales Nuno Sebastião Henning Spiegelberg Florian Stock Ioannis Zgeras

## Invited Talks

# Karl Hendrik Johansson, KTH Royal Institute of Technology, Sweden

# Control of Cyber-physical Systems: Fundamental Challenges and Applications to Transportation Networks

Cyber-physical systems are engineered systems whose operations are monitored, coordinated, controlled, and integrated by computing and communication cores interacting with humans and the physical environment. In this talk, we will discuss some recent developments on control architectures for cyber-physical systems. Motivated by application projects in goods transportation, we will consider the influence of local and partial plant state and model information on the synthesis problem. Some fundamental bounds relating global system performance with local information exchange and physical interactions will be introduced. Details will be given on an emerging goods transportation system based on fleets of platooning heavy-duty vehicles utilizing vehicle-to-vehicle and vehicleto-infrastructure communications. Some preliminary results from a large-scale evaluation currently being performed on the highway road network in Northern Europe will be discussed, showing the fuel saving and transport efficiency potentials of the system but also some of the challenges with humans in the loop and technology transfer. The presentation will be based on joint work with collaborators at KTH and at Scania.

# Ravi Nair, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, USA

#### Approximate Computing

There is an unprecedented amount of data being produced in the world today. Yet, cost and energy considerations are limiting a corresponding growth in the compute capability needed to process and analyze this data in a conventional manner. The adoption of computing devices by a wider segment of the world's population is leading to computing of the sort where the results are often ephemeral, and where there is a greater acceptance of approximate results. In addition though, approximate results are acceptable even in enterprise computing where, in comparison to traditional activities like accounting and inventory control, new activities such as decision support, search and datamining are consuming increasingly greater cycles and are frequently performed on input data that may be unreliable. It is becoming evident that there are significant computational and energy efficiencies to be gained by relaxing the expectation of preciseness in today's computational models and moving to a more approximate computing model. This talk will examine the implications of this notion of approximate computing on the exploitation of new technology and on the design of future systems.

# Thomas Ludwig, DKRZ Deutsches Klimarechenzentrum GmbH, Germany

#### High Performance Computers for Earth System Science

Earth system science has a long tradition in using high performance computers. The process of gaining new insight heavily depends on the available compute power. For decades we observe an exponential increase in this compute power. With the advent of Exascale architectures we are faced with new challenges for this research community. The talk will highlight options for new types of research as well as risks to be able to conduct specific investigations.

# Table of Contents

### Parallelization: Applications and Methods

| Resource-Aware Harris Corner Detection Based on Adaptive Pruning<br>Johny Paul, Walter Stechele, Manfred Kröhnert, Tamim Asfour,<br>Benjamin Oechslein, Christoph Erhardt, Jens Schedel,<br>Daniel Lohmann, and Wolfgang Schröder-Preikschat | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Victim Selection Policies for Intel TBB: Overheads and Energy<br>Footprint                                                                                                                                                                   | 13 |

| Non-preemptive Scheduling of Real-Time Software Transactional<br>Memory<br>António Barros and Luís Miguel Pinho                                                                                                                              | 25 |

### Self-Organization and Trust

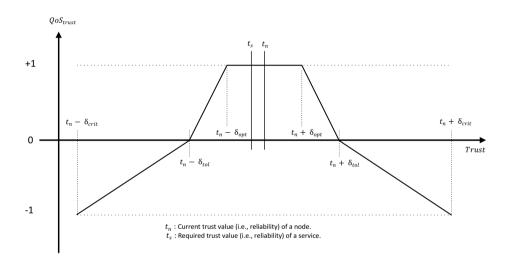

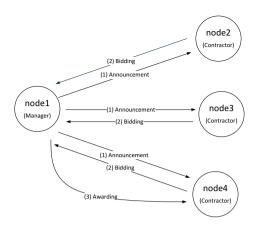

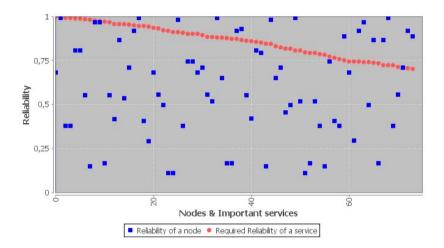

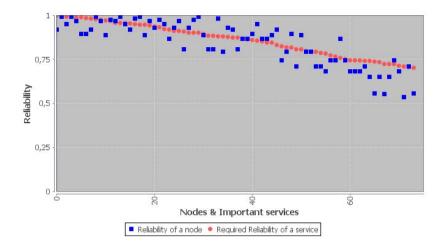

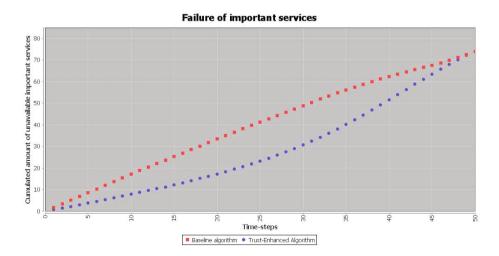

| Trust-Enhanced Self-configuration for Organic Computing Systems<br>Nizar Msadek, Rolf Kiefhaber, Bernhard Fechner, and Theo Ungerer                                               |    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

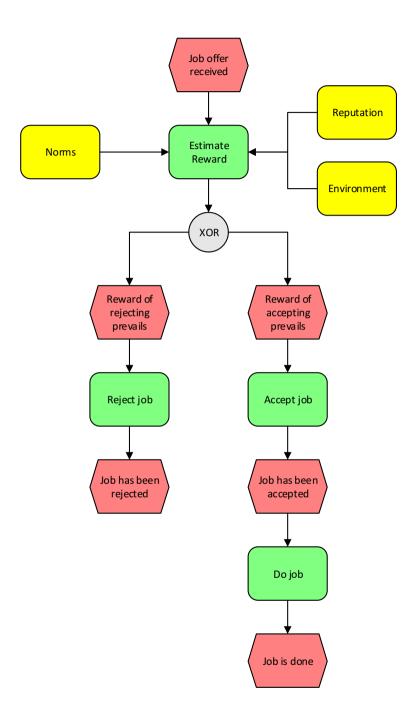

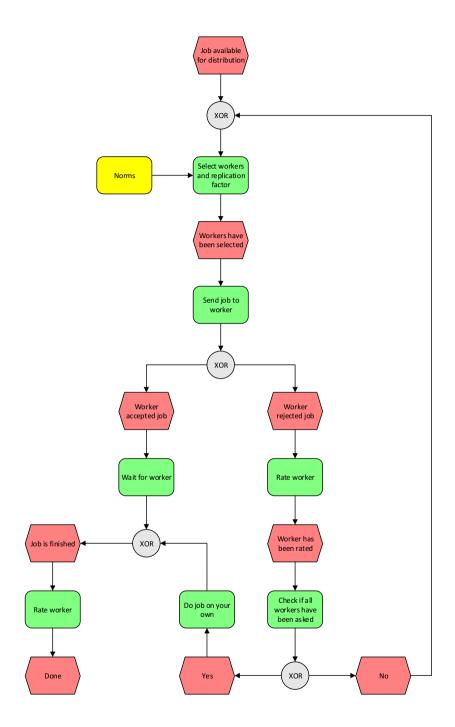

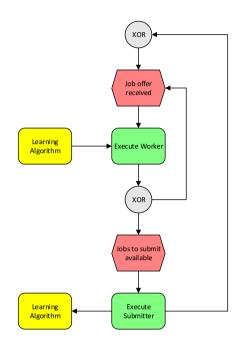

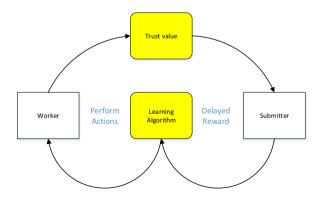

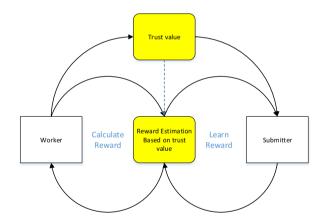

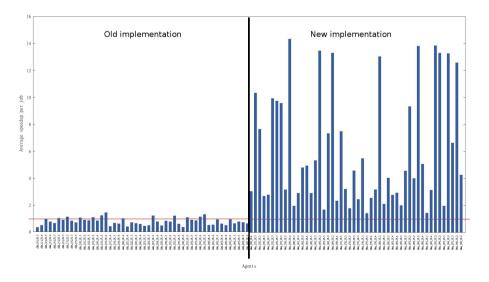

| Estimation of Reward and Decision Making for Trust-Adaptive Agents<br>in Normative Environments<br>Jan Kantert, Yvonne Bernard, Lukas Klejnowski, and<br>Christian Müller-Schloer | 49 |  |

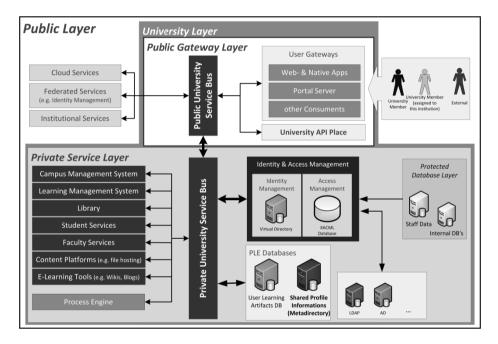

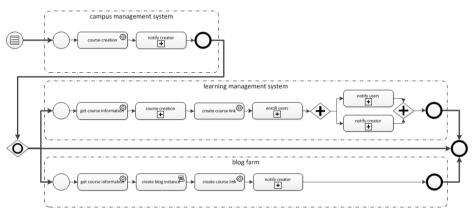

| An Adaptive Personal Learning Environment Architecture<br>Alexander Kiy, Ulrike Lucke, and Dietmar Zoerner                                                                        | 60 |  |

| Middleware for Dynamically Adaptive Systems<br>Sihem Loukil, Slim Kallel, and Mohamed Jmaiel                                                                                      | 72 |  |

| System Design I                                                                                                                                                                   |    |  |

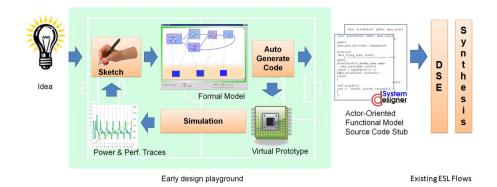

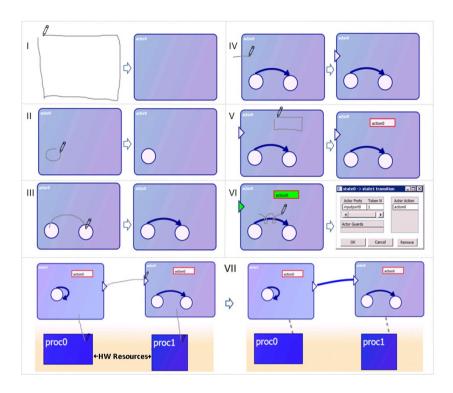

| Mahler: Sketch-Based Model-Driven Virtual Prototyping<br>Rafael Rosales, Michael Glaß, and Jürgen Teich                                                                           | 85 |  |

| Formal Architecture Specification for Time Analysis                                                                                                                               | 98 |  |

Hajer Herbegue, Mamoun Filali, and Hugues Cassé

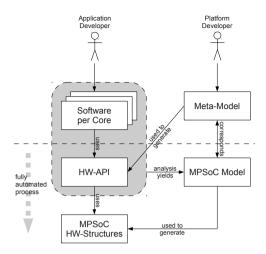

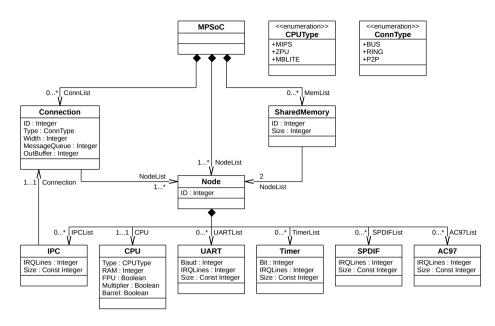

| Hardware APIs: A Software-Centric Approach for Automated<br>Derivation of MPSoC Hardware Structures Based on Static Code<br>Analysis |     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

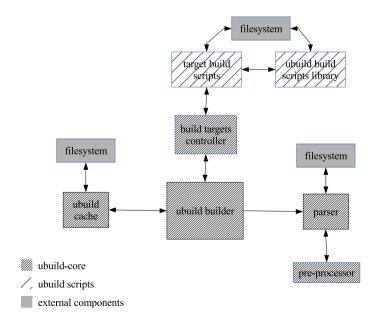

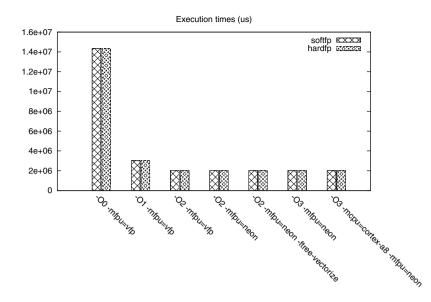

| uBuild: Automated Testing and Performance Evaluation of Embedded<br>Linux Systems                                                    | 123 |  |  |

### System Design II and Sensor Systems

| A Two-Tier Design Space Exploration Algorithm to Construct a GPU<br>Performance Predictor                                                                                                                                                     |     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

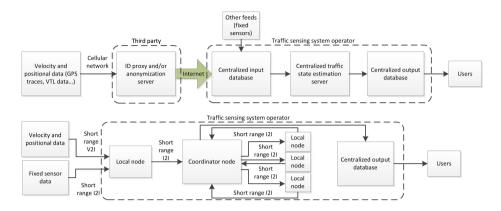

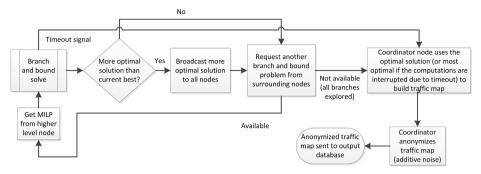

| A Sensor Network Architecture for Urban Traffic State Estimation<br>with Mixed Eulerian/Lagrangian Sensing Based on Distributed<br>Computing<br>Edward Canepa, Enas Odat, Ahmad Dehwah, Mustafa Mousa,<br>Jiming Jiang, and Christian Claudel | 147 |  |

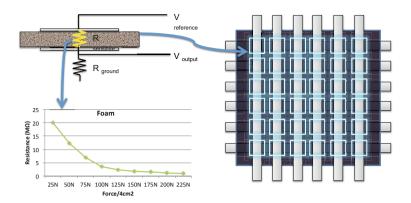

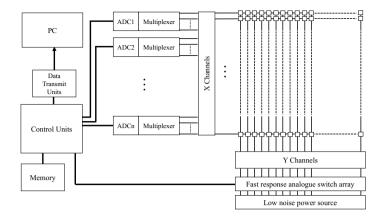

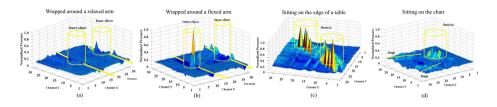

| From Smart Clothing to Smart Table Cloth: Design and Implementation<br>of a Large Scale, Textile Pressure Matrix Sensor<br>Bo Zhou, Jingyuan Cheng, Mathias Sundholm, and Paul Lukowicz                                                       | 159 |  |

### Virtualization: I/O, Memory, Cloud

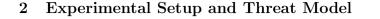

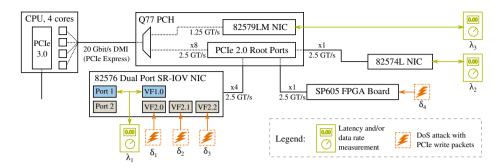

| Performance Isolation Exposure in Virtualized Platforms with PCI                                                                               |     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Passthrough I/O Sharing                                                                                                                        | 171 |

| Andre Richter, Christian Herber, Holm Rauchfuss,                                                                                               |     |

| Thomas Wild, and Andreas Herkersdorf                                                                                                           |     |

| 3D DRAM and PCMs in Processor Memory Hierarchy<br>Krishna Kavi, Stefano Pianelli, Giandomenico Pisano,<br>Giuseppe Regina, and Mike Ignatowski | 183 |

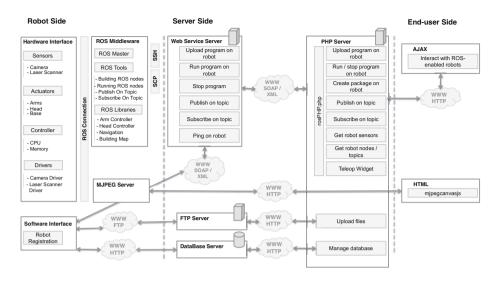

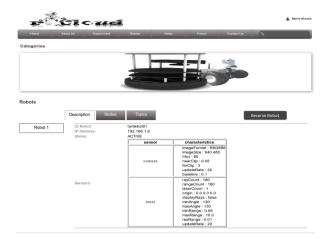

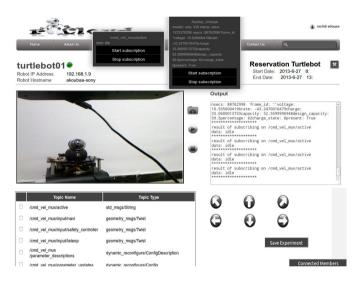

| A Service-Oriented Architecture for Virtualizing Robots<br>in Robot-as-a-Service Clouds<br>Anis Koubaa                                         | 196 |

# Dependability: Safety, Security, and Reliability Aspects

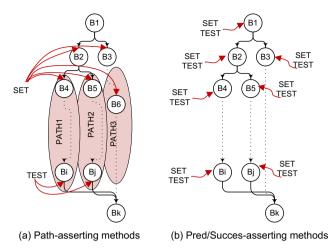

| Towards Code Safety with High Performance                | 209 |

|----------------------------------------------------------|-----|

| Ghazaleh Nazarian, Luigi Carro, and Georgi N. Gaydadjiev |     |

| Detecting Compromised Programs for Embedded System            |     |

|---------------------------------------------------------------|-----|

| Applications                                                  | 221 |

| Xiaojun Zhai, Kofi Appiah, Shoaib Ehsan, Wah M. Cheung,       |     |

| Gareth Howells, Huosheng Hu, Dongbing Gu, and                 |     |

| Klaus McDonald-Maier                                          |     |

| Independent Kernel/Process Checkpointing on Non-Volatile Main |     |

| Memory for Quick Kernel Rejuvenation                          | 233 |

| Shuichi Oikawa                                                |     |

|                                                               |     |

| Author Index                                                  | 245 |

# Resource-Aware Harris Corner Detection Based on Adaptive Pruning\*

Johny Paul<sup>1</sup>, Walter Stechele<sup>1</sup>, Manfred Kröhnert<sup>2</sup>, Tamim Asfour<sup>2</sup>, Benjamin Oechslein<sup>3</sup>, Christoph Erhardt<sup>3</sup>, Jens Schedel<sup>3</sup>, Daniel Lohmann<sup>3</sup>, and Wolfgang Schröder-Preikschat<sup>3</sup>

<sup>1</sup> Technical University of Munich, Germany <sup>2</sup> Karlsruhe Institute of Technology, Germany <sup>3</sup> Friedrich-Alexander University Erlangen-Nuremberg, Germany {johny.paul,walter.stechele}@tum.de, {manfred.kroehnert,asfour}@kit.edu, {oechslein,erhardt,schedel,lohmann,wosch}@cs.fau.de

**Abstract.** Corner-detection techniques are being widely used in computer vision – for example in object recognition to find suitable candidate points for feature registration and matching. Most computer-vision applications have to operate on real-time video sequences, hence maintaining a consistent throughput and high accuracy are important constrains that ensure high-quality object recognition. A high throughput can be achieved by exploiting the inherent parallelism within the algorithm on massively parallel architectures like many-core processors. However, accelerating such algorithms on many-core CPUs offers several challenges as the achieved speedup depends on the instantaneous load on the processing elements. In this work, we present a new resource-aware Harris corner-detection algorithm for many-core processors. The novel algorithm can adapt itself to the dynamically varying load on a many-core processor to process the frame within a predefined time interval. The results show a 19% improvement in throughput and an 18% improvement in accuracy.

**Keywords:** Harris corner detection, resource-aware programming, invasive computing, adaptive pruning.

#### 1 Introduction

*Corner detection* is used within computer-vision algorithms like motion detection, image registration, video tracking, feature descriptors for object recognition etc. to infer the contents of an image. Several corner detectors exist today in the literature and comparative evaluations have shown that the Harris [9] corner detectors achieve some of the best results. Recent evaluations in real-time applications such as video tracking [7], visual SLAM [8] and robotic navigation [19] have demonstrated that the preferred way to detect features in a scene is the use of a Harris detector in combination with more complex feature descriptors. Harris detectors are also used in the humanoid robot

<sup>\*</sup> This work was supported by the German Research Foundation (DFG) as part of the Transregional Collaborative Research Centre "Invasive Computing" (SFB/TR 89).

E. Maehle et al. (Eds.): ARCS 2014, LNCS 8350, pp. 1-12, 2014.

<sup>©</sup> Springer International Publishing Switzerland 2014

ARMAR-III [2] for recognizing and tracking textured objects [3]. A humanoid robot like ARMAR has to handle various tasks like vision, motion planning, speech recognition, etc. with the workload spread across multiple industrial PCs. The data from various sensors flows into the processing system, each dedicated for a different task like computer vision, motion control, speech processing, etc. Similarly, the humanoid robot Asimo uses two PCs, a control and planning processor plus an additional digital signal processor (DSP) for sound processing [18]. Two processor boards were also used in the humanoid robots HRP-2 [11] and HRP-4C [12]. The Hand Arm System from DLR [10] has three layers of computing hierarchy consisting of COTS PCs for control applications, an auxiliary Linux workstation for user interfaces and a composition layer constituted by FPGAs for hardware-accelerated tasks.

The use of multiple PCs results in high power consumption, low interconnect bandwidth and occupies a large amount of space on the robot. The use of many-core processors can mitigate some of the above mentioned problems on account of their immense computational power assembled in a compact design. However, the available resources on a many-core chip (processing elements (PEs), memories, interconnects, etc.) have to be shared among various applications running concurrently, which leads to unpredictable execution time or frame drops for vision applications. Our work focuses on analyzing the effect of sharing resources on a conventional Harris detector and propose a new resource-aware Harris detector to resolve the issues. Evaluations shows that the newly proposed Harris detector is capable of adapting to varying load conditions on the many-core processor and delivers better results in terms of throughput, accuracy and latency. This work also describes how to distribute the workload on the massively parallel PEs for best results, avoiding frame drops, even under varying load conditions.

This paper is organized as follows. Section 2 describes the state-of-the-art algorithms used for corner detection and different schemes using for accelerating the algorithm. Section 3 provides a brief overview of the conventional Harris detector and describes some of the challenges with implementing a conventional Harris detector on many-core processors. Section 4 starts with a brief description of various pruning techniques to accelerate corner detection. This is followed by the description of the resource-aware corner detector using an enhanced pruning technique. Section 5 provides an overview of the many-core system used for evaluation and Section 6 describes the implementation and results, followed by Section 7, which concludes the paper.

#### 2 State of the Art

Several techniques exist today to detect corners in an image. These include Harris corner detection [9], SUSAN [20], FAST [17], etc. Independent of the technique used, corner detection is a compute-intensive task and two main techniques have been used to speed it up. The first approach focuses on algorithmic techniques to reduce the computational complexity, while the second employs hardware accelerators or graphics processing units (GPUs) to accelerate the conventional algorithm. Independent of the technique used, they all pose a challenge to the programmer; how to control the worst-case execution time and avoid frame drops when the resources on the processor are shared across multiple applications. High throughput can be guaranteed using hardware accelerators

based on field-programmable gate arrays (FPGAs). However, the flexibility offered by FPGAs is quite low and requires very high effort in terms of design, implementation and verification. On the other hand, GPUs are very powerful and provide significant acceleration over small multi-core processors due to their massively parallel architecture. However, they consume very high power, are less flexible, difficult to debug and require data transfers between processor and the hardware accelerator, which increases the overall latency.

The use of many-core processors can overcome many of the above mentioned hurdles as they offer higher computing power necessary to accelerate the algorithms, while at the same time retaining the simplicity in programming and debugging. Today it is possible to put onto a single chip a large number of general-purpose cores, certainly tens of highly complex cores as on Intel's Single-Chip Cloud Computer [15] or Tilera's 64-core processor [4]. A major challenge associated with todays many-core systems is the question of how to program such systems to make best use of their computing power. In order to address these issues, [14] propose a new resource-aware operating system (ROS) for many-core hardware, with direct support for parallel applications and a scalable kernel. ROS offers a resource-management scheme based on resource provisioning which enables system-wide, efficient accounting and utilization of resources. Resources such as cores and memory are explicitly granted to the applications and revoked. The kernel exposes information about a process's current resource allocation and the system's utilization, and allows the application programs to make requests based on this information.

The demand for more stringent (OS-supported) resource awareness was also proposed in [21], put forward by a new programming methodology called *Invasive Computing*. The main idea and novelty of Invasive Computing is that it extends resourceaware programming support to various layers in the many-core system like resourceaware OS, communication interfaces like Network-on-Chip (NoC), and PEs. Programs running on this system get the ability to explore and dynamically spread their computations to neighboring processors and execute portions of code with a high degree of parallelism in parallel based on the availability of resources. Once the program terminates or if the degree of parallelism is expected to be lower again, the program may enter a *retreat* phase. At this point, the resources can be deallocated and execution resumed, for example, sequentially on a single processor. In this work, a resource-aware Harris corner-detection algorithm is evaluated using the Invasive Computing methodology. However, the concepts demonstrated in this work are platform-independent and can be demonstrated on any resource-aware platform including ROS.

#### **3** Harris Corner Detection

This section provides a brief overview of the conventional Harris corner-detection algorithm. The calculation is based on the local auto-correlation function that is approximated by a matrix M over a small window w for each pixel p(x, y):

$$M = \begin{bmatrix} \sum_{w} W(x) I_x^2 & \sum_{w} W(x) I_x I_y \\ \sum_{w} W(x) I_x I_y & \sum_{w} W(x) I_y^2 \end{bmatrix} = \begin{bmatrix} a & b \\ c & d \end{bmatrix}$$

(1)

where  $I_x$  and  $I_y$  are horizontal and vertical intensity gradients, respectively, and W(x) is an averaging filter that can be a box or a Gaussian filter. The eigenvalues  $\lambda_1$  and  $\lambda_2$  (where  $\lambda_1 \ge \lambda_2$ ) indicate the type of intensity change in the window w around p(x, y). If both  $\lambda_1$  and  $\lambda_2$  are small, p(x, y) is a point in a flat region. If  $\lambda_1$  is large and  $\lambda_2$  is small, p(x, y) is an edge point and if both  $\lambda_1$  and  $\lambda_2$  are large, p(x, y) represents a corner point. Harris combines the eigenvalues into a single corner measure R as shown in (2) (k is an empirical constant with value 0.04 to 0.06). Once the corner measure is computed for every pixel, a threshold is applied on the corner measures to discard the obvious non-corners.

$$R = \lambda_1 \lambda_2 - k \cdot (\lambda_1 + \lambda_2)^2 = (ac - b^2) - k \cdot (a + c)^2$$

(2)

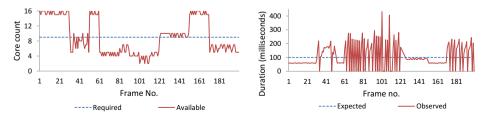

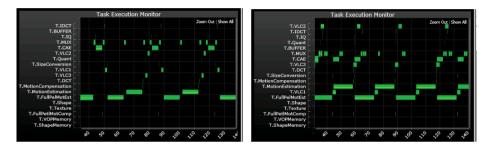

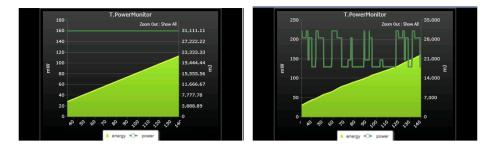

Corner detection is often employed as the first step in computer-vision applications with real-time video input. Hence, the application has to maintain a steady throughput and good response time to ensure quality results. However, the presence of other high-priority tasks may alter the behavior of the corner-detection algorithm. To evaluate such a dynamically changing situation, we analyzed the behavior of the conventional Harris detector on a many-core processor with 32 PEs. Fig. 1 shows resourceallocation schemes (left) along with the execution-time profiles (right). A video input with  $640 \times 480$  pixels at 10 frames per second was used, with the test running for 20 seconds. To evaluate the impact of other applications running concurrently on the many-core system, applications like audio processing, motor control, etc. were used. These applications create dynamically changing load on the processor based on what the robot is doing at that point in time. For instance, the speech-recognition application is activated when the user speaks to the robot. The conventional OS scheduler schedules the threads of the applications based on the overall system load. Sharing of available resources resulted in the execution-time profile shown in Fig. 1. It can be seen that the execution time varies from 0 to 430 milliseconds, based on the load condition. A lack of sufficient resources leads to very high processing intervals or frame drops (a processing interval of zero represents a frame drop). The number of frames dropped during this evaluation is as high as 20% and the worst-case latency increased by 4.3x (100 milliseconds to 430 milliseconds). Frame drops reduce the quality of the results and the robot may lose track of the object if too many consecutive frames are dropped. In order to overcome these challenges, we present a modified Harris detector for many-core processors capable of allocating resources based on the current workload. The algorithm can also adapt the workload based on the currently available resources. The following

Fig. 1. Variation in processing interval based on available resources

sections demonstrate how the resources are claimed and how the processing interval can be constrained to guarantee consistent throughput and processing intervals.

#### 4 Pruning Techniques

A pruning technique to reduce the computational complexity of the conventional Harris detector is described in [22]. This technique relies on the fact that in most situations, the obvious non-corners constitute a large majority of the image. Hence the Harris detectors incur a lot of redundant computations as they evaluate the entire image for a high corner response. From (2), R is most influenced by the term  $(ac - b^2)$  as the two (a + c) terms cancel out. For a good corner, R needs to be a large value. Hence maximizing  $(ac-b^2)$  can select good corners without explicit eigenvalue computation. However, this technique cannot demonstrate a noticeable speedup on platforms with FPU as the pixels are pruned away in the final step, just before eigenvalue computation. The limitations in [22] can be resolved using the multi-stage pruning technique described in [1]. The main difference between these techniques is that the second one can prune away pixels at a very early stage. A corner response (CR) is defined as:

$$CR = \min\left(\left|I_x\right|, \left|I_y\right|\right),\tag{3}$$

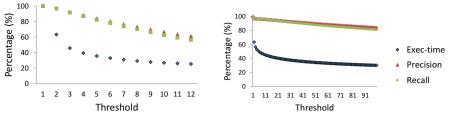

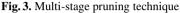

where  $I_x$  and  $I_y$  are the horizontal and vertical pixel-intensity derivatives. If CR is greater than a predefined gradient threshold, the pixel is a corner candidate and should be retained for processing in the subsequent steps. This technique ensures that the noncorner pixels are removed prior to more intensive processing. All candidate corners from the previous steps are further assessed by computing the eigenvalues as in the conventional Harris detector (2). Finally a non-maxima suppression is applied to suppress the corners that are close to each other. Some of the challenges posed by the conventional Harris detector on a many-core system can be resolved using the pruning techniques described above. In situations where the system is under-utilized, the threshold can be reduced, thereby processing more pixels and achieving a higher accuracy, whereas increasing the threshold can prune away more pixels when the processing system is heavily loaded by other high-priority tasks. Fig. 3 shows the relation between the threshold and the processing interval. The results were captured by applying the pruning technique to six different video sequences whose snapshots are shown in Fig. 2 (each video sequence consists of 200 frames). In order to evaluate the impact of pruning on the accuracy of detected corners, we use the metrics named precision and recall as proposed in [13]. The value of recall measures the number of correct matches out of

Fig. 2. Snapshot of the video-sequences used for evaluation

Fig. 4. Resource-aware pruning

the total number of possible matches, and the value of precision measures the number of correct matches out of all matches returned by the algorithm. From Fig. 3 it can be seen that the application performs well for a threshold below four. However, increasing the threshold further results in a drastic decrease in precision and recall rates (as low as 60% for a threshold of 12). Values beyond this point are not plotted in the graph as the corners with an accuracy below 60% are not suitable for practical use. The second drawback of this algorithm is that it offers only few candidate points for adaptations within an acceptable accuracy range.

In order to overcome the challenges with the multi-stage pruning technique, we present an enhanced pruning technique with better flexibility and higher accuracy compared to the conventional pruning technique presented in Section 4. Our algorithm uses a new threshold model as described in (4), where product of vertical and horizontal difference in pixel intensities is used and the candidates with low CR values are pruned away.

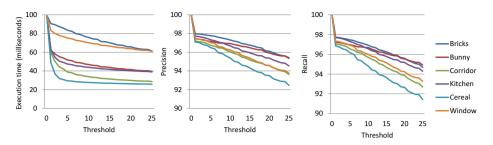

$$CR = (|I_x \cdot I_y|) \tag{4}$$

This new model results in significantly more selection points as shown in Fig. 4, offering a higher flexibility to the resource-aware algorithm whenever adaptations are necessary. In addition to this, there is a significant improvement in both precision and recall rates. For example, precision is improved from 84.0% to 90.8% and recall is improved from 82.3% to 89.2% for the same speedup value of 35%. The new model shows a consistent improvement in precision and recall for the entire range and higher values are obtained as the threshold is increased. A more detailed analysis on the video sequences shows that the effects of pruning vary based on the scene. For example, the speedup achieved (using the same threshold) is low for cluttered scenes like Bricks while the majority of the pixels can be pruned away for scenes with plain backgrounds. Fig. 5 shows the relation between speedup and accuracy for all six video sequences. This means that the amount of computing resources required to perform the corner detection will vary from one scene to another based on the nature of the foreground, background, etc. and therefore the resources have to be allocated on a frame-to-frame basis, based on the scene captured. A resource-aware many-core platform meeting the above requirements, is presented in Section 5 with emphasis on how to allocate and release resources in real-time based on application requirements.

#### **5** Evaluation Platform

As described in Section 2, our work focuses on exploring the benefits of resource-aware Harris corner detection. Therefore, we implemented our algorithms on top of OctoPOS

Fig. 5. Effects of pruning on processing time, precision and accuracy

[16], a resource-aware operating system for Invasive Computing. OctoPOS shares the same view with ROS [14] as far as application-directed resource management of many-core processors is concerned. Also, both approaches resort to an event-based kernel architecture and largely benefit from asynchronous and non-blocking system calls. The main difference, however, is in the execution model of OctoPOS that was specifically designed to support invasive-parallel applications.

#### 5.1 System Programming Interface

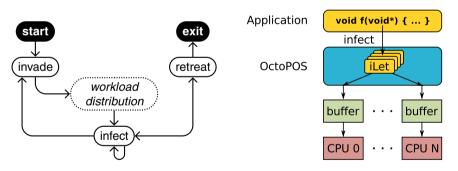

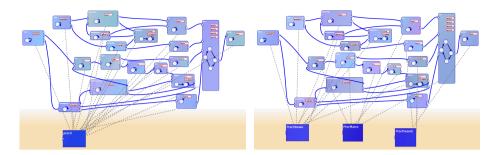

At the OctoPOS interface, resource-aware programming maps to three fundamental system calls: invade(), infect() and retreat(). The typical usage of these calls in the course of an application programm are depicted in Fig. 6. First, the application's

Fig. 6. Structure of an invasive program

Fig. 7. Execution model of applications in Octo-POS

resource demand has to be expressed to the system. We call this the *invade* phase. It yields a set of resources in the form of a *claim*, the central data structure in the system for representing the resources associated with an application (processors, memory, etc.). Depending on the structure of the *claim*, the application has to distribute its workload accordingly. For example, it can tune its algorithms towards the number of processors present in the claim. Actual computation is then performed using the *infect* call. After execution finishes, another computation phase can be started on the same set of

resources, resources can be released using *retreat*, or additional resources can be acquired using *invade*. The basic concept of Invasive Computing states that an application dynamically expands and shrinks its set of resources at runtime according to its own demand and that it can react to undersupply situations where not enough resources are available. Hence, depending on the current system state, the resulting claim may or may not fulfill the demands specified before. On the other side, once an application gets a claim, it gains full control over the associated resources. This guarantee on the acquired resources enables the application to balance its workload according to the dynamic runtime state of the system. Assumptions made during workload distribution before the *infect* phase hold until the application itself changes its resource allocation following the *infect* phase.

The main building blocks of applications in OctoPOS are so-called *i*-lets: Fragments of a program potentially executed in parallel with mostly run-to-completion semantics. These are represented by function and data pointers and thus are very lightweight entities. An *i*-let is like a Cilk procedure [5], but allows for the blocking of its executing thread by creating a "featherweight" continuation when actually releasing a PE. An application can create an arbitrary number of *i*-lets to be executed – potentially in parallel – using the *infect* system call. As depicted in Fig. 7, OctoPOS forwards *i*-lets to processor-local buffer queues for execution. Overall, this leads to an efficient implementation of *i*-let creation and dispatching. Moreover, with a tiled hardware architecture as described in Section 5.2, the buffering scheme is a possible candidate for hardware acceleration: To execute *i*-lets on distant tiles without obstructing the processors in the tile, the buffers can be maintained in hardware and accessed directly through the NoC. This leads to a very scalable system architecture especially suitable for many-core systems.

#### 5.2 Hardware Architecture

Our target many-core processor consists of 9 tiles interconnected by a NoC. Each compute tiles consists of 4 cores interconnected by a local bus and some fast, on-chip tilelocal memory, with a total of 32 cores (LEON3, a SPARC V8 design by Gaisler [6]) spread across 8 tiles. The 9th tile is a memory and I/O tile encompassing a DDR-III memory controller and Ethernet, UART, etc. for data exchange and debugging. Each core has a dedicated L1 cache while all the cores within a tile share a common L2 cache for accesses that go beyond the tile boundary to the external DDR-III memory. L1 caches are write-through and L2 is a write-back cache. Cache coherency is only maintained within the tile boundary to eliminate a possible scalability bottleneck when scaling to higher core counts. Therefore, data consistency has to be handled by the programmer through proper programming techniques that are built on top of hardware features to provide consistent data access and exchange between the different cachecoherency domains. This scheme is somewhat similar to the Intel SCC.

#### 6 Implementation and Results

The first step in the resource-aware Harris detector is to allocate sufficient resources to perform corner detection within the interval specified by the user. The number of PEs

required is calculated based on the input-image resolution, the processing interval, the nature of the scene, etc. The analysis starts with the generation of a differential image, where each pixel is computed using (4). In order to speed up the pruning logic within the algorithm, an integral histogram is computed from the differential image as described in Algorithms 1 and 2, where n is the total number of pixels to be processed,  $I_{diff}$  is the differential image, limit is the maximum possible value generated by (4) and H is the integral histogram computed from differential image. Once the integral histogram is computed, the values in the bin represent the number of pixels to be processed by the algorithm when the threshold is set to histogram-bin-index. The number of PEs ( $N_{pe}$ ) is calculated using (5).

$$N_{pe} \ge \frac{n \cdot T_{prn} + P_{pix}(th) \cdot T_{hcd}}{T_{exe} \cdot \eta(N_{pe})}$$

(5)

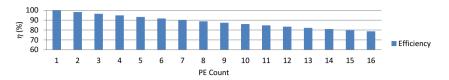

where n is the total number of pixels,  $T_{prn}$  is the processing time per pixel until the generation of integral histogram,  $P_{pix}$  is the number of pixels to be processed as computed by the pruning algorithm (a function of the threshold value th),  $T_{hcd}$  is the time to compute R for pixels with CR above threshold,  $T_{exe}$  is the processing interval and  $\eta(N_{pe})$  represents the algorithm's efficiency as a function of degree-of-parallelism or available resources  $(N_{pe})$ . Including an efficiency factor is important as every additional *i*-let created by the algorithm also creates additional load on the external memory and shared communication interfaces, limiting the overall scalability. For the best results, the threshold value th can be set to zero so that the algorithm will attempt to process all pixels in the image. It should be noted that  $T_{prn}$  and  $T_{hcd}$  may vary based on the actual implementation and processor architecture. Hence these values are estimated by profiling the application on the target platform. Fig. 8 shows the change in efficiency against degree of parallelism, on the target HW. It can be seen clearly that when the number of *i*-lets is doubled from 1 to 2, the execution time does not halve, but is reduced by a factor of 1.96, which means an efficiency of 98%. In the next step, an invade request (for  $N_{pe}$ ) is raised and the OS makes a final decision on the number of PEs considering the current system load. The PE count may vary from zero (if the system is too heavily loaded and no further resources can be allocated at that point in time) to the total number of PEs requested (provided that a sufficient number of idle PEs exist in the system and the current power mode offers sufficient power budget to enable the

| Algorithm 1. Differential image                                                                                                                                                                                      | Algorithm 2. Integral histogram                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1: $i \leftarrow 0$<br>2: $h \leftarrow 0$<br>3: while $i < n$ do<br>4: $I_{diff}(i) \leftarrow  dx(i) \cdot dy(i) $<br>5: $h(I_{diff}(i)) \leftarrow h(I_{diff}(i)) + 1$<br>6: $i \leftarrow i + 1$<br>7: end while | 1: $i \leftarrow 0$ 2: $H \leftarrow 0$ 3: while $i < limit$ do         4: $k \leftarrow i$ 5: while $k < limit$ do         6: $H(i) \leftarrow H(i) + h(k)$ 7: $k \leftarrow k + 1$ 8: end while         9: $i \leftarrow i + 1$ 10: end while |

Fig. 8. Efficiency map for Harris detector on target hardware

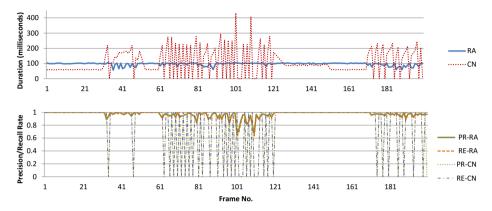

**Fig. 9.** Comparison between conventional and resource-aware model (RA = resource-aware-model, CN = conventional-model, PR = precision, RE = recall)

selected PEs). This means that under numerous circumstances the application has to adapt to the limited resources offered by the runtime system by increasing the threshold value th until the condition in (6) is satisfied.

$$P_{pix}(th) \le \frac{N_{pe} \cdot T_{exe} \cdot \eta(N_{pe}) - n \cdot T_{prn}}{T_{hcd}}$$

(6)

The new workload is processed by the allocated PEs and the resources can be released at the end of the processing interval or a new invade request can be raised if more PEs are required for the next frame due to a change in the scene. The behavior of the new resource-aware Harris detector is depicted in Fig. 9. The resource-allocation scheme remains same as described in Fig. 1. The execution-time profile in Fig. 9 shows that the resource-aware Harris detector can constrain the execution time per frame to the specified value of 100 milliseconds. The use of the conventional algorithm resulted in very high latencies under circumstances where sufficient resources are not available, and dropped frames occasionally. The values of precision and recall drops slightly in the region where the application has to adapt by pruning pixels. However, this helps to avoid overshoot in execution time and eliminate frame drops, so that results are consistently available within the predefined intervals. An overall comparison between the two scenarios is shown in Table 1. The use of the conventional algorithm leads to a very high worst-case execution time(WCET) and frame drops. The precision and recall values are low for the conventional algorithm as a frame drop leads to zero precision and recall for that particular frame. In brief, the resource-aware Harris detector can operate

|                | Throughput | WCET  | Precision | Recall |

|----------------|------------|-------|-----------|--------|

| Conventional   | 81%        | 4.31x | 0.82      | 0.81   |

| Resource-aware | 100%       | 1.04x | 0.98      | 0.98   |

Table 1. Comparison between conventional and resource-aware Harris detectors

very well under dynamically changing conditions by adapting the workload, avoiding frame drops and regulating the WCET, leading to high precision and recall rates.

#### 7 Conclusion

This paper presented a resource-aware Harris corner detector and demonstrated how to estimate the resources required for corner detection based on the scene, the resolution of the input image and the user-specified time interval. The application is aware of available resources on the many-core processor and can adapt the workload if sufficient resources are not available. The enhanced corner detector can generate results within the specified search interval and avoid frame drops. Our experiments show that incorporating resource awareness into the conventional Harris detector can significantly improve the quality of the algorithm. A detailed evaluation was conducted on an FPGA-based hardware prototype to ensure the validity of the results. The results show up to 19% improvement in throughput and 18% improvement in accuracy as described in Section6. Though the evaluations were conducted using the OS and hardware explained under Section 5, the benefits are expected to be visible on any resource-aware platform including ROS [14]. The resource allocation and release happens once per frame and the additional overhead in execution time is negligible when compared to the time taken by the detector to process millions of pixels in every frame.

#### References

- 1. Alkaabi, S., Deravi, F.: Candidate pruning for fast corner detection. Electronics Letters 40(1), 18–19 (2004)

- Asfour, T., Azad, P., et al.: ARMAR-III: An integrated humanoid platform for sensory-motor control. In: 6th IEEE-RAS International Conference on Humanoid Robots. IEEE (2006)

- Azad, P., Asfour, T., Dillmann, R.: Combining harris interest points and the sift descriptor for fast scale-invariant object recognition. In: Intelligent Robots and Systems, IROS 2009. IEEE (2009)

- Bell, S., Edwards, B., et al.: Tile64-processor: A 64-core soc with mesh interconnect. In: Solid-State Circuits Conference, 2008. Digest of Technical Papers, pp. 88–598. IEEE (2008)

- Blumofe, R.D., Joerg, C.F., et al.: Cilk: An efficient multithreaded runtime system. In: Proceedings of the Fifth ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP 1995 (1995)

- Gaisler, J., Catovic, E.: Multi-core processor based on leon3-ft ip core (leon3-ft-mp). In: DASIA 2006-Data Systems in Aerospace, vol. 630, p. 76 (2006)

- 7. Gauglitz, S., Höllerer, T., et al.: Evaluation of interest point detectors and feature descriptors for visual tracking. International Journal of Computer Vision 94(3), 335–360 (2011)

- Gil, A., Mozos, O.M., Ballesta, M., Reinoso, O.: A comparative evaluation of interest point detectors and local descriptors for visual slam. Machine Vision and Applications 21(6), 905– 920 (2010)

- Harris, C., Stephens, M.: A combined corner and edge detector. In: Alvey Vision Conference, Manchester, UK, vol. 15, p. 50 (1988)

- Jorg, S., Nickl, M., Nothhelfer, A., et al.: The computing and communication architecture of the dlr hand arm system. In: 2011 IEEE/RSJ International Conference on Intelligent Robots and Systems (IROS), pp. 1055–1062. IEEE (2011)

- Kaneko, K., Kanehiro, F., Kajita, S., Hirukawa, H., et al.: Humanoid robot HRP-2. In: Proceedings of the 2004 IEEE International Conference on Robotics and Automation, ICRA 2004, vol. 2, pp. 1083–1090 (May 2004)

- Kaneko, K., Kanehiro, F., Morisawa, M., Miura, K., Nakaoka, S., Kajita, S.: Cybernetic human HRP-4C. In: 9th IEEE-RAS International Conference on Humanoid Robots, Humanoids 2009, pp. 7–14 (December 2009)

- Klippenstein, J., Zhang, H.: Quantitative evaluation of feature extractors for visual slam. In: Fourth Canadian Conference on Computer and Robot Vision, CRV 2007, pp. 157–164. IEEE (2007)

- 14. Klues, K., Rhoden, B., Zhu, Y., Waterman, A., Brewer, E.: Processes and resource management in a scalable many-core os. In: HotPar 2010, Berkeley, CA (2010)

- Mattson, T., Riepen, M., et al.: The 48-core scc processor: the programmer's view. In: Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1–11. IEEE Computer Society (2010)

- Oechslein, B., Schedel, J., Henkel, J., Lohmann, D., Schröder-Preikschat, W., et al.: Octopos: A parallel operating system for invasive computing. In: Proceedings of the International Workshop on Systems for Future Multi-Core Architectures (SFMA). EuroSys (2011)

- Rosten, E., Drummond, T.: Machine learning for high-speed corner detection. In: Leonardis, A., Bischof, H., Pinz, A. (eds.) ECCV 2006, Part I. LNCS, vol. 3951, pp. 430–443. Springer, Heidelberg (2006)

- Sakagami, Y., Watanabe, R., Aoyama, C., Matsunaga, S., et al.: The intelligent ASIMO: system overview and integration. In: IEEE/RSJ International Conference on Intelligent Robots and Systems, vol. 3, pp. 2478–2483 (2002)

- Schmidt, A., Kraft, M., Kasiński, A.: An evaluation of image feature detectors and descriptors for robot navigation. In: Bolc, L., Tadeusiewicz, R., Chmielewski, L.J., Wojciechowski, K. (eds.) ICCVG 2010, Part II. LNCS, vol. 6375, pp. 251–259. Springer, Heidelberg (2010)

- Smith, S.M., Brady, J.M.: Susan—a new approach to low level image processing. International Journal of Computer Vision 23(1), 45–78 (1997)

- Teich, J., Henkel, J., Herkersdorf, A., Schröder-Preikschat, W., et al.: Invasive Computing: An Overview. In: Hübner, M., Becker, J. (eds.) Multiprocessor System-on-Chip – Hardware Design and ToolIntegration, pp. 241–268. Springer, Heidelberg (2011)

- Wu, M., Ramakrishnan, N., Lam, S.-K., Srikanthan, T.: Low-complexity pruning for accelerating corner detection. In: 2012 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1684–1687. IEEE (2012)

# Victim Selection Policies for Intel TBB: Overheads and Energy Footprint

Alexandru C. Iordan, Magnus Jahre, and Lasse Natvig

Norwegian University of Science and Technology, Trondheim, Norway {iordan, jahre, lasse}@idi.ntnu.no

Abstract. With the wide adoption of Chip Multiprocessors (CMPs), software developers need to switch to parallel programming to reach the performance potential of CMPs and maximize their energy efficiency. Management overheads due to parallelization can cause sub-linear speedups and increase the energy consumption of parallel programs. In this paper, we investigate the parallelization overheads of Intel TBB with a particular focus on its victim selection policy. We implement an "all knowing" oracle victim selection scheme as well as a pseudo-random scheme and compare them against TBB's default random selection policy. We also break down TBB's parallelization overheads and report how basic operations like task spawning, task stealing and task de-queuing impact the energy footprint. Our experiments show that failed task stealing is by far the highest energy consumer. In fact, the oracle victim selection policy can reduce the application energy footprint by 13.6% compared to TBB's default policy.

Keywords: Intel TBB, victim selection, energy efficiency.

#### 1 Introduction

Energy consumption has become the main challenge for almost all systems in the information world, from HPC to embedded devices. Architects and developers are trying to find solutions for problems ranging from reducing the high cost of operation of data centers to maximizing the battery life of mobile and embedded systems. For over 20 years, techniques like transistor-speed scaling, pipelining, out-of-order execution and speculation have increased CPU performance at a rate of 50% per year [1]. However, diminishing returns from transistor scaling and power budget limitations has almost removed the single-core performance improvement trend.

The introduction of Chip Multiprocessors (CMPs) enabled the mitigation of development constraints like the *power wall* and the *ILP wall*. CMPs allow chip designers to utilize the increasing transistor count available with each new generation without increasing the power budget [2]. However, to fully take advantage of this architecture, parallel software is required since the performance potential of CMPs lies in exploiting thread level parallelism. This places a new burden on the software developers because there is no widely adopted programming

E. Maehle et al. (Eds.): ARCS 2014, LNCS 8350, pp. 13-24, 2014.

<sup>©</sup> Springer International Publishing Switzerland 2014

model that facilitates easy parallelization. In this work, we focus on *Task Based Programming* (TBP) which is a parallel programming model that has received significant attention recently [3–6].

To reduce the impact of parallelization overheads, a necessary first step is to identify the root cause of such overheads. To this end, we investigate the extra instructions added by parallelization management and the energy consumption of these instructions which we refer to as the *energy footprint*. More precisely, the energy footprint is the energy spent for executing the given application or section of code in the context of the test system.

In our experiments, we utilize Intel's Thread Building Blocks (TBB) [6] library for parallelization. TBB is a C++ template library designed to help programmers create portable, parallel applications using task parallelism. It was designed to avoid the low level programming inherent in the direct use of threading packages such as pthreads [6].

To allow for extensive and noninvasive measurements, we use a performance simulator and a power estimation tool in our study. We implement two victim selection policies in addition to TBB's random policy and report the performance and energy overheads of 5 PARSEC benchmarks [7]. We also break down TBB's overheads and look into basic TBP operations like task spawning, task stealing and task de-queuing. In our results, failed steals are the highest contributor to the overheads' energy footprint. With more accurate victim selection, the energy footprint of the application can be reduced by up to 13.6%.

#### 2 Intel TBB

The concept of parallel programming is almost as old as the computer itself. Over the years, many parallel languages have been developed and a multitude of research was done in an effort to improve raw performance and maximize hardware utilization [8]. With the majority of those approaches, one factor was often overlooked: the composability of the resulting solution. Composability of an applications refers to its ability to run efficiently side by side with other applications and being able to cope with the fact that it does not have exclusive access to the hardware resources [9]. In today's *multi-core era*, if parallel applications are not developed to dynamically scale and take advantage of all the resources that are available to them, the overall efficiency of the system suffers. In this work we focus on Intel's TBB version 4.1.1., which was design to ensure a high degree of composability.

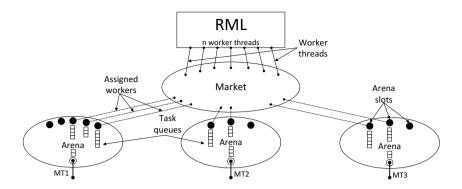

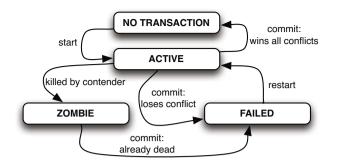

TBB allows parallelism to be annotated both explicitly, by calling the *spawn()* method, and implicitly, through some templates like *parallel\_for* or *parallel\_reduce*. Tasks get created by the *spawn()* method and then added to the calling thread's task queue inside the arena (see Fig. 1). From the arena the task is available for execution by its owner thread or by other workers through stealing. A task can instantiate and spawn other tasks resulting a hierarchical task tree.

When an application thread instantiates the *tbb::task\_scheduler\_init* object, that thread becomes a TBB master thread (MT). All threads created by TBB to

Fig. 1. Components of TBB's task scheduler

help complete the work of the MT are called *worker threads*. The *Resource Management Layer* (RML) is the component that hosts the pool of worker threads and gets instantiated first (see Fig. 1). No worker threads are created at this point, this being postponed until the first task is spawned.

Next a *Market* component is instantiated. This component was added in version 3.0 of TBB to ensure the composability of the framework. It guarantees that the work (the tasks) of one MT are isolated from other MTs that may be executing on the same machine. The role of the market is to assign workers to the arenas of each MT. The limit of the total number of workers available is set to 1 less than the maximum of the argument of the *tbb::task\_scheduler\_init* constructor and the total number of logical CPUs on the executing system.

Finally, the *Arena* associated with calling MT gets allocated. An arena encapsulates all the tasks and the execution resources (worker threads) available to a MT. Each arena is assigned a number of slots representing the number of workers the arena requires to perform its parallel tasks. This is defined as 1 less than the minimum of the argument of the *tbb::task\_scheduler\_init* constructor and the total number of workers available (limit set by the market). Because several MTs can coexist, the total number of workers requested by all arenas can be greater than the number of workers available in the RML's pool. In this situation, the market will allot workers proportionally to each MT's request.

All these components and limits are created only once, during the first instance of the *tbb::task\_scheduler\_init* object in the current execution. If an MT is not the first one to call the task scheduler, it will only create a new arena that will comply with the limitation imposed by the market. Upon creation or destruction of an arena, the worker threads can migrate between the active arenas.

After they are created, each worker thread runs a scheduling procedure called *wait\_for\_all()* consisting of 3 nested loops. The inner loop is executing the current task by calling its *execute()* method. TBB is a continuation-passing style library which means that the completion of this task returns a pointer to the next task that needs to be executed. If a new task is not referenced, the inner loop exits.

In the middle loop the  $get\_task()$  method tries to dequeue the local task queue using a LIFO order. If successful, the inner loop is called again. If unsuccessful because the queue is empty, the middle loop exits and the outer loop invokes the stealing mechanism by calling the  $receive\_or\_steal\_task()$  method.

#### 3 The Stealing Mechanism

#### 3.1 The TBB Implementation

Stealing is part of the *receive\_or\_steal\_task()* method. This method includes some other techniques to find a new task to execute than just stealing: mailing tasks via task-to-thread affinity mechanism, reload offloaded non-priority tasks, reload tasks abandoned by other workers. *Receive\_or\_steal\_task()* method runs an infinite loop and calls each of the above mentioned mechanisms, stealing being the last one. Before a steal is attempted, a victim thread is selected randomly from the current arena. If the attempt is successful, the method returns and the scheduler re-enters the inner loop. If unsuccessful, a failure counter is incremented and the execution pauses before looping back. Also, if the failure counter surpasses a given threshold (default value is 100), the current worker thread is freed and returns to the RML.

The first step when a steal is performed is to use the *lock\_task\_pool()* method and try to get a lock on the victim. If the *lock\_task\_pool()* fails, the worker thread goes through a 5 steps exponential backoff. After 5 fails, the current thread yields its resources and waits for its next time slot to try again locking the same victim. This locking mechanism assures the high composability of TBB we discussed in Section 2. However, since we simulate 1 thread / hardware core, the yielding function returns immediately and the thief thread will continue to try to lock its victim.

A stealing attempt can fail for several reasons. The most common situation is selecting from a victim with an empty task queue. Applications with an unbalanced workload distribution face this problem often.

Race contention is also a common situation for failure. When 2 or more threads are trying to get exclusive access to the same task queue by calling the *lock\_task\_pool()*, only one can succeed. A thief can return from the *lock\_task\_pool()* only if it either succeeds or the victim's task queue has been depleted.

A special situation is when a thief thread is competing for access with the owner thread of that task queue. If there are more than 1 task in the queue, there is no race contention because the thief will steal at one end while the owner will dequeue the other. However, if there is only 1 task in the queue, the owner thread will have priority and the thief will backoff even if it already acquired the lock.

#### 3.2 The Oracle Selection Scheme

In an attempt to set an upper bound for the performance gain, we first implemented an "all knowing" scheme we call oracle selection. This method leverages on the fact that we use a simulator and not a real machine and it provides TBB with information that would be otherwise very "expensive" to obtain. We created a data structure to store the occupancy of all tasks queues in the arena as well as the level of congestion for each queue (the number of workers trying to steal from this queue). This structure is stored outside the simulated memory space in our simulator and is updated by the application through specialized instructions called markers. Since we do all this computation outside the simulated environment, our TBB application sees the victim selection as an extremely fast procedure. The queue with available tasks for stealing and with the lowest congestion level is selected as victim. This oracle scheme provides very fast and accurate results, but it is not optimal. There are still situations when updates to our structure do not propagate fast enough and the selected victim ends up creating conflicts.

#### 3.3 The Pseudo-random Selection Scheme

The second selection method we implemented is a pseudo-random scheme inspired by the Wool library [5]. For the first stealing attempt, we randomly select a task queue. If stealing from this victim fails, we then start a loop and sequentially scan the other active task queues, excluding the one of the current thread. In this way we will first try to steal from all possible queues before looping back in the *receive\_or\_steal\_task()* and selecting a new random victim. Also, we removed the call to the yielding function from the *lock\_task\_pool()* and forced the method to return after the 5 steps exponential backoff. This approach eliminates the conflicts caused by the immediate return of the yielding function, but it will also make the stealing mechanism a bit more aggressive since it allows it to select new victims faster. It is worth mentioning that by doing this, we did not eliminate TBB's composability feature since yielding is implemented in more than one place.

#### 4 Methodology

#### 4.1 Simulation Tools

We performed our experiments using a parallel, x86 computer architecture simulator called Sniper [10]. Sniper uses the interval core model [11] and Graphite simulation infrastructure [12] to provide fast and accurate simulations. Our model is based on a Nehalem-based Xeon 5500-series multi-core CPU (code name Gainestown) with a clock frequency of 2.66 GHz and 3 levels of cache. Table 1 lists the main characteristics of the modeled processor.

The performance results from Sniper are fed into a power estimation tool called McPAT [13]. An important characteristic of McPAT is its ability to model dynamic, static and short-circuit power. Because we use only one CPU model, for a given core count the static power is a constant value. This is why for all our experiments we computed the energy footprint using only the dynamic power.

| Co                 | re                       | Cache       |                    | Main mem. |      |          |

|--------------------|--------------------------|-------------|--------------------|-----------|------|----------|

| #cores             | 1-,2-,4-,<br>8-,16-cores |             | Size               | Assoc.    |      |          |

| Clock<br>frequency | $2.66~\mathrm{GHz}$      | L1 i/dCache | #cores x 32KB      | 4/8       | Size | 2/4/8/   |

| Instruction<br>set | x86-64                   | L2 Cache    | #cores x 256KB     | 8         | Size | 16/32 GB |

| Dispatch<br>width  | 4                        | L3 Cache    | 2/4/8/<br>16/32 MB | 16        |      |          |

| Window size        | 128                      |             |                    |           |      |          |

Table 1. Main characteristics of modeled processor

#### 4.2 Benchmarks

For our experiments, we used the default TBB implementations of *Blackscholes*, *Bodytrack*, *Fluidanimate*, *Streamcluster* and *Swaptions* benchmarks with the medium input set from the PARSEC suite [7]. Collectively, these benchmarks express parallelism both explicitly as well as through some templates like *parallel\_for*, *parallel\_reduce* and pipelines. They also employ some special TBB constructs like cache affinity partitioners and cache allocators. All these provide a wide test base for our study.

Parallelization was done using TBB version 4.1.1. which we customized in order to isolate and measure the overheads introduced by task spawning, task de-queuing and task stealing. We added special instructions called *markers* in the beginning and at the end of each function of interest to allow us to make measurements on the enclosed region of code.

To ensure statistically stable results, we performed 10 simulations of each benchmark for every core count. We averaged the performance results before estimating the power requirements. We computed the standard deviation ( $\sigma$ ) of the execution time for each 10 simulation set as a percentage out of the average value for the set. Our results show a  $\sigma$  that ranges between 0.09% and 14.1% with no outliers (an outlier is a value that is above or bellow  $3\sigma \pm average$  value).

#### 5 Results

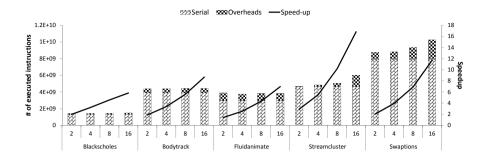

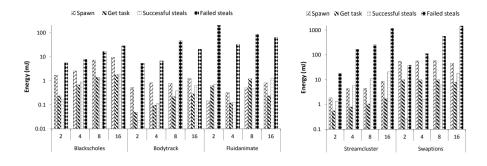

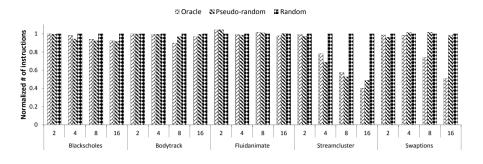

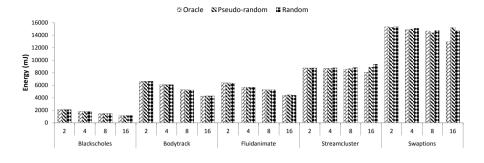

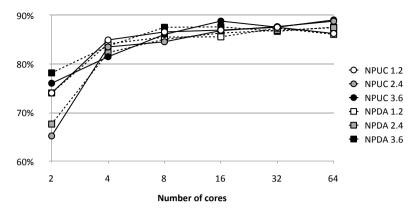

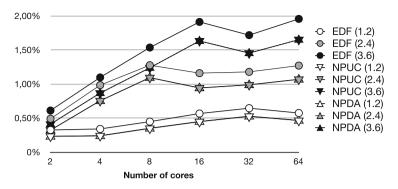

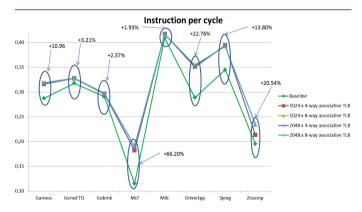

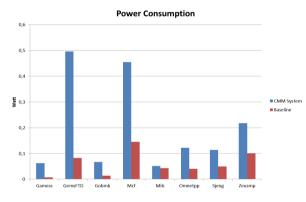

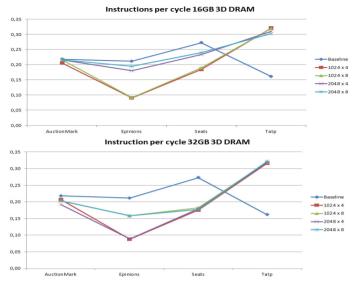

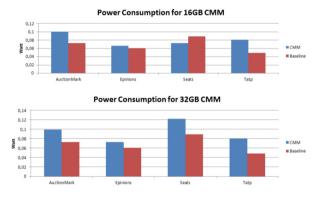

Parallelization overheads often account for the sub-linear speedups of parallel implementation. While this still means that the work gets done faster, the energy required to complete the parallel execution is often equal or greater than the serial one. In Section 5.1 we quantify these overheads as the difference in number of executed instructions between parallel and serial executions. We also break down the the overheads and see how task spawning, task de-queuing and task stealing impact the parallel execution and its energy footprint. For better visualization Fig. 3 is plotted with logarithmic scale on the vertical axis. Finally, in Section 5.2 we look into what performance and energy efficiency gains we can achieve by modifying the victim selection policy.

Fig. 2. Executed number of instructions and speedup

#### 5.1 Parallel Overheads

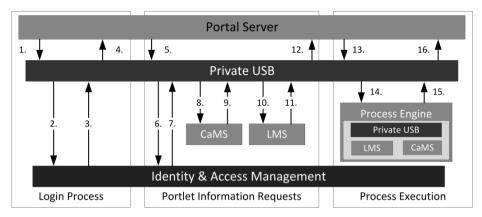

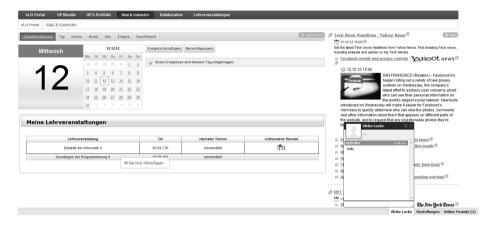

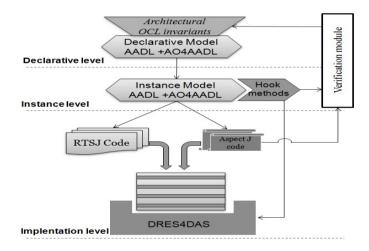

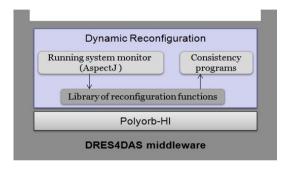

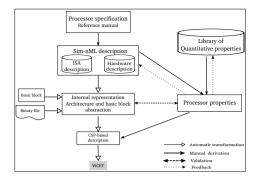

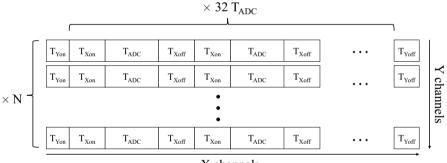

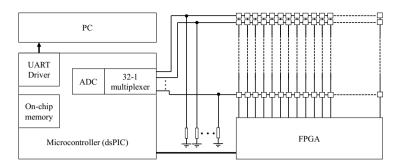

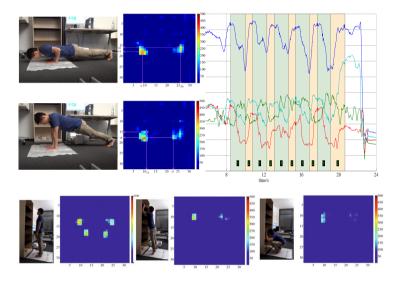

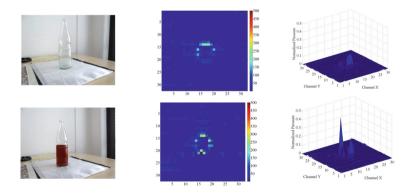

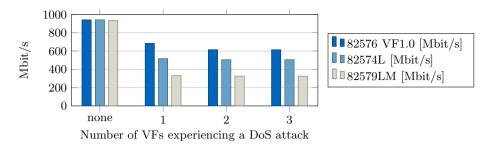

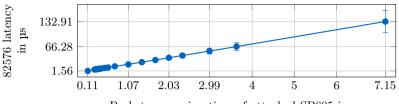

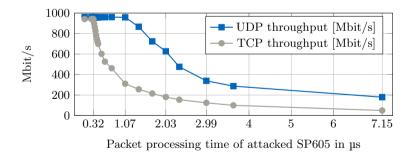

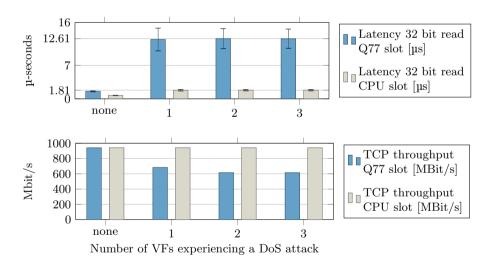

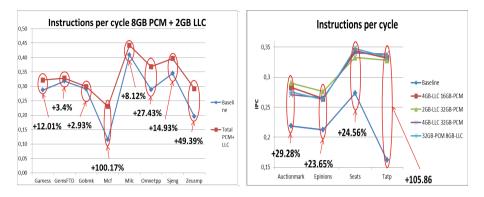

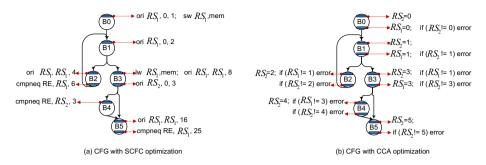

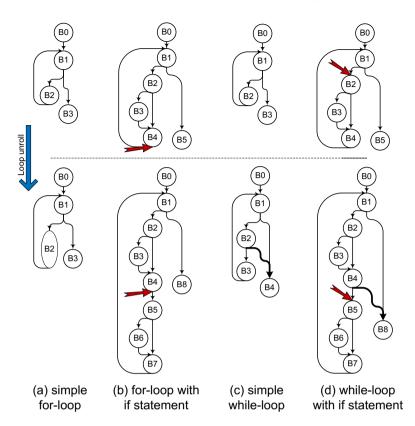

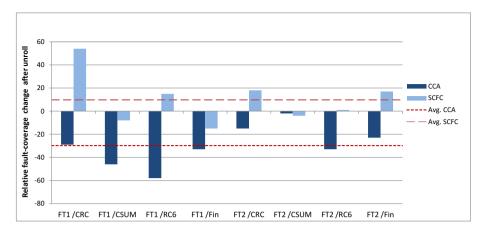

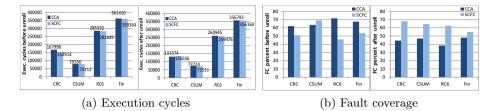

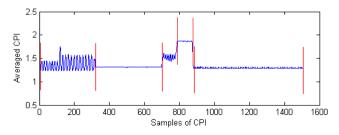

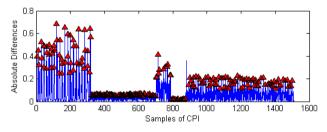

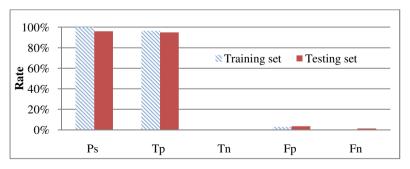

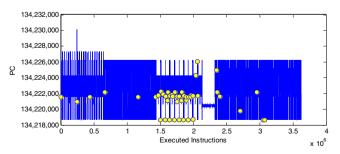

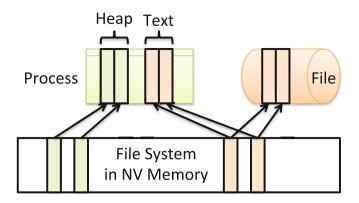

Blackscholes employs TBB's parallel\_for template for all the options in the input portfolio. Tasks are created by dividing these options on to the thread workers. This benchmark uses an *auto partitioning* algorithm to control the granularity of the tasks in order to handle work imbalance as well as possible. In Fig. 2 you can see that the overheads are almost constant across the core count. This shows how small the parallel section is compared to the serial one and also why we see only a 5.8 speedup on the 16 core execution. Fig. 3 breaks down the overheads and shows the energy footprint of the task spawning, task de-queuing and task stealing. Because we kept the input set constant across all core counts, our total number of tasks increases as we scale up the number of execution threads, but tasks also become finer. This has two consequences: the energy footprint for spawning increases from 2 to 16 cores (see Fig. 3) and the overhead to useful work ratio per task increases with the core count. Fig. 3 shows the same trend for the  $qet_task()$  method. Second, we have the high number of stealing attempts. The energy footprint for failed steals is highest among what we measured and the trend is: more cores means more conflicts which leads to more failed attempts. Successful stealing has a smaller footprint but the same trend.