Lecture Notes in Electrical Engineering 289

# Alessandro De Gloria *Editor*

# Applications in Electronics Pervading Industry, Environment and Society

## Lecture Notes in Electrical Engineering

#### Volume 289

#### Board of Series Editors

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Junjie James Zhang, Charlotte, USA

For further volumes: http://www.springer.com/series/7818

#### About this Series

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

Alessandro De Gloria Editor

# Applications in Electronics Pervading Industry, Environment and Society

*Editor* Alessandro De Gloria Electronic Engineering University of Genova Genova Italy

ISSN 1876-1100

ISSN 1876-1119 (electronic)

ISBN 978-3-319-04369-2

ISBN 978-3-319-04370-8 (eBook)

DOI 10.1007/978-3-319-04370-8

Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014943115

© Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

Electronics technology has known a very fast development becoming pervasive of everyday life activities. Nowadays, electronics devices are so common that we seldom pay attention to them considering them as usual objects. Electronics devices are often considered a commodity and the attention is toward the application instead of the devices.

Often the prefix "e" is used to technologically qualify a product or a service (E-mail, E-card, E-commerce, E-banking, E-business, E-book, to cite a few) and to communicate that it is new, modern, advanced. Electronics devices have become a part of our life; they are no more a product used in the industrial environment to improve the features of a product. They have changed our life; you only have to think to a smartphone.

The incursion of electronics devices in life has lead to a revision in the electronics engineer's role. It is not enough to be able to design and implement an efficient device. The design has to consider the context in which the device will be used. Factors like human-machine interaction, usability, scalability, reusability must be included into the specification and drive the design of the device.

These considerations lead to put the attention toward the applications and the development of systems that increasingly simplify human activities.

The APPLEPIES conference aims at bringing together researchers and stakeholders, in order to share the state of the art of research and market in the field of applied electronics. The goal is to discuss the most significant trends, to explore the challenges, issues, and opportunities in the research and to debate on visions about the future of the electronics pervading industry, environment, and society.

The conference also includes an exhibition, where industries can highlight their latest products and technological cornerstones for future applications.

APPLEPIES is an annual conference and it is building a scientific community for shaping the future research in the field. This community represents a significant blend of industrial and academic professionals, mainly at Italian level but with an opening over the international audience, committed to the study, development, and deployment of electronics systems in all the main application fields.

Alessandro De Gloria

# Contents

| 1 | SuperCap-Based Energy Back-up System for Automotive<br>Electronic Control Units                                                   |    |  |  |  |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|   | Electronic Control Units<br>Sergio Saponara, Roberto Saletti, Luca Fanucci, Roberto Roncella,<br>Marco Marlia and Corrado Taviani |    |  |  |  |  |

|   |                                                                                                                                   |    |  |  |  |  |

| 2 | CH <sub>4</sub> Monitoring with Ultra-Low Power Wireless                                                                          |    |  |  |  |  |

|   | Sensor Network                                                                                                                    | 13 |  |  |  |  |

|   | Davide Brunelli and Maurizio Rossi                                                                                                |    |  |  |  |  |

| 3 | Integrated Front-end Electronics for Silicon PhotoMultiplier                                                                      |    |  |  |  |  |

|   | Readout in Medical Imaging Applications                                                                                           | 27 |  |  |  |  |

|   | Nahema Marino, Sergio Saponara, Luca Fanucci, Federico Baronti,                                                                   |    |  |  |  |  |

|   | Roberto Roncella, Francesco Corsi, Cristoforo Marzocca,                                                                           |    |  |  |  |  |

|   | Gianvito Matarrese, Fabio Ciciriello, Francesco Licciulli,                                                                        |    |  |  |  |  |

|   | Maria Giuseppina Bisogni and Alberto Del Guerra                                                                                   |    |  |  |  |  |

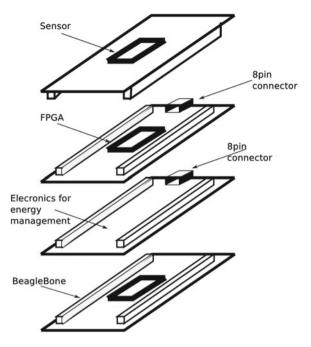

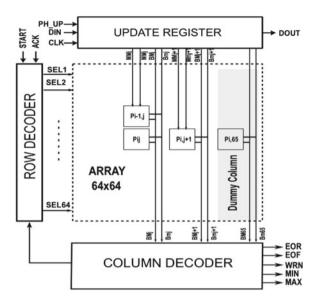

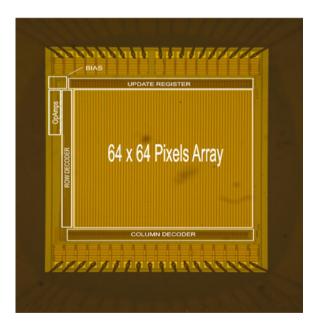

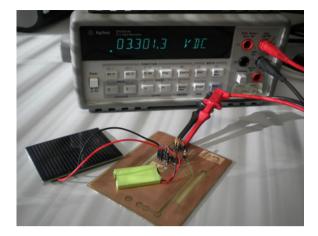

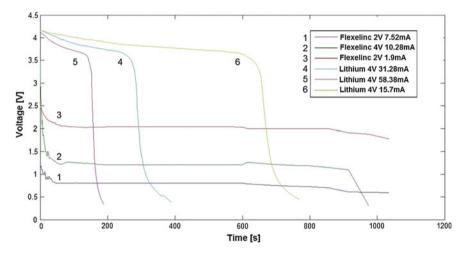

| 4 | Energy Autonomous Low Power Vision System                                                                                         | 39 |  |  |  |  |

|   | Davide Brunelli, Alberto Tovazzi, Massimo Gottardi,                                                                               |    |  |  |  |  |

|   | Michele Benetti, Roberto Passerone and Pamela Abshire                                                                             |    |  |  |  |  |

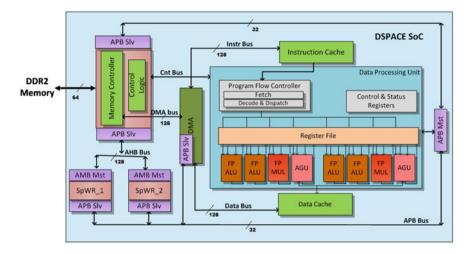

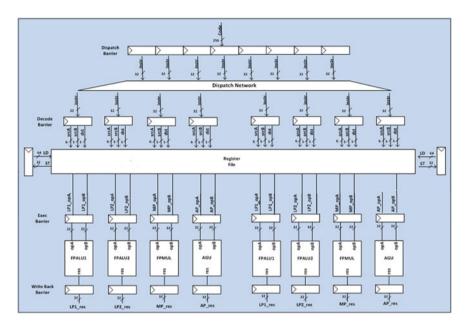

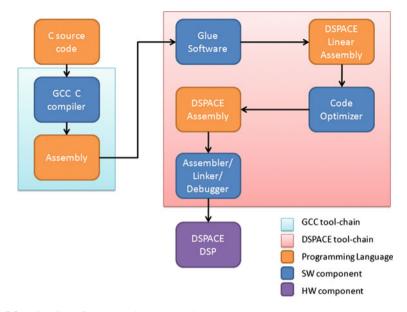

| 5 | A New Space Digital Signal Processor Design                                                                                       | 51 |  |  |  |  |

|   | Massimiliano Donati, Sergio Saponara, Luca Fanucci,                                                                               |    |  |  |  |  |

|   | Walter Errico, Annamaria Colonna, Giuseppe Piscopiello,                                                                           |    |  |  |  |  |

|   | Giovanni Tuccio, Franco Bigongiari, Maximilian Odendahl,                                                                          |    |  |  |  |  |

|   | Rainer Leupers, Antonio Spada, Vincenzo Pii, Elena Cordiviola,                                                                    |    |  |  |  |  |

|   | Francesco Nuzzolo and Frederic Reiter                                                                                             |    |  |  |  |  |

| 6 | Spatial Sound Rendering for Assisted Living                                                                                       |    |  |  |  |  |

|   | on an Embedded Platform                                                                                                           | 61 |  |  |  |  |

|   | Luca Rizzon and Roberto Passerone                                                                                                 |    |  |  |  |  |

| 7  | <b>BASIC32: A New ASIC for Silicon Photomultiplier Detectors</b> Fabio Ciciriello, Francesco Corsi, Francesco Licciulli, Cristoforo Marzocca, Gianvito Matarrese, Alberto Del Guerra and Maria Giuseppina Bisogni            | 75  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8  | Reconfigurable Implementation of a CNN-UM Platform<br>for Fast Dynamical Systems Simulation<br>Gianluca Borgese, Calogero Pace, Pietro Pantano<br>and Eleonora Bilotta                                                       | 85  |

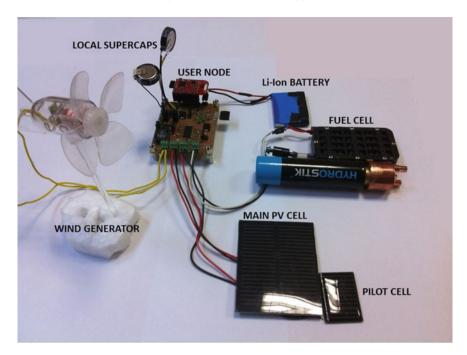

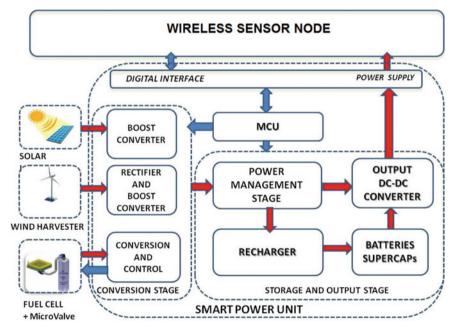

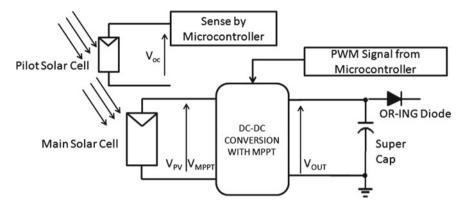

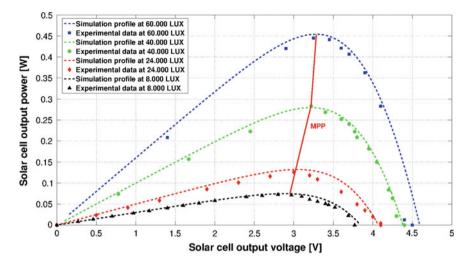

| 9  | A Multi Harvester with Hydrogen Fuel Cell<br>for Outdoor Applications<br>Davide Brunelli, Michele Magno, Danilo Porcarelli<br>and Luca Benini                                                                                | 103 |

| 10 | <ul> <li>A Dosimetric Device Based on CMOS Image Sensor</li> <li>for Interventional Radiology</li> <li>E. Conti, D. Magalotti, P. Placidi, L. Bissi, M. Paolucci,</li> <li>D. Passeri, A. Scorzoni and L. Servoli</li> </ul> | 113 |

| 11 | A Novel Wireless Sensor Network for Electric<br>Power Metering<br>Natale Galioto, Francesco Lo Bue, Daniele Rizzo,<br>Leonardo Mistretta and Costantino Giuseppe Giaconia                                                    | 121 |

| 12 | High Performance Bit-Stream Decompressor for PartialReconfigurable FPGAsGian Carlo Cardarilli, Marco Re and Ilir Shuli                                                                                                       | 133 |

| 13 | A Reconfigurable Functional Unit for Modular Operations Gian Carlo Cardarilli, Luca Di Nunzio, Rocco Fazzolari, Salvatore Pontarelli and Marco Re                                                                            | 141 |

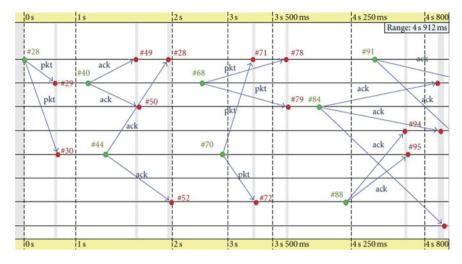

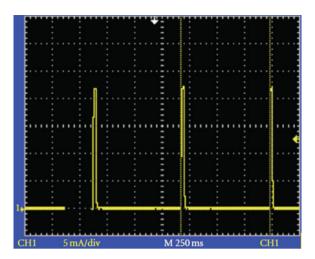

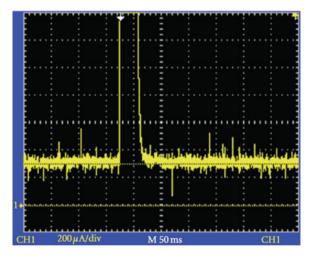

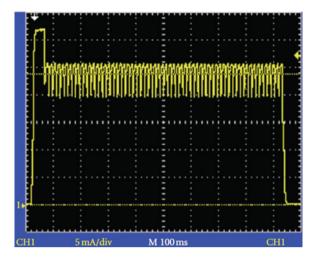

| 14 | Wireless and Ad Hoc Sensor Networks: An Industrial<br>Example Using Delay Tolerant, Low Power Protocols<br>for Security-Critical Applications<br>Claudio S. Malavenda, Francesco Menichelli and Mauro Olivieri               | 153 |

| 15 | A Social Serious Game Concept for Green, Fluid<br>and Collaborative Driving<br>Francesco Bellotti, Riccardo Berta and Alessandro De Gloria                                                                                   | 163 |

# Chapter 1 SuperCap-Based Energy Back-up System for Automotive Electronic Control Units

Sergio Saponara, Roberto Saletti, Luca Fanucci, Roberto Roncella, Marco Marlia and Corrado Taviani

**Abstract** The E-latch is a new automotive mechatronic device that substitutes the door closure mechanical system with electro-actuated parts plus an embedded electronic control unit (ECU) connected to the main vehicle network. Due to severe automotive safety-critical requirements for door closure, an energy back-up system is required. A solution based on supercaps and boost converter is proposed in this work to ensure E-latch operation even in case of main battery failure. An in-depth thermal, electrical and durability characterization of the supercaps proves the reliability of the energy back-up unit for automotive applications. A Components Off the Shelf (COTS) approach has been followed for the E-latch prototype and test phases. A migration towards an Application Specific Integrated Circuit (ASIC) design approach is envisaged for future large volume production.

R. Saletti e-mail: roberto.saletti@iet.unipi.it

L. Fanucci e-mail: luca.fanucci@iet.unipi.it

R. Roncella e-mail: roberto.roncella@iet.unipi.it

M. Marlia · C. Taviani MAGNA CLOSURES—Motrol Division, Guasticce, Livorno, Italy e-mail: marco.marlia@magnaclosures.com

C. Taviani e-mail: corrado.taviani@magnaclosures.com

S. Saponara (🖂) · R. Saletti · L. Fanucci · R. Roncella

Department of Information Engineering, University of Pisa, Pisa, Italy e-mail: sergio.saponara@iet.unipi.it

A. De Gloria (ed.), *Applications in Electronics Pervading Industry, Environment and Society*, Lecture Notes in Electrical Engineering 289, DOI: 10.1007/978-3-319-04370-8\_1, © Springer International Publishing Switzerland 2014

#### **1.1 Introduction**

A strong tendency in the automotive field is to make the mechanical systems more and more controlled by an Electronic Control Unit (ECU), which properly manages sensors and electro-actuators improves the mechanical system performance and even makes new functions available. Automatic transmission, suspension control, electronic controlled injection in internal combustion engine, brake-by-wire and steer-by-wire systems are just some examples of this consolidated trend [1-6]. As far the door subsystem is concerned window lifter and in some cars also the rear mirror are electronically controlled, while the door open/closure unit is still mechanical, as in [5]. The Advanced Mechatronic Door System (AMDS) project is the framework in which the industry-academic collaboration between Magna Closures and the University of Pisa led to the introduction of a new mechatronic system for door closure called *E-latch*. Several advantages are achieved: reduced weight and size as compared the mechanical-based door closure system; increased flexibility, scalability and re-programmability of the unit to address different vehicle models and vehicle generations; integration of the latch system in the vehicle networks to enable advanced safety features or new comfort functionalities.

The *E-latch* is a new node of the main vehicle network that is connected either through a Local Interconnect Network (LIN) or a Controller Area Network (CAN) bus. It manages all the following functions: reading the car handle and door status by means of Hall sensors or contact sensors; communicating with the car body computer by receiving commands from the users (lock, double lock, child lock, anti theft lock, release) and transmitting the door status or diagnostic info; driving the electric motor actuating the closure/release of the door (operating at 12 V nominal, 8 V minimum, with a current absorption in the order of several amperes); managing the available energy sources, both the main battery and the back-up one (the supercaps and boost converter subsystem proposed in this paper). The widespread adoption of the *E*-latch is strongly challenged by the high level of reliability that is mandatory to achieve, particularly by the energy back-up system. The correct functionality of door release must be guaranteed by the *E-latch* even in case of an accident or a general failure of the main vehicle battery. An energy back-up system with minimum power consumption and weight/size overhead during normal vehicle operation is thus necessary. To overcome this issue a new supercap-based energy back-up system for automotive ECU is proposed in this paper.

Although applied to the E-latch ECU, the proposed energy-back up subsystem is general enough to be applied to any automotive ECU. Hereafter Sect. 1.2 describes the E-latch architecture while Sect. 1.3 deals with the architecture of the energy back-up system. Section 1.4 discusses the thermal, electrical and life-cycle characterization of the new proposed energy back-up system. Conclusions are drawn in Sect. 1.5.

#### **1.2 The New E-latch Electronic Control Unit**

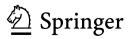

Figure 1.1a shows the modular architecture of the *E-Latch*, which is divided in two main units (Latch and Cinch). Each unit includes: (1) a micro-controller with LIN connectivity and multiple PWM output channels, (2) a high-voltage protection circuit for the direct connection to a 12 V power supply, (3) an integrated H-bridge power MOS motor driver to drive an electrical motor, (4) electrical motor and Hall sensors to carry on the door lock/release and monitor the door status, respectively. The Latch sub-unit, the detailed architecture of which is shown in Fig. 1.1b, is generally used in all the vehicles, since it manages the basic door locking and release (with special child-lock or double lock or anti-theft lock functionalities), whereas the Cinch is a special function, which automatically and gently closes the door when the door is leaved ajar by the user, to be installed in premium vehicles only.

The Latch sub-unit is connected to the body computer through a LIN port, while the Cinch module, when present, is a slave of the Latch one. The operating temperature of the *E-latch* spans from -40 to  $80^{\circ}$ C, and thousands of open/lock cycles are expected in its lifetime. The electronics must also withstand temperatures up to  $130^{\circ}$ C during the repainting process of a vehicle door. The micro-controller and the protection circuitry are realized by a System-on-a-Package (SIP) device with TQFP48 package, the Quest from Freescale [7], which integrates in the same package a digital chip (a 16-b S12 CPU with 20 MHz clock frequency, several kB of FLASH and RAM memory, 16-b timer) and an analog chip sustaining up to 18 V with on-chip temperature sensor, integrated low-drop out 2.5 V/5 V voltage regulator, 10-b ADC, multi-channel PWM module for high/low-side drivers, Hall sensor front-end, GPIO pins.

The integrated motor driver, from STMicroelectronics [8], is provided in a MultiPowerSO-30 package. It contains a dual monolithic high-side driver and two low side switches, with Power MOSFET and intelligent signal/protection circuitry. all It is able to sustain PWM motor control up to 20 kHz with 40 and 30 A voltage and current maximum values, well above the requirements of the Latch or Cinch modules.

The *E*-*latch* can work in two power modes: full power mode, where all the subunits are working; power-down mode, where all the devices are off and the ECU is ready to be waken-up by the watchdog timer or an external interrupt. The residual current consumption in this mode useful when the vehicle is parked is a few microampere. The *E*-*latch* complies with the paradigm of the safety-critical electronic design as dictated by ISO/DIS 26262 [9].

As the E-latch future market volumes are foreseen in millions of pieces, an envisaged evolution of the proposed architecture consists in partitioning the Latch and Cinch units, currently realized via hardware, via software, by adopting a single 32-bit automotive microcontroller, with a 64 pin package at least. Such kind of devices, which represents the next generation of automotive processors [10–12] from different vendors (e.g. TX03 family by Toshiba, SPC56 family by STMicroelectronics, Tricore family by Infineon, Fado and Bolero families by Freescale), are often

S. Saponara et al.

Fig. 1.1 a E-latch block diagram with Latch and Cinch functions. b Schematic of the E-latch unit

4

equipped with a double core thus increasing redundancy and hence fault-robustness. This way, the Cinch function or other advanced tasks can be added/removed by simply changing the firmware while the hardware of the E-latch ECU remains the same. The microcontroller 12 V protection/power managing circuitry (currently integrated in the single-package Quest device), the integrated motor drivers and the sparse glue logic could be realized single-chip as a custom ASIC, thus reducing the size and assembly cost of the E-latch. This new architecture can be the revolutionary approach to a completely new door system that, beside the E-latch, currently includes other two ECUs, the window lifter (integrating intelligent functionalities as the anti-pinch software) and the mirror control. A single 32-bit powerful automotive microcontroller could manage all the software tasks and the communication with the car body computer, while distributing multiple applications specific ICs for sensor interfacing and motor driving, one for each function (mirror, window lifter, latch/cinch), instead of having 3 different ECUs.

Whichever architecture is adopted, a key issue for door ECUs is guaranteeing the correct behaviour when the main battery fails: a supercapacitor-based energy backup system has been designed to this aim, and characterized in terms of electrical, thermal and durability performance.

#### **1.3 Architecture of the Energy Back-up Unit** for Automotive ECU

The energy back-up system of an automotive door systems must operate from -40to 80°C, and withstand up to 130°C in case of door repainting. The energy backup unit is kept charged by the main vehicle battery in normal conditions, so that it can provide enough energy (tens of joule in short bursts of about 100 ms, for about 100 W in power, 8-12 V in voltage and 6-10 A in current) to ensure several door releases in case of main battery failure. The energy back-up unit should be close to the ECU, robust to wiring failures, with minimum overhead in terms of cost, size and weight. Supercapacitor based energy storage systems are used in cars, but mainly for higher energy/power levels (tens of kWh/kW) [13–17]. Energy back-up solutions for low-power embedded systems are found in the literature mainly for ICT or consumer applications, not meeting the harsh environment requirements of vehicles. Our choice was exploring the use of super-capacitors as storage devices in the E-latch application, because of the large temperature range and the high power density needed. Lithium batteries, widely adopted [13, 14] for automotive electric or hybrid propulsion, would provide better energy density; however, a burst release of power is needed in the E-latch application when the emergency release is activated (supercapacitors provide better power density [15-21]) and the required temperature range is not covered by Lithium-based rechargeable batteries, typically limited up to 60°C. There are Lithium batteries (3.6 V Li-SOCl<sub>2</sub>) that operate up to 150°C, but they are non rechargeable and with high series resistance. Hence, these batteries

seem more suited as very long-term energy storage devices, useful to keep the energy backup system charged during the winter parking of cabriolet cars or every time the main battery is disconnected for a long time. In conclusion, Electric Double Layer Capacitors (EDLC) with 2.5 V supply and tens of Farads, available from several vendors such as Elna, Nichicon, Cooper-Bussmann, Maxwell, were selected as energy storage devices for the energy back-up system of the E-latch.

Since the electric motor of the Latch or Cinch needs a minimum drive of 8 V, and considering also redundancy issues, the back-up system includes: two EDLC supercapacitors (2.5 V nominal) connected in series plus an on-board x2 boost converter. This solution provides a nominal voltage of 10 V and a minimum of 8 V when the supercapacitors are not completely charged. As an example, two 2.5 V 10 F supercapacitors connected in series provide up to 62.5 J, an energy sufficient for 10 door releases in case of main battery failure. In fact, each release typically requires 10 V and 6 A for 100 ms.

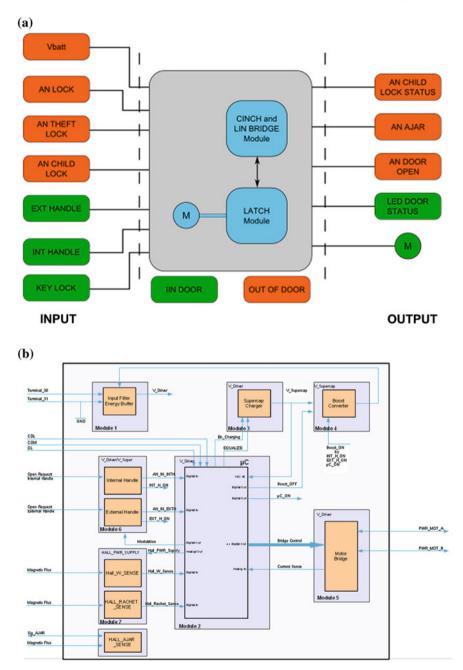

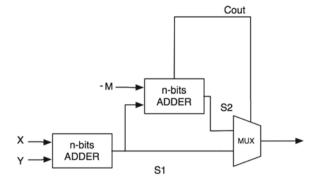

The switching architecture of the boost converter provides a high power efficiency in the voltage doubling. The PWM controller is realized with the TI TL5001A IC and small external RC components in the feedback loop, mounted on the same PCB. The *E-latch* micro-controller properly drives as open the boost converter switch SW1 and the feedback switch SW2 of Fig. 1.2, when the main battery voltage is present.

The boost converter is thus normally off, the super-capacitors maintain their backup energy and the resistors of the converter feedback do not waste power. When the main battery fails, the micro-controller is supplied by the two supercapacitors in series (5 V), and the switches SW1 and SW2 are now turned on, so that the door latch electric motor can be supplied by the supercapacitors.

The switches SW1 and SW2 are realized with low-resistance MOS to maximize power efficiency. The main inductor also has a series resistance of few milliohms. The feedback is realized with a divider of the output voltage realized with two resistors of 30 and 330 k $\Omega$ . Since a complete characterization of supercapacitors of few farads for energy back-up in automotive ECU is missing in the literature, the devices to be used in the *E-latch* have been chosen after a thorough characterization campaign of 2.5 V EDLC supercapacitors in the range 10–25 F, provided from the above cited vendors. Given the available space, not all the experimental data are reported. Instead, the characterization tests are described in Sect. 1.4 and the results obtained for the selected device, the 18 F Nichicon device with  $V_{nom} = 2.5$  V and  $V_{max} = 2.7$  V, are showed.

#### 1.4 Thermal, Electrical and Lifecycle Characterization of Supercap for Energy Back-up

Let us define C as the supercap capacitance,  $V_{nom}$  the nominal voltage,  $V_{max}$  the maximum allowed voltage,  $V_{ref} = 0.9 * V_{max} = 2.43$  V and  $I_{ref} = C * V_{ref}/30 = 1.62$  A. The following tests have been carried out.

Fig. 1.2 Schematic of the boost-converter used in the back-up energy unit

Constant-current charge/discharge capacitance test: the device is charged at 23°C for 3 cycles at a constant current  $I_{test} = I_{ref}/4 = 0.405$  A up to  $V_{ref}$ , then it is kept at this constant voltage for 10 ms and then is completely discharged at constant current  $I_{ref}/4$ ; the 3-cycle test is repeated with current values of  $I_{ref}/2 = 0.81$  A and  $2I_{ref} = 3.24$  A. The supercap capacitance in charge and in discharge modes is calculated as  $C = I_{test} * T_{test}/V_{ref}$ .

*Constant-current ESR test*: the supercap series resistance (ESR) has a visible effect during the above described charge/discharge tests at the start of the discharge phase, where the current step determines a voltage drop. Dividing the voltage drop by the constant discharge current gives the ESR value.

*Leakage test*: the supercap tends to loose charge because of the auto-discharge; this phenomenon is modeled as a parallel time-variant leakage resistance. The supercapacitor is charged from 0 to  $V_{ref}$  at 23°C and is kept at such voltage value for 3 h. The capacitor current  $I_{leak}$  needed to hold the constant voltage value during this time interval is the leakage current. The parallel resistance  $R_p$  is the ratio  $V_{ref}/I_{leak}$  and it is calculated after 30 min, 1, 2 and 3 h. This test is usually repeated at different temperatures and for different durations.

*Technology spreading and thermal tests*: the leakage, ESR and capacitance tests are repeated using different samples of the same device to evaluate the technology spreading. The tests are also repeated on the same super-capacitor at different temperatures to determine the temperature dependence of capacitance, ESR and leakage.

*Durability-temperature test:* after 10 charge/discharge training cycles at 1 A, the supercap is characterized at 23°C using the above described procedures. This is the starting point of a durability test. A loop of 52 cycles is repeated. The loop consists of a first charge from  $V_{max}/2$  to 0.9  $V_{max}$ ; 50 charge/slow discharge cycles between

90 and 80 % of  $V_{max}$  with a charging current of  $I_{ref}/20 = 80$  mA and a discharge current of 10 mA follow; 1 last charge/fast discharge cycle between 90 and 70 % of  $V_{max}$  with a charge current of 80 mA and a discharge of  $I_{ref}/2 = 800$  mA completes the loop. The entire loop is then repeated 60 times. Such tests are repeated at 25, -40 and 80°C for a total of around 10,000 cycles. The basic ESR-capacitance-leakage characterization at 23°C is carried out after each temperature value, to analyze degradations caused by the durability test.

*Repainting test*: It consists of 15 min test at 130°C followed by 60 min at 110°C. The supercap is characterized at 23°C (ESR, leakage, capacitance) before/after the test, to evaluate possible performance degradations due to the repainting cycle. All the thermal tests are carried out in Binder MK53 thermal chamber.

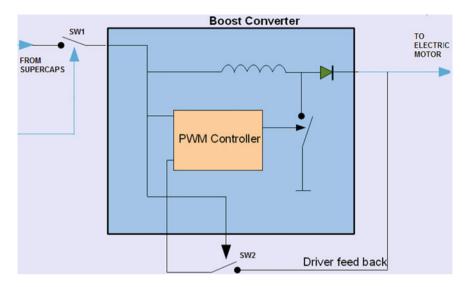

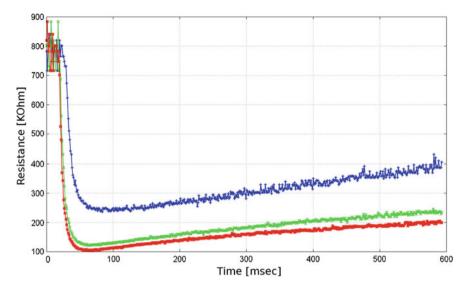

The above described tests have been applied to several EDLC supercapacitors from different vendors, with 2.5 V nominal voltage and capacitance ranging from 10 to 25 F. We report here the main results obtained for the selected device, a 18 F Nichicon EDLC, that demonstrates the suitability of the supercap to solve the energy back-up issue of the E-latch. The capacitance and ESR tests at 23°C shows a measured capacitance and resistance of 17.69 F and 39.42 mΩ, respectively, at 0.405 A. Values of 18.47 F and 18.92 m $\Omega$  are found at 3.24 A. The measured capacitance differs less than 2.6 % from the nominal value of 18 F; the series resistance is well below 100 m $\Omega$ . The time-variant parallel resistance extracted from the leakage test at 23°C is in the order of some kiloohm after 30 min and rises up to hundreds of kiloohm after 3h. Repeating the tests on different samples of the same super-capacitor gives a spreading of the results limited to few percent, showing a good repeatability of the device characteristics. A limited mismatch of the samples makes negligible the equalization problem that arises when two units are mounted in series, as it happens in the *E-latch* circuit. Instead, a higher dependence of the parameters on the temperature has been found, as expected from theory and from results presented in the literature for much larger size supercapacitors (up to of thousands of Farad) [15-21]. As an example, Fig. 1.3a shows the ESR measured with a  $I_{test} = I_{ref}/2 = 0.81$  A in a temperature range from -40 to  $100^{\circ}$ C. The ESR value increases when the temperature decreases, but the series resistance remains always below  $100 \text{ m}\Omega$ .

Since the capacitance value changes as a function of temperature, the voltage slope of the charge/discharge test changes in its turn, as it is demonstrated in Fig. 1.3b, where 0.81 A constant current tests at different temperatures are reported. While the ESR behavior is monotonic with the temperature and there is a large variation at low temperatures (Fig. 1.3a), the voltage slope value is instead weakly dependent on the temperature between  $-40^{\circ}$ C and room temperature (Fig. 1.3b). A difference in the time slope in Fig. 1.3b and hence in the capacitance is noticeable when going from room temperature to  $100^{\circ}$ C.

The slope and hence the capacitance increases with the temperature when going from -40 to  $80^{\circ}$ C; instead, the capacitance decreases going from 80 to  $100^{\circ}$ C. This behavior agrees with the results published in the literature over larger super-capacitors (thousands of Farad), in which a non-linear behaviour of the capacitance with the voltage is found. In fact, the capacitance is composed of a fixed part  $C_0$ ,

Fig. 1.3 a Thermal dependance of the ESR in the charge-discharge test,  $I_{test} = 0.81$  A. b Thermal dependance of the voltage slope in the charge-discharge test,  $I_{test} = 0.81$  A

that increases with the temperature, and a voltage dependent part,  $C_v(V)$ , that instead decreases when temperature increases.

The repainting test up to 130°C does not seem to affect the supercap performance. Indeed, the ESR, leakage current and capacitance values measured after the repainting thermal cycle shows that the capacitance and ESR are 17.61 F and 27.58 m $\Omega$ respectively at 0.405 A, and 17.85 F and 20.11 m $\Omega$  respectively, at 3.24 A. The leakage resistance varies from 2 to  $105 \text{ k}\Omega$  from 30 min to 3 h. Such values are acceptable for the normal use of a super-capacitor in the E-latch. Similar findings are obtained after the durability tests, see Table 1.1. The durability test consists of 10,000 cycles at temperatures from -40 to  $80^{\circ}$ C. It is found that the ESR only increases of a few percent and the capacitance decrease also is limited to a maximum of 10 %. These values are well acceptable for the application and demonstrate the suitability of the supercaps as energy back-up sources also after thousands of operating cycles. A major effect is instead noticed on the leakage current: the 3 h leakage value increases from 2 to 50 µA after the durability test. It means that after 10,000 cycles the investigated supercapacitor is completely autodischarged in about 10<sup>6</sup> s, i.e. around 11 days, if it is not recharged. This is not a problem when the main battery is working and it is continuously charging the supercapacitors (boost converter off). Should a

|               | ESR (m $\Omega$ ) |        | Capacitance (F) |         | Leakage current |  |

|---------------|-------------------|--------|-----------------|---------|-----------------|--|

|               | 0.405 A           | 1.62 A | 0.405 A         | 1.62 A  | _               |  |

| Initial       | 26.52             | 19.27  | 17.52           | 17.85   | 2 μΑ            |  |

| Max. derating | 27.35             | 19.47  | 16.04           | 16      | 50 µA           |  |

| Change        | 3.03 %            | 1.03 % | 8.45 %          | 10.36 % | -               |  |

Table 1.1

Performance derating after durability test

main battery failure occur, the supercapacitors backup energy source is needed to actuate the door release (e.g. to escape the car after a road accident) and hence 11 days before the autodischarge are still a long time considering the typical *E-latch* application.

#### **1.5 Conclusions**

A new generation of ECU where the mechanical door closure system is actuated by a motor controlled by an electronic system is showing up on the car market. The *E-latch* brings advantages in system modularity, scalability, cost, size and weight. Due to the severe automotive safety-critical requirements, an energy back-up solution is needed to ensure door release/closure also in case of main battery failure, e.g. after a road accident when the emergency release must be guaranteed. An energy back-up solution based on small-size super-capacitors and a boost converter is proposed to this aim. An in-depth thermal, electrical and durability characterization of the supercaps proves their applicability as energy back-up and the reliability of the energy backup unit for any automotive small energy back-up applications. The critical point is the right selection of the energy storage device. A thorough test and measurement campaign demonstrates that the selected EDLC supercaps allow for the required energy storage capability, with extended operating temperature range from  $-40^{\circ}$ C up to (non continuous)  $130^{\circ}$ C, low series resistance and leakage current, and low performance degradation even after 10,000-cycle durability test.

Acknowledgments This work has been supported by Tuscany Region under the project "AMDS: Advanced Mechatronic Door System".

#### References

- 1. Flamings, B.: Automotive electronics. IEEE Veh. Technol. Mag. 1(1), 40-42 (2006)

- Baronti, F., Lazzeri, A., Roncella, R., Saletti, R., Saponara, S.: Design and characterization of a Robotized Gearbox System based on Voice Coil Actuators for a Formula SAE race car. IEEE/ASME Trans. Mechatron. 18(1), 53–61 (2013)

- 1 SuperCap-Based Energy Back-up System

- Costantino, N., et al.: Design and test of an HV-CMOS intelligent power switch with integrated protections and self-diagnostic for harsh automotive applications. IEEE Trans. Ind. Electron. 58(7), 2715–2727 (2011)

- Baronti, F., Lenzi, F., Roncella, R., Saletti, R., Di Tanna, O.: Electronic Control of a Motorcycle Suspension for Preload Self-Adjustment. IEEE Trans. Ind. Electron. 55(7), 2832–2837 (2008)

- Zhaoxia, X., Youcheng, L.: IEEE hardware design of automobile door with local interconnect network bus. In: IEEE Conference on Control, Automation and System Engin (CASE), pp. 1–4 (2011)

- 6. Saponara, S., et al.: A flexible LED driver for automotive lighting applications: IC design and experimental characterization. IEEE Trans. Power Electron. **27**(3), 1071–1075 (2012)

- Quian, H.: MM912F634 (Quest) Workshop. www.freescale.com.cn/dwf/download/ IDCQuestWorkshopPublic.pdf (2010)

- 8. VNH2SP30: Automotive fully integrated H-bridge motor driver, p. 33 (2008)

- Hillenbrand, M., et al.: Failure mode and effect analysis based on electric and electronic architectures of vehicles to support the safety lifecycle ISO/DIS 26262. In: IEEE International Symposium on Rapid System Prototyping (RSP) 2010, pp. 1–7 (2010)

- Mayer, A., Hellwig, F.: System performance optimization methodology for Infineon's 32-bit automotive microcontroller architecture. In: 2008 Design, Automation and Test in Europe (DATE) Conference, pp. 962–966 (2008)

- 11. Zhang, G.: Freescale automotive microcontroller roadmap. August 2011, doc. n. FTF -AUT-F0783

- Saponara, S., et al.: Architectural exploration and design of Time-interleaved SAR arrays for low-power and high speed A/D converters. IEICE Trans. Electron. 6(E92-C), 843–851 (2009)

- Brandl, M. et al.: Batteries and battery management systems for electric vehicles. In: IEEE DATE 2012, pp. 971–976 (2012)

- Einhorn, M., Conte, F.V., Kral, C., Fleig, J.: Comparison, selection, and parameterization of electrical battery models for automotive applications. IEEE Trans. Power Electron. 28(3), 1429–1437 (2013)

- Gualous, H., Bouquain, D., Berthon, A., Kauffmann, J.M.: Experimental study of supercapacitor serial resistance and capacitance variations with temperature. J. Power Sour. 12, 86–93 (2003)

- Zhang, Y.C., Wei, L., Shen X.: Haiquan Liang: Study of supercapacitor in the application of power electronics. WSEAS Trans.Circ. Syst. 8(6), 508–517 (2009)

- Chang, J.H., Dawson, F.P., Lian, K.K.: A first principles approach to develop a dynamic model of electrochemical capacitors. IEEE Trans. Power Electr. 26(12), 3472–3480 (2011)

- Rizoug, N., Bartholomeüs, P., Le Moigne, P.: Modeling and characterizing supercapacitors using an online method. IEEE Trans. Ind. Electron. 57(12), 3980–3990 (2010)

- Gualous, H., Louahlia, H., Gallay, R.: Supercapacitor characterization and thermal modelling with reversible and irreversible heat effect. IEEE Trans. Power Electr. 26(11), 3402–3409 (2011)

- Kotz, R., Hahn, M., Gallay, R.: Temperature behavior and impedance fundamentals of suercapacitors. J. Power Sour. 154(2), 550–555 (2006)

- El Brouji, E.L.H. et al.: Aging assessment of supercapacitors during calendar life and power cycling tests. In: IEEE Energy Conversion Congress and Exposition (ECCE), pp. 1791–1798 (2009)

## Chapter 2 CH<sub>4</sub> Monitoring with Ultra-Low Power Wireless Sensor Network

Davide Brunelli and Maurizio Rossi

Abstract We propose a novel method to reveal and measure natural gas presence in air, using commercial off-the-self available MOX gas sensors in wireless sensor network applications. This technique reduces the power consumed by the catalytic sensors of a factor  $10\times$ , by an analysis on a reduced sampled period and thus extending the autonomy of battery operated systems. The information about the gas concentration is extracted from the sensor transient response through a discrete cosine transform (DCT) analysis and permits to immediately discriminate between clean-air and hazardous situations. The characterization of the sensing device has been conducted using a wide range of humidity and environmental conditions to demonstrate the effectiveness of the approach and a detailed comparison with the standard usage has been performed. Finally, the technique has been implemented in a Wireless Sensor Network designed specifically to measure air-quality in a large area and to share information over the internet.

#### 2.1 Introduction

The detection of volatile chemicals is an essential to assess the air quality and the safety of indoor environments, because together with surveillance techniques [1], it guarantees to keep the environment safe and secure. Catalytic gas sensors are widely used in environmental monitoring applications because of their low cost, and are available for many kind of chemicals. Moreover, they are more robust with very low maintenance, they exhibit long life time with respect to electrochemical sensors

M. Rossi

D. Brunelli (🖂)

University of Trento, Via Sommarive 14, 38123 Trento, Italy e-mail: davide.brunelli@unitn.it

University of Trento, Via Sommarive 5, 38123 Trento, Italy e-mail: maurizio.rossi@unitn.it

A. De Gloria (ed.), *Applications in Electronics Pervading Industry, Environment and Society*, Lecture Notes in Electrical Engineering 289, DOI: 10.1007/978-3-319-04370-8\_2, © Springer International Publishing Switzerland 2014

and have fast response time. However the low selectivity and the big energy consumption are challenging problems if the energy availability onboard is constrained. Indeed, nowadays, many environmental monitoring projects are moving toward the use of wireless sensor networks, where any mW of power counts. Usually WSN are designed with low power sensors (e.g. temperature, light, pressure, acceleration...); thus catalytic gas sensors would impact with the highest power consumption with respect to any other component on the sensor node, including radio transceivers. Sensors of this kind are commonly used with continuous power supply leaving it always powered (e.g. in smoke detectors), or, at least, for a time interval sufficient to ensure a reliable response. Furthermore, the influence of air humidity variations has been never investigated in the sensor behavior. In this work, both the energy reduction and the humidity influence are taken into consideration to describe the effectiveness of the proposed method.

Analyzing features of the transient response such as the DCT, it is possible to determine gas concentration and its dependence on environmental conditions (in particular humidity). The outcome is an estimation of the gas concentration, which is, of course, less accurate than the traditional method, but still reliable and capable to discriminate between clean air and hazardous concentration, saving more than one order of magnitude in terms of energy absorbed by the sensing device. The goal is to outperform the state-of-art gas sensors in terms of energetic efficiency, providing, at the same time, a new method to integrate the traditional time-based characterization [2] for catalytic sensors. A Wireless Sensor Network (WSN) has been developed to characterize the autonomy of the systems when the sensor are used on battery operated boards. To pave the way to future developments, the coordinator mote has been USB-connected with a smartphone to add internet connectivity. With this configuration, the system can upload the data about air quality to the cloud and make them available everywhere. The power budget needed to maintain the network is also mitigated by compressive sampling techniques such as [3].

#### 2.1.1 Related Works

Chemoresistive sensors are usually targeted at natural gas and combustibles detection, with a focus on performance in terms of ppm/ppb rather than consumption [4, 5]. A great variety of reliable sensors exists, but no one designed to low power applications as it is mandatory for WSNs. However, recently, electrochemical sensors and new catalytic sensors have been presented [6], with low consumption and developed to achieve good performance in environmental monitoring applications.

Unfortunately, an exhaustive characterization of these innovative sensors is not reported, and generally electrochemical devices exhibits a limited lifetime, due to the consumption of the electrochemical reactive elements. Thus, smart and not destructive power management, is still fundamental to achieve ultra-low power consumption with traditional and more robust technology. Some researchers focused their attention on the strategy used to sense the environment. Articles [7–10] propose efficient

duty-cycle activity of the node, and achieve an extension of the life of a node by  $2 \times$  or  $3 \times$ , still using the sensor as indicated by the manufacturer. Other kind of optimization were introduced in the hardware of nodes [11, 12], achieving significant reduction of wasted power when the device is in idle or sleeping state.

#### 2.2 Gas Measurement Characterization

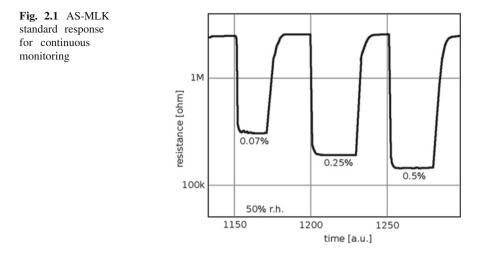

To validate our approach, we used the AS-MLK natural gas sensor, from the Applied Sensor. <sup>1</sup> This is intended for mass market application which key requirements are long lifetime, low cross sensitivity and long term stability. The AS-MLK is targeted at real-time monitoring applications, this means that it must be always switched on to have a prompt response, as shown in Fig. 2.1, where the characteristic provided by the manufacturer is depicted, and the output resistance (versus time) changes quickly to varying concentrations. This device is able to detect gas level in air in the order of hundreds part per million, well below the explosive threshold (5 %), and temperature and humidity slightly influence the measure. Generally, catalytic gas sensors need a constant voltage supply for a reliable measure because the reversible chemical reaction is triggered by heat. The energy consumption are then closely related with the time a sensor needs to reach stability, however, to save power, this time has to be shorten. In environmental monitoring applications, a high frequency of measurement is enough to detect abrupt changes, especially when a dangerous situation is unlikely to happen.

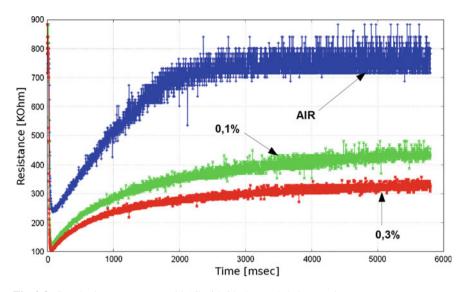

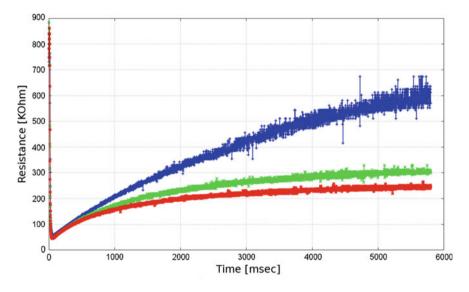

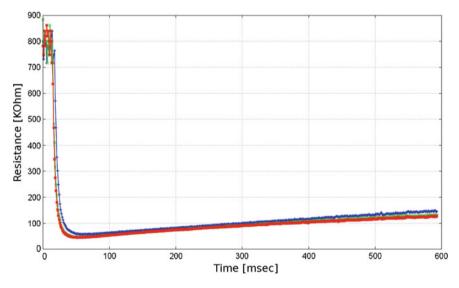

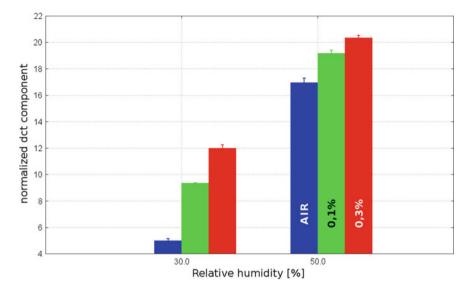

A duty-cycle strategy, in which a measure lasts for less than 6 s and are repeated with intervals of 2 min are shown in Figs. 2.3 and 2.4. The first one was collected with

<sup>&</sup>lt;sup>1</sup> AS-MLK Datasheet, http://www.appliedsensor.com.

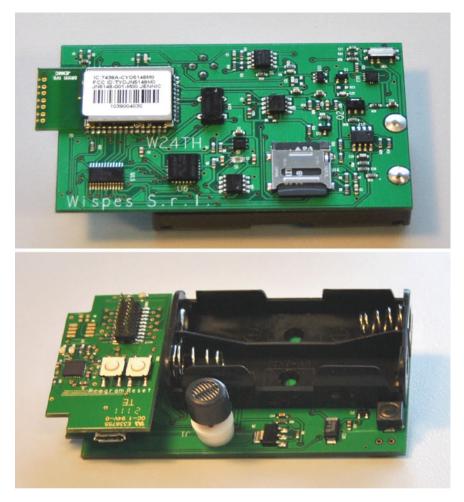

Fig. 2.2 W24TH mote used in our testbed with MOX sensor onboard

30 % of relative humidity in the fluxed mixture (technical air + natural gas), while the latter with 50 %. In both the cases the sensor reaches the stability in the response and it is easy to distinguish the gas level, which traces out the values extracted from the characteristic curve in the datasheet (Fig. 2.1). Unfortunately this approach does not achieve the expected performance, because of the transient response is too long and requires too much power.

#### 2.2.1 Ultra-Low Power Strategy

The transient responses presented in this paper are illustrated in Figs. 2.3 and 2.4, and are detailed in Figs. 2.5 and 2.6. Generally, the larger the humidity, the slower

Fig. 2.3 Standard output response 20 °C with 30 % RH, 5 % duty-cycle

Fig. 2.4 Standard output response 20 °C with 50 % RH, 5 % duty-cycle

the response time. Thus to achieve a good trade-off between energy saving and reliability, reducing the duty-cycle by decreasing the power-on time is not sufficient, because in some environmental conditions it is not possible to discriminate the gas concentration from few samples.

Fig. 2.5 Detail on first 512 samples 20 °C with 30 % RH, 5 % duty-cycle

Fig. 2.6 Detail on first 512 samples 20 °C with 50 % RH, 5 % duty-cycle

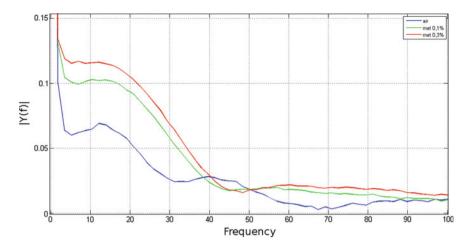

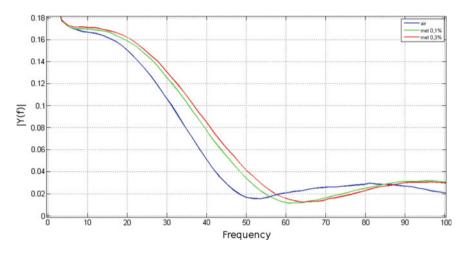

The output resistance of the catalytic sensor is an aperiodic signal and can be interpolated to extract a continuous spectrum through the Discrete Fourier Transform. From the analysis of the normalized amplitude spectrum, it has been observed that the components around 20 Hz, are pretty proportional to the gas concentration, despite the parameters listed before (i.e. time and humidity). This property has

Fig. 2.7 DFT on interpolated standard response 20 °C with 30 % RH, 5 % duty-cycle

Fig. 2.8 DFT on interpolated standard response 20 °C with 50 % RH, 5 % duty-cycle

been fully characterized and then used as feature to assess the gas concentration, while reducing the energy need by the device. Figures 2.7 and 2.8 show the normalized amplitude spectrum of the first 512 samples extracted from the experiments of Figs. 2.3 and 2.4. A Normalized Discrete Cosine Transform (DCT) has been implemented to concentrate on only one component at a time (20 Hz), as the definition shown in Eq. 2.1.

$$\hat{X}_{k} = \frac{\sum_{n=0}^{N-1} x_{n} \cdot e^{-i2\pi \frac{k}{N}n}}{\sum_{n=0}^{N-1} x_{n}}$$

(2.1)

Fig. 2.9 Characteristic response with DCT analysis 20 °C versus RH, 0.5 % duty-cycle

The main advantage of the DCT is the lack of complex computation, thus reducing the arithmetical operations and the amount of memory required, finally resulting in a fast execution of the task. Thus, the smart characterization of the sensor consists in the analysis of the spectrum obtained by the normalized DCT transform of 512 samples taken every 1  $\mu$ s, but it is strongly related with the strategy employed (i.e. repetition interval between measurements).

#### 2.2.2 Characterization

Natural gas is a dangerous volatile substance, thus it is important to guarantee a frequent measurements in the environment, and to assess the features of the proposed technique, we compared it with others implementation characterized by longer repetition interval, namely 2 min: 0.5 % duty-cycle, and 15 min: 0.07 % duty-cycle.

In both the characterization, showed in Figs. 2.9 and 2.10, the results are promising, despite the reduced range of relative humidity condition presented, due to the limits of the gas bench used. The first consideration is related to the very small standard deviation in the measures (the thick lines on top of each bin) which suggests the possibility to reach a smooth characterization and a quantitative determination of this chemical. The other is the behavior of the sensor, strongly related with the sleep time. For short interval, higher the concentration, higher the normalized measure, the opposite in the other case. This underline the importance of defining the sleep interval before each measurements and a careful characterization of the sensor response.

Fig. 2.10 Characteristic response with DCT analysis 20 °C versus RH, 0.07 % duty-cycle

However, these figures demonstrate that discriminating natural gas presence in air is possible, with a minimal energy. Moreover such techniques are compatible with renewable aware policies such as the scheduling proposed in [13].

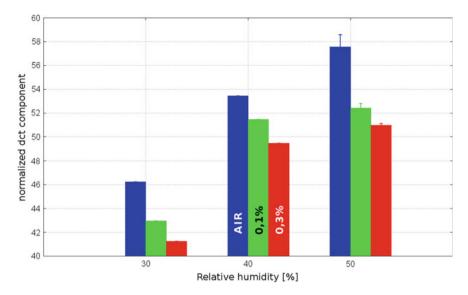

#### 2.3 Energy Saving in WSN Monitoring Applications

The ultra-low power approach, presented in this paper, permits to reduce of one order of magnitude the energy required to estimate the gas concentration in air, decreasing the response time from 6 s of continuous supply to almost 0, 6 s. The whole characterization of the devices and the final example presented in the results were conducted interfacing the sensor to battery operated and resource constraints platform such as a node of a Wireless Sensor Network. Specifications and performance of the nodes can be found in [11]; the most remarkable are the computational architecture (a 32bit microcontroller 32 MHz useful to perform on line processing), with integrated RF module, IEEE 802.15.4 compliant, and integrated antenna, sensors for temperature, relative humidity, light and dock for the catalytic sensors.

The analysis of the consumption is plotted in Fig. 2.11. The trace represents the profile of the power consumption and it is taken using 1  $\Omega$  shunt-resistor. It can be split in two parts: processing and transmission. From the data collected during the tests, we notice that the average duration of the measurement phase (collecting temperature, humidity, battery level, gas sampling, processing and log into SD-card) completes in 2.5 s with an average current consumption of 29 mA, while sleeping

Fig. 2.11 Power consumption profile of the W24TH node

Fig. 2.12 Web based user interface to represent collected data

Fig. 2.13 Picture of the extended wireless sensor network setup

the motes drains 8  $\mu$ A in average (oscillator on during sleep). Using two 2,500 mAh batteries, it is possible to reach nearly 168 weeks of autonomy in the case of 15 min interval, considering that gas sampling is not the only task to execute on the micro-controller. Of course, better autonomy performance can be achieved if the system is equipped with energy harvester devices [14–17] capable to extract and convert energy from the surroundings. Figure 2.13 shows the extended version of the environmental monitoring network, where the coordinator node has been connected to a smartphone, running Android Ice Cream Sandwich (ICS) OS. The data collected by the coordinator are then sent by USB to the smartphone, which uploads the information to the web. Figure 2.12 is a screenshot of the monitoring application's user interface.

#### 2.4 Conclusion

To extend the lifetime and energy autonomy of air monitoring devices, a new strategy of sensing have been investigated for available commercial off-the-shelf gas sensors. The approach is cheaper and faster with respect to developing a new silicon sensor-device. The results presented are straightforward with a reduction of one order of magnitude in energy consumption that has been achieved using the AS-MLK catalytic sensor for natural gas detection, by reducing the sampled interval to  $\approx 500 \ \mu s$  compared to the 5 s, at least, of the standard approach. In the near future we expect to

make a more exhaustive testing and to reduce even more the sampling period of the aerosols, to achieve an aggressive power saving strategy useful for an environmental monitoring application.

**Acknowledgments** The work presented in this paper was supported by the project *GreenDataNet*, funded by the EU 7th Framework Programme (grant n. 609000), and by the Autonomous Province of Trento within *EnerViS*—'*Energy Autonomous Low Power Vision System*' project.

#### References

- Magno, M., Tombari, F., Brunelli, D., Di Stefano, L., Benini, L.: Multimodal video analysis on self-powered resource-limited wireless smart camera. IEEE J. Emerg. Sel. Top. Circ. Syst. 3(2), 223–235 (2013)

- Varpula, A., Novikov, S., Haarahiltunen, A., Kuivalainen, P.: Transient characterization techniques for resistive metal-oxide gas sensors. Sens. Actuators B Chem. 159(1), 12–26 (2011)

- 3. Caione, C., Brunelli, D., Benini, L.: Distributed compressive sampling for lifetime optimization in dense wireless sensor networks. IEEE Trans. Ind. Inf. **8**(1), 30–40 (2012)

- 4. Xu, L., Li, T., Gao, X., Wang, Y.: A high-performance three-dimensional microheater-based catalytic gas sensor. IEEE Electron Device Lett.**33**(2), 284–286 (2012)

- Zhang, P., Vincent, A., Kumar, A., Seal, S., Cho, H.J.: A low-energy room-temperature hydrogen nanosensor: utilizing the schottky barriers at the electrode/sensing-material interfaces. IEEE Electron Device Lett. 31(7), 770–772 (2010)

- Somov, A., Baranov, A., Savkin, A., Ivanov, M., Calliari, L., Passerone, R., Karpov, E., Suchkov, A.: Energy-aware gas sensing using wireless sensor networks. In: Picco, G., Heinzelman, W. (eds.) Wireless Sensor Networks, ser. Lecture Notes in Computer Science, vol. 7158, pp. 245– 260. Springer, Berlin (2012)

- Vito, S.D., Palma, P.D., Ambrosino, C., Massera, E., Burrasca, G., Miglietta, M., Francia, G.D.: Wireless sensor networks for dis-tributed chemical sensing: addressing power consumption limits with on-board intelligence. IEEE Sens. J. 11(4), 947–955 (2011)

- Rossi, M., Brunelli, D.: Ultra low power wireless gas sensor network for environmental monitoring applications. In: 2012 IEEE Workshop on Environmental Energy and Structural Monitoring Systems (EESMS), pp. 75–81 (2012)

- Rossi, M., Brunelli, D.: Analyzing the transient response of mox gas sensors to improve the lifetime of distributed sensing systems. In:2013 5th IEEE International Workshop on Advances in Sensors and Interfaces (IWASI), pp. 211–216 (2013)

- Choi, S., Kim, N., Cha, H., Ha, R.: Micro sensor node for air pollutant monitoring: hardware and software issues. Sensors 9, 7970–7987 (2009)

- Jelicic, V., Magno, M., Brunelli, D., Paci, G., Benini, L.: A context-adaptive multimodal wireless sensor network for energy-efficient gas monitoring. IEEE Sens. J. 13(1), 328–338 (2013)

- Bhattacharyya, P., Verma, D., Banerjee, D.: Microcontroller based power efficient signal conditioning unit for detection of a single gas using mems based sensor. Int. J. Smart Sens. Intell. Syst. 3(4), (2010)

- Moser, C., Brunelli, D., Thiele, L., Benini, L.: Real-time scheduling with regenerative energy. In: 18th Euromicro Conference on Real-Time Systems (ECRTS06), 2006, pp. 261–270. DC, USA, Washington (2006)

- Dondi, D., Bertacchini, A., Larcher, L., Pavan, P., Brunelli, D., Benini, L.: A solar energy harvesting circuit for low power applications. In: IEEE International Conference on Sustainable Energy Technologies (ICSET 2008), 2008, pp. 945–949 (2008)

- Magno, M., Marinkovic, S., Brunelli, D., Popovici, E., O'Flynn, B., Benini, L.: Smart power unit with ultra low power radio trigger capabilities for wireless sensor networks. In: Design, Automation Test in Europe Conference Exhibition (DATE), 2012, pp. 75–80 (2012)

- 2 CH4 Monitoring with Ultra-Low Power Wireless Sensor Network

- D. Porcarelli, D. Brunelli, M. Magno, and L. Benini. A multi-harvester architecture with hybrid storage devices and smart capabilities for low power systems. In: 2012 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), pp. 946–951 (2012)

- Weddell, A.S., Magno, M., Merrett, G.V., Brunelli, D., Al-Hashimi, B.M., Benini, L.: A survey of multi-source energy harvesting systems. In: Design, Automation Test in Europe Conference Exhibition (DATE), 2013, pp. 905–908 (2013)

# Chapter 3 Integrated Front-end Electronics for Silicon PhotoMultiplier Readout in Medical Imaging Applications

Nahema Marino, Sergio Saponara, Luca Fanucci, Federico Baronti, Roberto Roncella, Francesco Corsi, Cristoforo Marzocca, Gianvito Matarrese, Fabio Ciciriello, Francesco Licciulli, Maria Giuseppina Bisogni and Alberto Del Guerra

**Abstract** The 4D-MPET project aims to design a positron emission tomography detection module capable of working inside a magnetic resonant imaging system. The proposed detector will feature a three-dimensional architecture based on two tiles of silicon photomultipliers coupled to a single LYSO scintillator on both its faces. Silicon photomultipliers are magnetic-field compatible photo-detectors with a very small size enabling novel detector geometries that allow the measurement of the depth of interaction. Furthermore they can be fabricated using standard silicon technology, have a large gain in the order of 106 and are very fast thus allowing evaluating the time of flight. Based on custom integrated circuits, the readout electronics include an innovative current mode front-end coupled to a novel time to digital converter. The former, implemented in AMS 0.35 µm SiGe-BiCMOS technology, features a very low input impedance (17  $\Omega$ ) current buffer and a large bandwidth (1 GHz), which lead to a time resolution of  $\sim 100$  ps FWHM. The time to digital converter exploits the combination of a submicron technology (UMC 65 nm LLLVT) together with a systolic topology so as to work at a high frequency of 2.5 GHz. This yields to a nominal time resolution of 29 ps ( $\sigma$ ) whereas the photon energy is evaluated with a bin size of 400 ps by using a time over threshold technique. Finally, the depth of interaction measurement is performed by an external FPGA with a simulated spatial resolution of 1.3 mm FWHM along the z coordinate.

M. G. Bisogni · A. Del Guerra Dip. di Fisica-Università di Pisa and INFN Sez. Pisa, Largo Bruno Pontecorvo 3, 56127 Pisa, Italy

N. Marino (🖾) · S. Saponara · L. Fanucci · F. Baronti · R. Roncella

Dip. di Ing. dell'Informazione-Università di Pisa and INFN Sez. Pisa, Via Caruso 16, 56122 Pisa, Italy

e-mail: nahema.marino@iet.unipi.it

F. Corsi · C. Marzocca · G. Matarrese · F. Ciciriello · F. Licciulli Dip. di Ing. Elettrica e dell'Informazione-Politecnico di Bari and INFN Sez. Bari, Via Orabona 4, 70125 Bari, Italy

A. De Gloria (ed.), *Applications in Electronics Pervading Industry, Environment and Society*, Lecture Notes in Electrical Engineering 289, DOI: 10.1007/978-3-319-04370-8\_3, © Springer International Publishing Switzerland 2014

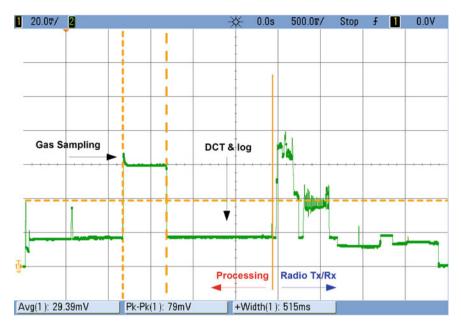

#### **3.1 Introduction**

Positron emission tomography (PET) is a molecular imaging technique that provides images of physiological processes inside the body. After decay of a radiotracer injected into the tissues, a positron is released which annihilates with an atomic electron thus producing two 511 keV photons (event). These pairs of gamma rays are emitted in almost exactly opposite directions within the PET scanner, as depicted in Fig. 3.1. Coincidence detection of the two photons is exploited to provide projection data used for image reconstruction. In clinical applications, PET image quality benefits from the time of flight (TOF) feature which is given by the difference in the arrival time of the two photons on the detectors of the PET ring. This information is used to estimate the position of the annihilation point along the line connecting the centres of the two detectors (LOR) thus enabling the reconstruction algorithm to provide the final image with fewer iterations and less image noise [1]. It has been shown that the quality benefits of TOF increase when increasing the time resolution for large size objects [2]. Thus, high speed electronics are required for the TOF measurement. However, although a single imaging modality can offer some insight into a disease process, in many circumstances the combination of both the morphological and functional information eventually provides a better diagnosis and prognosis. In this scenario, the innovative combination of PET with magnetic resonance imaging (MRI) within a hybrid facility offers better contrast in soft tissues (i.e. human brain) with respect to scanners where PET is coupled to computer tomography (CT) [3]. Furthermore, hybrid systems address most of the problems related to separate multimodality imaging, where PET and MRI images are software fused, such as different patient positioning on the couch, involuntary movement of internal organs and artefacts due to the fusion techniques [4, 5].

The implementation of TOF PET/MRI systems require innovative detector layouts featuring dedicated front-end designs. In this scenario, the use of SiPM coupled to fast electronic readout is fundamental to achieve good performance in terms of time and spatial resolution thus enabling the implementation of the TOF technique. Indeed, these solid state photo-sensors are MR-compatible and combine the advantages of both Photomultiplier Tubes (PMT), such as high gain and total quantum efficiency (QE), and Avalanche Photodiodes (APD), like the small dimensions which permits extremely compact, light and robust mechanical design.

The 4D-MPET (4 Dimensions Magnetic compatible module for Positron Emission Tomography) INFN project collaboration aims to develop a magnetic-field compatible TOF PET module with good spatial, time and energy resolution. To this end, innovative readout electronics are being developed to be combined with novel scintillator materials and high performing photodetectors.

The proposed TOF PET/MRI module is based on the combination of a single LYSO scintillator crystal coupled to SiPMs which allow a high precision in the determination of the (x, y) coordinates of the hits on the detector. Both the arrival time and the energy of the events are measured by integrated readout electronics.

Fig. 3.1 Schematic representation of PET

The detection module will also take advantage from the depth of interaction (DOI) feature related to the z coordinate of the gamma rays inside the crystal. Indeed, this information reduces the parallax error in the determination of the LOR [6].

#### 3.2 Readout of the TOF PET/MRI Module

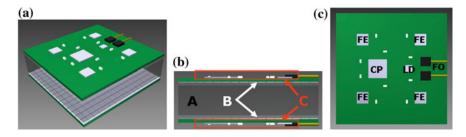

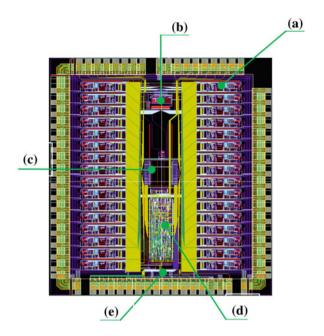

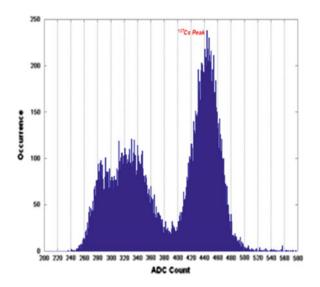

In Fig. 3.2 the block layout is depicted [7]. The LYSO scintillator slab (A in Fig. 3.2b) has a size of  $48 \times 48 \times 10$  mm<sup>3</sup>; spatial resolution optimization is achieved by painting the side faces of the crystal black. A SiPM layer is laid out both on the top and at the bottom of the scintillator (B in Fig. 3.2b). The detector matrices feature  $16 \times 16$  square pixels with 3 mm pitch and a microcell size of 50 µm, developed by FBK-irst (Trento, Italy [8]). Each pixel is read out by independent and identical multiple-channel electronics (C in Fig. 3.2b). Each board features several electronic blocks as shown in Fig. 3.2c: (1) four front-end (FE) application-specific integrated circuits (ASIC), each featuring 64 channels, for time and energy measurement; (2) a cluster processor (CP) ASIC for data reduction; (3) a laser driver/photodiode receiver/clock reconstruction (LD) ASIC for communication with an external data acquisition system through optical fibres (OF). Communication among ASICs is based on low voltage differential signalling (LVDS) pads for magnetic field compatibility. The electronics have to be mounted and wire-bonded without package; encapsulation for protection and top-side contact cooling will be performed after test. Given the SiPM jitter of 60 ps [9], a time resolution less than  $\sigma = 100$  ps must be reached to implement the TOF technique. Such resolution can be achieved by triggering events at a low threshold (TH<sub>low</sub>), which corresponds to the first emitted photoelectron so as to measure the interaction time within the crystal with high accuracy. However, the high SiPM dark noise of

Fig. 3.2 Block detector layout: three dimensional view (a), side view (b) and top view (c)

$\sim$ 2 MHz/mm<sup>2</sup> at room temperature (dark count for SiPMs manufactured by FBK-irst at the selected operating V<sub>bias</sub>) requires the additional use of a validation threshold TH<sub>high</sub> (corresponding to a programmable number of emitted photoelectrons) to discriminate events from noise as in a double threshold technique.

Simulations have shown that a resolution of  $\sigma = 102$  ps can be achieved [10]. Once a valid event has been detected, the system translates the relevant timestamp into a digital word by a converter and evaluates the associated energy by exploiting a time over threshold (TOT) technique. The best IC implementation of the discussed double threshold technique can be implemented with the aid of two different CMOS technologies. Therefore, the FE ASIC has been split up into two separated chips which communicate with each other: a current-mode (CM) ASIC which converts all SiPM analogue outputs into digital pulses and a time to digital converter (TDC) which provides both TOF and TOT information of valid pulses only. Furthermore, both clustering and DOI evaluation techniques are being examined on an external FPGA before moving to the CP ASIC implementation.

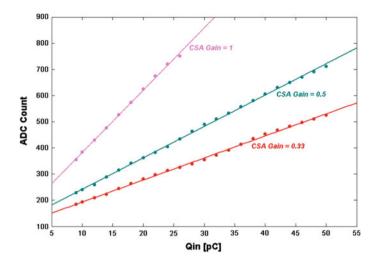

#### 3.2.1 Current Mode ASIC

The readout circuitry of the TOF PET module is based on a current-mode ASIC with low input impedance, fast current buffer as very first detector front-end [11]. Such architecture is implemented in AMS 0.35  $\mu$ m SiGe-BiCMOS technology featuring both MOSFET and fast HBT bipolar transistors. This allows achieving a time resolution of ~100 ps FWHM given the very low input impedance (17  $\Omega$ ) of the current buffer which leads to a short time constant even when combined with the large SiPM capacitive load. Furthermore, a wide bandwidth of about 1 GHz ensures a very short rise time of the response, which limits the jitter due to noise. Power consumption is also controlled at reasonable values, thanks to the large transconductance/current ratio offered by the fast HBT bipolar transistors.

The CM ASIC reads out the SiPM output current and translates it into a digital pulse whose rise edge timestamp represents the arrival time of the signal (TOF data) whereas the fall edge timestamp provides its energy information (TOT data).

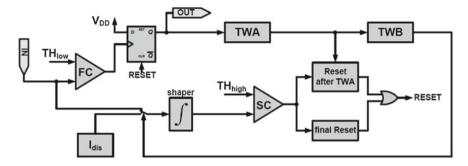

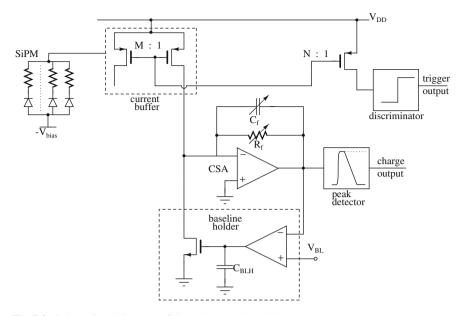

Fig. 3.3 Block diagram of the CM ASIC

Figure 3.3 shows the block diagram of the CM ASIC. At the input of the circuit, a SiPM output signal is compared with the low threshold  $TH_{low}$  by a fast comparator (FC). As soon as the input goes over  $TH_{low}$ , the FC sets a flip-flop which in turn triggers a counter labelled as Time Window A (TWA).

At the same time a shaper starts integrating the input so that its output, which feeds a slow comparator (SC), increases from zero. When TWA expires, the system evolves towards two different statuses according to the value of the SC output. If it is 0, the SiPM signal is recognized as noise because the shaper output is below the validation threshold (TH<sub>high</sub>); the circuit resets itself and a digital pulse with duration of TWA is produced at the circuit output. If it is 1, a second counter labelled as Time Window B (TWB) is triggered and the shaper keeps on integrating the SiPM output; when TWB expires the shaper is discharged through a constant current thus decreasing its output. As soon as the shaper output goes below TH<sub>high</sub> the circuit resets itself. The circuit outputs a digital pulse having duration of TWA plus TWB plus the time required by the shaper to be discharged: this time is proportional to the energy associated to the event and thus it represents the TOT information. It follows that the rising edge of a valid pulse provides the timestamp information (TOF) whereas the trailing edge contains the energy data.

The non-linear, constant current discharge mechanism of the charge integrated during TWA and TWB eliminates any constraint on the stability and uniformity of the SiPM pulse and relaxes precision requirements in the TDC for the TOT measurement, while preserving a good linearity. For calibration issues the counters TWA and TWB will be programmable within the time intervals (6–30) and (50–120) ns, respectively. Thus, in the event of noise, the CM ASIC outputs a short pulse which can be easily distinguished from valid data by the TDC ASIC.

# 3.2.2 Time to Digital Converter ASIC

The digital outputs of the CM ASIC are forwarded to the TDC ASIC which measures and digitizes both the TOF and TOT data of the events and neglects noise pulses. Time

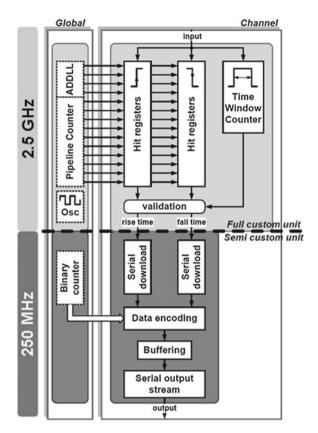

Fig. 3.4 Block diagram of the time to digital converter ASIC

to digital converters are electronic components which quantize small time differences between two signals (referred to as start and stop) and provide a digital representation of this time interval [12]. Technology progress, increased integration level capability and working speed have led to significant improvements in the time measurement performance. Some examples involve the time resolution [13], linearity [14], dynamic range [15], power consumption [16] and low process-voltage-temperature (PVT) variations [17] of the converter. The operation of a TDC is very similar to that of analogue to digital converters (ADC) although the former deals with the time difference rather than voltage or current differences. The measured time is evaluated as the phase difference between the positive edges of the start and stop signals. Thus, the input is defined in the continuous time domain whereas the output is expressed in digital form.

The proposed TDC has been implemented in UMC 65 nm CMOS technology and its block diagram is reported in Fig. 3.4. Here, two sections can be distinguished: a full custom unit which has been designed at transistor level and represents the core of the converter, and a semi custom unit that is based on standard cells for data management.

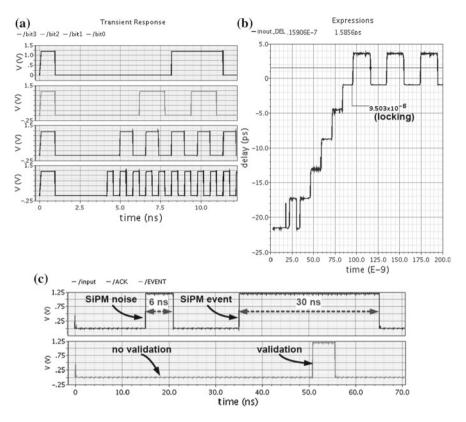

The TDC core is based on a pipeline architecture where local communication between adjacent cells arranged in a systolic array is exploited to implement any logic function with almost no frequency dependency. In systolic arrays, computations are performed simultaneously in all processing elements (referred to as systolic cells), while data travel from cell to cell, so that parallelism is exploited by partitioning the computation effort over the array elements [18]. In addition, working at high frequencies makes it possible to exploit master-slave dynamic flip flops to implement the systolic cells. Here, parasitic capacitances are used as data storage units and logic functions can be obtained with a smaller number of devices when compared to static logics, thus saving silicon area. These characteristics make this approach suitable to applications where multichannel feasibility is required. The proposed TDC makes use of a 10 bit systolic counter [19, 20] working at 2.5 GHz that provides a timestamp T<sub>coarse</sub> of 400 ps for the TOT measurement. The counter is coupled to a 4 stages delayed locked loop (DLL) which leads to a timestamp T<sub>fine</sub> decreased down to 100 ps to evaluate the TOF data. This corresponds to a theoretical time precision ( $\sigma$ ) of 29 ps which would satisfy the system requirements for the TOF feature. Moreover, the reduced number of delay elements in the DLL is promising in terms of linearity which is fundamental in one shot measurements as for PET. In Fig. 3.5a, the counter bits from b3 to b0 are depicted: it can be noticed that each bit is updated with one clock delay with respect to the previous one because of the pipeline latency. Figure 3.5b shows the behavior of the DLL until it locks to the input clock.

In order to implement a fully synchronous design, the 2.5 GHz system clock is provided by a configurable ring oscillator (RO). The RO is based on 4 tunable inverters where 8 digitally controlled varactors [21] serve as externally configurable load so that the oscillation frequency can be changed by the user with a resolution of 1 % per bit with respect to the central frequency in typical conditions. A fifth inversion is then provided by a NAND gate that receives an external enable signal. The DLL delay units have been designed with a configuration similar to that employed for the RO elements in order to guarantee the achievement of the locking condition between the DLL and the oscillator in any working condition.

The 10 bit systolic counter along with the DLL and the ring oscillator are global blocks inside the TDC and feed 8 readout channels that are accommodated within the same chip. In each channel, two clusters of pipeline hit registers are used: one group is in charge of sampling both the counter and the DLL digits in correspondence to the rise edge of the inputs sent by the CM ASIC. Another cluster samples the counter bits only in order to perform the fall edge measurement with a timestamp of  $T_{coarse}$ . In addition, a dedicated programmable systolic counter (Time Window Counter in Fig. 3.4) evaluates the width of the channel inputs so as to discard noise pulses without impairing the acquisition capability of the system. Indeed, a validation algorithm is implemented in each channel which allows for a correct data sampling even in the presence of a high noise rate. Figure 3.5c shows an example of both input discard and validation conditions by means of the Time Window Counter with an input width threshold set to 12.8 ns and assuming that the noise pulses sent from the CM ASIC are 6 ns large.

Fig. 3.5 Systolic counter output bits from b3 to b0 (a); evolution of the DLL behavior from the start to the locking condition (b); example of the input validation performance of the Time Window Counter (c)

The recorded timestamp and energy information are collected at 250 MHz by the semi custom unit with a double hit resolution of 170 ns. Here, an 18 bit binary counter is exploited to extend the TOF dynamic range to 1.048 ms. Each time validation is provided by the Time Window Counter, TOF and TOT bits are serially downloaded and stored in 4 word deep FIFOs after encoding. Finally, a 47 bit word is serially sent out to an FPGA for backend image signal processing.

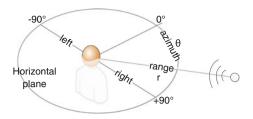

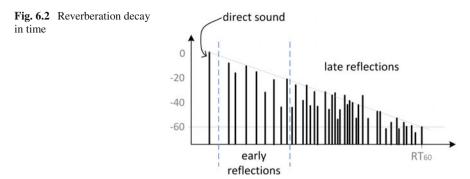

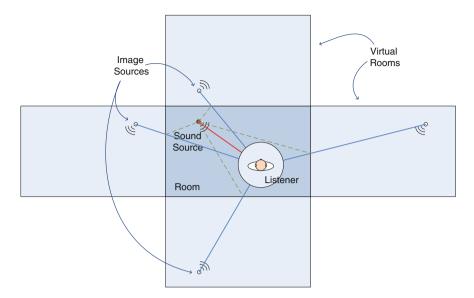

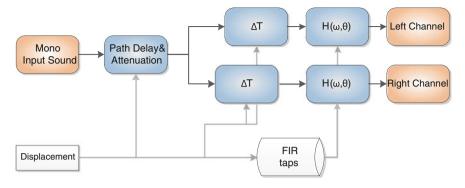

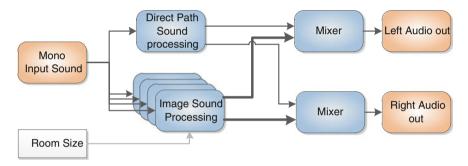

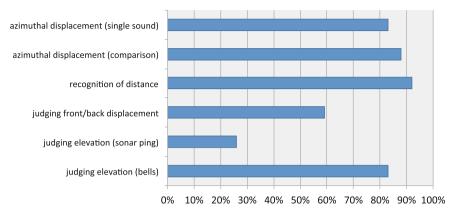

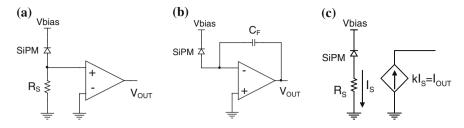

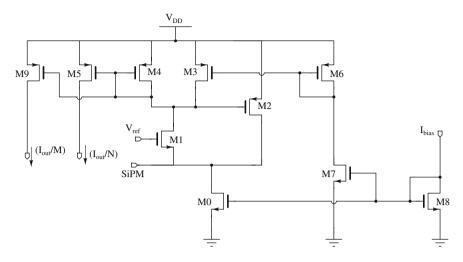

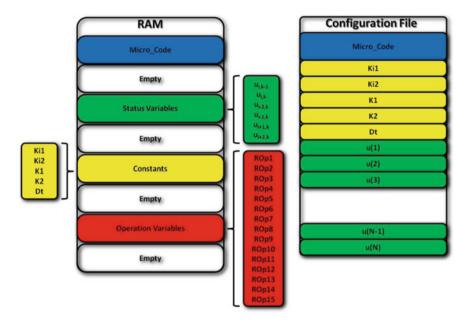

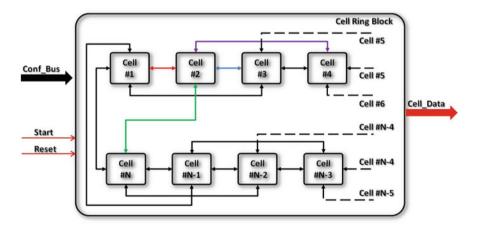

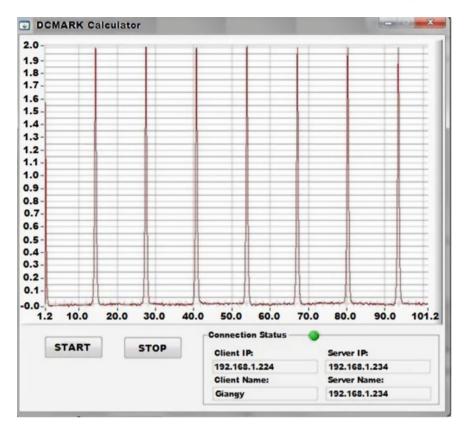

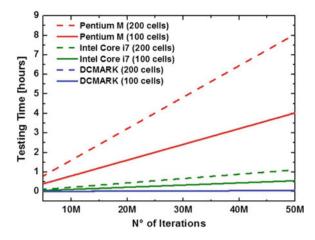

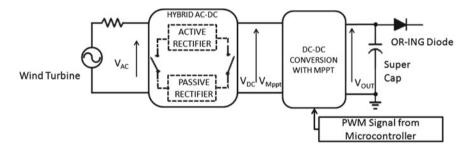

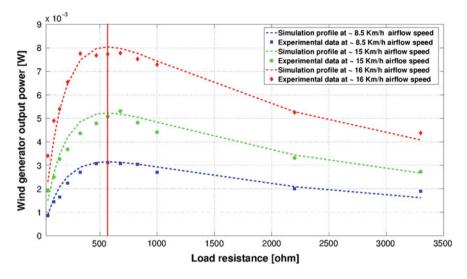

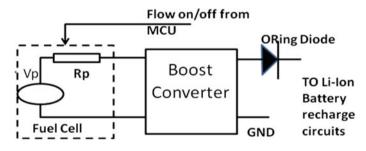

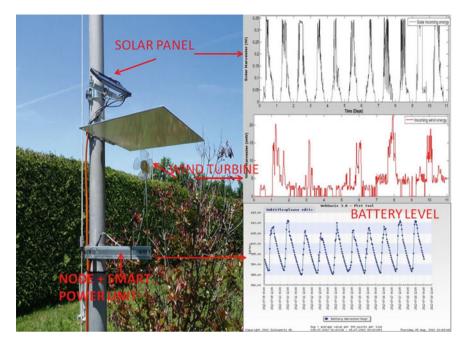

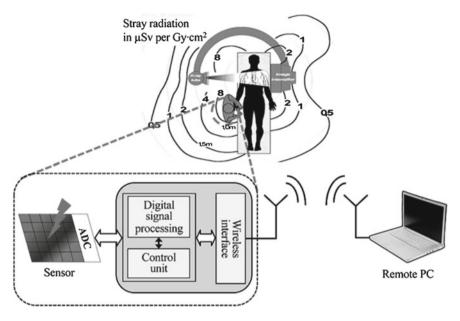

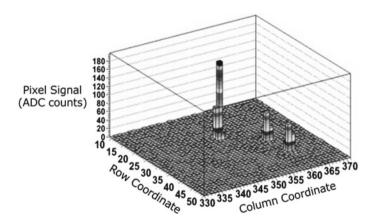

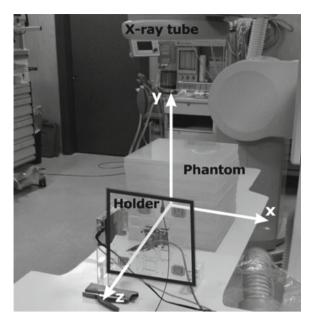

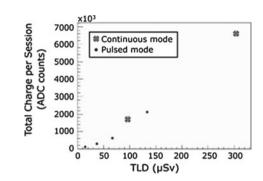

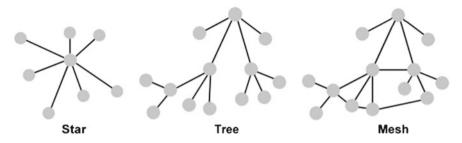

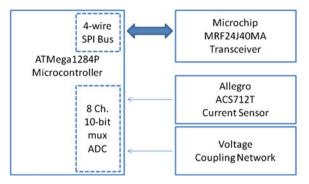

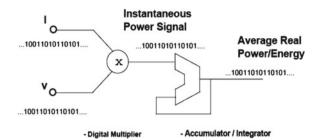

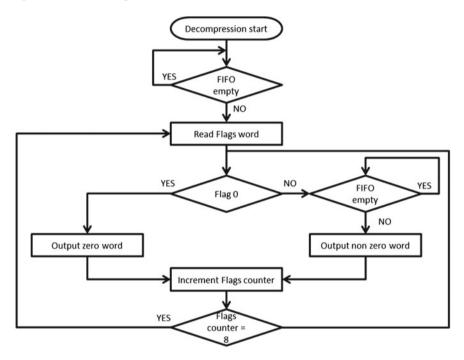

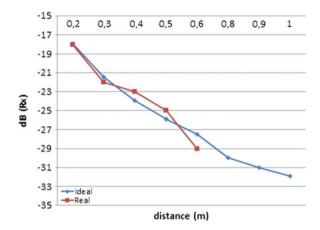

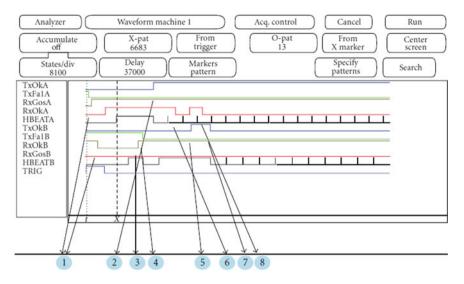

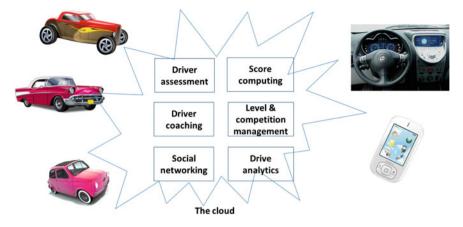

### 3.2.3 Clustering and Other Features