# Francesca lacopi Francis Balestra *Editors*

# More-than-Moore Devices and Integration for Semiconductors

More-than-Moore Devices and Integration for Semiconductors

Francesca Iacopi • Francis Balestra Editors

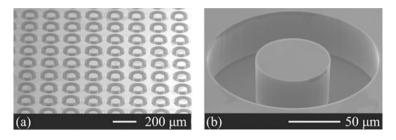

# More-than-Moore Devices and Integration for Semiconductors

Editors Francesca Iacopi D Australian Research Council Centre of Excellence in Transformative Meta-Optical Systems (TMOS) University of Technology Sydney Ultimo, Australia

Francis Balestra D Univ. Grenoble Alpes, CNRS, Grenoble INP, IMEP-LAHC Grenoble, France

ISBN 978-3-031-21609-1 ISBN 978-3-031-21610-7 (eBook) https://doi.org/10.1007/978-3-031-21610-7

© The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Switzerland AG 2023

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### Preface

#### Introduction

The term "More-than-Moore" appeared and was readily adopted by the semiconductor community since the early 2000s, when, in addition to the decades-long focused effort to scale down the footprint of logic and memory devices according to the wellknown Moore's Law, an orthogonal trend in electronics miniaturisation had started to gain momentum.

In contrast to the aggressive pursuit of increasingly more powerful computing led by Moore's Law (More Moore), the More-than-Moore trend focuses on the combination of an increasing number of functionalities within a miniaturised system [1]. One of the main application drives for More-than-Moore had clearly been the pursuit of smart portable systems, with smartphones being one of the consumer applications spearheading this new trend. While smart portable devices in the late 1990s and early 2000s were still at a very early stage of development, mainly focused on mobile computing functionalities such as palm-sized PCs and using rudimentary connectivity and awkward user interfaces, the launch of the first Apple iPhone model – among the first wave of truly multifunctional portable smartphones, precursor to today's ubiquitous technologies - took place not too long afterwards, in 2007. The opportunity for such an extraordinary leap of smart systems with increasing complexity, number of functionalities and autonomy, all within an increasingly small form factor (More-than-Moore trend), has originated out of the simultaneous convergence of several key technologies, including the evolution of the following:

- 1. Mobile communications, particularly digital cellular networks, also thanks to the development of ICs for wireless communications, including power MOSFET and RF ICs.

- Integrated power sources and energy-harvesting systems, key to ensuring autonomy.

- 3. Low-power ICs, specifically developed for mobile applications.

- 4. User interfaces such as advanced touchscreen technologies.

5. The availability of an increasing number of miniaturised functionalities, starting from the historically more advanced ones, such as digital CMOS cameras, MEMS technologies for sensors and actuators (loudspeakers, microphones, gyroscopes, etc.) and optoelectronics (LEDs, etc.)

More-than-Moore technologies have been taken into account in recent years in several International Roadmaps, in particular the NanoElectronics Roadmap for Europe (NEREID, [2]) and the IEEE International Roadmap for Devices and Systems (IRDS, [3]). While silicon technologies still play an absolutely central role, with many of the complementary functionalities to logic and memory still often using silicon as key material (MEMS, digital cameras, photonics, power, etc.), the emphasis of More-than-Moore is not so much on the miniaturisation of the single components as in the More Moore digital technologies, but rather on the miniaturisation and the improvement of the multifunctional system performance as a whole.

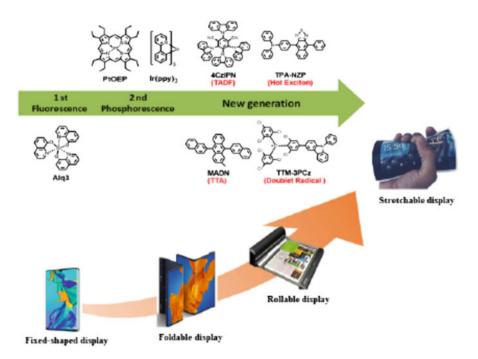

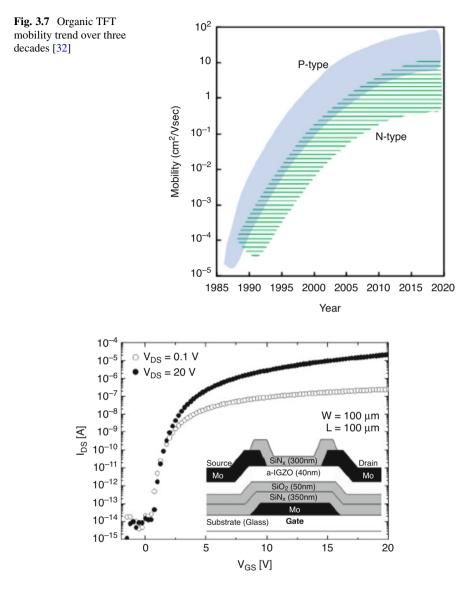

In addition, where alternative semiconductors to silicon are undoubtedly performing better than silicon, such as in optoelectronics, power and flexible electronics, new semiconductor technologies – from III–V to organic – are also being introduced and brought up fast to fabrication capabilities at scale either in combination with or complementary to silicon technologies [4–7]. This also means that we are seeing an increasingly more complex array of new semiconductors being brought onto a silicon fabrication platform, or different substrates to silicon being combined into the same system through advanced packaging.

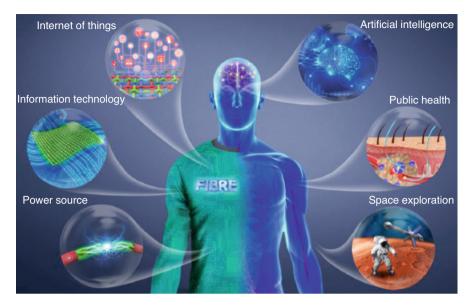

An additional application drive for More-than-Moore technologies has undoubtedly been the rise of the Internet of Things, or Internet of Everything [8]. IoT usually refers to interconnected "smart" sensing nodes which could be serving any aspect from traffic to air and water quality, to healthcare, energy and manufacturing automation, as well as to a plethora of consumer applications.

Although the concept of IoT had already been discussed as early as the 1990s [9], it is not until approximately a decade later that this concept developed practically over a large scale, supported by the progress in the 1–5 technologies above, but also importantly supported by the advances in AI and Big Data analytics [10].

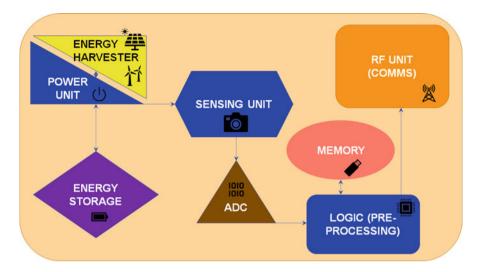

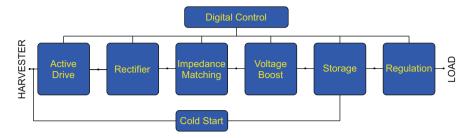

The schematic in Fig. 1 depicts a typical IoT node and its functionalities. The note would be generally built around a generic sensing unit, which represents a very broad range of potential sensing technologies (MEMS, optical, etc.) and specific applications. It would typically include an analog-to-digital converter (ADC) and potentially some embedded logic and memory, performing more or less extensive pre-processing operations on the acquired data. The processed data are then transmitted wirelessly to another node through the RF unit, which will include an appropriate antenna. Finally, another key component of an IoT node is the power unit and integrated power sources.

Depending on the projected consumption of the IoT node and the desired level of autonomy, the hardware needs for power can vary extensively, particularly in terms of power sources. Power considerations are in fact a key aspect for Morethan-Moore technologies and an important theme of this book discussed in Chaps.

Fig. 1 Simplified diagram representing the typical units and components required in a smart node of the Internet of Things

1 and 2. Additional specific units may be required beyond what depicted in Fig. 1, depending on the sensing purpose of the specific IoT node.

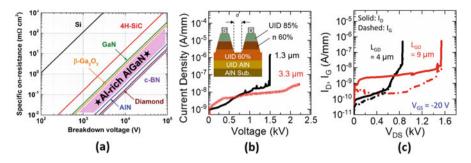

IoT has generated a strong push for a further level of required miniaturisation and autonomy of multifunctional systems. Extreme miniaturisation allows for cutting-edge applications for example in healthcare – see ingestible sensors able to monitor the health of the gut with wireless transmission capabilities [11], only one of the endless possibilities offered by miniaturised, autonomous systems. Smart sensor nodes have also strongly driven the necessity for uninterrupted autonomous power, which in turn has also led to the development of efficient in-situ miniature storage such as microbatteries [12] and miniaturised supercapacitors [13], but also to ambient energy harvesting systems, as explained by Yeatman in Chap. 1. The importance of the further development and convergence of power harvesting, storage and management technologies for Moore-than-Moore systems cannot be overstated. The extraordinary recent advances made in power electronics using wide band-gap materials are therefore extremely welcome news, as explained by Zekentes et al. in Chap. 2.

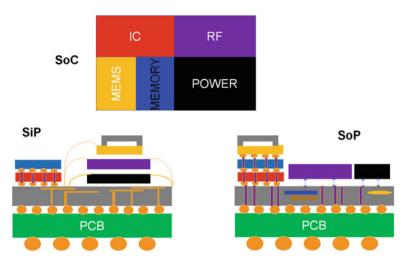

Additional key enablers of the further progress of More than Moore are heterogeneous integration and advanced packaging. Over the last decades, as the complexity of integrating different semiconductors, functionalities and technology nodes within the same chip has reached higher complexity, the system-on-chip (SoC [14], Fig. 2) trend has been slowing down as heterogeneous integration through advanced packaging has been expanding and greatly diversifying to cater for the numerous different technology combinations (see also the IEEE Heterogeneous Integration Roadmap, HIR [15]). While it would be difficult to provide an exhausting description of the plethora of relevant advanced packaging technologies available, it is

Fig. 2 Schematic depicting different system integration strategies, such as system-on-chip (SoC), and advanced packaging approaches such as system-in-package (SiP) and system-on-package (SoP)

useful to consider those enabled by the through-silicon-vias (TSV) technology, in particular the system-in-package (SiP) and system-on-package (SoP). They both aim at greatly reducing the footprint of a heterogeneous system by making use of silicon as either as a mostly passive interposer, connecting chips or "tiles" with different functionalities with much reduced pitch as compared to a PCB board (2.5D integration, [14]), or using active silicon chips to connect chips stacked in the vertical direction, also called 3D integration [14], respectively. These approaches are depicted in Fig. 2. The main aim would be to contain the whole system in a single package hence dramatically reducing the system footprint, although this may not always be possible because of specific packaging requirements for example for sensing chips, which may need to have access to the ambient to perform their functions [16] or other restrictions.

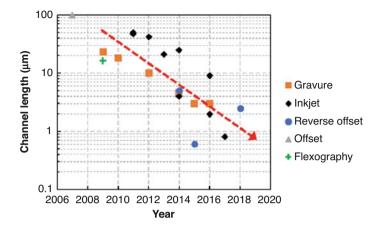

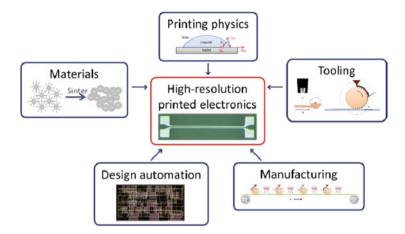

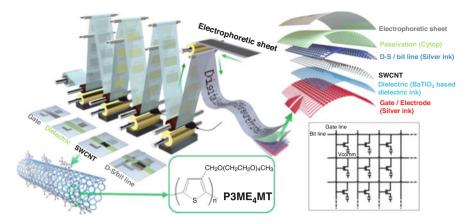

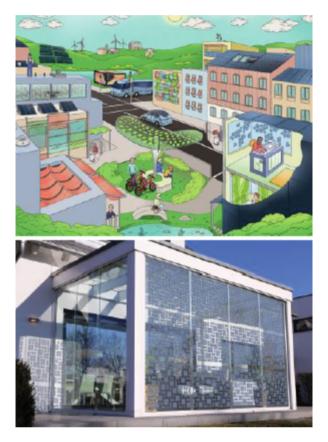

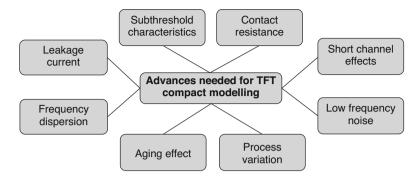

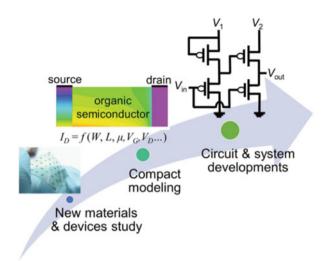

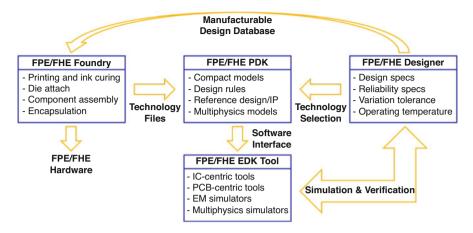

Further, there are several other trends in advanced packaging that are expected to deliver major contributions for More-than-Moore technologies. One is the "chiplets" or "dielets" route, which allows to combine two chips with an extreme pitch and is also currently providing a boost to logic chips [17]. Another important example, which represents a departure from a fully rigid silicon-based package, is the flexible hybrid electronics [18]. This approach is going to be particularly favourable when considering system integration for wearables, allowing for the most advanced logic to be combined in the same system with flexible technologies based on organic and or printed electronics, including 3D-printed components such as antennas and filters [19]. The rise of flexible electronics and the advanced combination of rigid and flexible are key aspects of More-than-Moore for smart sensing, as explained by Iniguez in Chap. 3.

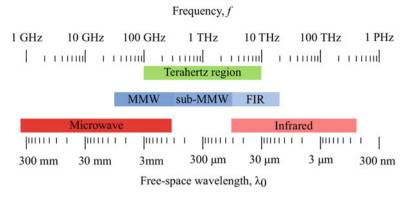

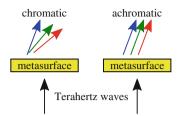

The rapid evolution and versatility of advanced packaging enables electronics, and particularly More-than-Moore integration, to keep bringing more and more complementary technologies and functionalities, as they become available, under a single package. In particular, the advancement of miniaturised photonics is primed to advance particular areas of computing, including quantum, as well as interconnects and sensing [20, 21]. The advent of metamaterials and metasurfaces [22] has also opened the door to a long awaited, dramatic miniaturisation of optical components by using semiconductor materials and processing, which could lead to unprecedented functionalities that include the vastly underexploited THz gap in electromagnetic radiation, as explained by Atakaramians et al. in Chap. 4.

Undoubtedly, heterogeneous integration has grown increasingly complex in recent times, opening new fabrication and reliability frontiers which still need to be completely settled and addressed.

In particular, the appearance of silicon effectively as a packaging material with the TSV technology has created divergent views of ownership and handshake between silicon fabs and outsourced semiconductor assembly and test (OSAT) companies, which have been debated for almost a decade. This, together with the additional reliability challenges caused by the combination of vastly different technologies – very different materials, with mismatched properties like CTE, elastic modulus, lattice constants and different thermal stabilities, and not as extensively known as silicon, different technology nodes, different packaging needs – serving the broad range of required functionalities, has made More-than-Moore integration an area potentially as challenging as that of Moore's scaling.

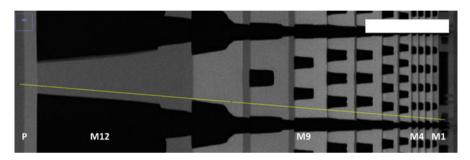

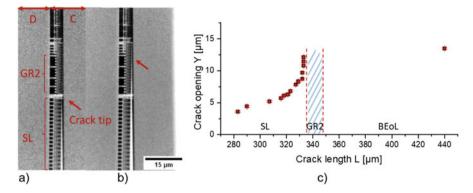

Reliability is hence a key issue in More-than-Moore integration [23]. This book puts specific emphasis on mechanical reliability, more specifically fracture mechanisms, failure modes and their inspection and mitigation strategies (Chap. 5 by Zschech and Elizalde). Mechanical reliability is one very challenging aspect of such integrated systems, in addition to electrical reliability as well as thermal reliability, which still strongly limits the deployment of 3D integration to this date, due to the lack of an efficient heat removal technology [24, 25].

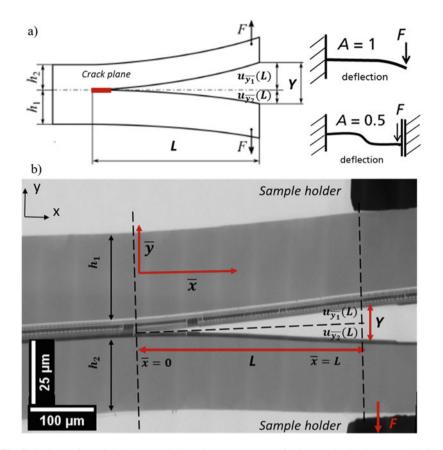

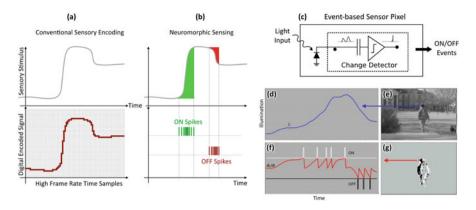

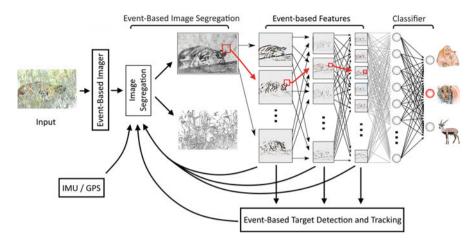

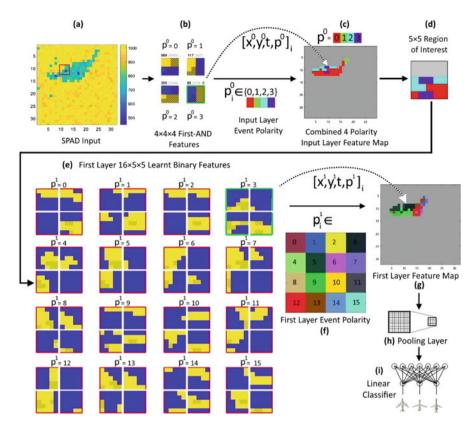

Finally, in this book we wanted to provide some tangible examples where More-than-Moore technologies are going to play an increasingly important role in enabling advanced integrated capabilities able to take full advantage of the sustained advances in artificial intelligence (AI). Chapter 6 by Delic and Afshar explains how advanced 3D packaging of advanced photonics, optoelectronics and CMOS-based neuromorphic computing can enable a portable navigation system based on event-driven imaging (LiDAR). The future development of truly neuromorphic hardware is expected to further enable autonomous miniaturised systems for low-latency, highly accurate event-driven AI operations, achieving powerful intelligent systems with minimal energy consumption.

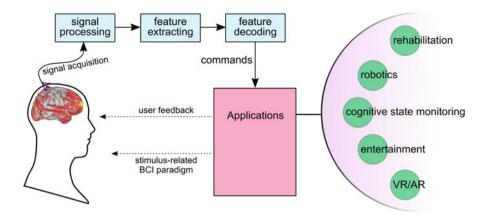

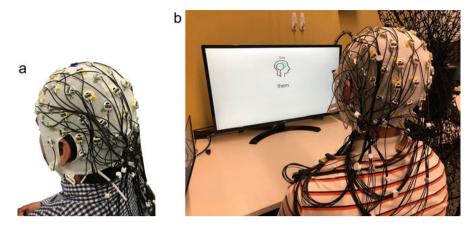

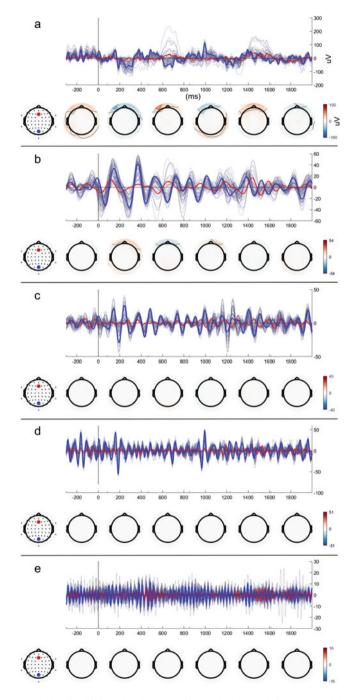

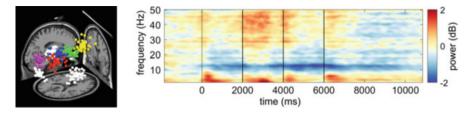

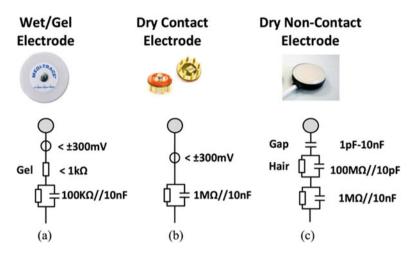

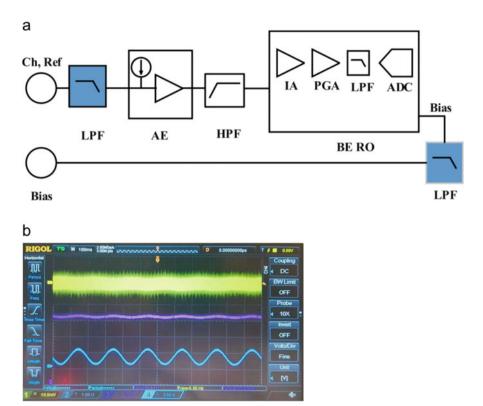

Chapter 7 by Do, Duong and Lin, provides a snapshot into how our interaction with such a smart system could look like, thanks to brain-computer interfaces (BCIs) and AI. This aspect has a dual meaning, as it opens the door to a different way for humans to interact with electronic machines and smart systems, while also

explaining how miniaturised technologies and the integration offered by More-than-Moore could advance non-invasive sensing for BCIs.

As neural interfaces, neuromorphic computing, wearable technologies, integrated power sources and integrated photonics advance further, it is clear to see what the next paradigm shift enabled by More-than-Moore integration is likely going to be. Human-computer integration [26] is going to change completely the way we interact with electronic systems, and perhaps it is going to make the demarcation line between the biological parts and electronic extensions of a human being somewhat ambiguous. In other words, More-than-Moore integration is going to be at the core of the latest generation of the Internet of the Bodies [27], where human bodies and their technological extensions, both wearable or internal/implanted, will appear seamlessly integrated – be it different types of sensors, of communication interfaces, smart prosthetic devices [28], advanced pacemakers, artificial organs [29] and other forms of technological replacement or augmentation of the biological functions of the human body.

We hope this book will make a useful and inspirational reading for academics, professionals, as well as for students in a wide range of technical disciplines.

#### Acknowledgements

We would like to thank the following colleagues for their help in peer-reviewing this book's material: Dr. Yang Yang and Dr. Diep Nguyen (University of Technology Sydney, Australia); Prof. Xuan-Tu Tran (Vietnam National University Hanoi), Prof. Gustavo Ardila and Prof. Pascal Xavier (University Grenoble Alpes, France); and Prof. Edwige Bano (Grenoble INP, France). FI would also like to acknowledge support from the Australian Research Council Centre of Excellence in Transformative MetaOptical Systems (TMOS, CE200100010).

Ultimo, NSW, Australia Grenoble, France Francesca Iacopi Francis Balestra

#### References

- G.Q. Zhang, M. Graef, F.V. Roosmalen, The rationale and paradigm of "more than Moore", in 56th Electronic Components and Technology Conference 2006, (2006), pp. 151–157. https:// doi.org/10.1109/ECTC.2006.1645639

- 2. NEREID | NanoElectronics Roadmap for Europe: Identification and Dissemination. https://www.nereid-h2020.eu/. Accessed 25 Aug 2022

- IEEE International Roadmap for Devices and Systems IEEE IRDS. https://irds.ieee.org/. Accessed 25 Aug 2022

- L. Basiricò, G. Mattana, M. Mas-Torrent, Editorial: Organic electronics: Future trends in materials, fabrication techniques and applications. Front. Phys. 10, 888155 (2022). https:// doi.org/10.3389/fphy.2022.888155

- F. Iacopi, M. Van Hove, M. Charles, K. Endo, Power electronics with wide bandgap materials: Toward greener, more efficient technologies. MRS Bull. 40(5), 390–395 (2015). https:// doi.org/10.1557/mrs.2015.71

- M. Tang et al., Integration of III-V lasers on Si for Si photonics. Prog. Quantum Electron. 66, 1–18 (2019). https://doi.org/10.1016/j.pquantelec.2019.05.002

- P.J. Wellmann, Review of SiC crystal growth technology. Semicond. Sci. Technol. 33(10), 103001 (2018). https://doi.org/10.1088/1361-6641/aad831

- D.J. Langley, J. van Doorn, I.C.L. Ng, S. Stieglitz, A. Lazovik, A. Boonstra, The internet of everything: Smart things and their impact on business models. J. Bus. Res. 122, 853–863 (2021). https://doi.org/10.1016/j.jbusres.2019.12.035

- M. Weiser, The computer for the 21st century. Sci. Am. 265, 94–104 (1991). https://doi.org/ 10.1038/scientificamerican0991-94

- E. Ahmed et al., The role of big data analytics in internet of things. Comput. Netw. 129, 459–471 (2017). https://doi.org/10.1016/j.comnet.2017.06.013

- K. Kalantar-zadeh, N. Ha, J.Z. Ou, K.J. Berean, Ingestible sensors. ACS Sens. 2(4), 468–483 (2017). https://doi.org/10.1021/acssensors.7b00045

- Z. Zhu et al., Recent advances in high-performance microbatteries: Construction, application, and perspective. Small 16(39), 2003251 (2020). https://doi.org/10.1002/smll.202003251

- J. Liang, A.K. Mondal, D.-W. Wang, F. Iacopi, Graphene-based planar microsupercapacitors: Recent advances and future challenges. Adv. Mater. Technol. 4(1), 1800200 (2019). https:// doi.org/10.1002/admt.201800200

- 14. R.R. Tummala, M. Swaminathan, *Introduction to System-On-Package (SOP) : Miniaturization* of the Entire System (McGraw-Hill, New York, 2008)

- Heterogeneous Integration Roadmap | SEMI. https://www.semi.org/en/communities/ heterogeneous\_integration\_roadmap. Accessed 25 Aug 2022

- M. Chiao, Y.-T. Cheng, L. Lin, Introduction to MEMS packaging, in *Microsystems and Nanotechnology*, ed. by Z. Zhou, Z. Wang, L. Lin, (Springer Berlin Heidelberg, Berlin, Heidelberg, 2012), pp. 415–446

- P. Gupta, S.S. Iyer, Goodbye, motherboard. Bare chiplets bonded to silicon will make computers smaller and more powerful: Hello, silicon-interconnect fabric. IEEE Spectr. 56(10), 28–33 (2019). https://doi.org/10.1109/MSPEC.2019.8847587

- S.S. Iyer, A. Alam, Flexible hybrid electronics using fan-out wafer-level packaging, in *Embedded and fan-out wafer and panel level packaging technologies for advanced application* spaces, (Wiley-IEEE Press, 2022), pp. 233–260

- M. Li, Y. Yang, F. Iacopi, M. Yamada, J. Nulman, Compact multilayer bandpass filter using low-temperature additively manufacturing solution. IEEE Trans. Electron. Devices 68(7), 3163–3169 (2021). https://doi.org/10.1109/TED.2021.3072926

- L.A. Coldren, P.A. Verrinder, J. Klamkin, A review of photonic systems-on-chip enabled by widely tunable lasers. IEEE J. Quantum Electron. 58(4), 1–10 (2022). https://doi.org/10.1109/ JQE.2022.3168041

- Z. Zhou, B. Yin, J. Michel, On-chip light sources for silicon photonics. Light Sci. Appl. 4(11), e358–e358 (2015). https://doi.org/10.1038/lsa.2015.131

- N. Yu, F. Capasso, Flat optics with designer metasurfaces. Nat. Mater. 13(2), 139–150 (2014). https://doi.org/10.1038/nmat3839

- 23. R. Radojcic, More-than-Moore 2.5D and 3D SiP Integration, 1st edn. (Springer, Cham, 2017)

- H. Liu et al., Thermal-mechanical reliability assessment of TSV structure for 3D IC integration, in 2016 IEEE 18th Electronics Packaging Technology Conference (EPTC), (2016), pp. 758–764. https://doi.org/10.1109/EPTC.2016.7861584

- C. Bäumler, J. Franke, J. Lutz, Reliability aspects of 3D integrated power devices, in 2021 Third International Symposium on 3D Power Electronics Integration and Manufacturing (3D-PEIM), (2021), pp. 1–6. https://doi.org/10.1109/3D-PEIM49630.2021.9497262

- M. Mehrali et al., Blending electronics with the human body: A pathway toward a cybernetic future. Adv. Sci. 5(10), 1700931 (2018). https://doi.org/10.1002/advs.201700931

- G. Boddington, The internet of bodies—Alive, connected and collective: The virtual physical future of our bodies and our senses. AI Soc., 1–17 (2021). https://doi.org/10.1007/s00146-020-01137-1

- L.J. Marks, J.W. Michael, Artificial limbs. BMJ 323(7315), 732–735 (2001). https://doi.org/ 10.1136/bmj.323.7315.732

- 29. X. Wang, Bioartificial organ manufacturing technologies. Cell Transplant. **28**(1), 5–17 (2019). https://doi.org/10.1177/0963689718809918

## Contents

| 1 | Energy Harvesters and Power Management                         | 1   |  |  |  |

|---|----------------------------------------------------------------|-----|--|--|--|

|   | Michail E. Kiziroglou and Eric M. Yeatman                      |     |  |  |  |

|   | 1 Introduction                                                 | 1   |  |  |  |

|   | 2 Motion                                                       | 3   |  |  |  |

|   | 3 Heat                                                         | 13  |  |  |  |

|   | 4 Electromagnetic Fields                                       | 21  |  |  |  |

|   | 5 Energy Harvesting from Waves                                 | 28  |  |  |  |

|   | 6 Power Management                                             | 31  |  |  |  |

|   | 7 Conclusion                                                   | 37  |  |  |  |

|   | References                                                     | 39  |  |  |  |

| 2 | SiC and GaN Power Devices                                      | 47  |  |  |  |

|   | Konstantinos Zekentes, Victor Veliadis, Sei-Hyung Ryu,         |     |  |  |  |

|   | Konstantin Vasilevskiy, Spyridon Pavlidis, Arash Salemi,       |     |  |  |  |

|   | and Yuhao Zhang                                                |     |  |  |  |

|   | 1 Introduction                                                 | 47  |  |  |  |

|   | 2 Silicon Carbide Diodes                                       | 50  |  |  |  |

|   | 3 SiC BJTs                                                     | 57  |  |  |  |

|   | 4 SiC Junction Field-Effect Transistors                        | 59  |  |  |  |

|   | 5 SiC MOSFETs                                                  | 63  |  |  |  |

|   | 6 SiC IGBTs                                                    | 72  |  |  |  |

|   | 7 III-Nitrides Power Devices                                   | 75  |  |  |  |

|   | 8 Conclusions                                                  | 90  |  |  |  |

|   | References                                                     | 91  |  |  |  |

| 3 | Flexible and Printed Electronics                               | 105 |  |  |  |

|   | Benjamin Iñiguez                                               |     |  |  |  |

|   | 1 Introduction                                                 | 105 |  |  |  |

|   | 2 Materials and Processes for Flexible and Printed Electronics | 106 |  |  |  |

|   | 3 Devices for Flexible and Printed Electronics                 | 111 |  |  |  |

|   | 4 Conclusions                                                  | 121 |  |  |  |

|   | References                                                     | 122 |  |  |  |

| 4  | Terahertz Metasurfaces, Metawaveguides, and Applications                          | 127 |  |  |

|----|-----------------------------------------------------------------------------------|-----|--|--|

|    | Wendy S. L. Lee, Shaghik Atakaramians,                                            |     |  |  |

|    | and Withawat Withayachumnankul                                                    |     |  |  |

|    | 1 Introduction.                                                                   | 127 |  |  |

|    | 2 Metasurfaces                                                                    | 133 |  |  |

|    | 3 Terahertz Metawaveguides                                                        | 143 |  |  |

|    | 4 Conclusion and Outlook                                                          | 150 |  |  |

|    | References                                                                        | 151 |  |  |

| 5  | Mechanical Robustness of Patterned Structures and Failure                         |     |  |  |

| 5  | Mechanisms                                                                        |     |  |  |

|    | Ehrenfried Zschech and Maria Reyes Elizalde                                       | 157 |  |  |

|    | 1 Reliability of Microelectronic Products and Failure Mechanisms                  | 157 |  |  |

|    | 2 Risks of Microcrack Propagation and Design                                      | 161 |  |  |

|    | 3 Characterization of Microcrack Behavior                                         | 163 |  |  |

|    | 4 Understanding of Microcrack Behavior                                            | 170 |  |  |

|    | 5 Summary and Outlook                                                             | 180 |  |  |

|    | References                                                                        | 183 |  |  |

| 6  | Nonnomphic Computing for Compact LiDAD Systems                                    | 191 |  |  |

| U  | Neuromorphic Computing for Compact LiDAR Systems<br>Dennis Delic and Saeed Afshar | 191 |  |  |

|    | 1     Introduction                                                                | 191 |  |  |

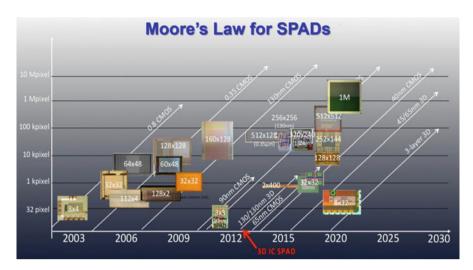

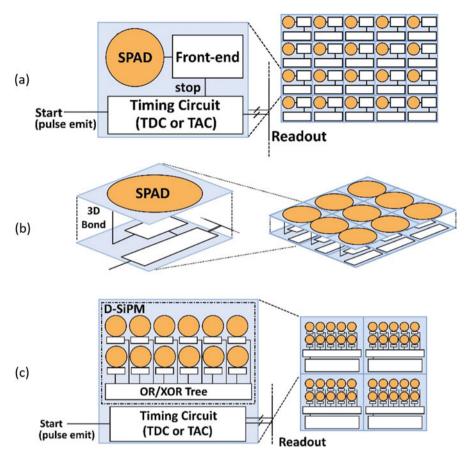

|    | <ol> <li>Innovating SPAD Array Sensors for 3D Flash LiDAR</li> </ol>              | 211 |  |  |

|    | <ul> <li>3 SPAD Neuromorphic Event-Based Sensing and Processing</li> </ul>        | 211 |  |  |

|    | 4 Future Concepts and Summary                                                     | 223 |  |  |

|    | References                                                                        | 230 |  |  |

|    | References                                                                        | 232 |  |  |

| 7  | Integrated Sensing Devices for Brain-Computer Interfaces                          | 241 |  |  |

|    | Tien-Thong Nguyen Do, Ngoc My Hanh Duong, and Chin-Teng Lin                       |     |  |  |

|    | 1 Introduction                                                                    | 241 |  |  |

|    | 2 The Principles of Brain Signal Acquisition                                      | 242 |  |  |

|    | 3 Applications in BCI                                                             | 249 |  |  |

|    | 4 Future Electrode Directions                                                     | 251 |  |  |

|    | 5 Challenges and Outlooks                                                         |     |  |  |

|    | References                                                                        | 254 |  |  |

| _  |                                                                                   |     |  |  |

| In | dex                                                                               | 259 |  |  |

## Chapter 1 Energy Harvesters and Power Management

Michail E. Kiziroglou and Eric M. Yeatman

#### 1 Introduction

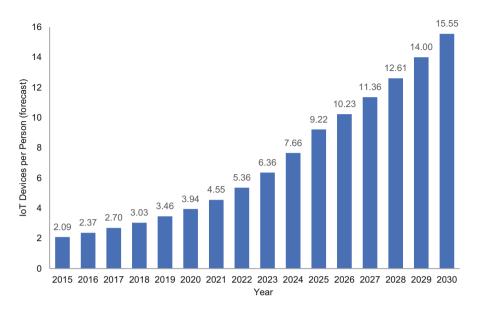

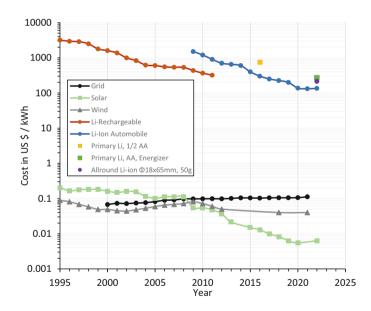

Advances in electronics have led to a vast proliferation of commercial devices over the last several decades. Driven by cost reduction, miniaturisation and wireless communications, a large proportion of these are untethered to mains electricity, and so in most cases are battery powered. However, in an even wider range of potential applications, battery replacement or recharging imposes an unacceptable maintenance burden. As an example, the worldwide average of Internet of Things (IoT) devices per person is expected to rise beyond 10 in the short term (Fig. 1.1). In addition, the cost of portable power in comparison to the electrical grid is at least three orders of magnitude higher (Fig. 1.2). To address these challenges, a strong incentive to develop methods for powering such devices from ambient energy has been created. This approach of generating electrical power from ambient sources, at small scale, for use in a self-powered device or system, we will refer to as energy harvesting.

Ambient energy can be present in many forms, the principal ones being light, heat and motion. Use of such sources for electronics is not new – for example, pocket calculators powered by photovoltaic cells were commercially available already in the 1970s. In this chapter, we will summarise the progress made since then, and the challenges remaining. Although most reported energy harvesting devices are too large for monolithic electronic integration, we will emphasise those with the most potential for at least hybrid integration at chip-scale. Some discussion will also be included of wireless power transfer, where the target remains untethered but the

M. E. Kiziroglou · E. M. Yeatman (🖂)

Imperial College London, London, UK

e-mail: e.yeatman@imperial.ac.uk

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Switzerland AG 2023 F. Iacopi, F. Balestra (eds.), *More-than-Moore Devices and Integration for Semiconductors*, https://doi.org/10.1007/978-3-031-21610-7\_1

Fig. 1.1 Projected number of IoT devices per person, calculated from publicly available statistics

**Fig. 1.2** Cost of energy from various sources and in various forms, from publicly available statistics and prices. Solar panel energy was calculated from power, for 20 years of operation at 5 hours of average exposure per day. For the battery energy cost, the commercial purchase cost is plotted. Batteries can be recharged for as high as 1000 times, but the recharging process introduces significant costs and limitations

energy source is intentionally introduced, because of the close relationship between these two technologies.

#### 2 Motion

A great variety of mechanical energy sources exist from which energy can be harvested. Such environmental energy can come as a varying force applied directly on the microdevice such as a heel strike [1], strain on a surface [2] or a pressure [3] or as varying acceleration, such as vibrations or irregular human body motion [4]. In most cases, some force or motion translation is required from the environmental form to a form suitable for the transduction mechanism used. In the following subsections, the key features of these methods are summarised. A more comprehensive review of motion translation mechanisms for energy harvesting can be found in [5].

#### 2.1 The Use of a Proof Mass

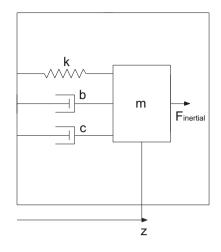

Harvesting of energy from a moving body without the need for connection to stationary structure is very attractive for flexibility of application, and for miniaturisation. This can be achieved by using a proof mass attached to the frame such that it can move inside the device (Fig. 1.3). When the frame experiences acceleration from the motion of the host body, the inertia of the proof mass results in relative motion between it and the frame. This relative motion is used to transduce energy. A general formulation of equations for inertial microgenerators, including piezoelectric, electrostatic and electromagnetic transduction, can be found in [6]. Inertial harvesters have effectively the same structure and operating principle as inertial sensors, although the need to maximise output power results in different design choices, particularly maximisation of the proof mass, which is a disadvantage for monolithic integration.

With a harmonic input motion but without assuming harmonic motion of the proof mass, an upper limit of the power for motion energy harvesters can be calculated as a function of device size (maximum internal displacement amplitude  $Z_1$ , mass m) and the source motion (vibration frequency  $\omega$  and vibration amplitude  $Y_0$ ) [7]. The maximum transduction force  $F_T$  that can be applied is the mass m times the external acceleration  $\omega^2 Y_0$ ; otherwise, the internal motion will cease. The energy extracted is this force times the internal displacement  $2Z_1$ , and this can be obtained twice (once in each direction) for each period  $T = 2\pi/\omega$ , giving a maximum power [7]:

$$P_{\rm max} = \frac{2}{\pi} Y_{\rm o} Z_1 \omega^3 m \tag{1.1}$$

Fig. 1.3 Model of an inertial motion energy harvesting system

From this equation, one can assess the viability of particular motion harvesting applications. This is an absolute limit for inertial harvesting devices – it cannot be overcome by improved transduction methods, or by nonlinear motion structures such as frequency up-conversion methods. The only exceptions are where the input motion is rotational rather than kinematic [8]. In that case, resonant rotating devices and gyroscopic devices offer potential for large power density increases, but neither has been yet demonstrated in practice.

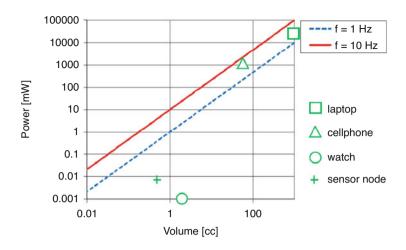

In Fig. 1.4, the maximum power is plotted as a function of device size for frequencies in the range expected for human motion, acceleration  $\omega^2 Y_0$  of 10 m/s<sup>2</sup> and a proof mass density of 20 g/cm<sup>3</sup> occupying half of the device volume. By comparison with the power requirements and size of a typical laptop, cellphone, watch and (very low power) sensor node, one concludes that human motion harvesting is not enough for the first two applications, while there is substantial promise for the last two. Indeed, the watch application has already been commercialised in high volumes, and sensors powered by harvesting are becoming more common.

#### 2.2 Electrostatic

Electrostatic transducers convert energy between kinetic and electrical form through the electrostatic force between charged bodies. This approach is especially well suited to micro-electro-mechanical systems (MEMS), because it can be implemented in many cases with standard MEMS materials and is easily adapted to a quasi-two-dimensional design. The similarity in structure to accelerometers is also an advantage. Consequently, most true MEMS energy harvesters are electrostatic in operation. This mechanism is typically described using the example of two charged parallel plates which can move with respect to each other. For a given capacitance *C*

Fig. 1.4 Maximum power for motion harvesters versus size for two different excitation frequencies, with size and power requirement of various applications superimposed [7]

and voltage V, with area A and separation t, the electrostatic force  $F_{es}$  between the plates is:

$$F_{\rm es} = \frac{1}{2} \frac{\varepsilon_0 A V^2}{t^2} \tag{1.2}$$

where  $\varepsilon_0$  is the electrical permittivity of free space. If one of the plates is moved perpendicularly to the plate surface so that the distance *t* between the plates is increased,  $F_{es}$  will produce work against the motion. This work will be stored in the capacitor as electrical energy. The same will occur if the motion is parallel to the surface of the plates. This can be understood by considering that the electric field will be rotated by this motion and a component of electrostatic force arises that is parallel to the field.

Effectively, if the motion results in a change of capacitance, there will be conversion between mechanical and electrical energy, as long as there is some initial charge in the system. A common operational approach is to add a charge at a position of maximum capacitance  $C_{\text{max}}$  and subsequently extract the energy at a minimum  $C_{\text{min}}$ . The harvested energy will be given by:

$$\Delta E_{\rm es} = \frac{1}{2} V_{\rm in}^2 \frac{C_{\rm max}}{C_{\rm min}} \left( C_{\rm max} - C_{\rm min} \right)$$

(1.3)

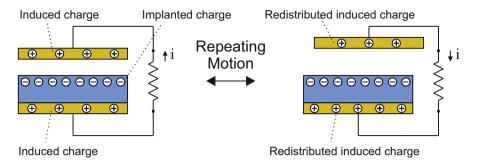

Fig. 1.5 Operation principle of electret harvester

This indicates the importance of both a large capacitance ratio and a large capacitance difference. The former will usually be limited by stray capacitance. A high priming voltage  $V_{in}$  is also essential, which creates practical challenges in the interface electronics. Another technique is to keep the voltage constant and let charge flow in or out of the plates during capacitance decrease or increase, respectively.

For the priming of electrostatic generators, inserting charge from the external circuit can be avoided by use of electrets. Electrets are dielectrics with trapped charge that allows them to have (quasi)-permanent polarisation. A typical orientation for an electret-based device is shown in Fig. 1.5 [9, 10]. Its trapped charge creates an electric field which is equivalent to charging the capacitor with a high voltage (typically hundreds of volts). Any capacitance-changing relative motion of the plates, in-plane or perpendicular-to-plane, will result in charge motion through the circuit, delivering electrical energy to a load resistance R. In this operating scheme, the electret effectively provides the initial priming of the electrostatic harvesting device. Various geometrical implementations of such devices have been proposed including in-plane shifting electrodes [9], rotating electrodes [11], patterned electrodes [12] and comb-like electrode structures [13]. A quantitative analysis of operation for such devices can be found in [12].

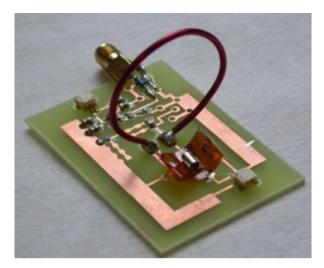

Beyond electret-based devices, electrostatic priming can be provided by an active circuit, although a method for device initialisation is still required in this case. Another approach is the direct use of a passive sensor with voltage output as the priming source of an electrostatic harvester [14]. An implementation using a pH sensor for priming is shown in Fig. 1.6 [14]. That device includes radio frequency (RF) transmission of the sensor information at distances up to 1 m by direct discharge of the harvested energy into a loop antenna. The main challenge of this implementation is related to the voltage range of common passive sensors which is usually lower than that required for efficient operation of electrostatic harvesters.

In electrostatic MEMS actuators, the hyperbolic increase of electrostatic field with decreasing gap distance results in an instability that causes sudden attraction to the point of minimum separation. This is called the pull-in effect and disturbs motion control for MEMS devices. In MEMS microgenerators, the induced field opposes

Fig. 1.6 Electrostatic harvester with an external proof mass, pH-sensor priming and RF transmission [14]

the motion and therefore cannot lead to such an effect. However, when using active pre-biasing techniques (outlined in the power management section of this chapter) to increase damping in electrostatic devices, the pull-in effect should be considered. A review of pull-in instability effects for MEMS actuators can be found in [15].

A variant of electrostatic motion transduction is triboelectric energy harvesting which is usually considered as a separate device concept. Triboelectricity is the effect of static charge exchange between the surfaces of two different materials when they come to contact, due to different electron energy distribution. Various device implementations have been proposed to exploit this effect, often employing nanostructures to increase contact area. A general description of the operating mechanism and a review of nanopatterning methods for triboelectric harvesters can be found in [16, 17], respectively.

#### 2.3 Electromagnetic

In electromagnetic transducers, electromagnetic induction as described by Faraday's law is employed. Relative motion between a magnet and a coil results in magnetic flux variation which induces an electromotive force across the coil. The motion is damped when electrical power is taken from the output coil. While electromagnetic transduction is used in most macro-scale electric generators, it does not scale well into the micro-domain. This is due to the difficulty of designing a planar implementation suitable for MEMS fabrication, the difficulty of effectively guiding magnetic flux in such a planar or quasi-planar configuration (particularly if high permeability materials cannot be integrated) and the limited number of turns achievable in micro-scale coils, which results in low output voltages which cannot be efficiently rectified.

For sensing applications, the design of electromagnetic transducers focuses on sensitivity, signal-to-noise ratio and overall optimised measurement of the effect/quantity of interest [16]. In contrast, for energy microsystems, including energy harvesters and actuators, maximum power transduction is generally the priority, requiring a different operation point and transducer design. Coils are needed to operate such that they provide maximum power and are therefore connected to impedance matched loads, instead of high-impedance signal acquisition circuitry such as analogue to digital converters. Consequently, the coil impedance is far more important in energy microsystems than in sensing. This results in significant design differences between sensing inductive transducers and inductive transducers for motion harvesting.

On the other hand, most macro-scale generators employ rotational motion. In micro-mechanics, low-loss bearings are difficult to implement, and consequently most devices use vibrating motion and flexures rather than sliding or rolling bearings. In harvesters that have rotational input motion, the rotation can be converted to oscillation via some translation mechanism. Such methods are discussed in [16].

To achieve high flux density in the small scale, high-performance permanent magnets may be employed. Systems that usually follow this approach include microturbines for fluid flow [3] and rotational motion [18] energy harvesters. As an example, an image of a microturbine by Holmes et al. is shown in Fig. 1.7 [19]. This device is based on MEMS fabricated coils and springs, but it relies on manual placement for its 35 mg NdFeB permanent magnet. In this way, the MEMS magnet fabrication which usually involves high-temperature sintering processes is avoided. For the same reason, most electromagnetic harvesters use commercially purchased and externally assembled NdFeB as permanent magnets [20–29]. Reviews of various implementations, including performance comparison tables, can be found in [6, 30].

MEMS integration of permanent magnets by sputtering for NdFeB and SnCo [31–33], and by electrodeposition for CoPt and FePt compounds [34–40], has been demonstrated with promising potential. The deposited materials are magnetised by the application of a strong field, which can be several Tesla, during [41] or after deposition [32]. A review of magnetic material MEMS integration can be found in [42].

The challenge of employing effective magnetic materials into micromachining processes has limited the flux density availability. The use of soft magnetic materials with high magnetic permeability as flux guides has the potential of achieving high flux densities in microsystems. As this technique has been developed for inductive energy harvesting for power lines and structural currents [43], it is discussed in Sect. 1.4 of this chapter. Integrating high permeability materials into microfabrication processes may enable high-performance electromagnetic micro-transducers for energy as well as sensing and actuating microsystems in the near future. Candidate materials include conventional ferrites, nanocrystalline structures,

Fig. 1.7 A MEMS electromagnetic turbine energy harvester by Holmes et al. [19]. (Courtesy of A. S. Holmes)

ferrite films [44] as well as printable [45] and electrodeposited [46] soft magnetic materials. A promising integration method for soft cores based on atomic layer deposition and agglomeration has been reported in [47, 48].

#### 2.4 Piezoelectric

Piezoelectricity is the electromechanical coupling between stress T, strain S, electric field E and surface charge density D (displacement) in a bulk material [16]. The change of interatomic distances in a strained dielectric material with certain crystal asymmetries can result in changes of dipole distribution. This causes material polarisation P and a corresponding surface charge  $Q = P \cdot A$ , where A is the surface area. Normal and shear strain in each direction can result in polarisation in all three dimensions. The relation between applied T and resulting P can be approximated as linear, with a tensor factor d:

$$\boldsymbol{P} = \boldsymbol{d} \cdot \boldsymbol{T} \tag{1.4}$$

As a practical simplification, for a given selected input-output pair of stress and polarisation axes, a single effective *d* value can be used, although such a value may

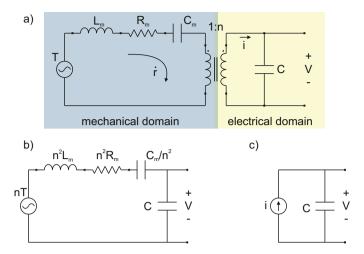

**Fig. 1.8** (a) Lumped element model of a piezoelectric generator. (b) Corresponding all-electrical model. (c) Simplified model encompassing the excitation source and mechanical response into a current source

vary for different boundary conditions in other directions. If electrodes are deposited on two back-to-back surfaces of a piezoelectric material, a capacitor *C* is formed. Stress-driven polarisation moves charge *Q* to and from the electrodes. Hence, a piezoelectric generator can be modelled as a current source in parallel with a capacitor *C*. The dielectric (shunt) leakage and series resistance can also be included in such a model by adding corresponding components. The mechanical behaviour of the structure can be modelled with lumped elements. The link between the electrical and the mechanical domain can be represented by a transformer, leading to equivalent circuits such as the one shown in Fig. 1.8a [49]. In this example, force is represented as a potential quantity, analogous to voltage, while mass displacement rate  $\dot{r}$  is represented as a flow quantity, analogous to current. In this way, the inductance  $L_{\rm m}$ , resistance  $R_{\rm m}$  and capacitance  $C_{\rm m}$  represent the structure mass (inertia), mechanical losses and elasticity, respectively. The transformer ratio *n* translates force to voltage and 1/n translates displacement rate to current, and its units are therefore *V/N* or equivalently *C/m*.

Using circuit analysis, the mechanical components can be transferred to the electrical side as shown in Fig. 1.8b. This model can be used to analyse the electromechanical behaviour of piezoelectric transducers. The determination of  $L_m$ ,  $R_m$  and  $C_m$  depends on the mechanical properties and geometry of the full mechanical structure. For bulk piezoelectric transducers such as in acoustic devices, the parameter values are primarily determined by the piezoelectric itself, while for devices such as accelerometers where the piezoelectric material forms just a small part of the moving structure, they are determined by the mechanical properties of the overall structure. An example is the typical unimorph structure.

| Table 1.1   Summary of            | Material           | d <sub>33</sub> (nC/N) | d <sub>31</sub> (nC/N) | Reference |  |  |

|-----------------------------------|--------------------|------------------------|------------------------|-----------|--|--|

| common piezoelectric<br>materials | PZT                | 0.63                   | -0.28                  | [50]      |  |  |

| materials                         | PMN-PT             | 1.25                   | -0.15                  | [54]      |  |  |

|                                   | PNN-PZT            | 1.75                   | -0.44                  | [55]      |  |  |

|                                   | LiNbO <sub>3</sub> | 0.006                  | -0.001                 | [56]      |  |  |

|                                   | AlN                | 0.004                  | -0.002                 | [57]      |  |  |

|                                   | PVDF               | 0.02                   | -0.015                 | [58]      |  |  |

|                                   | KNN-BNZ-AS-Fe      | 0.5                    | -                      | [59]      |  |  |

|                                   |                    |                        |                        |           |  |  |

A list of piezoelectric materials typically employed for energy applications is presented in Table 1.1 [16]. The most common is lead zirconate titanate (PZT) which exhibits a  $d_{33}$  of around 0.63 nC/N, one of the highest available in the market [50]. While such ceramic piezoelectrics are generally formed by sintering of powders, thin film processes suitable for monolithic MEMS integration have been widely investigated [51–53]. Single-crystal piezoelectrics employ the electrostrictive (relaxor) effect and can exhibit higher *d* values. The typical lead magnesium niobate-lead titanate (PMN-PT) exhibits constants higher than 1 nC/N in single-crystal form, e.g. 1.25 nC/N in [54]. The electrostrictive type materials are usually more challenging to use because of the high cost of single crystal and the requirement for an additional polarisation field. In microgenerators, piezoelectric materials are usually integrated in bimorph cantilever structures, exploiting their  $d_{31}$  coefficient which is smaller than  $d_{33}$ . AlN and PVDF exhibit low coupling factors but are easier to integrate. PVDF is also a flexible material allowing the implementation of high elasticity transducers.

A review of piezoelectric energy harvesting devices can be found in [60].

#### 2.5 Comparison of Transduction Mechanisms

The broad range of differences in prototype architecture, fabrication methods, testing conditions and target application makes a fair and useful comparison very difficult to achieve, especially across the transduction mechanisms. Furthermore, in most device cases, there is little reported on performance in real environments. Instead of an exhaustive figure of merit comparison, a table with three indicative implementations for piezoelectric, electrostatic and electromagnetic transduction is presented in Table 1.2. A comparison of key features for each mechanism is presented in Table 1.3. For state-of-the-art comparative tables, the reader is referred to recent reviews [30, 60–64].

| Mechanism       | Reference Power     |        | Proof mass | Conditions                     |  |

|-----------------|---------------------|--------|------------|--------------------------------|--|

| Piezoelectric   | Elfrink et al. [65] | 85 μW  | 0.1 g      | 17.5 m/s <sup>2</sup> , 325 Hz |  |

| Electrostatic   | Suzuki et al. [66]  | 1 μW   | 0.1 g      | 20 m/s <sup>2</sup> , 63 Hz    |  |

| Electromagnetic | Shin et al. [67]    | 165 μW | 0.05 g     | 4 m/s <sup>2</sup> , 46 Hz     |  |

Table 1.2 Performance of three indicative MEMS energy harvesters

Table 1.3 Comparison of features for microgenerators based on different transduction mechanisms. Green, amber and red indicate high, medium and low, respectively [16]

| Mechanism                     | Complexity |           | Scalability | Power       |         |

|-------------------------------|------------|-----------|-------------|-------------|---------|

|                               | Material   | Structure | Circuit     | Scalability | Density |

| Piezoelectric                 | •          | •         | •           | •           | •       |

| Non-Electret<br>Electrostatic | ٠          |           | •           | ٠           | •       |

| Electret<br>Electrostatic     | ٠          | •         | •           | •           | •       |

| Electromagnetic               | •          | •         |             | •           | •       |

| Triboelectric                 | •          | •         | •           | •           | •       |

#### 2.6 Opportunities

A discussion of the main current challenges and opportunities in motion energy harvesting has been presented in [16]. Considering motion energy harvesting as a combination of a motion adaptor, an active material and a power management system with optimised interfaces may allow the combination of techniques that have been developed and are currently bound to specific device types. For example, prebiasing has been developed for piezoelectric transducers but active driving of other materials may offer significant potential.

In practice, the main limiting factor in industrial adoption of energy harvesting microsystems is the requirement for specific device designs, tailored to a very narrow set of environmental specifications, such as the availability of vibration at a specific frequency. This leads to a demand for customised and high cost research and development for each potential application. In spite of significant research advancement in broadening these environmental requirements, microgenerator prototypes tend to operate at lower performance in real application conditions. To address this limitation, a combination of energy harvesting and wireless power transfer could potentially be adopted. This approach applies to other energy harvesting mechanisms as well and is therefore discussed in Sect. 1.7 of this chapter.

#### 3 Heat

The environmental heat is another source that can be used to power microsystems, by the thermoelectric effect, the pyroelectric effect or gas heat engines such as the Stirling engine. This section focuses on thermoelectric energy harvesting because it is the most common mechanism used in micro energy harvesting applications. A review of pyroelectric materials including energy harvesting applications can be found in [68]. Gas engines are considered to be beyond the scope of this chapter.

The thermoelectric effect is based on the coupling between heat transfer and charge carrier transport. In a classical picture, a certain percentage of heat is carried by electron flow in metals, and either electrons or holes in semiconductors. The rest is carried through phonons, i.e. propagation of lattice vibration. In a quantum mechanical view, the net carrier transport in one direction, either along or against the heat flow, depends on the asymmetry of the density of states on either side of the Fermi level. In both interpretations, this results in a voltage difference between the hot and the cold side of a material  $\Delta V = S\Delta T$ , where *S* is a temperature-dependent factor called the Seebeck coefficient of the material and  $\Delta T$  is the temperature difference. To access a  $\Delta V$  on the same side of the device (either the hot or the cold one), a couple of materials with different *S* are required:

$$\Delta V = (S_{\rm A} - S_{\rm B}) \cdot \Delta T = S_{\rm AB} \cdot \Delta T \tag{1.5}$$

where  $S_{AB}$  is the Seebeck coefficient of the material couple. This is called a thermocouple. The efficiency of power transduction increases with the square of *S* and the material electrical conductivity  $\sigma$  and decreases with thermal conductivity *k*. Therefore, the following figure of merit is often used for thermoelectric materials:

$$zT = \frac{\sigma S^2}{k}T \tag{1.6}$$

In practice, because S is small (below 1 mV/K), an array of thermocouples electrically connected in series is typically employed. For a generator with total electrical resistance  $R_e$  and thermal conductance K, the overall figure of merit is defined in the literature as:

$$ZT = \frac{S^2}{KR_e}T\tag{1.7}$$

Note that in the theoretical case of a thermocouple with the same electrical and thermal conductivity, the device level *ZT* is equal to zT/4. This means that when a material is reported to exhibit a certain zT, its contribution to a generator device will correspond to zT/4. An equation for the maximum efficiency of a thermoelectric generator (TEG) as a function of *ZT*, hot side temperature  $T_h$  and cold side temperature  $T_C$  can be calculated to be [69]:

$$\eta_{\text{TEG}} = \frac{\Delta T_{\text{TEG}}}{T_{\text{h}}} \cdot \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + \frac{T_{\text{c}}}{T_{\text{h}}}} = \xi \left(ZT, T_{\text{h}}\right) \cdot \Delta T_{\text{TEG}}$$

(1.8)

where  $\xi(ZT, T_h)$  is defined in this equation. Note that this is the maximum possible efficiency of the TEG. The operating efficiency in general depends also on the electrical load connected to the TEG. The operation point of maximum efficiency is not the same with the one for maximum output power, due to the effect of current flow on the TEG heat conductivity [70, 71]. Nevertheless, the difference between the two operating points is less than 10% for typical temperature and *ZT* values [70], and for this reason, Eq. (1.8) is widely used in the literature to evaluate the performance of TEGs.

The TEG efficiency depends on the available  $\Delta T$ , on temperature range and on ZT. The value of ZT is determined by the material properties and is independent from the device design. Research towards high ZT values has focused on developing materials with high  $\sigma$  and small k, e.g. by employing phononconfining nanostructures or superlattices, or with higher Seebeck coefficients, by enhancing carrier transport asymmetry. Bismuth tellurides have been, and still are, the most commonly used thermoelectric materials. Other materials, including silicon nanostructures [72, 73], have been under investigation. A material of special interest is tin selenide (SnSe), which has been shown to exhibit zT values over 2 at high temperatures (~900 K) in single-crystal form, and over 3 in polycrystalline form [74]. Another promising technique is carrier transport energy filtering, which has been shown to improve heat and charge transport coupling [75]. This technique can be implemented by metal particle implantation which introduces thermionic emission to current transport. The energy selectivity of thermionic emission, in turn, reduces electrical conductivity  $\sigma$  but boosts the Seebeck coefficient S, resulting in an overall increase of the power factor  $\sigma S^2$  of the material. This is demonstrated in [76] by implantation of Ag nanoparticles in an antimony telluride thermoelectric material. A review of material and device level thermoelectric research can be found in [77].

Beyond improvement of zT (and the corresponding ZT), the temperature difference across a TEG has a key role in output power as heat flow is proportional to  $\Delta T$ , for a given TEG thermal conductance K, and the transduction efficiency is also almost proportional to  $\Delta T$ , through Eq. (1.8). Hence, the TEG output power scales with  $\Delta T^2$ , and achieving the optimal  $\Delta T$  is of decisive importance in practical installations. This relies on the TEG design, which defines its K, as well as on the thermal design of interfacing with the environmentally available temperature difference  $\Delta T_E$ . The environmental  $\Delta T_E$  can be directly available between two heat conductive bodies, with a series thermal resistance  $R_{\text{th}, E}$ , or can be created artificially from fast temperature fluctuations in time. The two cases, coined static and dynamic thermoelectric energy harvesting, are discussed in the following two subsections.

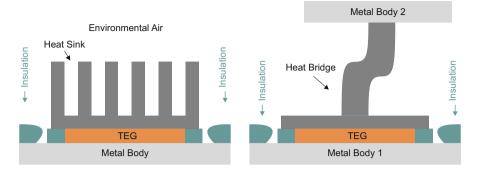

Fig. 1.9 Installation of a static thermoelectric harvester between a metal body and air using a heat sink (left) and two metal bodies using a heat bridge (right)

#### 3.1 Static Thermoelectric Harvesting

In the case of static thermoelectric harvesting, the environmental  $\Delta T_{\rm E}$  is available between a heat conductive body, such as a metal structure, and the surrounding air, or between two heat conductive bodies, as illustrated in Fig. 1.9. The TEG is installed such that one of its surfaces is in direct thermal contact with one of the bodies, while the other is either in contact with air through a heat sink (Fig. 1.9, left) or with the second body through a thermal bridge (Fig. 1.9, right). The thermal resistance of the heat sink, the heat bridge or the heat conductive bodies themselves are in series with the thermal resistance of the TEG,  $R_{\rm th, TEG}$ . If the total series resistance is denoted as  $R_{\rm th, E}$ , then the heat flow through the TEG will be:

$$Q = \frac{\Delta T_{\rm E}}{R_{\rm th, TEG} + R_{\rm th, E}}$$

(1.9)

The temperature difference across the TEG will be:

$$\Delta T_{\rm TEG} = \Delta T_{\rm E} \frac{R_{\rm th, TEG}}{R_{\rm th, TEG} + R_{\rm th, E}}$$

(1.10)

Given that the efficiency in Eq. (1.8) varies linearly with  $\Delta T_{\text{TEG}}$  ( $\eta_{\text{TEG}} = \xi(ZT, T) \cdot \Delta T_{\text{TEG}}$ ), in good approximation (see [78] Fig. 17.14), the TEG maximum output power can be written as:

$$P_{\text{TEG}} = \eta_{\text{TEG}} \cdot Q = \xi \cdot \Delta T_{\text{TEG}} \cdot \frac{\Delta T_{\text{E}}}{R_{\text{th},\text{TEG}} + R_{\text{th},\text{E}}} = \xi \cdot \Delta T_{\text{E}}^2 \frac{R_{\text{th},\text{TEG}}}{\left(R_{\text{th},\text{TEG}} + R_{\text{th},\text{E}}\right)^2}$$

(1.11)

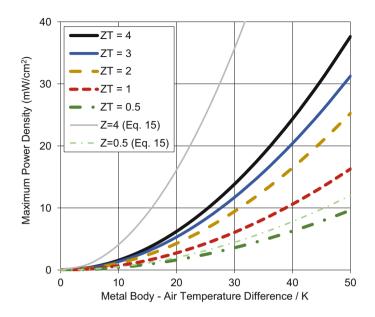

**Fig. 1.10** Maximum static TEG power output as a function of environmental body-to-air  $\Delta T$ , using a typical heat sink with a moderate airflow, calculated by Eq. (1.12). Calculations from the simpler Eq. (1.13) are also shown as faded lines for ZT = 0.5 and ZT = 4, for comparison. An order of magnitude agreement for ZT = 0.5 is observed

This expression shows that to maximise  $P_{\text{TEG}}$ , the minimum possible  $R_{\text{th, E}}$  is desirable. In practice this is limited by size, geometry and installation access restrictions. In the case of using air convection, as in the body-to-air case of Fig. 1.9 left, ventilation is a significant limiting factor. For a given application, once  $R_{\text{th, E}}$  is minimised, the  $R_{\text{th, TEG}}$  must be selected for maximum  $P_{\text{TEG}}$ . Under the approximation of a constant  $R_{\text{th, TEG}}$ , which is not affected substantially by the Seebeck and the Ohmic effects, the dependence of  $P_{\text{TEG}}$  on  $R_{\text{th, TEG}}$  has a typical load-matching form. The optimal  $R_{\text{th, TEG}}$  can be calculated by zeroing the first derivative of (1.11) to be equal to  $R_{\text{th, E}}$ , yielding:

$$P_{\text{TEG,MAX}} = \xi \cdot \frac{\Delta T_{\text{E}}^2}{4R_{\text{th,E}}} = \frac{1}{T_{\text{h}}} \cdot \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + \frac{T_{\text{c}}}{T_{\text{h}}}} \cdot \frac{\Delta T_{\text{E}}^2}{4R_{\text{th,E}}}$$

(1.12)

Using this equation, the energy harvesting power expected from an environment with a certain available  $\Delta T_{\text{E}}$  and achievable  $R_{\text{th, E}}$  can be calculated for different thermoelectric figures of merit ZT. An indicative calculation, for  $T_{\text{C}} = 300$  K, and  $R_{\text{th, E}} = 20$  K/W corresponding to a typical 1 cm<sup>2</sup> finned heat sink at a mild 0.5 m/s airflow [79] is presented in Fig. 1.10.

As already mentioned, the calculation of maximum output power as given in Eq. (1.12) is based on three approximations. First, that the Seebeck, Peltier, Ohmic

and Thomson effects do not alter the TEG thermal resistance as experienced by the heat flow, and hence the  $\Delta T$  distribution across  $R_{\text{th, E}}$  and  $R_{\text{th, TEG}}$ . If this was taken into account, the optimum thermal resistance balance would deviate from the  $R_{\text{th, TEG}} = R_{\text{th, E}}$  condition. Second, that the maximum power occurs at maximum conversion efficiency. To take this into account, a different expression for TEG efficiency should be used, as given in [69, 70], corresponding to an electrical load matching,  $R_{\text{L}} = R_{\text{e}}$ , condition. Third, that the electrical current, as controlled by  $R_{\text{L}}$ , also has a negligible effect to the  $\Delta T$  distribution. In summary, Eq. (1.12) does include the Peltier and Ohmic effects on the conversion efficiency (in the  $\xi$ term), but not on the optimisation of thermal and electrical resistance ratios. These approximations lead to deviations in the 10% range for small ZT and  $\Delta T$  values (<1 and <20 K, respectively).

On the other hand, if the Peltier, Ohmic and Thomson effects are considered to be negligible for such small ZT and  $\Delta T$  values, a much simpler calculation of  $P_{\text{TEG, MAX}}$  can be made by considering the Seebeck coefficient, thermal and electrical load matching conditions:

$$P_{\text{TEG,MAX}} = \frac{\Delta V^2}{4R_{\text{e}}} = \frac{S^2 \Delta T_{\text{E}}^2}{16R_{\text{e}}} = \frac{Z}{4} \cdot \frac{\Delta T_{\text{E}}^2}{4R_{\text{th,E}}}$$

(1.13)

This equation can also be derived from the TEG efficiency expression at electrical load matching conditions (as given in [69, 70]), by neglecting the Peltier and Ohmic terms in the denominator. It provides an order-of-magnitude agreement with the predictions of (1.12) for small ZT and  $\Delta T$  (<1 and <20 K, respectively) but deviates significantly for higher values. For comparison, the corresponding calculation curves for ZT = 0 and ZT = 4 are plotted as grey lines in Fig. 1.10.

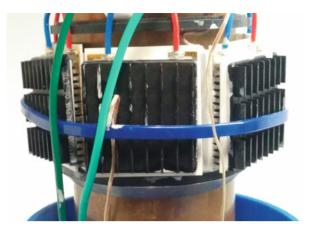

The employment of detailed analysis, identifying the optimal TEG thermal resistance and the optimal electrical load resistance such as those in [80, 81], may offer significant improvement of device performance, especially for higher *ZT* and  $\Delta T$  values. A photograph of an experimental setup developed for the evaluation of static energy harvesting from hot metal pipes under different Ohmic loads is shown in Fig. 1.11.

While research results demonstrating ZT values as high as 2, in practice, for room temperature applications with  $\Delta T$  values around 20 K, commercially available TEGs exhibit a ZT of approximately 0.5. Overall, a power density up to 10 mW/cm<sup>2</sup> may be expected for direct TEG harvesting applications. As discussed in this section, the main limitation is  $\Delta T$  availability and the associated practically achievable  $R_{\text{th, E}}$ . Dynamic thermoelectric harvesters offer an alternative method of acquiring a significant  $\Delta T$  across a TEG. This concept is discussed in the following subsection.

**Fig. 1.11** Static thermoelectric energy harvesting from hot pipelines in the Advanced Materials for Energy Lab, UC Berkeley in 2016

#### 3.2 Dynamic Thermoelectric Harvesting

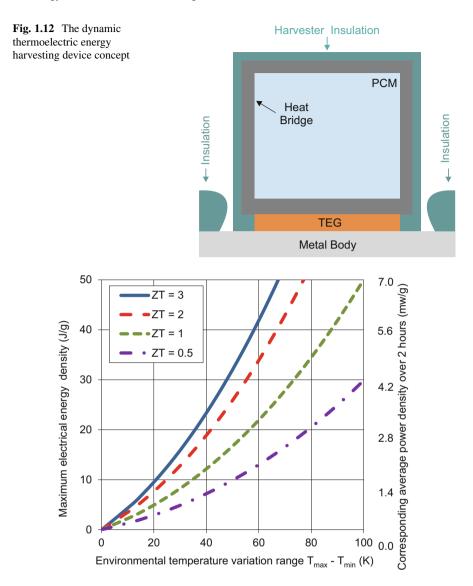

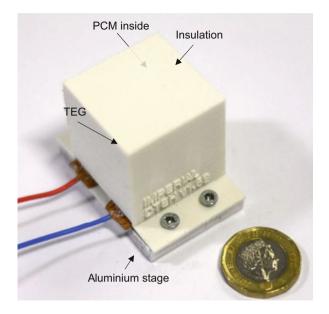

Dynamic thermoelectric devices comprise an insulated heat storage unit (HSU) which is in thermal contact to the environment (e.g. to a metal body) through a TEG as shown in Fig. 1.12. The HSU is filled with a phase change material (PCM) to increase thermal storage density and the time constant of its heat dynamics. When the environment undergoes temperature fluctuation in time, the HSU follows this change with a delay, achieving a substantial  $\Delta T$  across the TEG, which is essential for efficient power transduction and management. This device concept was introduced in [82], studied analytically and numerically [70] and used in various implementations, including demonstrators for aircraft applications and flight tests [83] and integrated wireless sensor networks [84]. A model for phase change inhomogeneity was introduced in [85]. A practical dry fabrication method was proposed, based on 3D-printed double-wall insulation and water capsules [86].

A dynamic analysis of this device concept has shown that the maximum energy per temperature cycle, from a temperature fluctuation range  $\Theta$ , using a HSU with heat capacity *C* and latent heat *L* can be written as [70]:

$$E_{\text{MAX}} = 2 \cdot (\Theta \cdot C + L) \cdot \eta_{\text{TEG}} \left(\frac{\Theta}{2}\right)$$

(1.14)

where  $\eta_{\text{TEG}}(\Theta/2)$  is the TEG efficiency at temperature difference  $\Delta T = \Theta/2$ . This means that the overall maximum possible efficiency is simply the TEG efficiency for  $\Theta/2$ . Indicative results using Eq. (1.8) for  $\eta_{\text{TEG}}$  are plotted in Fig. 1.13 as a function of ambient temperature variation. For this calculation, a latent heat density of L/m = 334 kJ/kg and heat capacity density of C/m = 4.2 kJ/(K · kg) were used, where *m* is the PCM mass. These values correspond to using water as a PCM, and

**Fig. 1.13** Dynamic thermoelectric harvesting energy availability vs environment temperature fluctuation range [70]. The corresponding average power assuming a 7200 s fluctuation period (corresponding to an aircraft use case) is indicated on the right vertical axis

it is chosen because its heat storage properties are superior to other salt-based or organic solutions. The phase change temperature must lie within the environmental temperature fluctuation range, and therefore, for applications with temperatures not crossing 0 °C, other suitable PCMs may be required.

Fig. 1.14 Dynamic thermoelectric harvesting prototype developed for aircraft applications, presented in [87]

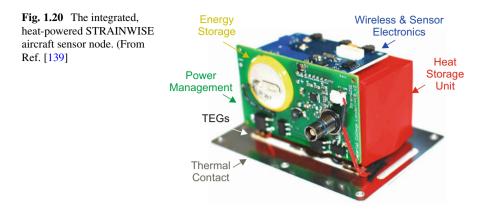

A photograph of a dynamic thermoelectric energy harvester developed for aircraft sensor power supply applications is shown in Fig. 1.14.

#### 3.3 Opportunities

In the literature, review papers have studied the thermoelectric harvesting state of the art, offering insight in key technology aspects such as material properties [88], thermal contact improvement [89], the potential of silicides [90] and BiTe nanostructures [91], electrodeposited tellurides [92] and room temperature TEGs, including organic and carbon-based [93]. At device level, reviews focusing on TEG microfabrication [94], wearable applications [95] and thermal design prototypes [96, 97] can be found among others. Further to the key promising aspects highlighted in these works, the following are suggested as topics of particular interest for the short- and mid-term future:

The wide temperature range of potential applications has led to a wide distribution of research effort, at the cost of slow and out-of-focus advancement.

Focusing material research to temperature ranges associated with priority applications would be beneficial for the advancement of thermoelectric energy harvesters and especially energy autonomous microsystems.

- 1 Energy Harvesters and Power Management

- Dynamic thermoelectric harvesting has been shown to address the challenge of unreliable  $\Delta T$  availability, by employing heat storage. Extension of TEG design to include dynamic response and even incorporate heat storage could lead to a more widely applicable generation of TEG devices.

- The inherent interconnection of heat flow dynamics, steady-state  $\Delta T$  distribution across series thermal resistance and electrical load matching means that a more holistic dynamic design approach could potentially increase power output. Switching the thermal as well as the electrical contacts towards a fully dynamic thermoelectric operation, in combination with heat storage, could lead to significant improvement of TEG performance in real application environment.

- The impressive performance of SnSe at high temperature in single crystal as well as in polycrystalline form could offer an opportunity of further understanding the mechanisms of controlling electrical conductivity, thermal conductivity and the Seebeck coefficient. This would in turn benefit the development of new materials at lower temperatures with broader application range.

- As also pointed out in [88], energy filtering and engineering the densityof-state asymmetry may lead to materials of improved heat/charge transport coupling. Furthermore, the employment of engineered thermally and electrically asymmetric contacts, such as clean Schottky interfaces, could offer an additional means of asymmetric, energy filtered transport, especially in microfabricated thermoelectrics. An investigation of the role of contacts in general to thermoelectric performance beyond their view as parasitic resistance may lead to new understanding and opportunities in TEG fabrication.

#### 4 Electromagnetic Fields

Another very interesting type of energy harvesting is coupling with environmental local electromagnetic fields. Such fields are usually available around power lines and other alternating current (AC) carrying structures. In this way, power can be delivered to stationary or portable microsystems that require energy autonomy, without invasion to existing electrical infrastructure. In the case of power lines, in addition to portability and installation simplicity benefits over physical Cu wire splitting, such a method also offers security, isolation and electrical decoupling, which can be highly desirable for microsystems that require separate autonomy and reliability in their functionality, such as in security or emergency systems. Relevant environments include industrial plants and machinery, the electrical power grid, electrical installations of buildings, vehicle power networks and any electrified infrastructure such as road and utility networks.

Piezoelectric [98–104], electrostatic [105–108], and inductive [109–116] coupling methods have been proposed in the literature. In most of these works, it has already been demonstrated that adequate power density can be achieved by noninvasive coupling, to support wireless sensors with continuous power. In this section, a brief overview of piezoelectric and electrostatic (capacitive) devices for energy harvesting from AC power lines is presented. Subsequently, the inductive coupling method is discussed in some more detail, because of its broader applicability to other environments and power delivery/collection applications including inductive wireless power transfer.

#### 4.1 Piezoelectric Harvesting from AC Power Lines

The alternating magnetic field around an AC power line can be exploited by employing a permanent magnet mounted on a piezoelectric beam. If the beam is installed such that the magnetic flux density vector *B* lies in the direction of the beam deflection, the magnetic force can drive the beam into oscillation which is in turn transduced into electricity by the piezoelectric material. This electromechanical approach offers electrical isolation and protection of the secondary circuit, at the expense of an additional intermediate energy transduction step. For a constant given power line frequency, the beam can be designed to operate at resonance, thereby minimising losses. This method was introduced in [104], demonstrating 0.35 mW from a 13 A RMS 60 Hz current, using a 0.26 cm<sup>3</sup> piezoelectric beam installed on a bipolar power supply cable. A similar approach using a Halbach magnet array for field amplification was adopted in [102], demonstrating 0.52 mW from a 5 A RMS, 50 Hz current, from a 2.5 cm<sup>3</sup> beam.

#### 4.2 Electrostatic Harvesting from AC Power Lines

The electric field of an AC power line can also be used for coupling to the conductor voltage. This is possible by employing a capacitor structure, located such that the field gradient creates a voltage difference between its two conductive plates. As the field alternates, charge can flow in and out of the capacitor plates, similar to the electrostatic motion energy harvesting concept, providing a current to a connected electrical load. Thereby, energy is transferred from the power line voltage to a circuit that can drive a local microsystem. A benefit of this approach is that it is functional even without current flow. On the other hand, the electric field is inversely proportional to the conductor/ground distance leading to weak coupling in certain applications. Experimental prototypes have been reported mainly for power grid applications. In [106], a 0.1-m-diameter, 0.2-m-long cylindrical device was proposed. Tests on a 60 kV/50 Hz commercial power grid line demonstrated 16 mW of harvested power. In [108] a device of similar scale was shown to provide 23 mW, in laboratory tests using a 12.7 kV/50 Hz line. In [107], a noninvasive voltage metre solely powered by capacitive electrical field harvesting was demonstrated. A comparative overview of several other implementations can be found in [108]. As mentioned, the output performance of electrostatic power line harvesters relies on the electric field strength. Therefore, applications involving high voltage, single wire

non-shielded conductors and short line-to-ground distance could be of particular interest for this energy harvesting concept.

#### 4.3 Inductive Coupling for Energy Collection

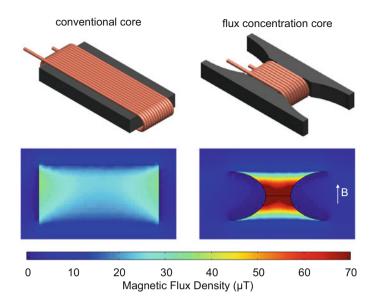

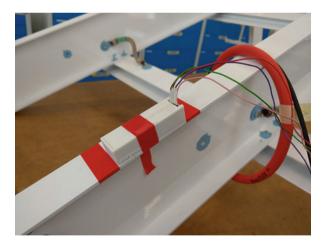

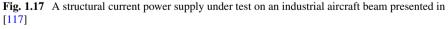

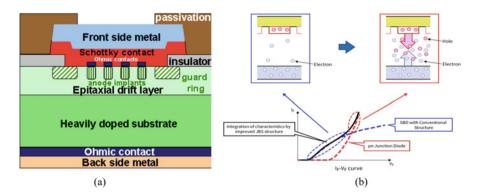

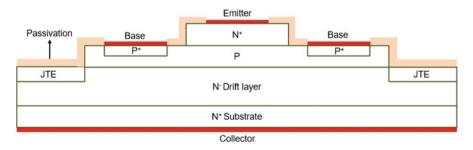

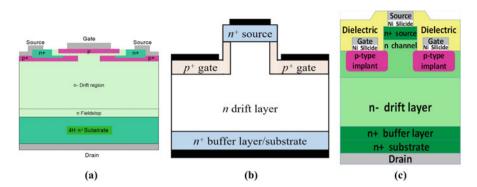

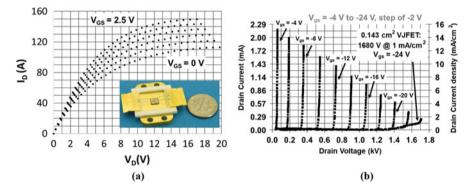

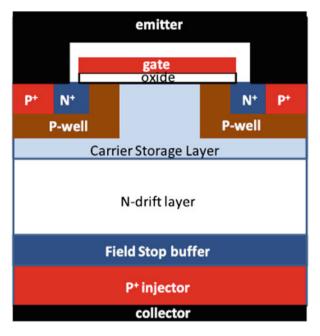

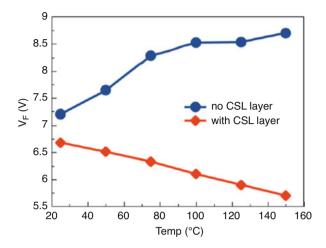

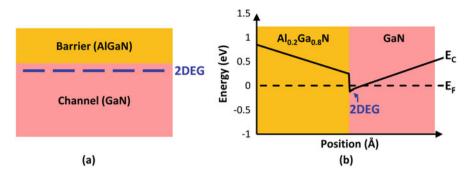

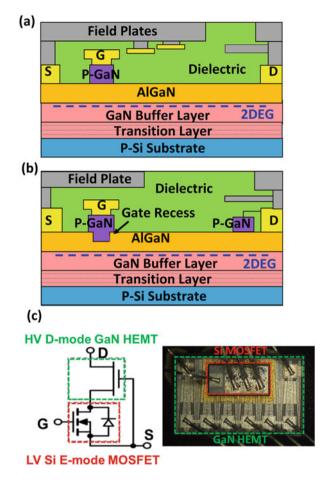

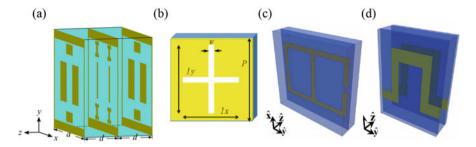

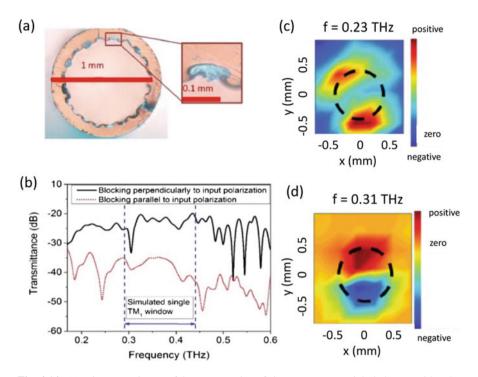

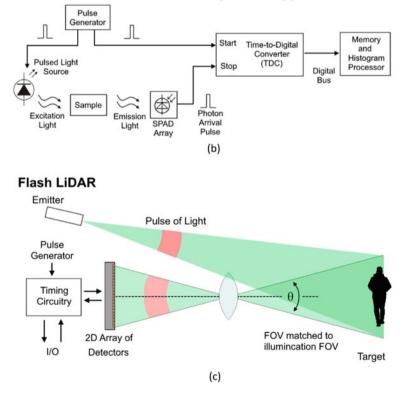

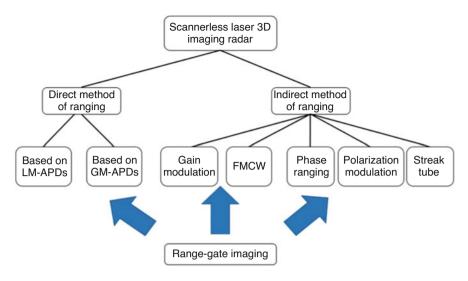

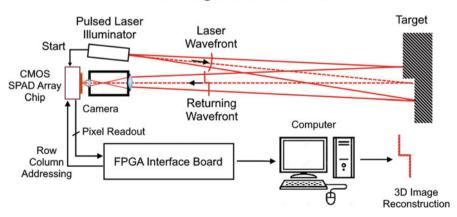

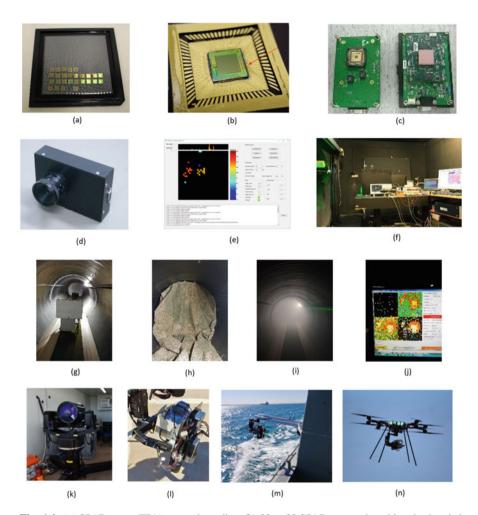

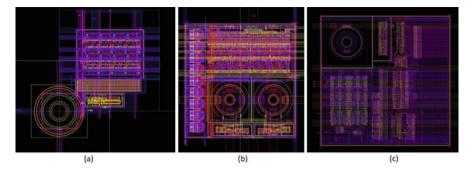

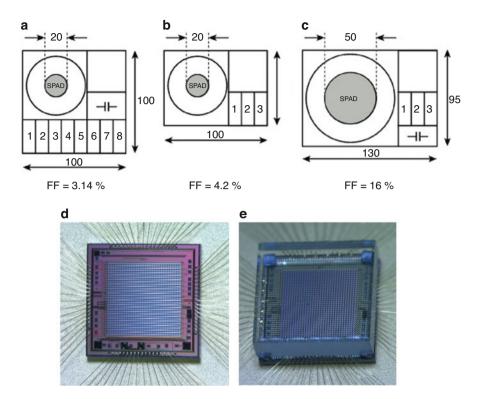

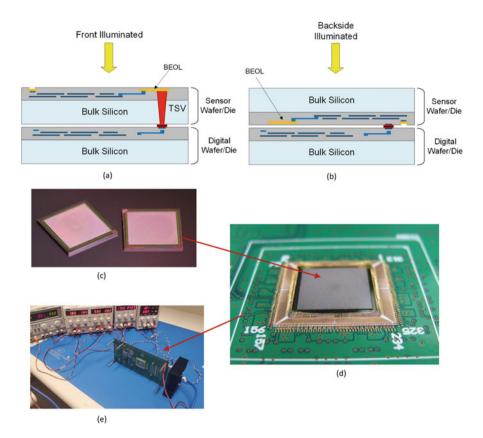

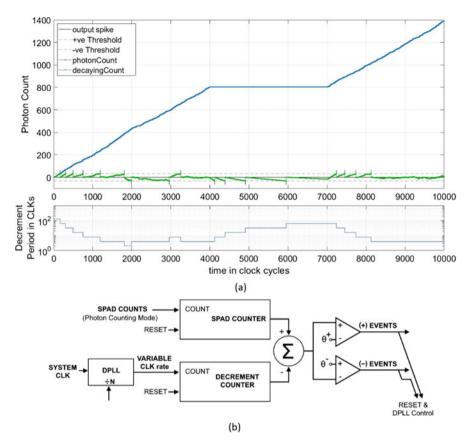

Inductive coupling is one of the main transduction methods used in energy harvesting. In addition, it is dominant in currently available wireless power transfer technologies. Therefore, research on coil design and flux engineering is of wide significance, and relevant to both environmental energy collection and wireless power distribution. In the rest of this section, a summary of indicative inductive energy harvesting devices developed for power lines is given. Subsequently, an overview of coil design and flux concentration considerations is presented, followed by a discussion of opportunities for further progress on electromagnetic energy harvesting in general.