Ana-Lucia Varbanescu Abhinav Bhatele Piotr Luszczek Baboulin Marc (Eds.)

# High Performance Computing

37th International Conference, ISC High Performance 2022 Hamburg, Germany, May 29 – June 2, 2022 Proceedings

## Lecture Notes in Computer Science 13289

#### Founding Editors

Gerhard Goos Karlsruhe Institute of Technology, Karlsruhe, Germany

Juris Hartmanis Cornell University, Ithaca, NY, USA

#### **Editorial Board Members**

Elisa Bertino Purdue University, West Lafayette, IN, USA

Wen Gao Peking University, Beijing, China

Bernhard Steffen D TU Dortmund University, Dortmund, Germany

Moti Yung D Columbia University, New York, NY, USA More information about this series at https://link.springer.com/bookseries/558

Ana-Lucia Varbanescu · Abhinav Bhatele · Piotr Luszczek · Baboulin Marc (Eds.)

## High Performance Computing

37th International Conference, ISC High Performance 2022 Hamburg, Germany, May 29 – June 2, 2022 Proceedings

*Editors* Ana-Lucia Varbanescu University of Twente Enschede, The Netherlands

Piotr Luszczek D University of Tennessee Knoxville, TN, USA Abhinav Bhatele University of Maryland College Park, MD, USA

Baboulin Marc Université Paris-Saclay Orsay, France

ISSN 0302-9743

ISSN 1611-3349 (electronic)

Lecture Notes in Computer Science

ISBN 978-3-031-07311-3

ISBN 978-3-031-07311-3

ISBN 978-3-031-07312-0 (eBook)

https://doi.org/10.1007/978-3-031-07312-0

© Springer Nature Switzerland AG 2022, corrected publication 2023

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

ISC High Performance Computing—formerly known as the International Supercomputing Conference—was founded in 1986 as the Supercomputer Seminar. Originally organized by Hans Meuer, Professor of Computer Science at the University of Mannheim, and former director of its computer center, the 1986 edition of the seminar brought together a group of 81 scientists and industrial partners who shared an interest in high-performance computing (HPC). Since then, the annual conference has become a major international event within the HPC community, growing beyond its humble beginnings, and moving out of Mannheim into other cities throughout the years: Frankfurt, Heidelberg, Dresden, Hamburg, Leipzig, and this year back to Hamburg. Prior to the coronavirus pandemic, the conference had seen a steady increase in the number of submissions of high-quality research papers and corresponding growth in the number of conference attendees. Benefiting from the improving health indicators, ISC-HPC 2022 was again held in person in Hamburg.

The call for papers to ISC-HPC 2022 was issued in Fall 2021, inviting the researchers, developers, and practitioners alike to submit their latest results for consideration for one of the five conference tracks: (1) Architecture, Networks, and Storage; (2) HPC Algorithms and Applications; (3) Machine Learning, AI, and Emerging Technologies; (4) Performance Modeling, Evaluation, and Analysis; and (5) Programming Environments and Systems Software. In all, 53 full submissions were received from authors all over the world. The Research Papers Program Committee consisted of 71 members from 18 countries. After initial reviews were completed, a rebuttal process offered authors an opportunity to respond to reviewers' questions and help clarify issues the reviewers might have had. A virtual Program Committee meeting was held to discuss all the papers and to finalize consensus on the papers. Finally, the committee selected 18 papers for publication.

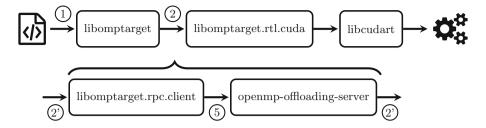

For the past several years, the ISC-HPC conference has presented an ISC-sponsored award to encourage outstanding research in HPC and to honor the overall best research paper submitted to the conference. Four years ago, this annual award was renamed in memory of the late Dr. Hans Meuer, who was general chair of the ISC-HPC conference from 1986 through 2014, and a co-founder of the TOP500 project. This year, from all research papers submitted, the Best Paper Committee selected the best paper based on its technical merit, its novelty, and impact on the HPC community. During a live ceremony, the following paper was awarded the Hans Meuer Award: *Remote OpenMP Offloading* by Atmn Patel from University of Waterloo, Canada, and Johannes Doerfert from Argonne National Laboratory, USA. The paper extended the canonical scope of OpenMP, which is traditionally confined to a shared memory domain, by utilizing the standard's modern features to offload the computational workload to GPU accelerators housed in remote cluster nodes. The Best Paper Committee appreciated the paper's unique combination of OpenMP familiarity and ease of use with accelerated and distributed computing that were accompanied by analysis of scaling capabilities. The winning paper also showed the

solution's versatility and how it could use multiple transport layers, each of which offers a different set of trade-offs between performance, portability, and scalability potential.

As the chairs of the Research Papers Committee, we would like to express our gratitude to our colleagues for submitting high-quality papers to all five ISC-HPC scientific tracks. Also, we wish to extend our thanks to the track, area, and conflict chairs, as well as the members of the Best Paper Committee, and finally to the Research Papers Committee that provided the reviews and manuscript evaluation throughout the submission stages. We hope to express our thanks in person during this year's meeting and upcoming ISC-HPC 2023.

May 2022

Ana Lucia Varbanescu Abhinav Bhatele

## Organization

## **Program Chair**

| Keren Bergman                     | Columbia University, USA                   |

|-----------------------------------|--------------------------------------------|

| Program Deputy Chair              |                                            |

| John Shalf                        | Lawrence Berkeley National Laboratory, USA |

| Research Papers Program Committee |                                            |

| <b>Research Papers Chairs</b>     |                                            |

| Ana Lucia Varbanescu (Chair)   | University of Amsterdam, Netherlands |

|--------------------------------|--------------------------------------|

| Abhinav Bhatele (Deputy Chair) | University of Maryland, USA          |

#### Architecture, Networks, and Storage

| Jay Lofstead (Chair)  | Sandia National Laboratories, USA               |

|-----------------------|-------------------------------------------------|

| Edson Borin           | University of Campinas, Brazil                  |

| Elsa Gonsiorowski     | Lawrence Livermore National Laboratory, USA     |

| Mozhgan Kabiri Chimeh | NVIDIA, UK                                      |

| Nectarios Koziris     | National Technical University of Athens, Greece |

| Michael Kuhn          | Otto von Guericke University Magdeburg,         |

|                       | Germany                                         |

| Jay Lofstead          | Sandia National Laboratories, USA               |

| Preeti Malakar        | Indian Institute of Technology Kanpur, India    |

| Dhabaleswar Panda     | Ohio State University, USA                      |

| Guangming Tan         | Institute of Computing Technology (ICT), China  |

| Osamu Tatebe          | University of Tsukuba, Japan                    |

| Carsten Trinitis      | Technical University of Munich, Germany         |

| Venkatram Vishwanath  | Argonne National Laboratory, USA                |

|                       |                                                 |

#### **HPC Algorithms and Applications**

| m Unat (Chair) | Koç University, Turkey                                                     |

|----------------|----------------------------------------------------------------------------|

| h Abdulah      | KAUST, Saudi Arabia                                                        |

| net Belviranli | Colorado School of Mines, USA                                              |

| Cai            | Simula Research Laboratory and University of Oslo, Norway                  |

| net Belviranli | Colorado School of Mines, USA<br>Simula Research Laboratory and University |

| Lin Gan              | Tsinghua University and National<br>Supercomputing Center in Wuxi, China |

|----------------------|--------------------------------------------------------------------------|

| Clemens Grelck       | University of Amsterdam, Netherlands                                     |

| Fuerlinger Karl      | Ludwig Maximilian University Munich (LMU),<br>Germany                    |

| Kamer Kaya           | Sabancı University, Turkey                                               |

| Simon McIntosh-Smith | University of Bristol, UK                                                |

| Gabriel Noaje        | NVIDIA, Singapore                                                        |

| Lena Oden            | Fernuniversität in Hagen and Forschungszentrum<br>Jülich GMBH, Germany   |

| Johann Rudi          | Argonne National Laboratory, USA                                         |

| Tuğba Torun          | Koç University, Turkey                                                   |

| Miwako Tsuji         | RIKEN, Japan                                                             |

|                      |                                                                          |

#### Machine Learning, AI, and Emerging Technologies

| Theodore L. Willke (Chair) | Intel Corporation, USA                          |

|----------------------------|-------------------------------------------------|

| Nikoli Dryden              | ETH Zurich, Switzerland                         |

| Gurbinder Gill             | Katana Graph Inc., USA                          |

| Jiajia Li                  | William and Mary College, USA                   |

| Maryam Mehri Dehnavi       | University of Toronto, Canada                   |

| Bogdan Nicolae             | Argonne National Laboratory, USA                |

| Mostofa Patwary            | NVIDIA, USA                                     |

| Shaden Smith               | Microsoft, USA                                  |

| Edgar Solomonik            | University of Illinois at Urbana-Champaign, USA |

| Sofia Vallecorsa           | CERN, Switzerland                               |

| Abhinav Vishnu             | AMD, USA                                        |

| Yang You                   | National University of Singapore, Singapore     |

## Performance Modeling, Evaluation, and Analysis

| Nathan Tallent (Chair) | Pacific Northwest National Laboratory, USA  |

|------------------------|---------------------------------------------|

| Ivy B. Peng            | Lawrence Livermore National Laboratory, USA |

| Alexandru Calotoiu     | ETH Zürich, Germany                         |

| Marc Casas             | Barcelona Supercomputing Center, Spain      |

| Tom Deakin             | University of Bristol, UK                   |

| Seyong Lee             | ORNL, USA                                   |

| Simon McIntosh-Smith   | University of Bristol, UK                   |

| Xiaozhu Meng           | Rice University, USA                        |

| Bernd Mohr             | Juelich Supercomputing Centre, Germany      |

| Scott Pakin            | Los Alamos National Laboratory, USA         |

| Xian-He Sun            | Illinois Institute of Technology, USA       |

| Jidong Zhai            | Tsinghua University, China                  |

| Tianwei Zhang          | Nanyang Technological University, Singapore |

|                        |                                             |

## Programming Environments and Systems Software

| Michele Weiland (Chair) | EPCC, University of Edinburgh, UK           |

|-------------------------|---------------------------------------------|

| Bilel Hadri             | KAUST Supercomputing Laboratory,            |

|                         | Saudi Arabia                                |

| Guido Juckeland         | HZDR, Germany                               |

| Michael Klemm           | AMD and OpenMP ARB, Germany                 |

| Pouya Kousha            | Ohio State University, USA                  |

| John L. inford          | Arm, USA                                    |

| István Z. Reguly        | Pázmány Péter Catholic University, Hungary  |

| Harvey Richardson       | Hewlett Packard Enterprise, UK              |

| Martin Ruefenacht       | Leibniz Supercomputing Centre, Germany      |

| Roxana Rusitoru         | Arm, UK                                     |

| Thomas R. W. Scogland   | Lawrence Livermore National Laboratory, USA |

| Simon Smart             | ECMWF, UK                                   |

| Hiroyuki Takizawa       | Tohoku University, Japan                    |

| Christian Terboven      | RWTH Aachen University, Germany             |

| Justs Zarins            | EPCC, University of Edinburgh, UK           |

|                         |                                             |

## **Birds of a Feather Committee**

| Roman Wyrzykowski (Chair)    | Czestochowa University of Technology, Poland                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------|

| Iosif Meyerov (Deputy Chair) | Lobachevsky State University of Nizhni                                                              |

|                              | Novogorod, Russia                                                                                   |

| Michael Bader                | Technical University of Munich, Germany                                                             |

| Claudia Blaas-Schenner       | TU Wien, VSC Research Center, Austria                                                               |

| Dominik Göddeke              | University of Stuttgart, Germany                                                                    |

| Aleksandar Ilic              | INESC-ID and Universidade de Lisboa, Portugal                                                       |

| Jacek Kitowski               | AGH University of Science and Technology,<br>Poland                                                 |

| Dieter Kranzlmueller         | Ludwig Maximilian University Munich (LMU)<br>and Leibniz Rechenzentrum, Germany                     |

| Carola Kruse                 | Centre Européen de Recherche et de Formation<br>Avancée en Calcul Scientifique (CERFACS),<br>France |

| Krzysztof Kurowski           | Poznań Supercomputing and Networking Center,<br>Poland                                              |

| Marco Lapegna                | University of Naples Federico II, Italy                                                             |

| Simon McIntosh-Smith         | University of Bristol, UK                                                                           |

| Iosif Meyerov                | Lobachevsky State University of Nizhni<br>Novogorod, Russia                                         |

| Koji Nakano                  | Hiroshima University, Japan                                                                         |

| Gabriel Oksa                 | Slovak Academy of Sciences, Slovakia                                                                |

| Dana Petcu                   | West University of Timisoara, Romania                                                               |

| Antonio J. Peña    | Barcelona Supercomputing Center, Spain                                                                  |

|--------------------|---------------------------------------------------------------------------------------------------------|

| Thomas Rauber      | University of Bayreuth, Germany                                                                         |

| Lubomir Riha       | IT4Innovations National Supercomputing Center<br>and Technical University of Ostrava,<br>Czech Republic |

|                    | 1                                                                                                       |

| Masha Sosonkina    | Old Dominion University, USA                                                                            |

| Vladimir Stegailov | Higher School of Economics and JIHT RAS,<br>Russia                                                      |

| Dave Turner        | Kansas State University, USA                                                                            |

| Bora Ucar          | CNRS and ENS-Lyon, France                                                                               |

## **Project Posters Committee**

| Christian Perez (Chair)              | Inria, France                                                                        |

|--------------------------------------|--------------------------------------------------------------------------------------|

| Are Magnus Bruaset<br>(Deputy Chair) | Simula Research Laboratory, Norway                                                   |

| Marco Aldinucci                      | University of Torino, Italy                                                          |

| Bartosz Bosak                        | Poznań Supercomputing and Networking Center,<br>Poland                               |

| Nick Brown                           | EPCC, University of Edinburgh, UK                                                    |

| Theodoros Christoudias               | The Cyprus Institute, Cyprus                                                         |

| Andrew Ensor                         | Auckland University of Technology, New Zealand                                       |

| Ana Gainaru                          | Oak Ridge National Laboratory, USA                                                   |

| Andra Hugo                           | Apple, France                                                                        |

| Kamer Kaya                           | Sabancı University, Turkey                                                           |

| Francesc Lordan Gomis                | Barcelona Supercomputing Center, Spain                                               |

| Maciej Malawski                      | Sano Centre for Computational Medicine,<br>Institute of Computer Science AGH, Poland |

| Kengo Nakajima                       | University of Tokyo and RIKEN, Japan                                                 |

| Bogdan Nicolae                       | Argonne National Laboratory, USA                                                     |

| Eric Petit                           | Intel, France                                                                        |

| Phil Ridley                          | Arm, UK                                                                              |

| Jonathan Rouzaud-Cornabas            | Inria and INSA de Lyon, France                                                       |

| Kentaro Sano                         | RIKEN, Japan                                                                         |

| Francieli Zanon Boito                | Inria, France                                                                        |

| Ameli Chi Zhou                       | Shenzhen University, China                                                           |

## **Research Posters Committee**

| Aparna Chandramowlishwaran<br>(Chair) | UCI, USA                                                                    |

|---------------------------------------|-----------------------------------------------------------------------------|

| Hartwig Anzt                          | Karlsruhe Institute of Technology, Germany and University of Tennessee, USA |

Maryam Mehri Dehnavi Jee Choi Ana Gainaru Lin Gan

Amal Khabou Mariam Kiran Penporn Koanantakool Ronald Kriemann Ang Li Jiajia Li Piyush Sao Christian Terboven Bo Wu Rio Yokota Rohit Zambre

## **Tutorials Committee**

Kathryn Mohror (Chair) Suren Byna (Deputy Chair) Ritu Arora Rosa M. Badia Wahid Bhimji Philip Carns James Dinan Ann Gentile Tanzima Islam Simon McIntosh-Smith Diana Moise Sarah Neuwirth C I Newburn Dhabaleswar Panda Raghunath Raja Chandrasekar Michela Taufer Michele Weiland

## Workshops Committee

Hartwig Anzt (Chair)

Amanda Bienz (Deputy Chair) Cody Balos University of Toronto, Canada University of Oregon, USA Oak Ridge National Laboratory, USA Tsinghua University and National Supercomputing Center in Wuxi, China Université Paris-Saclay, France Lawrence Berkeley National Laboratory, USA Google LLC, USA MPI for Math. i.t.S., Germany Pacific Northwest National Laboratory, USA William and Mary College, USA Oak Ridge National Laboratory, USA **RWTH** Aachen University, Germany Colorado School of Mines, USA Tokyo Institute of Technology, Japan AMD Research, USA

Lawrence Livermore National Laboratory, USA Lawrence Berkeley National Laboratory, USA University of Texas at San Antonio, USA Barcelona Supercomputing Center, Spain Lawrence Berkeley National Laboratory, USA Argonne National Laboratory, USA NVIDIA, USA Sandia National Laboratories, USA Texas State University, USA University of Bristol, UK Cray, and HPE, Switzerland Goethe-University Frankfurt, Germany NVIDIA, USA Ohio State University, USA Frau, USA The University of Tennessee, USA EPCC – University of Edinburgh, UK

Karlsruhe Institute of Technology, Germany and University of Tennessee, USA University of New Mexico, USA Lawrence Livermore National Laboratory, USA

| Harun Bayraktar          | NVIDIA, USA                                     |

|--------------------------|-------------------------------------------------|

| Natalie Beams            | University of Tennessee, USA                    |

| Luc Berger-Vergiat       | Sandia National Laboratories, USA               |

| George Bosilca           | University of Tennessee, USA                    |

| Lisa Claus               | LBNL, USA                                       |

| Terry Cojean             | Karlsruhe Institute of Technology, Germany      |

| Anthony Danalis          | University of Tennessee Knoxville, USA          |

| Edoardo Di Napoli        | Juelich Supercomputing Centre, Germany          |

| Markus Goetz             | Karlsruhe Institute of Technology, Germany      |

| Aditya Kashi             | Karlsruhe Institute of Technology, Germany      |

| Sarah Knepper            | Intel, USA                                      |

| Andreas Knuepfer         | Technische Universität Dresden, Germany         |

| Martin Kronbichler       | Technical University of Munich, Germany         |

| Weifeng Liu              | China University of Petroleum, China            |

| Simone Pezzuto           | Università della Svizzera italiana, Switzerland |

| Enrique S. Quintana-Orti | Universitat Politècnica de València, Spain      |

| Estela Suarez            | Jülich Supercomputing Centre, Germany           |

| Nico Trost               | AMD, Germany                                    |

| Markus Wittmann          | Friedrich-Alexander-Universität                 |

|                          |                                                 |

#### HPC in Asia Committee

| Kento Sato (Chair)       | RIKEN, Japan                         |

|--------------------------|--------------------------------------|

| James Lin (Deputy Chair) | Shanghai Jiao Tong University, China |

## **Inclusivity Committee**

Laura Schulz (Chair) Frau, Germany

## **Publicity Committee**

Carsten Trinitis (Chair)

Technical University of Munich, Germany

Erlangen-Nürnberg, Germany

#### **Proceedings Chairs**

| Piotr Luszczek (Chair)       | University of Tennessee, USA    |

|------------------------------|---------------------------------|

| Marc Baboulin (Deputy Chair) | Université Paris-Saclay, France |

## Contents

#### Architecture, Networks, and Storage

| Accelerating MPI All-to-All Communication with Online Compression                                                                                                                                             | -   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| on Modern GPU Clusters                                                                                                                                                                                        | 3   |

| Kawthar Shafie Khorassani, Aamir Shafi, Hari Subramoni,<br>and Dhabaleswar K. Panda                                                                                                                           |     |

| NVIDIA's Quantum InfiniBand Network Congestion Control Technology                                                                                                                                             |     |

| and Its Impact on Application Performance                                                                                                                                                                     | 26  |

| Yuval Shpigelman, Gilad Shainer, Richard Graham, Yong Qin,<br>Gerardo Cisneros-Stoianowski, and Craig Stunkel                                                                                                 |     |

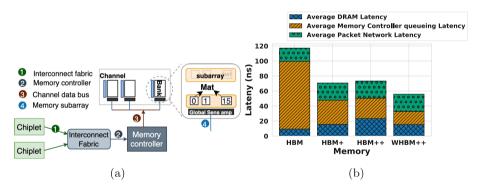

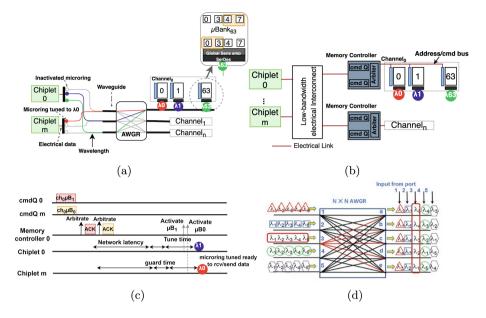

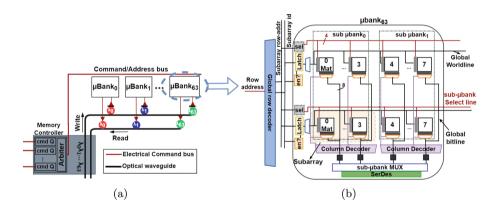

| LLM: Realizing Low-Latency Memory by Exploiting Embedded Silicon<br>Photonics for Irregular Workloads                                                                                                         | 44  |

| Marjan Fariborz, Mahyar Samani, Pouya Fotouhi, Roberto Proietti,<br>Il-Min Yi, Venkatesh Akella, Jason Lowe-Power, Samuel Palermo,<br>and S. J. Ben Yoo                                                       | 44  |

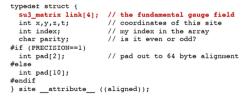

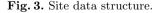

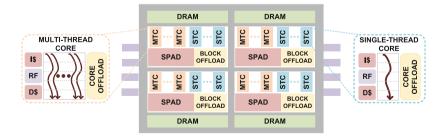

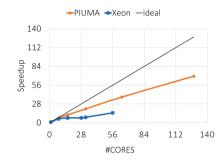

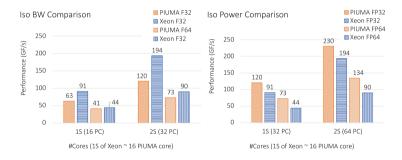

| SU3_Bench on a Programmable Integrated Unified Memory Architecture                                                                                                                                            |     |

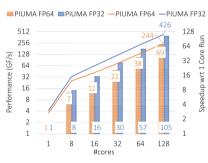

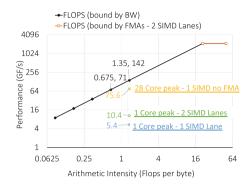

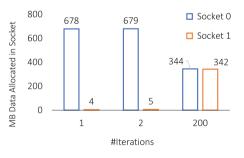

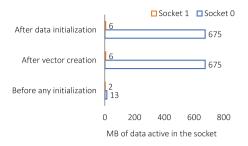

| (PIUMA) and How that Differs from Standard NUMA CPUs<br>Jesmin Jahan Tithi, Fabio Checconi, Douglas Doerfler,<br>and Fabrizio Petrini                                                                         | 65  |

| Machine Learning, AI, and Emerging Technologies                                                                                                                                                               |     |

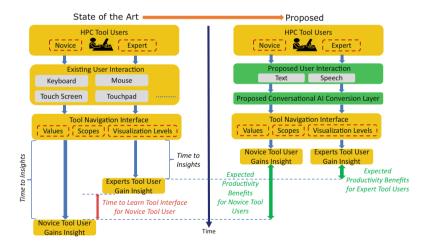

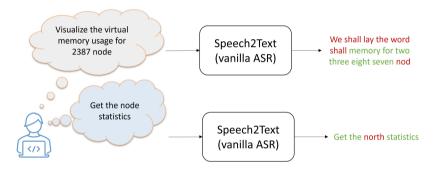

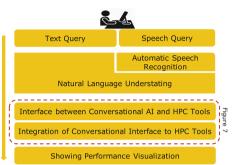

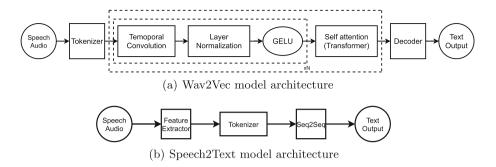

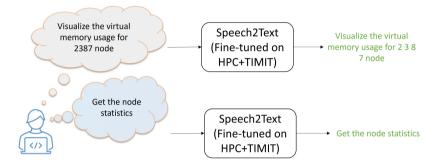

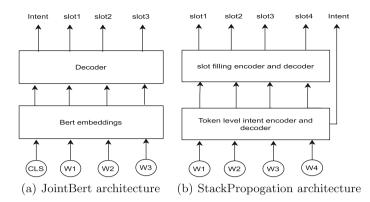

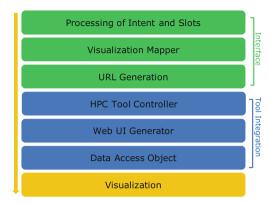

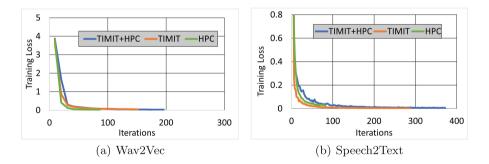

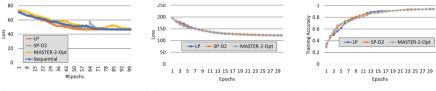

| "Hey CAI" - Conversational AI Enabled User Interface for HPC Tools<br>Pouya Kousha, Arpan Jain, Ayyappa Kolli, Saisree Miriyala,<br>Prasanna Sainath, Hari Subramoni, Aamir Shafi,<br>and Dhableswar K. Panda | 87  |

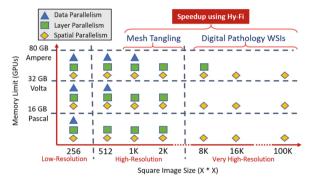

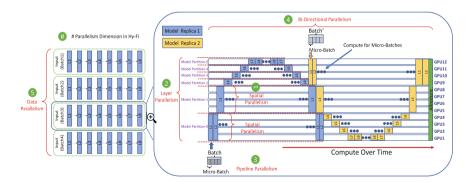

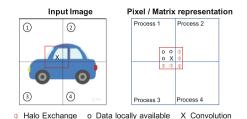

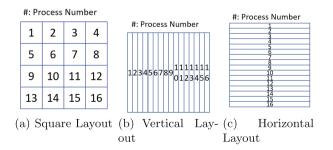

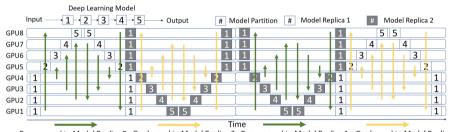

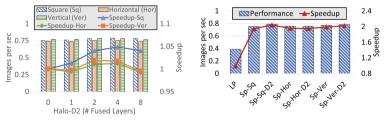

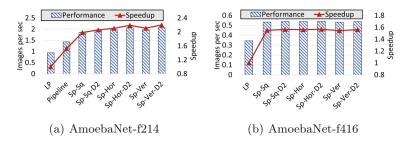

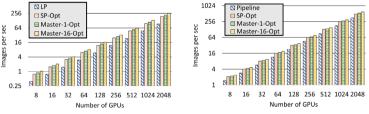

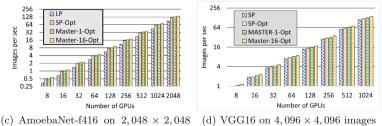

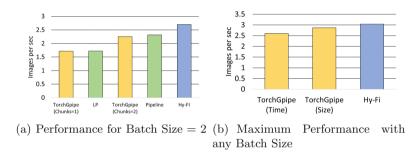

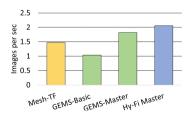

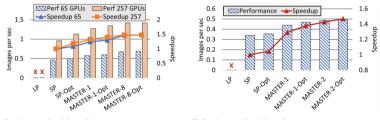

| Hy-Fi: <u>Hy</u> brid <u>Fi</u> ve-Dimensional Parallel DNN Training<br>on High-Performance GPU Clusters                                                                                                      | 109 |

| America Annia Control Clusters                                                                                                                                                                                | 109 |

Arpan Jain, Aamir Shafi, Quentin Anthony, Pouya Kousha, Hari Subramoni, and Dhableswar K. Panda

## HPC Algorithms and Applications

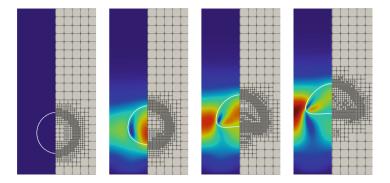

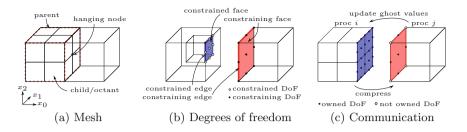

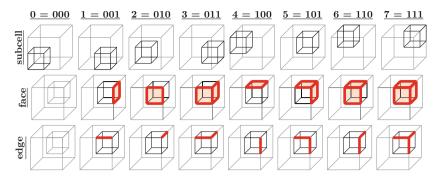

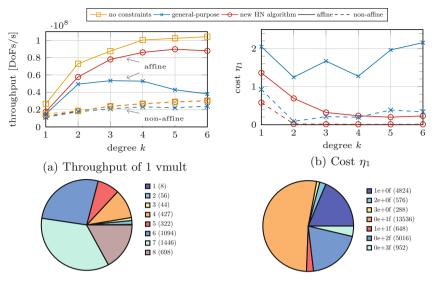

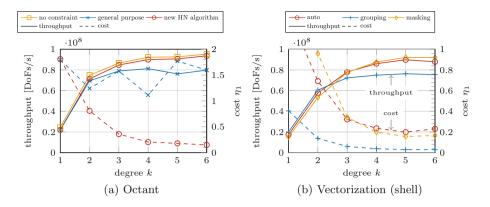

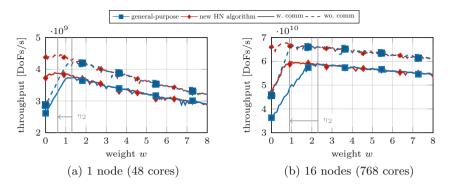

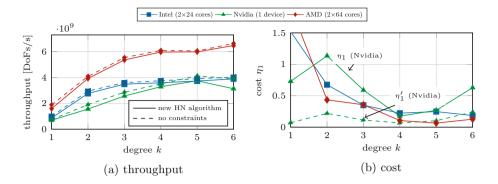

| Efficient Application of Hanging-Node Constraints for Matrix-Free<br>High-Order FEM Computations on CPU and GPU<br>Peter Munch, Karl Ljungkvist, and Martin Kronbichler                   | 133 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Dynamic Task Fusion for a Block-Structured Finite Volume Solver<br>over a Dynamically Adaptive Mesh with Local Time Stepping<br>Baojiu Li, Holger Schulz, Tobias Weinzierl, and Han Zhang | 153 |

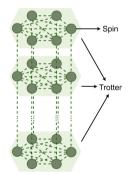

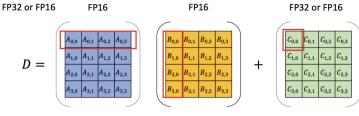

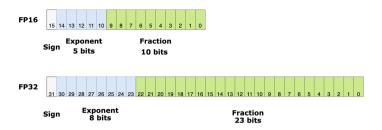

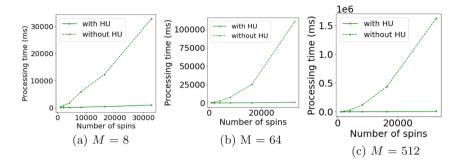

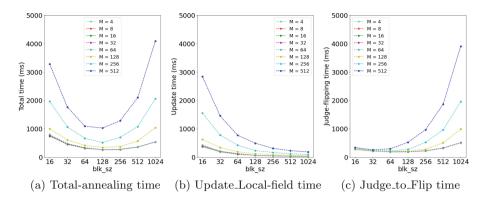

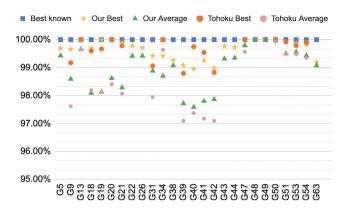

| Accelerating Simulated Quantum Annealing with GPU and Tensor Cores<br>Yi-Hua Chung, Cheng-Jhih Shih, and Shih-Hao Hung                                                                    | 174 |

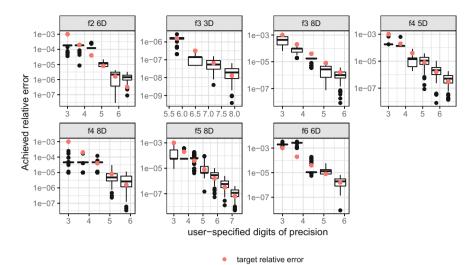

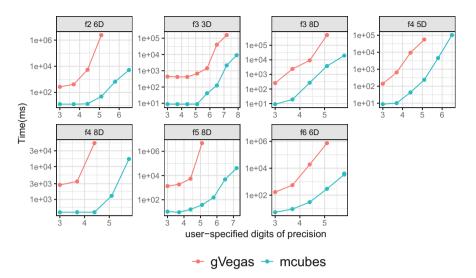

| <i>m</i> -CUBES: An Efficient and Portable Implementation of Multi-dimensional<br>Integration for GPUs                                                                                    | 192 |

| Performance Modeling, Evaluation, and Analysis                                                                                                                                            |     |

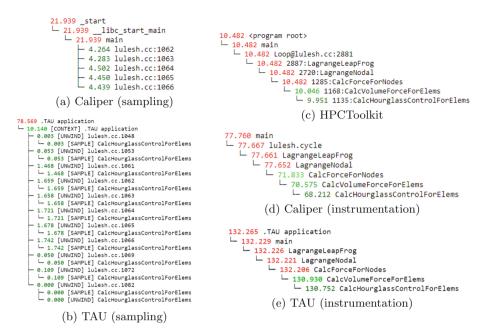

| Comparative Evaluation of Call Graph Generation by Profiling Tools<br>Onur Cankur and Abhinav Bhatele                                                                                     | 213 |

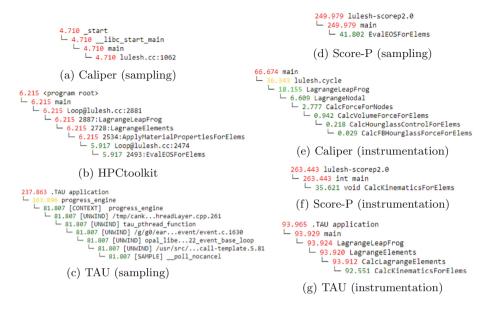

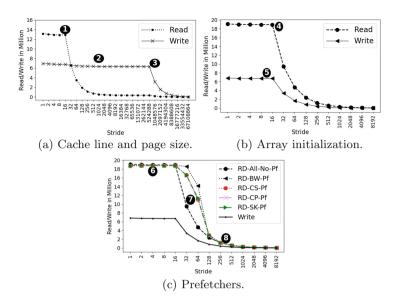

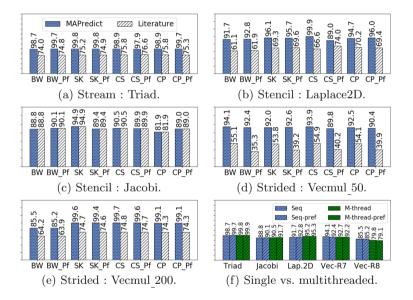

| MAPredict: Static Analysis Driven Memory Access Prediction Framework<br>for Modern CPUs<br>Mohammad Alaul Haque Monil, Seyong Lee, Jeffrey S. Vetter,<br>and Allen D. Malony              | 233 |

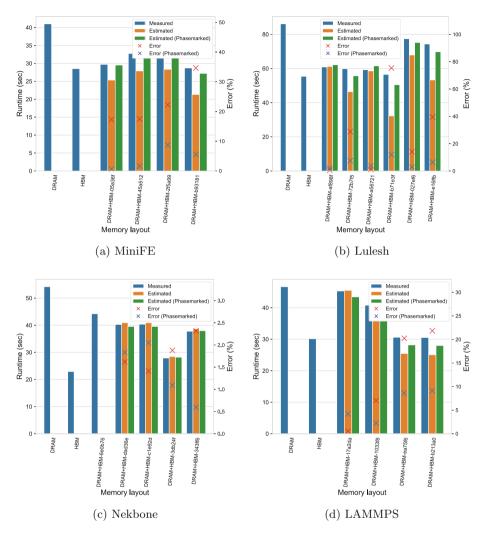

| Rapid Execution Time Estimation for Heterogeneous Memory Systems<br>Through Differential Tracing                                                                                          | 256 |

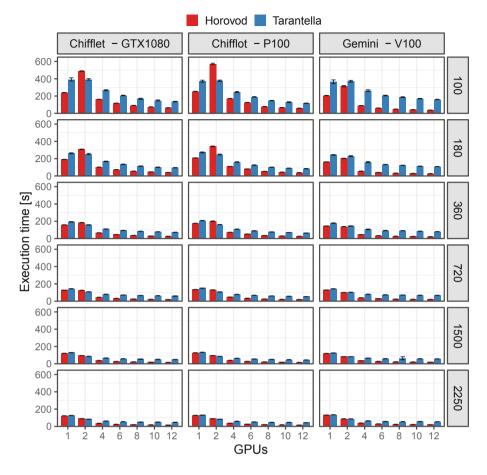

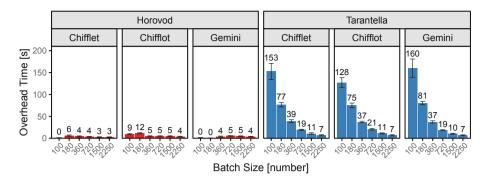

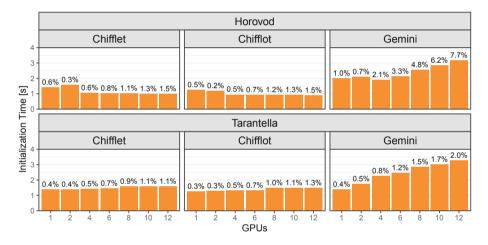

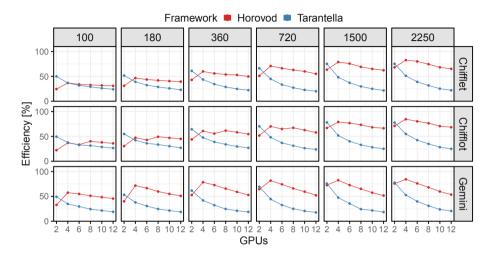

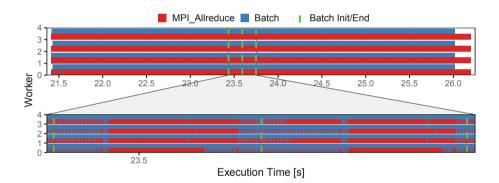

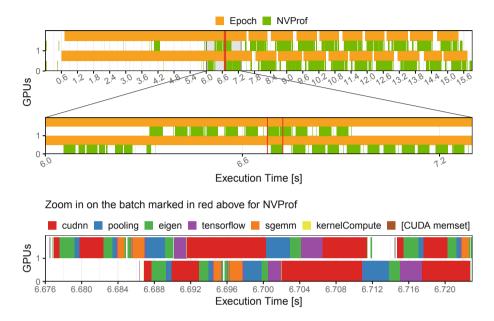

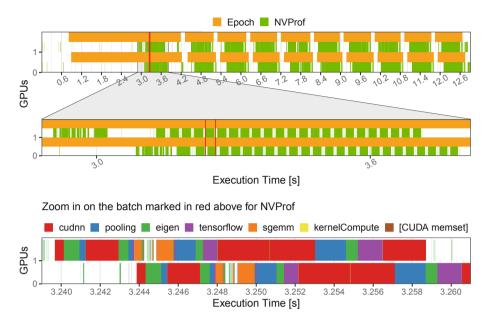

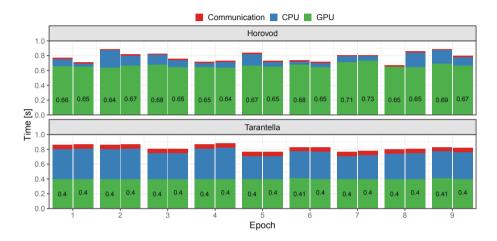

| Understanding Distributed Deep Learning Performance by Correlating<br>HPC and Machine Learning Measurements<br>Ana Luisa Veroneze Solórzano and Lucas Mello Schnorr                       | 275 |

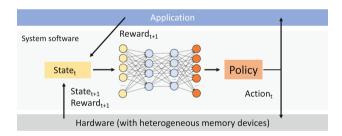

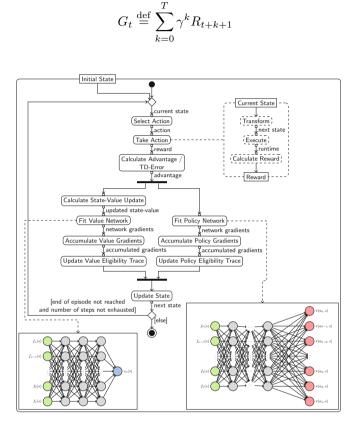

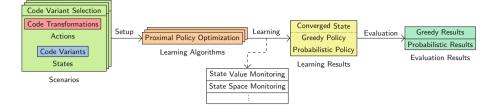

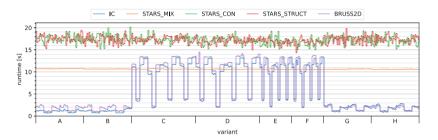

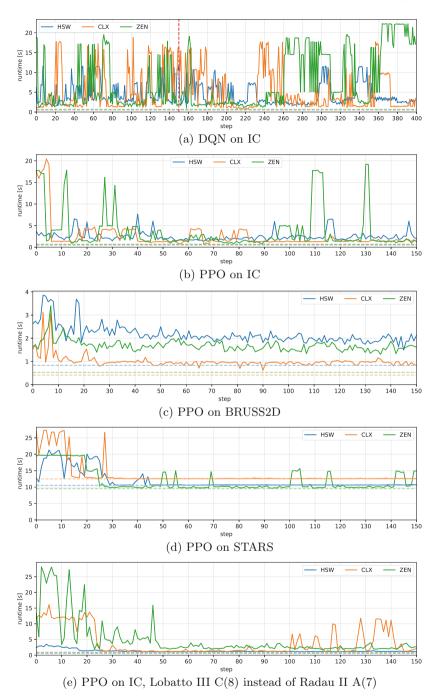

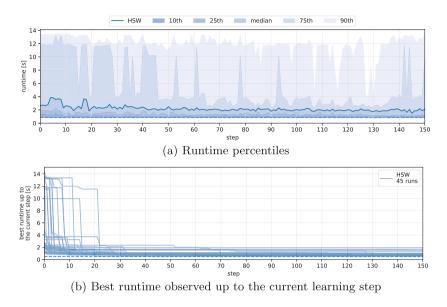

| A Motivating Case Study on Code Variant Selection by Reinforcement<br>Learning<br>Oliver Hacker, Matthias Korch, and Johannes Seiferth                                                    | 293 |

| Programming Environments and System Software                                                                                                                                              |     |

| Remote OpenMP Offloading                                                                                                                                                                  | 315 |

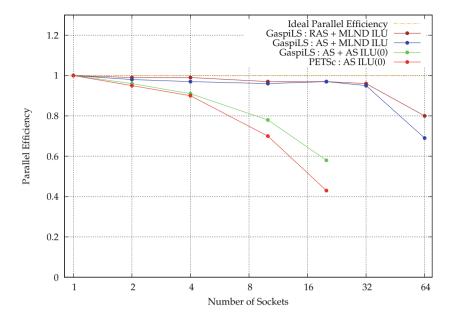

| Hybrid Parallel ILU Preconditioner in Linear Solver Library GaspiLS<br>Raju Ram, Daniel Grünewald, and Nicolas R. Gauger                                                                                                        | 334 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

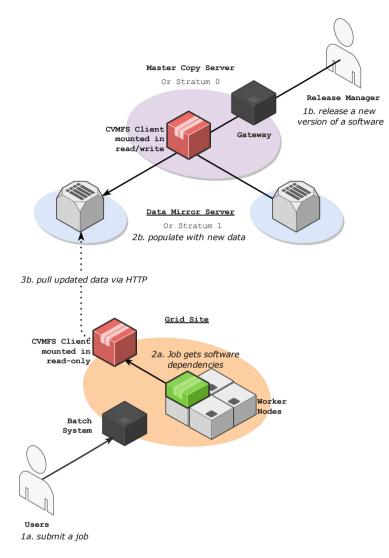

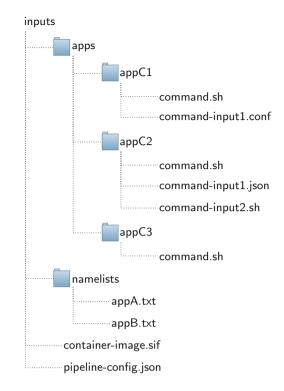

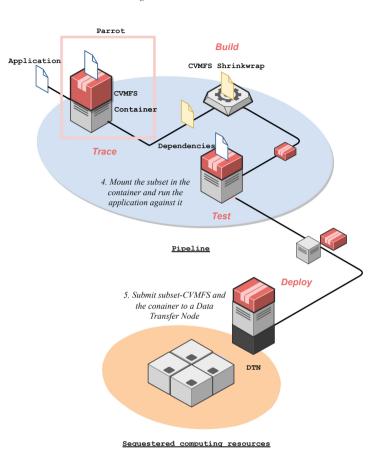

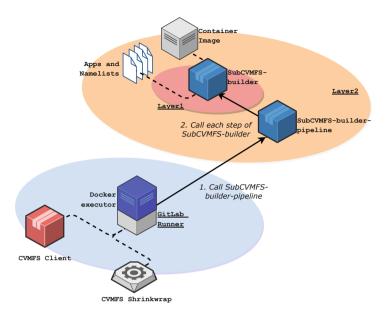

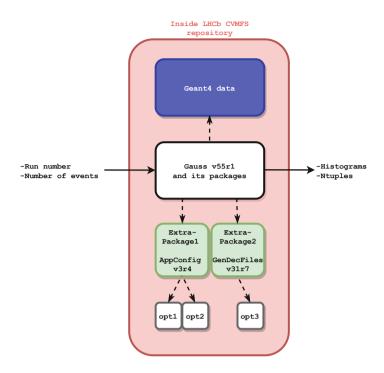

| A Subset of the CERN Virtual Machine File System: Fast Delivering<br>of Complex Software Stacks for Supercomputing Resources                                                                                                    | 354 |

| Correction to: "Hey CAI" - Conversational AI Enabled User Interface<br>for HPC Tools<br>Pouya Kousha, Arpan Jain, Ayyappa Kolli, Saisree Miriyala,<br>Prasanna Sainath, Hari Subramoni, Aamir Shafi,<br>and Dhableswar K. Panda | C1  |

| Author Index                                                                                                                                                                                                                    | 373 |

Architecture, Networks, and Storage

## Accelerating MPI All-to-All Communication with Online Compression on Modern GPU Clusters

Qinghua Zhou<sup>(⊠)</sup>, Pouya Kousha, Quentin Anthony, Kawthar Shafie Khorassani, Aamir Shafi, Hari Subramoni, and Dhabaleswar K. Panda

The Ohio State University, Columbus, OH 43210, USA {zhou.2595,kousha.2,anthony.301,shafiekhorassani.1,shafi.16, subramoni.1,panda.2}@osu.edu

Abstract. As more High-Performance Computing (HPC) and Deep Learning (DL) applications are adapting to scale using GPUs, the communication of GPU-resident data is becoming vital to end-to-end application performance. Among the available MPI operations in such applications, All-to-All is one of the most communication-intensive operations that becomes the bottleneck of efficiently scaling applications to larger GPU systems. Over the last decade, most research has focused on the optimization of large GPU-resident data transfers. However, for stateof-the-art GPU-Aware MPI libraries, MPI\_Alltoall communication for large GPU-resident data still suffers from poor performance due to the throughput limitation of commodity networks. However, the development of GPU-based compression algorithms with high throughput can reduce the volume of data transferred. The recent research of point-topoint-based online compression with these compression algorithms has shown potential on modern GPU clusters.

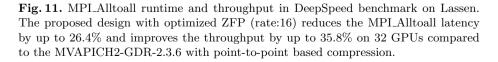

In this paper, we redesign an MPI library to enable efficient collectivelevel online compression with an optimized host-staging scheme for All-to-All communication. We demonstrate that the proposed design achieves benefits at both microbenchmark and application levels. At the microbenchmark level, the proposed design can reduce the All-to-All communication latency by up to 87%. For PSDNS, a traditional HPC application, our proposed design can reduce the All-to-All communication latency and total runtime by up to 29.2% and 21.8%, respectively, while ensuring data validation and not affecting the application convergence time. For Microsoft's DeepSpeed, a DL optimization library, the proposed design reduces the MPLAlltoall runtime by up to 26.4% compared to a state-of-the-art MPI library with point-to-point compression while ensuring data validation. To the best of our knowledge, this is the first work that leverages online GPU-based compression techniques to significantly accelerate MPLAlltoall communication for HPC and DL applications.

© Springer Nature Switzerland AG 2022

<sup>\*</sup>This research is supported in part by NSF grants #1818253, #1854828, #1931537, #2007991, #2018627, #2112606, and XRAC grant #NCR-130002.

A.-L. Varbanescu et al. (Eds.): ISC High Performance 2022, LNCS 13289, pp. 3–25, 2022. https://doi.org/10.1007/978-3-031-07312-0\_1

Keywords: All-to-All  $\cdot$  GPU  $\cdot$  Compression  $\cdot$  GPU-Aware MPI  $\cdot$  HPC  $\cdot$  DL

#### 1 Introduction

Emerging high-performance computing (HPC) and cloud computing systems are widely adopting Graphics Processing Units (GPUs) to support the computational power required by modern scientific and deep learning (DL) applications. By offering high-bandwidth memory, tensor processing, and massive parallelism, GPUs enable running complex applications such as weather forecasting, brain data visualization, and molecular dynamics. MPI is the de facto communication standard widely used in developing parallel scientific applications on HPC systems. To further enhance the high compute power of current generation of hardware, researchers are building large-scale GPU clusters to benefit from massive computation capabilities offered by these accelerators.

Due to the computing power offered by GPUs, a large range of applications have been adapted to scale on GPU-based systems by application developers. Communication performance plays a vital role in end-to-end application performance on such systems. In fact, at a large scale, the communication operations become the performance bottleneck for any massively parallel HPC and DL application. Over the last decade, researchers have significantly optimized data transfers in MPI for GPU-resident data [2,21,24]. Inter-node communication operations for large messages are highly optimized to saturate the bandwidth of the InfiniBand network by the state-of-the-art MPI libraries [9,24]. [32] has shown the saturated inter-node network bandwidth of the state-of-the-art MPI libraries. Although these MPI libraries are well optimized, the communication time at the application level is still a major bottleneck for many HPC and DL applications. Since the inter-node communication bandwidth is already saturated via optimizations implemented by major MPI libraries, we should seek other innovative ways to reduce the communication time of the HPC applications.

Thinking outside the box, we propose exploiting compression to aid with optimizing the performance of MPI stacks and HPC/DL applications, subsequently. Compression can reduce the amount of data that needs to be transmitted and/or stored helping to mitigate the cost of communication. Various compression techniques have been proposed in the literature diving into CPU-based algorithms and GPU-based algorithms. The common issue with CPU-based algorithms is the low throughput compared to GPU-based designs [14,31]. Existing GPU-based compression schemes such as MPC [31], SZ [3], and ZFP [14] are typically focused on achieving a high compression ratio and not absolute high performance.

#### 1.1 Motivation

There are challenging aspects to consider when applying compression to the HPC domain. HPC requires low overhead while maintaining high throughput. Further, some HPC applications require that the underlying compression and decompression operations are handled by the MPI library, leaving the HPC/DL application unchanged. We refer to this qualifier as "Online" compression. Online compression means the message should be compressed and decompressed in real-time inside the MPI library during a communication operation without any modifications to the end applications. This implies that the online compression algorithms should be self-contained with low overheads. Meeting these requirements first before maximizing the compression ratio and revamping the communication pattern/algorithm to fully exploit the HPC system's available transfer bandwidth is a challenging task that we undertake in this paper.

Since most MPI users are domain scientists first and programmers second, modifying the application to use compression is often out of reach. Adding support often involves understanding compression techniques and when to apply them based on message features such as size. Therefore, using compression directly in HPC/DL applications is a daunting task for domain scientists. In this context, [32] proposed an online compression enabled MPI library for pointto-point operations—this is an initial work in this direction.

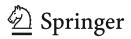

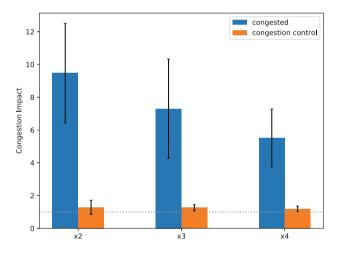

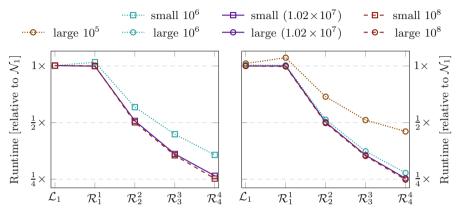

**Fig. 1.** Motivating Example: All-to-all communication time for 8 GPUs on 2 Longhorn nodes. The observed message range in PSDNS is 1.2 MB to 9.5 MB. With more GPUs, All-to-all communication time becomes dominant within the overall runtime of PSDNS application.

In this paper, we use the online compression idea to optimize the performance of MPI collective operations and improve HPC/DL application performance. One of the most communication-intensive operations is MPI\_Alltoall which is used in many applications like PSDNS [23] and DeepSpeed [22]. DeepSpeed depends on MPI\_Alltoall to support the addition of Mixture-of-Experts [10]. As shown in the Fig. 1(a), with larger scale, the MPI\_Alltoall time dominates the overall execution time of the PSDNS application. Figure 1(b) shows the message size range of MPI\_Alltoall operations observed in PSDNS application. In this context, the MPI\_Alltoall operation is ideally suited to benefit from compression since it is the most dense communication operation used in various HPC and DL applications.

#### 1.2 Challenges

To design an efficient online compression scheme for MPLAlltoall operation, following research challenges need to be addressed.

Challenge-1: The Limitation of Point-to-Point Based Online Compression Technique: MVAPICH2-GDR-2.3.6 is the only public library that has support for online compression. Table 1 summarizes the representative MPI\_Alltoall algorithms in the MVAPICH2-GDR-2.3.6 MPI library and existing support for online compression.

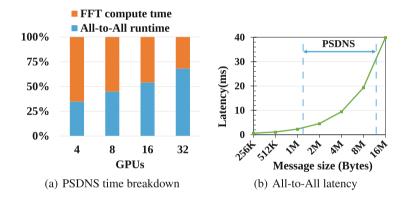

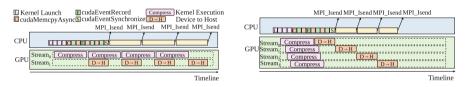

Both the Scatter Destination (SD) and Pairwise Exchange (PE) algorithms rely on the GPU-based point-to-point communication to transfer data between GPUs. With the current point-to-point based online compression, these algorithms can leverage compression for both inter-node and intra-node communication. However, there are limitations in the existing point-to-point based online compression design. For the PSDNS application, we use the NVIDIA profiler Nsight to monitor the compression behavior of the existing GPU-based Scatter Destination and Pairwise Exchange All-to-All algorithms in the state-of-theart MVAPICH2-GDR-2.3.6 library. Figure 2 shows the existing design that utilizes point-to-point operations in the MVAPICH2-GDR-2.3.6 library. The figure also proposes a design to overcome this limitation. As shown in the existing design section of Fig. 2, when a process sends data to other processes, the compression kernel in a single send operation does not overlap with kernels in other send operations even though they run on different CUDA streams.

| Algorithms                                   | Compression<br>support | Compression<br>level | Inter-node<br>data<br>transfer | Intra-node<br>data<br>transfer | Multiple<br>streams<br>compression | Hide<br>compression<br>overhead | Overlap<br>opportunity |

|----------------------------------------------|------------------------|----------------------|--------------------------------|--------------------------------|------------------------------------|---------------------------------|------------------------|

| GPU-aware<br>Scatter<br>Destination<br>[28]  | Y                      | Point-to-<br>Point   | GPUDirect                      | IPC                            | Within single<br>Send/Recv         | N                               | N                      |

| GPU-aware<br>Pairwise<br>Exchange<br>[29]    | Y                      | Point-to-<br>Point   | GPUDirect                      | IPC                            | Within single<br>Send/Recv         | N                               | N                      |

| CPU Staged<br>Scatter<br>Destination<br>[28] | N                      | N                    | RDMA                           | Shared<br>Memory               | N                                  | N                               | N                      |

| CPU Staged<br>Pairwise<br>Exchange<br>[29]   | N                      | N                    | RDMA                           | Shared<br>Memory               | N                                  | N                               | N                      |

| Proposed<br>Design                           | Y                      | Collective<br>level  | Staging + I                    | RDMA                           | Across<br>multiple<br>Send/Recv    | Y                               | Y                      |

**Table 1.** Comparison of existing online compression support in MVAPICH2-GDR-2.3.6 with proposed design

This limitation is similar for the decompression kernels in receive operations. This essentially becomes a bottleneck for implementing dense collective operations like MPI\_Alltoall efficiently.

Fig. 2. Comparison between using existing compression method for point-to-point operations versus proposed design. The proposed design increases the overlap of kernel initialization and wait time by enabling compression at the collective level instead of the point-to-point level.

Challenge-2: Move the Point-to-Point Compression to the Collective-*Level:* The above limitation can be handled by utilizing compression at the collective level. In MPI libraries, collectives operations are typically built using point-to-point operations. In collective-level compression, the compression/decompression is done at the collective algorithm level before calling the underlying point to point send/receive operation to transfer data. This provides us the opportunity that CUDA kernels across multiple send/receive operations can be overlapped to reduce the compression overheads—this is depicted in Fig. 2 and forms the primary motivation of our proposed design in this paper. However, the underlying mechanism of Scatter Destination and Pairwise Exchange algorithms prevents us from moving the compression to the collective level efficiently. This pushes us to explore other MPI\_Alltoall algorithms. The CPU Staging algorithm [28] moves the data from GPU to host and leverages the host-based Scatter Destination, Pairwise Exchange, or other MPI\_Alltoall algorithms to transfer the data. Since the send and receive operations are host-based, we cannot merely use the existing GPU-based point-to-point compression. We need to co-design the GPU-based compression at the collective level (Sect. 3).

Challenge-3: Revamp and Optimize GPU-Based Compression for the Collective-Level Online Compression: While point-to-point compression focuses on reducing the inherent compression-related overheads, collective-level compression aims to further reduce the effective kernel computing time by co-designing the compression with the collective operations. This needs the enhancement of designing interfaces for the existing collective operations to support GPU-based compression. Furthermore, naive integration of the compression algorithms at the collective level may not achieve optimal performance (Sect. 3.1). We have to analyze the bottlenecks of such naive compression designs, revamp the existing GPU-based algorithm, upgrade the naive design to support the new interface, and optimize the collective operations. The implementations of each optimization will be proposed (Sect. 4).

## 1.3 Contributions

In this paper, we design and implement high-performance online message compression for the MPLAlltoall communication operation on modern GPU clusters. To the best of our knowledge, this is the first work that leverages GPU-based compression techniques to significantly improve MPLAlltoall communication performance while maintaining data validation and not affecting the convergence time. To summarize, this paper makes the following main contributions:

- We conduct a thorough analysis of the limitations and possible optimization opportunities for existing MPI\_Alltoall algorithms with online compression support on modern GPU systems.

- We propose an online compression design that is integrated into the underlying communication libraries (e.g., MPI) for host-staging based MPI\_Alltoall communication. Later, we analyze the limitations of naively integrating the existing ZFP compression library.

- We optimize the ZFP compression library to enable execution of compression/ decompression kernels on multiple CUDA streams. These strategies reduce the overhead of compression/decompression kernels and improve overall performance.

- We use the OSU Micro Benchmark (OMB) suite to evaluate MPI\_Alltoall communication and show that the proposed design can achieve up to 87% improvement in performance. We also enhance OMB to use real data sets and get up to 75% improvement in the MPI\_Alltoall operation.

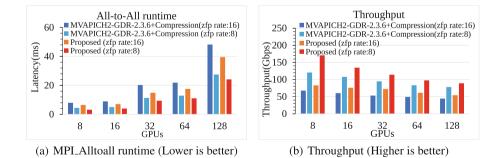

- We evaluate the effectiveness of the proposed design through application studies. In the PSDNS application, we can gain up to 29.2% and 21.8% reduced MPI\_Alltoall runtime and total execution time, respectively, compared to the existing MVAPICH2-GDR-2.3.6 with point-to-point compression. In the Deep Learning framework DeepSpeed, the proposed design reduces the MPI\_Alltoall runtime by up to 26.4% and improves throughput by up to 35.8%.

## 2 Background

In this section, we provide the necessary background knowledge including the recent development of GPU based compression algorithms, MPI\_Alltoall algorithms in MPI libraries, GPUDirect technology, and GPU-aware communication middlewares.

#### 2.1 Compression Algorithms for HPC Applications

In recent years, lossy compression libraries have shown acceptable errorbounds [6] for HPC applications. Among them, ZFP [14] is a well-known public compression library with user-friendly interfaces and supports CUDA-enabled fixed-rate compression. ZFP deconstructs a d-dimensional array into  $4^d$  blocks. The resulting compression rate is the number of amortized compressed bits among these blocks. For example, for single-precision (32-bit) floating-point data, a compression rate of 8 bits/value can get a compression ratio of 4. In this work, we use the ZFP compression library.

NVIDIA recently proposed nvCOMP [19], a CUDA-based lossless compression interface to achieve high-performance compression kernels. nvCOMP supports Cascaded, LZ4, and Snappy compression methods. However, the burden of integrating nvCOMP APIs and using them for HPC applications requires changing application code. Since nvCOMP is a user-level library, we don't consider it for online compression.

#### 2.2 Algorithms for MPI\_Alltoall Communication

Different MPI libraries have their own implementations of MPI\_Alltoall algorithms and often tune their library to pick up the most efficient MPI\_Alltoall algorithm for a given system and message size at runtime. In existing MPI libraries, there are three representative MPI\_Alltoall algorithms for large-message data transfers. (a) In the Scatter Destination algorithm [28], each process posts a series of MPI\_Isend and MPI\_Irecv operations and waits for these operations to complete. (b) In the Pairwise Exchange algorithm [29], each process runs MPI\_Sendrecv to communicate with only one source and one destination. These send and receive operations will reply with GPU-based point-to-point communication schemes to transfer data between GPUs. (c) The CPU staging algorithm [28] leverages the host-based send and receive operations to transfer the data. The GPU data will be moved from GPU to host before the MPI\_Isend operation, and will be copied back from host to GPU after MPI\_Irecv.

#### 2.3 GPU-Aware Communication Middleware

*GPU-aware* MPI libraries like SpectrumMPI [5], OpenMPI [20], and MVAPICH2 [17] can distinguish between host buffers and GPU buffers. These libraries have been optimized with GPU-based point-to-point communication schemes like CUDA Inter-Process Communication (IPC) [25] and NVIDIA GPUDirect technology [18] which supports direct reading and writing to host and device memory by the CPU and GPU. Such technologies provide optimal performance across varied communication paths.

## 3 Proposed Online Compression Design for MPI\_Alltoall Communication

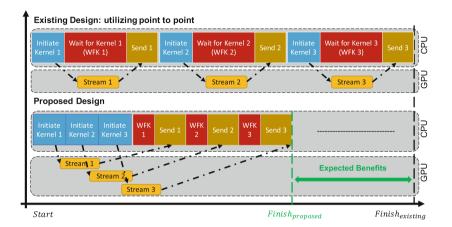

To tackle the limitation of using point-to-point based compression (Challenge-1) for MPLAlltoall communication and move the point-to-point compression to collective level (Challenge-2), we redesign the host-staging based MPLAlltoall algorithm in the MPI library to implement efficient MPLAlltoall communication of GPU data with online compression. Figure 3 depicts the data flow of host-staging based MPLAlltoall operations with compression. GPU data are exchanged among four GPUs. In GPU0, the device buffer sendbuf contains data A0, A1, A2, A3 which will be sent to the recvbuf in GPU0, GPU1, GPU2 and GPU3 respectively.

**Fig. 3.** Host-Staging based MPI\_Alltoall with compression. GPU data will be compressed to the temporary device buffer sendbuf\_tmp and copied by cudaMemcpyAsync to the host buffer sendbuf\_host. MPI\_Isend sends out the data in the host buffer to other CPUs. MPI\_Irecv collects the data to the host buffer recvbuf\_host from other CPUs. The received data will be copied by cudaMemcpyAsync to the temporary device buffer recvbuf\_tmp and decompressed to the recvbuf.

Algorithm 1 provides a high-level overview of the compression design for host-staging based MPI\_Alltoall. Before staging the GPU data to the CPU, a compression kernel will be launched on the send buffer for each process (Line 4). The compressed data will be stored into the corresponding part of a temporary device buffer sendbuf\_tmp. Once the compression kernel finishes, the compressed data will be copied to the host buffer sendbuf\_host using cudaMemcpyAsync on a specific CUDA stream *Stream1* (Line 5). After each cudaMemcpyAsync, a CUDA event will be recorded on the same CUDA stream (Line 6).

With compression, the data size of the transferred data is changed. The MPI\_Isend operation needs to specify the compressed data size instead of the original data size. We use a data size array B to record the data size of each compressed data after compression. For the peer processes on other GPUs, they

also should specify the correct data size for the upcoming data in MPI\_Irecv. To transfer such data size information before transferring the compressed data, we run an MPI\_Alltoall to exchange the elements in the data size array between all the CPUs (Line 7). Since each element is only a 4 bytes integer, the overhead of such operation is negligible compared to the large data transfer.

The multiple MPI\_Irecv operations for all the peer processes will be issued ahead of MPI\_Isend (Line 9). Each MPI\_Irecv is associated with a receive request. Before MPI\_Isend, we use cudaEventSynchronize to indicate the completion of related cudaMemcpyAsync from device to host (Line 11). The MPI\_Isend will be issued to send out data in the host buffer  $S_H$  to the buffer address in another CPU (Line 12).

Once a receive request is completed, the related compressed data is stored in the host buffer  $R_{-H}$ . Similar to the send operation, the data will be copied to a temporary device buffer  $R_{-t}mp$  using cudaMemcpyAsync on a specific CUDA stream (Line 14). The decompression kernel will be launched on the data of each process in  $R_{-t}mp$  after the corresponding cudaMemcpyAsync is finished (Line 19). The compressed data will be restored to the receive buffer R.

**Algorithm 1:** Online Compression/Decompression Design for Host-Staging based MPI\_Alltoall Communication

: Send buffer S, Control parameters A, Number of MPI processes N, Input Preallocated GPU buffer S\_tmp, R\_tmp, Preallocated Host buffer S\_H, R\_H, CUDA events for send  $E_{-S}$ , CUDA events for receive  $E_{-R}$ Output: Receive buffer R, Compressed data size B for send buffer, Compressed data size C for receive buffer 1 for i = 1 to N do Construct  $zfp\_stream$  and  $zfp\_field$ ; 2 Attach A to *zfp\_stream* and *zfp\_field*; з  $(B_i, S_tmp_i) = zfp_compress(S_i, A_i); //Runs on default CUDA Stream0$ 4  $cudaMemcpyAsync(S_tmp_i, S_H_i, B_i, cudaMemcpyDeviceToHost, Stream1);$ 5  $cudaEventRecord(E_S_i, Stream1);$ 6 MPI\_Alltoall(B, 1, MPI\_INT, C, 1, MPI\_INT, MPI\_COMM\_WORLD); // Exchange 7 the compressed data size for i = 1 to N do 8 MPI\_Irecv( $R_H_i, C_i, ...$ ) //Receive compressed data; 9 10 for i = 1 to N do  $cudaEventSynchronize(E_S_i);$ 11 MPI\_Isend( $S_H_i, B_i, ...$ ); // Send compressed data; 12 if MPI\_Irecv finishes for  $R_H_i$  then 13  $cudaMemcpyAsync(R_tmp_i, R_H_i, C_i, cudaMemcpyHostToDevice, Stream2);$ 14 cudaEventRecord( $E_R_i$ , Stream2); 15 for i = 1 to N do 16 cudaEventSynchronize $(E_R_i)$ ; 17 Construct zfp-stream and zfp-field based on control parameter A; 18  $R_i = \text{zfp\_decompress}(R\_tmp_i, C_i, A_i); //\text{Runs on default CUDA Stream0}$ 19

We define runtime parameters to enable/disable compression in the hoststaging based MPI\_Alltoall design. We also define several control parameters such as compression rate, dimensionality, and data type to run the ZFP compression library,

#### 3.1 Analysis of the Benefits and Limitation for the Naive Compression Design

In this section, we analyze the compression-related benefits and costs to find out the bottleneck (Challenge-3) in the naive compression design. With compression, there will be less data movement by cudaMemcpyAsync between CPU and GPU in the staging operations. The run time of the staging operation will be reduced. MPLIsend can send out the data in the host buffer much earlier. Similarly, the run time of transferring data between the CPUs will be reduced. On the receiver side, it will take less time to copy data from the host buffer to the device buffer. However, similar to the point-to-point based compression [32], there is also extra compression/decompression kernel execution time and related kernel launching overheads in the naive host-staging based compression. When the compression ratio is not high enough, the benefits brought by the reduced data size may not compensate for these extra running time costs. We need to optimize the compression design to reduce such costs.

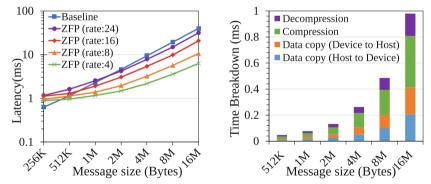

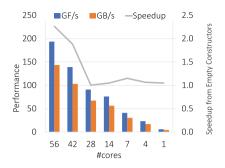

(a) Performance of MPI\_Alltoall with naive (b) Time breakdown of key operations with compression design ZFP (rate:24)

Fig. 4. Performance of host-staging based MPI\_Alltoall with naive compression design on 2 nodes (4 ppn) of the Longhorn cluster. Higher compression rate (16, 24) indicates a lower compression ratio. The design only starts to outperform the baseline from larger message size 1 MB for rate = 16 and 2 MB for rate = 24. The time breakdown shows the latency of single compression/decompression kernel, and data copy from host to device and device to host.

We evaluate the proposed compression design using the OSU Micro-Benchmark suite (OMB) on 2 nodes with 4ppn (4GPUs/node) of the TACC Longhorn cluster. As shown in Fig. 4(a), the proposed host-staging based naive ZFP compression design can achieve benefits from 512 KB with low compression rates 8 and 4. However, with a higher compression rate (and consequently a lower compression ratio), it only starts to outperform the baseline for larger message size. Since ZFP is a lossy compression algorithm, this shortage will prevent the design from applying to those applications which need higher accuracy. Figure 4(b) depicts the time breakdown of some key operations in the naive compression design with ZFP (rate:24). The results show the latency of every single operation.

In the existing ZFP library, compression kernel cuZFP::encode runs on the default CUDA stream. In the naive compression design, although the cudaMemcpyAsync executing on a non-default stream with a non-blocking flag cudaStreamNonBlocking can achieve overlap with the compression kernels for other ranks, each cudaMemcpyAsync still needs to wait for the completion of compression kernel for its rank. As we can see in Fig. 5(a), since the compression kernels run serially in the default stream, there is a long waiting time for the MPI\_Isend operation to send out the data since MPI\_Isend must wait for the finish of compression kernel and memory copy from device to host.

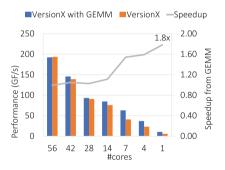

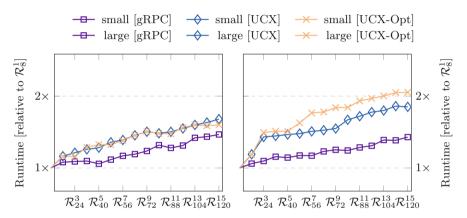

(a) Send operations with naive compression on (b) Send operations with optimized compresdefault stream sion on multiple streams

Fig. 5. Comparison between compression on the default CUDA stream and multiple CUDA streams for send operations in the host-staging based All-to-All. Overall compression time is reduced due to the overlap between the compression kernels. The data will be sent out faster since the cudaMemcpyAsync and MPI\_Isend can be executed much earlier.

There is also a similar limitation for the decompression phase. As shown in Fig. 6(a), the decompression kernel cuZFP::decode also runs on default CUDA stream. Although the cudaMemcpyAsync can be overlapped with the decompression kernel, it will cost a long operation time to restore data in the GPU due to the serial operations among the decompression kernels.

sion on default stream

(a) Receive operations with naive decompres- (b) Receive operations with optimized decompression on multiple streams

Fig. 6. Comparison between ZFP decompression on the default CUDA stream and multiple CUDA streams. Explicit calling of cudaEventSynchronize is not needed. Overall decompression time is reduced due to the overlap between the decompression kernels.

#### 4 **Optimization Strategies in the Host-Staging Based** MPI\_Alltoall

Based on the previous analysis of the limitation of the naive compression design, we propose the following optimizations to address the Challenge-3.

#### 4.1 Enabling Multiple CUDA Streams in ZFP Library

To reduce the overall compression and decompression time, we aim to achieve overlap between the kernels. However, the current ZFP library does not provide such an interface to run the kernels concurrently on non-default CUDA streams. Therefore, we enhance the existing ZFP library to allow compression and decompression kernels to run on multiple streams. We define two new functions, zfp\_compress\_multi\_stream and zfp\_decompress\_multi\_stream. A new parameter of CUDA stream object cudaStream\_t is added to these functions. At the user level, we can assign a specific stream to the compression and decompression. ZFP uses a function table to select the correct low-level compression and decompression functions according to the execution policy (Serial, OpenMP, CUDA), stride, dimensionality, and scalar type. We extend the function table and introduce a new execution policy named zfp\_exec\_cuda\_multi\_stream to allow the selection of new lower-level APIs with a stream parameter. We add a new cudaStream\_t parameter to all the related lower-level APIs.

In the proposed compression design, we use the 1D array type for ZFP compression with the number of floating-point values as the dimensionality. The compression kernel cudaEncode1 and decompression kernel cudaDecode1 will be launched to the CUDA stream specified by the new High-level APIs. In the existing compression kernel, launch function, and constant setup function, two synchronous CUDA memory copy functions (cudaMemset and cudaMemcpy-ToSymbol) are used to prepare for the compression and decompression on the default stream. We change them to cudaMemsetAsync and cudaMemcpyToSymbolAsync, respectively, with the same CUDA stream used for compression or decompression.

#### 4.2**Proposed Optimization Metrics**

With the enhanced ZFP library (ZFP-OPT), we use two new API calls in the compression design: zfp\_compress\_multi\_stream and zfp\_decompress\_multi\_stream.

| Algorithm 2: Proposed optimized multi-stream compression/decompression                                                                                       |   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| for MPI_Alltoall Communication                                                                                                                               |   |  |  |  |  |

| <b>Input</b> : Send buffer $S$ , Control parameters $A$ , Number of MPI processes $N$ ,                                                                      |   |  |  |  |  |

| Preallocated GPU buffer $S\_tmp$ , $R\_tmp$ , Preallocated Host buffer                                                                                       |   |  |  |  |  |

| $S_H$ , $R_H$ , CUDA events for send $E_S$ , CUDA events for receive $E_H$                                                                                   | , |  |  |  |  |

| $[S_1,, S_N]$ = Send buffers for peer processes in Send buffer S;                                                                                            |   |  |  |  |  |

| $[S\_tmp_1,, S\_tmp_N]$ = Divided N partitions of $S\_tmp;$                                                                                                  |   |  |  |  |  |

| $[R_{-}H_1,, R_{-}H_N]$ = Receive buffers for peer processes in $R_{-}H$ ;                                                                                   |   |  |  |  |  |

| $[R\_tmp_1,, R\_tmp_N]$ = Divided N partitions of $R\_tmp$                                                                                                   |   |  |  |  |  |

| <b>Output:</b> Receive buffer $R$ , Compressed data size $B$ for send buffer, Compressed                                                                     |   |  |  |  |  |

| data size $C$ for receive buffer                                                                                                                             |   |  |  |  |  |

| 1 Multi-stream compression for send operation:                                                                                                               |   |  |  |  |  |

| 2 for $i = 1$ to N do                                                                                                                                        |   |  |  |  |  |

| 3 Construct $zfp\_stream$ and $zfp\_field$ based on control parameter $A$ ;                                                                                  |   |  |  |  |  |

| 4 $zfp\_stream\_set\_execution(zfp\_stream, zfp\_exec\_cuda\_multi\_stream);$<br>5 $(P_{a}, C_{a}, t_{a}, \dots, t_{a}) = f_{a}$                             |   |  |  |  |  |

| 5 $(B_i, S\_tmp_i) = zfp\_compress\_multi\_stream(S_i, A_i, Stream_i); //Runs on non-default CUDA Stream$                                                    |   |  |  |  |  |

|                                                                                                                                                              |   |  |  |  |  |

| 6 cudaMemcpyAsync $(S_H_i, M_i, B_i, $ cudaMemcpyDeviceToHost, $Stream_i)$ ;<br>//Run on the same CUDA stream                                                |   |  |  |  |  |

| 7 cudaEventRecord( $E_i$ , $Stream_i$ );                                                                                                                     |   |  |  |  |  |

|                                                                                                                                                              |   |  |  |  |  |

| 8 MPLIsend, MPLIrecv operations;                                                                                                                             |   |  |  |  |  |

| 9 Multi-stream decompression for receive operation:                                                                                                          |   |  |  |  |  |

| 10 for $i = 1$ to N do                                                                                                                                       |   |  |  |  |  |

| 11 cudaMemcpyAsync( $R_{-}H_i$ , $R_{-}tmp_i$ , $C_i$ , cudaMemcpyHostToDevice,                                                                              |   |  |  |  |  |

| $Stream_i$ ; // Runs on non-default CUDA stream                                                                                                              |   |  |  |  |  |

| 12 Construct $zfp\_stream$ and $zfp\_field$ based on control parameter $A$ ;<br>26 $zfp\_stream$ act evention ( $zfp\_stream$ $zfp\_stream$ $zfp\_stream$ ); |   |  |  |  |  |

| 13 $zfp\_stream\_set\_execution(zfp\_stream, zfp\_exec\_cuda\_multi\_stream);$                                                                               |   |  |  |  |  |

| 14 $R_i = \text{zfp\_decompress\_multi\_stream}(R\_tmp_i, A_i, Stream_i); //Runs on the same CUDA Stream$                                                    |   |  |  |  |  |

|                                                                                                                                                              |   |  |  |  |  |

Algorithm 2 provides a high-level overview of the multi-stream compression and decompression for the for MPI\_Alltoall operation. For the compression on send operation side, we set a new execution policy zfp\_exec\_cuda\_multi\_stream (Line 4). Then we launch the compression kernels to different CUDA streams (Line 5). Each corresponding cudaMemcpyAsync also runs on the same stream as the kernel (Line 6). The benefits of concurrent kernel execution are two-fold. Due to the overlap between the compression kernels, the overall compression time is reduced. Furthermore, since cudaMemcpyAsync can copy the compressed data to CPU earlier, MPLIsend can send out the data from CPU in advance. Figure 5(b) depicts the optimized send operations with this mechanism. Note that, the

overlapping situation among the kernels and data copy operations depends on the number of processes in the MPI\_Alltoall operation and the compression rate.

Similarly, on the receive operation side, we optimize decompression using multiple CUDA streams. Once a receive request is finished, we run the cudaMemcpyAsync on a non-default stream to copy the compressed data from host to device (Line 11). To enable the multi-stream decompression, we also need to use the execution policy of zfp\_exec\_cuda\_multi\_stream (Line 13). The related decompression kernel will also run on the same stream (Line 14). In this way, we do not need to explicitly launch cudaEventSynchronize to wait for the completion of cudaMemcpyAsync. As shown in Fig. 6(b), the overlap between the decompression kernels will reduce the overall decompression time and thus, accelerate the data restoration phase in the GPU. In the proposed design, we define wrapper functions to execute the compression/decompression kernels. Such optimization metrics can be easily applied to compression/decompression kernels of other compression algorithms.

#### 5 Microbenchmark Results and Analysis

We run the experiments on three GPU-enabled clusters: Longhorn [16] and the Liquid [15] subsystem at the Texas Advanced Computing Center, and the Lassen [13] system at Lawrence Livermore National Laboratory. Each computing node on the Longhorn and Lassen systems is equipped with IBM POWER9 CPUs and 4 NVIDIA V100 GPUs. They use RHEL operating system. Both systems enable NVLink2 interconnection between CPU and GPU, and Infiniband EDR between nodes. Each node on Frontera Liquid is installed with Intel Xeon E5-2620 CPUs and 4 NVIDIA Quadro RTX5000 GPUs. Frontera Liquid uses PCIe Gen3 interconnection between CPU and GPU, and Infiniband FDR between nodes. It installs CentOS operating system. More details about the system configurations can be found in their respective specification documents.

We used osu\_alltoall in the OSU Micro-Benchmark suite (OMB) to evaluate the MPI\_Alltoall communications of GPU data on multiple nodes. We also enhanced OMB to use real data sets for the MPI\_Alltoall communication tests.

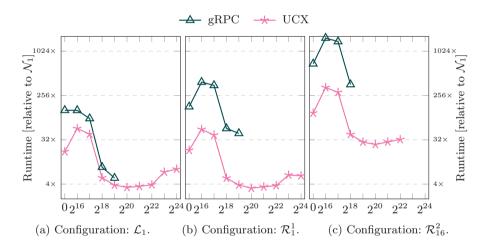

#### 5.1 MPI\_Alltoall Communication Latency on Micro-Benchmark

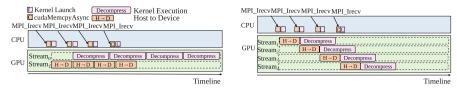

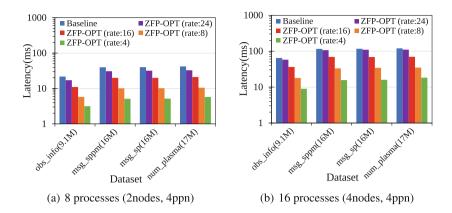

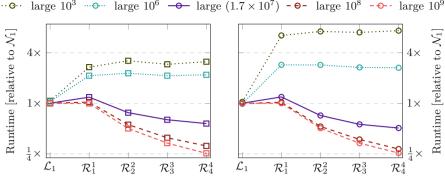

We run the OSU Micro-Benchmark suite (OMB) to evaluate the MPI\_Alltoall communication latency. Figures 7(a) and 7(b) show the MPI\_Alltoall communication latency of message size from 256 KB to 16 MB on the Frontera Liquid system. Since the proposed design is aimed at the transfer of large GPU messages, the performance results of smaller message sizes are not shown in the figures. We observe performance improvement with the optimized compression design in the 256 KB to 16 MB message range. With a lower compression rate, ZFP-OPT achieves a higher compression ratio and a further reduced communication latency. Compared to the baseline, ZFP-OPT (rate:4) can achieve up to 87.1% reduced latency at 16 MB on both 2nodes and 4nodes with 4ppn

(4 GPUs/node). Figures 7(c) and 7(d) show the MPI\_Alltoall communication latency on the Longhorn system. On 2 nodes with 4ppn, ZFP-OPT starts to outperform the baseline from around 512 KB. Compared to Fig. 4(a), Fig. 7(c) demonstrates the performance improvement with the optimization strategies discussed in Sect. 4. On 4 nodes, except for rate = 24, ZFP-OPT has performance benefits starting from 256 KB. Similar to the Frontera liquid system, ZFP-OPT (rate:4) can achieve up to 87.1% reduced latency at 16 MB on 2 nodes and 4 nodes.

(a) Frontera: 8GPUs (b) Frontera: 16GPUs (c) Longhorn: 8GPUs (d) Longhorn: 16GPUs (2nodes, 4ppn) (4nodes, 4ppn) (2nodes, 4ppn) (4nodes, 4ppn)

Fig. 7. Latency of MPI\_Alltoall on Frontera Liquid and Longhorn. On Frontera Liquid, ZFP-OPT starts to show benefits from 256 KB on both 2 nodes and 4 nodes. With a lower compression rate, ZFP-OPT achieves a higher compression ratio and reduces communication latency. On Longhorn, ZFP-OPT shows performance improvement from about 512 KB on 2 nodes. On 4 nodes, except for rate = 24, ZFP-OPT achieves benefits from 256 KB. On both systems, ZFP-OPT (rate:4) can achieve up to 87.1% reduced latency at 16 MB on 2 nodes and 4 nodes.

#### 5.2 MPI\_Alltoall Communication Latency with Real Data Sets

This section evaluates the impact of the proposed design on the MPI\_Alltoall communication performance on the Longhorn system with real data sets from [31]. Figures 8(a) and 8(b) show the results of MPI\_Alltoall communication latency on 2 nodes and 4 nodes respectively. In the fixed-rate compression mode, with the same compression rate, ZFP will have the same compression ratio it has in the micro-benchmark test. The proposed design achieves similar benefits as the Micro-benchmark test. With lower compression rate, it reduces communication latency further. ZFP-OPT (rate:4) reduces the MPI\_Alltoall communication latency by up to 75% (num\_plasma) on 2 nodes, 72% (obs\_info) on 4 nodes respectively.

Fig. 8. Latency of MPI\_Alltoall with real datasets on Longhorn. With a lower compression rate, ZFP-OPT achieves greater performance benefit. ZFP-OPT (rate:4) reduces the MPI\_Alltoall communication latency by up to 75% (data set num\_plasma) on 2 nodes and 72% (data set obs\_info) on 4 nodes, respectively.

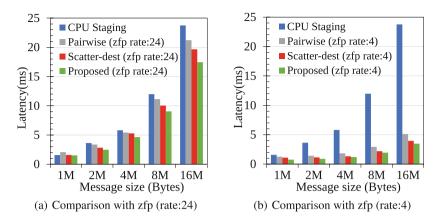

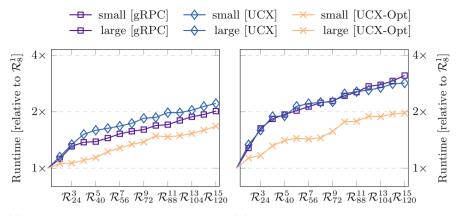

#### 5.3 Comparison of the Proposed Design and Existing MPI\_Alltoall Algorithms with Point-to-Point Compression

In this section, we compare our proposed design with different algorithms: CPU Staging (No compression), Scatter Destination, and Pairwise Exchange in MVAPICH2-GDR-2.3.6. We use the runtime parameters provided by the MVAPICH2-GDR-2.3.6 to trigger the point-to-point compression for Scatter Destination and Pairwise Exchange.

On the Lassen system, for 8 GPUs on 2 nodes, our proposed design performs better than these algorithms starting from 1 MB as shown in Fig. 9(a) and 9(b). Figure 9(a) shows, for 16 MB data, the proposed design reduces the MPLAlltoall latency by up to 11.2%, 17.8% and 26.6% compared to the Scatter Destination(zfp rate:24), Pairwise Exchange(zfp rate:24), and CPU Staging (No compression), respectively. In Fig. 9(b), with zfp compression (rate:4), the latency is reduced by up to 12.4%, 32.3%, and 85.4% compared to the Scatter Destination, Pairwise Exchange, and CPU Staging (No compression), respectively.

In application tests, we observe greater benefit compared to the Scatter Destination and Pairwise Exchange on larger scales.

19

Fig. 9. MPI\_Alltoall latency with different algorithms for 8 GPUs on 2 Lassen nodes. With zfp compression (rate:24), the proposed design reduces the MPI\_Alltoall latency by up to 11.2%, 17.8%, and 26.6% compared to the Scatter Destination, Pairwise Exchange, and CPU Staging (No compression), respectively. With zfp compression (rate:4), the latency is reduced by up to 12.4%, 32.3%, and 85.4% compared to the Scatter Destination, Pairwise Exchange, and CPU Staging (No compression), respectively

#### 6 Application Results and Analysis

#### 6.1 PSDNS

We evaluate the proposed design with a modified 3D-FFT kernel of the Fourier pseudo spectral simulation of turbulence (PSDNS) application [23]. The code was written in Fortran with a hybrid MPI+OpenMP approach and compiled with the IBM XL compiler. We run PSDNS on the Lassen system which uses the IBM Power9 CPU architecture. In the 3D-FFT kernel, MPI\_Alltoall is used to transfer the transposed data among the multiple GPUs. The kernel will also generate a timing report about the runtime per timestep of MPI\_Alltoall operations, FFT computing, and other operations. It also checks the max global difference of the sinusoidal velocity field as an accuracy criteria. The underlying different algorithms of MPI\_Alltoall can be triggered by runtime parameters. Note that the Scatter Destination and Pairwise Exchange algorithms are built on top of point-to-point operations. We compare our proposed design with the state-ofthe-art MVAPICH2-2-GDR-2.3.6 with point-to-point compression.

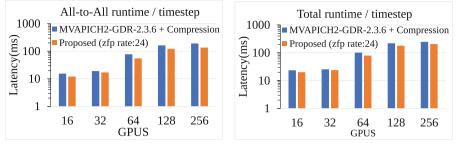

(a) MPI\_Alltoall runtime per timestep, 4 (b) Total runtime per timestep, 4 GPUs/node GPUs/node (Lower is better) (Lower is better)

Fig. 10. MPI\_Alltoall runtime in the 3D-FFT kernel of the PSDNS application on the Lassen system. The proposed design with optimized ZFP(rate:24) can reduce the MPI\_Alltoall runtime and total runtime by up to 29.2% and 21.8%, respectively, on 64 GPUs compared to the state-of-the-art MVAPICH2-GDR-2.3.6 with point-to-point compression.

As shown in Fig. 1(a), the MPLAlltoall communication is dominant when the application runs on large scale. In this section, by increasing the grid size of nx, ny, nz along with the number of GPUs, we can evaluate our compression design on different problem scales. For 128 GPUs, the grid size (nx, ny, nz) is (1536, 1536, 1536).