# Shahzad Muzaffar Ibrahim (Abe) M. Elfadel

# Secure, Low-Power IoT Communication Using Edge-Coded Signaling

# Secure, Low-Power IoT Communication Using Edge-Coded Signaling

# Secure, Low-Power IoT Communication Using Edge-Coded Signaling

Shahzad Muzaffar Khalifa University Abu Dhabi, United Arab Emirates Ibrahim (Abe) M. Elfadel Khalifa University Abu Dhabi, United Arab Emirates

#### ISBN 978-3-030-95913-5 ISBN 978-3-030-95914-2 (eBook) https://doi.org/10.1007/978-3-030-95914-2

#### © Springer Nature Switzerland AG 2022

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

To my parents (Shamshad and Muzaffar), beloved wife (Umber), son (Anzar) and sisters (Shumaila, Shaista, and Sumaira) Shahzad

To the blessed memory of my brother Zaher Elfadel 1965–2010 Abe

### Prologue

Your assumptions are your windows on the world. Scrub them off every once in a while, or the light won't come in.

Isaac Asimov

The accepted IoT wisdom is that it is much more energy-efficient to compute on the edge than to communicate with the hub. Yet, this accepted wisdom is based on the premise that the power hog that lives in the communication subsystem of the IoT node must be avoided at all costs and that whatever power that is still available should be used to make the IoT node *smart*. The TinyML framework for machine learning on tiny micro-controllers is based on such premise and epitomizes the current wisdom under the edge-computing paradigm.

The ultimate aim of this research monograph is to revisit this premise by giving a concrete example of a novel, ultra-low-power, robust, and secure, IoT communication protocol that is meant to enable innovative IoT architectures that can bridge the chasm between edge and cloud computing.

The research described herein is a summary of several years of investigation into a single *what-if* question with regards to the design of signaling protocols, namely, *what if* the IoT communication subsystem can operate reliably and securely *without* the circuitry dedicated to clock and data recovery (CDR).

The main motivation of asking this *what-if* question is the basic observation that a CDR circuit is a significant contributor to power consumption in the communication transceiver. Being able to save as much of its power as possible in an IoT node is bound to impact the debate on computation vs. communication and on edge vs. cloud intelligence. In terms of real estate, transceivers with CDR circuits have tens of thousands of gates, and therefore a significant saving of silicon area will be achieved in case the CDR circuit is simplified or even possibly eliminated.

Not only do we give an existence proof of such a CDR-less communication link, but also, we provide a complete ecosystem of hardware and firmware built around such a communication link. This ecosystem comprises an application-specific processor, automatic protocol configuration, power and data rate management, cryptographic primitives, and automatic failure recovery modes. The resulting link and its associated ecosystem are fully compatible with IoT requirements on power, footprint, security, robustness, and reliability.

The fundamental idea of the proposed IoT communication protocol is to encode the ON bit in the data word as a sequence of pulses whose count is based on the ON-bit index. At the receiver, this index is decoded by simply counting the number of rising edges in the pulse sequence. This is the main reason we have called this protocol *Edge-Coded Signaling* or ECS.

From this basic idea, ECS has evolved through three different generations, ECS1, ECS2, and ECS3, into a full family of protocols. They are all variations on the fundamental theme of pulse generation for the ON bits at the transmitter end of the link and edge counting at the receiver end. They are all described in this monograph along with hardware prototypes that allow us to thoroughly benchmark and precisely quantify the IoT advantages of this novel family of signaling protocols. These advantages can be summarized as follows:

- 1. ECS results in a major simplification of the IoT device transceiver. This simplification in turn contributes to major gains in footprint, power savings, and cost.

- 2. ECS supports dynamic data rates, and the ECS parameters can be readily optimized to achieve the maximum average data rate for a given application.

- 3. ECS is robust in that it tolerates significant device-to-device variations in clock frequency as may be expected in a heterogeneous, asynchronous IoT network.

- 4. Along with a low-power design point due to transceiver simplification, ECS provides additional opportunities for power saving, both at the physical layer level and at the pulse design level, that are straightforward to implement.

- 5. ECS supports network protocols for automatic ECS parameter settings across a set of networked IoT devices. These automatic ECS configuration protocols are universal in that they can be applied for any network topology.

- 6. The ECS family of protocols is amenable to compact programming using a domain-specific, RISC-like, ECS processor. Its instruction set architecture achieves more than an order of magnitude of reduction in embedded code size and provides IoT designers with the flexibility to program new ECS protocols that are adapted to specific IoT communication tasks.

- 7. ECS supports low-overhead doubling of data rates using double-edge-coded signaling where both the rising and falling edge of the pulse are used to encode the ON bits in the bit stream.

- 8. ECS enables a close synergy between encoding and encryption, and provides a unique opportunity for significantly strengthening light-weight encryption algorithms in a way that is not possible with traditional signal encoding methods.

- 9. ECS development is supported with various tools for embedded C programming, debugging, and system integration. These tools greatly facilitate the deployment of hardware platforms for IoT sensor networks.

- 10. The robustness and reliability properties of ECS make it the signaling technique of choice in challenging media such as body-coupled communication.

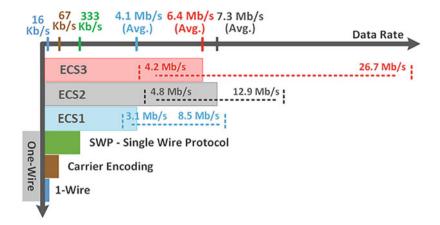

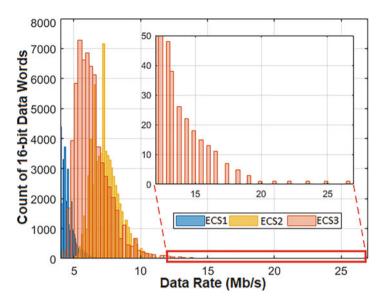

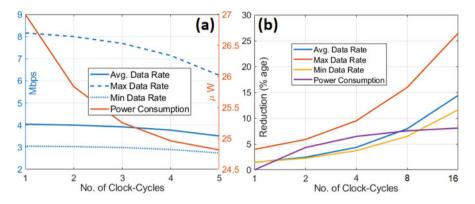

The above 10 advantages are aligned with the 10 chapters of this monograph. By and large, each chapter is organized to lead from the IoT communication design problem to its solution under the ECS paradigm along with supporting hardware validation using either an FPGA or an embedded design platform. ASIC synthesis results using GLOBAFOUNDRIES 65 nm technology node have also been used throughout the chapters to further support the hardware results of the FPGA and embedded design platforms. Our own design of the ECS protocol targeted the sweet spot of a single-channel IoT communication link with a data rate in the range from 4.2 to 26.7 Mbps and with a power consumption cap of 20  $\mu$ W.

Although significant work has already been invested in developing, testing, and validating ECS and its ecosystem, there are still several open research problems that are important to tackle in the next phase of ECS development. We have alluded to many of these problems at appropriate sections within the book chapters. In an epilogue to this book, we have consolidated and summarized all these open research problems with the hope that they will be of interest to colleagues and graduate students from the IoT research community.

Many of the results described in this monograph have already appeared in our prior conference and journal publications between 2015 and 2021. However, we have made a determined effort to synthesize these results and present them in a coherent notational and conceptual framework so that the monograph can serve as an accessible, self-contained reference, not just for IoT professionals but also for graduate students who are entering the field and interested in pursuing research in the area of secure, low-power IoT communication.

Abu Dhabi, United Arab Emirates Abu Dhabi, United Arab Emirates November 2021 Shahzad Muzaffar Ibrahim (Abe) M. Elfadel

### Acknowledgements

This research monograph is based on the PhD thesis of the first author conducted under the supervision of the second author at the Advanced Digital Systems Laboratory of the Masdar Institute, now part of Khalifa University, Abu Dhabi, UAE.

Several colleagues have contributed time, effort, and support to this research over the years. We particularly thank Dr. Jerald Yoo (National University of Singapore) and Dr. Ayman Shabra (MediaTek, USA) for helpful discussions at the early stages of this project. We also thank Dr. Zeyar Aung (Khalifa University, UAE) and Dr. Owais Waheed Talaat (Habib University, Pakistan) for their help with ECS encryption, and Mr. Numan Saeed (Mohamed Bin Zayed University of Artificial Intelligence, UAE) for his help with ECS automatic configuration. Special thanks are due to Prof. Neville Hogan (MIT) and Dr. Mihai Sanduleanu (Khalifa University, UAE) for serving on the PhD Thesis Committee of the first author and providing valuable feedback.

The authors gratefully acknowledge the support provided by the Semiconductor Research Corporation (SRC), USA, under the Abu Dhabi SRC Center of Excellence on Energy-Efficient Electronic Systems (ACE<sup>4</sup>S), Contract 2013 HJ2440, with customized funding from the Mubadala Investment Company, Abu Dhabi, UAE.

They also thank the Office of Technology Management and Innovation at Khalifa University for their help in prosecuting US Patents 10,263,765 and 11,133,891.

# Contents

| 1 | Intro                           | oduction |                                         | 1  |

|---|---------------------------------|----------|-----------------------------------------|----|

| 2 | Edge-Coded Signaling Techniques |          |                                         | 7  |

|   | 2.1                             |          | Coded Signaling (ECS)                   | 8  |

|   |                                 | 2.1.1    | Edge-Coding Scheme                      | 8  |

|   |                                 | 2.1.2    | ECS Segmentation                        | 9  |

|   |                                 | 2.1.3    | ECS Encoding                            | 9  |

|   |                                 | 2.1.4    | ECS Transmitter                         | 11 |

|   |                                 | 2.1.5    | ECS Receiver                            | 13 |

|   |                                 | 2.1.6    | ECS Transmission System                 | 15 |

|   |                                 | 2.1.7    | ECS Data Rate                           | 16 |

|   | 2.2                             | ECS C    | Optimizations                           | 18 |

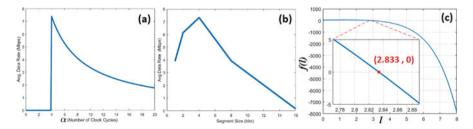

|   |                                 | 2.2.1    | Optimum Inter-symbol Separator <i>α</i> | 18 |

|   |                                 | 2.2.2    | Optimum Segment Length <i>l</i>         | 19 |

|   | 2.3                             | Earlier  | Versions of ECS                         | 20 |

|   |                                 | 2.3.1    | Data Rates                              | 22 |

|   |                                 | 2.3.2    | Optimizations                           | 22 |

|   | 2.4                             | Experi   | mental Setups and Results               | 23 |

|   | 2.5                             | Analys   | sis                                     | 28 |

|   |                                 | 2.5.1    | Data Rate                               | 28 |

|   |                                 | 2.5.2    | Data Word Length and Complexity         | 29 |

|   |                                 | 2.5.3    | Error Detection and Correction          | 31 |

|   |                                 | 2.5.4    | Bit Error Rate                          | 32 |

|   |                                 | 2.5.5    | Pulse Width and Shape                   | 33 |

|   |                                 | 2.5.6    | Reliability                             | 33 |

|   |                                 | 2.5.7    | Robustness                              | 34 |

|   |                                 | 2.5.8    | Overall Latency                         | 35 |

|   |                                 | 2.5.9    | Networking                              | 35 |

|   | 2.6                             | Conclu   | isions                                  | 36 |

| 3   | Timi | ing and Robustness Analysis 3                            |

|-----|------|----------------------------------------------------------|

|     | 3.1  | Timing and Robustness Analysis                           |

|     |      | 3.1.1 Sources of Errors                                  |

|     |      | 3.1.2 Pulse Width Coefficient 4                          |

|     |      | 3.1.3 Inter-symbol Separation Coefficient 4              |

|     |      | 3.1.4 Clock Discrepancy Tolerance                        |

|     |      | 3.1.5 Selection of Inter-symbol Separation Coefficient 4 |

|     |      | 3.1.6 Summary on Inter-symbol Separation 4               |

|     | 3.2  | Protocol Failure Modes and Error Correction 4            |

|     | 3.3  | Experimental Verification 4                              |

|     | 3.4  | Conclusions 4                                            |

| 4   | Doul | bling the ECS Data Rate 4                                |

| ÷., | 4.1  | Single-Edge Scheme: An Example                           |

|     | 4.2  | Double Data Rate Edge-Coded Signaling   5                |

|     | 4.3  | Hardware Implementation                                  |

|     | 1.5  | 4.3.1 Transmitter                                        |

|     |      | 4.3.2 Receiver                                           |

|     | 4.4  | Formulation and Optimizations                            |

|     | 4.5  | Experimental Verification and Results                    |

|     | 4.6  | Conclusions                                              |

| _   |      |                                                          |

| 5   |      | er Management                                            |

|     | 5.1  | ECS1 Power Management                                    |

|     |      | 5.1.1 Sources of Power Consumption                       |

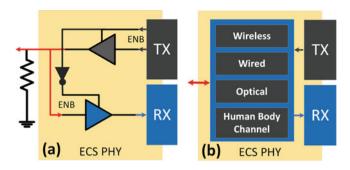

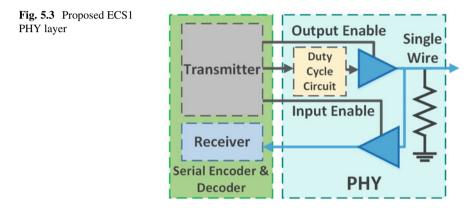

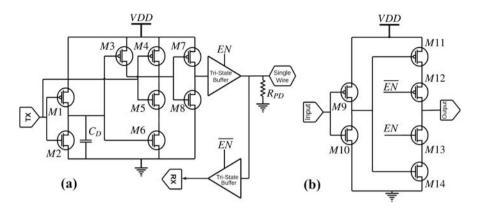

|     |      | 5.1.2 Proposed ECS1 PHY                                  |

|     |      | 5.1.3 Delay Capacitor                                    |

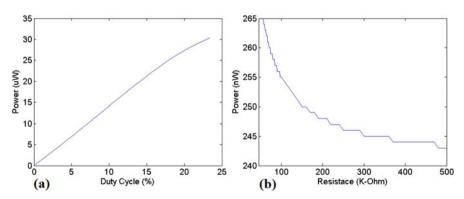

|     |      | 5.1.4 Sizing the Pull-Down Resistor                      |

|     | 5.0  | 5.1.5 Duty Cycle                                         |

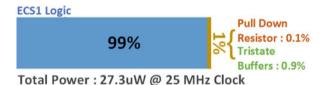

|     | 5.2  | Results                                                  |

|     |      | 5.2.1 Power Analysis                                     |

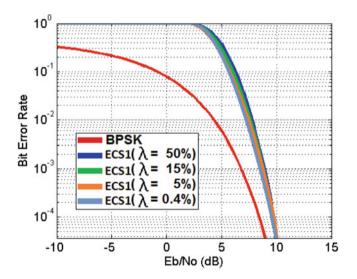

|     | 5.2  | 5.2.2 BER Analysis                                       |

|     | 5.3  | Conclusions 6                                            |

| 6   | Auto | matic Protocol Configuration                             |

|     | 6.1  | Automatic Parameter Detection                            |

|     |      | 6.1.1 Algorithm 6                                        |

|     |      | 6.1.2 Inter-symbol Separator Coefficient Calculation     |

|     |      | 6.1.3 Low-overhead Hardware for $\alpha_F$ Calculation   |

|     | 6.2  | Experimental Verification 7                              |

|     | 6.3  | Conclusions                                              |

| 7   | Secu | re ECS Communication                                     |

| -   | 7.1  | Introduction                                             |

|     | 7.2  | Proposed Multilayer Secure Communication Architecture    |

|     |      | 7.2.1 Re-architecting A5/1 for ECS                       |

|     |      | 7.2.2 Secure ECS Communication                           |

|     |      | 7.2.3 Multiple Layers of Security                        |

|     |      | ······································                   |

|   | 7.3        | Examp    | ele of Secure ECS Communication                 | 90  |

|---|------------|----------|-------------------------------------------------|-----|

|   |            | 7.3.1    | Secure Packetization                            | 90  |

|   |            | 7.3.2    | Secure Reception                                | 92  |

|   | 7.4        | Crypta   | nalysis of the Multilayer Cipher                | 94  |

|   | 7.5        | Implen   | nentation, Cipher Overhead, and Comparison with |     |

|   |            | Prior A  | \rt                                             | 95  |

|   |            | 7.5.1    | Microcontroller Prototype                       | 96  |

|   |            | 7.5.2    | FPGA Prototype                                  | 96  |

|   |            | 7.5.3    | ASIC Synthesis                                  | 97  |

|   |            | 7.5.4    | Secure ECS Design Alternatives                  | 98  |

|   |            | 7.5.5    | Comparison with Lightweight Ciphers             | 99  |

|   | 7.6        | Conclu   | isions                                          | 101 |

| 8 | Dom        | ain-Spec | cific ECS Processor                             | 103 |

|   | 8.1        |          | action                                          | 103 |

|   | 8.2        |          | Coded Signaling Interface Architecture (ECSIA)  | 106 |

|   |            | 8.2.1    | Register Set                                    | 107 |

|   |            | 8.2.2    | Instruction Formats and Types                   | 107 |

|   |            | 8.2.3    | Addressing Modes                                | 111 |

|   |            | 8.2.4    | External I/O and Interrupts                     | 111 |

|   |            | 8.2.5    | ISA Discussion                                  | 112 |

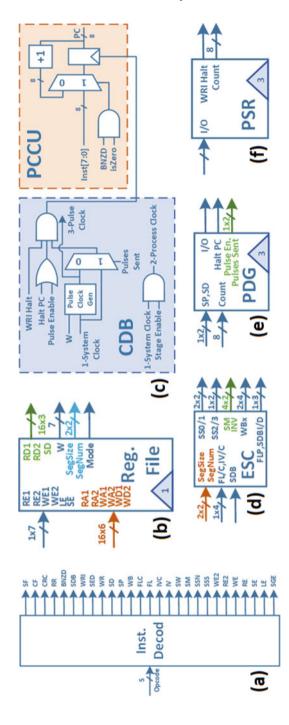

|   | 8.3        |          | Micro-Architecture                              | 112 |

|   |            | 8.3.1    | Memory Interface                                | 113 |

|   |            | 8.3.2    | Instruction Decoder                             | 113 |

|   |            | 8.3.3    | Register File                                   | 115 |

|   |            | 8.3.4    | Clock Distribution and PC Control               | 116 |

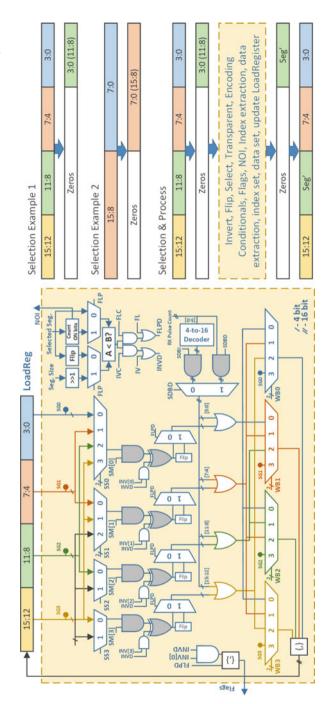

|   |            | 8.3.5    | Encoder and Select Control (ESC)                | 116 |

|   |            | 8.3.6    | Encoder and Selector (ES)                       | 117 |

|   |            | 8.3.7    | Pulse and Delay Generator (PDG)                 | 121 |

|   |            | 8.3.8    | Pulse Stream Receiver (PSR)                     | 121 |

|   |            | 8.3.9    | Interrupt Handler                               | 122 |

|   |            | 8.3.10   | Micro-Architecture Discussion                   | 122 |

|   | 8.4        | Experi   | mental Verification and Results                 | 123 |

|   | 8.5        |          | isions                                          | 126 |

| 9 | 4 nn       | lication | Hardware Platform for IoT Sensor Networks       | 127 |

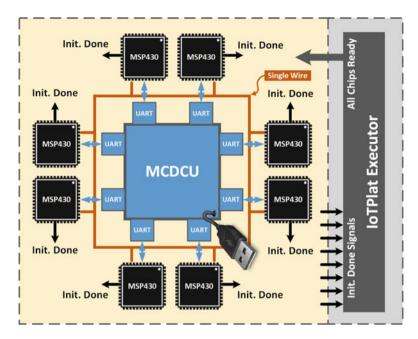

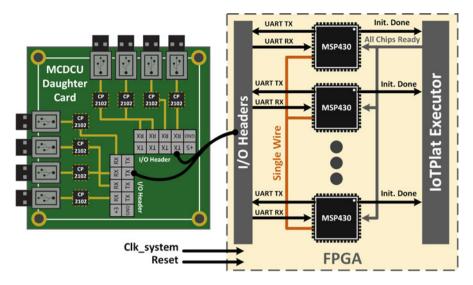

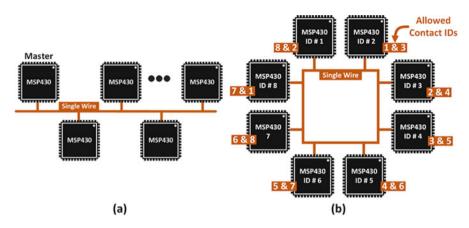

| 1 | 9.1        |          | m Architecture                                  | 127 |

|   | 9.2        |          | m Implementation and Testing                    | 129 |

|   | 1.2        | 9.2.1    | Sensor Nodes                                    | 129 |

|   |            | 9.2.2    | Multi-Core Debug Control Unit (MCDCU)           | 130 |

|   |            | 9.2.2    | Embedded C ECS1 Transceivers                    | 130 |

|   |            | 9.2.3    | System Integration                              | 131 |

|   | 9.3        |          | ler and Debugging Tools                         | 131 |

|   | 9.3<br>9.4 | -        | isions                                          | 132 |

|   | 2.4        | Concit   | 1010110                                         | 155 |

| 10  | Appli     | cation: Body-Coupled Communication | 135 |  |

|-----|-----------|------------------------------------|-----|--|

|     | 10.1      | Introduction                       | 135 |  |

|     | 10.2      | ECS Signaling and BCC              | 137 |  |

|     | 10.3      | BCC Transceiver                    | 138 |  |

|     | 10.4      | Testing and Verification           | 139 |  |

|     | 10.5      | Conclusions                        | 142 |  |

| Epi | logue .   |                                    | 143 |  |

| Ref | erence    | s                                  | 145 |  |

| Ind | <b>ex</b> |                                    | 151 |  |

# Abbreviations

| ACK    | Acknowledgement                             |

|--------|---------------------------------------------|

| APD    | Automatic Parameter Detector                |

| ASIC   | Application Specific Integrated Circuit     |

| BAN    | Boddy Area Network                          |

| BCC    | Boddy Channel Communication                 |

| BER    | Bit Error Rate                              |

| BPSK   | Binary Phase Shift Keying                   |

| CDB    | Clock Distribution Block                    |

| CDR    | Clock and Data Recovery                     |

| Cflags | Combined Flags                              |

| CNOI   | Combined NOIs                               |

| CoM    | Center of Mass                              |

| CPM    | Communication Processor Module              |

| CPU    | Central Processing Unit                     |

| DMA    | Direct Memory Access                        |

| DS     | Data Segment                                |

| Eb     | Energy per Bit                              |

| ECS    | Edge-Coded Signaling                        |

| ECSIA  | Edge-Coded Signaling Interface Architecture |

| EDS    | Encoded Data Segment                        |

| EFlags | Encrypted Flags                             |

| ENOI   | Encrypted NOI                               |

| EPD    | Encrypted PIC Data                          |

| ESC    | Encoder and Select Control                  |

| ESC    | Encoder and Selector                        |

| FPGA   | Field Programmable Gate Array               |

| FSK    | Frequency Shift Keying                      |

| HBC    | Human Body Communication                    |

| HDL    | Hardware Description Language               |

| IC     | Integrated Circuit                          |

| ISA    | Instruction Set Architecture                |

| LSB     | Least Significant Bit                           |

|---------|-------------------------------------------------|

| LTC     | Logical Topology Control                        |

| M2M     | Machine-to-Machine                              |

| MA5/1   | Modified A5/1                                   |

| Mbps    | Mega Bits Per Second                            |

| MCDCU   | Multi-Core Debug Control Unit                   |

| MSB     | Most Significant Bit                            |

| NOI/NOS | Number of Indices/Number of Symbols             |

| NRZ     | Non-Return-to-Zero                              |

| NST     | Normal Serial Transfer                          |

| NVL     | Number of Vulnerable Locations                  |

| OFDM    | Orthogonal Frequency-Division Multiplexing      |

| OOK     | On-Off Keying                                   |

| PCCU    | PC Control Unit                                 |

| PDG     | Pulse and Delay Generator                       |

| PHY     | Physical Layer                                  |

| PIC     | Pulsed-Index Communication                      |

| PIoT    | Prototyped IoT                                  |

| PLL     | Phase-Locked Loop                               |

| PSR     | Pulse Stream Receiver                           |

| RISC    | Reduced Instruction Set Computer                |

| RZ      | Returns to Zero                                 |

| SATA    | Serial AT Attachment                            |

| SRL     | Serializer                                      |

| SSFC    | Sandwiched Sensor Force Consolidators           |

| ST      | Schmitt Trigger                                 |

| TCP/IP  | Transmission Control Protocol/Internet Protocol |

| USB     | Universal Serial Bus                            |

| VLSI    | Very Large Scale Integration                    |

| WDM     | Wavelength-Division Multiplexing                |

|         |                                                 |

## Chapter 1 Introduction

[The transmitter] could, for example, take a written message and use some code to encipher this message into, say, a sequence of numbers; these numbers then being sent over the channel as the signal.

Warren Weaver

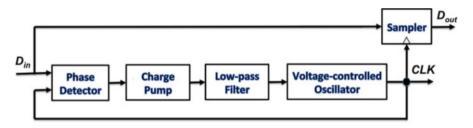

Not only is the Internet of Things (IoT) extending the reach of the Internet of People (IoP) to the world of inanimate objects, but also it is providing innovators, engineers, and technologists, with a golden opportunity to revisit some of the fundamental assumptions that have been at the basis of the IoP physical infrastructure and evaluate their relevance and compatibility with the IoT physical infrastructure. One of these fundamental assumptions is that the receiver in a single-channel, serial communication interface will need a synchronization circuit in order to recover the data bits from the incoming bitstream. Examples of such single-channel, serial communication interfaces include the humble USB, the ubiquitous Ethernet, and the high-performance fiber optics network. The latter has of course been crucial for the exponential growth of the IoP. The receiver synchronization circuit goes with a name that perfectly describes its function: clock and data recovery (CDR). Indeed, each CDR has the double duty to infer the clock signal from the incoming data bits and use this inferred clock signal to retime (or resample) the data bits at the most appropriate instant of the bit time. The inference of the clock signal is based on the transitions experienced by the incoming data bits, while the sampling times are selected using feedback circuit architectures, the most common of which is the so-called phase-locked loop (PLL). A generic architecture of a CDR circuit using PLL is given in Fig. 1.1. For a thorough treatment of CDR architectures, the reader is referred to Chapter 9 of [67].

One important aspect of CDR performance is that it is very much dependent on the encoding of the incoming bits. One of the most common bit encodings is the Non-Return-to-Zero (NRZ) code in which bit 1 is coded HIGH and bit 0 is coded LOW throughout the bit time. One of the objectives of CDR is to generate a clock signal whose rate is equal to the bit rate. Such generation depends on the detection of transition *edges* between HIGH and LOW bits. When the incoming data has long

<sup>©</sup> Springer Nature Switzerland AG 2022

S. Muzaffar, I. M. Elfadel, Secure, Low-Power IoT Communication Using Edge-Coded Signaling, https://doi.org/10.1007/978-3-030-95914-2\_1

Fig. 1.1 Generic architecture of a clock and data recovery circuit using PLL

stretches of HIGH or LOW bits, the transition information is missing, and the PLL has no edges to lock onto. One possible remedy to this loss of information is to use bit encodings in which the 1 bit returns to zero (RZ) during the latter 50% of the bit time, thus forcing a transition whenever a string of 1 bits is received. The Manchester encoding forces transitions for both the 1 and 0 bits during bit time, thus totally addressing the information loss problem in the CDR phase detector. Of course, the disadvantage of such RZ encodings is that they require larger channel bandwidth than the NRZ case or require that the transmitter send data bits at reduced rates to meet channel bandwidth constraints. Another approach to balance the bit transitions in the data stream is to use block encoding instead of bit encoding, and one of the most widespread block techniques is the byte-oriented 8b/10b encoding [79] that has been used in several communication technologies, including the Gigabit Ethernet, USB 3.0, SATA, and InfiniBand, among many others. The relevance of 8b/10b to CDR is that it guarantees that the difference between the numbers of 1 bits and 0 bits in the 10-bit code is at most 2 and that no more than 5 bits can have the same value in a row.

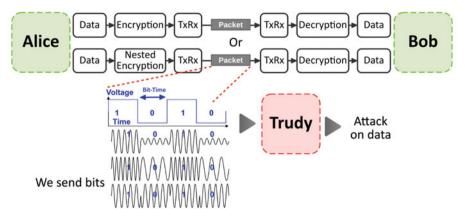

Based on this well-established interplay between CDR performance and data encoding, one is led to ask the extreme but basic question whether *there exist data encodings that would totally do away with CDR while maintaining reasonable levels of data rate and reliability*. The pertinence of this question to the IoT infrastructure is that with such encodings the receiver architecture in a sensor or actuator device can be significantly simplified with the resulting architecture taking much smaller footprint and consuming less power. Of course, such simplified, low-power, compact architecture must not compromise another crucial requirement for constrained IoT nodes, namely, data authentication and security. One potential approach to providing a layer of data protection is lightweight cryptography, which despite much recent progress still requires a significant area and power overhead, while its lightweight nature makes it a relatively easy target for malicious attacks.

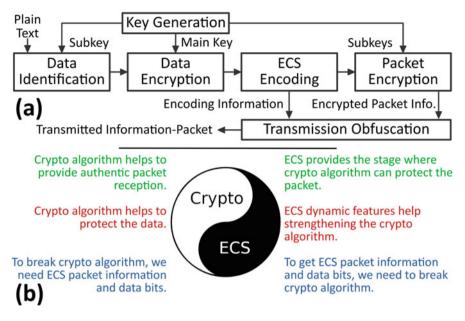

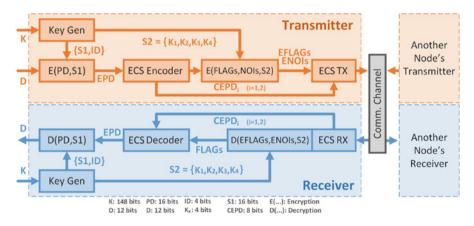

The answer to this existence question has turned out to be affirmative with the recent emergence of a novel family of block-oriented signaling techniques for single-channel, serial communications. These techniques are based on the fundamental concept of encoding data bits as pulse trains whose counts are also transmitted and used by the receiver for decoding. Since the receiver uses the rising edges of the pulses to decode the transmitted bits, this family of protocols is called *Edge-Coded* Signaling (ECS) [56] and hence the title of this book. The three representative members of this novel family are ECS1 [57], ECS2 [51], and ECS3[56]. While the three techniques require no CDR, they differ in fundamental aspects that are related to transmission security and packet reliability. ECS1 and ECS3 have been proven compatible with symmetric stream ciphers and capable of providing multilayered protection of data in transmitted packets [59]. ECS2 has no such compatibility and is not amenable to multilayered encryption for secure data transmission. On the other hand, ECS2 and ECS3 achieve better data rates than ECS1 and have been experimentally proven to have less packet transmission failures than ECS1 [51]. We will explore the three ECS family member techniques in Chap. 2. The main objective of this chapter is to describe the most recent version of the family, ECS3, that combines and enhances the best advantages of ECS1 and ECS2 while avoiding their pitfalls and shortcomings. ECS1 and ECS2 are also included in the chapter as the earlier variants of the protocol. The newest family member shares with ECS1 and ECS2 the same underlying idea of encoding bits as pulse streams with inter-symbol spacings used to separate data words. However, ECS3 possesses several additional features above and beyond ECS1 and ECS2, including the following:

- 1. ECS3 employs an optimized segmentation process and a simplified encoding scheme that help reduce the number of ON bits and lower their index numbers. The process ultimately reduces the overall number of *packet* pulses needed to transmit a *data* word.

- For a given data word length, ECS3 forms the most compact packet and therefore results in the maximum data rate. This is achieved mainly through a very compact header describing the encoding operations to which the data bits have been subjected.

- 3. Not only does ECS3 exploit the edge detection of received pulses to eliminate the need for CDR and to achieve remarkable robustness with respect to jitters, skews, and clock inaccuracies between the transmitter and receiver, but it also provides the flexibility of architecting transceivers to transmit multiple data words or to pipeline data transmission.

- 4. The ECS3 packet has a layered architecture and dynamic features that can be combined synergistically with the crypto algorithms to enhance communication security.

- 5. ECS3 is architecturally flexible in that it can be configured according to any signaling topology such as Master–Slave, Ring, Star, or Tree.

The data protection approach that ECS3 and ECS1 enable is based on a tight synergy between the communication protocol and the lightweight encryption algorithm with the communication protocol providing the encryption algorithm with additional protocol parameters whose encryption can further protect the data. In comparison with existing single-wire, CDR-less protocols such as 1-wire [10, 16, 26, 27, 44, 78], ECS1 has the double advantage of higher data rates (Mbps vs. Kbps) and stronger security (up to a factor of 2<sup>20</sup> increase in attack complexity)

while remaining within the IoT device envelop of power and footprint. The ECS security mechanism is discussed in detail in Chap. 7.

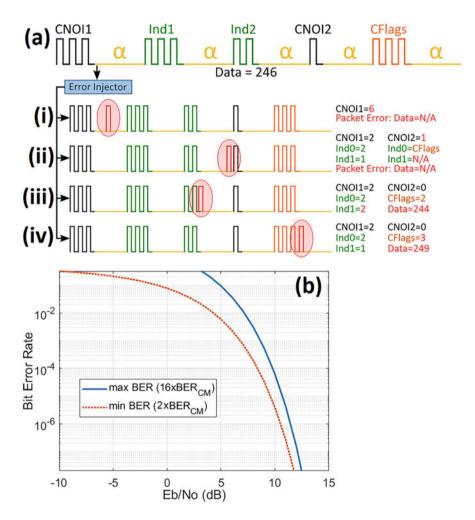

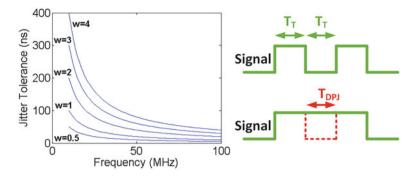

Chapter 3 focuses on the detailed analysis of ECS protocols. In this chapter, we also present a full quantitative analysis of the timing and robustness properties of ECS protocols, including the impact of important protocol parameters such as pulse width and inter-symbol separator on average data rate and protocol robustness with respect to clock variations. The main result of this chapter is a theoretical upper bound on clock variability between transmitter and receiver below which the protocol operates with zero decoding error over an ideal channel.

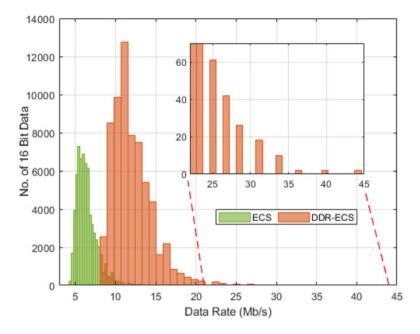

ECS encodes information using pulse counts with the counting based on one of the pulse edges. In Chap. 4, we address the problem of improving the ECS data rate for a given clock frequency and under a given power envelop by using both pulse edges of the ECS pulse stream. We call the novel protocol double data rate ECS (DDR-ECS) in analogy with DDR memory systems. While the concept is intuitive and attractive, its hardware implementation is not. This chapter, therefore, presents an efficient hardware design of the DDR-ECS transceiver that preserves the ECS built-in features while essentially doubling the data rate at the same clock frequency and within the same power budget [55].

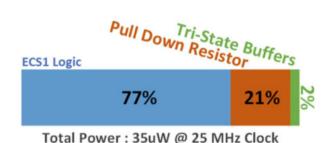

Chapter 3 highlights the power savings that ECS can achieve as a result of the elimination of circuitry devoted to clock and data recovery. In Chap. 5, we show that further power saving can be achieved using the duty cycle of the pulse as a power control parameter. This power control policy is applied to a single-wire link with significant power saving achieved above and beyond the savings due to CDR elimination. These power savings are obtained without any impact on data rate [48].

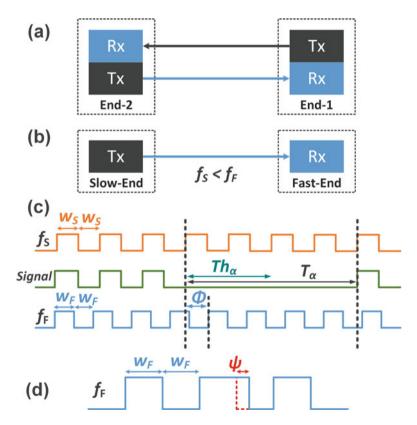

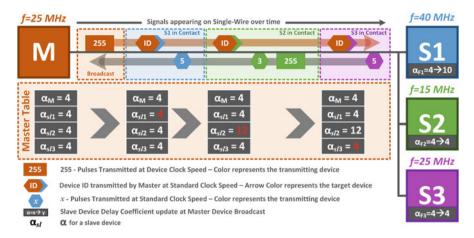

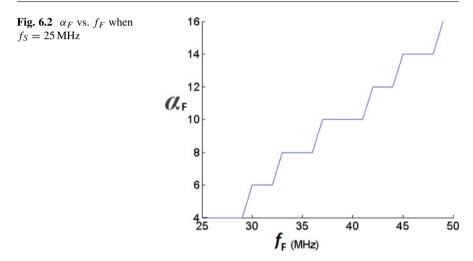

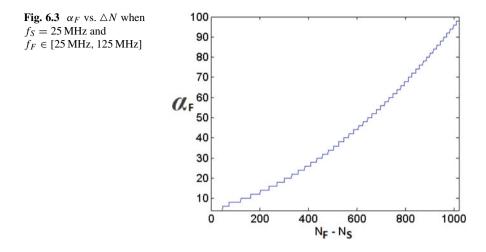

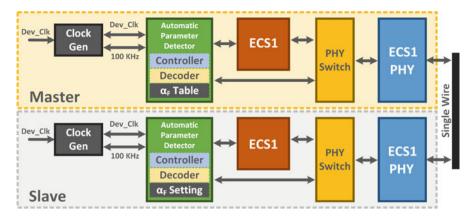

Well-known multi-wire protocols, such as I2C, SPI, and UART, need to set the same baud rate on both ends of the link before the connected devices start communicating. The baud rates of all these devices are either factory set or require to be configured manually. Manual configuration is usually performed either by using the software settings or by hardware control. ECS family member techniques can also be configured on a per-device basis in a similar fashion, but such an approach will defeat the very purpose of ECS in providing a scalable, robust, ultra-low-power, and high data rate communication protocol for IoT devices. The error-free operation of ECS with maximum data rate requires a careful and judicious setting of ECS data packet and pulse timing parameters. In Chap. 6, we present a new algorithm for automatically detecting and setting the ECS protocol parameters at the poweron phase while removing the restriction on the IoT devices in the ECS network to communicate at a given baud rate. The hardware realization of the algorithm is power-efficient and uses closed-form formulas that assign suitable protocol parameters to both ends of the transmission link based on clock rate differences. This difference is determined by a preliminary exchange of clock pulse streams between the transmitter and the receiver. The automatic parameter setting remains operational even in the presence of variations between the local clock frequencies of the IoT devices communicating via ECS. The algorithm is illustrated in the case of several IoT devices with different local clock frequencies that are in need to synchronize their communication parameters with respect to the clock frequency of a master gateway node [58].

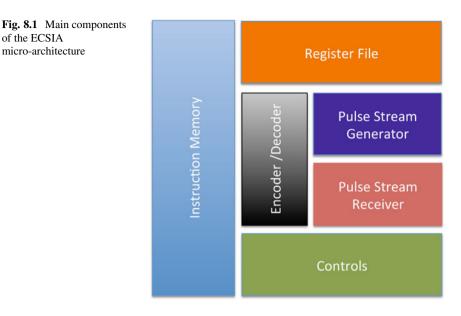

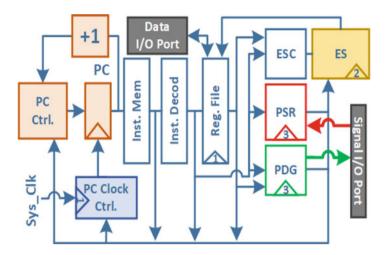

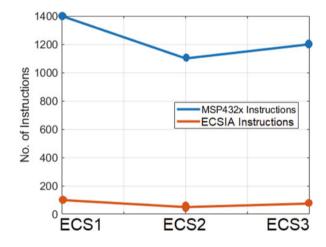

In Chap. 8, we present a domain-specific processor architecture, named Edge-Coded Signaling Interface Architecture (ECSIA). Aside from the traditional aspects of ISA design such as addressing modes, instruction types, instruction formats, registers, interrupts, and external I/O, the ISA includes domain-specific instructions that facilitate bit stream encoding and decoding based on the edge-coded signaling techniques. The domain-specific ECSIA micro-architecture employs a set of optimized processing blocks that can be used programmatically to encode and decode the transmitted data in the most economical way. The ECSIA allows customizations that support both standard edge-coded signaling techniques and specialized protocols that belong to the same family. The ECSIA design further allows an amalgamation of software and hardware that significantly reduces the number of instructions required to implement a given communication interface without impacting the data rates and reliability of the pulsed-signaling protocols [52, 53].

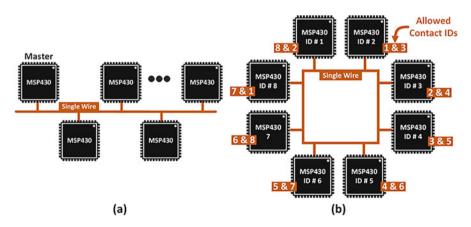

The last two chapters, Chaps. 9 and 10, are devoted to describing two recent applications of ECS communication technique. An FPGA hardware platform for the prototyping and analysis of ultra-low-power IoT sensor networks is discussed in Chap. 9. The platform is meant to address the problem of evaluating network topology design options for IoT sensor communications using single-channel communication protocols. The network topologies include bus, star, ring, and tree topologies. This FPGA-based IoT network platform is based on three fundamental ingredients: a full HDL implementation of the ultra-low-power TI MSP430 micro-controller, a novel ultra-low-power single-wire communication protocol that does not require any clock and data recovery, and embedded C implementation of the transceivers within the TI MSP430 without any need for external hardware circuitry. The platform is flexible in that it allows the design, analysis, and comparison of various networking graph topologies among the IoT sensors, including ones that contain gateways and hubs. The platform is also scalable in that the resources used for a two-sensor point-to-point communication are minimal [50].

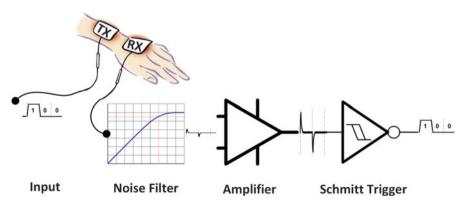

The second application in Chap. 10 is a self-synchronizing, low-power, lowcomplexity body-coupled communication (BCC) transceiver using the ECS techniques. The unique features of these techniques are used to simplify the BCC transceiver hardware and reduce its power consumption by eliminating the need for circuits dedicated to clock and data recovery (CDR) and duty cycle correction. The self-synchronizing feature of the transceiver is achieved by exploiting the edgecoding property of ECS. A working prototype of the proposed BCC transceiver using off-the-shelf components is developed and used to test, for the first time, a full, bi-directional BCC link by transmitting arbitrary 16-bit data words through the human body over a range of 150 cm with *zero* bit error rate and sub-1nJ/bit energy efficiency [54].

## Chapter 2 Edge-Coded Signaling Techniques

When one door closes another door opens; but we so often look so long and so regretfully upon the closed door, that we do not see the ones which open for us.

Alexander Graham Bell

The objective of this chapter is to present the analysis of signaling protocols for data transfer over a single-wire achieving high data rates (in the Mbs range), low power consumption, and small footprint. The protocols do not require a CDR, can operate with signals at low amplitude voltage ( $\sim 1$  V), has simple encoding and decoding schemes, and can tolerate baud rate differences between transmitter and receiver. We collectively refer to this new family as Edge-Coded Signaling (ECS) because its core idea is to transfer the indices of only the ON bits as a series of transition edges rather than bit times. A very compact packet header gives information about the number of such indices and the encoding operations to which the raw bits have been subjected. When the pulses are received, the receiver applies the appropriate decoding to infer the original data bits. The ECS protocols are dynamic in that they can accommodate several data rates. It exploits edge detection of incoming pulses to achieve remarkable robustness with respect to jitters, skews, and clock inaccuracies between the transmitter and the receiver. The protocols achieve significant improvements in data rate, reliability, packet security, and power efficiency with respect to state-of-the-art CDR-less techniques. ECS is also architecturally flexible in that it can be configured according to the signaling topology (Master-Slave, Ring, Star, etc.).

#### 2.1 Edge-Coded Signaling (ECS)

#### 2.1.1 Edge-Coding Scheme

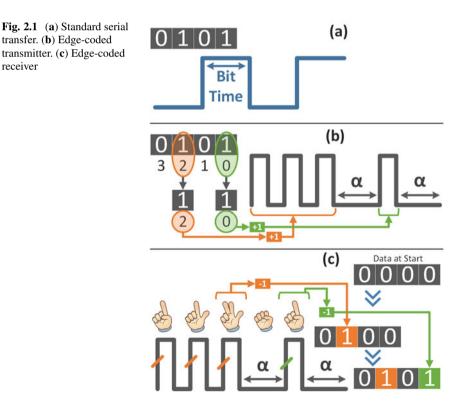

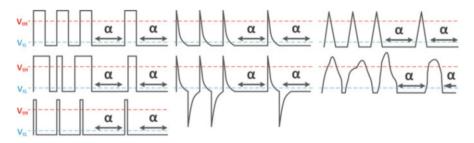

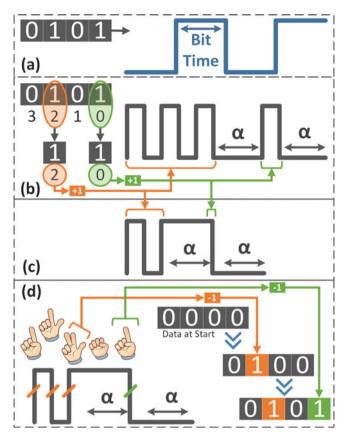

The core idea of ECS is to select the ON bits in a data word and transmit their index numbers as pulse streams instead of transmitting the data bits themselves. An example is given in Fig. 2.1 where the bit sequence "0101" (a) is transformed into series of pulses (b) in which the count of pulses in each series is n + 1 with n being the ordinal number of the ON bit in the binary sequence. In the example of Fig. 2.1b, there are two series of pulses. The first series has one pulse corresponding to the leading ON bit at position 0, and the second series has three pulses corresponding to the ON bit at position 2. One series of pulses is separated from an adjacent one by an inter-symbol separator  $\alpha$ . Please note that  $\alpha$  is not a time delay but rather a spacing or separation symbol that is measured in clock cycles with the clock-cycle count given by the local transmitter clock at transmission and the local receiver clock at reception. The clocks at both ends do not have to be synchronized. Also, note that one is always added to the pulse count corresponding to the index number. This

operation is necessary to handle the transmission of index 0. Otherwise, no pulse will be transferred if the bit at index 0 is ON. For each input pulse series, the ECS receiver counts the number of the incoming rising edges, subtracts one to retrieve the index number (i.e., n = PulseCount - 1), and sets a data bit at the index number. This is shown in Fig. 2.1c. The apparent drawback is that more work is seemingly needed to transmit such pulse series than the raw bits themselves. However, this is not the case as it is conceivable to achieve high data rates, using an encoding process that makes the index numbers as small as possible. This is accomplished by breaking the bit stream into smaller segments, reducing the number of ON bits as much as possible in each segment and relocating these ON bits to the lowest index positions. The encoding information and the number of ON bits in the encoded data are sent as a packet header along with the index numbers. All the information in the packet header itself is transmitted as pulse streams, exactly as the index numbers. In short, instead of transmitting bits, ECS codes them as edge counts and transmits them along with the formatting information, itself edge-coded, so that the receiver is able to reconstitute the data word. The steps involved in ECS transmission are explained in the following subsections.

#### 2.1.2 ECS Segmentation

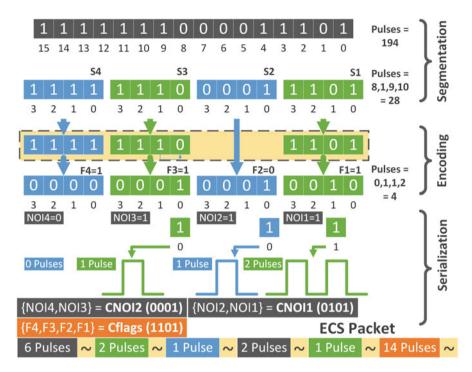

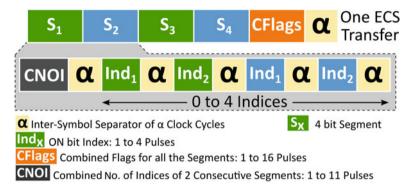

The number of pulses to transmit increases rapidly with the data word size *B* and the number of its ON bits. The most significant bits require larger number of pulses to represent their index numbers. Considering the worst case where all the bits are ON, the number of pulses required would be B(B + 1)/2. The rapid increase in the number of pulses reduces the data rate rapidly and, therefore, the count of pulses must be limited. To do so, ECS breaks the data word into smaller segments of size l = 4 bits each, thus limiting the index numbers to a maximum of 3 (i.e., 4 + 3 + 2 + 1). With the reduced segment size, the maximum number of pulses per segment reduces to 10. An ECS segmentation example is given in Fig. 2.2 where a 16-bit word is partitioned into 4-bit segments  $S_i$ , 1 < i < 4. The segmentation steps are also shown in Algorithm 1 on lines 1 and 2. The optimization of the segment size *l* is discussed in Sect. 2.2.

#### 2.1.3 ECS Encoding

The increase in data word size also increases the number of inter-symbol separators needed to separate out the pulse streams, representing the ON bits. Such separators reduce the data rate significantly. Reducing the number of ON bits helps in mitigating the effect of separators on data rate. ECS encoding effectively reduces the number of ON bits in each data segment. The ECS encoding is simply a conditional bit-wise NOT operation on a target segment, with the condition being that the

Fig. 2.2 Example: ECS packet formation

#### Algorithm 1 ECS segmentation and encoding process

#### **Inputs:**

- Data: 16-bit data word

#### **Outputs:**

- CFlags: Concatenated Encoding Indicators

- CNOI1, CNOI2: Concatenated ON-bit Counts

- 1:  $S_1 = Data[3:0], S_2 = Data[7:4]$ 2:  $S_3 = Data[11:8], S_4 = Data[15:12]$ 3: for i=1 to 4 do 4:  $NOI_i = countONbits(S_i)$ 5:  $F_{i} = 0$ 6: if  $NOI_i > l/2$  then 7:  $S_i = \sim S_i$ 8:  $F_{i} = 1$ 9:  $NOI_i = countONbits(S_i)$ 10: end if 11: end for 12:  $CFlags = \{F_4, F_3, F_2, F_1\}$ 13:  $CNOI_1 = \{NOI_2, NOI_1\}, CNOI_2 = \{NOI_4, NOI_3\}$

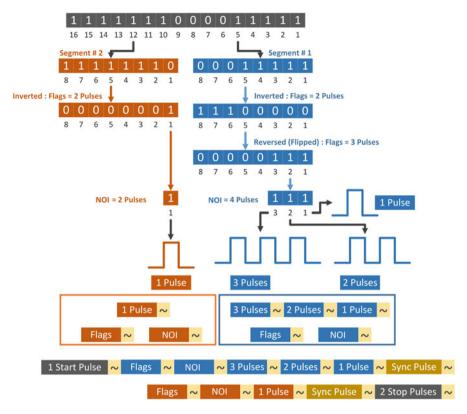

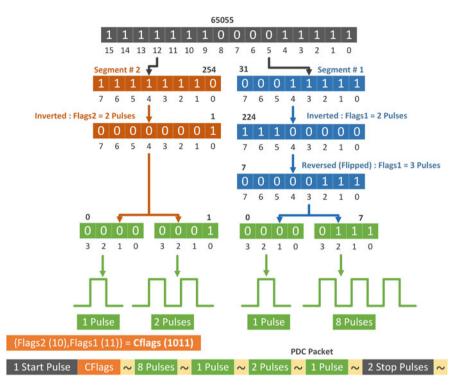

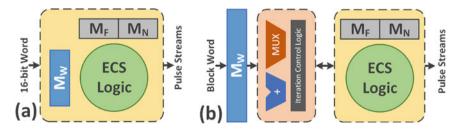

number of ON bits in a segment is longer than half of the segment size. To explain the encoding scheme further, let us assume B = 16. If a segment satisfies the said condition, bits of the segment are inverted and a 1-bit flag,  $F_i$ , is set to represent the applied operation. The subscript *i* represents the segment number. The encoding steps are presented in Algorithm 1 from lines 3–11 and in the encoding section of Fig. 2.2. Each segment is processed independently, and four distinct flags are generated, one for each segment. These four flags are then concatenated to yield a single 4-bit flag named *CFlags*. Additionally, the encoding process produces four 2-bit Numbers of Indices, each, denoted  $NOI_i$ , representing the number of ON bits in segment *i*. The *NOIs* of two consecutive segments are concatenated to yield two 4-bit concatenated NOIs that are denoted CNOIs. The generation of CFlags and CNOIs is shown in Algorithm 1 on lines 12 and 13 and in the serialization section of Fig. 2.2. At the end of this process, all the information required for transmission gets compacted in nibbles of 4 bits each, which is the same as the size of the 4bit segment and, hence, helps in maximizing the data rate. The efficient hardware implementation of an encoder performing segmentation and encoding is discussed in Sect. 2.4.

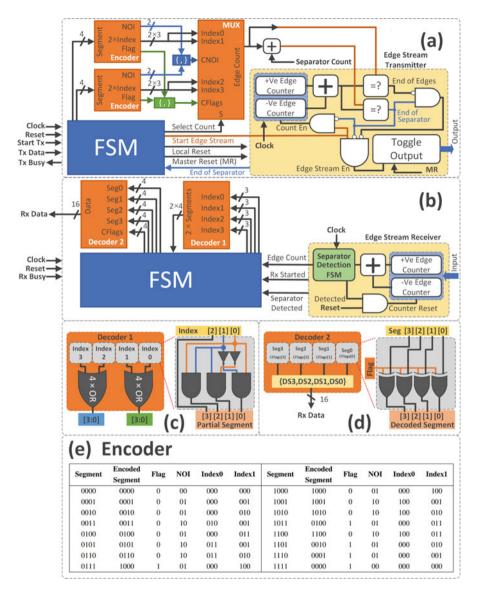

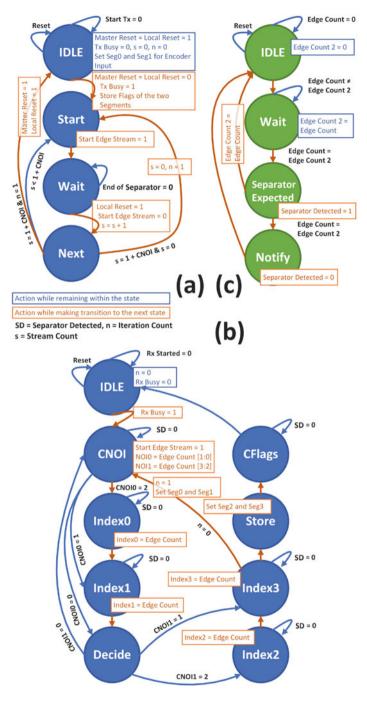

#### 2.1.4 ECS Transmitter

#### **Pulse Stream and Separator Generation Scheme**

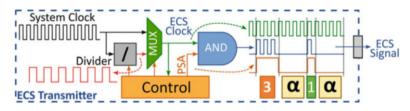

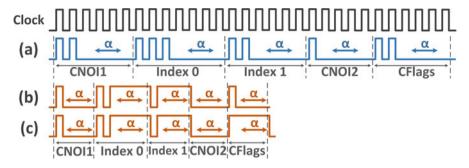

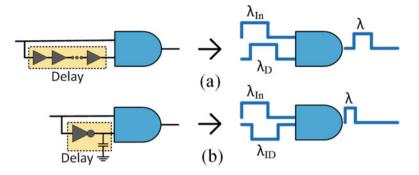

In the ECS transmission process, the ECS scheme for generating the pulse streams and the inter-symbol separators plays a crucial role. The encoding pulses in the ECS packet and the  $\alpha$  spacings between packets are generated using the ECS clock, which can be obtained in two ways. One way is for the system clock to be routed directly to the ECS clock port. Another way is for the system clock to be divided to generate a slower ECS clock. The pulse generation process is illustrated in Fig. 2.3. The ECS clock is ANDed with a control signal, *Pulse Stream Active* (PSA), set by the control module. The PSA is high during the transmission of a pulse stream, allowing the ECS clock cycles to go through. During the transmission of the intersymbol separator  $\alpha$ , PSA is low, thus gating the ECS clock. Please note that  $\alpha$  in ECS is not a time delay, but rather a count of the rising or falling edges of the ESC clock. In Fig. 2.3, we have used  $\alpha = 4$  clock cycles as it is the optimal count at which the maximum data rate is achieved. This will be discussed further in Sect. 2.2.

#### **Transmission Flow**

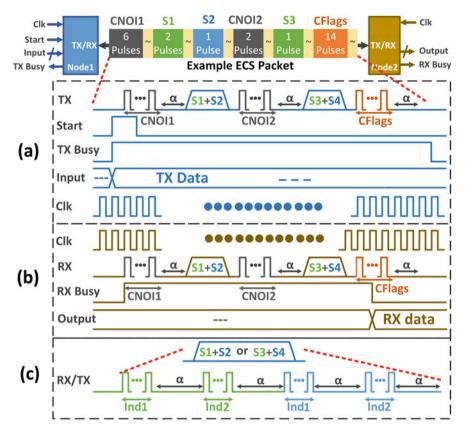

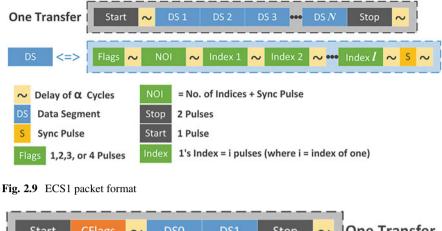

The format of the ECS packet is shown in Fig. 2.4 and a numerical example is given in Fig. 2.2. The *CFlags* are transmitted to inform the receiver about the encoding process, while the *CNOIs* are transmitted to help the receiver account for all the incoming ON bit indices. The ECS transceiver starts the transmission by sending a

Fig. 2.3 ECS pulse stream and inter-symbol separator generator (indices from Fig. 2.1)

Fig. 2.4 ECS packet

pulse stream with a pulse count equal to  $CNOI_1 + 1$  followed by an inter-symbol separator  $\alpha$  of four clock cycles (line 2 in Algorithm 2). The additional pulse is needed to inform the receiver not to expect any index number when the count of ON bits in the first two segments is zero. Next, the transmitter sends a number of pulse streams equal in count to  $NOI_1 + NOI_2$  followed by an  $\alpha$  at the end of each stream. The pulse count in each pulse stream is equal to the index number of an ON bit in segments  $S_1$  and  $S_2$  plus an additional pulse, making a total of *index* + 1 pulses. The additional pulse is used to handle the transmission of a zero index number. The transmission process of indices is presented in Algorithm 2 on lines 3 through 9. A similar transmission follows for the next two segments,  $S_3$  and  $S_4$ , during which  $CNOI_2$  and the index numbers of the ON bits in these segments are transmitted. At the end of the transmission of all segments, the CFlags are transmitted, also in the form of a pulse stream followed by an  $\alpha$  (line 10 in Algorithm 2). Their pulse count is equal to CFlags + 1. An additional pulse is needed to represent zero content of CFlags as in the case when no segment goes through the encoding inversion. The graphical transmission process and the generated waveforms are shown in Fig. 2.6.

#### Algorithm 2 ECS transmitter algorithm

#### Inputs:

```

- CFlags: Concatenated Encoding Indicators

```

```

- CNOI<sub>1</sub>, CNOI<sub>2</sub>: Concatenated ON-bit Counts Outputs:

```

- ECS Signal: The pulse streams and inter-symbol separators

```

1: for j=1,2 do

2:

sendPulsesWithSeparator(CNOI_i + 1, \alpha)

3:

for each ON bit in S_{2i-1} with index i do

4:

sendPulsesWithSeparator(i + 1, \alpha)

5:

end for

6:

for each ON bit in S<sub>2i</sub> with index i do

7:

sendPulsesWithSeparator(i + 1, \alpha)

8:

end for

9: end for

10: sendPulsesWithSeparator(CFlags + 1, \alpha)

```

#### 2.1.5 ECS Receiver

#### **Pulse Stream and Separator Reception**

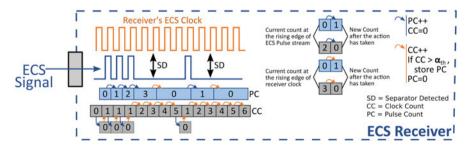

The ECS receiver is unique in that it does not require any clock and data recovery (CDR) circuitry either to receive the incoming data over single channel or to synchronize it with a local clock. The ECS exploits detection and count of edges of the incoming pulse streams to receive all the information required to rebuild the transmitted data successfully. Contrary to standard serial transfer, the width of transmitted pulses is inconsequential to ECS and, hence, does not employ this information in receiving data. Though there could be different implementations of the ECS receiver, our implementation is focused on counting the number of clock cycles between two ECS pulses to detect the inter-symbol spacing and separate out the incoming pulse streams. The ECS pulse stream reception process is illustrated in Fig. 2.5. The ECS receiver keeps track of two counts, the pulse count and the clock count. The reception process starts with the very first rising edge of the input pulse stream. At each rising edge of the pulse stream, the pulse count is incremented, and

Fig. 2.5 ECS pulse stream and inter-symbol separator receiver (input signal from Fig. 2.3)

Fig. 2.6 (a) Transmitter. (b) Receiver. (c) Indices

the clock count is cleared. At each rising edge of the receiver's ECS clock, the clock count is incremented and compared with a separator threshold  $\alpha_{th}$  that is set to half of  $\alpha$  in our implementation of the protocol. If the condition is satisfied, an intersymbol separator is declared, and the current pulse count is accordingly stored as a record of the transmitted packet.

#### **Reception Flow, Decoding, and Reconstruction**

The ECS packet reception process starts with the very first rising edge of the first pulse stream for  $CNOI_1$ . The pulse stream is received as described in the previous subsection. Similarly, all the following pulse streams for the indices of  $S_1$ ,  $S_2$ , and  $CNOI_2$  and the indices of  $S_3$ ,  $S_4$ , and CFlags are received, and the corresponding parts of the ECS packet are updated. Bits of each segment are complemented if the corresponding bit in CFlags is set. At this stage, all the transmitted segments are assembled to rebuild the data word. The full process of receiving, decoding, and

assembling is shown in Algorithm 3. An efficient implementation of ECS encoding and decoding is discussed in Sect. 2.4. The transmission and reception processes along with their generated waveforms are shown in Fig. 2.6.

| Algorithm 3 ECS receiver algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inputs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| - ECS Signal: The pulse streams and inter-symbol separators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Outputs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| - Data: 16-bit data word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

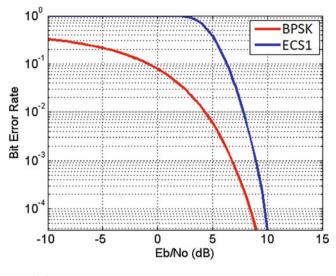

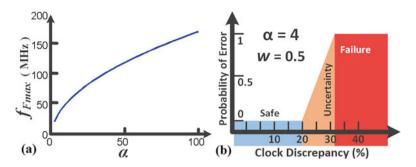

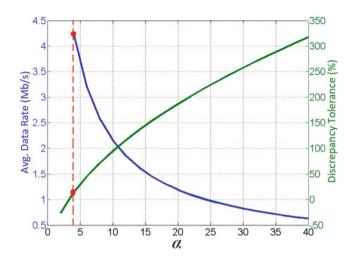

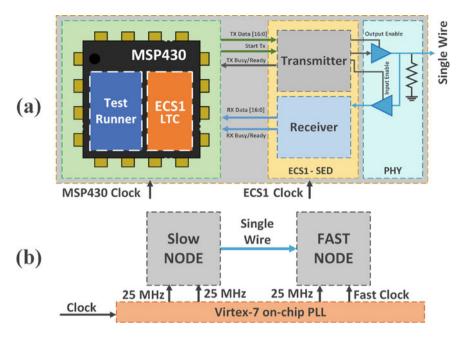

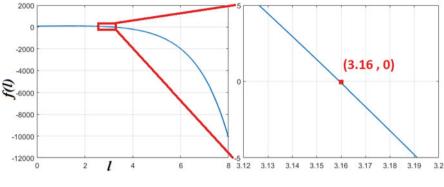

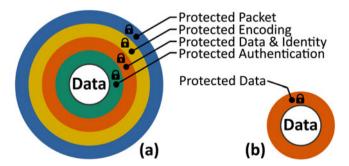

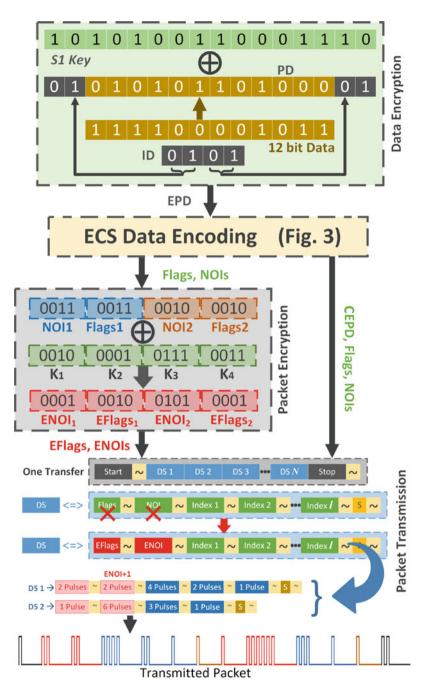

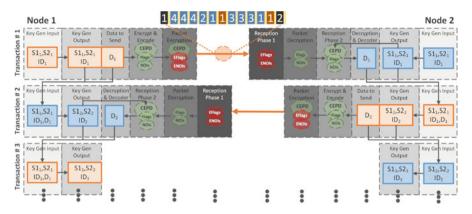

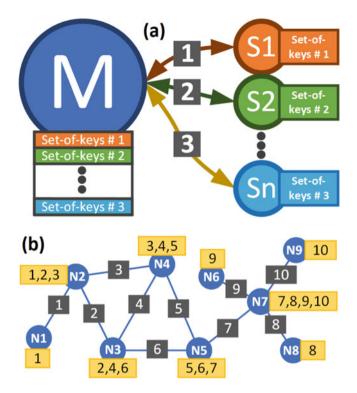

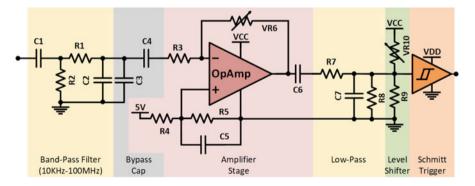

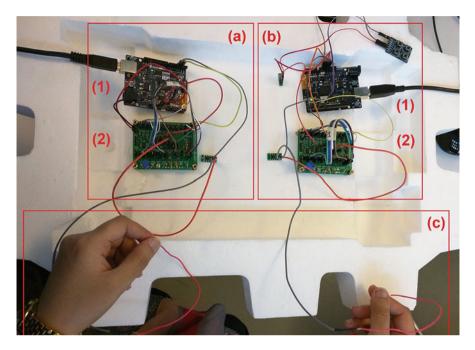

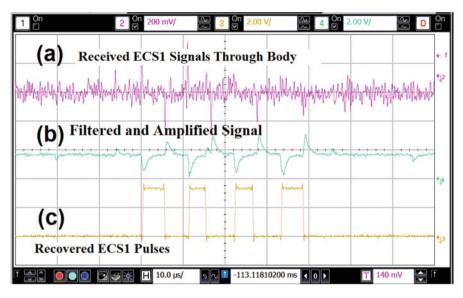

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |