Benedetto Vigna Paolo Ferrari Flavio Francesco Villa Ernesto Lasalandra Sarah Zerbini *Editors*

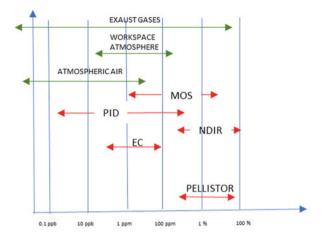

# Silicon Sensors and Actuators

The Feynman Roadmap

Silicon Sensors and Actuators

Benedetto Vigna • Paolo Ferrari Flavio Francesco Villa • Ernesto Lasalandra Sarah Zerbini Editors

## Silicon Sensors and Actuators

The Feynman Roadmap

*Editors* Benedetto Vigna Analog MEMS & Sensors R&D STMicroelectronics (Italy) Cornaredo, Milano, Italy

Flavio Francesco Villa ST Microelectronics, Analog MEMS and Sensors Group, MEMS Technology and Design R&D Agrate Brianza Monza Brianza, Italy

Sarah Zerbini Analog, MEMS and Sensors Group STMicroelectronics (Italy) Cornaredo, Milano, Italy Paolo Ferrari ST Microelectronics, Analog MEMS and Sensors Group, MEMS Technology and Design R&D Agrate Brianza Monza Brianza, Italy

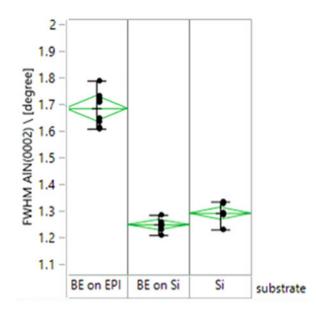

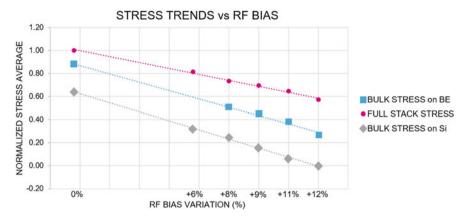

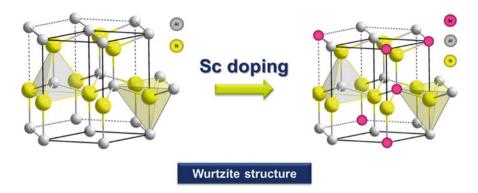

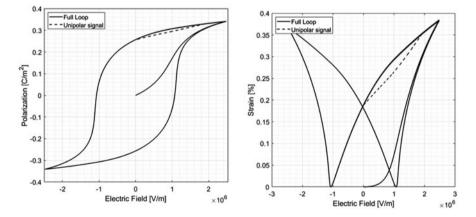

Ernesto Lasalandra Analog, MEMS and Sensors Group STMicroelectronics (Italy) Cornaredo, Milano, Italy

#### ISBN 978-3-030-80134-2 ISBN 978-3-030-80135-9 (eBook) https://doi.org/10.1007/978-3-030-80135-9

© Springer Nature Switzerland AG 2022, corrected publication 2022

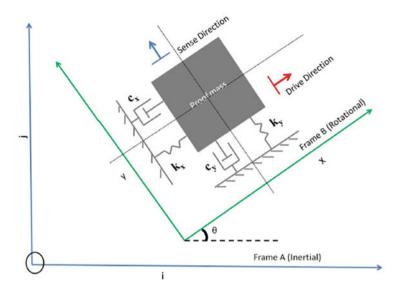

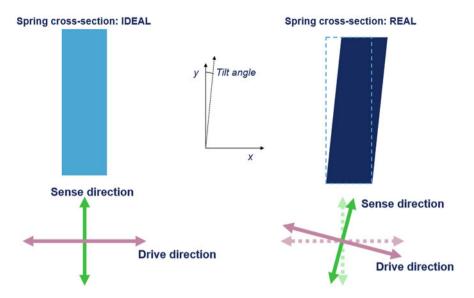

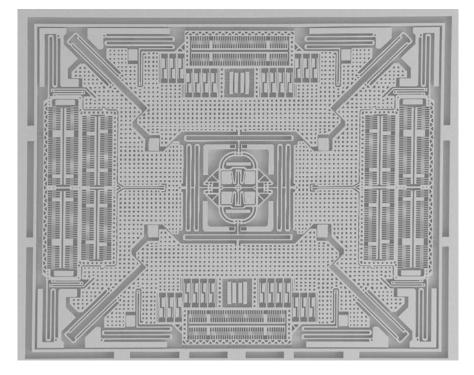

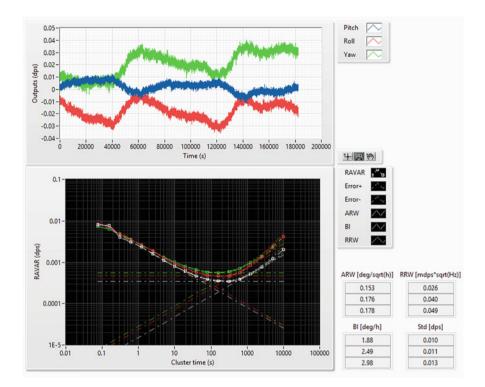

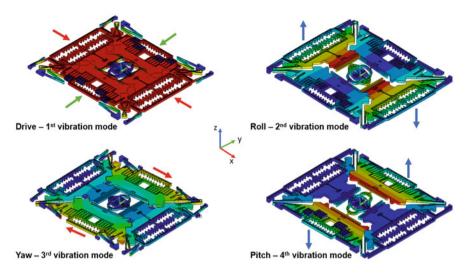

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

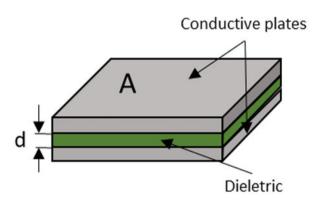

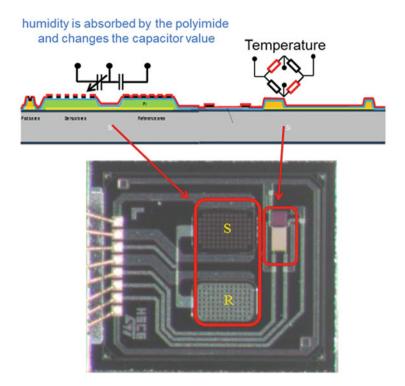

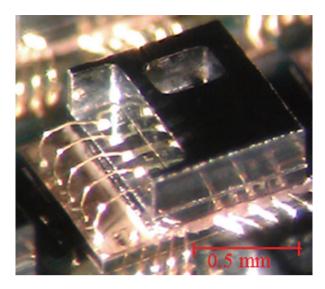

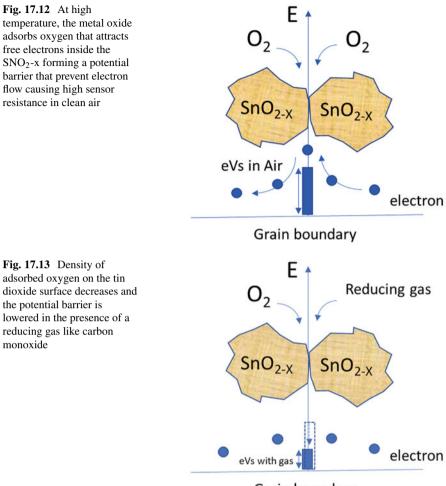

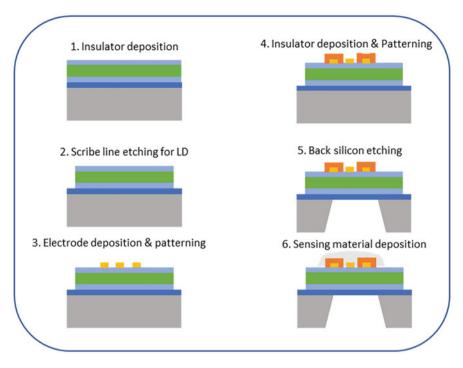

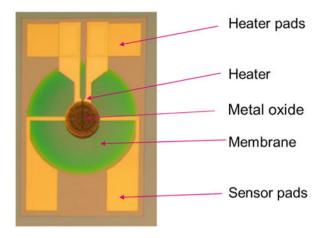

#### Foreword

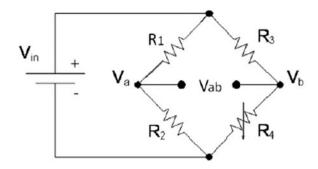

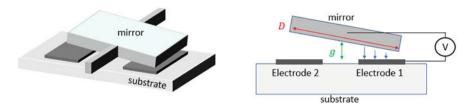

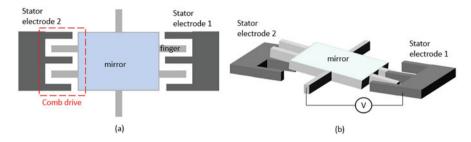

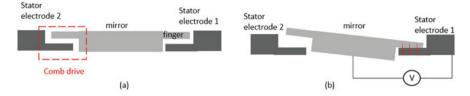

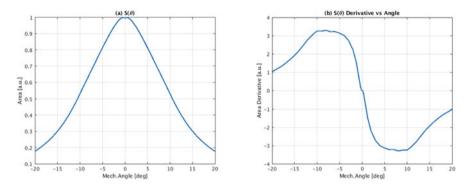

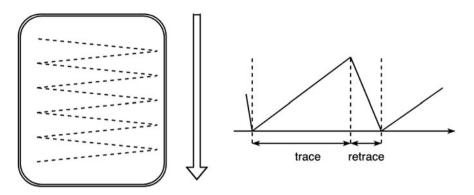

I have spent my entire professional career in the semiconductor industry, and I had the pleasure and the luck to see in first person two important turning points of this industry. In the 1960s, the technological community started to integrate successfully on silicon many transistors aiming to mimic the function of the brain, the memory, the nervous system, and the muscle of human beings. In the 1990s, instead, new components, such as variable capacitors and variable resistors, became the core of miniaturized silicon transducers, either sensors or actuators, and we started to integrate into silicon the five senses of human beings. It has been for sure a big revolution.

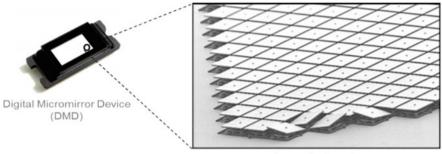

In the last 20 years, the pace of transducer development accelerated thanks to the progresses in microfabrication techniques and successful high-volume market applications. Nowadays, transducers are all around us: in cars, in smartphones, in factories, in printers, in tablets, in satellites, in drones, in smart speakers, in watches, and even in medical patches and shoes.

There is no doubt we are living in interesting times, with many challenges opportunities in front of us. Internet of Things, artificial intelligence, and 5G networks will boost the GDP of many countries and will enable new business models. I really hope these new technologies will help reduce the negative impact of humankind on nature and will also help reduce the gap between the richest and poorest countries in the world.

Within the frame of this new blurred world, micromachined silicon sensors will play even a more important role than today. Several parameters, such as vibrations, sound, atmospheric pressure, pollution level, will reach the digital world without the need of people typing on a keyboard or moving a mouse or touching an advanced display.

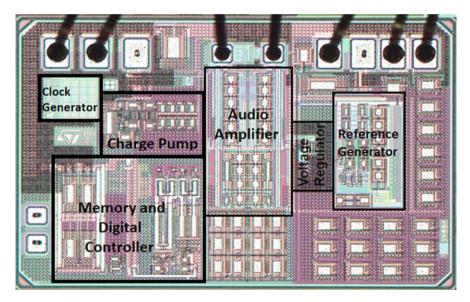

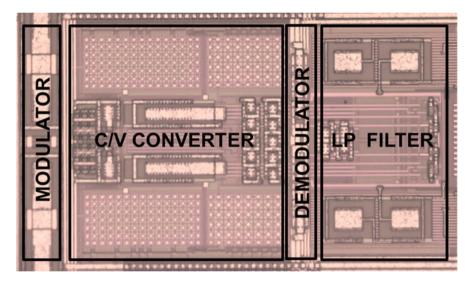

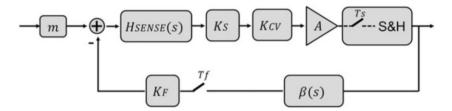

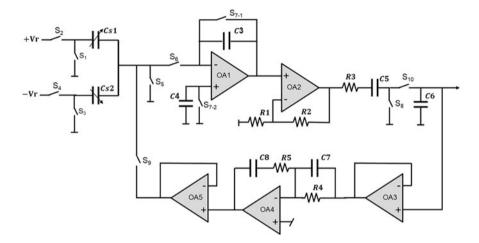

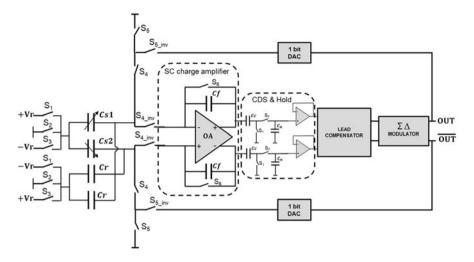

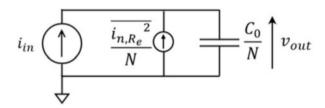

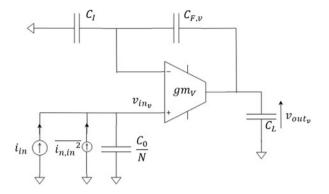

The most successful transducers in the market are not exploiting complex quantum physics effects. Their operation mode is relatively easy to be understood. But under this apparent simplicity, two big challenges reside. On one side, being multidisciplinary devices, they require the mastering of many disciplines (physics, engineering, electronics, and materials science) for their proper design. On the other side, there are many secrets and details to be tailored during their qualification and their production so to reach the high-yield high-reliability low-cost target. In my career, I have been contacted by many professors and startups and I read many papers about innovative transducers. But only few of them reached the market successfully, because they tackled properly all the dimensions, beyond the intrinsic beauty of a new silicon structure.

Physics and technology of silicon-based transducers are rather complex, and they are treated in numerous publications scattered throughout the literature. Therefore, a clear need exists for a book that thoroughly and systematically reviews the present basic knowledge on these devices. My enthusiastic welcome, therefore, goes to this enlightening book, *Silicon Sensors and Actuators*, written with the contributions of more than eighty authors with different backgrounds and education (technologists, physicists, and electronic, mechanical, and biotech engineers). At the origin of this book and its scientific contents, there is a fantastic adventure, which began about 25 years ago in STMicroelectronics, a mature hi-tech semiconductor multibillion-dollar company. All these people, with the support of whole organization of STMicroelectronics and the one of Academic and research centers all over the world, have been able to conceive, design, qualify, produce, and sell more than 20 billion transducers to many customers big and small.

This book provides a complete and up-to-date overview of these devices, including industrialization's biggest challenges related to reliability, packaging, and engineering. I believe that students, researchers, or engineers involved in siliconbased sensor and actuator research and development will find a wealth of useful information in this book, thanks to the proven track of record of the authors. The reader will be able to acquire a solid theoretical and practical background that will allow them to analyze the key performance aspects of these devices, critically judge a fabrication process, and conceive and design new ones for future applications. This book and its great collection of achievements represents a milestone for technicians and passionate supporters of the field. I believe it can help to stimulate the fantasy and creativity of the readers so as to generate new devices that can enhance the brilliant thinking nature of Homo Sapiens, such as we are.

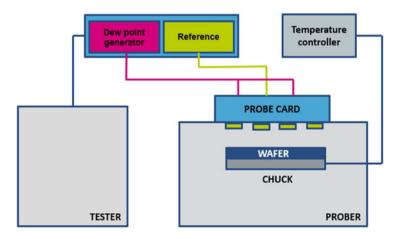

I had the opportunity and the pleasure to work with some of these highly talented people. Twenty-five years are gone, but without any doubt the challenges of these transducers' development and industrialization helped all of us stay young in spirit.

I really hope you will enjoy reading this book.

Bruno Murari ST Technical advisor and former director of Divisional Research Development Center – Cornaredo (Mi), Italy

The original version of this book was revised: The author name "Paolo Ferrari" has been changed to "Paolo Ferrarini" in Chapters 4 and 10. The correction to this book is available at https://doi.org/10.1007/978-3-030-80135-9\_28

#### Introduction

Fourteen was the number of the Third Industrial Revolution, also known as the Digital Revolution, and Fourteen is the number of the Fourth Industrial Revolution. Fourteen is the number of electrons around a nucleus composed by 14 protons and 14 neutrons. These elementary particles all together compose the beautiful atom of silicon, discovered in 1824 by the Swedish chemist Berzelius. Today, without silicon, we would not have any of the key blocks of the Digital Revolution (computers, mobile phones, the World Wide Web) that nowadays we all take for granted; we also couldn't think about the present and future waves of artificial intelligence.

In the second half of the twentieth century, the silicon transistor, invented in 1947, boosted the pace of innovation, and consequently the worldwide gross domestic product was as never seen before in the history of mankind. Silicon started to be used for its semiconductor properties in analog and digital circuits, in discrete and integrated chips, and it drove the third industrial revolution of the 1970s. The first operational amplifier, the first microcontroller, the first memory, the first analog to digital converter were all using silicon as their base material. Nowadays, the semiconductor industry has a value of about 400B\$ and it employs several million people around the world. As often happens during the progress of mankind, military applications drove the development of this strategic industry, and at the time in which this book is being written, it is still creating tense geopolitical frictions between the USA and China.

What triggered the Silicon Revolution was a simple silicon transistor, which was realized on 1" wafer, replacing the mature and reliable vacuum tube thanks to its semiconductor properties. Moreover, during the past 60 years, lithographic pitch reduction has been driving and aligning all the players of this industry along the guidelines of the well-known Moore's Law.

In parallel, in the last four decades, in a few research laboratories scattered throughout the USA and Europe and in a handful of almost-obsolete manufacturing plants, a few visionary and brave pioneers have been exploiting other physical properties of silicon (see Part I of this book). These people were the actor of what I like to call the "Secret MEMS Revolution." These researchers didn't appreciate

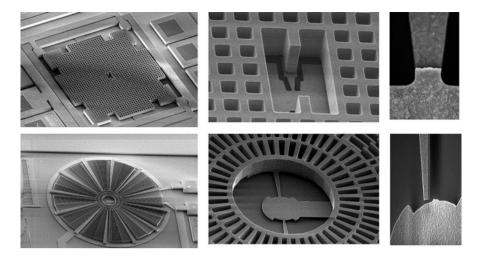

deep submicron technologies running in 12" high capital-intensive wafer fabs, they didn't fall in love with Moore's Law. Inspired by the motivating words of the Noble Prize winner R. P. Feynman's legendary talk ("There's Plenty of Room at the Bottom," 1959), the ambition of those pioneers was very simple: to manufacture low-cost energy-efficient miniaturized sensors and actuators on silicon wafers to help as many people as possible. Later, those miniaturized devices became more known as micro-electromechanical Systems (MEMS): millimeter-sized systems where not only electrons are moving, but also fluids, cantilevers, and membranes. The manufacturing processes required to realize such devices are well described in Part II of this book.

All those explorers, out of the mainstream silicon technology development roadmap and with limited support by the Semiconductor Industry Association, have gone through many theoretical and practical challenges to bring their ideas to the market. Only a few innovative companies with brave and resilient teams, who dared to challenge themselves with a clear vision that beyond Moore's Law there is another business worth world, have been successful. STMicroelectronics is among the few successful semiconductor companies thanks to its early investment in 8" MEMS manufacturing line in 2005 and to a great team whose words you can read in this book.

Tool making has always differentiated our species from all others on Earth. Four hundred thousand years ago, Homo Sapiens carved aerodynamically shaped wooden spears to kill animals to feed themselves properly and all the members of their tribe. Since the Cognitive Revolution thirty-five thousand years ago, Homo Sapiens have been able to imagine a new world and influence it. Homo Sapiens are equipped with five senses (smell, touch, sight, taste, hearing), two couples of actuators (arms and legs), and, most importantly, the best brain in nature able to integrate the signals gathered by sensors and then moving the innate actuators. Over time, our ancestors realized that they needed more precise sensors and more efficient actuators to better master the world around them, and thus they started to use their brains to conceive, develop, and manufacture sensors and actuators to augment the limited capabilities of their body.

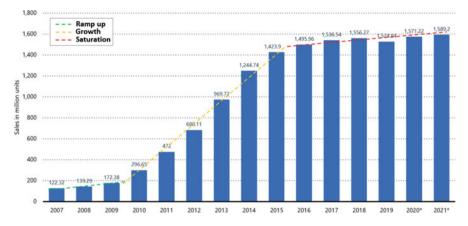

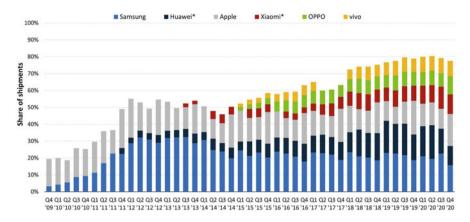

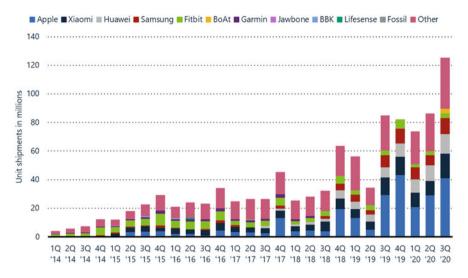

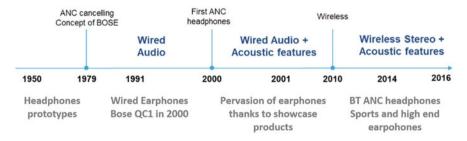

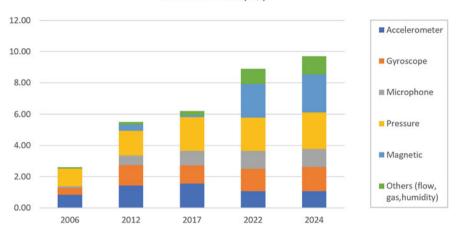

Time has been the first variable that mankind has been interested to measure. In the ancient world, time measurement was important for many different purposes: from knowing the exact hour during which to hold religious rites to the time slot allocated to the defense lawyers in ancient Rome's courts and then to the paid time slot allocated to prostitutes' customers in many brothels all over the world. The Egyptians used large obelisks to track the movements of the sun and to measure the passing of time; they also developed water clocks, later used by both the Greeks (a.k.a. clepsydrae) and the Chinese. With the exception of a few other instruments (like the compass invented in China, used for divination first and later for navigational orienteering around 1050 AD), we will need to wait for the Scientific Revolution of the seventeenth century, whose foundational Galilean scientific method required the development of many more instruments to challenge the dogmatism of the pre-modern era. Barometers, accelerometers, thermometers, and other bulky and expensive sensors were all invented starting from the seventeenth century. Their widespread use has been limited by their high price, also linked to the amount of raw material used to realize those sensors. Only in the last 25 years, a strong boost to the massive adoption of sensors came from the automotive market (airbags, ...) and, later, from the consumer (Nintendo Wii Console) and personal electronics market (computers, mobile phones, watches, etc.), thanks to the sensors' increased reliability, optimized power consumption, miniaturized size, and, most importantly, more affordable cost (see Parts III, VI, and VII of this book).

Almost eight thousand years ago, Homo Sapiens started using cows for tilling the land for more efficient farming, and later began riding horses to move more quickly from one point to another. Much later, in the eighteenth and the nineteenth centuries, J. Watt's steam and the electromagnetic fields of T. Edison and N. Tesla, respectively, ignited the First and the Second Industrial Revolution in the Old Continent. All these innovations were meant to offset the natural limit of our legs and arms and sustain the economic and demographic growth of mankind thanks to an increase in productivity.

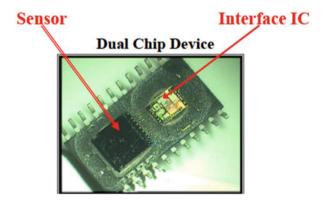

Today, these sensors and actuators surround us, and we interact with them daily.

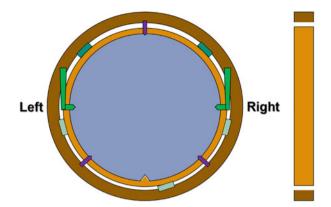

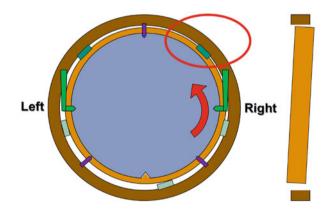

We can find several types of sensors in cars, smartphones, pacemakers, drones, smart speakers, washing machines, and many other equipment. Their uses are very widespread. They can help us interact in an easier way with complex digital devices or they can make our cars greener, smarter, and safer. These sensors are all made in silicon, and a detailed description of these sensors can be found in Part III of this book. The sensors that we find all around us are much smaller than their macroscopic counterpart of the past. As an example, let's consider the example of the gyroscope, a sensor able to measure angular rates of the system where it is mounted. We can find it in all medium and higher-end cars and, since 2010, also in medium-high-end smartphones of several brands. The silicon gyroscope occupies a volume of few cubic millimeters, it has a weight of few milligrams, and it is much smaller than the Foucault's pendulum (year 1851) used to measure the Earth's rotation, thanks to a suspended 28-kilogram brass-coated lead bob attached to a 67-meter long wire!

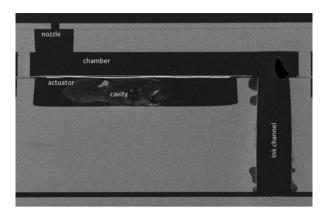

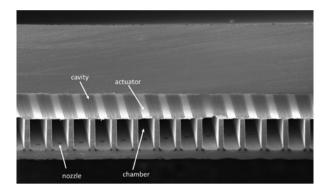

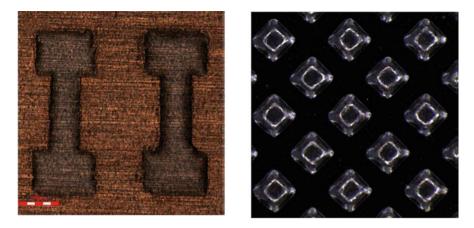

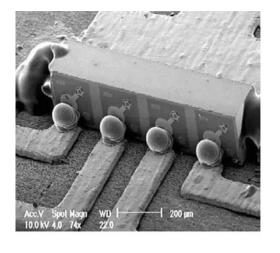

Today, we are used to printing many documents easily, remaining in the comfort of our homes and offices. These printers are much smaller and cheaper than the original press machine of Gutenberg (year 1453). That machine was about three cubic meters with a weight about 200 kg ! Today, ink-jet printers are much smaller thanks to a micromachined thermal or piezoelectric actuator able to eject accurately and quickly picoliter-size droplets of ink. (see Part IV).

This field of sensors and actuators is so diverse and multidisciplinary that it is difficult for any single person to follow up all its activity. Thus, I asked my colleagues, expert in sensors and actuators, to join me in writing all the relevant and specific topics that concern this vast field. The result is this new book on silicon sensors and actuators.

This book is intended for practicing engineers, scientists, and advanced graduate students who seek a broader understanding on important subjects regarding the micro-sensor and micro-actuators field. The topics in this book are arranged in logical order in the form of eight parts. Besides this introduction and a part related to the silicon properties, five other important areas are covered: micromachining technology, device modeling and required circuitry, assembly and calibration techniques, reliability tests, and present and future device applications.

The first part provides a good overview of the silicon properties. The second part describes the different micromachining technologies and the varied materials used to realize sensors and actuators. Parts III and IV describe in detail the theory and working mode of the transducer element of different type of sensors and actuators, while Part V addresses the challenges of the related electronic circuitry. Part VI focuses on the importance of assembly and calibration on the performances and high-volume manufacturability of MEMS, while the seventh part addresses reliability, a very important, but often-forgotten topic. In the last part, we take a quick glance at potential future applications of sensors and actuators.

In this book, we purposely decided not to address the topic of CMOS image sensors, since they require 12" factories and, like microprocessors and memory chips, follow more closely the Moore's law.

Most of the 80 writers of this book are coming from STMicroelectronics. We also received valuable contributions from colleagues at Politecnico di Milano, and from uSound and Polight, two European startups with which we cooperate. The reader of this book will have the pleasure to see all the theoretical and industrial challenges explained in detail by a very talented team which has been able to scale up the production of several MEMS products, from few low-yield prototypes to high-volume high-yield production scale. Together, this team acquired in 25 years thousands of patents and thousands of years of experience in MEMS, through successes and, most importantly, through failures. This is the team behind the twenty billion units of silicon sensors and actuators deployed in the market in the last two decades. This team has been able to grow such business thanks to strong teamwork, high talent, and obviously some luck. "Audaces Fortuna Iuvat," old Romans were saying.

Each part of this book is self-contained, and readers interested in a subject will be able to find the needed information easily. It is my sincere wish that the combination of the variety and depth of the topics and industrial experience shared in this book will make it a valuable reference as well as a useful teaching text.

Benedetto Vigna

### Contents

| Par | t I Silicon as Sensor Material                                                                                         |     |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|

| 1   | Silicon Properties and Crystal Growth<br>Flavio Francesco Villa                                                        | 3   |

| Par | t II MEMS Processes                                                                                                    |     |

| 2   | <b>Epitaxy</b><br>Roberto Campedelli and Igor Varisco                                                                  | 37  |

| 3   | Thin Film Deposition                                                                                                   | 75  |

| 4   | Thin Films Characterization and Metrology<br>Paolo Ferrarini, Luca Lamagna, and Francesco Daniele Revello              | 105 |

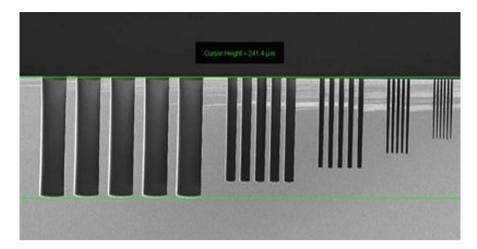

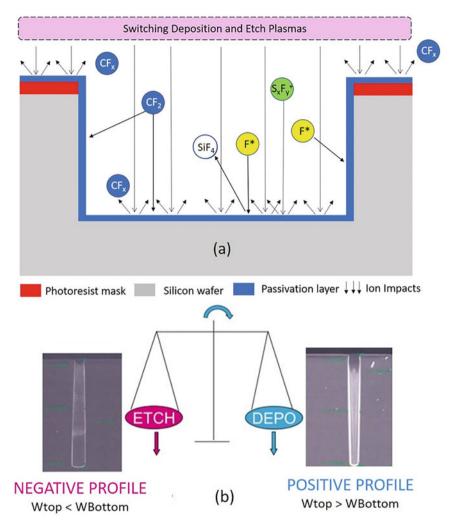

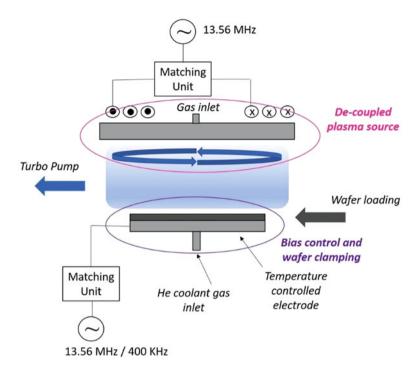

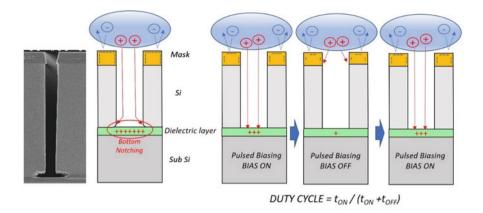

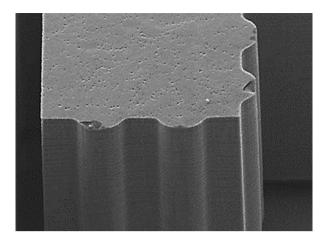

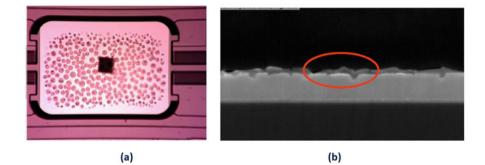

| 5   | <b>Deep Silicon Etch</b><br>Anna Alessandri, Filippo D'Ercoli, Pietro Petruzza,<br>and Alessandra Sciutti              | 133 |

| 6   | <b>Optical Lithography</b><br>Aldo Bortolotti, Nadia Galimberti, Marco Salina, Martina Scolari,<br>and Lorenzo Tentori | 169 |

| 7   | HF Release<br>Maria Carolina Turi, Ilaria Gelmi, and Raffaella Pezzuto                                                 | 203 |

| 8   | Galvanic Growth<br>Giuseppe Visalli, Riccardo Gianola, and Linda Montagna                                              | 231 |

| 9   | Wet Etching and Cleaning<br>Gianluca Longoni, Davide Assanelli, and Cinzia De Marco                                    | 259 |

| Co | nte | nts |

|----|-----|-----|

|    |     |     |

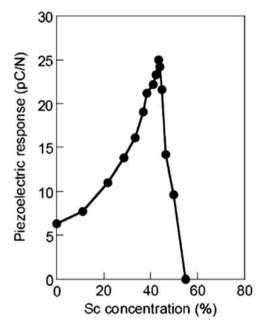

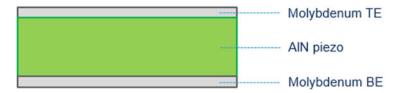

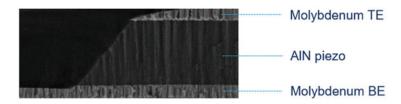

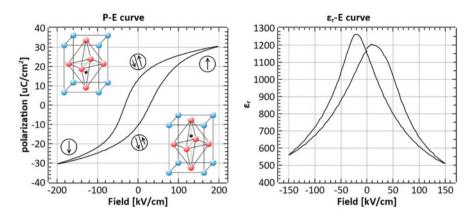

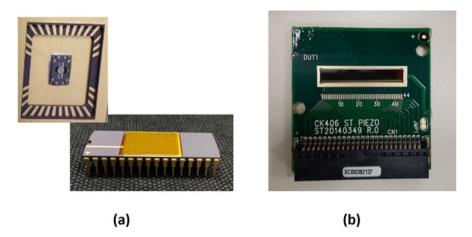

| 10  | <b>Piezoelectric Materials for MEMS</b><br>Andrea Picco, Paolo Ferrarini, Claudia Pedrini, Angela Cimmino,<br>Lorenzo Vinciguerra, Michele Vimercati, Alberto Barulli,<br>and Carla Maria Lazzari | 293 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

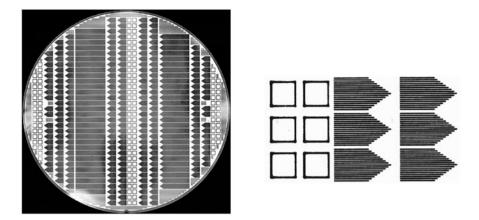

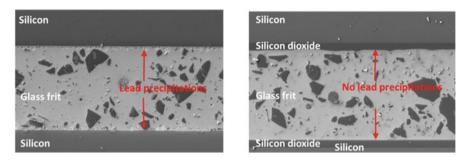

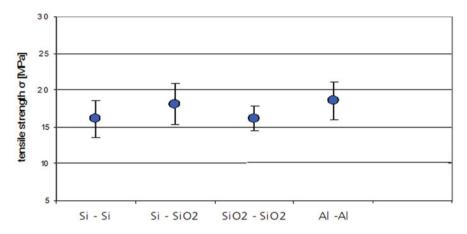

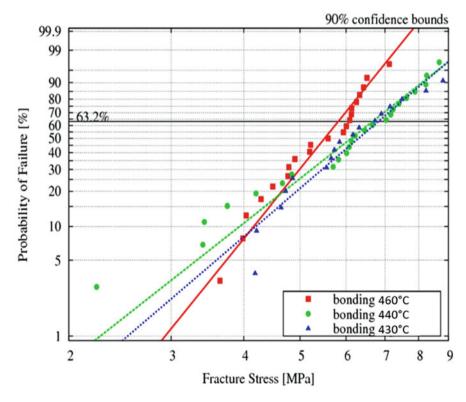

| 11  | Wafer-to-Wafer Bonding<br>Laura Oggioni, Matteo Garavaglia, and Luca Seghizzi                                                                                                                     | 345 |

| Par | t III MEMS Sensors                                                                                                                                                                                |     |

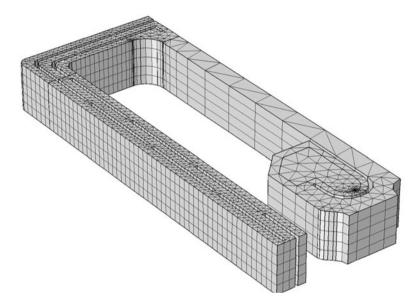

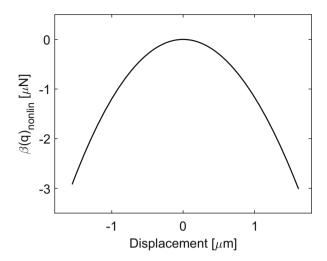

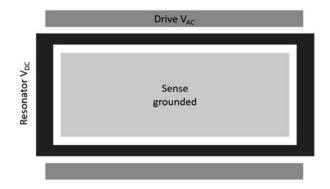

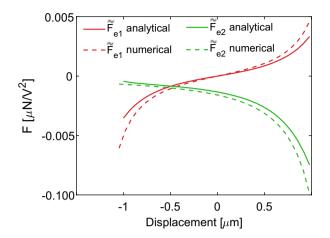

| 12  | Linear and Nonlinear Mechanics in MEMS<br>Claudia Comi, Alberto Corigliano, Attilio Frangi, and Valentina Zega                                                                                    | 389 |

| 13  | Inertial Sensors                                                                                                                                                                                  | 439 |

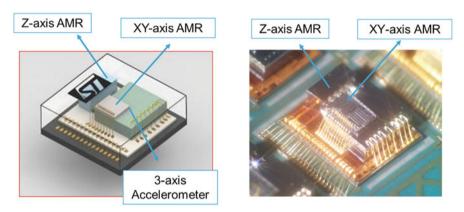

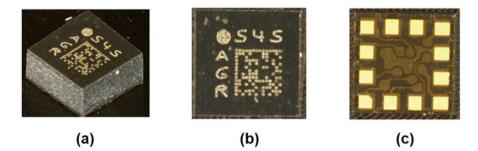

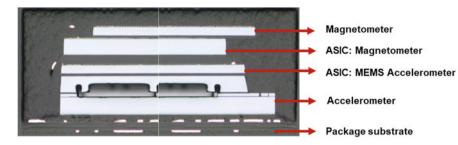

| 14  | Magnetometers<br>Dario Paci, Anna Cantoni, and Giorgio Allegato                                                                                                                                   | 477 |

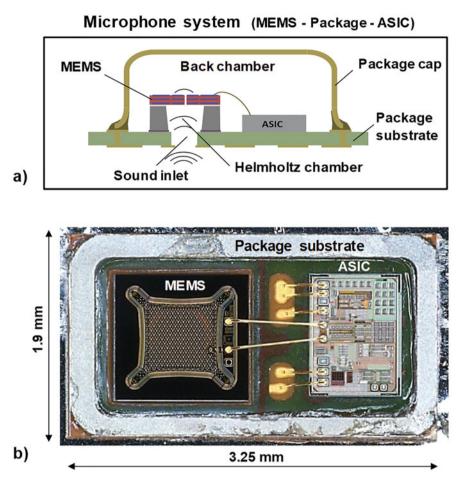

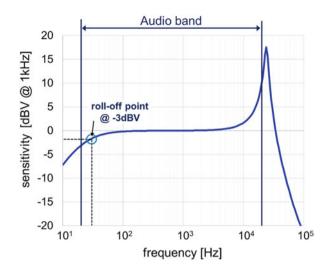

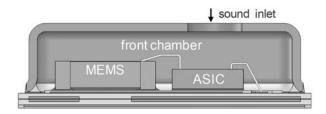

| 15  | Microphones                                                                                                                                                                                       | 503 |

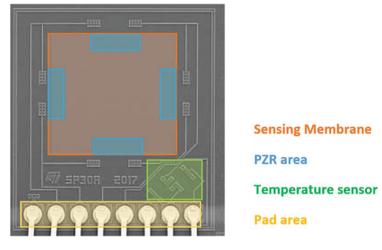

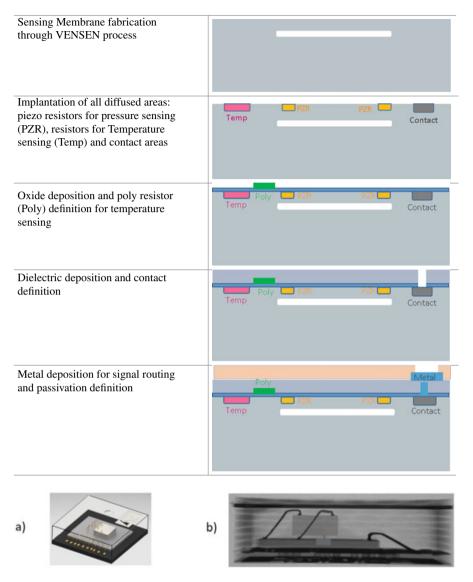

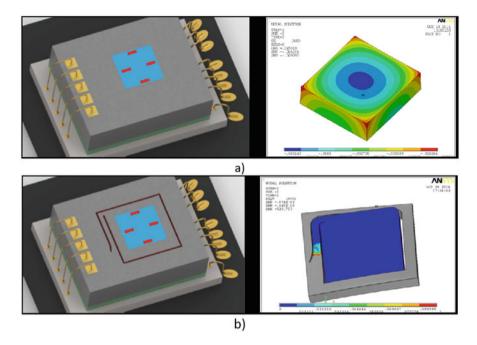

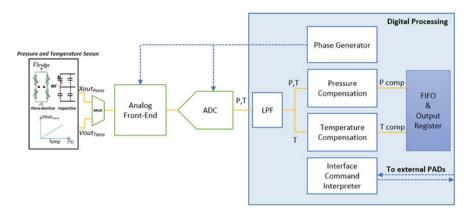

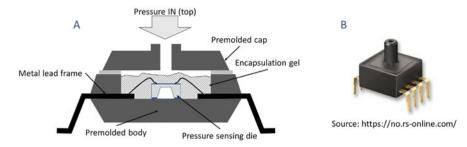

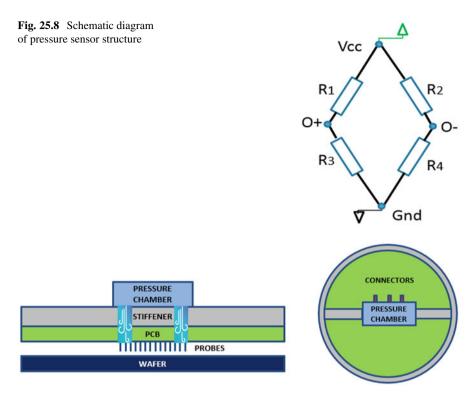

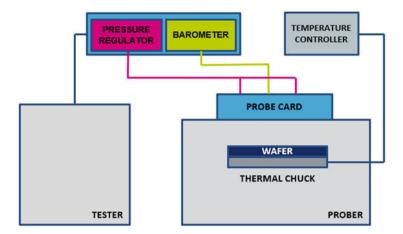

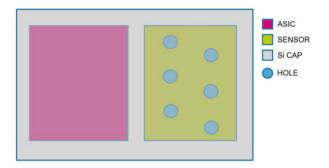

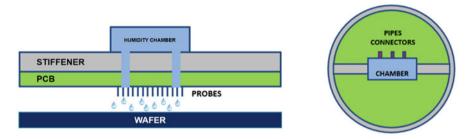

| 16  | Pressure Sensors<br>Enri Duqi, Giorgio Allegato, and Mikel Azpeitia                                                                                                                               | 523 |

| 17  | Environmental Sensors<br>Giuseppe Bruno and Michele Vaiana                                                                                                                                        | 543 |

| Par | t IV MEMS Actuators                                                                                                                                                                               |     |

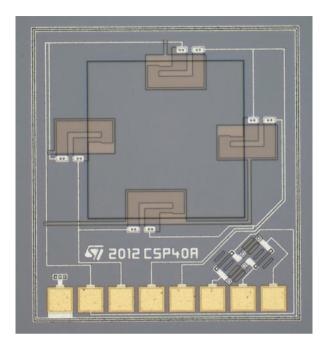

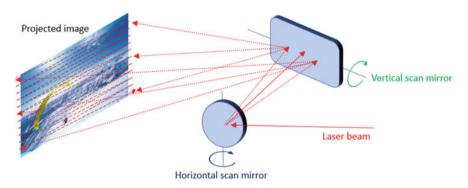

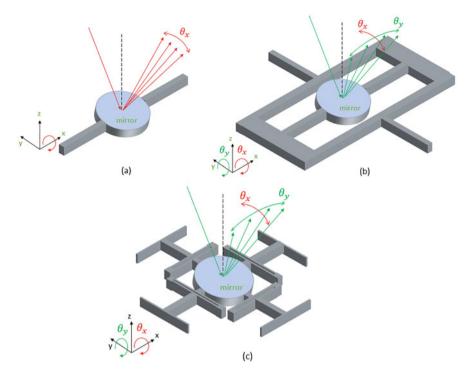

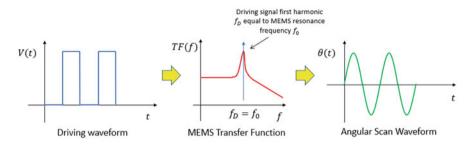

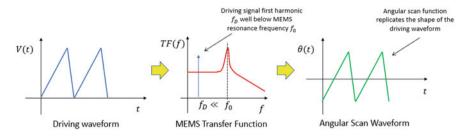

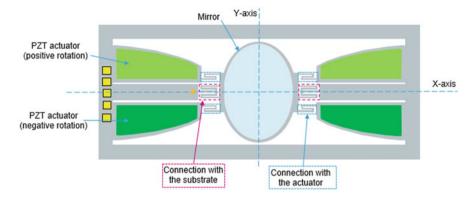

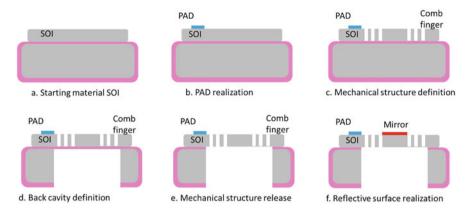

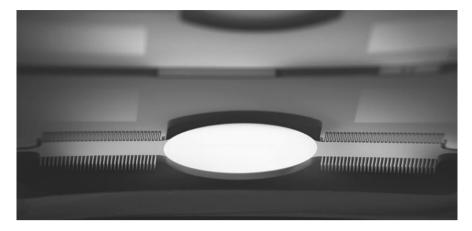

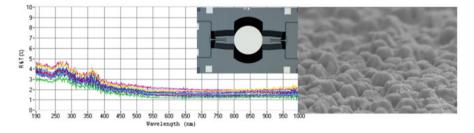

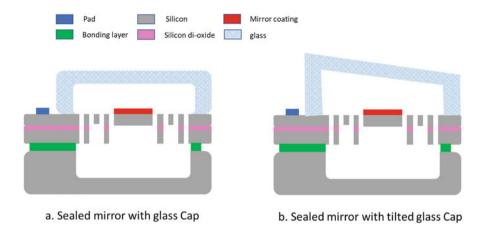

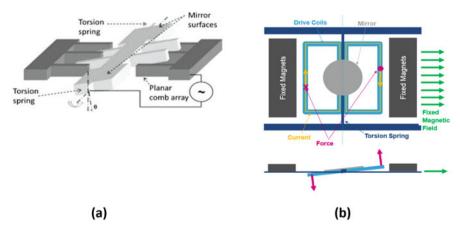

| 18  | Micromirrors<br>Roberto Carminati and Sonia Costantini                                                                                                                                            | 565 |

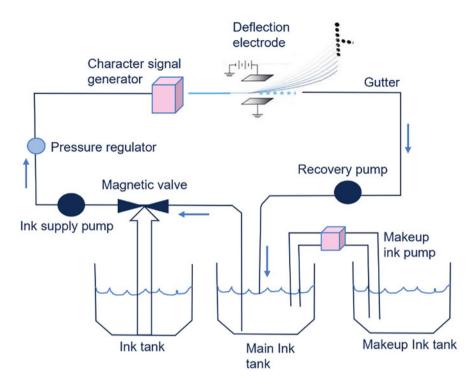

| 19  | Inkjet Printhead<br>Domenico Giusti, Sonia Costantini, Stefano Brovelli,<br>and Marco Ferrera                                                                                                     | 603 |

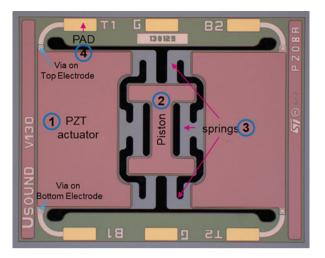

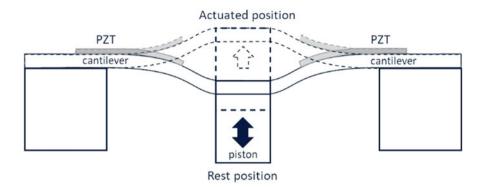

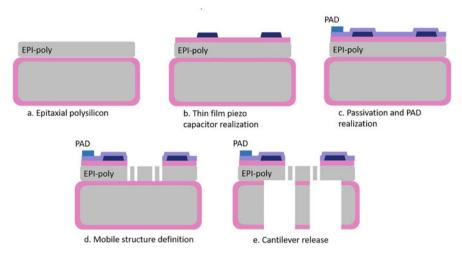

| 20  | Micro Speakers<br>Andrea Rusconi, Sonia Costantini, and Carlo Prelini                                                                                                                             | 651 |

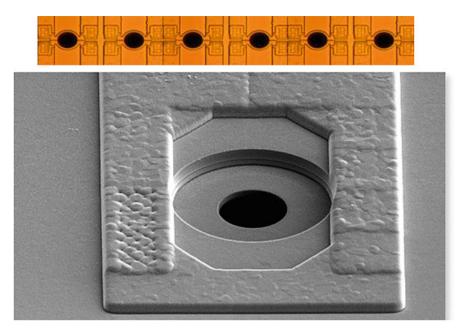

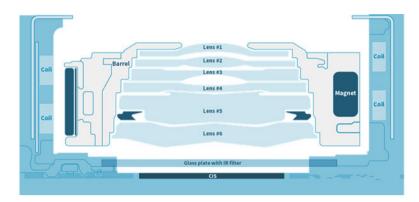

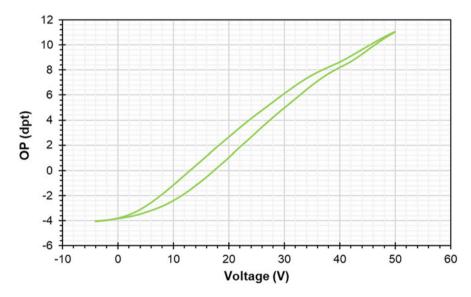

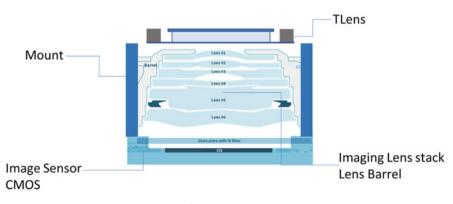

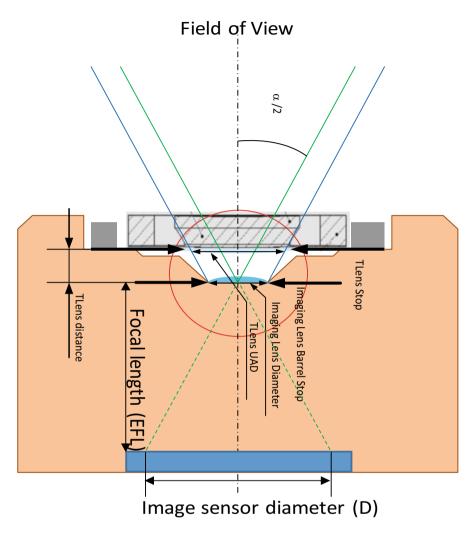

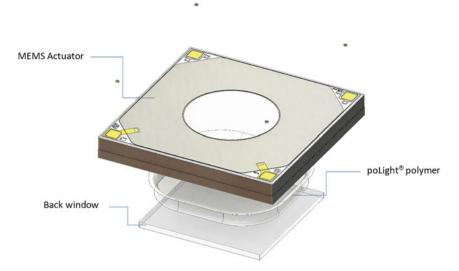

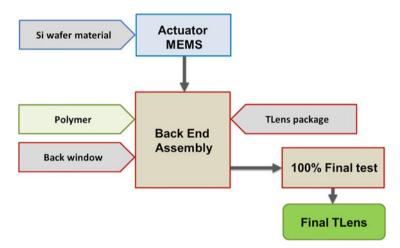

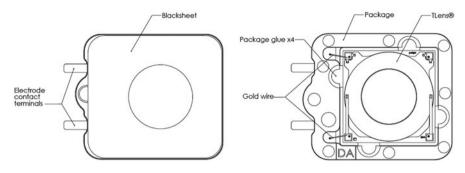

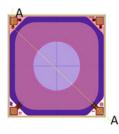

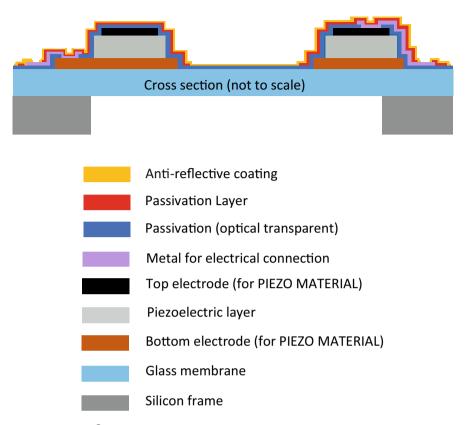

| 21  | <b>Tunable Lenses for Autofocus</b><br>Sonia Costantini, Irene Martini, Dario Paci, Adriana Cozma,<br>Gjermund Kittilsland, and Pierre Craen                                                      | 677 |

| Par | t V Electronic Interfaces                                                                                                                                                                         |     |

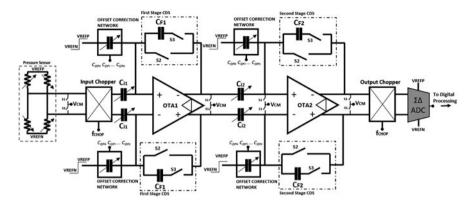

| 22  | Electronic Sensors Front-End<br>Tommaso Ungaretti, Sergio Pernici, Daniele De Pascalis,                                                                                                           | 711 |

Deyou Fang, Mario Maiore, and Giovanni Pelligra

| 23 | Electronic Interfaces for Actuators            |  |  |  |  |

|----|------------------------------------------------|--|--|--|--|

|    | Andrea Barbieri, Luca Molinari, Mauro Pasetti, |  |  |  |  |

|    | and Marco Zamprogno                            |  |  |  |  |

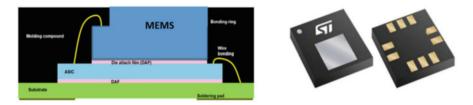

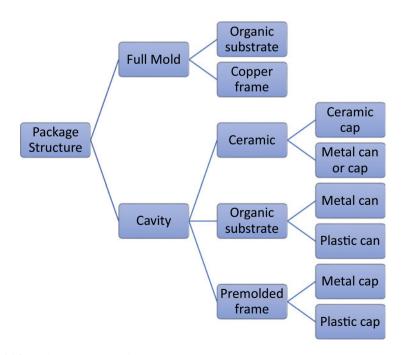

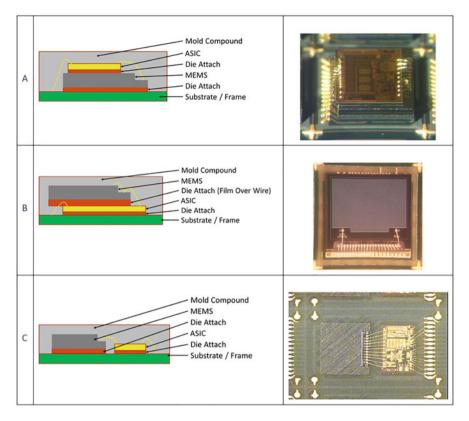

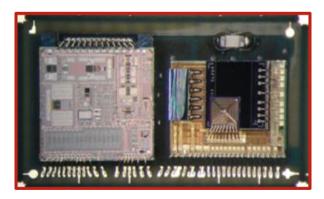

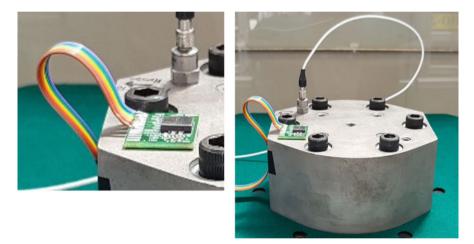

#### Part VI MEMS Back-end

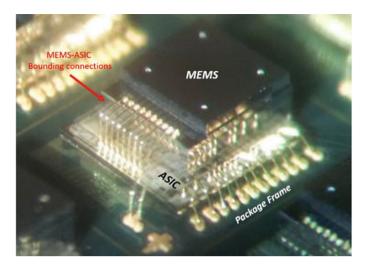

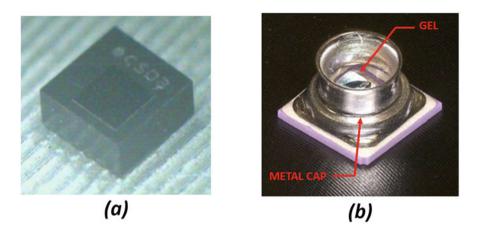

| 24 | MEMS Package Design and Technology | 833 |

|----|------------------------------------|-----|

|    | Marco Del Sarto                    |     |

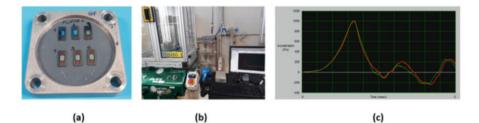

| 25 | MEMS Testing: Sensors Testing and Calibration Impact             |     |

|----|------------------------------------------------------------------|-----|

|    | on Product Performances                                          | 861 |

|    | Michele Tronconi, Paolo Aranzulla, Giacomo Calcaterra,           |     |

|    | Matteo Catalano, Paolo Cerri, Fabiano Frigoli, Valeria Montuori, |     |

|    | Dario Premi, Marco Rossi, and Giancarlo Spoldi                   |     |

#### Part VII Reliability

| <b>26</b> | Reliability                                               | 899 |

|-----------|-----------------------------------------------------------|-----|

|           | Alessandro Balzelli Ludovico, Fabio Banfi, Stefano Losa,  |     |

|           | Francesco Petralia, Ernesto Fabrizio Speroni, Aldo Ghisi, |     |

|           | and Stefano Mariani                                       |     |

|           |                                                           |     |

#### Part VIII The Future of Sensor and Actuators

| 27  | <b>MEMS: From a Bright Past Towards a Shining Future</b><br>Alessandro Morcelli, Simone Ferri, and Anton Hofmeister | 945 |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

| Cor | rrection to: Silicon Sensors and Actuators                                                                          | C1  |

| Ind | ex                                                                                                                  | 979 |

## Part I Silicon as Sensor Material

#### **Chapter 1 Silicon Properties and Crystal Growth**

Flavio Francesco Villa

#### 1.1 Properties of Silicon

Silicon is an abundant element found in the Earth's crust in various compounds. Silica, or silicon dioxide, is the most common starting raw material for purified silicon for semiconductor and sensor applications, and the Siemens process is the most used in semiconductor-grade silicon production.

The advent of solid-state electronics dates from the invention of the transistor by Bardeen, Brattain, and Shockley [1]. During the early 1950s, the electronic components were made from germanium, a material whose melting point is lower in respect to the silicon one. This characteristic allows to grow the germanium ingot with greater ease in respect to the silicon one; however, its narrow bandgap (0.66 eV) limits the operation of germanium-based devices to temperatures of roughly 90 °C due to the major leakage currents observed at higher temperatures. On the contrary, silicon electronic devices are capable of operating at up to 200 °C, thanks to wider bandgap of silicon (1.12 eV). But there is a more serious problem than the narrow bandgap: germanium does not readily provide a stable passivation layer on the surface. For example, germanium dioxide (GeO<sub>2</sub>) is water soluble, dissociates at approximately 800 °C, and is a poor electrical insulator. Silicon, unlike germanium, has a remarkable synergy with its oxide, silicon dioxide  $(SiO_2)$ . By simply heating silicon in an oxygen atmosphere, a high dielectric strength and electrically insulating silicon dioxide is inexpensively formed. This oxide layer is chemically and mechanically very stable, effectively passivates the surface states of underlying silicon, form an effective diffusion barrier for the commonly used dopant species, and can be easily preferentially etched from the silicon, and vice

F. F. Villa (🖂)

B. Vigna et al. (eds.), *Silicon Sensors and Actuators*, https://doi.org/10.1007/978-3-030-80135-9\_1

ST Microelectronics, Analog MEMS and Sensors Group, MEMS Technology and Design R&D, Agrate Brianza, Monza Brianza, Italy e-mail: flavio.villa@st.com

<sup>©</sup> Springer Nature Switzerland AG 2022

versa, with high selectivity. Other advantages of silicon are that it is completely nontoxic, and that silica (SiO<sub>2</sub>), the raw material from which silicon is obtained, constitute together with oxygen, about 75% of the Earth's crust. This implies that the silica is available in plentiful supply to the semiconductor industry. Moreover, electronic grade silicon can be obtained at less then one-tenth the cost of germanium. All these advantages have caused silicon to almost replace germanium completely in the semiconductor industry.

Silicon is one of the most studied elements in the periodic table and many of its physical properties have been measured. A more comprehensive treatise on basic silicon properties can be found, for instance, in a handbook edited by Hull [2] or in Landolt-Börnstein [3, 4].

#### 1.1.1 Crystal Planes and Orientation

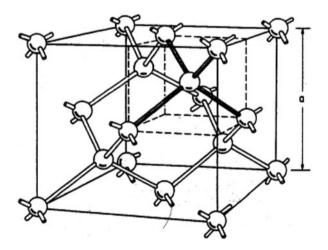

Silicon crystallizes into a diamond cubic crystal structure (Fig. 1.1) in which the atoms are covalently bonded. The unit cell contains eight atoms, and the atoms follow a face centered cubic (fcc) Bravais lattice. The unit cell length (**as** in Fig. 1.1) at room temperature is 0.5431 nm. This value is one of the most precisely known among elements, since silicon crystal can be grown almost perfectly, and the lattice parameter can be measured precisely [5] with an uncertainty of about  $3-6 \cdot 10^{-8}$ .

Fig. 1.1 The silicon lattice unit cell

#### 1.1.1.1 Miller Index System

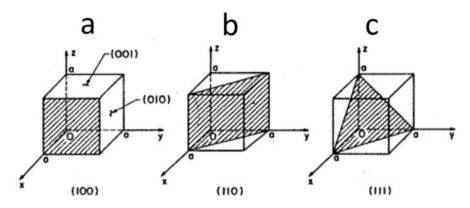

A convenient way to describe atomic planes and directions in the crystal lattice is to use Miller indexes. When the lattice axes are orthogonal and the lattice parameters in all directions x, y, z are identical as for the silicon lattice, the Miller notation is easy to use. In fact, let us consider, as in Fig. 1.2, an orthogonal coordinate system, with axes x, y, and z, with equal unit vector size, **a**. The plane intercepts, Fig. 1.2a, the x axis at a distance **a** from the origin and is parallel to the y- and z-axes. The intercept points in each axis are thus  $\mathbf{a}, \infty, \infty$ . Since this is an uncomfortable notation, Miller indexes (*hkl*) are constructed in such a way that reciprocals of the intersect points are taken. Thus, in the case of Fig. 1.2a, the Miller indexes (*hkl*) are  $\mathbf{a}/\mathbf{a}, \mathbf{a}/\infty$ , respectively, is (110). A plane, Fig. 1.2c, intersecting axis x at **a**, axis y at **a** and z axis at **a** axis at **a** is (111).

Some other conventions are also followed, which are reported below.

- 1. (hkl) identifies a plan.

- 2. {*hkl*} identifies all planes in the same family, and in a cubic lattice it means that {khl} includes all eight identical plans.

- 3. [*hkl*] identifies a direction. The direction is perpendicular to the plane (*hkl*).

- 4. *<hkl>* identifies a family of directions, and again in cubic lattice it includes all identical directions.

Those who would like to have a comprehensive picture of Miller indexes should consult, for instance, [6].

Fig. 1.2 Miller indexes

#### 1.1.2 Electronic and Mechanical Characteristics

Semiconductors, such as silicon, are solid materials that have electrical conductivities in between those of conductors and those of insulators. The physical reason causing a material to behave as a conductor, semiconductor, or insulator lies in the availability, or lack thereof, of free current carriers in the material. Semiconductors are characterized by the narrow bandgap between the valence bands, occupied by electrons, and the conduction band, in which electrons move freely according to applied electrical fields. Intrinsic (i.e., pure) semiconductors act as insulators at room temperatures, but their behavior changes dramatically with temperature, and, more to the point, with small impurities present in the crystal. Very small amounts of electrically active impurities can totally alter the electrical properties of semiconductors such as silicon. This is because the electrically active impurities either easily donate valence electrons (donors) or accept them, creating holes (acceptors). These electrons or holes are free (i.e., not bound to individual atoms). Their movement due to applied electrical fields carries electrical currents, giving rise to the term charge carriers used to denote them. The electrical properties of semiconductor materials such as single-crystal silicon is thus defined by the impurity concentrations present in the silicon lattice. Impurities are introduced into the starting materials during crystal growth and modified during device processing by additional doping of the silicon material with electrically active impurities. In intentional doping of silicon, impurity atoms from group III (acceptors) and group V (donors) are used. Techniques used include both very traditional methods, such as deep diffusions of dopants, which have been abandoned in mainstream semiconductor processes, and current standard techniques such as ion implantation and epitaxial deposition. Silicon is a semiconductor whose resistivity can be adjusted by doping from sub-m $\Omega$  cm to several k $\Omega$  cm; it is quite inert in a normal environment, hard, transparent in an infrared region, and elastic at room temperature with no plastic deformation and with high fracture strength. However, silicon wafers do break-sometimes without apparent cause; silicon wafers and parts of wafers may 'also easily chip'. In fact, defects (scratches, dents, mechanical damage, etc.) on the surface or periphery of the silicon wafer can cause premature cracking under stress along cleavage planes, because of the notch effect. Silicon wafers having a rough surface or residual damage left on the wafer surface (cut wafer, lapped wafer, or ground wafer without stress relief) are more prone to break compared with polished wafers. The ideal, "strong" wafer is double side polished, and the wafer edge is polished and round, also. The potential of silicon as a micromechanical material was widely described by Kurt E. Petersen [7]. This review shows the advantages of employing silicon as a mechanical material, the relevant mechanical characteristics of silicon, and the processing techniques which are specific to micromechanical structures. The basis of micromechanics is that silicon, in conjunction with its conventional role as an electronic material, and taking advantage of an already advanced microfabrication technology, can also be exploited as a high-precision, high-strength, high reliability mechanical material, especially applicable wherever

| Table 1.1  | Silicon physical |

|------------|------------------|

| properties |                  |

| 14                                        |

|-------------------------------------------|

| Diamond                                   |

| 0.5431 nm                                 |

| $5 \times 10^{22}$ atoms.Cm <sup>-3</sup> |

| 1687 K                                    |

| 3538 K                                    |

| 2.329 g.cm <sup>-3</sup> at 298 K         |

| $2.57 \text{ g.cm}^{-3}$                  |

| 19.79 J.Mol <sup>-1</sup> K <sup>-1</sup> |

| 50.21 kJ/mol                              |

| 383 kJ/Mol                                |

| 19.789 J/(Mol·K)                          |

| $8433 \text{ m.s}^{-1}$                   |

| $1.02 \times 10^{-8} \text{ KPa}^{-1}$    |

| $\sim 3.54 \lambda = 1.1 \ \mu m$         |

| $\sim 3.48 \ \lambda = 2 \ \mu m$         |

| At room temperature                       |

|                                           |

Table 1.2

Silicon mechanical and thermal properties

|                                  | Si   | С    | SiC  | SiN  | Fe   | W    | Steel | Мо   | AI   |

|----------------------------------|------|------|------|------|------|------|-------|------|------|

| Yield Strength<br>(GPa)          | 7    | 53   | 21   | 14   | 12.6 | 4    | 2.1   | 2.1  | 0.17 |

| Knoop Hardness<br>(Kg/mm2)       | 850  | 7000 | 2480 | 3486 | 400  | 485  | 660   | 275  | 130  |

| Young Modulus<br>(100 GPa)       | 1.9  | 10.3 | 7    | 3.8  | 1.96 | 4.1  | 2     | 3.43 | 0.7  |

| Density (g/cm3)                  | 2.3  | 3.5  | 3.2  | 3.1  | 7.8  | 19.3 | 7.9   | 10.3 | 2.7  |

| Thermal Conductivity<br>(W/cm K) | 1.57 | 20   | 3.5  | 0.19 | 0.8  | 1.78 | 0.32  | 1.38 | 2.36 |

| Thermal Expansion<br>(ppm/K)     | 2.33 | 1    | 3.3  | 0.8  | 12   | 4.5  | 17.3  | 5    | 25   |

miniaturized mechanical devices and components must be integrated or interfaced with electronics. Tables 1.1 and 1.2 list some basic properties of silicon. Some of the parameters depend on doping level as well as temperature.

Silicon is almost an ideal structural material: It has about the same Young's modulus as steel, but is as light as aluminum, has low thermal expansion (Its thermal expansion coefficient is about eight times smaller than that of steel and is more than ten times smaller than that of aluminum), a high speed of sound and very low intrinsic mechanical losses. Silicon shows virtually no mechanical hysteresis. It is thus an ideal candidate material for MEMS, Sensors, and Actuators.

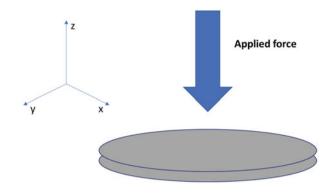

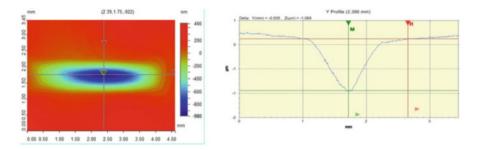

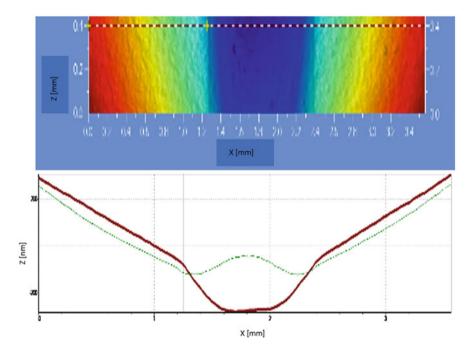

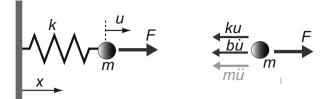

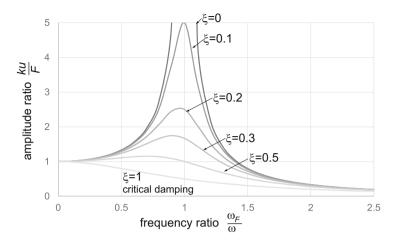

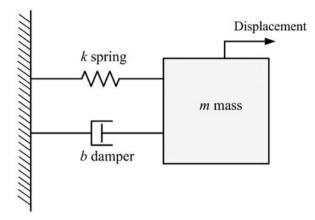

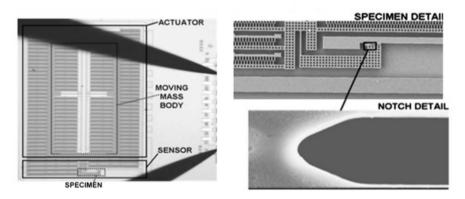

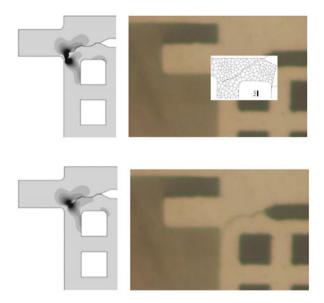

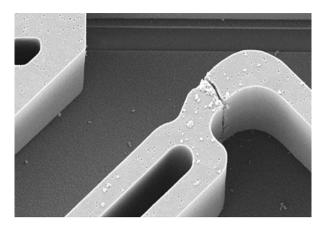

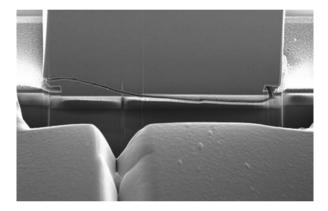

The performance of Micro Electronic and Mechanical Systems (MEMS) strongly depends on the mechanical properties of materials used. The evaluation of the

mechanical properties of MEMS materials is indispensable for designing MEMS devices. Accurate values of mechanical properties (elastic properties, internal stress, strength, fatigue) are necessary for obtaining the optimum performances. For an example, elastic properties are necessary in prediction of the amount of deflection from an applied force and material strength sets device operational limits. Also, in view of reliability and lifetime requirements, mechanical characterization of MEMS materials becomes increasingly important. Reliability, accuracy, and repeatability of evaluation methods also became an issue.

#### 1.1.2.1 Elastic Properties

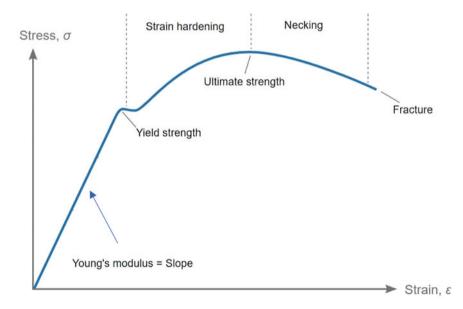

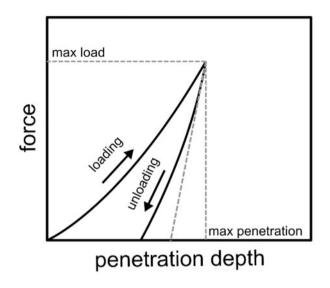

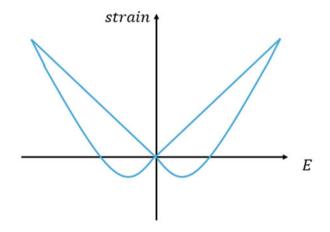

Elastic properties are directly related to the device performance. Young's modulus and Poisson's ratio are basic elastic properties that govern the mechanical behavior. Since two independent mechanical properties are necessary for full definition of mechanical properties of MEMS materials, their properties can be accurately determined by measuring Young's modulus and Poisson's ratio. Young's modulus (E) is a measure of a material stiffness. It is the slope of the linear part of stress-strain ( $\varepsilon$ - $\sigma$ ) curve of a material (Fig. 1.3). Poisson's ratio is a measure of lateral expansion or contraction of a material when subjected to an axial stress within the elastic region. Young's modulus, Poisson's ratio, and shear modulus are isotropic on silicon (111), whereas the variations on silicon (100) and (110) are quite significant.

Fig. 1.3 Stress-Strain curve in ductile materials

In engineering and materials science, a stress–strain curve [8] for a material gives the relationship between stress  $\sigma$  (a force applied over area-for uniaxial stress) and strain  $\varepsilon$  (a measure of the deformation of the material). It is obtained by gradually applying load to a test coupon and measuring the deformation, from which the stress and strain can be determined. These curves reveal many of the properties of a material, such as the Young's modulus, the yield strength, and the ultimate tensile strength. The first stage is the linear elastic region. The stress is proportional to the strain, that is, obeys the general Hooke's law ( $\sigma = \varepsilon$  E), and the slope is Young's modulus or modulus of elasticity E. In this region, the material undergoes only elastic deformation. The end of the stage is the initiation point of plastic deformation. The stress component of this point is defined as yield strength. The yield strength or yield stress is a material property and is the stress corresponding to the yield point at which the material begins to deform plastically. The yield strength is often used to determine the maximum allowable load in a mechanical component, since it represents the upper limit to forces that can be applied without producing permanent deformation; for Silicon (annealed) the yield strength range is about 5000-9000 MPa [9].

#### 1.1.2.2 Strength

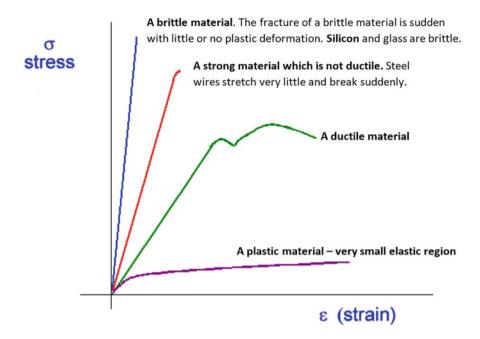

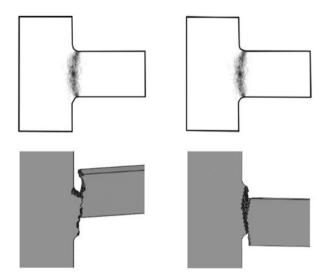

The strength of a material determines how much force can be applied to a MEMS device. It needs to be evaluated to assure reliability of MEMS devices. Strength depends on the geometry, loading conditions, as well as on material properties. As the useful measure for brittle materials, the fracture strength is defined as the normal stress at the beginning of fracture. The flexural strength is a measure of the ultimate strength of a specified beam in bending and it is related to specimen's size and shape. For inelastic materials, the yield strength is defined as a specific limiting deviation from initial linearity. Silicon is a hard, brittle material, and at room temperature under stress, silicon single crystal elongates elastically until fracture stress appears without significant plastic deformation (Fig. 1.4). It is well known that while the amorphous and polycrystalline brittle solids behave isotropically, brittle single crystals manifest mostly anisotropic behavior. For the silicon single crystal, the fracture anisotropy has been reported [10] with reference to the low index plane, such as {001}, {110}, and {111}; silicon has two principal cleavage planes:  $\{111\}$  planes, usually the easy cleavage planes, and  $\{110\}$  planes [11-13]. On the contrary Polysilicon, an aggregation of pure silicon crystals with random orientations deposited on the top of silicon substrates, is even stronger than single silicon crystals; Polysilicon is the most frequently used MEMS material.

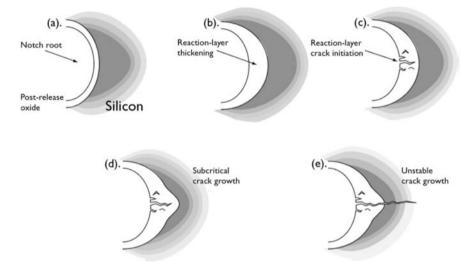

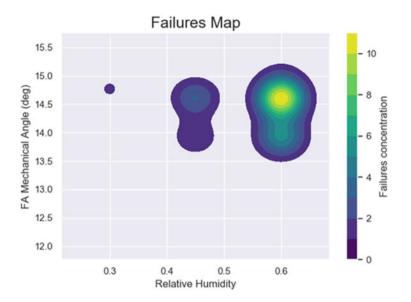

#### 1.1.2.3 Fatigue

MEMS devices are often exposed to cyclic or constant stress for a long-time during operation. Such operational conditions may induce fatigue. Fatigue may be observed

Fig. 1.4 Materials behaviors in stress-strain curve

as change in elastic constants and plastic deformation leading to sensitivity changes and offset drift in MEMS devices. It may also be observed as the strength decreases that may lead to fracture and consequentially failure of the device. Fatigue behavior of a MEMS device also depends on its size, surface effects, effect of the environment such as humidity and temperature, resonant frequencies, etc. To realize a highly reliable MEMS device, a detailed analysis of the fatigue behavior must be performed using accelerated life test method as well as life prediction method.

#### **1.2 Starting Materials**

The preparation of silicon single-crystal substrates, as it well known, is the first step in the long and complex process of device and circuits fabrication. Silicon is the second most abundant element, after oxygen, in the earth's crust, in the form of silica (SiO<sub>2</sub>) and silicates and is readily extracted from silica-rich sands. In nature, it typically contains large amounts of impurities and so the initial stages of the manufacturing process are concerned with reduction and purification of the silica sand to produce Metallurgical Grade polysilicon (MG), typically greater than 98% pure silicon. This is then further refined to produce Electronic semiconductor Grade polysilicon (EG), which can be used as basic material for crystal growth to produce single crystal silicon substrate suitable for device and circuits manufacturing.

#### 1.2.1 Metallurgical-Grade Silicon

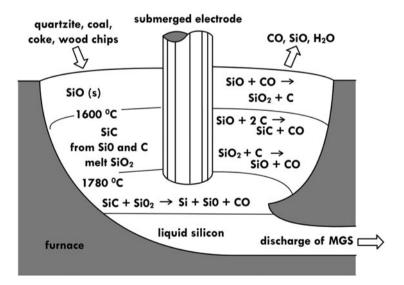

Metallurgical Grade polysilicon (MG) is produced through the reduction of silica by mixing it with carbon in the form of coal, coke, or wood chips and heating the mixture to high temperatures (more than 2000 °C) in a submerged electrode arc furnace (Fig. 1.5). The reaction that takes place is the following:

$$SiO_2 + 2C \rightarrow Si + 2CO$$

Silicon produced by this method typically contains ~2% impurities as Fe and Al and other impurities, including B and P.

#### 1.2.2 Electronic-Grade (EG) Polysilicon

The metallurgical grade silicon is converted into trichlorosilane (SiHCl<sub>3</sub>) in a fluidized bed by reaction with anhydrous hydrogen chloride:

**Fig. 1.5** Submerge-electrode arc furnace for Metallurgical-Grade Silicon (MGS) production. The temperature is maintained above the melting point of silicon so that the molten semiconductor is removed from the bottom

$Si(MG) + 3HCl \rightarrow SiHCl_3 + H_2$

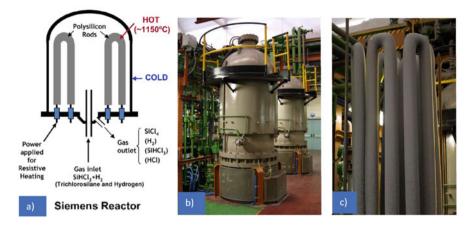

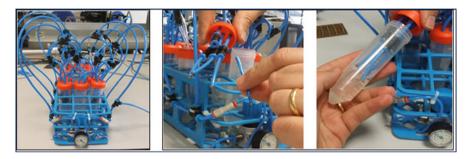

Fig. 1.6 (a) Schematic sketch of reactor vessel. (b) External view. (c) As grown polysilicon rods after reactor run (Current generation reactors have many rods)

During this reaction, which takes place at about 300 °C, various impurities such as Fe, Al, and B are removed by converting them into their halides (FeCl<sub>3</sub>, AlCl<sub>3</sub>, and BCl<sub>3</sub>, respectively), and byproducts such as SiCl<sub>4</sub> and H<sub>2</sub> are also produced. Subsequently the trichlorosilane is fractionally distilled from the impurity halides to obtain a very high purity compound (impurities are in the low parts per billion (ppb) range or less) a necessary requirement for production of semiconductor devices. The liquid TCS is then converted to solid polysilicon by the Siemens process. In this process, the triclorosilane is thermally decomposed into silicon and HCl in the presence of hydrogen as follows:

$SiHCl_3 + H_2 \rightarrow Si(EG) + 3HCl$

The decomposition of SiHCl<sub>3</sub> (1000–1200 °C) is accomplished in a reactor in which a thin rod of silicon known as a *slim rod* is available for the deposition of the silicon formed as a result of above reaction. Other intermediate compounds such as silicon tetrachloride (SiCl<sub>4</sub>) and silane (SiH<sub>4</sub>) can also be used. Figure 1.6a) is a schematic sketch of the reaction vessel in which the decomposition of SiHCl<sub>3</sub> takes place. The *slim rod* has to be of a purity level comparable to that of the deposited silicon. About 80% of the world's polisilicon is produced using the Siemen's process developed in the 1950s [14].

#### **1.3** Growth of Single Crystal Silicon

The growth of single crystal of silicon from high-purity polysilicon represents the first significant step in the manufacture of a highly perfect semiconductor material.

The industry standard for production of monocrystalline silicon for semiconductors is the Czochralski (CZ) method.

#### Historical Development of Single Crystal Growth – Czochralski's Creative Mistake.

The method currently used to grow a Single Crystal was discovered in 1916 [15] by Jan Czochralski (Fig. 1.7), a Polish chemist, while investigating the rate of crystallization of metals. The method was developed as a result of an accident and through Czochralski's careful observation [16]. One evening he left aside a crucible with molten tin and returned to writing notes into the laboratory notebook. At some moment, lost in thought, instead of dipping his pen in the inkpot he dipped it in the crucible. Alarmed, he quickly lifted his arm and noted that a long, thin thread was hanging onto the pen, which later proved to be a *single* crystal. They were not single crystals in today's understanding, though, they were "threads" of such metals as zinc, tin, and lead. At the time, there was no need whatsoever for monocrystalline materials, as all materials industrially exploited at that time were polycrystalline. It is worth noting that up to the Second World War, scientists were mainly interested in the properties of metals and their alloys, so mainly such crystals were grown at that time. After invention of germanium-based transistor in 1947, G.K. Teal and J.B. Little from Bell Laboratory used the Czochralski method to obtain germanium single crystals [17, 18]. Later, Teal and Buehler grew CZ-Si using the same technique, but they could only grow dislocated single crystals of specified orientation [19]. The first demonstration of dislocation-free CZ silicon crystal growth was demonstrated in 1959 by Dash, [20] using a modified seeding technique. Growth of silicon crystals by the CZ method have been widely studied

Fig. 1.7 Jan Czochralski, around 1907. (Photograph by kind permission of Prof. P.E. Tomaszewski)

over the course of the following five decades and significant progress has been made. Dislocation-free, high-purity silicon crystal up to 450 mm in diameter is now possible on a commercial scale.

#### 1.3.1 The Czochralski Crystal Pulling Method

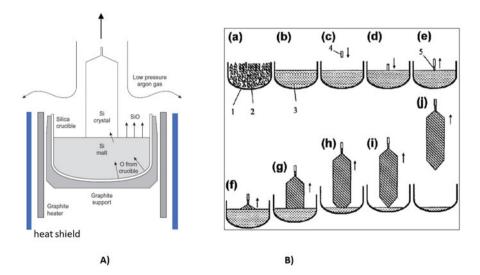

Schematic view of typical Czochralski silicon crystal growing system, today in use, is represented in Fig. 1.8A. It consists of a silica crucible (which is often called quartz crucible), a graphite susceptor around the silica crucible, a cylindrical heater, and a heat shield around the heater. As the silica crucible contains the melt, it is the most important component of the growth apparatus. The crucible material must be chemically unreactive with molten silicon. Also, the material must have high melting point, thermal stability, and hardness. The materials for crucible, which satisfy these properties, are silicon nitride  $(Si_3N_4)$  and fused silica  $(SiO_2)$ . The latter is in exclusive use nowadays. The graphite susceptor, around the silica crucible, is mandatory because the high temperature causes the crucible to soften, and a proper mechanical support is therefore needed. The susceptor also helps distribute heat around the silica crucible a little bit more uniformly. Graphite is the material of choice because of its high-temperature properties. The graphite must be pure to prevent contamination of the crystal from impurities that could be volatilized from the graphite at the temperature involved. The susceptor rests on a pedestal

**Fig. 1.8** (A) Czochralski silicon crystal growing system. (B) Czochralski Process steps: (a) The polycrystalline feedstock (1) is put inside a crucible (2); (b) it is melted (3); (c, d) Seeding procedure: The seed crystal (4) is dipped into the melt, followed (e) by Dash necking (5), (f) shouldering, (g) cylindrical growth, (h) growth of end cone, (i) lift off, (j) cooling down and removing of the crystal

whose shaft is connected to a motor that provides rotation. The heater is usually connected to two or four electrodes at its lower edge, typically by supporting elements also made of graphite. The electrodes deliver the required power, which is at least tens of kilowatts, but often well exceeds 100 kW. The heater is normally of picket type, which means that it has vertical slits cut into it in a manner that forces the electric current to flow up and down, in opposite directions in neighboring pickets. The voltage is quite low, and amperage is high, mainly because of the high electrical conductance of the heater, but also because of the poor electrical insulation properties of the inert gas at the low pressure and high temperature normally used in silicon CZ growth. The heat shield around the heater drastically reduces the power consumption, and it also helps create a more controlled temperature distribution around the susceptor.

At the beginning of the process, Fig. 1.8B, the feed material is put into a cylindrically shaped crucible and melted by resistance or radio-frequency heaters to one temperature that is slightly more than the silicon melting point of 1420  $^{\circ}$ C. A small single-crystal rod of silicon called a *seed crystal* is then dipped into the silicon melt. The conduction of heat up the seed crystal will produce a reduction in the temperature of the melt in contact with the seed crystal to slightly below the silicon melting point. The silicon will therefore freeze onto the end of the seed crystal, and as the seed crystal is slowly pulled up out of the melt it will pull up with it a solidified mass of silicon that will be a crystallographic continuation of the seed crystal. Both the seed crystal and the crucible are rotated but in opposite directions during the crystal pulling process to produce crystalline ingots of circular cross section. During the silicon growth process the shape of the crystal, especially the diameter, is controlled by carefully adjusting the heating power, the pulling rate, and the rotation rate of the crystal. In the initial stages, the pull rate is quite high, and the growing crystal is only about 3–5 mm in diameter. This narrow portion of the crystal is called the "neck" and was first used by Dash [20, 21] for producing a dislocation-free crystal and is standard practice in the industry today. In fact, in (111) and (100) oriented Si seed crystals, dislocations introduced, due to the thermal stress generated between seed (*cold*) and the melt (*hot*), will propagate obliquely to the growth direction, and will terminate on the sides of the neck rather than propagating down into the body of the growing crystal, provided the neck length to diameter ratio is sufficiently large. This was an important breakthrough for yield and reliability of semiconductor device fabrication processes, since dislocations can be killer defects in diode and transistor fabrication. Once the neck is several centimeters long, the pull rate is slowed allowing the crystal diameter to increase to the desired dimension. At the end of crystal growth, the diameter of the crystal is tapered to form a conical tail that minimizes the number of dislocations formed by the thermal shock of withdrawing the crystal from the melt and allows these dislocations to propagate out of the sides of the cone rather than into the body of the crystal, maintaining a dislocation free crystal. Silicon CZ growth takes place under a continuous flow of inert gas. A schematic picture of the gas flow pattern is shown in Fig. 1.8(A)Considering the high temperature and the reactivity of silicon melt, noble gases are the only ones allowed. Argon is the gas of choice because of its much lower

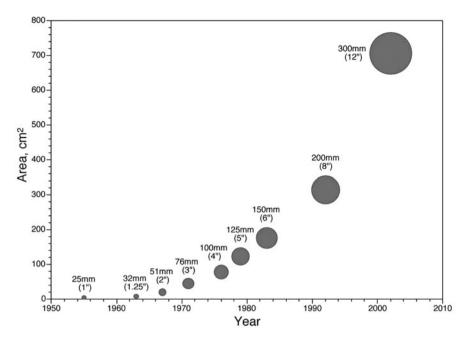

**Fig. 1.9** (a) A single crystal of silicon, 300 mm in diameter, 2 m long, and weighing 265 kg drawn using the CZ process; photograph reprinted here with permission of Wacker-Chemie – from Ref. [16]. (b) Increase in areas of CZ silicon crystal sections over the years

cost than that of other noble gases. Argon has also the advantage of poor thermal conductivity compared with, for example, helium, and this feature facilitates the effort to insulate hot areas around the melt from the water-cooled vacuum-chamber walls. Oxygen is dissolved from the crucible, and the purge gas removes volatile silicon monoxide from the vicinity of the melt and the crystal. Only a small fraction of total dissolved oxygen ends up in the growing crystal. Figure 1.9a) displays a cooled silicon single crystal that was produced by the CZ method. At the top of the single crystal is situated the thin seed which at the start of drawing is dipped into a crucible containing molten silicon. In Fig. 1.9b) is shown the increase in areas of CZ silicon crystal sections over the years.

Fig. 1.9 (continued)

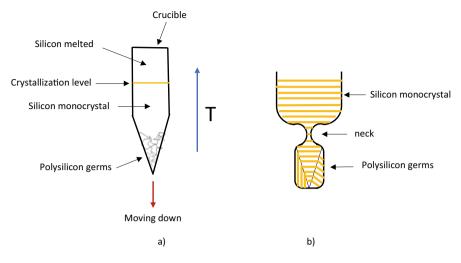

#### About Seed Crystal

The first silicon single crystals were obtained in the fifties of the last century, starting from polycrystalline germs. The technique used, proposed by *Stockbarger*, was to grow preferentially a "polycrystalline grain" over the others. In this method, the substance, in our case the polycrystalline silicon, is melted in a crucible, Fig. 1.10a), where there is a temperature gradient. The crucible is then lowered slowly, towards the lower temperature zone, so that the crystallization starts from its bottom, which is shaped like a cone. In a first time, several crystalline or disoriented polysilicon grains are formed, but continuing the crystallization (and the lowering of the crucible) one of them will have the upper hand over the others and affect growth of the whole rest of the melted, obtain a single crystal with the same orientation of the initial "grain". Things can be facilitated by shaping the crucible tip as shown in Fig. 1.10b). This shaping also has the advantage of preventing dislocations in the growing single crystal. Once the first crystal was made available, subsequent germs were obtained directly by cutting the crystal. Today's industrial germ-building process reproduces itself with a simpler cloning process; from a single crystal the new germs are cut out for many other single crystals.

Fig. 1.10 Technique used to grow the first silicon seed crystal

#### 1.3.2 Impurities in Czochralski Silicon

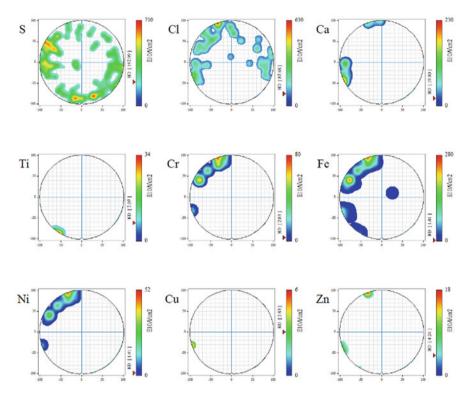

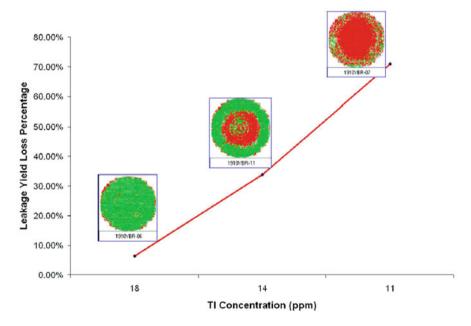

The CZ silicon crystals contain small amounts of impurities of which some are essential, in controlled amounts, for the quality of the crystal and wafers as oxygen, while other impurities are harmful if their concentration is too high and, thus, the latter elements must be avoided. The harmful impurities in CZ silicon crystals include transition-metal impurities (e.g., Fe, Cu, and Ni) [22-25], and alkali and alkali earth metals (e.g., Na). These impurities, as well as accidental dopants, may originate from the starting materials (polysilicon, recycled silicon, if used, and dopants), silica crucible, and materials and contamination of the furnace and the hot zone [26]. Carbon, (typically less than 0.5 ppma) introduced from the graphite parts used in the crystal puller hot zone, is electrically inactive in silicon, while transition-metal impurities may form deep impurity levels within the band gap between the conduction and valence bands, behaving as recombination centers or as unwanted acceptors and/or donors, or forming complexes with dopants under certain conditions. The transition metals, or their precipitates, may increase the recombination lifetimes and cause leakage currents in the junctions of the devices, quality problems with gate oxides in metal-oxide-semiconductor structures, or even a shift of the resistivity. For example, iron can be very effective in decreasing the recombination lifetime, especially in p-type silicon [27], while copper is considered to have a greater impact on the lifetime of n-type wafers than on p-type wafers. Oxygen originating from the silica crucible is one of the most characteristic impurities in CZ silicon. A suitable oxygen concentration is among the main quality factors to be controlled in the crystal-growing process. Oxygen in interstitials gives the wafers mechanical strength against thermal or mechanical stress during heat treatments, decreasing the risk of slip dislocation formation and wafer warping

[28, 29]. Furthermore, oxygen forms precipitates [30-32], which are often used for impurity gettering in device processing, where gettering is a method to remove harmful metal impurities from the device region of the wafer [33]. Also, too high an oxygen concentration can be harmful if it induces too strong precipitation of oxygen and formation of defects. In fact, oxide precipitates formed in the active device region near the wafer surface can cause the device to fail but those away from the surface, in the bulk of the wafer, can provide a benefit by trapping metal impurities that may contaminate a wafer during processing. The process of trapping impurities in this way is called *internal gettering*. For gettering to take place with maximum advantage, it is necessary to ensure that oxygen precipitates form only in the wafer bulk and not near the surface. This can be achieved by employing silicon wafers with tightly controlled oxygen levels (typically within the range ~8-15 ppma depending upon the specific application) and subjecting them to a thermal cycle at sufficiently high temperature and length of time to out diffuse oxygen near the wafer surface such that the concentration is below the critical supersaturation level to form precipitates. Under these conditions, during the remaining thermal processes of the device manufacturing, the oxygen near the wafer surface remains in solution, while in the supersaturated wafer bulk it precipitates forming gettering centers [34]. The near-surface region without precipitates is known as the denuded zone (DZ).

#### **1.3.3** Defects in Silicon Crystals

Although single crystalline silicon made with CZ growing method is almost perfect contain anyway some defects. Furthermore, during the processing of silicon wafers for implementing the devices other defects are formed. These defects can be classified as:

- (a) Point defects: vacancies and self-interstitials or their agglomerates

- (b) Linear defects: dislocations

- (c) Planar defects: stacking faults

- (d) Volume defects: precipitates, COP (Crystal Originated Particles)

Short descriptions of the typical defects in CZ silicon are given in the list below.

Vacancies and self-interstitials: They are generating during silicon crystals grown from the melt because of their low diffusivity; in such a way the vacancies and self-interstitials are "frozen in" the crystal during the cooling phase. Vacancies and interstitials have equilibrium concentrations that depend on temperature and they play a very important role in the kinetics of diffusion and oxidation in the technical processes of silicon. In fact, the diffusion of many dopants depends on the vacancy concentration, as does the oxidation rate. Reviews of Falster et al. [35, 36] give an overview of intrinsic point defects in CZ silicon.

- Linear defects are called dislocations. In silicon single crystals grown by CZ or in wafers cut from these crystals, the dislocations density is practically zero. During the processing of the silicon wafer at higher temperatures, the applied stress may generate dislocations. The origin of these stresses can be thermal gradients during temperature transients in heat treatment steps, or mismatch stresses caused by thin films or heavily doped areas in combination by high temperatures. Movement of dislocations through the crystal lattice causes permanent deformation. Dislocations in silicon move on {111} planes along [110] directions. If the deformation is heavy, the wafer warpage may increase. In general, dislocations in silicon wafers have adverse effects on device performance. Dislocations attract impurities, and the result can be that moving dislocations leave precipitate colonies behind.

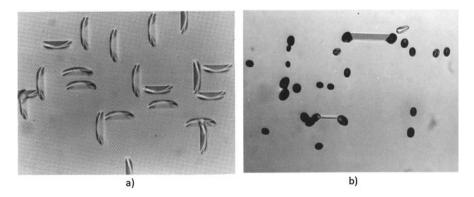

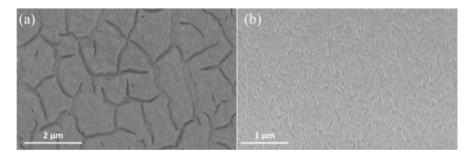

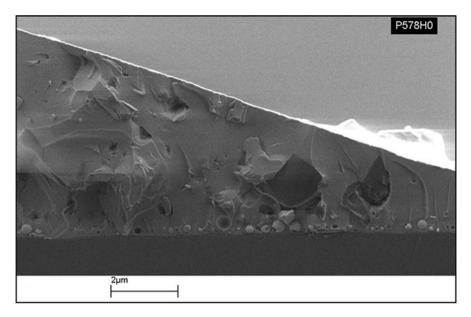

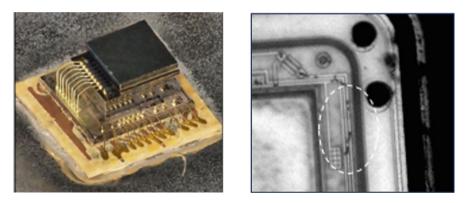

- **Planar defects** are called stacking faults. In silicon, stacking faults are along (111) atomic planes and they are surrounded by partial dislocation. A silicon lattice may contain an extra atomic place; this stacking fault is called extrinsic. If an atomic plane is missing, the stacking fault is intrinsic. Most stacking faults in silicon is of the extrinsic type. Extrinsic stacking faults are formed by excess silicon interstitials; oxidation-induced stacking faults or stacking faults around growing oxide precipitates are typical examples. A large oxygen precipitate may generate stacking fault(s) to reduce misfit stresses. Wet oxidation of silicon wafer also may induce stacking faults. Figure 1.11a) displays surface Stacking Faults (SF) on CZ wafer after Secco D' Aragona chemical etch (3 min); Fig. 1.11b) shows bulk Stacking Faults and dislocations on CZ after 48 h dry oxidation at 1100 °C (3 min Secco, 500x). The lattice strain caused by Oxidation Stacking Faults (OSF) is strongest at those positions where the partial dislocations enter the surface. This leads to the formation of stacking fault etch pits in the form of "dog-bones".

- **Volume defects** in silicon are precipitates. They can be coherent (the lattice of the precipitate is aligned with the host silicon lattice), or non-coherent, when there

**Fig. 1.11** (a) Surface stacking faults (SF) on CZ (3 min Secco). (b) Bulk SF and dislocations on CZ (3 min Secco)

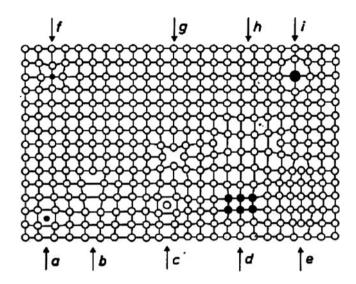

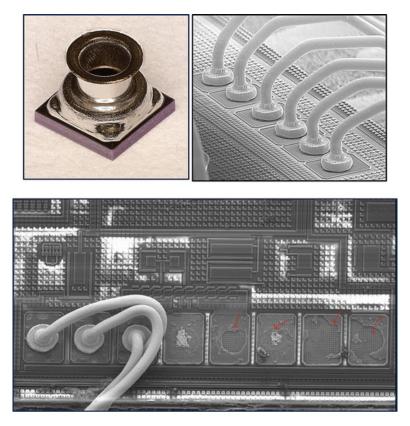

Fig. 1.12 Various crystal defects in a simple cubic lattice (a) Interstitial impurity atom, (b) edge dislocation, (c) self-interstitial, (d) coherent precipitate of substitutional impurity atoms, (e) small dislocation loop formed by agglomeration of self-interstitials, (f) substitutional impurity atom widening the lattice (tensile strain), (g) vacancy, (h) small dislocation loop formed by agglomeration of vacancies, (i)substitutional impurity atom compressing the lattice (compressive strain)

is a mismatch in lattice alignment. Small precipitates are often coherent, and when they grow, they turn first semi coherent, and then non-coherent. Precipitates are normally compounds of silicon: silicates or silicon dioxide. COP (Crystal Originated Particles), a cluster of vacancies, is also a volume defect. The size and density of this defect depends on the crystal growth process; the average size can be from tens of nanometer to less than 200 nm. COP has mostly an effect gate oxide quality in CMOS devices. Because the COP originates from crystal growth process involving melt, epitaxial layers are free from COPs.

A schematically representation of various crystal defects in a simple cubic lattice (silicon) is shown in Fig. 1.12.

#### 1.4 New Crystal Growth Methods

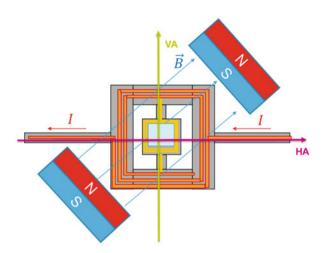

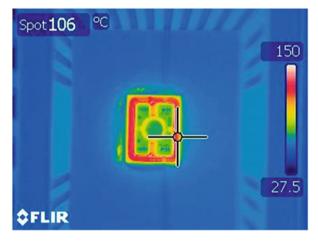

## 1.4.1 Czochralski Growth with an Applied Magnetic Field (MCZ)

The use of magnetic fields for the growth of semiconductor crystals have already been considered many decades ago. As early as in 1966, Chedzey et al. [37] and

Utech et al. [38] reported about InSb crystals grown in a horizontal boat under the influence of a magnetic field. They found a suppression of temperature fluctuations in the InSb melt and a decrease of growth variations (striations) in the crystal. In 1970, Witt et al. [39] applied a static transverse (horizontal) magnetic field to the Czochralski (CZ) growth of InSb crystals. Ten years later, in 1980, the transverse field was also used for the CZ growth of silicon single crystals [40, 41]. Originally MCZ was intended for the growth of CZ silicon crystals that contain low oxygen concentrations and therefore have high resistivities with low radial variations. In other words, MCZ silicon was introduced to replace the FZ (Floating Zone method) silicon almost exclusively used for power device fabrication. Since then, the method has received considerable attention over the years. The effect of the magnetic field is explained by its ability to fluid flow damping; the movement of an electrically conducting fluid, as liquid silicon, in a magnetic field causes, due to Lorentz force, an electromotive force that is perpendicular to both the field and the direction of movement. This electromotive force tends to create electric currents that, interacting with the external magnetic field, oppose the fluid motion. The field strengths typical for magnetic CZ (MCZ) processes are sufficient to slow down various flow patterns very significantly. This has implications to a range of crystal properties such as oxygen and dopant distributions; but they also tend to reduce crucible wear, thus extending the lifetime of the crucible, and reduce thermal fluctuations in the melt, which, together with reduced crucible wear, results in better dislocations - free growth yields. After the MCZ technology had been established as a standard method for low-oxygen CZ material, it was found that magnetic fields were also useful for the growth of advanced CZ crystals, e.g., the so-called "perfect", "pure", or "ultimate" silicon [42–44]. Silicon crystals of this type are grown under conditions which avoid large agglomerates of intrinsic point defects, i.e., L pits (Si interstitial aggregates) and voids (vacancy aggregates). Below a critical size, these defects are no longer harmful to device functioning and, hence, can be tolerated. Today, a substantial part of the CZ pullers is equipped with a transverse magnetic field of 3000-5000 G, which has been shown to be most suitable to produce this advanced material.

#### 1.4.2 Continuous Czochralski Method (CCZ)

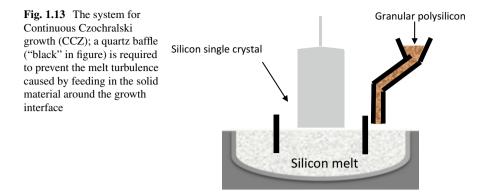

Crystal production costs depend to a large extent on the cost of materials, in particular the cost of those used for quartz crucibles. In the conventional CZ process, called a *batch process*, a crystal is pulled from a single crucible charge, and the quartz crucible is used only once and is then discarded. This is because the small amount of remaining silicon cracks the crucible as it cools from a high temperature during each growth run. Today, supply for large silicon wafers has driven the growth of silicon crystals from 200 to 300 mm in diameter. With the increasing silicon ingot sizes, melt volume has grown dramatically, exacerbating the costs and problems related to oxygen control and resistivity in the silicon monocrystal. A proposed

strategy to resolve these issues consists of continuously adding feed as the crystal is grown and thereby maintain the melt at a constant volume. According to this method, named Continuous Czochralski Method (CCZ), the silicon monocrystal can be pulled while the amount of the silicon melt in the crucible remains constant. Therefore, the oxygen concentration and resistivity of the silicon monocrystal, which depend on the amount of the silicon melt in the crucible, can be constantly maintained. This makes it possible to considerably improve the manufacturing yield of the silicon monocrystal, which in turn allows reduction in manufacturing costs and provides an ideal environment for silicon crystal growth. Continuous charging is commonly performed by polysilicon feeding, as shown in Fig.1.13 This system consists of a hopper for storing the polysilicon raw material and a vibratory feeder that transfers the polysilicon to the crucible. In the crucible that contains the silicon melt, a quartz baffle is required to prevent the melt turbulence caused by feeding in the solid material around the growth interface. The CCZ method certainly solves most of the problems related to inhomogeneities in crystal grown by the conventional CZ method. Moreover, the combination of MCZ and CCZ (the Magnetic-field-applied Continuous CZ [MCCZ] method) is expected to provide the ultimate crystal growth method, giving ideal silicon crystals for a wide variety of microelectronic applications [45, 46].

#### 1.4.3 Neckingless Growth Method

As mentioned in 1.3.1, Dash's necking process, able to eliminate grown-in dislocations, has been the industry standard for more than 40 years. However, recent demands for large crystal diameters (greater than 300 mm, weighing over 300 kg) have resulted in the need for larger diameter necks that do not introduce dislocations into the growing crystal, since a thin neck 3–5 mm in diameter cannot support such large crystals' weight. It is estimated that large diameter necks 12 mm in diameter can support CZ crystals as heavy as 2000 kg [47]. Such a large size of the neck, however, is unable to block the propagation of dislocations into the body of the growing crystal. Fortunately, it was found that the boron concentration limit in the seed for no dislocation formation due to thermal shock was  $1 \times 10^{18}$  atoms/cm<sup>3</sup>, and the maximum admissible discrepancy of boron concentration in the seed and in the crystal was  $7 \times 10^{18}$  atoms/cm<sup>3</sup> for no dislocation formation in the crystal due to the lattice misfit. Consequently, it is revealed that dislocation-free CZ-Si crystals can be grown from undoped Si melt without the Dash-necking process when a seed with a suitable boron concentration is used. The mechanism by which dislocations are not incorporated into the growing crystal has been primarily attributed to hardening effect of the heavy doping of boron in the silicon.

#### **1.5** Silicon Wafers Preparation and Properties

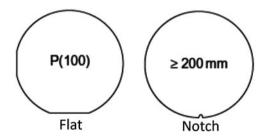

After the silicon crystal has cooled, it is removed from the crystal puller for machining. Silicon crystals, or ingots in the terminology, commonly in use are typically up to 2 m in length, and they have a small over-diameter to eliminate yield loss in final wafers due to diameter fluctuation and small deviations from round shape during the growth. Therefore, crystals are typically grown a few millimeters oversize on diameter and ground down to the required size prior to slicing. Initially the shoulder and tail portions are removed with a diamond blade cropping saw and recycled. The body of the crystal is then sawed into lengths that can be accommodated by the subsequent slicing operation and prepared for grinding to the required diameter. In the days of smaller wafers, a flat was ground along one side to indicate crystallographic direction as determined by X-ray diffraction, but later, on larger wafers and in the interests of preserving surface area for saleable devices, the flat was replaced by a notch (see figure on the right side).

#### 1.5.1 Silicon Wafers Manufacturing Process

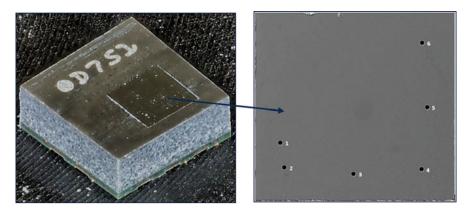

The **wafer production process** (Fig.1.14) starts with slicing of the crystal ingot. The ingot to be sliced into wafers needs a support to hold cut wafers; therefore, a ceramic

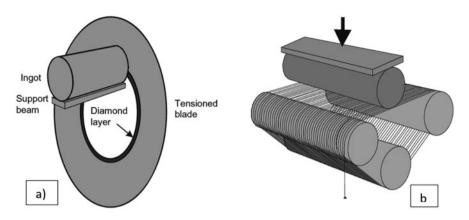

Fig. 1.14 (a) Internal Diameter (ID) saw machine; (b) Wire saw machine

or graphite beam is glued onto the piece of ingot. Two types of slicing methods have been used in the silicon wafer industry: the internal diameter (ID) saw, Fig. 1.14a, and the wire saw, Fig. 1.14b. The ID saw uses a thin annular blade with a diamond bonded region on the inside edge of the annulus. ID saws cut only one wafer at a time, taking a few minutes to slice each wafer from the crystal. Today, wafers (and from 200 mm up, extensively) are increasingly cut in wire-cutting machines because of productivity reasons. ID cutting, however, retains the flexibility of manufacturing smaller lots, but with higher cost.

Wire saw slicing of silicon is achieved predominantly by Free Abrasive Machining (FAM) using a slurry comprising silicon carbide (SiC) grit suspended in either oil or ethylene glycol. The wire acts to transport slurry to the silicon ingot where the grit becomes trapped between the tensioned wire and the ingot creating what is known as a rolling and indenting cutting mechanism [48–50]. Recently, wire cutting using diamond coated wire has been introduced. The method was introduced first to solar grade silicon wafer manufacturing and is now becoming more common in semiconductor grade wafer manufacturing. By using diamond wire, it is possible to use water as a coolant, creating savings in waste treatment and as-sawn wafer surface quality is improved [51, 52]. However, reports indicate that diamond wire wafers in as-sawn state are more prone to fracturing [53]. Ideally, the slicing process would produce wafers with a polished surface perfectly flat and clean ready for device fabrication. In practice, cut wafers have significant crystallographic damage induced by the slicing process. They are typically slightly warped, of nonuniform thickness with rough, contaminated surfaces, and a square edge profile which is easily chipped. Independent of the cutting method, wafers are cleaned after cutting, and the supporting beam piece is removed. In addition to cleaning, a slight etch may be used to reduce surface damage to make the wafer mechanically stronger, and reduce the stress-related warp. The wafering process sequence after sawing is designed to produce the ideal wafer at the lowest cost and includes the steps of Edge Grinding, Lapping and Etching, Polishing and Cleaning.

#### Edge Grinding

Silicon wafers after cutting have sharp edges, and they chip easily. The wafer edge is shaped to remove sharp, brittle edges; rounded edges minimize the risk for chipping. The edge shaping operation makes the wafer perfectly round (off-cut wafers are oval shaped after slicing), the diameter is adjusted, and orientation flat(s) or notch is dimensioned or made. This operation is done normally with a profiled diamond wheel, and the edge profile follows the shape given by SEMI M1-0414 [54].

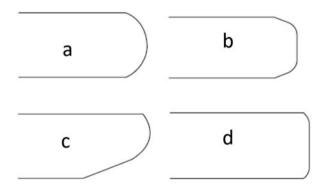

The SEMI standard profile is often not suitable or ideal for MEMS applications. If the wafer is to be thinned after processing, the wafer edge may, as a result, be sharp and thus brittle using the standard profile; therefore, an asymmetric edge profile can be used. Also, wafer bonding may set specific requirements for the wafer edge shape; typically, for bonding applications, a blunter profile is recommended to achieve a good bond up to wafer edge. In Fig. 1.15 are shown some examples of the edge profiles. Profiles (a) and (b) are conventional. Profiles (c) and (d) are optimized for wafer thinning after processing. Profile (d) is also suitable for various bonding applications.

#### Lapping and Etching

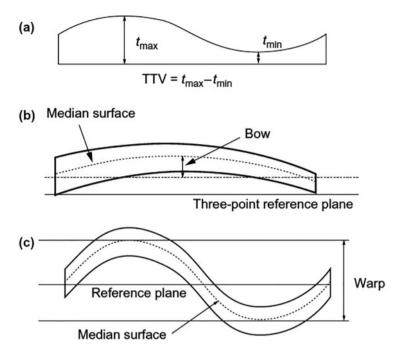

Cut wafers from a saw typically have a higher TTV (Total Thickness Variation: the absolute variation of wafer thickness relative to a reference plane) than that required for state-of-the-art lithographic processes used by device manufacturers. This state is corrected by subjecting the wafers to a grinding (fixed abrasive) or lapping (loose abrasive) process. The macroscopic flatness of wafers is typically determined by this lapping or grinding process. Subsequent chemical etching removes the crystallographic damage that these processes produce.

Fig. 1.15 Examples of the wafer edge profiles

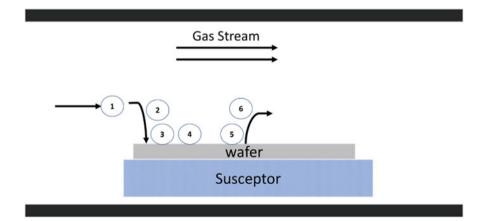

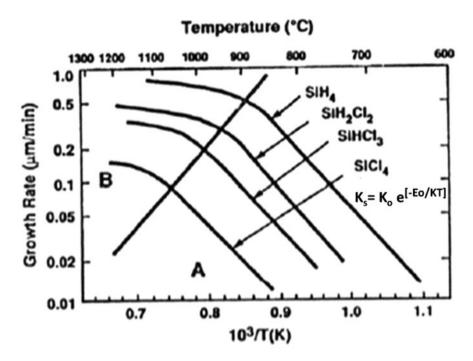

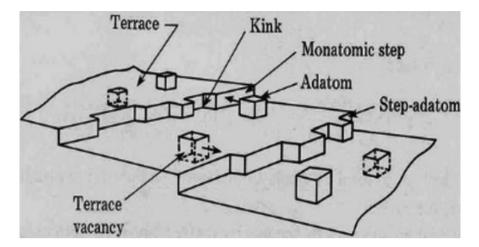

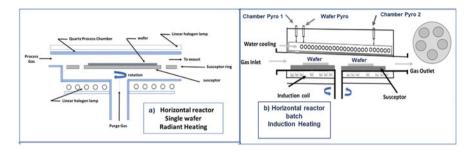

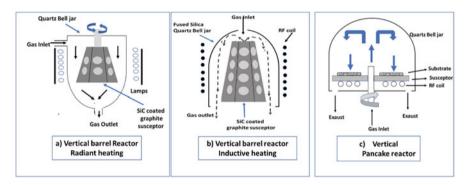

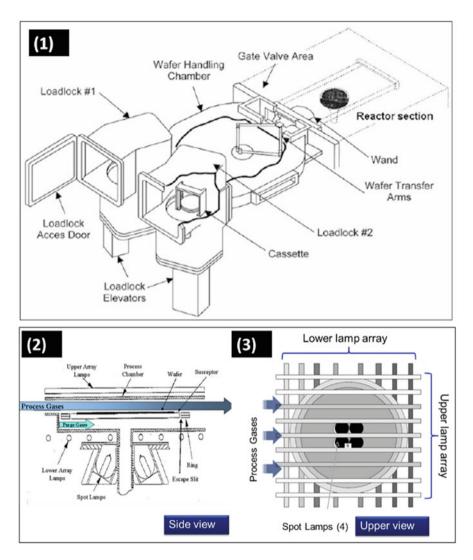

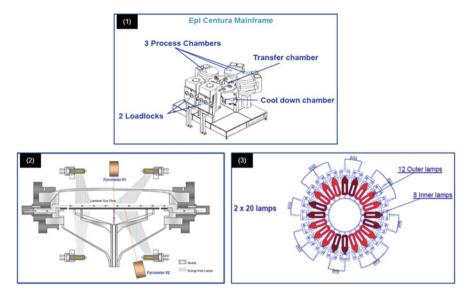

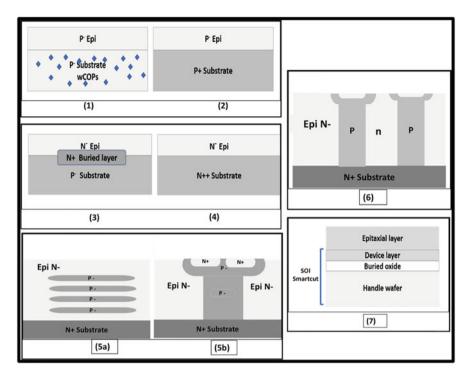

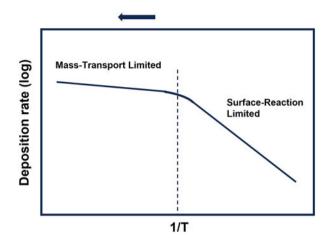

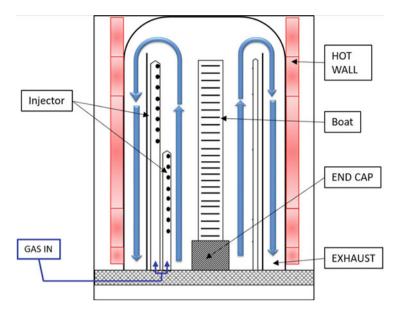

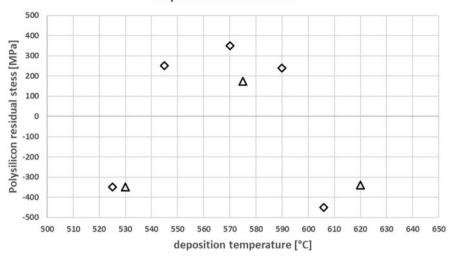

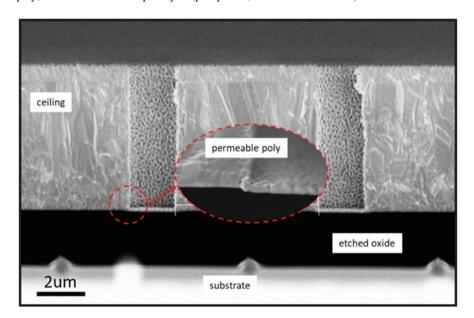

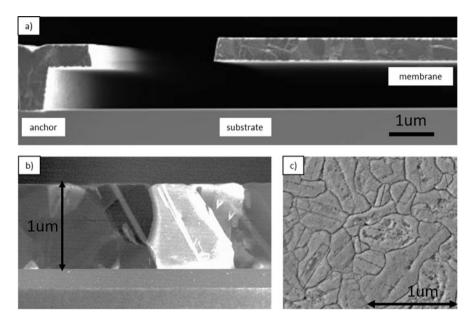

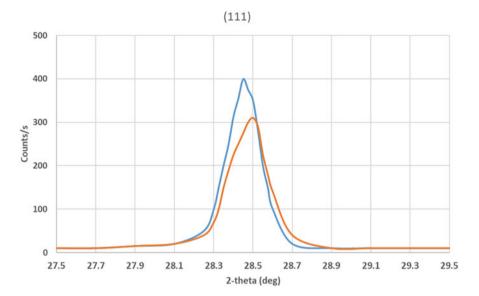

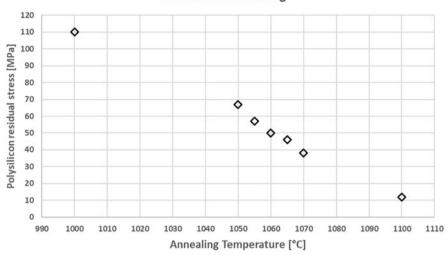

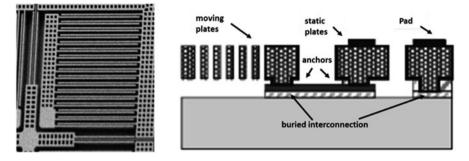

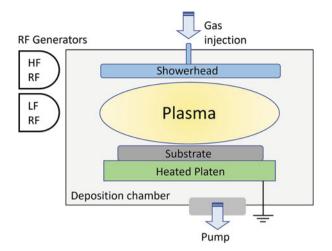

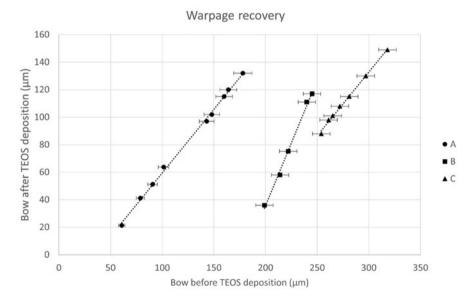

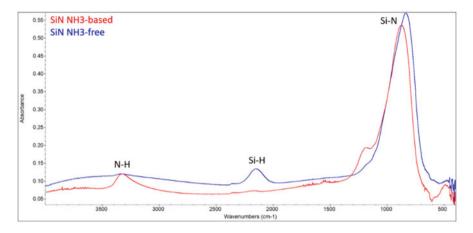

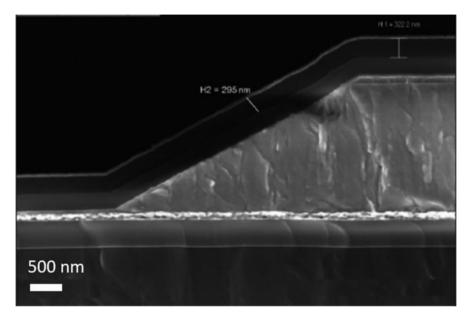

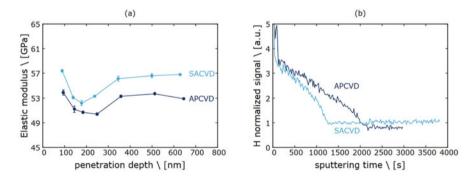

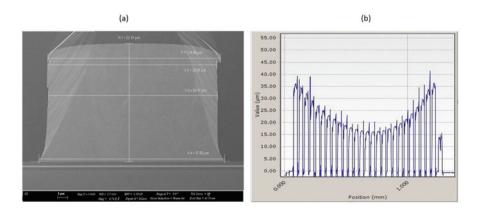

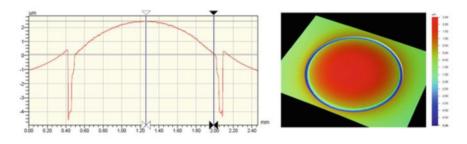

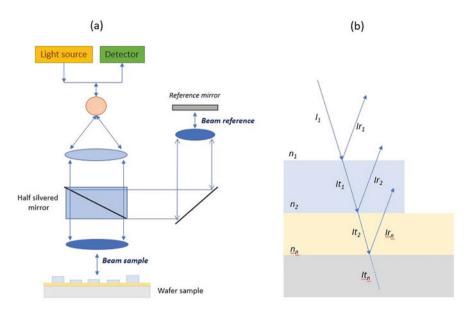

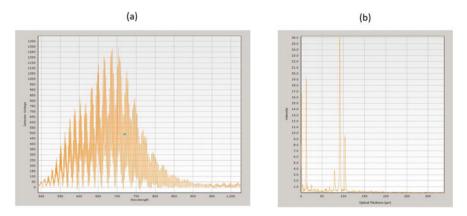

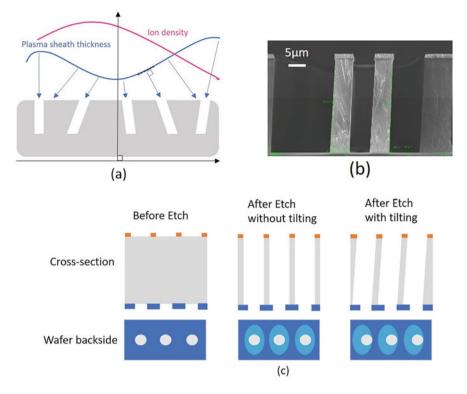

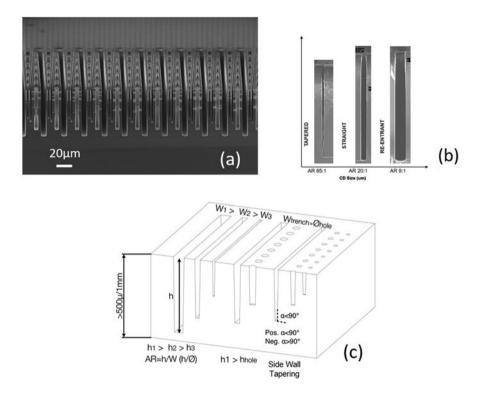

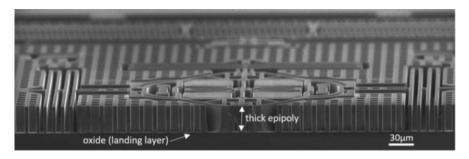

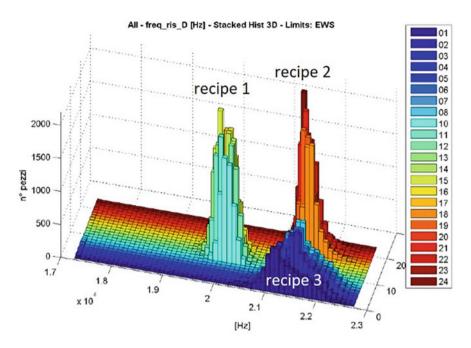

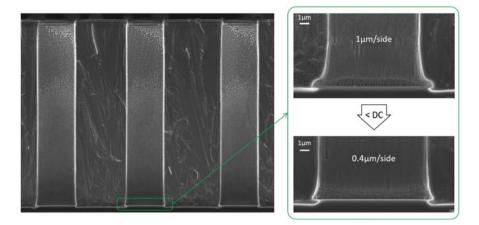

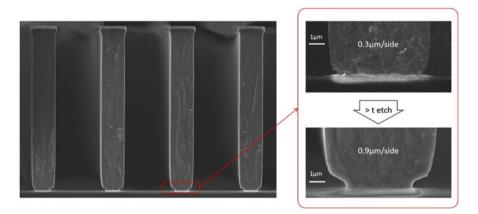

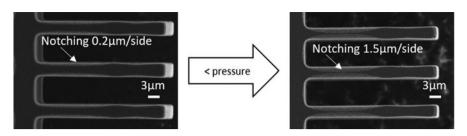

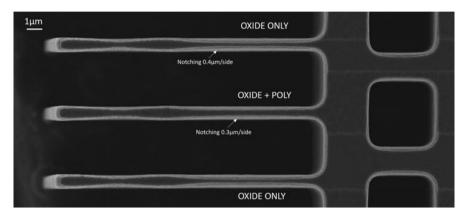

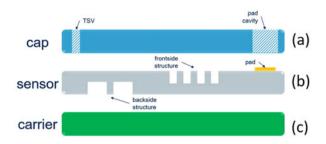

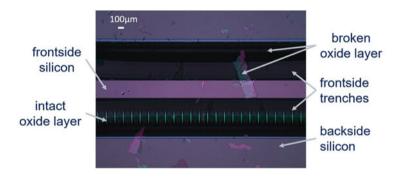

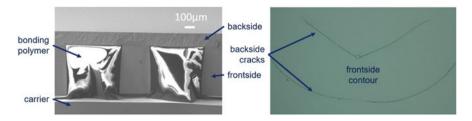

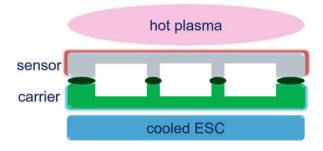

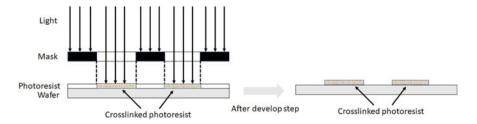

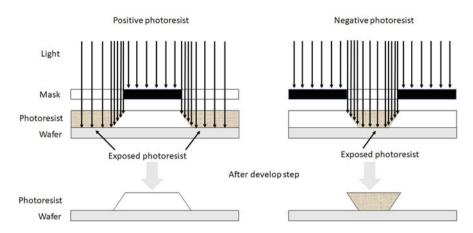

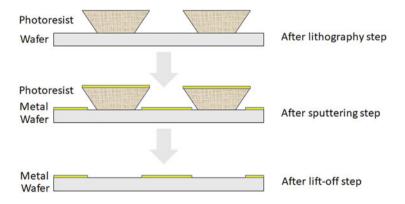

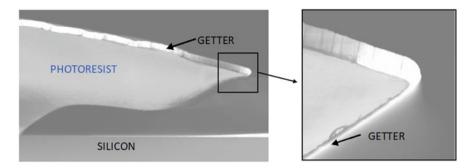

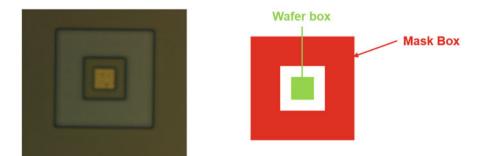

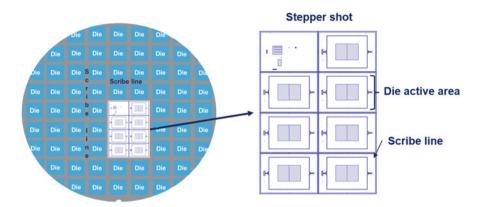

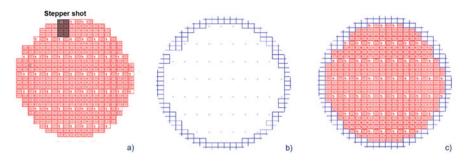

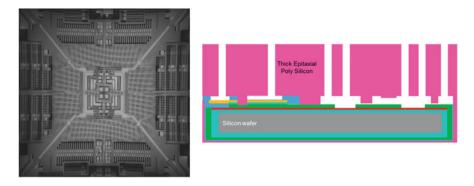

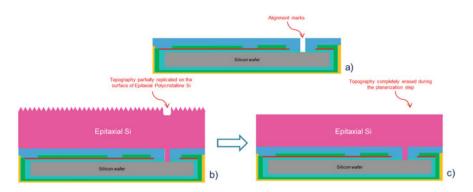

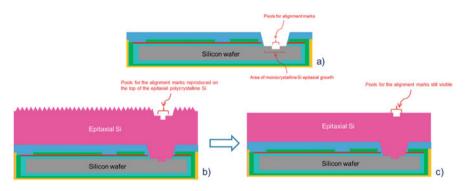

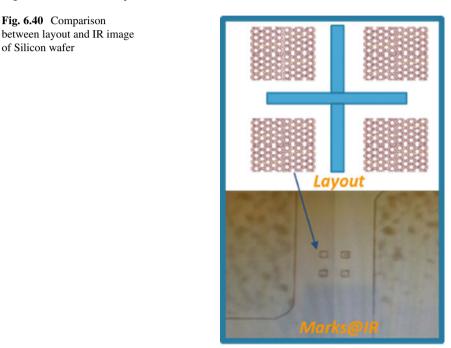

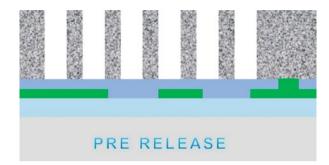

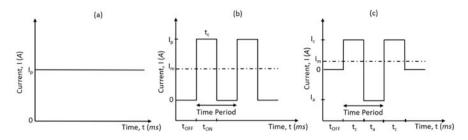

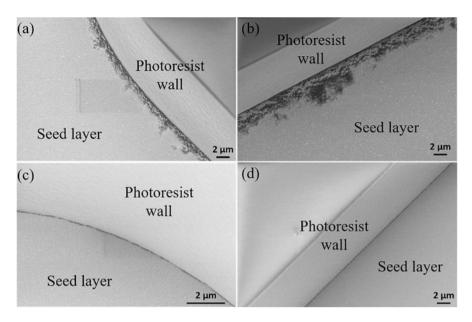

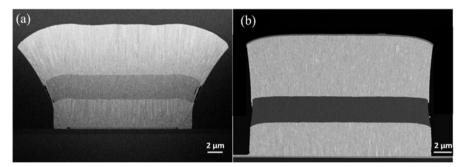

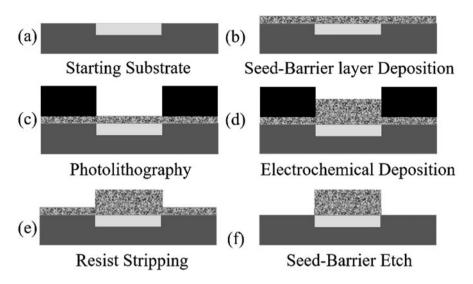

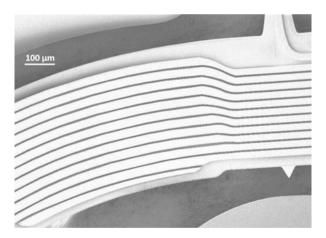

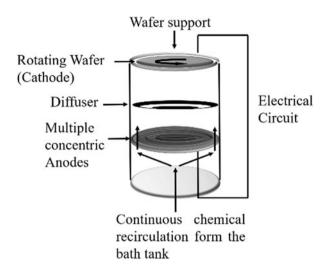

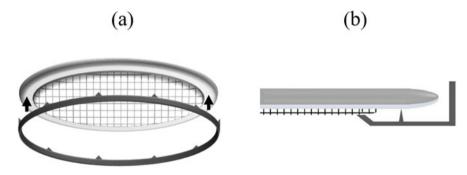

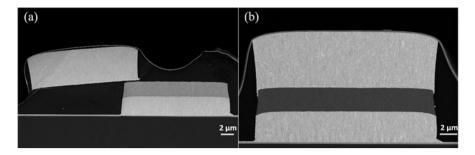

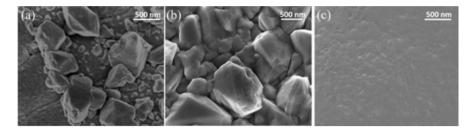

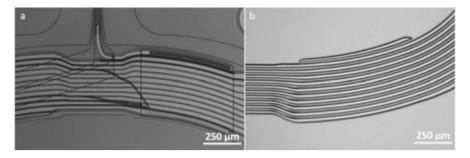

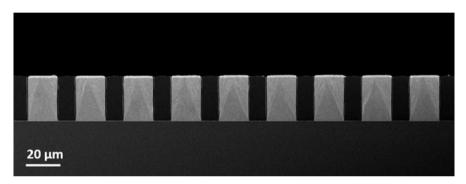

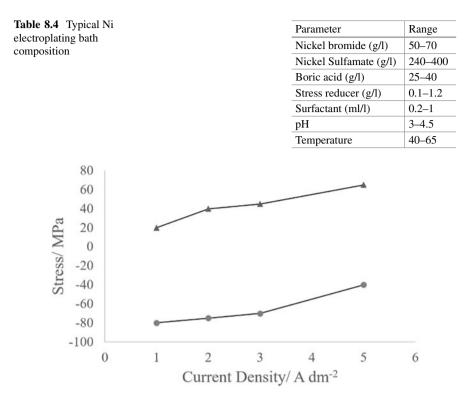

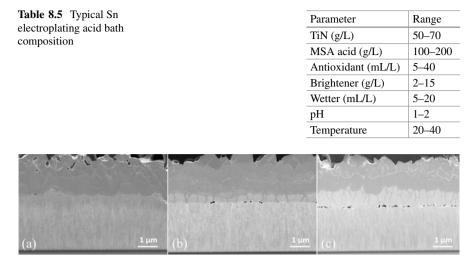

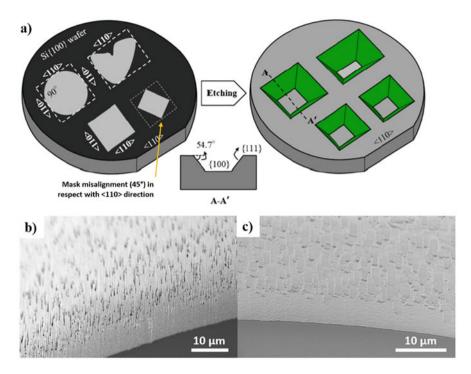

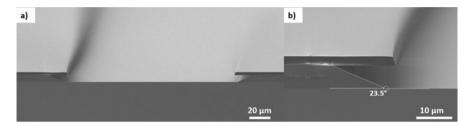

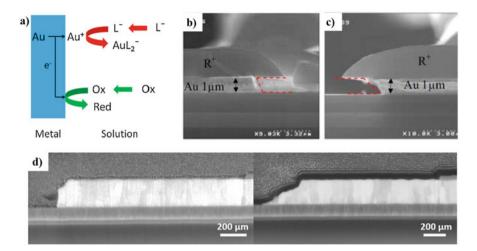

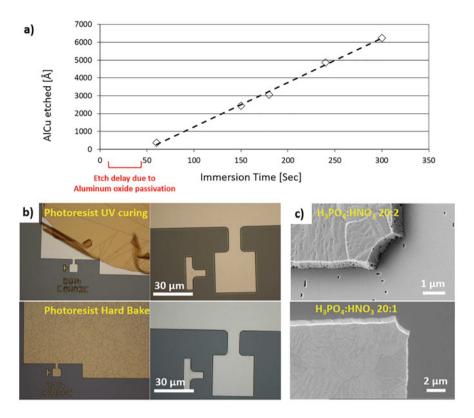

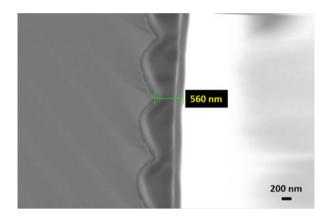

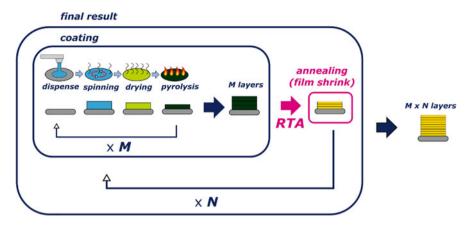

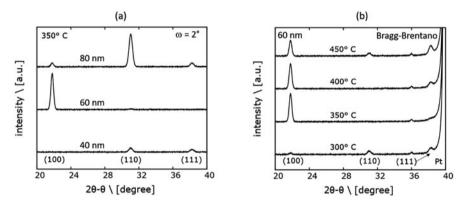

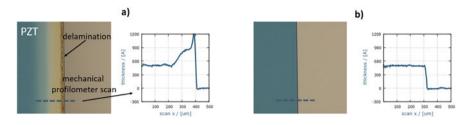

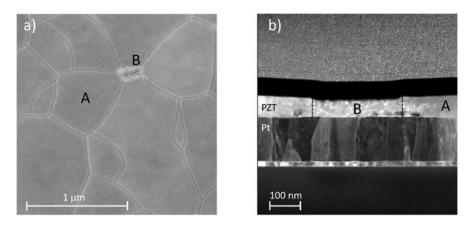

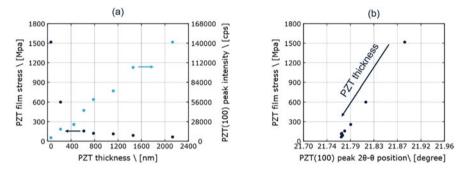

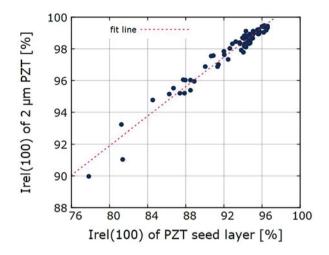

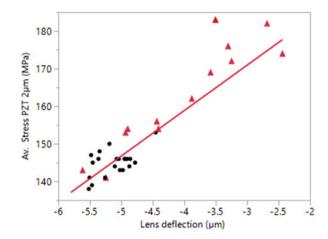

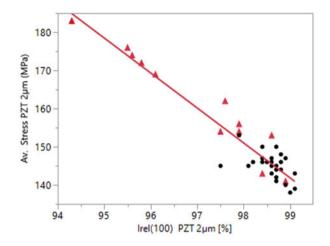

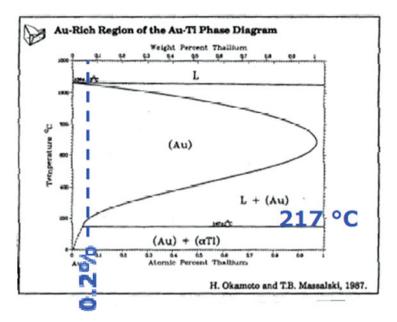

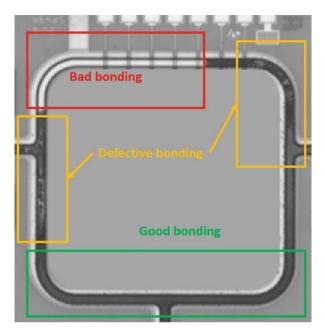

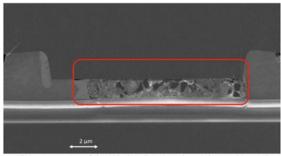

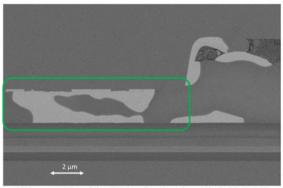

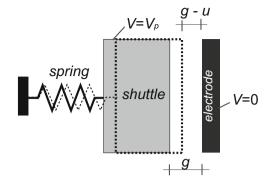

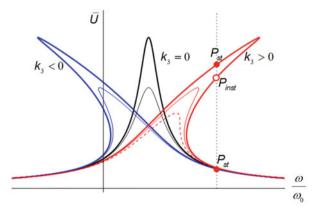

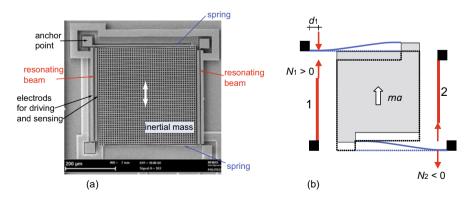

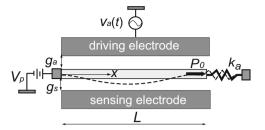

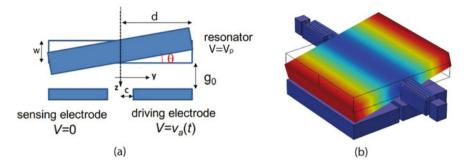

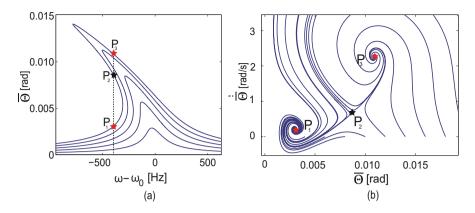

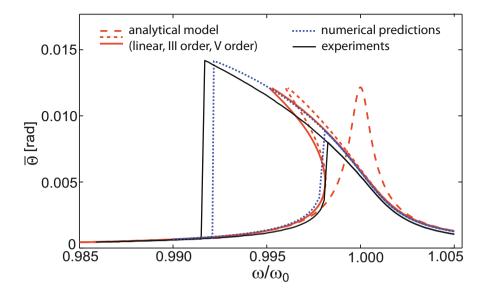

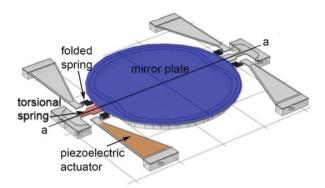

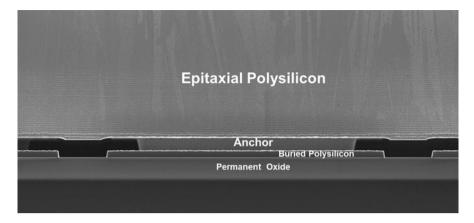

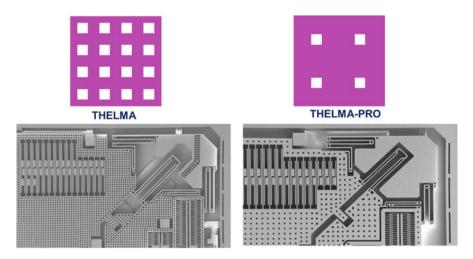

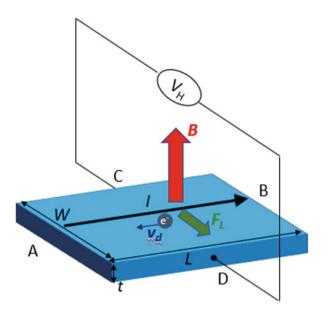

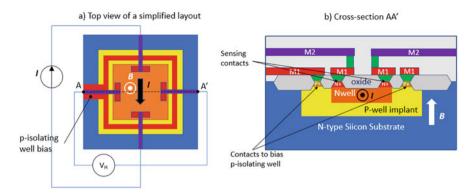

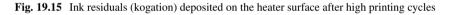

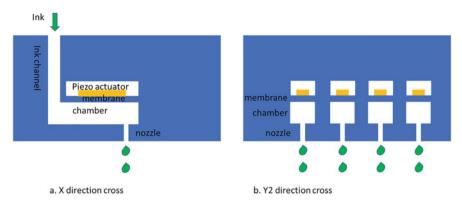

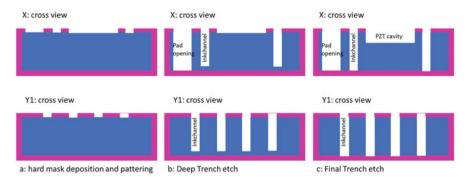

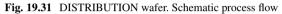

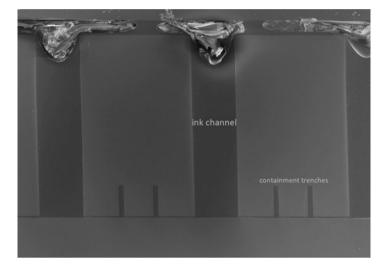

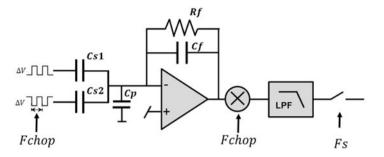

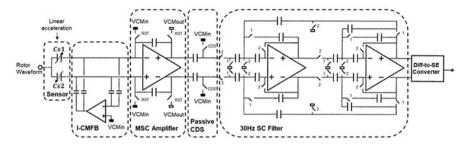

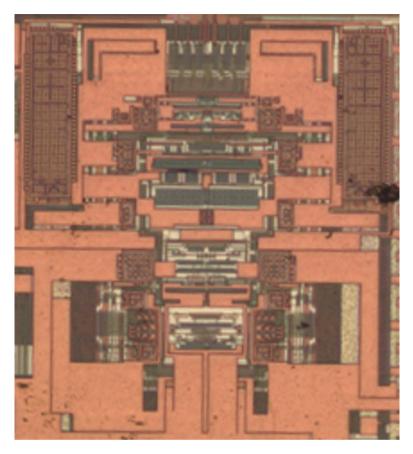

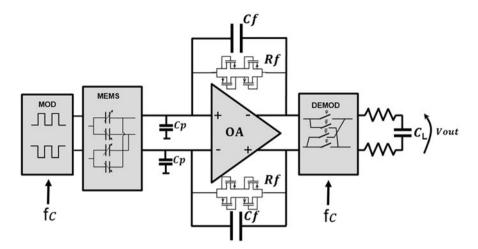

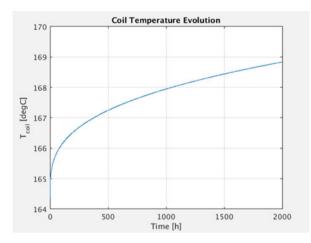

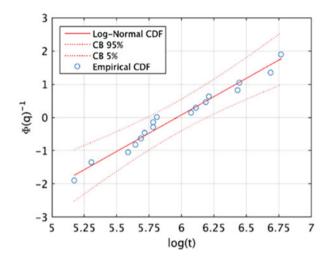

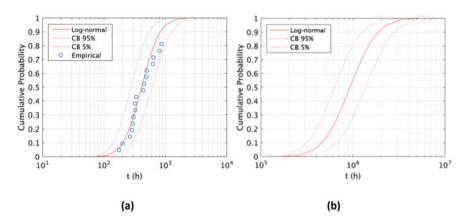

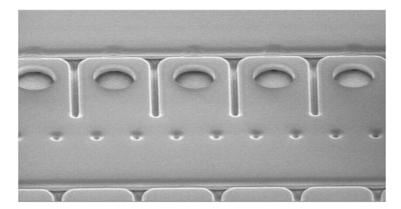

#### Polishing