# Analysis of Warpage Induced by Thick Copper Metal on Semiconductor Device

Michele Calabretta<sup>1</sup>( $\boxtimes$ ), Alessandro Sitta<sup>1,2</sup>, Salvatore Massimo Oliveri<sup>2</sup>, and Gaetano Sequenzia<sup>2</sup>

<sup>1</sup> ADG R&D, STMicroelectronics, Stradale Primosole 50, Catania, Italy michele.calabretta@st.com

<sup>2</sup> Dipartimento di Ingegneria Elettrica, Elettronica e Informatica (DIEEI), Università degli Studi di Catania, Viale Andrea Doria 5, Catania, Italy

Abstract. Electrochemical deposited (ECD) thick film copper on silicon substrate is one of the most challenging technological brick for semiconductor industry representing a relevant improvement from the state of art because of its excellent electrical and thermal conductivity compared with traditional compound such as aluminum. The main technological factor that makes challenging the industrial implementation of thick copper layer is the severe wafer warpage induced by Cu annealing process, which negatively impacts the wafer manufacturability. The aim of presented work is the understanding of warpage variation during annealing process of ECD thick (~20  $\mu$ m) copper layer. Warpage has been experimental characterized at different temperature by means of Phase-Shift Moiré principle, according to different annealing profiles. A linear Finite Element Model (FEM) has been developed to predict the geometrically stress-curvature relation, comparing results with analytical models.

Keywords: Semiconductor  $\cdot$  FEM  $\cdot$  Phase-Shift Moiré  $\cdot$  ECD  $\cdot$  Warpage

## 1 Introduction

Thick film copper on silicon substrate is one of the major challenges in the semiconductor industry because of its excellent electrical and thermal conductivity. Compared to other materials, such as aluminum, these features allow respectively to reduce the Joule effect and help the efficient dissipation of heat generated during operation. Furthermore, Cu metallization is better than aluminum in terms of resistance to electromigration and stress voiding phenomena. The main technique to produce thick copper film on silicon substrate is electrochemical deposition (ECD), which is a highly efficient wet process for depositing a uniform layer of metal (like copper) on a semiconductor wafer. Furthermore, Cu front metal is very attractive for integrated circuit (IC) manufacturing because it enables high-reliable Cu-Cu wire bonding solution [1]. The integration of Cu into ICs is still a technical challenge due to the severe wafer warpage induced by Cu annealing, which affects the accuracy of the subsequent manufacturing processes, such as the wafer handle and the adsorption of vacuum suction cup, having also a negative impact on

device reliability. Wafer warpage caused by thick Cu layer is mostly due to plastic deformation during the annealing [2], which is a thermal process aimed to make softer Cu compound, increasing and then stabilizing the Cu grains dimension. Stabilizing metal grain size, annealing permits to avoid electromigration issues in interconnect reliability, e.g. during reliability application-related test [3, 4]. It seems to miss in literature a detailed experimental warpage analysis for thick Cu layer: available data refer about maximum 5  $\mu$ m thick Cu metal. For what concerns analytical models, Stoney equation [5] have been commonly used as reference. This formula has been developed for "membranelike" geometries made by two materials, such as the system made by semiconductor wafer and ECD metal, in which one layer (in our case, ECD Cu) is much thinner than other. However due to complex not-linear Cu behavior during annealing, Stoney results are not reliable to predict stress and warpage during annealing. The scope of this work is to characterize the warpage induced by 20 µm thick Cu film on a rectangular wafer slice, considering two different annealing profiles. A Finite Element Model (FEM) has been developed to predict the geometrically stress-curvature relation inside the elastic regime. Numerical outcomes have been compared with the results of Stoney and Timoshenko equations.

### 2 Sample and Test Description

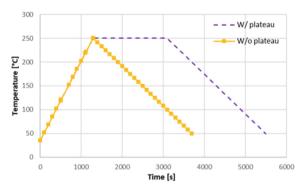

The considered samples for warpage analysis were  $50 \times 10 \times 0.75$  mm beam, made by bulk Silicon 730 µm-thick, TiW 0.3 µm, Cu seed 0.2 µm and ECD Copper 20 µmthick. These portions have been sliced from wafer just after copper electro-deposition at room temperature, therefore copper has not been thermally treated before samples formation. The slices have been annealed following two different temperature profile, shown in Fig. 1. The ramps have been characterized by fixed heating and cooling rate (respectively 10 and 5 °C/min), maximum temperature of 250°C. The only difference between profiles is the presence in profile "W/ plateau" of a period of 30 min in which temperature is fixed at 250 °C. Profile "W/o plateau" has been repeated three times to investigate on hysteretic behavior after the first cycle.

Fig. 1. Temperature profile considered for annealing the samples and measuring the warpage in temperature.

Warpage has been measured continuously during the annealing, according to methodology explained in following paragraph. Due to simple geometrical considerations, beam curvature has been derived from warpage and compared with the calculated by Finite Element Model in linear elastic regime.

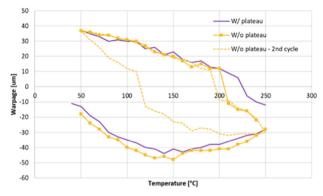

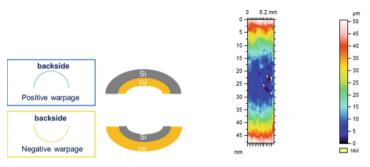

#### **3** Warpage Measurements

A method based on Moirè Phase Shift has been considered to experimentally quantify the warpage, using the commercial equipment "TDM Compact" by Insidix [6]. The sample to be analyzed is illuminated by a structured light made by stripe pattern. The stripe pattern is deformed by the sample's surface structure and the resulting image is captured by a CCD camera, that correlates the out-of-plane deformation with the xy coordinates. The desired temperature profiles have been reproduced during warpage measurement, heating sample by the infrared heater and cooling with compressed air. More detailed method explanation has been proposed in [7, 9]. Warpage has been monitored in temperature, according to thermal profiles described in Sect. 2. It has been plotted in Fig. 2, following the sign convention declared in Fig. 3.

**Fig. 2.** Measured warpage during temperature profiles. Negative values are reached during the heating, while positive ones during the cooling phase. Dotted line represents the warpage vs temperature profile occurred during a second temperature cycle.

Analysis has highlighted that annealing process modifies warpage at 50 °C in both temperature profiles. Warpage is ~  $-10 \ \mu$ m at the start, whereas it becomes ~ + 35  $\mu$ m at the end of first cycle. Looking to the second cycle, warpage behaves as a closed loop because there is no warpage modification between the start and the end of cycle. It has been observed the first part of warpage-temperature diagram in the second cycle (between 50 and 90 °C) has a linear trend. The incremental ratio between warpage variation and temperature in this range has been considered to benchmark the different warpage calculation methods presented in following paragraph. The warpage trend in temperature during the heating phase shows a change in slope that occurs at 150 °C, at which warpage reaches its maximum. This observed behavior could indicate an irreversible in copper layer: dedicated physical analysis will help to better understand the phenomenology.

Fig. 3. Sign convention for warpage and warpage map at 150 °C.

## 4 Finite Element Model

A Finite Element Model has been developed with Comsol Multiphysics to calculate the warpage variation, curvature and mechanical stress due to temperature variation. Material properties, reported in Table 1, have been taken from on-line archive Matweb [10], excepting for Young Modulus of copper layer, which has been derivate multiplying the Indentation Modulus  $E_{IT}$ , measured by nanoindentation, for factor  $1-\nu^2$ . It has been assumed material behavior as elastic, neglecting the properties temperature dependence.

| Material     | Young Modulus [GPa] | CTE [ppm/K] | Poisson ratio |

|--------------|---------------------|-------------|---------------|

| Silicon [10] | 120                 | 2.5         | 0.28          |

| Copper [10]  | 77.5                | 16.4        | 0.364         |

Table 1. Considered material data for simulation.

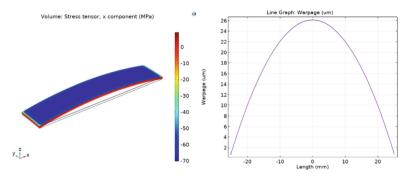

Linear elastic warpage and stress behavior has been calculated with the customized FE model and two different literature approaches. One is derived from the Timoshenko theory for bi-metal thermostats [8] and the other is the Stoney equation [5], to calculate thermal warpage in thin film. Warpage results have been benchmarked with experimental warpage observed in the second cycle during the first heating phase (50–90 °C). Stress along x direction and warpage variation in temperature range 50–90 °C have been calculated with FEM, considering the system stress and strain free at 50 °C. The results, shown in Fig. 4, have highlighted stress is uniformed distributed on the strip, compressive on copper side due to positive temperature variation. Warpage is correlated by means of a parabolic law with strip length.

The comparison between warpage and stress variation coming from considered methods has been resumed in Table 2. FEM warpage is the closest with measurements and underestimates the experimental behavior of about 6%. Comparing between them the calculation methods, FEM predicts the highest warpage and highest stress.

59

Fig. 4. Direction x-stress component and warpage on z-direction computed by FEM

Table 2. Benchmark between experiments, FE model and literature analytical approach.

| Method             | Experimental | FEM   | Timoshenko | Stoney |

|--------------------|--------------|-------|------------|--------|

| Warpage<br>[µm/°C] | 0.700        | 0.660 | 0.605      | 0.632  |

| Stress<br>[MPa/°C] | n.a.         | 1.683 | 1.003      | 1.075  |

#### 5 Conclusions

In this work, it has been studied the evolution of the deformation during the annealing process of ECD thick copper film (20  $\mu$ m), measuring at different temperature the warpage of a wafer slice by means of dedicated optical technique. Analyses have shown an irreversible strain at a reference temperature (50 °C) induced by the first heating cycle. Plateau has not affected the residual warpage. The deformation in elastic regime has been reproduced with a preliminary linear FE model, which is a starting point to develop a more complete model to predict ECD warpage during entire annealing profile, considering the involved not-linearities and correlating it with further physical analysis dedicated to address the involved phenomenology.

#### References

- Mancaleoni, A., et al.: Copper wire bonding process characterization and simulation. In: CIPS 2020; 11th International Conference on Integrated Power Electronics Systems. VDE, 2020

- Cheng, G., Xu, G., Gai, W., Luo, L.: Influence of observed anelasticity of Cu on the wafer warpage evolution during thermal processes. In: 2018 19th International Conference on Electronic Packaging Technology (ICEPT), pp. 1119–1122. IEEE, August 2018

- Russo, S., Bazzano, G., Cavallaro, D., Sitta, A., Calabretta, M.: Thermal analysis approach for predicting power device lifetime. IEEE Trans. Device Mater. Reliab. 19(1), 159–163 (2019)

- Sitta, A., Russo, S., Bazzano, G., Cavallaro, D., Greco, G., Calabretta, M.: Numerical approach to predict power device reliability. In: 2018 13th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), pp. 1–5. IEEE, April 2018

- Stoney, G.G.: The tension of metallic films deposited by electrolysis. In: Proceedings of the Royal Society of London. Series A, Containing Papers of a Mathematical and Physical Character, vol. 82, no. 553, pp. 172–175 (1909)

- Weidmann, D., Dubois, G., Hertl, M., Chauffleur, X.: Determination of strength of interface in packages based on an approach using coupling of experimental and modeling results. In: 2011 12th International Conference on Thermal, Mechanical & Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, pp. 1–6. IEEE, April 2011

- Calabretta, M., Sitta, A., Oliveri, S.M., Sequenzia, G.: An integrated approach to optimize power device performances by means of stress engineering. In: International Conference on Design, Simulation, Manufacturing: The Innovation Exchange, pp. 481–491. Springer, Cham, September, 2019

- 8. Timoshenko, S.: Analysis of bi-metal thermostats. Josa 11(3), 233–255 (1925)

- Mirone, G., Sitta, A., D'Arrigo, G., Calabretta, M.: Material characterization and warpage modeling for power devices active metal brazed substrates. IEEE Trans. Device Mater. Reliab. 19(3), 537–542 (2019)

- 10. Matweb, Material Property Data. www.matweb.com. Accessed 21 April 2020

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.