Sandra Wienke Sridutt Bhalachandra (Eds.)

# Accelerator Programming Using Directives

6th International Workshop, WACCPD 2019 Denver, CO, USA, November 18, 2019 Revised Selected Papers

# Lecture Notes in Computer Science

# 12017

#### Founding Editors

Gerhard Goos Karlsruhe Institute of Technology, Karlsruhe, Germany Juris Hartmanis Cornell University, Ithaca, NY, USA

#### Editorial Board Members

Elisa Bertino Purdue University, West Lafayette, IN, USA Wen Gao Peking University, Beijing, China Bernhard Steffen TU Dortmund University, Dortmund, Germany Gerhard Woeginger RWTH Aachen, Aachen, Germany Moti Yung Columbia University, New York, NY, USA More information about this series at http://www.springer.com/series/7408

# Accelerator Programming Using Directives

6th International Workshop, WACCPD 2019 Denver, CO, USA, November 18, 2019 Revised Selected Papers

*Editors* Sandra Wienke D RWTH Aachen University Aachen, Germany

Sridutt Bhalachandra D Lawrence Berkeley National Laboratory Berkeley, CA, USA

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-030-49942-6 ISBN 978-3-030-49943-3 (eBook) https://doi.org/10.1007/978-3-030-49943-3

LNCS Sublibrary: SL2 - Programming and Software Engineering

#### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

The ever-increasing heterogeneity in supercomputing applications has given rise to complex compute node architectures offering multiple, heterogeneous levels of massive parallelism. As a result, the 'X' in MPI+X demands more focus. Exploiting the maximum available parallelism out of such systems necessitates sophisticated programming approaches that can provide scalable as well as portable solutions without compromising on performance. A programmer's expectation from the scientific community is to deliver solutions that would allow maintenance of a single code base whenever possible avoiding duplicate effort.

Raising the abstraction of the code is one of the effective methodologies to reduce the burden on the programmer while improving productivity. Software abstraction-based programming models, such as OpenMP and OpenACC, have been serving this purpose over the past several years as the compiler technology steadily improves. These programming models address the 'X' component by providing programmers with high-level directive-based approaches to accelerate and port scientific applications to heterogeneous platforms.

These proceedings contain the papers accepted for presentation at the 6th Workshop on Accelerator Programming using Directives (WACCPD 2019) – http://waccpd.org/. WACCPD is one of the major forums for bringing together users, developers, and the software and tools community to share knowledge and experiences when programming emerging complex parallel computing systems.

Recent architectural trends indicate a heavy reliance of future exascale machines on accelerators for performance. Toward this end, the workshop highlighted improvements to the state of the art through the accepted papers and prompted discussion through keynotes/panels that drew the community's attention to key areas that will facilitate the transition to accelerator-based high-performance computing (HPC). The workshop aimed to showcase all aspects of heterogeneous systems discussing innovative high-level language features, lessons learned while using directives to migrate scientific legacy code to parallel processors, compilation and runtime scheduling techniques, among others.

The WACCPD 2019 workshop received 13 submissions out of which 7 were accepted to be presented at the workshop and published in these proceedings. The Program Committee of the workshop comprised 24 members spanning universities, national laboratories, and industries. Each paper received an average of five reviews.

For 2019, we encouraged all authors to add the Artifact Description (AD) to their submissions. Two additional pages were made available to authors (however without obligations) to make their code and data publicly available (e.g. on GitHub, Zenodo, Code Ocean, etc.) in support of the reproducibility initiative. As a further push, only papers with AD were considered for the Best Paper Award.

Of the 7 accepted papers, 86% had reproducibility information and these manuscripts are highlighted with an 'artifacts available' logo in this book.

The program co-chairs invited Dr. Nicholas James Wright from Lawrence Berkeley National Laboratory (LBL) to give a keynote address on "Perlmutter – A 2020 Pre-Exascale GPU-accelerated System for NERSC: Architecture and Application Performance Optimization." Dr. Nicholas J. Wright is the Perlmutter chief architect and the Advanced Technologies Group lead in the National Energy Research Scientific Computing (NERSC) center at LBL. He led the effort to optimize the architecture of the Perlmutter machine, the first NERSC platform designed to meet the needs of both large-scale simulation and data analysis from experimental facilities. Nicholas has a PhD from the University of Durham in computational chemistry and has been with NERSC since 2009.

Robert Henschel from Indiana University gave an invited talk titled "The SPEC ACCEL Benchmark – Results and Lessons Learned." Robert Henschel is the director of Research Software and Solutions at Indiana University. He is responsible for providing advanced scientific applications to researchers at Indiana University and national partners as well as providing support for computational research to the Indiana University School of Medicine. Henschel serves as the chair of the Standard Performance Evaluation Corporation (SPEC) High-Performance Group and in this role leads the development of production quality benchmarks for HPC systems. He also serves as the treasurer of the OpenACC organization. Henschel has a deep background in HPC and his research interests focus on performance analysis of parallel applications.

The workshop concluded with a panel "Convergence, Divergence, or New Approaches? – The Future of Software-Based Abstractions for Heterogeneous Supercomputing" moderated by Fernanda Foertter from NVIDIA. The panelists included:

- Christian Trott, Sandia National Laboratories, USA

- Michael Wolfe, Nvidia, USA

- Jack Deslippe, Lawrence Berkeley National Laboratory, USA

- Jeff Hammond, Intel, USA

- Johannes Doerfert, Argonne National Laboratory, USA

Based on rigorous reviews and ranking scores of all papers reviewed, the following paper won the Best Paper Award. The authors of the Best Paper Award also included reproducibility results to their paper, which the WACCPD workshop organizers had indicated as a criteria to be eligible to compete for the Best Paper Award.

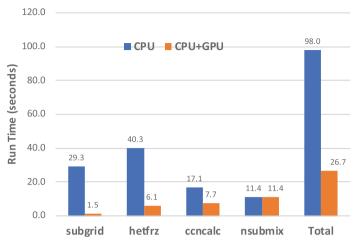

Hongzhang Shan and Zhengji Zhao from Lawrence Berkeley National Laboratory, and Marcus Wagner from Cray: "Accelerating the Performance of Modal Aerosol Module of E3SM Using OpenACC"

Emphasizing the importance of using directives for legacy scientific applications, each keynote/invited speakers, panelists, and Best Paper Award winners were given a book on "OpenACC for Programmers: Concepts & Strategies."

April 2020

Sandra Wienke Sridutt Bhalachandra

# Organization

### **Steering Committee**

| Barbara Chapman | Stony Brook, USA              |

|-----------------|-------------------------------|

| Duncan Poole    | OpenACC, USA                  |

| Kuan-Ching Li   | Providence University, Taiwan |

| Oscar Hernandez | ORNL, USA                     |

| Jeffrey Vetter  | ORNL, USA                     |

|                 |                               |

# **Program Co-chairs**

| Sandra Wienke        | RWTH Aachen University, Germany            |

|----------------------|--------------------------------------------|

| Sridutt Bhalachandra | Lawrence Berkeley National Laboratory, USA |

#### **Publicity Chair**

| Neelima Bayyapu | NMAM Institute of Technology, Karnataka, India |

|-----------------|------------------------------------------------|

| Web Chair       |                                                |

| Shu-Mei Tseng   | University of California, Irvine, USA          |

## **Program Committee**

| Edinburgh Parallel Computing Centre,<br>University of Edinburgh, UK |  |  |  |

|---------------------------------------------------------------------|--|--|--|

| Forschungszentrum Jülich, Germany                                   |  |  |  |

| Google, USA                                                         |  |  |  |

| Microsoft, USA                                                      |  |  |  |

| Technische Universität Darmstadt, Germany                           |  |  |  |

| RWTH Aachen University, Germany                                     |  |  |  |

| Lawrence Berkeley National Laboratory, USA                          |  |  |  |

| NVIDIA, USA                                                         |  |  |  |

| Oak Ridge National Laboratory, USA                                  |  |  |  |

| Giuseppe Congiu Argonne National Laboratory, USA                    |  |  |  |

| NASA Ames Research Center, USA                                      |  |  |  |

| NVIDIA, USA                                                         |  |  |  |

| IBM, USA                                                            |  |  |  |

| Intel, USA                                                          |  |  |  |

| NVIDIA/PGI, USA                                                     |  |  |  |

| Indiana University, USA                                             |  |  |  |

| AMD, USA                                                            |  |  |  |

|                                                                     |  |  |  |

| Ronan Keryell   | Xilinx, USA                                       |

|-----------------|---------------------------------------------------|

| Seyong Lee      | Oak Ridge National Laboratory, USA                |

| Simon Hammond   | Sandia National Laboratories, USA                 |

| Sameer Shende   | University of Oregon, USA                         |

| Thomas Schwinge | Mentor Graphics, Germany                          |

| Tom Scogland    | Lawrence Livermore National Laboratory, USA       |

| William Sawyer  | Swiss National Supercomputing Centre, Switzerland |

Held in conjunction with the International Conference for High Performance Computing, Networking, Storage and Analysis (SC 2019), Denver, USA:

## Contents

#### **Porting Scientific Applications to Heterogeneous Architectures Using Directives**

| GPU Implementation of a Sophisticated Implicit Low-Order Finite Element<br>Solver with FP21-32-64 Computation Using OpenACC<br>Takuma Yamaguchi, Kohei Fujita, Tsuyoshi Ichimura, Akira Naruse,<br>Maddegedara Lalith, and Muneo Hori | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Acceleration in Acoustic Wave Propagation Modelling Using<br>OpenACC/OpenMP and Its Hybrid for the Global Monitoring System<br>Noriyuki Kushida, Ying-Tsong Lin, Peter Nielsen, and Ronan Le Bras                                     | 25 |

| Accelerating the Performance of Modal Aerosol Module of E3SM<br>Using OpenACC.<br>Hongzhang Shan, Zhengji Zhao, and Marcus Wagner                                                                                                     | 47 |

| Evaluation of Directive-Based GPU Programming Models on a Block<br>Eigensolver with Consideration of Large Sparse Matrices                                                                                                            | 66 |

#### **Directive-Based Programming for Math Libraries**

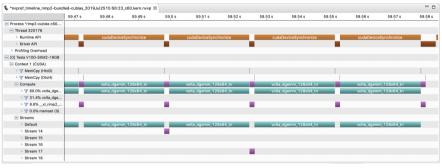

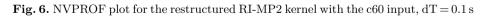

| Performance of the RI-MP2 Fortran   | Kernel of GAMESS on GPUs                   |    |

|-------------------------------------|--------------------------------------------|----|

| via Directive-Based Offloading with | Kernel of GAMESS on GPUs<br>Math Libraries | 91 |

| JaeHyuk Kwack, Colleen Bertoni,     | , Buu Pham, and Jeff Larkin                |    |

#### Performance Portability for Heterogeneous Architectures

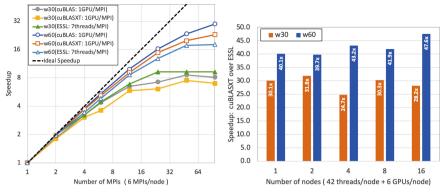

| Performance Portable Implementation of a Kinetic Plasma Simulation<br>Mini-App.                                                                                  | 117 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Yuuichi Asahi, Guillaume Latu, Virginie Grandgirard, and Julien Bigot                                                                                            | 117 |

| A Portable SIMD Primitive Using Kokkos for Heterogeneous Architectures<br>Damodar Sahasrabudhe, Eric T. Phipps, Sivasankaran Rajamanickam,<br>and Martin Berzins | 140 |

| Author Index                                                                                                                                                     | 165 |

# Porting Scientific Applications to Heterogeneous Architectures Using Directives

# GPU Implementation of a Sophisticated Implicit Low-Order Finite Element Solver with FP21-32-64 Computation Using OpenACC

Takuma Yamaguchi<sup>1( $\boxtimes$ )</sup>, Kohei Fujita<sup>1,2</sup>, Tsuyoshi Ichimura<sup>1</sup>, Akira Naruse<sup>3</sup>, Maddegedara Lalith<sup>1</sup>, and Muneo Hori<sup>4</sup>

<sup>1</sup> The University of Tokyo, Yayoi, Bunkyo, Tokyo, Japan

<sup>2</sup> Center for Computational Science, RIKEN, Minatojima-minamimachi, Chuo, Kobe, Japan {yamaguchi,fujita,ichimura,lalith}@eri.u-tokyo.ac.jp <sup>3</sup> NVIDIA Corporation, Akasaka, Minato, Tokyo, Japan anaruse@nvidia.com

Japan Agency for Marine-Earth Science and Technology, Kanazawa, Yokohama, Kanagawa, Japan

horimune@jamstec.go.jp

4

Abstract. Accelerating applications with portability and maintainability is one of the big challenges in science and engineering. Previously, we have developed a fast implicit low-order three-dimensional finite element solver, which has a complicated algorithm including artificial intelligence and transprecision computing. In addition, all possible tunings for the target architecture were implemented; accordingly, the solver has inferior portability and maintainability. In this paper, we apply OpenACC to the solver. The directive-based implementation of OpenACC enables GPU computation to be introduced with a smaller developmental cost even for complex codes. In performance measurements on AI Bridging Cloud Infrastructure (ABCI), we evaluated that a reasonable speedup was attained on GPUs, given that the elapsed time of the entire solver was reduced to 1/14 of that on CPUs based on the original CPU implementation. Our proposed template to use transprecision computing with our custom FP21 data type is available to the public; therefore, it can provide a successful example for other scientific computing applications.

**Keywords:** OpenACC · Finite element analysis · Conjugate gradient solver · Transprecision computing · Lower-Precision data types

#### 1 Introduction

Nowadays, computer architectures are becoming increasingly diverse and new hardware, including heterogeneous systems, is released every year. Software

Electronic supplementary material The online version of this chapter (https://doi.org/10.1007/978-3-030-49943-3\_1) contains supplementary material, which is available to authorized users.

© Springer Nature Switzerland AG 2020

S. Wienke and S. Bhalachandra (Eds.): WACCPD 2019, LNCS 12017, pp. 3–24, 2020. https://doi.org/10.1007/978-3-030-49943-3\_1 needs to keep up with this rapid development of hardware. Unfortunately, developing codes for every type of architecture leads to huge developmental costs. In addition, handling all the maintenance in such a case becomes increasingly difficult. These two factors in particular have a marked influence on sophisticated algorithms, which leads to long lines of codes.

Reflecting this situation, OpenACC [20] is in widespread use. OpenACC is a programming model that offloads computations onto GPUs or multi-core CPUs by inserting a few directives. Reference [3] demonstrated that simple codes can easily be ported using OpenACC. For various scientific applications, porting more complex algorithms to GPUs using OpenACC can be a successful example.

In this paper, we target a finite element analysis. We use implicit time integration for stability and low-order elements for complicated geometries; therefore, the code tends to be complex and the performance decreases due to random memory accesses. This analysis is regarded as a de-facto standard for manufacturing and Earth sciences; therefore, its acceleration is beneficial to these fields. We demonstrated in WACCPD 2016 [5] and WACCPD 2017 [25] that finite element solvers designed for CPU-based computers can be ported using OpenACC and that such ported solvers exhibit reasonable performances.

Meanwhile, a solver extremely tuned for better performance on GPU-based supercomputers was proposed [8]. Hereafter, we refer to this solver as the SC18-GBF solver. It has a sophisticated algorithm including artificial intelligence (AI) and transprecision computing with lower-precision data types. Moreover, its performance is thoroughly optimized when using specialized hardware in the targeted architecture, e.g., two-way packed half-precision computations on NVIDIA Tesla V100 GPUs [19]. Therefore, the developed code lacks portability and maintainability.

We apply OpenACC to the SC18GBF solver to improve its compatibility for portability and its performance. We show that our target application achieves a reasonable speedup with a smaller developmental cost in a directive-based method even though our solver includes a non-standard data type. Our sample codes to use the lower-precision data type FP21 are available to the public [26]; thus, it could prove beneficial to other scientific computing applications.

The remainder of this paper is organized as follows. Section 2 describes the baseline solver on CPU-based computers, and Sect. 3 describes the GPU implementation with FP21-32-64 data types using OpenACC. In Sect. 4, we show the effectiveness of our proposed method via performance measurements on AI Bridging Cloud Infrastructure (ABCI). In addition, we show an application example on the supercomputer Summit. Section 5 provides our conclusions.

#### 2 Baseline Solver on CPU-based Computers

In this paper, we target a low-order unstructured implicit finite element method used for solving complex shaped three-dimensional (3D) domains. When solving this type of problem, solver programs often become complex due to the use of sophisticated preconditioners in iterative solvers. Further, it is difficult to attain a good computational performance because the computation of unstructured elements requires a large amount of random memory accesses. The target SC18GBF solver is further complicated compared to standard solvers due to its use of AI and transprecision arithmetic in its preconditioner. Below we pose the target problem and explain the solver algorithm and its CPU implementation.

#### 2.1 The Target Problem

Earthquake simulations involve large-domain nonlinear time-evolution problems with locally complex structures. Therefore, we solve the target dynamic nonlinear continuum mechanics problem using a nonlinear dynamic 3D finite element method with second-order tetrahedral elements because such a method is suitable for modeling complex geometries and analytically satisfies the traction-free boundary condition at the surface. The target equation using the Newmark- $\beta$ method ( $\beta = 1/4$ ,  $\delta = 1/2$ ) for time integration is

$$\mathbf{A}_n \ \delta \mathbf{u}_n = \mathbf{b}_n, \tag{1}$$

where

$$\begin{cases} \mathbf{A}_n = \frac{4}{dt^2} \mathbf{M} + \frac{2}{dt} \mathbf{C}_n + \mathbf{K}_n, \\ \mathbf{b}_n = \mathbf{f}_n - \mathbf{q}_{n-1} + \mathbf{C}_n \mathbf{v}_{n-1} + \mathbf{M} \left( \mathbf{a}_{n-1} + \frac{4}{dt} \mathbf{v}_{n-1} \right). \end{cases}$$

Here,  $\delta \mathbf{u}$ ,  $\mathbf{u}$ ,  $\mathbf{v}$ ,  $\mathbf{a}$ ,  $\mathbf{q}$ , and  $\mathbf{f}$  are the incremental displacement, displacement, velocity, acceleration, internal force, and external force vectors, respectively,  $\mathbf{M}$ ,  $\mathbf{C}$ , and  $\mathbf{K}$  are the consistent mass, damping, and stiffness matrices, respectively, dt is the time increment, and n is the time step. We use Rayleigh damping [1] for  $\mathbf{C}$ . After solving Eq. 1,  $\mathbf{q}$ ,  $\mathbf{u}$ ,  $\mathbf{v}$ , and  $\mathbf{a}$  are updated using

$$\begin{cases} \mathbf{q}_{n} = \mathbf{q}_{n-1} + \mathbf{K}_{n} \delta \mathbf{u}_{n}, \\ \mathbf{u}_{n} = \mathbf{u}_{n-1} + \delta \mathbf{u}_{n}, \\ \mathbf{v}_{n} = -\mathbf{v}_{n-1} + \frac{2}{dt} \delta \mathbf{u}_{n}, \\ \mathbf{a}_{n} = -\mathbf{a}_{n-1} - \frac{4}{dt} \mathbf{v}_{n-1} + \frac{4}{dt^{2}} \delta \mathbf{u}_{n}. \end{cases}$$

(2)

In summary, the time-history response  $\mathbf{u}^n$  is computed by repeating the following steps.

- 1. Read the boundary conditions.

- 2. Evaluate  $\mathbf{C}_n$  and  $\mathbf{K}_n$  based on the constitutive relationships and the strain at the time step n-1.

- 3. Obtain  $\delta \mathbf{u}_n$  by solving Eq. 1.

- 4. Update Eq. 2 using  $\delta \mathbf{u}_n$ .

Because most of the computational cost is incurred when solving Eq. 1, we explain the details of the linear equation solver in the next subsection.

#### 2.2 The Solver Algorithm

Although it is sparse, the symmetric positive definite matrix **A** in Eq. 1 becomes large in scale. Therefore, it is difficult to store **A** or variants of **A** directly in fast memory; consequently, matrix-free matrix-vector products are often used in iterative solvers for solving Eq. 1. For example, the PCGE method, which combines a matrix-free matrix-vector product [24] with  $3 \times 3$  block diagonal preconditioned conjugate gradient solver is often used. This method solves the entire target domain uniformly in double precision and, therefore, is robust for solving a wide range of problems. However, its convergence rate is often slow, which makes it computationally expensive. The efficiency of the conjugate gradient solver is improved in the SC18GBF solver by changing the intensity of the computation according to the mathematical properties of the target problem and, further, by using AI methods considering the convergence characteristics. Below, we explain the solver algorithm in detail following Algorithm 1.

1. Use of an adaptive conjugate gradient method

We first use an adaptive conjugate gradient method [6]. Instead of using a fixed matrix approximating the inverse matrix  $\mathbf{A}^{-1}$  in the preconditioner of each conjugate gradient iteration, the preconditioning equation  $\mathbf{z} = \mathbf{A}\mathbf{r}$  is solved using another conjugate gradient solver. We refer to the solving of the preconditioning equation as the inner iteration (Algorithm 1, lines 5–17), while we refer to the original conjugate gradient iteration as the outer iteration (Algorithm 1, lines 18–28). By setting suitable thresholds for the tolerances of the preconditioning solvers, we can shift most of the computational cost to the inner iterations. Because the preconditioning equation only needs to be roughly solved, this allows for flexibility in the algorithm design combining different methods with varying accuracies and computational costs in the preconditioner.

2. Use of AI in a preconditioner

Data analytics exemplified by AI is often faster in inference than equationbased methods; however, its accuracy is often not as high [11]. Therefore, the direct use of data analytics in equation-based methods may lead to a degradation of the accuracy of the result or a divergence in the solution. Therefore, to use AI in linear equation solvers, an algorithm design considering the solver robustness is required. Here we focus on the heterogeneity of the convergence characteristics of a target matrix  $\mathbf{A}$ ; that is, we develop a preconditioner algorithm that can coarsen or refine the solving process according to the convergence characteristics. Using this approach, even if the inference of the convergence characteristics is not perfectly accurate, it is only used in the preconditioner; therefore, the robustness of the solver and the accuracy of the solution are maintained and only the computational performance is affected.

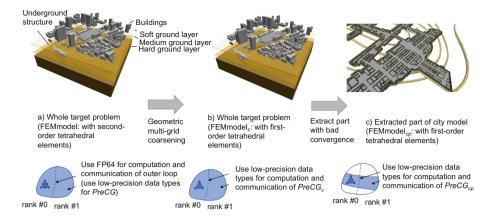

First, in preparation for the training with AI, we uniformly coarsen the target second-order tetrahedral finite element model (FEMmodel shown in Fig. 1a)

Algorithm 1. SC18GBF solver algorithm for solving  $\mathbf{A}\mathbf{x} = \mathbf{b}$  on FEMmodel. The matrix vector product  $\mathbf{A}\mathbf{y} = (\frac{4}{dt^2}\mathbf{M} + \frac{2}{dt}\mathbf{C} + \mathbf{K})\mathbf{y}$  is computed using matrixfree matrix-vector products (i.e., element-by-element method):  $\sum_{i}^{N}(\frac{4}{dt^2}\mathbf{M}_i + \frac{2}{dt}\mathbf{C}_i + \mathbf{K}_i)\mathbf{y}_i$ , where dt is the time increment,  $\mathbf{M}$ ,  $\mathbf{C}$ , and  $\mathbf{K}$  are the consistent mass, damping, and stiffness matrices, respectively, and subscript i indicates the i-th element.  $diag[\]$ , (<sup>-</sup>), and  $\epsilon$  indicate the  $3\times 3$  block Jacobi of [\], singleprecision variable, and tolerance for relative error, respectively. ( $)_c$  and ( $)_{cp}$ indicates the calculation related to FEMmodel<sub>c</sub> and FEMmodel<sub>cp</sub>, respectively, while the other is the related calculation of the FEMmodel.  $\mathbf{P}$  is a mapping matrix, from FEMmodel<sub>c</sub> to FEMmodel, which is defined by interpolating the displacement in each element of FEMmodel<sub>c</sub>.  $\mathbf{p}$ ,  $\mathbf{q}$ ,  $\mathbf{r}$ , and  $\mathbf{z}$  are temporal vectors and  $\alpha$ ,  $\beta$ , and  $\rho$  are scalars in conjugate gradient method and i denotes the number of iteration.

1:  $\mathbf{r} \leftarrow \mathbf{b} - \mathbf{A}\mathbf{x}$ , where  $\mathbf{x}$  is initial solution 2:  $\beta \Leftarrow 0, i \Leftarrow 1$ 3: (\* outer loop start \*) 4: while  $\|\mathbf{r}\|_2 / \|\mathbf{b}\|_2 \ge \epsilon$  do (\* inner loop start \*) 5: 6:  $\bar{\mathbf{r}} \Leftarrow \mathbf{r}$  $\bar{\mathbf{z}} \Leftarrow diaq[\mathbf{A}]^{-1}\mathbf{r}$ 7:  $\bar{\mathbf{r}}_c \Leftarrow \bar{\mathbf{P}}^T \bar{\mathbf{r}}$ 8:  $\bar{\mathbf{z}}_c \Leftarrow \bar{\mathbf{P}}^T \bar{\mathbf{z}}$ 9: Solve  $\bar{\mathbf{r}}_c = \bar{\mathbf{A}}_c \bar{\mathbf{z}}_c$  (\* *PreCG<sub>c</sub>*: solved on FEMmodel<sub>c</sub> by PCGE with  $\epsilon_c^{in}$  and 10: initial solution  $\bar{\mathbf{z}}_c$  \*) Extract  $\bar{\mathbf{z}}_{cp}$  from  $\bar{\mathbf{z}}_c$  and  $\bar{\mathbf{r}}_{cp}$  from  $\bar{\mathbf{r}}_c$ 11: Solve  $\bar{\mathbf{r}}_{cp} = \bar{\mathbf{A}}_{cp} \bar{\mathbf{z}}_{cp}$  (\*  $PreCG_{cp}$ : solved on FEMmodel<sub>cp</sub> by PCGE with  $\epsilon_{cp}^{in}$  and 12:initial solution  $\bar{\mathbf{z}}_{cp}$  with Dirichlet boundary condition of  $\bar{\mathbf{z}}_c$  at boundary \*) Update  $\bar{\mathbf{z}}_c$  with  $\bar{\mathbf{z}}_{cp}$ 13:14: $\bar{\mathbf{z}} \Leftarrow \mathbf{P} \bar{\mathbf{z}}_c$ Solve  $\bar{\mathbf{r}} = \bar{\mathbf{A}}\bar{\mathbf{z}}$  (\* *PreCG*: solved on FEMmodel by PCGE with  $\epsilon^{in}$  and initial 15:solution  $\bar{\mathbf{z}}^{*}$ ) 16: $\mathbf{z} \Leftarrow \bar{\mathbf{z}}$ (\* inner loop end \*) 17:18:if i > 1 then 19: $\beta \Leftarrow (\mathbf{z}, \mathbf{q}) / \rho$ end if 20:21: $\mathbf{p} \Leftarrow \mathbf{z} + \beta \mathbf{p}$ 22: $\mathbf{q} \leftarrow \mathbf{A}\mathbf{p}$  (\* computed by matrix-free matrix-vector multiplication \*) 23: $\rho \Leftarrow (\mathbf{z}, \mathbf{r})$  $\alpha \Leftarrow \rho/(\mathbf{p}, \mathbf{q})$ 24:25: $\mathbf{q} \Leftarrow -\alpha \mathbf{q}$ 26: $\mathbf{r} \Leftarrow \mathbf{r} + \mathbf{q}$ 27: $\mathbf{x} \Leftarrow \mathbf{x} + \alpha \mathbf{p}$  $i \Leftarrow i + 1$ 28:29: end while 30: (\* outer loop end \*)

Algorithm 2. Standard time-integration algorithm for solving  $\mathbf{A}_i \mathbf{x}_i = \mathbf{b}_i (i = 0, ..., n-1)$ . Values with over bars (<sup>-</sup>) indicate approximate values, while values without over bars indicate exact values.

- 1: Set  $\mathbf{x}_{-1} \Leftarrow 0$

- 2: for i = 0; i < n; i = i + 1 do

- 3: Guess  $\bar{\mathbf{x}}_i$  using standard predictor

- 4: Set  $\mathbf{A}_i$  and  $\mathbf{b}_i$  using  $\mathbf{x}_{i-1}$

- 5: Solve  $\mathbf{A}_i \mathbf{x}_i = \mathbf{b}_i$  with error tolerance  $\frac{|\mathbf{A}_i \mathbf{x}_i \mathbf{b}_i|}{|\mathbf{b}_i|} \leq \epsilon$  using initial solution  $\bar{\mathbf{x}}_i$ : Computed using iterative solver with matrix-free matrix-vector multiplication kernel (1 vector)

- 6: **end for**

**Algorithm 3.** Time-parallel time-integration algorithm for solving  $\mathbf{A}_i \mathbf{x}_i = \mathbf{b}_i (i = 0, ..., n - 1)$ . Values with over bars (<sup>-</sup>) indicate approximate values, while values without over bars indicate exact values. Algorithm 1 is used to solve m sets of linear systems of equations in line 9 in parallel.

1: Set  $\mathbf{x}_{-1} \leftarrow 0$  and  $\bar{\mathbf{x}}_i \leftarrow 0 (i = 0, ..., m - 2)$ 2: for i = 0; i < n; i = i + 1 do 3: Guess  $\bar{\mathbf{x}}_{i+m-1}$  using standard predictor Set  $\mathbf{A}_i$  and  $\mathbf{b}_i$  using  $\mathbf{x}_{i-1}$ 4: 5: $\mathbf{A}_i \Leftarrow \mathbf{A}_i$ 6:  $\mathbf{b}_i \Leftarrow \mathbf{b}_i$ while  $\frac{|\mathbf{A}_i \bar{\mathbf{x}}_i - \mathbf{b}_i|}{|\mathbf{b}_i|} > \epsilon$  do 7: 8: Guess  $\bar{\mathbf{A}}_j$  and  $\bar{\mathbf{b}}_j$  using  $\bar{\mathbf{x}}_{j-1}$  (j = i+1, ..., i+m-1)9: Refine solution  $\{\bar{\mathbf{A}}_i \bar{\mathbf{x}}_j = \bar{\mathbf{b}}_j\}$  with initial solution  $\bar{\mathbf{x}}_j (j = i, ..., i + m - 1)$ : Computed using iterative solver with matrix-free matrix-vector multiplication kernel (m vectors) end while 10:11:  $\mathbf{x}_i \Leftarrow \bar{\mathbf{x}}_i$ 12: end for

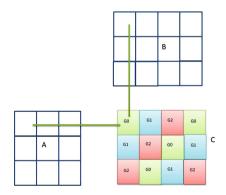

using a geometric multi-grid [21] to obtain a first-order tetrahedral finite element model (FEMmodel<sub>c</sub> shown in Fig. 1b). Next, we obtain the error history distribution of a small-scale problem with similar characteristics to the target large-scale problem using a standard PCGE solver. Using this error distribution data, we train an artificial neural network (ANN) that inputs mesh information at a target node (i.e., the element connectivity, material property, and element sizes) and outputs the level of error at that node. Using this ANN, we infer the error levels at each node of the large-scale target problem using the element connectivity, material property, and element size as input. The nodes that are guessed to have large error levels (i.e., bad convergence) are included in FEMmodel<sub>cp</sub>, as shown in Fig. 1c. We use a solver on FEMmodel<sub>cp</sub> (Algorithm 1, lines 11–13) to refine the rough solution obtained by the solver on the uniformly coarsened FEMmodel<sub>c</sub> (Algorithm 1, line 10) in the preconditioner.

Fig. 1. Extraction of part of the problem having bad convergence using AI.

Finally, we map this result to a second-order finite element model and use it as an initial solution for the solver on FEMmodel (Algorithm 1, line 15), and further use the results for the search direction z in the outer iteration.

By setting the tolerance of each preconditioning solver to a suitable value, we can solve parts of the problem with bad convergence extensively while solving most of the problem with good convergence less extensively. This leads to a reduction in the computational cost compared to a solver that solves the entire domain uniformly. Even if the selection of FEMmodel<sub>cp</sub> by ANN is slightly altered, the effects are absorbed by the other preconditioning solvers ( $PreCG_c$  and PreCG); therefore, the solver becomes highly robust.

The training and reference of the AI for extracting  $\text{FEMmodel}_{cp}$  are conducted offline using commercial neural network packages on a few GPUs, and are conducted only once prior to the time-history earthquake simulation.

3. Use of low-precision arithmetic in the preconditioner

While the solution of the entire solver is required in double precision, we can use transprecision computing [15] in the preconditioner because it is only used to obtain rough solutions. We can use not only FP32 but also other data types, such as FP21, which has an intermediate range and the accuracy of FP32 and FP16 to reduce the data transfer cost and the memory footprint. As mentioned later, all vectors can be in FP21 on CPUs while FP32 must be used for some vectors on GPUs. The introduction of FP21 data types in both CPU and GPU implementations makes maintenance of the entire code and performance evaluation more complex; thus, we use custom data type only in GPU implementation for simplicity.

4. Use of time-parallel time integration in the solver

Although AI with a transprecision-computing solver appears to be highly complicated, it is merely a combination of conjugate gradient-based solvers solved using simple PCGE methods. Therefore, the majority of its computational costs consist of matrix-vector products. However, because the computation of matrix-vector products becomes dominated by random memory accesses in unstructured finite element methods, it has become difficult to attain high performance on recent computational architectures regardless of the use of CPU or GPU. Using the fact that mesh connectivity is invariable in the time domain even for an unstructured finite element method, the SC18GBF solver uses a time-parallel time-integration algorithm [7] to improve the computational efficiency. In standard time integration, each step is solved step by step (Algorithm 2), while in the time-parallel solver, several steps, including future time steps, are solved simultaneously (Algorithm 3). When indicating the number of time steps solved simultaneously as m, the arithmetic count for computing a single iteration of the iterative solver becomes m times of that of a standard solver. However, the results obtained by the time-parallel solver can be used as high-precision initial solutions for future time steps; therefore, the total number of iterations is reduced by approximately 1/m. Accordingly, the total arithmetic count becomes approximately the same as that of a standard time-integration method. The advantage of using a time-parallel method is that random accesses are reduced by 1/mcompared to a standard solver by placing time-directional nodal variables consecutively in memory. This leads to the efficient use of single-instruction multiple-data (SIMD) units, which leads to a short time-to-solution for the entire solver. Typically, m = 4 is used because enlarging m leads to an increase in the total arithmetic count due to the degradation in the prediction accuracy of future time steps.

Because the approximated methods are only used in the preconditioner or are used to obtain the initial solutions of the iterative solver, the obtained solution  $\delta \mathbf{u}_i (i = 1, 2, ...)$  is same as that of the double-precision PCGE method within the solver error tolerance  $\epsilon$ . Further, because most of the computational cost is in matrix-vector products, we can maintain load balance by allocating an equal number of elements to each process/thread, which leads to high scalability for large-scale systems.

#### 2.3 Implementation of Solver for CPU Systems

Because the innermost loop of the solver becomes the length m = 4 with consecutive data accesses, the current algorithm can be implemented using packed SIMD units with width 4. Furthermore, for systems with AVX-512 instruction units, loop blocking and splitting are applied for use of the 8-wide FP64 and the 16-wide FP32 SIMD units in the computation of matrix-vector products. We avoid data recurrence in multi-core computation of matrix-vector products by coloring of elements for each core. See Ref. [4] for details of the SIMD and multi-core implementation of matrix-vector products. This leads to an implementation of the solver with most of its computation using SIMD instructions on multi-cores. For simplicity of implementation, we use FP32 for the computations and communication in the inner loop solvers ( $PreCG_c$ ,  $PreCG_{cp}$ , and PreCG) in the CPU version. Using the SC18GBF solver algorithm, the FLOP count is reduced by 5.56fold compared to the standard PGCE solver for an earthquake wave propagation problem in a ground region with a buried concrete structure. Because mixed-precision arithmetic and highly efficient SIMD arithmetic can be used, we expected an additional speedup from the reduction in the arithmetic count. Indeed, we obtained 9.09-fold speedup from the PCGE method [8] when measured on the CPU-based K computer system [18].

#### 3 GPU Implementation Using OpenACC

Our solver algorithm, as described in the previous section, is suitable not only for CPUs but also for GPUs. For example, the introduction of time-parallel computation circumvents random accesses to the global vector in a matrix-vector multiplication kernel, which greatly improves the performance on GPUs. In addition,  $PreCG_{cp}$  computation can reduce the data transfer size as well as the computational amount; accordingly, this solver is appropriate for GPUs because data transfer is a major bottleneck in GPU computations. We assume that our solver will be accelerated even by a straightforward implementation of GPU computations. In this section, we first describe a baseline OpenACC implementation and then optimize its performance using lower-precision data types and other tunings.

#### 3.1 Baseline Implementation

We apply OpenACC to our CPU-based code following the general procedures given below.

1. Define where to apply OpenACC

In our solver, all computations are computed for each node or each element and are easily parallelized by GPUs. Therefore, we target the entire solver to be ported to the GPUs. Conversely, the training and reference of the AI for extracting FEMmodel<sub>cp</sub> conducted only once and their computational cost is negligible. Accordingly, we do not port this part of the code.

2. Insert directive to parallelize loops We can compute targeting loops on GPUs by adding the corresponding directives, as shown in Fig. 2. OpenACC has three levels of parallelism: gang, worker, and vector. On NVIDIA GPUs, gang and vector correspond to block and thread, respectively, and usually the worker level is ignored. We insert directives so that the expected granularity of the parallelization can be attained. Figure 2 describes an outline of the implementation in a matrixvector multiplication kernel. Loops for elements and time steps are collapsed to enable further parallelism. Each thread on the NVIDIA GPU is assigned to one element and its element-wise results are added to the global vector, which may cause data race conditions between threads. A previous study [5] showed that addition via atomic operations is much faster than explicit reordering

```

1 #pragma acc parallel loop collapse(2)

for(i ele = 0; i ele < (*n element); i ele++){</pre>

2

3

for(i vec = 0; i vec < (*n vector); i vec++){</pre>

4

cny0 = connect[i_ele][0];

5

cny1 = connect[i ele][1];

6

7

cny9 = connect[i ele][9];

8

9

u0x = u[cny0][0][i_vec];

10

u0y = u[cny0][1][i_vec];

u0z = u[cny0][2][i_vec];

11

12

13

u9z = u[cny9][2][i vec];

14

15

Au0x = ...

16

....

17

Au9z = ...

18

19

#pragma acc atomic

20

r[cny0][0][cny0] += Au0x;

21

....

22

#pragma acc atomic

23

r[cny9][2][cny9] += Au9z;

24

}

25 }

```

Fig. 2. Porting example of the matrix-vector multiplication kernel on a tetrahedral second order mesh.

```

1 #pragma acc data present_or_copy(u, r, connect, err,...){

2 while(err < tolerance){

3

4    /* CG computation in GPU */

5

6    #pragma acc update host(err)

}

7 }</pre>

```

Fig. 3. Example code for data transfer in a conjugate gradient loop.

via coloring; therefore, we use atomic operations for this part. As shown in Fig. 2, we can enable atomic operations by adding the option #pragma acc atomic.

3. Control data transfer between CPUs and GPUs

Without explicit instructions, OpenACC automatically transfers the necessary data from the CPUs to the GPUs prior to the GPU computation and from the GPUs to the CPUs following the GPU computation to obtain the expected results. When data are transferred too frequently, the performance greatly diminishes; therefore, we add directives to control the data transfer, as described in Fig. 3, to minimize these data transfer costs.

```

/* pack data in sendbuf */

1

2

3

#pragma acc host data use device(sendbuf, recvbuf){

4

ret = MPI Irecv(recvbuf, mpicount, MPI REAL,

source, tag, MPI COMM WORLD, &prequest[0]);

ret = MPI Isend(sendbuf, mpicount, MPI REAL,

5

dest, tag, MPI COMM WORLD, &prequest[1]);

ret = MPI Waitall(commcount, prequest, pstatus)

6

7

}

8

/* unpack data in recvbuf */

9

```

Fig. 4. Example code for point-to-point communication.

In addition, original codes are designed for the MPI parallelization to allow us to use multiple GPUs and assign one GPU to each MPI process. Point-to-point communication requires data transfer between GPUs; we use GPUDirect. We issue MPI\_Isend/Irecv to access GPU memory directly by adding the corresponding directives, as shown in Fig. 4.

We refer to these implementations as the baseline OpenACC implementation. To improve the performance, we introduce lower-precision data types and modify a few parts of the code that can decrease the performance.

#### 3.2 Introduction of Lower-Precision Data Types

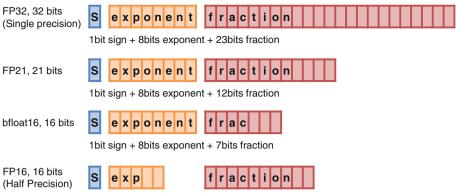

Our proposed solver can introduce transprecision computing to preconditioning conjugate gradient solvers. These solvers include many memory-bound computations. Therefore, we can reduce the computational cost simply by reducing the number of bits in each variable and reducing the footprint. In CPU-based implementations, a single-precision data type (FP32) is used in  $PreCG_c$ ,  $PreCG_{cp}$ , and PreCG. Typical floating-point numbers including FP32 are standardized in IEEE 754 as  $x = (-1)^{sign} \times (1. fraction) \times 2^{exponent-bias}$  for normalized numbers [13]. The sign bit determines the sign of the number, the exponent width influences the dynamic range of the number, and the fraction width defines the accuracy of the data type. Recently, data types with lower precision than FP32 have become widely supported on various types of hardware. The half-precision number, FP16, is a major example of such data types. It shortens the number of exponent bits and fraction bits compared to FP32 data types. It is not difficult to use FP16 for applications that do not require very high accuracy, e.g., deep learning [14]; however, using it for general scientific computations is challenging due to its narrow dynamic range. For our iterative solver, more exponent bits are required. Another data type, bfloat16, was proposed in Ref. [23]. It has the same width of exponent bits as FP32; therefore, it can avoid overflow/underflow in more general computations. However, it cuts down on the fraction bits by only 7 bits; accordingly, its machine epsilon becomes  $1/2^7 = 1/128$ . This low accuracy may lead to poor convergency.

1bit sign + 5bits exponent + 10bits fraction

Fig. 5. Bit alignments for the sign, exponent, and fraction parts in each data type. Each cell describes one bit.

Therefore, we define our custom 21-bit data type in Fig. 5. Hereafter, we refer to this data type as FP21. FP21 has the advantage of the same dynamic range as FP32 and bfloat16 and a better accuracy than FP16 or bfloat16. In addition, the border between the sign bit and exponent bits and the border between the exponent bits and fraction bits in FP21 are the same as those in FP32 numbers; therefore, conversions between FP21 and FP32 are easier than conversions between other combinations of data types. To facilitate the bit operations, we store three FP21 numbers in one component of the 64-bit arrays and space 1-bit. Our proposed data type is not supported on our targeted hardware; therefore, we use it only when storing into memory. We convert the FP21 data types into FP32 prior to computation in FP32 and convert the results in FP32 into FP21 numbers following the computation. Figure 6 shows an implementation of the data type conversion. Only addition or subtraction operations and bit operations are required for this conversion, and they can be implemented entirely within OpenACC. If these functions are called with stack frames, they decrease the performance. Therefore, they have to be in-line in all related computations. When we convert FP32 data types into FP21, we can remove the lower 11-bits in the fraction parts; however, rounding to the nearest number can halve the rounding error compared to dropping the lower-bits. We obtain rounded numbers as follows. First, we remove the last 11 bits of the original FP32 number aand obtain the FP21 number  $\bar{a}$ . Then, we can obtain the result by removing the last 11 bits of  $a + (a - \bar{a})$  in FP32.

Here, we are targeting a 3D problem; therefore, we have the three components of x, y, and z per node. Using FP21 for this problem enables us to assign one component in the 64-bit arrays to one node including the x, y, and z components in FP21; therefore, we can easily handle memory access to the FP21 numbers.

```

1 static inline float conv fp21 to fp32(unsigned int fp21tmp)

2 {

3

fp21tmp <<= 11;

4

float *b = reinterpret cast<float*>(&fp21tmp);

5

return b[0];

6 }

7

8 static inline float conv_fp21x3_to_fp32_x(unsigned long fp21x3tmp)

9

{

10

return conv fp21 to fp32(

((unsigned int)((fp21x3tmp >> 0) & 0x1fffff)));

11 }

12

13

static inline float conv fp21x3 to fp32 y(unsigned long fp21x3tmp)

14 {

15

return conv fp21 to fp32(

((unsigned int)((fp21x3tmp >> 21) & 0x1fffff)));

16 }

17

18 static inline float conv fp21x3 to fp32 z(unsigned long fp21x3tmp)

19 {

20

return conv fp21 to fp32(

((unsigned int)((fp21x3tmp >> 42) & 0x1fffff)));

21 }

```

Fig. 6. Mock code for the FP21 implementation. These functions convert FP21 numbers into FP32 numbers and are in-line for all computations requiring FP21 computations.

Note that atomic operations used in matrix-free matrix-vector multiplication are supported only for FP16/32/64 and that the output vector of this kernel must be in FP32. Therefore, vectors in FP21 and FP32 are mixed in the preconditioning solvers.

#### 3.3 Miscellaneous Optimizations in the Solver

The introduction of FP21 data types is expected to reduce the computational time of memory bound computations compared to the baseline implementation using OpenACC; however, our solver algorithm includes several operations that greatly decrease the performance compared to the low-level description, e.g., CUDA. We avoid this performance decrease via the following modifications.

1. Dot product targeting multiple vectors

Originally, dot products could be computed on OpenACC by adding the option reduction to the loop directive **#pragma acc loop**. However, the current version of OpenACC does not allow us to specify arrays for the target of the reduction, which prevents the parallelization of the inner loops for four time steps. We can compute dot products by creating multiple scalar variables and corresponding loops, as described in Fig. 7. However, such an implementation leads to strides in the memory accesses and a decline in the

Fig. 7. Example code for computing dot products for multiple vectors in OpenACC.

```

1 __global__

2 void dotproduct(int *n, float *x, float *y, float *z, float *xy){

3 /* CUDA computation */

4 }

1 void dotproduct_wrapper(int *n, float *x, float *y, float *z, float *xy){

2 dotproduct<<<960,128>>>(n, x, y, z, xy);

3 }

1 #pragma acc host_data use_device(n, x, y, z, xy){

2 dotproduct_wrapper(n, x, y, z, xy);

3 }

```

Fig. 8. Example code to call the dot product kernel in CUDA from the OpenACC codes.

performance. Therefore, we use a CUDA kernel to compute dot products. We can call CUDA-based kernel from the OpenACC-based code via a wrapper, as shown in Fig. 8, and improve the performance of this computation.

2. Overheads for launching kernels

OpenACC has larger overheads for launching kernels than CUDA. The degrees of freedom in  $PreCG_c$  and  $PreCG_{cp}$  in our solver become smaller than the original problem; therefore, the relative overhead cost increases for computations with shorter loop lengths. To reduce overhead costs, we modify several kernels. In particular, we add options **#pragma acc async(1)** and **#pragma acc wait(1)** for kernels that can be computed asynchronously to overlap the overhead cost. Moreover, local arrays in OpenACC loops are sometimes stored in local memory instead of in registers. When local memory is used, memory allocation is required and this increases the overhead for launching kernels; therefore, we redefine these local arrays as scalar variables.

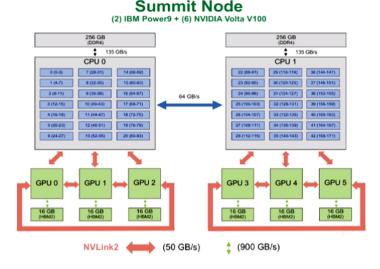

#### 4 Performance Measurement

In this section, we evaluate the performance of our proposed solver using GPUbased supercomputer ABCI [2], which is operated by the National Institute of Advanced Industrial Science and Technology. Each compute node of ABCI has four NVIDIA Tesla V100 GPUs and two Intel Xeon Gold 6148 CPUs (20 cores). Its peak performance in double precision is 7.8 TFLOPS  $\times 4 = 31.2$  TFLOPS on the GPUs and 1.53 TFLOPS  $\times 2 = 3.07$  TFLOPS on the CPUs. In addition, its theoretical memory bandwidth is 900 GB/s  $\times 4 = 3600$  GB/s on the GPUs and 126 GB/s  $\times 2 = 256$  GB/s on the CPUs. The GPUs in each compute node are connected via NVLink, with a bandwidth of 50 GB/s bandwidth in each direction.

We generated a finite element model assuming a small-scale city problem. The problem settings were nearly the same as those of our previous performance measurement in Ref. [8] except for the domain size and the number of MPI processes. The target domain included two soil layers and a layer with material properties similar to concrete. This problem had 39,191,319 degrees of freedom. In addition,  $PreCG_{cp}$ ,  $PreCG_{c}$ , and PreCG had 659,544, 5,118,339, and 39,191,319 degrees of freedom, respectively. The target domain was decomposed into four sub-domains, and four MPI processes were used in the computation. We used 10 OpenMP threads per MPI process when using CPUs so that all CPU cores on an ABCI compute node were used. We applied semi-infinite absorbing boundary conditions on the sides and bottom of the domain. We can incorporate any constitutive laws into our proposed solver. Here, we used modified RO model [9] and the Masing rule [16]. Kobe waves observed during the 1995 Southern Hyogo Earthquake [10] were input at the bottom of the model. The time increment was 0.01 seconds, and we computed 25 time steps. Convergence in the conjugate gradient loops was judged using a tolerance value of  $\epsilon = 1.0 \times 10^{-8}$ . In addition, the tolerances in  $PreCG_{cp}$ ,  $PreCG_c$ , and PreCG were set to 0.05, 0.7, and 0.25, respectively, according to Ref. [8].

#### 4.1 Performance Evaluation of FP21 Computation

We evaluated the performance of each computation in the solver. The elapsed time was measured using MPI\_Wtime. In this section, we compared the original CPU-based implementation, the baseline implementation using OpenACC, and our proposed implementation.

First, we measured the performance of the real Alpha X Plus Y (AXPY) operation. We extracted a computation in the *PreCG* solver of  $x(i) = x(i) + \alpha y(i)$ , where the arrays x(i) and y(i) are in FP32 or FP21 and the coefficient  $\alpha$ is in FP32. The elapsed times of all the implementations are described in Table 1. This computation was a memory-bound computation. Given that the theoretical memory bandwidths of the CPUs and GPUs per MPI process are 63.9 GB/s and 900 GB/s, the expected performance ratio was (CPU):(baseline OpenACC):(proposed) = 1/(32/63.9):1/(32/900):1/(21/900) = 1:14.1:21.5. Judging from this ratio, our GPU implementation achieved a reasonable speedup.

Judging from this ratio, our GPU implementation achieved a reasonable speedup. In addition, the measured bandwidth was close to the results of another benchmark [12]:  $900 \text{ GB/s} \times 83.3\% = 750 \text{ GB/s}$ ; therefore, we concluded that our performance was reasonable. In addition, using FP21 variables resulted in a 1.5-fold

speedup; therefore, we confirmed that the computational cost for the data type conversion was negligible.

Second, we measured the performance of a dot product. The target kernel computes  $\alpha = \sum_i ((x(1,i) \times y(1,i) + x(2,i) \times y(2,i) + x(3,i) \times y(3,i)) \times z(i))$ , where the arrays x(,i) and y(,i) are in FP32 or FP21 and the array z(i) is in FP32. The expected performance ratio was (CPU):(baseline OpenACC):(proposed) =  $1/((32 \times 7)/63.9):1/((32 \times 7)/900):1/((21 \times 6 + 32)/900) = 1:14.1:20.0$ . Compared to the AXPY kernel, the measured memory bandwidth in the baseline OpenACC implementation decreased because OpenACC cannot use the reduction option for arrays and causes stride memory access to the vectors. Conversely, our proposed implementation with CUDA attained nearly the same bandwidth as the AXPY kernel.

Finally, we show the performance of the matrix-vector multiplication kernel in Table 1. The simple implementation and our proposed method obtained 15.0fold and 14.8-fold speedups for our CPU-based kernel. The performance for these kernels on the GPUs reached 4 TFLOPS. The bottlenecks of this kernel are not memory bandwidth but the atomic addition to the global vector and the element-wise multiplication; therefore, we were unable to observe a significant difference in the performance even when using FP21 data types for the input vectors. Regarding this kernel, the data conversion between FP32 and FP21 in our proposed method was a possible reason for the slight performance gap between these two kernels.

|                       | Precision                            | CPU-based           | Baseline OpenACC     | Proposed             |

|-----------------------|--------------------------------------|---------------------|----------------------|----------------------|

|                       |                                      | FP32                | FP32                 | FP32/21              |

| AXPY                  | Elapsed time                         | $9.61\mathrm{ms}$   | $0.605\mathrm{ms}$   | $0.401\mathrm{ms}$   |

|                       | Measured<br>bandwidth                | $50.2\mathrm{GB/s}$ | $797.1\mathrm{GB/s}$ | $802.2\mathrm{GB/s}$ |

|                       | Speeding up<br>ratio                 | 1                   | 15.8                 | 24.0                 |

| Dot product           | Elapsed time                         | $6.20\mathrm{ms}$   | $0.456\mathrm{ms}$   | $0.277\mathrm{ms}$   |

|                       | Measured<br>bandwidth                | $54.0\mathrm{GB/s}$ | $735.1\mathrm{GB/s}$ | $822.9\mathrm{GB/s}$ |

|                       | Speeding up<br>ratio                 | 1                   | 13.6                 | 22.4                 |

| Matrix-vector product | Elapsed time                         | $54.61\mathrm{ms}$  | $3.65\mathrm{ms}$    | $3.69\mathrm{ms}$    |

|                       | Measured<br>FLOPS per<br>MPI process | 0.27 TFLOPS         | 4.11 TFLOPS          | 4.07 TFLOPS          |

|                       | Speeding up<br>ratio                 | 1                   | 15.0                 | 14.8                 |

Table 1. Performance of each kernel in the solver.

#### 4.2 Performance Evaluation of the Entire Solver

In this section, we evaluate the elapsed time for the entire solver. We compare the original CPU-based solver, a solver simply ported using OpenACC, a solver simply ported using CUDA, our proposed solver based on OpenACC, and the SC18GBF solver [8]. The SC18GBF solver improved its performance at the cost of portability. For example, shared memory on the V100 GPU was used to summarize the element-wise computation results and reduce the number of atomic operations in the element-by-element kernel and two-way packed FP16 computations in the V100 GPU were also applied. Moreover, matrix-vector multiplication and point-to-point communication were reordered as described in Ref. [17] so that computationally expensive data transfers could be overlapped. The SC18GBF solver, designed for large-scale computers, conducted further reductions in the data transfer cost by splitting the four time steps into two sets of two vectors and overlapping point-to-point communications with other vector operations. However, we compared the performance of the solver using only one compute node in this paper. Each GPU in the compute node was connected via NVLink; therefore, the data transfer cost was lower. Considering these problem settings, we computed the four time step vectors without splitting. In the GPU computations, we used atomic operations when the element-wise results were added to the global vector; therefore, numerical errors occur due to differences in the computation order. The final results of the analysis are consistent within the tolerance of the conjugate gradient solver; however, the number of iterations in the solver differs every time we run the program. Accordingly, we took the average of 10 trials for each solver.

The elapsed time for each solver is described in Table 2. The test took 781.8 s when using only CPUs on an ABCI compute node. Conversely, we reduced the computation time to 66.71 s via the simple implementation of OpenACC, resulting in a speedup ratio of 11.7. It took 61.02s using the simple implementation with CUDA. This gap in performance between OpenACC and CUDA is attributed to the following three factors. The first is the performance decline in the dot product kernels. The second is that kernels that conduct complex computations and require many variables cause register spilling, which does not occur in CUDA implementations. The third is that OpenACC has a larger overhead for launching each kernel than CUDA, which resulted in a large gap in  $PreCG_{cp}$ . Our proposed solver based on OpenACC used the FP21 data types and introduced techniques to circumvent the overhead in the OpenACC kernels. The elapsed time of this solver was 55.84 s; it was 9% faster than the original OpenACC implementation as well as faster than the simple implementation using CUDA. Therefore, we confirmed that the introduction of the FP21 data types was beneficial in accelerating the solver. Our proposed solver attained approximately 86% of the SC18GBF solver performance. Performance gap in  $PreCG_{cp}$ between our proposed solver and the SC18GBF solver was larger than those in  $PreCG_c$  and PreCG. This was because the degrees of freedom in  $PreCG_{cp}$  was smaller than other preconditioning solvers and data transfer cost was relatively higher, which was mostly overlapped in the SC18GBF solver. The performance of our proposed solver is very good from a practical point of view considering the portability provided by OpenACC.

Table 2. Elapsed time for the entire solver measured on ABCI. The total elapsed time includes the output of the analysis results. Performance of the preconditioning solvers is summarized in order of their appearance in CG solver. The numbers of iteration in each solver are also shown in parentheses.

| Precision in<br>$PreCG_c$ ,<br>$PreCG_{cp}$ ,<br>and $PreCG$ | CPU-based         | Baseline OpenACC  | Baseline CUDA     | Proposed          | SC18GBF           |

|--------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|                                                              | FP32              | FP32              | FP32              | FP32/21           | FP32/21/16        |

| $PreCG_c$                                                    | $161.4\mathrm{s}$ | 14.89 s           | $14.21\mathrm{s}$ | $9.79\mathrm{s}$  | 7.47 s            |

|                                                              | (6199)            | (6300)            | (6210)            | (4751)            | (4308)            |

| $PreCG_{cp}$                                                 | $69.9\mathrm{s}$  | $15.94\mathrm{s}$ | $12.20\mathrm{s}$ | $13.22\mathrm{s}$ | $8.98\mathrm{s}$  |

|                                                              | (28830)           | (28272)           | (28491)           | (28861)           | (26887)           |

| PreCG                                                        | $372.0\mathrm{s}$ | $22.90\mathrm{s}$ | $22.30\mathrm{s}$ | $18.27\mathrm{s}$ | $16.98\mathrm{s}$ |

|                                                              | (2674)            | (2729)            | (2735)            | (2575)            | (2797)            |

| CG                                                           | $83.9\mathrm{s}$  | $5.77\mathrm{s}$  | $4.57\mathrm{s}$  | $5.89\mathrm{s}$  | $8.32\mathrm{s}$  |

|                                                              | (91)              | (89)              | (89)              | (122)             | (129)             |

| Other                                                        | $94.8\mathrm{s}$  | $7.21\mathrm{s}$  | $7.73\mathrm{s}$  | $8.66\mathrm{s}$  | $5.99\mathrm{s}$  |

| Total                                                        | 781.8 s           | $66.71\mathrm{s}$ | $61.02\mathrm{s}$ | $55.84\mathrm{s}$ | $47.75\mathrm{s}$ |

| Speeding up<br>ratio                                         | 1                 | 11.7              | 12.8              | 14.0              | 16.4              |

When we used lower-precision numbers, e.g., FP16 or FP21, the convergence characteristics in the solver changed. When we replaced a computation in FP21 with a computation in bfloat16 for comparison, the solver failed to converge. These results indicate that more fraction bits than provided by bfloat16 were required for our problem settings. A detailed verification of the convergency when using lower-precision data types will be a future task.

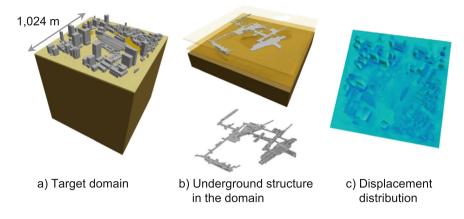

Finally, we solved problems with complicated geometry comprised of the ground and underground structures with 16,291,917,564 degrees of freedom and 3,961,851,160 elements, as demonstrated in Ref. [8]. Here we used 384 compute nodes of the supercomputer Summit [22]. We computed for 2,500-time steps with time increment dt = 0.001 s. As shown in Fig. 9, we obtained the displacement distribution reflecting complex geometries; therefore, the importance of our method was demonstrated.

Regarding the developmental cost, the introduction of CUDA required an additional 18,342 lines of code (our original code had 33,527 lines in total). Our OpenACC implementation required the addition of 9,300 lines of code; therefore, maintenance of our codes are expected to become easier when using OpenACC.

Fig. 9. Application example on Summit. a)  $1,024 \text{ m} \times 1,024 \text{ m}$  city area with underground and building structures surrounded by two-layered ground modeled; b) underground structures in the domain; c) displacement distribution at t = 2.50 s.

#### 5 Conclusions

To increase productivity in science and engineering fields, providing performance improvements that are portable and maintainable is a big challenge. In this paper, we target an implicit low-order finite element solver, for which it is considered difficult to attain high performances. The acceleration of this solver is required to enable practical applications in commerce or industry. We have developed fast solvers using supercomputers to reduce computational costs. Our latest solver has a sophisticated algorithm including AI and transprecision computing. Moreover, we thoroughly optimized the performance of each kernel using specialized hardware in our targeted architecture. Accordingly, the developed codes lacked portability and maintainability.

We applied OpenACC to this finite element solver. Via a performance measurement on ABCI, we confirmed that the OpenACC-based implementation achieved a 14.0-fold speedup compared to the original CPU codes. This is approximately 86% the performance of our extremely tuned solver using CUDA. Considering that the number of lines modified for the GPU implementation is much less than the number modified for CUDA and that the developmental cost is smaller, our proposed solver is sufficiently suitable for practical use. Our developed template to use transprecision computing with FP21 data types is available to the public [26]; therefore it can provide an example of how to accelerate other scientific computing applications using lower-precision data types. Acknowledgement. Our results were obtained using Computational resource of AI Bridging Cloud Infrastructure (ABCI), National Institute of Advanced Industrial Science and Technology (AIST). We acknowledge support from Post K computer project (Priority Issue 3 - Development of integrated simulation systems for hazards and disasters induced by earthquakes and tsunamis), and Japan Society for the Promotion of Science (17K14719, 18H05239, 18K18873). Part of our results were obtained using the Summit at Oak Ridge Leadership Computing Facility, a US Department of Energy, Office of Science User Facility at Oak Ridge National Laboratory.

#### Data Availability Statement.

#### Summary of the Experiments Reported

We ran our built-from-scratch implicit solver for unstructured finite elements on AI bridging cloud infrastructure with PGI compiler and OpenMPI.

#### Artifact Availability

Software Artifact Availability: Some author-created software artifacts are NOT maintained in a public repository or are NOT available under an OSI-approved license.

Hardware Artifact Availability: There are no author-created hardware artifacts.

Data Artifact Availability: Some author-created data artifacts are NOT maintained in a public repository or are NOT available under an OSI-approved license.

*Proprietary Artifacts:* There are associated proprietary artifacts that are not created by the authors. Some author-created artifacts are proprietary.

List of URLs and/or DOIs where artifacts are available:

http://doi.org/10.6084/m9.figshare.11603382 http://www.data.jma.go.jp/svd/eqev/data/kyoshin/jishin/hyogo\_nanbu/dat/ H1171931.csv.

Details regarding baseline experimental setup, and modifications made for the paper are available at [26].

## References

- Bielak, J., Ghattas, O., Kim, E.: Parallel octree-based finite element method for large-scale earthquake ground motion simulation. Comput. Model. Eng. Sci. 10(2), 99 (2005)

- 2. Computing Resources of AI bridging Clound Infrastructure. https://abci.ai/en/ about\_abci/computing\_resource.html. Accessed 11 Oct 2019

- 3. Farber, R.: Parallel programming with OpenACC. Newnes, Oxford (2016)

- Fujita, K., et al.: Development of element-by-element kernel algorithms in unstructured implicit low-order finite-element earthquake simulation for many-core Wide-SIMD CPUs. In: Rodrigues, J., et al. (eds.) ICCS 2019. LNCS, vol. 11536, pp. 267–280. Springer, Cham (2019). https://doi.org/10.1007/978-3-030-22734-0\_20

23

- Fujita, K., Yamaguchi, T., Ichimura, T., Hori, M., Maddegedara, L.: Acceleration of element-by-element kernel in unstructured implicit low-order finite-element earthquake simulation using OpenACC on pascal GPUs. In: Proceedings of the Third International Workshop on Accelerator Programming Using Directives, pp. 1–12. IEEE Press (2016)

- Golub, G.H., Ye, Q.: Inexact preconditioned conjugate gradient method with innerouter iteration. SIAM J. Sci. Comput. 21(4), 1305–1320 (1999)

- Ichimura, T., et al.: A fast scalable implicit solver with concentrated computation for nonlinear time-evolution problems on low-order unstructured finite elements. In: 2018 IEEE International Parallel and Distributed Processing Symposium (IPDPS), pp. 620–629. IEEE (2018)

- 8. Ichimura, T., et al.: A fast scalable implicit solver for nonlinear time-evolution earthquake city problem on low-ordered unstructured finite elements with artificial intelligence and transprecision computing. In: SC18: International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 627–637. IEEE (2018)

- Idriss, I.M., Dobry, R., Sing, R.: Nonlinear behavior of soft clays during cyclic loading. J. Geotech. Geoenviron. Eng. **104**(ASCE 14265), 1427–1447 (1978)

- Japan Meteorological Agency: Strong ground motion of The Southern Hyogo prefecture earthquake in 1995 observed at Kobe JMA observatory. https://www.data.jma.go.jp/svd/eqev/data/kyoshin/jishin/hyogo\_nanbu/ dat/H1171931.csv. Accessed 11 Oct 2018

- Jeong, S., Solenthaler, B., Pollefeys, M., Gross, M., et al.: Data-driven fluid simulations using regression forests. ACM Trans. Graph. (TOG) 34(6), 199 (2015)

- Jia, Z., Maggioni, M., Staiger, B., Scarpazza, D.P.: Dissecting the NVIDIA volta GPU architecture via microbenchmarking. arXiv preprint arXiv:1804.06826 (2018)

- Kahan, W.: IEEE standard 754 for binary floating-point arithmetic. Lecture Notes Status IEEE 754(94720–1776), 11 (1996)

- Kurth, T., et al.: Exascale deep learning for climate analytics. In: Proceedings of the International Conference for High Performance Computing, Networking, Storage, and Analysis, p. 51. IEEE Press (2018)

- Malossi, A.C.I., et al.: The transprecision computing paradigm: concept, design, and applications. In: 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 1105–1110. IEEE (2018)

- 16. Massing, G.: Eigenspannungen und verfestigung beinn messing. In: Proceedings of the 2nd International Congress of Applied Mechanics (1926)

- Micikevicius, P.: 3D finite difference computation on GPUs using CUDA. In: Proceedings of 2nd Workshop on General Purpose Processing on Graphics Processing Units, pp. 79–84. ACM (2009)

- Miyazaki, H., Kusano, Y., Shinjou, N., Shoji, F., Yokokawa, M., Watanabe, T.: Overview of the K computer system. Fujitsu Sci. Tech. J. 48(3), 302–309 (2012)

- 19. NVIDIA Tesla V100 GPU architecture. https://images.nvidia.com/content/voltaarchitecture/pdf/volta-architecture-whitepaper.pdf. Accessed 11 Oct 2019

- 20. OpenACC. http://www.openacc.org/. Accessed 11 Oct 2019

- Saad, Y.: Iterative Methods for Sparse Linear Systems, vol. 82. SIAM, Philadelphia (2003)

- 22. Summit. https://www.olcf.ornl.gov/olcf-resources/compute-systems/summit/. Accessed 11 Oct 2019

- Using bfloat16 with tensorflow models. https://cloud.google.com/tpu/docs/ bfloat16. Accessed 11 Oct 2019

- Winget, J.M., Hughes, T.J.: Solution algorithms for nonlinear transient heat conduction analysis employing element-by-element iterative strategies. Comput. Methods Appl. Mech. Eng. 52(1–3), 711–815 (1985)

- Yamaguchi, T., Fujita, K., Ichimura, T., Hori, M., Lalith, M., Nakajima, K.: Implicit low-order unstructured finite-element multiple simulation enhanced by dense computation using OpenACC. In: Chandrasekaran, S., Juckeland, G. (eds.) WACCPD 2017. LNCS, vol. 10732, pp. 42–59. Springer, Cham (2018). https://doi. org/10.1007/978-3-319-74896-2\_3

- 26. Yamaguchi, T., Fujita, K., Ichimura, T., Naruse, A., Lalith, M., Hori, M.: FP21AXPY. Figshare (2020). https://doi.org/10.6084/m9.figshare.11603382. Accessed 22 Jan 2020

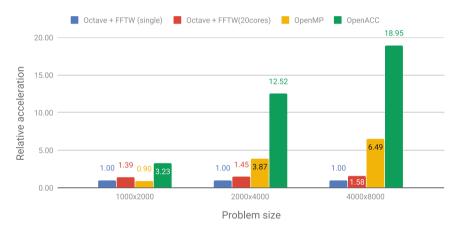

# Acceleration in Acoustic Wave Propagation Modelling Using OpenACC/OpenMP and Its Hybrid for the Global Monitoring System

Noriyuki Kushida<sup>1(⊠)</sup>, Ying-Tsong Lin<sup>2</sup>, Peter Nielsen<sup>1</sup>, and Ronan Le Bras<sup>1</sup>

<sup>1</sup> Comprehensive Nuclear-Test Ban Treaty Organization, Vienna, Austria {noriyuki.kushida,peter.nielsen,ronan.lebras}@ctbto.org http://www.ctbto.org

<sup>2</sup> Woods Hole Oceanographic Institution, Woods Hole, MA 02543, USA ytlin@whoi.edu

Abstract. CTBTO is operating and maintaining the international monitoring system of Seismic, Infrasound, Hydroacoustic and Airborne radionuclide facilities to detect a nuclear explosion over the globe. The monitoring network of CTBTO, especially with regard to infrasound and hydroacoustic, is quite unique because the network covers over the globe, and the data is opened to scientific use. CTBTO has been developing and improving the methodologies to analyze observed signals intensively. In this context, hydroacoustic modelling software, especially which that solves the partial differential equation directly, is of interest. As seen in the analysis of the Argentinian submarine accident, the horizontal reflection can play an important role in identifying the location of an underwater event, and as such, accurate modelling software may help analysts find relevant waves efficiently. Thus, CTBTO has been testing a parabolic equation based model (3D-SSFPE) and building a finite difference time domain (FDTD) model. At the same time, using such accurate models require larger computer resources than simplified methods such as ray-tracing. Thus we accelerated them using OpenMP and OpenACC, or the hybrid of those. As a result, in the best case scenarios, (1) 3D-SSFPE was accelerated by approximately 19 times to the original Octave code, employing the GPU-enabled Octfile technology, and (2) FDTD was accelerated by approximately 160 times to the original Fortran code using the OpenMP/OpenACC hybrid technology, on our DGX—Station with V100 GPUs.

**Keywords:** OpenACC/OpenMP hybrid · OpenACC with Octave/Matlab · Split Step Fourier · FDTD · Hydroacoustic modelling

© Springer Nature Switzerland AG 2020

S. Wienke and S. Bhalachandra (Eds.): WACCPD 2019, LNCS 12017, pp. 25–46, 2020. https://doi.org/10.1007/978-3-030-49943-3\_2

Electronic supplementary material The online version of this chapter (https://doi.org/10.1007/978-3-030-49943-3\_2) contains supplementary material, which is available to authorized users.

#### 1 Introduction

The Comprehensive Nuclear-Test-Ban Treaty (CTBT) is the treaty which bans nuclear explosions in any environment over the globe, such as in the atmosphere, in the ocean, and underground. Although the treaty has not entered into force, Preparatory Commission for the CTBT Organization (CTBTO) has been monitoring signs of nuclear explosions using four technologies, namely, seismic, infrasound, hydroacoustic and air-borne radionuclide. The monitoring network of CTBTO, especially with regard to infrasound and hydroacoustic, is quite unique because the network covers over the globe and the data is opened to scientific use. Therefore, CTBTO has been developing and improving the methodologies to analyze observed signals intensively. Because of the complex natures of the oceans and the atmosphere, computer simulation can play an important role in understanding the observed signals. In this regard, methods which depend on partial differential equations, in other words an "ab-initio" approach, are preferable in order not to overlook any subtle phenomena. However, there have been only a few groups which perform such computer modelling with the parabolic equation (PE) methods [10,11]. Based on such circumstances, CTBTO has been testing and developing hydroacoustic simulation software packages based on PE called 3D-SSFPE [20], and the finite difference method (FDM) [18] respectively. Lin et al. explained the advantages of 3D-SSFPE over other PE methods in their literature i.e. 3D-SSFPE is designed for long distance modelling.

One of the biggest drawbacks of using such accurate methods is the high demand on computer resources, especially the arithmetic computing performance. Although computer simulation is not considered as a necessary product for the treaty, providing the member states with modelling results promptly may help their decision-making.