Osman Hasan Frédéric Mallet (Eds.)

**Communications in Computer and Information Science**

1165

# Formal Techniques for Safety-Critical Systems

7th International Workshop, FTSCS 2019 Shenzhen, China, November 9, 2019 Revised Selected Papers

# Communications in Computer and Information Science 1165

Commenced Publication in 2007

Founding and Former Series Editors:

Simone Diniz Junqueira Barbosa, Phoebe Chen, Alfredo Cuzzocrea,

Xiaoyong Du, Orhun Kara, Ting Liu, Krishna M. Sivalingam,

Dominik Ślęzak, Takashi Washio, Xiaokang Yang, and Junsong Yuan

#### **Editorial Board Members**

Joaquim Filipe 10

Polytechnic Institute of Setúbal, Setúbal, Portugal

Ashish Ghosh

Indian Statistical Institute, Kolkata, India

Igor Kotenko

St. Petersburg Institute for Informatics and Automation of the Russian Academy of Sciences, St. Petersburg, Russia

Raquel Oliveira Prates (1)

Federal University of Minas Gerais (UFMG), Belo Horizonte, Brazil Lizhu Zhou

Tsinghua University, Beijing, China

More information about this series at http://www.springer.com/series/7899

# Osman Hasan · Frédéric Mallet (Eds.)

# Formal Techniques for Safety-Critical Systems

7th International Workshop, FTSCS 2019 Shenzhen, China, November 9, 2019 Revised Selected Papers

Editors

Osman Hasan

National University of Sciences

and Technology

Islamabad, Pakistan

Frédéric Mallet D Université Cote d'Azur Sophia Antipolis Cedex, France

ISSN 1865-0929 ISSN 1865-0937 (electronic)

Communications in Computer and Information Science

ISBN 978-3-030-46901-6 ISBN 978-3-030-46902-3 (eBook)

https://doi.org/10.1007/978-3-030-46902-3

#### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Preface**

This volume contains the proceedings of the 7th International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2019), held in Shenzhen, China, on November 9, 2019, as a satellite event of the ICFEM conference.

The aim of this workshop is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safety-critical computer systems. FTSCS strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics include, but are not limited to:

- Case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, medical, and other kinds of safety-critical and QoS-critical systems

- Methods, techniques, and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems

- Analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.)

- Formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.

- Code generation from validated models

The workshop received 16 regular and 1 tool paper submissions. Based on the reviews and extensive discussions, the Program Committee selected 6 regular papers, 1 tool paper, and 1 work-in-progress paper for presentation at the workshop and inclusion in this volume. Another highlight of the workshop was an invited talk by Sofiène Tahar on "Formal Verification of Cyber-Physical Systems." We organized the discussion into three sessions. One specifically on avionic and spacecraft domain. The second one on a wider range of application domains including transportation, circuits, and medical applications. The last one included work-in-progress and tool papers.

Many colleagues and friends have contributed to FTSCS 2019. We thank Sofiène Tahar for giving an excellent invited talk and the authors who submitted their work to FTSCS 2019 and who, through their contributions, made this workshop an interesting event. We are particularly grateful that so many well-known researchers agreed to serve on the Program Committee, and that they provided timely, insightful, and detailed reviews. We also thank the editors of *Communications in Computer and Information Science* for agreeing to publish the proceedings of FTSCS 2019 as a volume in their series, and Shengchao Qin and Lijun Zhang for their help with the local arrangements.

March 2020 Osman Hasan Frédéric Mallet

# **Organization**

# **Program Committee**

Musab Alturki King Fahd University of Petroleum and Minerals,

Saudi Arabia

Étienne André Université Paris 13, LIPN, CNRS, UMR, France

Toshiaki Aoki JAIST, Japan

Cyrille Valentin Artho KTH Royal Institute of Technology, Sweden Kyungmin Bae Pohang University of Science and Technology

(POSTECH), South Korea

Osman Hasan National University of Sciences and Technology,

Pakistan

Klaus Havelund

Ralf Huuck

Alexander Knapp

Sven Linker

Robi Malik

Frederic Mallet

Stefan Mitsch

Jet Propulsion Laboratory, USA

UNSW Sydney, LOGILICA, Australia

Universität Augsburg, Germany

The University of Liverpool, UK

University of Waikato, New Zealand

Université Cote d'Azur, France

Carnegie Mellon University, USA

Roberto Nardone Mediterranean University of Reggio Calabria, Italy

Thomas Noll RWTH Aachen University, Germany

Lee Pike Galois, Inc., USA

Zhiping Shi Beijing Engineering Research Center of High Reliable

Embeded System, China

Sofiene Tahar Concordia University, Canada

Carolyn Talcott SRI International, USA

Jean-Pierre Talpin Inria, France

Nils Timm University of Pretoria, South Africa

Tatsuhiro Tsuchiya Osaka University, Japan

Tom van Dijk University of Twente, The Netherlands Huibiao Zhu East China Normal University, China

Peter Ölveczky University of Oslo, Norway

# **Additional Reviewers**

Ahmad, Waqar Gruner, Stefan Li, Ximeng Qasim, Muhammad Zhang, Qianying

# **Contents**

| Invited Paper                                                                                                                                                                              |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Formal Verification of Cyber-Physical Systems Using Theorem Proving<br>Adnan Rashid, Umair Siddique, and Sofiène Tahar                                                                     | 3   |

| Avionics and Spacecraft                                                                                                                                                                    |     |

| Formal Development of Multi-Purpose Interactive Application (MPIA) for ARINC 661.  Neeraj Kumar Singh, Yamine Aït-Ameur, Dominique Méry, David Navarre, Philippe Palanque, and Marc Pantel | 21  |

| Verifying Resource Adequacy of Networked IMA Systems at Concept Level                                                                                                                      | 40  |

| Automated Ada Code Generation from Synchronous Dataflow Programs on Multicore: Approach and Industrial Study                                                                               | 57  |

| Applications                                                                                                                                                                               |     |

| POP: A Tuning Assistant for Mixed-Precision Floating-Point Computations                                                                                                                    | 77  |

| Visualising Railway Safety Verification                                                                                                                                                    | 95  |

| Probabilistic Activity Recognition for Serious Games with Applications in Medicine                                                                                                         | 106 |

| Tools and Work in Progress                                                                                                                                                                 |     |

| A Framework for Model Checking Against CTLK Using Quantified Boolean Formulas                                                                                                              | 127 |

# viii Contents

| Formal Semantics Extraction from MIPS Instruction Manual | 133 |

|----------------------------------------------------------|-----|

| Author Index                                             | 141 |

# Formal Verification of Cyber-Physical Systems Using Theorem Proving

Adnan Rashid<sup>1(⊠)</sup>, Umair Siddique<sup>2</sup>, and Sofiène Tahar<sup>2</sup>

School of Electrical Engineering and Computer Science (SEECS), National University of Sciences and Technology (NUST), Islamabad, Pakistan adnan.rashid@seecs.nust.edu.pk

<sup>2</sup> Department of Electrical and Computer Engineering, Concordia University, Montreal, Canada

{muh\_sidd,tahar}@ece.concordia.ca

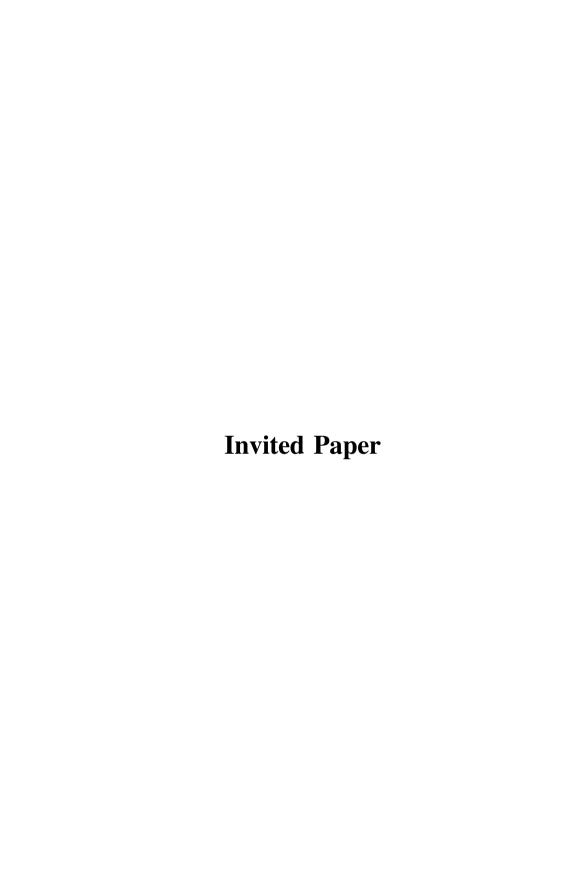

**Abstract.** Due to major breakthroughs in software and engineering technologies, embedded systems are increasingly being utilized in areas ranging from aerospace and next-generation transportation systems, to smart grid and smart cities, to health care systems, and broadly speaking to what is known as Cyber-Physical Systems (CPS). A CPS is primarily composed of several electronic, communication and controller modules and some actuators and sensors. The mix of heterogeneous underlying smart technologies poses a number of technical challenges to the design and more severely to the verification of such complex infrastructure. In fact, a CPS shall adhere to strict safety, reliability, performance and security requirements, where one needs to capture both physical and random aspects of the various CPS modules and then analyze their interrelationship across interlinked continuous and discrete dynamics. Oftentimes however, system bugs remain uncaught during the analysis and in turn cause unwanted scenarios that may have serious consequences in safety-critical applications. In this paper, we introduce some of the challenges surrounding the design and verification of contemporary CPS with the advent of smart technologies. In particular, we survey recent developments in the use of theorem proving, a formal method, for the modeling, analysis and verification of CPS, and overview some real world CPS case studies from the automotive, avionics and healthtech domains from system level to physical components.

**Keywords:** Cyber-Physical Systems (CPS)  $\cdot$  Formal methods  $\cdot$  Theorem proving  $\cdot$  Physical systems  $\cdot$  Hybrid systems  $\cdot$  Performance  $\cdot$  Dependability

#### 1 Introduction

Cyber-Physical systems (CPS) [74] are engineered systems involving a cyber component that controls the physical components, as shown in Fig. 1. The cyber elements include embedded systems and network controllers, which are usually

<sup>©</sup> Springer Nature Switzerland AG 2020

O. Hasan and F. Mallet (Eds.): FTSCS 2019, CCIS 1165, pp. 3-18, 2020.

#### A. Rashid et al.

4

modeled as discrete events. Whereas, the physical components exhibit continuous dynamics, such as the physical motion of a robot in space or the working of an analog circuit, and are commonly modeled using differential equations. CPS are capable of performing two main functionalities (a) constructing the cyber space using intelligent data management, computational and analytical capabilities; and (b) real-time data acquisition from the physical world and information feedback from the cyber space using some advanced connectivity, as depicted in Fig. 1. They can be small, such as artificial pancreas, or very large and complex, such as a smart car or smart energy grid. The development of powerful embedded system hardware, low-power sensing and widely deployed communication networks has drastically increased the dependence of system functionality on CPS. CPS are widely used in advanced automotive systems (autonomous vehicles and smart cars), avionics, medical systems and devices, optical systems, industrial process control, smart grids, traffic safety and control, robotics and telecommunication networks, etc. For example, smart (self-driving) cars are considered as a highly complex autonomous CPS composed of over one hundred processors, and an array of sensors and actuators that interact with the external environment, like the road infrastructure and internet.

Fig. 1. Components of a CPS [2]

The main goals for an efficient design of CPS are to co-design its cyber and physical parts, and to engineer the system of systems involving the intrinsic heterogeneity. Moreover, an increase in the complexity of its various components and the utilization of advanced technologies pose a major challenge for developing a CPS. For example, in the case of smart cars, it is required to develop cost-effective methods ensuring: (a) design and analysis (verification) of its various components at different levels of abstraction, i.e., at different systems and software architecture levels; (b) analyzing and understanding the interactions of

system of systems, e.g., cars' control system and its various components, such as engine, wheel, steering; (c) minimizing the cost of the car by ensuring the safety, reliability, performance and stability of the overall system. Thus, these requirements have to be fulfilled for the efficient design and analysis of a CPS.

The analysis of CPS can generally be characterised as of three types, namely, functional, performance and dependability analysis. For example, the functional analysis involves the analysis of the physical, control and signal processing components of CPS. Each of these characteristics also need to consider a hybrid behavior incorporating both continuous and discrete dynamics, e.g., the physical and cyber elements of the underlying system.

Conventionally, CPS are analyzed using paper-and-pencil methods or computer-based numerical and symbolic techniques. Moreover, most of the time is spent on designing the life-cycle of CPS and their physical (dynamical) behaviour needs to be manipulated. However, there is a lack of theoretical foundations for CPS dynamics and compositional theories for the heterogeneous systems in the tools associated with these analyses. Moreover, these analysis methods suffer from their inherent limitations, like human-error proneness, discretization and numerical errors and the usage of unverified simplification algorithms [23] and thus cannot provide absolute accuracy of the corresponding analysis. Due to the safety critical-nature of CPS, the accuracy of their design and analysis is becoming a dire need. For example, the fatal crash of Uber's self-driving car in March 2018 that killed a pedestrian in Tempe, Arizona, USA was found to be caused by some sensor's anomalies [1]. A more rigourous analysis of CPS could have avoided this incident.

Formal methods [44] have been used as a complementary technique for analyzing CPS and thus can overcome the above-mentioned inaccuracy limitations of the analysis. The two most commonly used formal methods are model checking [14] and theorem proving [35]. Model checking is based on developing a state-space based model of the underlying system and formally verifying the properties of interest, specified in temporal logic. It has been used for analyzing several aspects of a CPS [21]. However, this kind of analysis involves the discretization of the continuous dynamical models and thus compromises the accuracy of the corresponding analysis. Moreover, it also suffers from the state-space explosion problem [14]. Theorem proving [35] is a computer based mathematical method that involves developing a mathematical model of the given system in an appropriate logic and the formal verification of the properties of interest based on mathematical reasoning within the sound core of a theorem prover. The involvement of the formal model and its associated formally specified properties along with the sound nature of theorem proving ensures the accuracy and completeness of the analysis. Based on the decidability or undecidability of the underlying logic, e.g., propositional or higher-order logic, theorem proving can be automatic or interactive, respectively.

Many theorem provers, e.g., HOL4 [92], HOL Light [36], Isabelle [69], KeYmaera [73], Coq [19], PVS [68] have been used for the formal analysis (formal verification) of CPS, e.g., formal functional analysis, formal probabilistic and

performance analysis, formal dependability analysis, and hybrid analysis. For instance, the KeYmaera theorem prover has been specifically designed for the formal verification of hybrid systems, thus, incorporating both the continuous and discrete dynamics of the underlying system. KeYmaera is based on deductive reasoning and computer algebraic prover technologies. It uses differential dynamic logic for the model implementation and specification of the underlying system, which is a first-order logic. Similarly, HOL Light provides an extensive support of mathematical libraries that have been used for the functional analysis, i.e., the verification of various continuous aspects of CPS, such as control systems, power electronics, electromagnetic, quantum and optical systems. HOL4 and Isabelle theorem provers provide an extensive support for the formal probabilistic and dependability analysis of systems. Likewise, Isabelle and HOL4 have been extensively used for the verification of software components, providing safety and security analysis of the underlying CPS. In this paper, we report these developments that have been done for the modeling, analysis and verification of CPS in these theorem provers.

# 2 Formal Functional Analysis

#### 2.1 Verification of Physical Components

Hasan et al. [38] proposed a framework for analyzing the optical waveguides using HOL4. In particular, the authors formally analyzed the eigenvalues for the planar optical waveguides and utilized their proposed framework for analyzing a planar asymmetric waveguide. Afshar et al. [5] developed a formal support for the complex vector analysis using HOL Light and used it to formally verify the law of reflection for the planar waves. Later, the authors used the formalization of complex vectors to formalize the notions of electromagnetic optics [51], which is further used for performing the formal analysis of the resonant cavity enhanced photonic devices.

Siddique et al. [86] provided a formalization of geometrical optics using HOL Light. The authors formalized fundamental concepts about geometrical optics, i.e., ray, free space, optical system and its stability. Finally, they used their proposed formalization to perform the stability analysis of the Fabry-Perot resonator with fiber rod lens [82]. Next, the authors extended their framework by formalizing the ray optics of the cardinal points and utilized it for formally analyzing a thick lens [87] and the optical instrument used to compensate the ametropia of an eye [89]. Moroever, the authors formalized the notion of optical resonators and used it for formally verifying the 2-D microresonator lattice optical filters [88]. Finally, the authors extended their formal support for geometrical optics in HOL Light by performing the formal analysis of the gaussian [90] and periodic [91] optical systems.

As a part of the optics formal verification project [6], Mahmoud et al. [60] provided a support for the formal analysis of the quantum systems using HOL Light. In particular, the authors formalized the infinite dimension linear spaces and used it for formally verifying a quantum beam splitter. Next, the authors

used their formalization of linear algebra to formalize the optical quantum circuits, i.e., the flip gate and used it to formally verify the beam splitter and the phase conjugating mirror [61]. Later, the authors also formalized the notion of coherent light, which is a light produced by the laser sources and formally verified its various properties using HOL Light [62]. Based on these findings, Beillahi et al. [15] proposed a framework for the hierarchical verification of the quantum circuit and used it for the formal analysis of a controlled-phase gate and the Shor's factoring quantum circuits. Rand et al. [75] proposed a framework implementing the QWIRE quantum circuit language in Coq, which accepts a high-level abstract model of the quantum circuits and allows the verification of their properties using Coq's features such as dependently-typed circuits and proof-carrying code. Liu et al. [54] formalized the theory of Quantum Hoare Logic (QHL) and used it for formally verifying the correctness of a nontrivial quantum algorithm using Isabelle.

#### 2.2 Verification of Software Components

The High-Assurance Cyber Military Systems (HACMS) research program [33] was started by the Defense Advanced Research Projects Agency (DARPA) in the USA with an aim of creating a technology for constructing CPS that are resilient against cyber-attacks, i.e., CPS providing an appropriate security and safety properties. One of the major goals of this program is to create a high-assurance software for vehicles, ranging from automobiles to military vehicles, such as quadcopters and helicopters. As a part of this project, Cofer et al. [22] proposed a formal approach for constructing a secure airvehicle software to ensure security against cyber attacks using Isabelle. Moreover, the authors applied their proposed approach for formally analyzing the SMACCMcopter, which is a modified commercial quadcopter, and Boeing's Unmanned Little Bird (ULB), which is a full-sized optionally-piloted helicopter. Klein et al. [52] presented the formal verification of seL4 microkernel in HOL4, which is a third-generation microkernel of L4 provenance. The authors formally proved that the implementation of the underlying system follows the high-level specification of the kernel behaviour using Isabelle. Moreover, they also verified two vital properties of the microkernel, i.e., (1) the kernel will not perform an unsafe operation; (2) it will never crash.

#### 2.3 Verification of Control and Signal Processing Components

Transform methods, such as Laplace, Fourier and z-transforms are widely used for solving dynamical models and performing the frequency domain analysis of systems. Generally, the dynamics of a system in frequency domain are characterized by the transfer function and frequency response, providing a relationship between its input and output and are important properties of the control and signal processing components of a CPS. In this regards, Taqdees et al. [93] formalized the Laplace transform using multivariate calculus theories of HOL Light.

Moreover, the authors used their formalization of the Laplace transform for formally verifying the transfer function of the Linear Transfer Converter (LTC) circuit. Next, the authors extended their framework and provided a support to formally reason about the linear analog circuits, such as Sallen-Key low-pass filters [94] by formalizing the system governing laws such as Kirchhoff's Current Law (KCL) and Kirchhoff's Voltage Law (KVL) using HOL Light. Later, Rashid et al. [81] proposed a new formalization of the Laplace transform based on the notion of sets and used it for analyzing the control system of the Unmanned Free-swimming Submersible (UFSS) vehicle [79] and  $4-\pi$  soft error crosstalk model [76]. The Laplace transform [49,96] has also been formalized in Isabelle and Coq theorem provers. Similarly, Rashid et al. [77] formalized the Fourier transform in HOL Light and used it to formally analyze an Automobile Suppension System (ASS), an audio equalizer, a drug therapy model and a MEMs accelerometer [78].

To perform the transfer function based analysis of the discrete-time systems, Siddique et al. [84] formalized z-transform using HOL Light and used it for the formal analysis of Infinite Impulse Response (IIR) Digital Signal Processing (DSP) filter. Later, the authors extended their proposed framework by providing the formal support for the inverse z-transform and used it for formally analyzing a switched-capacitor interleaved DC-DC voltage doubler [85]. Beillahi et al. [17] proposed a formalization of signal-flow graph, which is widely used for evaluating the system performance in the form of transfer function, using HOL Light. The authors used their proposed framework for formally analyzing a die design process [16], 1-boost cell interleaved DC-DC, Pulse Width Modulation (PWM) push-pull DC-DC converters [17], Double-coupler Double-ring (DCDR) photonic processor [83], z-source impedance network and PANDA Vernier resonator [18].

Faroog et al. [32] proposed a formal framework for the kinematic analysis of a two-link planar manipulator, which describes a geometrical relationship between the robotic joints and links, and is widely used to capture the motion of the robots. Moreover, the authors performed the formal kinematic analysis of a biped walking robot using HOL Light. Next, Affeldt et al. [4] carried forward this idea and formalized the foundational support for 3D analysis of the robotic manipulators in Coq. The authors used their proposed framework for the kinematic analysis of the SCARA robot manipulator. Wu et al. [97] used HOL4 to formally reason about the forward kinematics of the 3-DOF planar robot manipulator. Similarly, Li et al. [53] provided the formal verification of the Collision-free Motion Planning Algorithm (CFMPA) of Dual-arm Robot (DAR) using HOL4. Walter et al. [95] formally verified a collision-avoidance algorithm for service robots in Isabelle. The authors mainly formalized the safety zone of the robot based on the algorithm and used it to formally verify that the robot will stop upon facing an obstacle, otherwise, it will continue its movement within the safety zone. Recently, Rashid et al. [80] provided the formal modeling and analysis of the 2-DOF robotic cell injection systems using HOL Light.

#### 2.4 Formal Hybrid Analysis

Platzer et al. [70] developed an algorithm for the verification of the safety properties of CPS. The authors used the notion of continuous generalization of induction to compute the differential invariants, which do not require solving the differential equations capturing the dynamics of CPS. Moreover, they used their proposed algorithm for formally verifying the collision avoidance properties in car controls and aircraft roundabout maneuvers [71] using KeYmaera. Similarly, Platzer et al. [72] verified the safety, controllability, liveness, and reactivity properties of the European Train Control System (ETCS) protocol using KeYmaera. KeYmaera has also been widely used for the dynamical analysis of various CPS, such as a distributed car control system [59], freeway traffic control [67], autonomous robotic vehicles [66] and industrial airborne collision avoidance system [50]. Recently, Bohrer et al. [20] presented VeriPhy, a verified pipeline for automatically transforming verified models of CPS to verified controller executables. It proves CPS safety at runtime by verified monitors. All these analysis performed using KeYmaera are based on the differential dynamics logic, which captures both the continuous and discrete dynamics of CPS and their interaction. This logic allows the suitable automation of the verification process as well. Similarly, Foster et al. [34] proposed a framework for the verification of CPS based on Unifying Theories of Programming (UTP) and Isabelle/HOL. In particular, the authors provide the implementation of designs, reactive processes, and the hybrid relational calculus, which are important foundational theories for analyzing CPS.

# 3 Formal Probabilistic and Performance Analysis

Hasan et al. [45] proposed a higher-order logic framework for the probabilistic analysis of the systems using HOL4. The authors first formalized the standard uniform random variable [39]. Next, they used this random variable alongside a non-uniform random number generation method to formalize continuous uniform random variables. Finally, the authors used their proposed formalization for the probabilistic analysis of roundoff error in a digital processor [39]. Next, Hasan et al. [41] used HOL4 for the formal verification of the expectation and variance of the discrete random variable and used their expectation theory to formally reason about the Coupon Collector's problem [41]. Later, the authors extended their framework by providing the formal verification of the expectation properties of the continuous random variables, i.e., Uniform, Triangular and Exponential [37]. Next, the authors formalized the indicator random variables using HOL4 and used it for the expected time complexity analysis of various algorithms, i.e., the birthday paradox, the hat-check and the hiring problems [42]. Elleuch et al. [30] used the probability theory of HOL4 to formally reason about the detection properties of Wireless Sensor Networks (WSNs) and a WSN-based monitoring framework [31]. Moreover, the authors conducted the performance analysis of WSNs [29]. Hasan et al. also used their probability theory in HOL4 for conducting the performance analysis of Automatic-repeat-request (ARQ) protocols, i.e.,

Stop-and-Wait, Go-Back-N and Selective-Repeat protocols [40]. Finally, Hasan et al. [43] formalized the notion of conditional probability and formally verified its classical properties, i.e., Bayes' theorem and total probability law. The authors utilized their formalization for formally analyzing the binary asymmetric channel, which is widely used in communication systems. Mhamdi et al. [63] formalized the Lebesgue integral using HOL4 and used it for formally verifying the Markov and Chebyshev inequalities, and the Weak Law of Large Numbers (WLLN) theorem. Next, the authors built upon Lebesgue integral to formalize the Radon-Nikodym derivative and used it for formalizing the fundamentals of information theory, i.e., Shannon and relative entropies [64]. Later, Mhamdi et al. [65] used the probabilistic analysis support developed in HOL4 to evaluate the security properties of the confidentiality protocols. A library for the formal probabilistic analysis has also been developed in Isabelle. Holzl et al. [47] formalized measure theory with extended real numbers as measure values, in particular, the authors formalized Lebesgue integral, product measures and Fubini's theorem using Isabelle. Eberl et al. [24] developed an inductive compiler, which takes programs in a probabilistic functional language and computes density functions for the probability spaces using Isabelle. Similarly, Holzl et al. [48] proposed a formalization of Markov chains and used it to formally verify the ZeroConf and the Crowds protocols using Isabelle.

# 4 Formal Dependability Analysis

Hasan et al. [46] formalized some fundamental concepts about the reliability theory in HOL4 and used it for formal reliability analysis of reconfigurable memory arrays in the presence of stuck-at and coupling faults. Moreover, the authors performed the reliability analysis of the combinational circuits, such as full adders, comparators and multiplier. Later, Abbasi et al. [3] extended the reliability analysis framework by formally verifying some statistical properties, i.e., second moment and variance and other reliability concepts, i.e., survival, hazard and fractile functions. The authors utilized their proposed framework for formally analyzing the essential electronic and electrical system components.

Liu et al. [56] proposed a framework to reason about the finite-state discrete-time Markov chains using HOL4 and formally verified some of its properties such as joint and steady-state probabilities, and reversibility. The authors utilized their proposed framework to formally analyze a binary communication channel and an automatic mail quality measurement protocol [58]. Next, the authors formalized the discrete-time Markov reward models and used it to formally reason about the memory contention problem of a multi-processor system [57]. Later, the authors proposed a framework to formally reason about the properties of the Hidden Markov Models (HMMs) such as joint probabilities and formally analyzed a DNA sequence [55].

Ahmad et al. [9] developed a higher-order logic based framework for the formal dependability analysis using probability theory of HOL4. The proposed analysis provides the failure characteristics of the systems, i.e., reliability, availability, maintainability, etc. The authors formalized the Reliability Block Diagrams

(RBD) [11], which are the graphical representations providing the functional behaviour of a system modules and their interconnections. The proposed formalization of RBD has been used for formally analyzing a simple oil and gas pipeline, a generic Virtual Data Center (VDC) [13], Reliable Multi-Segment Transport (RMST) data transport, Event to Sink Reliable Transport (ESRT) protocols [12] and Logistics Service Supply Chains (LSSCs) [10]. Similarly, Ahmad et al. [7] proposed a framework for the formal fault tree analysis using HOL4. The authors formalized the fault tree gates, i.e., AND, OR, NAND, NOR, XOR and NOT and formally verified their generic expressions for probabilities failures. Moreover, their proposed framework was used to perform the fault tree analysis of a solar array, which is used as a major source of power in the Dong Fang Hong-3 (DFH-3) satellite [7] and a communication gateway software for the next generation Air Traffic Management System (ATMS) [8].

Elderhalli et al. [26] developed a higher-order logic based framework for the formal dynamic dependability analysis using HOL4. The proposed analysis provides the dynamic failure characteristics of the systems, i.e., dynamic reliability and fault trees, etc. The authors formalized the Dynamic Fault Trees (DFTs) [25] and Dynamic Reliability Block Diagrams (DRBD) [27] using HOL4. Moreover, they used their proposed formalization for formally analyzing the Drive-by-wire System (DBW), a Shuffle-exchange Network (SEN) and Cardiac Assist System (CAS) [28].

## 5 Theorem Proving Support for CPS

Table 1 summarizes the formal libraries that are available in various theorem provers for performing the formal analysis of CPS. For example, the formal support for the dependability analysis of systems is only available in HOL4. Similarly, the libraries to formally reason about robotics and software components are available in most of the theorem provers. KeyMaera provides a support for formally analyzing the hybrid systems. Moreover, HOL4 and Isabelle theorem provers have a quite dense library for probabilistic and performance analyses

|                          |      | 1         | I            | 1   |     |          |

|--------------------------|------|-----------|--------------|-----|-----|----------|

| Analysis/Theorem provers | HOL4 | HOL light | Isabelle/HOL | Coq | PVS | Keymaera |

| Transform methods        | 1    | ✓         | 1            | 1   |     |          |

| Probabilistic analysis   | 1    |           | ✓            |     |     |          |

| Performance analysis     | 1    |           | 1            |     |     |          |

| Dependability analysis   | 1    |           |              |     |     |          |

| Hybrid systems           |      |           |              |     |     | 1        |

| Optical systems          |      | 1         |              |     |     |          |

| Quantum systems          |      | 1         | 1            | 1   |     |          |

| Robotic systems          | 1    | 1         | 1            |     | 1   | ✓        |

| Software components      | 1    | 1         | 1            |     | 1   | 1        |

**Table 1.** Libraries for formal analysis in major theorem provers

of systems. Similarly, the transform methods are partially available in Isabelle, Coq and HOL4 theorem provers, i.e., only the Laplace transform is formalized in these theorem provers. However, HOL Light contains formal libraries for most of the transform methods, i.e., Laplace, Fourier and z-transforms. Also, the formal library for analyzing the optical systems is only available in HOL Light.

# 6 Conclusion

CPS are highly complex systems composed of actuators, sensors, and several electronic, communication and controller modules, and exhibit both the continuous and discrete dynamics. Due to the safety critical-nature of CPS, their accurate analysis is of utmost importance. This paper surveys some of the efforts that have been done regarding the formal verification of CPS using theorem proving by highlighting the aspects of CPS that have been verified using different theorem provers. In this regard, only one dedicated theorem prover, KeYmaera, has been developed for analyzing hybrid systems. However, we need to develop dedicated formal libraries in other theorem provers that can support the analysis of hybrid systems, i.e., incorporating the interlinked discrete and continuous-time features of a CPS simultaneously.

# References

- (2018). https://arstechnica.com/tech-policy/2018/05/report-software-bug-led-to-death-in-ubers-self-driving-crash/?amp=1

- 2. (2020). https://www.2b1stconsulting.com/cyber-physical-systems-cps/

- Abbasi, N., Hasan, O., Tahar, S.: An approach for lifetime reliability analysis using theorem proving. J. Comput. Syst. Sci. 80(2), 323–345 (2014)

- 4. Affeldt, R., Cohen, C.: Formal foundations of 3D geometry to model robot manipulators. In: Certified Programs and Proofs, pp. 30–42. ACM (2017)

- Afshar, S.K., Aravantinos, V., Hasan, O., Tahar, S.: Formalization of complex vectors in higher-order logic. In: Watt, S.M., Davenport, J.H., Sexton, A.P., Sojka, P., Urban, J. (eds.) CICM 2014. LNCS (LNAI), vol. 8543, pp. 123–137. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08434-3\_10

- Afshar, S.K., et al.: Formal analysis of optical systems. Math. Comput. Sci. 8(1), 39–70 (2014)

- Ahmed, W., Hasan, O.: Towards formal fault tree analysis using theorem proving. In: Kerber, M., Carette, J., Kaliszyk, C., Rabe, F., Sorge, V. (eds.) CICM 2015. LNCS (LNAI), vol. 9150, pp. 39–54. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-20615-8\_3

- Ahmed, W., Hasan, O.: Formalization of fault trees in higher-order logic: a deep embedding approach. In: Fränzle, M., Kapur, D., Zhan, N. (eds.) SETTA 2016. LNCS, vol. 9984, pp. 264–279. Springer, Cham (2016). https://doi.org/10.1007/ 978-3-319-47677-3\_17

- 9. Ahmed, W., Hasan, O., Tahar, S.: Formal dependability modeling and analysis: a survey. In: Kohlhase, M., Johansson, M., Miller, B., de Moura, L., Tompa, F. (eds.) CICM 2016. LNCS (LNAI), vol. 9791, pp. 132–147. Springer, Cham (2016). https://doi.org/10.1007/978-3-319-42547-4\_10

- Ahmad, W., Hasan, O., Tahar, S., Hamdi, M.: Towards formal reliability analysis

of logistics service supply chains using theorem proving. In: Implementation of

Logics, pp. 111–121 (2015)

- Ahmed, W., Hasan, O., Tahar, S., Hamdi, M.S.: Towards the formal reliability analysis of oil and gas pipelines. In: Watt, S.M., Davenport, J.H., Sexton, A.P., Sojka, P., Urban, J. (eds.) CICM 2014. LNCS (LNAI), vol. 8543, pp. 30–44. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08434-3\_4

- 12. Ahmed, W., Hasan, O., Tahar, S.: Formal reliability analysis of wireless sensor network data transport protocols using HOL. In: Wireless and Mobile Computing, Networking and Communications, pp. 217–224. IEEE (2015)

- Ahmed, W., Hasan, O., Tahar, S.: Formalization of reliability block diagrams in higher-order logic. J. Appl. Logic 18, 19–41 (2016)

- Baier, C., Katoen, J.P., Larsen, K.G.: Principles of Model Checking. MIT Press, Cambridge (2008)

- 15. Beillahi, S.M., Mahmoud, M.Y., Tahar, S.: Hierarchical verification of quantum circuits. In: Rayadurgam, S., Tkachuk, O. (eds.) NFM 2016. LNCS, vol. 9690, pp. 344–352. Springer, Cham (2016). https://doi.org/10.1007/978-3-319-40648-0\_26

- 16. Beillahi, S.M., Siddique, U., Tahar, S.: Towards the Application of Formal Methods in Process Engineering. In: Fun With Formal Methods, pp. 1–11 (2014)

- 17. Beillahi, S.M., Siddique, U., Tahar, S.: Formal analysis of power electronic systems. In: Butler, M., Conchon, S., Zaïdi, F. (eds.) ICFEM 2015. LNCS, vol. 9407, pp. 270–286. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-25423-4\_17

- Beillahi, S.M., Siddique, U., Tahar, S.: Formal analysis of engineering systems based on signal-flow-graph theory. In: Bogomolov, S., Martel, M., Prabhakar, P. (eds.) NSV 2016. LNCS, vol. 10152, pp. 31–46. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-54292-8\_3

- Bertot, Y., Castéran, P.: Interactive Theorem Proving and Program Development: Coq'Art: the Calculus of Inductive Constructions. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-662-07964-5

- Bohrer, B., Tan, Y.K., Mitsch, S., Myreen, M.O., Platzer, A.: VeriPhy: verified controller executables from verified cyber-physical system models. In: Programming Language Design and Implementation, pp. 617–630 (2018)

- 21. Clarke, E.M., Zuliani, P.: Statistical model checking for cyber-physical systems. In: Bultan, T., Hsiung, P.-A. (eds.) ATVA 2011. LNCS, vol. 6996, pp. 1–12. Springer, Heidelberg (2011). https://doi.org/10.1007/978-3-642-24372-1\_1

- 22. Cofer, D., et al.: A formal approach to constructing secure air vehicle software. Computer 51(11), 14-23 (2018)

- 23. Durán, A.J., Pérez, M., Varona, J.L.: Misfortunes of a mathematicians' Trio using computer algebra systems: can we trust? CoRR abs/1312.3270 (2013)

- 24. Eberl, M., Hölzl, J., Nipkow, T.: A verified compiler for probability density functions. In: Vitek, J. (ed.) ESOP 2015. LNCS, vol. 9032, pp. 80–104. Springer, Heidelberg (2015). https://doi.org/10.1007/978-3-662-46669-8\_4

- Elderhalli, Y., Ahmad, W., Hasan, O., Tahar, S.: Probabilistic analysis of dynamic fault trees using HOL theorem proving. J. Appl. Logic-IfCoLog J. Logics Appl. 6(3), 469–512 (2019)

- Elderhalli, Y., Hasan, O., Ahmad, W., Tahar, S.: Formal dynamic fault trees analysis using an integration of theorem proving and model checking. In: Dutle, A., Muñoz, C., Narkawicz, A. (eds.) NFM 2018. LNCS, vol. 10811, pp. 139–156. Springer, Cham (2018). https://doi.org/10.1007/978-3-319-77935-5\_10

- Elderhalli, Y., Hasan, O., Tahar, S.: A formally verified algebraic approach for dynamic reliability block diagrams. In: Ait-Ameur, Y., Qin, S. (eds.) ICFEM 2019. LNCS, vol. 11852, pp. 253–269. Springer, Cham (2019). https://doi.org/10.1007/ 978-3-030-32409-4\_16

- 28. Elderhalli, Y., Hasan, O., Tahar, S.: A methodology for the formal verification of dynamic fault trees using HOL theorem proving. IEEE Access 7, 136176–136192 (2019)

- Elleuch, M., Hasan, O., Tahar, S., Abid, M.: Towards the formal performance analysis of wireless sensor networks. In: Enabling Technologies: Infrastructure for Collaborative Enterprises, pp. 365–370. IEEE (2013)

- Elleuch, M., Hasan, O., Tahar, S., Abid, M.: Formal probabilistic analysis of detection properties in wireless sensor networks. Formal Aspects Comput. 27(1), 79–102 (2015)

- 31. Elleuch, M., Hasan, O., Tahar, S., Abid, M.: Formal probabilistic analysis of a WSN-based monitoring framework for IoT Applications. In: Artho, C., Ölveczky, P.C. (eds.) FTSCS 2016. CCIS, vol. 694, pp. 93–108. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-53946-1\_6

- 32. Farooq, B., Hasan, O., Iqbal, S.: Formal kinematic analysis of the two-link planar manipulator. In: Groves, L., Sun, J. (eds.) ICFEM 2013. LNCS, vol. 8144, pp. 347–362. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-642-41202-8-23

- Fisher, K., Launchbury, J., Richards, R.: The HACMS program: using formal methods to eliminate exploitable bugs. Philos. Trans. Roy. Soc. A Math. Phys. Eng. Sci. 375(2104), 20150401 (2017)

- Foster, S., Woodcock, J.: Towards verification of cyber-physical systems with UTP and Isabelle/HOL. In: Gibson-Robinson, T., Hopcroft, P., Lazić, R. (eds.) Concurrency, Security, and Puzzles. LNCS, vol. 10160, pp. 39–64. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-51046-0\_3

- 35. Harrison, J.: Handbook of Practical Logic and Automated Reasoning. Cambridge University Press, Cambridge (2009)

- Harrison, J.: HOL light: a tutorial introduction. In: Srivas, M., Camilleri, A. (eds.)

FMCAD 1996. LNCS, vol. 1166, pp. 265–269. Springer, Heidelberg (1996). https://doi.org/10.1007/BFb0031814

- 37. Hasan, O., Abbasi, N., Akbarpour, B., Tahar, S., Akbarpour, R.: Formal reasoning about expectation properties for continuous random variables. In: Cavalcanti, A., Dams, D.R. (eds.) FM 2009. LNCS, vol. 5850, pp. 435–450. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-05089-3\_28

- 38. Hasan, O., Khan Afshar, S., Tahar, S.: Formal analysis of optical waveguides in HOL. In: Berghofer, S., Nipkow, T., Urban, C., Wenzel, M. (eds.) TPHOLs 2009. LNCS, vol. 5674, pp. 228–243. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-03359-9\_17

- 39. Hasan, O., Tahar, S.: Formalization of the standard uniform random variable. Theoret. Comput. Sci. **382**(1), 71–83 (2007)

- Hasan, O., Tahar, S.: Performance analysis of ARQ protocols using a theorem prover. In: Performance Analysis of Systems and Software, pp. 85–94. IEEE (2008)

- 41. Hasan, O., Tahar, S.: Using theorem proving to verify expectation and variance for discrete random variables. J. Autom. Reasoning 41(3–4), 295–323 (2008)

- 42. Hasan, O., Tahar, S.: Formally analyzing expected time complexity of algorithms using theorem proving. J. Comput. Sci. Technol. **25**(6), 1305–1320 (2010)

- 43. Hasan, O., Tahar, S.: Reasoning about conditional probabilities in a higher-order-logic theorem prover. J. Appl. Logic 9(1), 23–40 (2011)

- 44. Hasan, O., Tahar, S.: Formal Verification Methods. In: Encyclopedia of Information Science and Technology, pp. 7162–7170. IGI Global Publication (2015)

- 45. Hasan, O., Tahar, S.: Formalized Probability Theory and Applications Using Theorem Proving. IGI Global, Pennsylvania (2015)

- 46. Hasan, O., Tahar, S., Abbasi, N.: Formal reliability analysis using theorem proving. IEEE Trans. Comput. **59**(5), 579–592 (2010)

- 47. Hölzl, J., Heller, A.: Three chapters of measure theory in Isabelle/HOL. In: van Eekelen, M., Geuvers, H., Schmaltz, J., Wiedijk, F. (eds.) ITP 2011. LNCS, vol. 6898, pp. 135–151. Springer, Heidelberg (2011). https://doi.org/10.1007/978-3-642-22863-6\_12

- 48. Hölzl, J., Nipkow, T.: Interactive verification of Markov Chains: two distributed protocol case studies. arXiv preprint arXiv:1212.3870 (2012)

- 49. Immler, F.: Laplace transform archive of formal proofs (2018). https://www.isa-afp.org/entries/Laplace\_Transform.html

- 50. Jeannin, J.B., et al.: Formal verification of ACAS X, an industrial airborne collision avoidance system. In: Embedded Software, pp. 127–136. IEEE (2015)

- Khan-Afshar, S., Hasan, O., Tahar, S.: Formal analysis of electromagnetic optics.

In: Novel Optical Systems Design and Optimization XVII, vol. 9193, p. 91930A.

International Society for Optics and Photonics (2014)

- 52. Klein, G., et al.: SeL4: formal verification of an OS kernel. In: Operating Systems Principles, pp. 207–220. ACM (2009)

- Li, Li, Shi, Z., Guan, Y., Zhao, C., Zhang, J., Wei, H.: Formal verification of a collision-free algorithm of dual-arm robot in HOL4. In: Robotics and Automation, pp. 1380–1385. IEEE (2014)

- 54. Liu, J., et al.: Formal verification of quantum algorithms using quantum hoare logic. In: Dillig, I., Tasiran, S. (eds.) CAV 2019. LNCS, vol. 11562, pp. 187–207. Springer, Cham (2019). https://doi.org/10.1007/978-3-030-25543-5\_12

- Liu, L., Aravantinos, V., Hasan, O., Tahar, S.: On the formal analysis of HMM using theorem proving. In: Merz, S., Pang, J. (eds.) ICFEM 2014. LNCS, vol. 8829, pp. 316–331. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-11737-9\_21

- Liu, L., Hasan, O., Tahar, S.: Formalization of finite-state discrete-time Markov Chains in HOL. In: Bultan, T., Hsiung, P.-A. (eds.) ATVA 2011. LNCS, vol. 6996, pp. 90–104. Springer, Heidelberg (2011). https://doi.org/10.1007/978-3-642-24372-1.8

- 57. Liu, L., Hasan, O., Tahar, S.: Formal analysis of memory contention in a multiprocessor system. In: Iyoda, J., de Moura, L. (eds.) SBMF 2013. LNCS, vol. 8195, pp. 195–210. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-642-41071-0\_14

- Liu, L., Hasan, O., Tahar, S.: Formal reasoning about finite-state discrete-time Markov Chains in HOL. J. Comput. Sci. Technol. 28(2), 217–231 (2013)

- Loos, S.M., Platzer, A., Nistor, L.: Adaptive cruise control: hybrid, distributed, and now formally verified. In: Butler, M., Schulte, W. (eds.) FM 2011. LNCS, vol. 6664, pp. 42–56. Springer, Heidelberg (2011). https://doi.org/10.1007/978-3-642-21437-0\_6

- Mahmoud, M.Y., Aravantinos, V., Tahar, S.: Formalization of infinite dimension linear spaces with application to quantum theory. In: Brat, G., Rungta, N., Venet, A. (eds.) NFM 2013. LNCS, vol. 7871, pp. 413–427. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-642-38088-4-28

- Mahmoud, M.Y., Aravantinos, V., Tahar, S.: Formal verification of optical quantum flip gate. In: Klein, G., Gamboa, R. (eds.) ITP 2014. LNCS, vol. 8558, pp. 358–373. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08970-6\_23

- 62. Yousri Mahmoud, M., Tahar, S.: On the quantum formalization of coherent light in HOL. In: Badger, J.M., Rozier, K.Y. (eds.) NFM 2014. LNCS, vol. 8430, pp. 128–142. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-06200-6\_10

- 63. Mhamdi, T., Hasan, O., Tahar, S.: On the formalization of the Lebesgue integration theory in HOL. In: Kaufmann, M., Paulson, L.C. (eds.) ITP 2010. LNCS, vol. 6172, pp. 387–402. Springer, Heidelberg (2010). https://doi.org/10.1007/978-3-642-14052-5\_27

- 64. Mhamdi, T., Hasan, O., Tahar, S.: Formalization of entropy measures in HOL. In: van Eekelen, M., Geuvers, H., Schmaltz, J., Wiedijk, F. (eds.) ITP 2011. LNCS, vol. 6898, pp. 233–248. Springer, Heidelberg (2011). https://doi.org/10.1007/978-3-642-22863-6\_18

- 65. Mhamdi, T., Hasan, O., Tahar, S.: Evaluation of anonymity and confidentiality protocols using theorem proving. Formal Meth. Syst. Des. 47(3), 265–286 (2015)

- 66. Mitsch, S., Ghorbal, K., Platzer, A.: On provably safe obstacle avoidance for autonomous robotic ground vehicles. In: Robotics: Science and Systems (2013)

- 67. Mitsch, S., Loos, S.M., Platzer, A.: Towards formal verification of freeway traffic control. In: Cyber-Physical Systems, pp. 171–180. IEEE Computer Society (2012)

- Owre, S., Rushby, J.M., Shankar, N.: PVS: a prototype verification system. In: Kapur, D. (ed.) CADE 1992. LNCS, vol. 607, pp. 748–752. Springer, Heidelberg (1992). https://doi.org/10.1007/3-540-55602-8\_217

- 69. Paulson, L.C.: Isabelle: A Generic Theorem Prover, vol. 828. Springer, Heidelberg (1994). https://doi.org/10.1007/BFb0030541

- Platzer, A., Clarke, E.M.: Computing differential invariants of hybrid systems as fixedpoints. Formal Meth. Syst. Des. 35(1), 98–120 (2009)

- Platzer, A., Clarke, E.M.: Formal verification of curved flight collision avoidance maneuvers: a case study. In: Cavalcanti, A., Dams, D.R. (eds.) FM 2009. LNCS, vol. 5850, pp. 547–562. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-05089-3\_35

- Platzer, A., Quesel, J.-D.: European train control system: a case study in formal verification. In: Breitman, K., Cavalcanti, A. (eds.) ICFEM 2009. LNCS, vol. 5885, pp. 246–265. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-10373-5\_13

- 73. Platzer, A., Quesel, J.-D.: KeYmaera: a hybrid theorem prover for hybrid systems (system description). In: Armando, A., Baumgartner, P., Dowek, G. (eds.) IJCAR 2008. LNCS (LNAI), vol. 5195, pp. 171–178. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-71070-7-15

- 74. Rajkumar, R., Lee, I., Sha, L., Stankovic, J.: Cyber-physical systems: the next computing revolution. In: Design Automation Conference, pp. 731–736. IEEE (2010)

- Rand, R., Paykin, J., Zdancewic, S.: QWIRE practice: formal verification of quantum circuits in COQ. arXiv preprint arXiv:1803.00699 (2018)

- Rashid, A., Hasan, O.: Formalization of Lerch's theorem using HOL light. J. Appl. Logics-IFCoLog J. Logics Appl. 5(8), 1623–1652 (2018)

- Rashid, A., Hasan, O.: On the formalization of fourier transform in higher-order logic. In: Blanchette, J.C., Merz, S. (eds.) ITP 2016. LNCS, vol. 9807, pp. 483–490. Springer, Cham (2016). https://doi.org/10.1007/978-3-319-43144-4\_31

- Rashid, A., Hasan, O.: Formal analysis of continuous-time systems using Fourier transform. arXiv preprint arXiv:1707.09941 (2017)

- Rashid, A., Hasan, O.: Formal analysis of linear control systems using theorem proving. In: Duan, Z., Ong, L. (eds.) ICFEM 2017. LNCS, vol. 10610, pp. 345–361. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-68690-5\_21

- Rashid, A., Hasan, O.: Formal analysis of robotic cell injection systems using theorem proving. In: Chamberlain, R., Taha, W., Törngren, M. (eds.) CyPhy 2017.

LNCS, vol. 11267, pp. 127–141. Springer, Cham (2019). https://doi.org/10.1007/978-3-030-17910-6\_10

- Rashid, A., Hasan, O.: Formalization of transform methods using HOL light. In: Geuvers, H., England, M., Hasan, O., Rabe, F., Teschke, O. (eds.) CICM 2017. LNCS (LNAI), vol. 10383, pp. 319–332. Springer, Cham (2017). https://doi.org/ 10.1007/978-3-319-62075-6-22

- 82. Siddique, U., Aravantinos, V., Tahar, S.: Formal stability analysis of optical resonators. In: Brat, G., Rungta, N., Venet, A. (eds.) NFM 2013. LNCS, vol. 7871, pp. 368–382. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-642-38088-4\_25

- Siddique, U., Beillahi, S.M., Tahar, S.: On the formal analysis of photonic signal processing systems. In: Núñez, M., Güdemann, M. (eds.) FMICS 2015. LNCS, vol. 9128, pp. 162–177. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-19458-5\_11

- Siddique, U., Mahmoud, M.Y., Tahar, S.: On the formalization of Z-transform in HOL. In: Klein, G., Gamboa, R. (eds.) ITP 2014. LNCS, vol. 8558, pp. 483–498.

Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08970-6-31

- 85. Siddique, U., Mahmoud, M.Y., Tahar, S.: Formal analysis of discrete-time systems using Z-transform. J. Appl. Logics-IFCoLog J. Logics Appl. 5(4), 875–906 (2018)

- 86. Siddique, U., Tahar, S.: A framework for formal reasoning about geometrical optics. In: Watt, S.M., Davenport, J.H., Sexton, A.P., Sojka, P., Urban, J. (eds.) CICM 2014. LNCS (LNAI), vol. 8543, pp. 453–456. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08434-3\_38

- 87. Siddique, U., Tahar, S.: Towards ray optics formalization of optical imaging systems. In: Information Reuse and Integration, pp. 378–385. IEEE (2014)

- 88. Siddique, U., Tahar, S.: Towards the formal analysis of microresonators based photonic systems. In: Design, Automation & Test in Europe, pp. 1–6. IEEE/ACM (2014)

- Siddique, U., Tahar, S.: On the formalization of cardinal points of optical systems.

In: Bouabana-Tebibel, T., Rubin, S.H. (eds.) Formalisms for Reuse and Systems Integration. AISC, vol. 346, pp. 79–102. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-16577-6\_4

- 90. Siddique, U., Tahar, S.: On the formal analysis of gaussian optical systems in HOL. Formal Aspects Comput. **28**(5), 881–907 (2016)

- Siddique, U., Tahar, S.: Formal verification of stability and chaos in periodic optical systems. J. Comput. Syst. Sci. 88, 271–289 (2017)

- Slind, K., Norrish, M.: A brief overview of HOL4. In: Mohamed, O.A., Muñoz, C., Tahar, S. (eds.) TPHOLs 2008. LNCS, vol. 5170, pp. 28–32. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-71067-7\_6

- Taqdees, S.H., Hasan, O.: Formalization of laplace transform using the multivariable calculus theory of HOL-light. In: McMillan, K., Middeldorp, A., Voronkov, A. (eds.) LPAR 2013. LNCS, vol. 8312, pp. 744–758. Springer, Heidelberg (2013). https://doi.org/10.1007/978-3-642-45221-5\_50

- 94. Taqdees, S.H., Hasan, O.: Formally verifying transfer functions of linear analog circuits. IEEE Des. Test **34**(5), 30–37 (2017)

- 95. Walter, D., Täubig, H., Lüth, C.: Experiences in applying formal verification in robotics. In: Schoitsch, E. (ed.) SAFECOMP 2010. LNCS, vol. 6351, pp. 347–360. Springer, Heidelberg (2010). https://doi.org/10.1007/978-3-642-15651-9\_26

- 96. Wang, Y., Chen, G.: Formalization of Laplace transform in COQ. In: Dependable Systems and Their Applications, pp. 13–21. IEEE (2017)

- 97. Wu, A., Shi, Z., Yang, X., Guan, Y., Li, Y., Song, X.: Formalization and analysis of Jacobian matrix in screw theory and its application in kinematic singularity. In: Intelligent Robots and Systems, pp. 2835–2842. IEEE (2017)

# Formal Development of Multi-Purpose Interactive Application (MPIA) for ARINC 661

Neeraj Kumar Singh<sup>1(⊠)</sup>, Yamine Aït-Ameur<sup>1</sup>, Dominique Méry<sup>2</sup>, David Navarre<sup>3</sup>, Philippe Palanque<sup>3</sup>, and Marc Pantel<sup>1</sup>

**Abstract.** This paper reports our experience for developing Human-Machine Interface (HMI) complying with ARINC 661 specification standard for interactive cockpits applications using formal methods. This development relies on the FLUID modelling language, we have proposed and formally defined in the FORMEDICIS project. FLUID contains essential features required for specifying HMI. To develop the Multi-Purpose Interactive Applications (MPIA) use case, we follow the following steps: an abstract model of MPIA is written using the FLUID language; this MPIA FLUID model is used to produce an Event-B model for checking the functional behaviour, user interactions, safety properties, and interaction related to domain properties; the Event-B model is also used to check temporal properties and possible scenario using the ProB model checker; and finally, the MPIA FLUID model is translated to Interactive Cooperative Objects (ICO) using the PetShop CASE tool to validate the dynamic behaviour, visual properties and task analysis. These steps rely on different tools to check internal consistency along with possible HMI properties. Finally, the formal development of the MPIA case study using FLUID and its embedding into other formal techniques, demonstrates reliability, scalability and feasibility of our approach defined in the FORMEDICIS project.

**Keywords:** Human-machine interface (HMI)  $\cdot$  Formal method  $\cdot$  Refinement and proofs  $\cdot$  Event-B  $\cdot$  PetShop  $\cdot$  Verification  $\cdot$  Validation  $\cdot$  Animation

#### 1 Introduction

Developing a human-machine interface (HMI) is a difficult and time-consuming task [22] due to complex system characteristics and user requirements, which require anticipating human behaviour, system components and operational environment. Moreover, the design principles of HMI are different from traditional software development processes, including techniques and tools [29]. Considering every aspect of the HMI development process in a single framework, from requirement analysis to implementation, is

<sup>©</sup> Springer Nature Switzerland AG 2020 O. Hasan and F. Mallet (Eds.): FTSCS 2019, CCIS 1165, pp. 21–39, 2020. https://doi.org/10.1007/978-3-030-46902-3\_2

a challenging task. Since a long time, formal methods play an importa role for analyzing system interaction [5,10,11], and their use has been widely adopted in the current development process of HMI. Yet, to our knowledge there is no standard approach that can be used to formally develop and design a safety-critical HMI from spec to code.

The ongoing project, ANR-FORMEDICIS [14] where our work takes place, aims to propose a suite that can be used for developing and designing safety-critical HMIs. In this project, we develop a pivot modelling language, FLUID (Formal Language of User Interface Design), for the formal specification of HMI based on state transitions systems allowing to express requirements, assumptions, expectations, nominal and non nminal properformal models in common languages can the be derived from a FLUID model for verification, validation, simulation and animation. The derived formal models use theorem provers and model checkers for analyzing the different required functional properties, nominal and non nominal properties, and scenarios. In our work, we use the Event-B [1] modelling language for producing an abstract formal model and the Pet-Shop CASE tool [27] for producing Interactive Cooperative Objects (ICO) model [23]. The produced models are analyzed with specific developed tools. Rodin [2] is used for Event-B models and PetShop for ICO models. The analyzed models provide feedback to the original FLUID model.

We propose to illustrate the FORMEDICIS approach applying it for the development of a complex case study issued from aircraft cockpit design: MPIA (Multi-Purpose Interactive Applications). First, we develop a FLUID model for MPIA and then we generate an Event-B model and an ICO model from the developed FLUID model. In this development, we begin by specifying different MPIA components, including functional behaviour, states, assumptions, expectations, interactions, properties and scenarios. The embedding of the formal FLUID development of MPIA in Event-B preserves the required behaviour in the developed model. In the generated model, we prove important properties, such as functional behaviour, user interactions, safety properties, and interaction related domain properties. We use the ProB model checker tool [21] to analyze and validate the developed models, and to check temporal properties and possible scenario for HMI. In the ICO model, we provide the dynamic behaviour of MPIA. The developed ICO specification fully describes the potential interactions that users may have with the application. It covers both input and output aspects related to users. In the ICO formalism, there are four components: a cooperative object which describes the behaviour of the object, a presentation part, activation function and rendering function to link between the cooperative object and the presentation part.

This paper is organized as follows. Section 2 presents the required background. Section 3 describes the FLUID language. Section 4 provides the selected MPIA case study. Section 5 presents a formal development of the case study in FLUID. Section 6 and Sect. 7 illustrates the formal developments of the FLUID model in Event-B and PetShop, respectively. In Sect. 8, we provide an assessment of our work and Sect. 9 presents related work. Finally, Sect. 10 concludes the paper with future work.

#### 2 Preliminaries

#### 2.1 The Modelling Framework: Event-B

This section describes the modelling components of the Event-B language [1]. The Event-B language contains two main components, context for describing the static properties of a system using carrier sets s, constants c, axioms A(s,c) and theorems  $T_c(s,c)$ , and machine for describing behavioural properties of a system using variables v, invariants I(s,c,v), theorems  $T_m(s,c,v)$ , variants V(s,c,v) and events evt. A context can be extended by another context, a machine can be refined by another machine and a machine can use sees relation to include other contexts.

An Event-B model is characterized by a list of *state variables* possibly modified by a list of *events*. A set of invariants I(s,c,v) shows typing invariants and the required safety properties that must be preserved by the defined system. A set of events presents a state transition in which each event is composed of guard(s) G(s,c,v,x) and action(s) v: |BA(s,c,v,x,v'). A *guard* is a predicate, built on state variables, for enabling the event's action(s). An action is a generalized substitution that describes the ways one or several state variables are modified by the occurrence of an event.

The Event-B modelling language supports the *correct by construction* approach to design an abstract model and a series of refined models for developing any large and complex system. Refinements, introduced by the REFINES clause, transform an abstract model to a more concrete version by modifying the state description. A refinement allows modelling a system gradually by introducing safety properties at various refinement levels. New variables and new events may be introduced in a new refinement level. These refinements preserve the relation between the refining model and its corresponding refined concrete model, while introducing new events and variables to specify more concrete behavior of a system. The defined abstract and concrete state variables are linked by introducing the *gluing invariants*. The generated proof obligations ensure that each abstract event is correctly refined by its concrete version.

Rodin [2] is an integrated development environment (IDE) for the Event-B modelling language based on Eclipse. It includes project management, stepwise model development, proof assistance, model checking, animation and automatic code generation. Once an Event-B model is modelled and syntactically checked on the Rodin platform then a set of proof obligations (POs) is generated using the Rodin proof engine. Event-B supports different kinds of proof obligations, such as invariant preservation, non-deterministic action feasibility, guard strengthening in refinements, simulation, variant, well-definedness etc. More details related to the modelling language and proof obligations can be found in [1].

#### 2.2 ICO Notation and PetShop CASE Tool

This section recalls the main features of the Interactive Cooperative Objects (ICOs) formal description technique used for modelling software of interactive systems. ICO is dedicated to the specification of interactive systems [23]. It uses concepts borrowed from the object-oriented approach (dynamic instantiation, classification, encapsulation,

inheritance, client/server relationship) to describe the structural or static aspects of systems, and uses high-level Petri nets to describe their dynamic or behavioural aspects.

ICOs are dedicated to the modelling and the implementation of event-driven interfaces, using several communicating objects to model the system, where both behavior of objects and communication protocol between objects are described by the Petri net dialect called Cooperative Objects (CO). In the ICO formalism, an object is an entity featuring four components: a cooperative object which describes the behavior of the object, a presentation part (i.e. the graphical interface), and two functions (the activation function and the rendering function) which make the link between the cooperative object and the presentation part.

An ICO specification fully describes the potential interactions that users may have with the application. The specification encompasses both the "input" aspects of the interaction (i.e. how user actions impact on the inner state of the application, and which actions are enabled at any given time) and its "output" aspects (i.e. when and how the application displays information relevant to the user). These aspects are expressed by means of the activation function (for input) and the rendering function (for output). ICOs description do not integrate graphical rendering of information and objects. This is usually delegated to Java code or to other description techniques such as UsiXML [9]. The ICO notation is fully supported by a CASE tool called PetShop [27]. All the models presented in the next sections have been edited and simulated using PetShop. Some formal analysis is also supported by the tool but limited to the underlying Petri net, removing the specificities brought by the high-level Petri net model.

# 3 FLUID Language

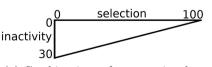

The FLUID language<sup>1</sup> developed in the FORMEDICIS project is organized in three main parts to describe *static*, *dynamic* and *requirements*. The static part defines type definition, constant, sets and the required features for interactions. The dynamic part defines a state-transition system for describing interactive system. The requirements part expresses the required behaviour, including user tasks and scenarios. A FLUID model is an INTERACTION module which is composed of six sections (see Fig. 1). The first three sections, DECLARATION, ASSUMPTIONS and EXPECTATIONS, describe the static part of a model. The following STATE and EVENT sections describe the dynamic part of a model, and the last REQUIREMENT section describes the requirement part of a model. The DECLARATION section allows to define new typing information that can be used to describe a HMI model.

The typing information may depend on generic and abstract types, such as sets, constants, enumerated sets, and natural and integer numbers. The STATE section declares a list of variables, which are classified as Input, Output, SysInput and SysOutput. The interactions between system and user can be characterized by the Input and Output variables while the interactions between system components can be characterized by SysInput and SysOutput variables. Note that all these variables can be tagged using domain knowledge concepts borrowed from an external knowledge.

<sup>&</sup>lt;sup>1</sup> Deliverable D1.1a: Language specification Preliminary version.

Model using the @taq (i.e. Enabled, Visible, Checked, Colors) to make explicit the HMI domain properties of HMI components. The EVENT section describes a set of events to present a state transition in which each event is composed of guard(s) and action(s). All these events are also categorized as acquisition, presentation and internal events. Acquisition events model acquisition operations of HMI component by modifying the acquisition state variables. Similarly, the presentation events model presentation operation by modifying the presentation state variables. The internal events model internal operations by modifying the internal state variables. These classification of events allow to check reactive properties, such as one stating that every acquisition is immediately followed by a presentation event or an internal event. This section also contains an INITIALISATION event to set initial values.

```

INTERACTION Component_Name

DECLARATION

SETS s

CONSTANT c

STATE

Input State Variables

Output State Variables

SysInput State Variables

SysOutput State Variables

//A variable without @tag

v@tag

//A variables with domain specific @taq

EVENTS

INIT

Acauisition Events

Presentation Events

Internal Frents

Event evt@taq[x]

where

G(s, c, v, x, v@taq, x@taq)

then

v: |BA(s, c, v, x, v', v@tag, x@tag, v'@tag)|

end

ASSUMPTIONS

A(s,c)

EXPECTATIONS

Exp(s,c)

REQUIREMENTS

PROPERTIES

Prop(s, c, v, v@tag)

SCENARIOS

NOMINAL

SC(s, c, v, v@tag)

NON NOMINAL

NSC(s, c, v, v@taq)

END Component_Name

```

Fig. 1. FLUID model structure

The ASSUMPTIONS section introduces the required assumptions related to environment that includes the user and machine agents. These assumptions can be expressed as logical properties to express HMI properties. The EXPECTATIONS section describes *prescriptive* statements that are expected to be fulfilled by parts of the environment of an interactive system. Note that the assumptions and expectations can be expressed in the same way, but both are different. The REQUIREMENTS section is divided into two subsections, known as PROPERTIES and SCENARIOS. The PROPERTIES section describes in logic all the required properties of an interactive system that must be preserved by a defined system. The SCENARIOS section describes both nominal and non-nominal scenarios using algebraic expressions, close to CTT [28], for analyzing possible acceptable and non-acceptable interactions.

# 4 MPIA Case Study

ARINC 661 is a standard, designed by the Airlines Electronic Engineering Committee (AEEC), for normalizing the definition of a Cockpit Display System (CDS) [6] and it provides guidelines for developing the CDS independently from the aircraft systems. The CDS provides graphical and interactive services to use applications within the flight

deck environment. It controls user-system interaction by integrating input devices, such as keyboard and mouse.

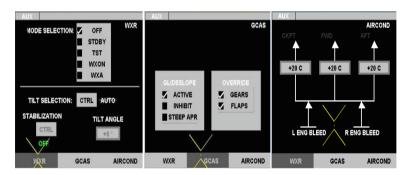

We present the Multi-Purpose Interactive Application (MPIA) that complies with ARINC 661 standard to demonstrate our formal modelling and verification approach considering several software engineering concepts related to HMI. Figure 2 depicts MPIA which is a real User Application (UA) for handling several flight parameters. This application contains a tabbed panel with three tabs, WXR for managing weather radar information, GCAS for Ground Collision Avoidance System parameters and AIR-COND for dealing with air conditioning settings. A crew member is allowed to switch to any mode (see Fig. 2) using tabs. These tabs have three different applications which can be controlled by the pilot and the co-pilot using any input devices.

The MPIA window of any tab is composed of three main parts: *information area*, workspace area and menu bar. The information area is the top bar of any tab that splits in two parts for displaying the current state of the application on the left part and the error messages, actions in progress or bad manipulation when necessary on the right part. The workspace area shows changes according to the selected interactive control panel. For example, WXR workspace displays all the modifiable parameters of the weather radar sensor, GCAS workspace shows some of the working modes of GCAS, and AIRCOND workspace displays the selected temperature inside an aircraft. The menu bar area contains three tabs for accessing the interactive control panels related to WXR, GCAS and AIRCOND.

Fig. 2. Snapshots of the MPIA (from left to right: WXR, GCAS and AIRCOND)

# 5 Formal Development of MPIA in FLUID

We present a formal description of MPIA in FLUID. Due to space limitation, we show only the FLUID model of weather radar information (WXR). The other HMI widgets, such as GCAS and AIRCOND, of MPIA are developed in a similar way.

#### 5.1 Declaration

For modelling the HMI of WXR in FLUID, we define a set of enumerated datatypes and a constant to represent system properties in the DECLARATION clause. Three enumeration sets are: WXR\_MODE\_SELC\_SET for modes, WXR\_TILT\_STAB\_MSG for messages, and WXR\_ACTIONS for actions. A constant WXR\_ANGL\_RANG is defined a range of tilt angle.

#### 5.2 State

In WXR model, we define several state variables in STATE clause for representing *Input, Output, SysInput* and *SysOutput* states. There are four variables to represent input or acquisition states and six variables to represent output or presentation states. All these variables associated with tag information (*Input, Enabled, Visible, Checked, etc.*) are defined with the given datatypes. Note that the associated tags are defined in a HMI metadata library, including types.

#### 5.3 Events

To model the functional interactive behaviour of WXR. we define a set of events, including an INIT event in the EVENT clause. The INIT event only sets initial value for each state variable while the other events are used model possible HMI behaviour (state changes). In the INIT event, we show initial state of an acquisition variable  $(A \ Mode$ Selection) and a presenvariable (P check Mode), including taq details. Other state variables and their associated taqs are initialized in a similar way.

```

DECLARATION

// WXR Mode enumeration set

TYPE WXR_MODE_SELC_SET = enumeration (M_OFF, STDBY, TST, WXON, WXA)

// WXR Tilt and Stabilisation message enumeration set

TYPE WXR_TILT_STAB_MSG = enumeration (ON, OFF, AUTO, MANUAL)

// WXR Till angle range

CONSTANT WXR_ANGL_RANG = [ -15 . . 15 ]

// WXR actions

TYPE WXR_ACTIONS = enumeration (TILT_CTRL, STAB_CTRL)

```

```

STATE Section

//Acquisition states

A_ModeSelection@(Input, Checked) : WXR_MODE_SELC_SET // Mode state

A_TiltSelection@(Input, Enabled) : WXR_TILT_SELC_SET // Tilt state

A_Stabilization@(Input, Enabled) : WXR_STAB_SELC_SET // Stabilization state

A_TiltAngle@(Input, Enabled) : WXR_ANGL_RANG // Tile angle state

...

//Presentation states

// Radio buttons presentation states

P_checkMode@(Output, Checked) : WXR_MODE_SELC_SET \rightarrow BOOL

// CTRL ith button presentation state

P_ctrlModeTilt_Button@(Output, Enabled) : WXR_ACTIONS

// CTRL stabilization button presentation state