Lecture Notes in Electrical Engineering 627

# Sergio Saponara Alessandro De Gloria *Editors*

# Applications in Electronics Pervading Industry, Environment and Society APPLEPIES 2019

# Lecture Notes in Electrical Engineering

### Volume 627

#### Series Editors

Leopoldo Angrisani, Department of Electrical and Information Technologies Engineering, University of Napoli Federico II, Naples, Italy

Marco Arteaga, Departament de Control y Robótica, Universidad Nacional Autónoma de México, Coyoacán, Mexico

Bijaya Ketan Panigrahi, Electrical Engineering, Indian Institute of Technology Delhi, New Delhi, Delhi, India Samarjit Chakraborty, Fakultät für Elektrotechnik und Informationstechnik, TU München, Munich, Germany Jiming Chen, Zhejiang University, Hangzhou, Zhejiang, China

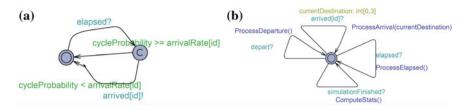

Shanben Chen, Materials Science and Engineering, Shanghai Jiao Tong University, Shanghai, China

Tan Kay Chen, Department of Electrical and Computer Engineering, National University of Singapore, Singapore, Singapore

Rüdiger Dillmann, Humanoids and Intelligent Systems Laboratory, Karlsruhe Institute for Technology, Karlsruhe, Germany

Haibin Duan, Beijing University of Aeronautics and Astronautics, Beijing, China

Gianluigi Ferrari, Università di Parma, Parma, Italy

Manuel Ferre, Centre for Automation and Robotics CAR (UPM-CSIC), Universidad Politécnica de Madrid, Madrid, Spain

Sandra Hirche, Department of Electrical Engineering and Information Science, Technische Universität München, Munich, Germany

Faryar Jabbari, Department of Mechanical and Aerospace Engineering, University of California, Irvine, CA, USA

Limin Jia, State Key Laboratory of Rail Traffic Control and Safety, Beijing Jiaotong University, Beijing, China Janusz Kacprzyk, Systems Research Institute, Polish Academy of Sciences, Warsaw, Poland

Alaa Khamis, German University in Egypt El Tagamoa El Khames, New Cairo City, Egypt Torsten Kroeger, Stanford University, Stanford, CA, USA

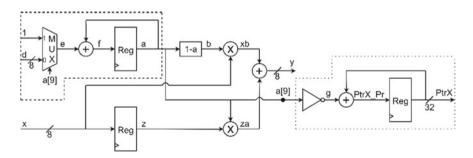

Qilian Liang, Department of Electrical Engineering, University of Texas at Arlington, Arlington, TX, USA Ferran Martín, Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, Bellaterra, Barcelona, Spain

Tan Cher Ming, College of Engineering, Nanyang Technological University, Singapore, Singapore Wolfgang Minker, Institute of Information Technology, University of Ulm, Ulm, Germany

Pradeep Misra, Department of Electrical Engineering, Wright State University, Dayton, OH, USA

Sebastian Möller, Quality and Usability Laboratory, TU Berlin, Berlin, Germany

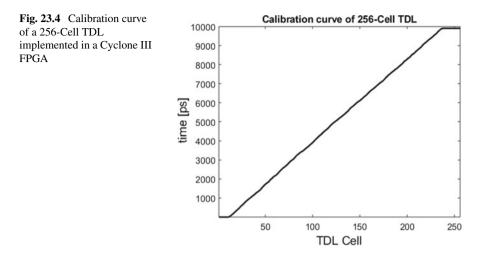

Subhas Mukhopadhyay, School of Engineering & Advanced Technology, Massey University, Palmerston North, Manawatu-Wanganui, New Zealand

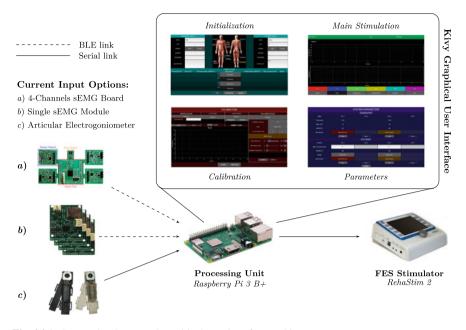

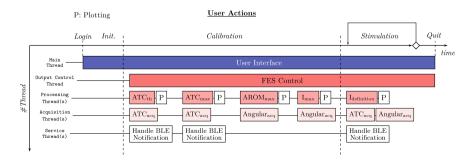

Familiston Norui, Manawatu-wanganui, New Zearand

Cun-Zheng Ning, Electrical Engineering, Arizona State University, Tempe, AZ, USA

Toyoaki Nishida, Graduate School of Informatics, Kyoto University, Kyoto, Japan

Federica Pascucci, Dipartimento di Ingegneria, Università degli Studi "Roma Tre", Rome, Italy

Yong Qin, State Key Laboratory of Rail Traffic Control and Safety, Beijing Jiaotong University, Beijing, China

Gan Woon Seng, School of Electrical & Electronic Engineering, Nanyang Technological University,

Singapore, Singapore

Joachim Speidel, Institute of Telecommunications, Universität Stuttgart, Stuttgart, Germany

Germano Veiga, Campus da FEUP, INESC Porto, Porto, Portugal

Haitao Wu, Academy of Opto-electronics, Chinese Academy of Sciences, Beijing, China Junjie James Zhang, Charlotte, NC, USA

The book series *Lecture Notes in Electrical Engineering* (LNEE) publishes the latest developments in Electrical Engineering—quickly, informally and in high quality. While original research reported in proceedings and monographs has traditionally formed the core of LNEE, we also encourage authors to submit books devoted to supporting student education and professional training in the various fields and applications areas of electrical engineering. The series cover classical and emerging topics concerning:

- Communication Engineering, Information Theory and Networks

- Electronics Engineering and Microelectronics

- Signal, Image and Speech Processing

- Wireless and Mobile Communication

- Circuits and Systems

- Energy Systems, Power Electronics and Electrical Machines

- Electro-optical Engineering

- Instrumentation Engineering

- Avionics Engineering

- Control Systems

- Internet-of-Things and Cybersecurity

- Biomedical Devices, MEMS and NEMS

For general information about this book series, comments or suggestions, please contact leontina.dicecco@springer.com.

To submit a proposal or request further information, please contact the Publishing Editor in your country:

#### China

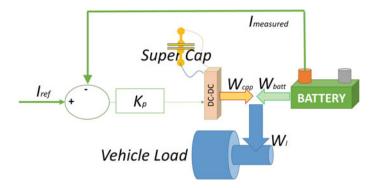

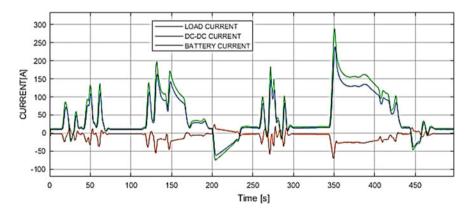

Jasmine Dou, Associate Editor (jasmine.dou@springer.com)

#### India, Japan, Rest of Asia

Swati Meherishi, Executive Editor (Swati.Meherishi@springer.com)

#### Southeast Asia, Australia, New Zealand

Ramesh Nath Premnath, Editor (ramesh.premnath@springernature.com)

#### USA, Canada:

Michael Luby, Senior Editor (michael.luby@springer.com)

#### All other Countries:

Leontina Di Cecco, Senior Editor (leontina.dicecco@springer.com)

**\*\*** Indexing: The books of this series are submitted to ISI Proceedings, EI-Compendex, SCOPUS, MetaPress, Web of Science and Springerlink **\*\***

More information about this series at http://www.springer.com/series/7818

Sergio Saponara · Alessandro De Gloria Editors

# Applications in Electronics Pervading Industry, Environment and Society

APPLEPIES 2019

*Editors* Sergio Saponara DII University of Pisa Pisa, Italy

Alessandro De Gloria DITEN University of Genoa Genoa, Italy

ISSN 1876-1100 ISSN 1876-1119 (electronic) Lecture Notes in Electrical Engineering ISBN 978-3-030-37276-7 ISBN 978-3-030-37277-4 (eBook) https://doi.org/10.1007/978-3-030-37277-4

#### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### Preface

The 2019 edition of the conference on *Applications in Electronics Pervading Industry, Environment and Society* was held in Pisa, Italy, on September 11–13, 2019, at the School of Engineering (Aula Magna U. Dini and Aula Magna A. Pacinotti).

During the three days, 110 registered participants, from 35 different entities (25 universities and 10 industries), discussed electronic applications in several domains, demonstrating how electronics has become pervasive and ever more embedded in everyday objects and processes.

The conference had the technical and/or financial support of University of Pisa, University of Genoa, SIE (Italian Association for Electronics), Giakova, and the H2020 European Processor Initiative.

After a strict blind-review selection process, 21 interactive posters and 43 lectures have been accepted (with co-authors from 14 different nations) in 11 sessions focused on circuits and electronic systems and their relevant applications in the following fields: wireless and IoT, health care, vehicles and robots (electrified and autonomous), power electronics and energy storage, cybersecurity, AI and data engineering.

More in details the interactive poster (IP) sessions involved contributions on IP1 Vehicular, Robotic and Energy Electronic Systems, IP2 IoT and Integrated Circuits, IP3 Digital Circuits and Systems, while the oral sessions involved contributions on O1 Rad-Hard Electronics, O2 Internet of Things, O3 Processors and Memories, O4 VLSI and Signal Processing, O5 Digital Circuits and AI Data Processing, O6 Sensors and Sensing Electronic Systems, O7 Power and High Voltage Electronics, O8 Signal and Data Processing.

There were also two special events:

A round table on EuroHPC and the European Processor Initiative with contributions from E4, CINECA, STMicroelectronics, University of Bologna, University of Pisa  A demo session of high-performance instrumentation and prototypes for battery management system, aerospace onboard data communication, high-speed drivers for optical modulators.

The proposed papers, collected in this book, and the talks and roundtables of the special events, prove that the computing, storage and networking capabilities of today electronic systems are such that their applications can fulfill the needs of humankind in terms of mobility, health care, connectivity, energy management, smart production, ambient intelligence, smart living, safety and security, education, entertainment, tourism, and cultural heritage.

To exploit such capabilities, multidisciplinary knowledge and expertise are needed to support a virtuous iterative cycle from user needs to the design, prototyping and testing of new products and services. The latter are more and more characterized by a digital core.

The design and testing cycles go through the whole system engineering process, which includes analysis of users' needs, specification definition, verification plan definition, software and hardware co-design, laboratory and user testing and verification, maintenance management, and lifecycle management of electronics applications. The design of electronics-enabled systems should provide key features such as innovation, high performance, real-time operations, implementations with low-cost and reduced budgets in terms of size, weight and power consumption. To succeed in this, one of the most important factors is the adoption of a suited design flow and relevant electronic design automation (EDA) tools. Platform-based design and meet in the middle between top-down and bottom-up design flows are needed to fulfill the time and cost-related challenges of nowadays' market scenarios.

All these challenging aspects call for the importance of the role of academia as a place where new generations of designers can learn and practice with cutting-the-edge technological tools and are stimulated to devise solutions for challenges coming from a variety of application domains.

The APPLEPIES 2019 conference aims at becoming a reference point in the field of electronics systems design and applications, trying to fill at scientific and technological R&D level a gap that the most farsighted industries have already indicated and are striving to cover.

Pisa, Italy

Sergio Saponara General Chair

Genoa, Italy

Alessandro De Gloria Honorary Chair

# Contents

#### Part I Rad-Hard Electronics

| 1    | Advanced Radiation Sensors VLSI Design in CMOS Technology         for High Energy Physics Applications       3         Tommaso Croci, Arianna Morozzi, Pisana Placidi and Daniele Passeri                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | Design, Operation and BER Test of Multi-Gb/s Radiation-HardDrivers in 65 nm Technology for Silicon Photonics OpticalModulatorsModulatorsG. Ciarpi, S. Cammarata, S. Faralli, P. Velha, G. Magazzù,F. Palla and Sergio Saponara |

| 3    | A Rad-Hard Bandgap Voltage Reference for High Energy19Physics Experiments19G. Traversi, L. Gaioni, M. Manghisoni, M. Pezzoli, L. Ratti,19V. Re, E. Riceputi and M. Sonzogni19                                                  |

| 4    | Analysis and Comparison of Ring and LC-Tank Oscillatorsfor 65 nm Integration of Rad-Hard VCO for SpaceFibreApplicationsD. Monda, G. Ciarpi, G. Mangraviti, L. Berti and Sergio Saponara                                        |

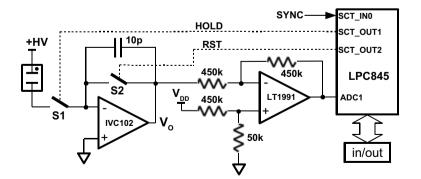

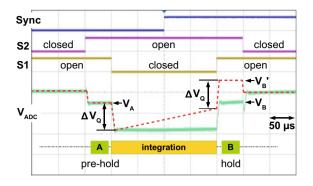

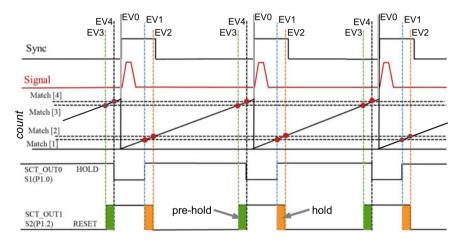

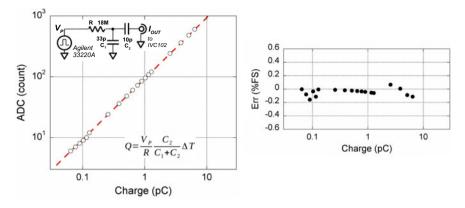

| 5    | A Compact Gated Integrator for Conditioning Pulsed Analog<br>Signals                                                                                                                                                           |

| Part | II Internet of Things                                                                                                                                                                                                          |

| 6 | Multivariate Microaggregation with Fixed Group Size Based |    |

|---|-----------------------------------------------------------|----|

|   | on the Travelling Salesman Problem                        | 43 |

|   | Armando Maya López and Agusti Solanas                     |    |

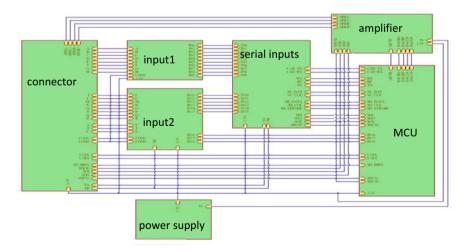

| 7    | Modular Design of Electronic Appliances for ReliabilityEnhancement in a Circular Economy PerspectiveSimone Orcioni, Cristiano Scavongelli and Massimo Conti                                  | 51  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

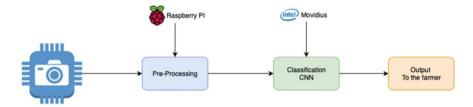

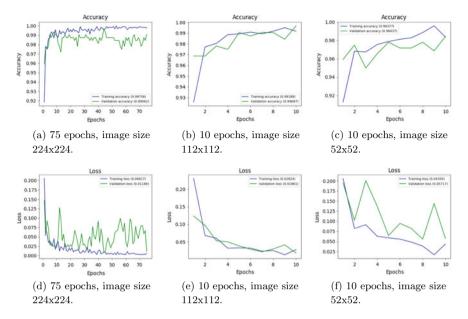

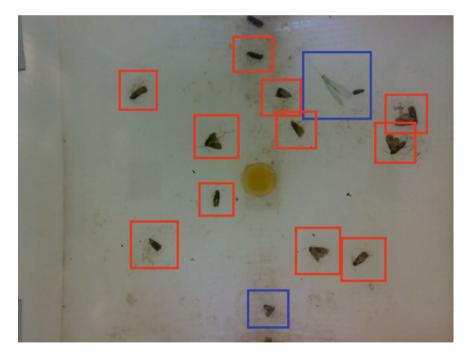

| 8    | Pest Detection for Precision Agriculture Based on IoT Machine         Learning         Andrea Albanese, Donato d'Acunto and Davide Brunelli                                                  | 65  |

| 9    | Statistical Flow Classification for the IoT<br>Gennaro Cirillo, Roberto Passerone, Antonio Posenato<br>and Luca Rizzon                                                                       | 73  |

| 10   | Using LPWAN Connectivity for Elderly Activity Monitoring<br>in Smartcity Scenarios<br>D. Fernandes Carvalho, P. Ferrari, E. Sisinni, P. Bellitti,<br>N. F. Lopomo and M. Serpelloni          | 81  |

| Part | t III Processors and Memories                                                                                                                                                                |     |

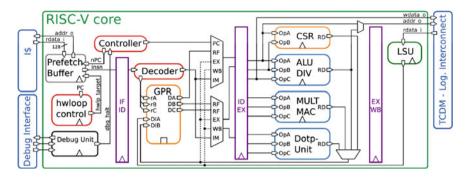

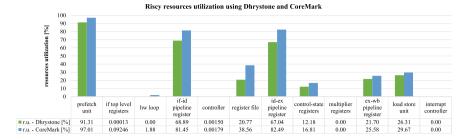

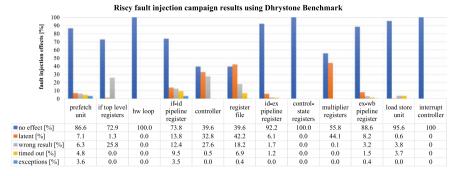

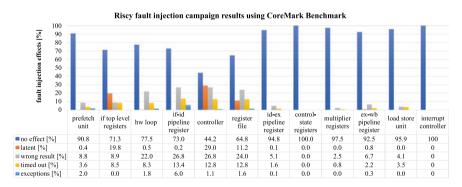

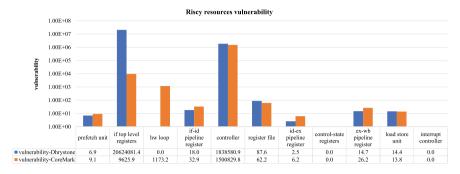

| 11   | Characterization of a RISC-V Microcontroller Through Fault<br>Injection                                                                                                                      | 91  |

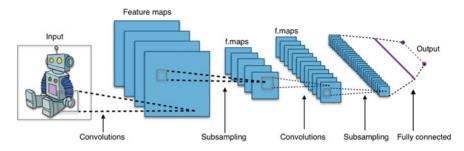

| 12   | Analyzing Machine Learning on Mainstream Microcontrollers<br>Vincenzo Falbo, Tommaso Apicella, Daniele Aurioso, Luisa Danese,<br>Francesco Bellotti, Riccardo Berta and Alessandro De Gloria | 103 |

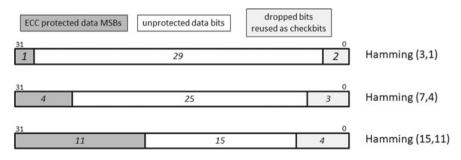

| 13   | Quality Aware Selective ECC for Approximate DRAM<br>Giulia Stazi, Antonio Mastrandrea, Mauro Olivieri<br>and Francesco Menichelli                                                            | 109 |

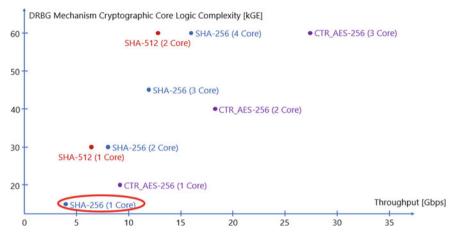

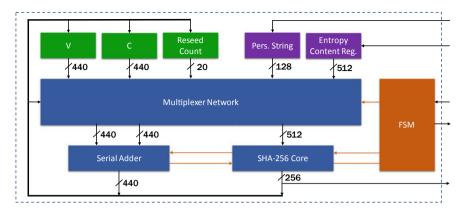

| 14   | Digital Random Number Generator Hardware AcceleratorIP-Core for Security ApplicationsLuca Baldanzi, Luca Crocetti, Francesco Falaschi, Jacopo Belli,Luca Fanucci and Sergio Saponara         | 117 |

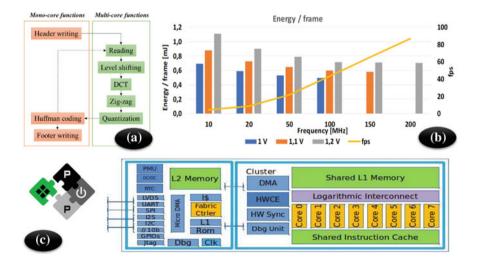

| 15   | An Energy Optimized JPEG Encoder for Parallel<br>Ultra-Low-Power Processing-Platforms<br>Tommaso Polonelli, Daniele Battistini, Manuele Rusci,<br>Davide Brunelli and Luca Benini            | 125 |

| Part | t IV VLSI & Signal Processing                                                                                                                                                                |     |

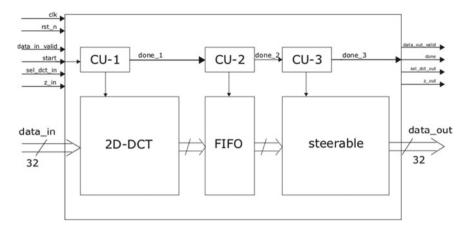

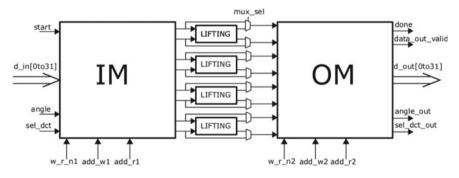

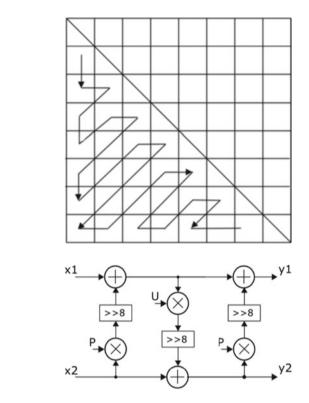

| 16   | VLSI Architectures for the Steerable-Discrete-Cosine-Transform                                                                                                                               |     |

| Contents |

|----------|

|----------|

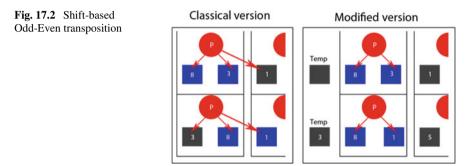

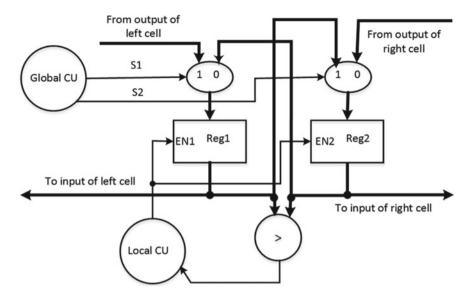

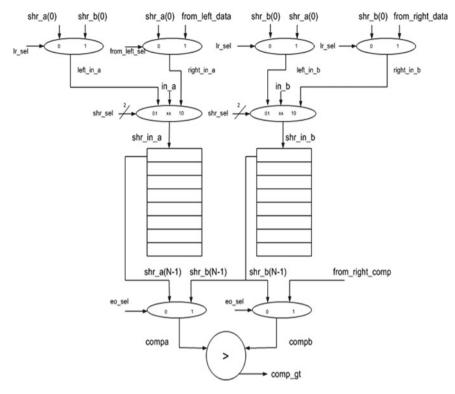

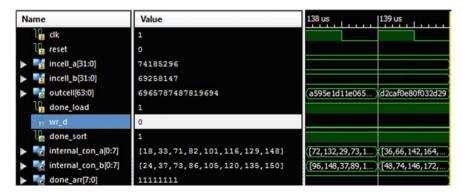

| 17  | Hardware Architecture for a Bit-Serial Odd-Even Transposition<br>Sort Network with On-The-Fly Compare and Swap<br>Ghattas Akkad, Rafic Ayoubi, Ali Mansour and Bachar ElHassan                           | 145 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 18  | Variable-Rounded LMS Filter for Low-Power Applications Gennaro Di Meo, Davide De Caro, Ettore Napoli, Nicola Petra and Antonio G. M. Strollo                                                             | 155 |

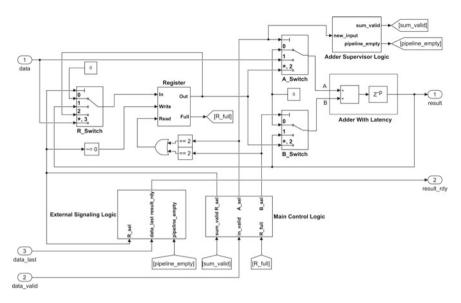

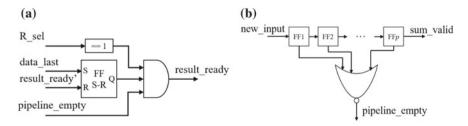

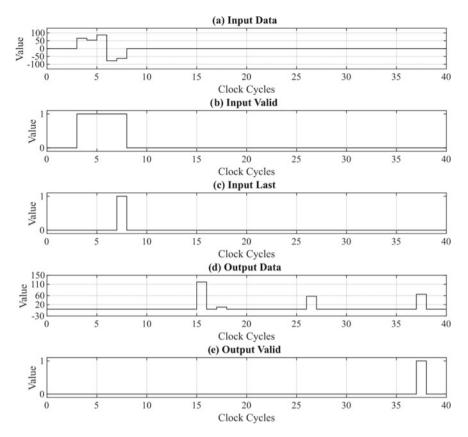

| 19  | A Simulink Model-Based Design of a Floating-Point Pipelined<br>Accumulator with HDL Coder Compatibility for FPGA<br>Implementation                                                                       | 163 |

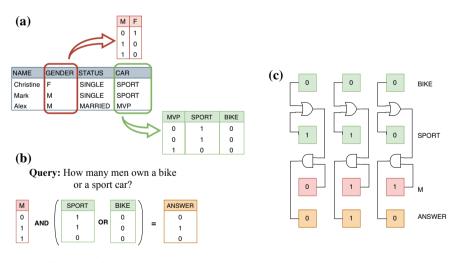

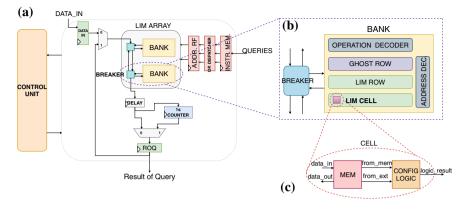

| 20  | Bitmap Index: A Processing-in-Memory ReconfigurableImplementationM. Andrighetti, G. Turvani, G. Santoro, M. Vacca, M. Ruo Roch,M. Graziano and M. Zamboni                                                | 173 |

| Par | t V Digital Circuits and AI Data Processing                                                                                                                                                              |     |

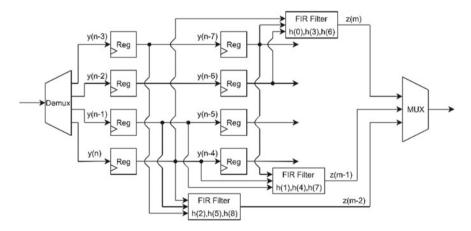

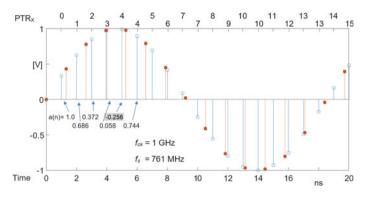

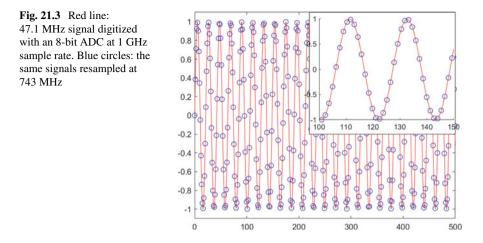

| 21  | Digital Circuit for the Arbitrary Selection of Sample Ratein Digital Storage OscilloscopesM. D'Arco, E. Napoli and E. Zacharelos                                                                         | 183 |

| 22  | An Intelligent Informative Totem Application Based on Deep         CNN in Edge Regime         Paolo Giammatteo, Giacomo Valente and Alessandro D'Ortenzio                                                | 191 |

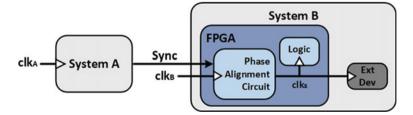

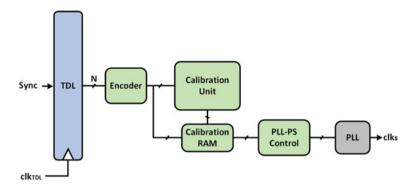

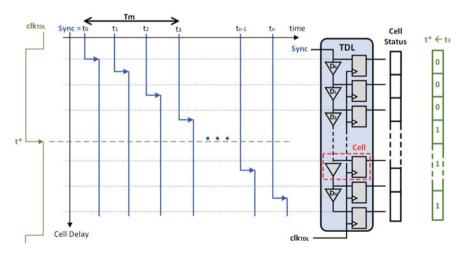

| 23  | <b>FPGA-Based Clock Phase Alignment Circuit for Frame Jitter Reduction</b> Dario Russo and Stefano Ricci                                                                                                 | 199 |

| 24  | <b>Real-Time Embedded System for Event-Driven sEMG</b><br><b>Acquisition and Functional Electrical Stimulation Control</b> Fabio Rossi, Ricardo Maximiliano Rosales, Paolo Motto Ros and Danilo Demarchi | 207 |

| 25  | A Fast Approximation of the Hyperbolic Tangent When Using<br>Posit Numbers and Its Application to Deep Neural Networks<br>Marco Cococcioni, Federico Rossi, Emanuele Ruffaldi<br>and Sergio Saponara     | 213 |

| Par | t VI Sensors and Sensing Electronic Systems                                                                                                                                                              |     |

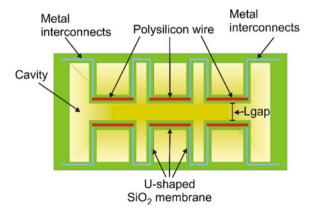

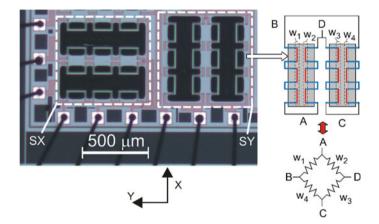

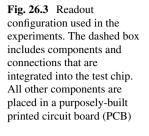

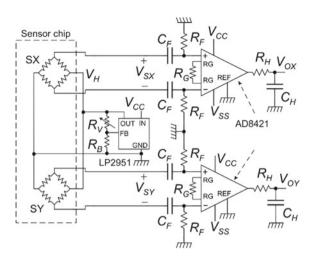

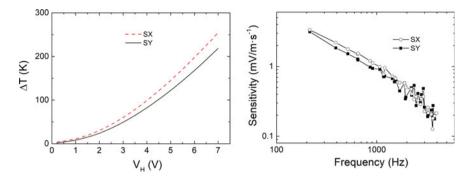

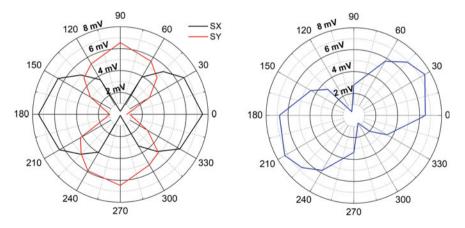

| 26  | 2-D Acoustic Particle Velocity Sensors Based on a Commercial<br>Post-CMOS MEMS Technology                                                                                                                | 225 |

Contents

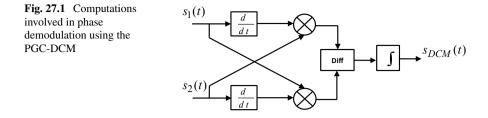

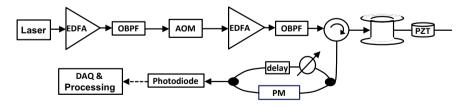

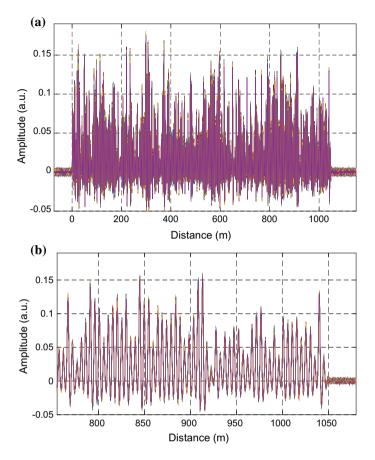

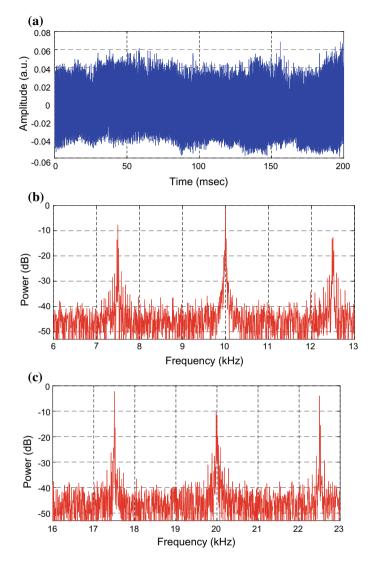

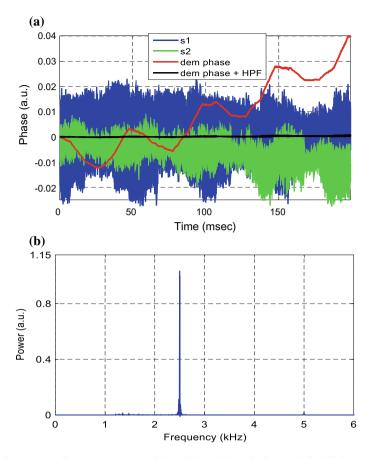

|    | A High-SNR Distributed Acoustic Sensor Based on φ-OTDR<br>Using a Scalable Phase Demodulation Scheme Without Phase<br>Unwrapping                                                                       | 233 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

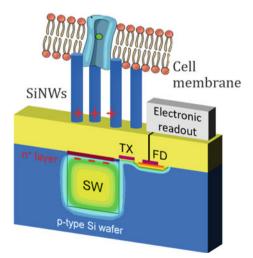

|    | Silicon Nanowires as Contact Between the Cell Membrane and<br>CMOS Circuits<br>P. Piedimonte, D. A. M. Feyen, M. Mercola, E. Messina, M. Renzi<br>and F. Palma                                         | 243 |

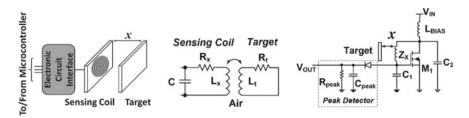

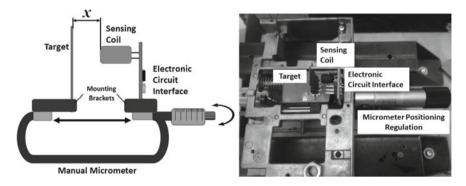

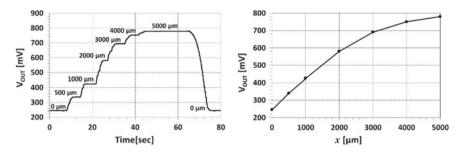

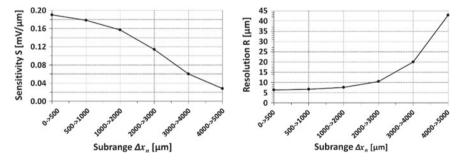

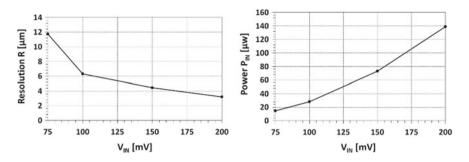

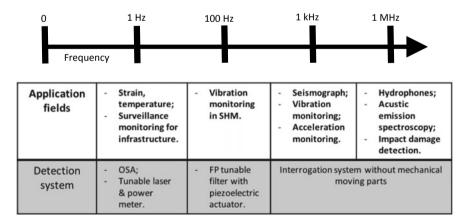

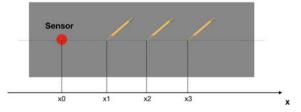

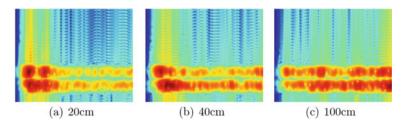

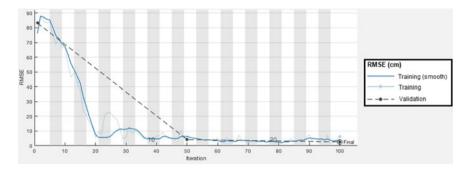

|    | Ultra-Low Power Displacement Sensor                                                                                                                                                                    | 251 |

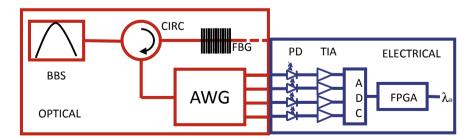

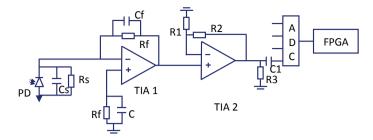

|    | Simulation of an Optical-to-Digital Converter for High<br>Frequency FBG Interrogator<br>Vincenzo Romano Marrazzo, Francesco Fienga, Michele Riccio,<br>Luca Maresca, Andrea Irace and Giovanni Breglio | 259 |

|    | Wireless Sensors for Intraoral Force Monitoring<br>M. Merenda, D. Laurendi, D. Iero, D. M. D'Addona<br>and F. G. Della Corte                                                                           | 267 |

| rt | VII Power and High Voltage Electronics                                                                                                                                                                 |     |

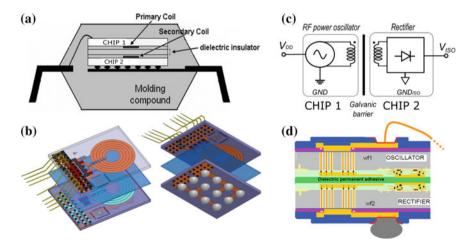

|    | Reinforced Galvanic Isolation: Integrated Approaches<br>to Go Beyond 20-kV Surge Voltage (invited)<br>Egidio Ragonese, Nunzio Spina, Alessandro Parisi<br>and Giuseppe Palmisano                       | 277 |

|    | Experimental Characterization of a Commercial Sodium-Nickel                                                                                                                                            | 285 |

| Part | VII Power and High Voltage Electronics                                                                                                                                                                                   |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 32   | Reinforced Galvanic Isolation: Integrated Approaches<br>to Go Beyond 20-kV Surge Voltage (invited)<br>Egidio Ragonese, Nunzio Spina, Alessandro Parisi<br>and Giuseppe Palmisano                                         | 277 |

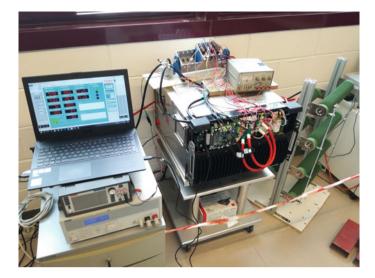

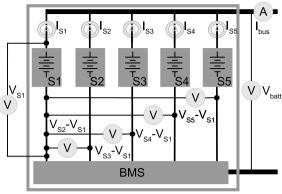

| 33   | <b>Experimental Characterization of a Commercial Sodium-Nickel</b><br><b>Chloride Battery for Telecom Applications</b><br>Federico Baronti, Roberto Di Rienzo, Roberto Roncella,<br>Gianluca Simonte and Roberto Saletti | 285 |

| 34   | <b>Design and Development of a Prototype of Flash Charge Systems</b><br><b>for Public Transportation</b>                                                                                                                 | 293 |

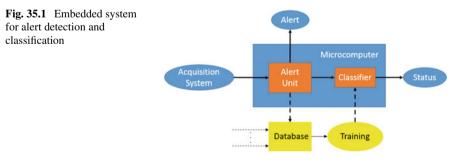

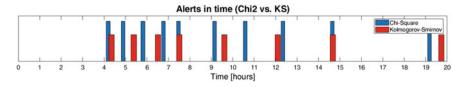

| 35   | Unsupervised Monitoring System for Predictive Maintenance<br>of High Voltage Apparatus<br>Christian Gianoglio, Andrea Bruzzone, Edoardo Ragusa<br>and Paolo Gastaldo                                                     | 301 |

| 36   | Control System Design for Cogging Torque Reduction Based<br>on Sensor-Less Architecture                                                                                                                                  | 309 |

Dini Pierpaolo and Sergio Saponara

х

27

28

29

30

31

#### Contents

#### Part VIII Signal and Data Processing

| 37   | Acoustic Emissions Detection and Ranging of Cracks in Metal<br>Tanks Using Deep Learning<br>Gian Carlo Cardarilli, Luca Di Nunzio, Rocco Fazzolari,<br>Daniele Giardino, Marco Matta, Marco Re and Sergio Spanò                                                                                                                                         | 325 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

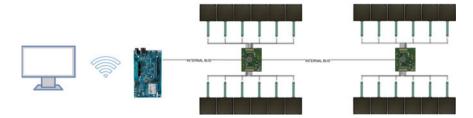

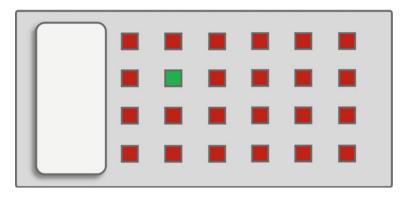

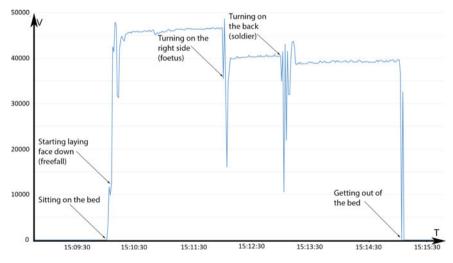

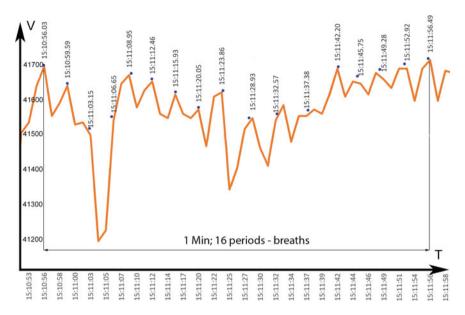

| 38   | Recognizing Breathing Rate and Movement While Sleeping<br>in Home Environment.<br>Maksym Gaiduk, Ralf Seepold, Natividad Martínez Madrid,<br>Simone Orcioni and Massimo Conti                                                                                                                                                                           | 333 |

| 39   | A Fast Face Recognition CNN Obtained by Distillation<br>Luca De Bortoli, Francesco Guzzi, Stefano Marsi, Sergio Carrato<br>and Giovanni Ramponi                                                                                                                                                                                                         | 341 |

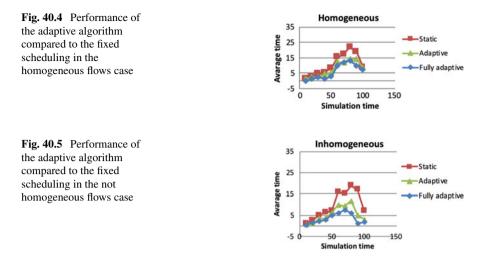

| 40   | <b>Fine-Grain Traffic Control for Smart Intersections</b><br>Jessica Bellitto, Valentina Schenone, Francesco Bellotti,<br>Riccardo Berta and Alessandro De Gloria                                                                                                                                                                                       | 349 |

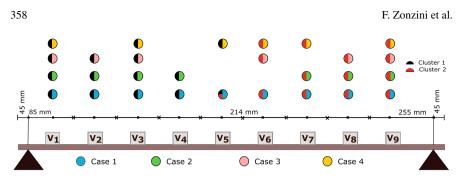

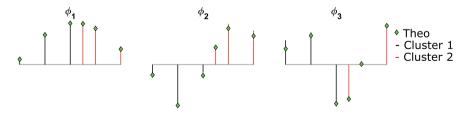

| 41   | A Graph Signal Processing Technique for Vibration Analysis<br>with Clustered Sensor Networks                                                                                                                                                                                                                                                            | 355 |

| 42   | Guided Waves Direction of Arrival Estimation Based<br>on Calibrated Multiresolution Wavelet Analysis                                                                                                                                                                                                                                                    | 363 |

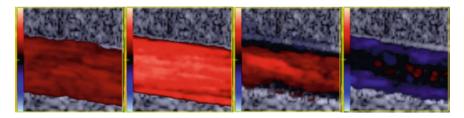

| 43   | High-Frame-Rate Ultrasound Color Flow Imaging Based<br>on an Open Scanner<br>Francesco Guidi, Enrico Boni, Alessandro Dallai, Valentino Meacci<br>and Piero Tortoli                                                                                                                                                                                     | 371 |

| Part | t IX Vehicular, Robotic and Energy Electronic Systems                                                                                                                                                                                                                                                                                                   |     |

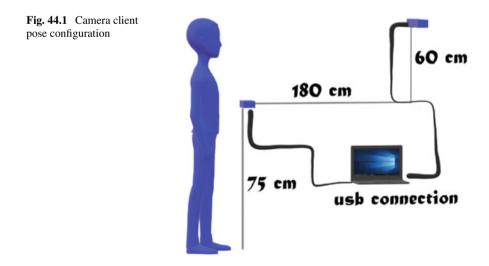

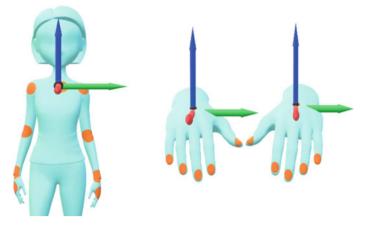

| 44   | Empowering Deafblind Communication Capabilities<br>by Means of AI-Based Body Parts Tracking and Remotely<br>Controlled Robotic Arm for Sign Language Speakers<br>Silvia Panicacci, Gianluca Giuffrida, Luca Baldanzi, Luca Massari,<br>Giuseppe Terruso, Martina Zalteri, Mariangela Filosa,<br>Giovanni Tonietti, Calogero Maria Oddo and Luca Fanucci | 381 |

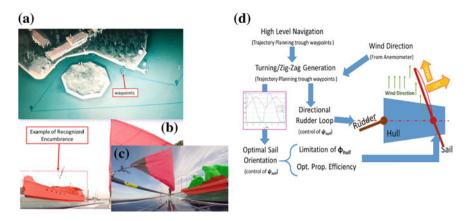

| 45   | Project VELA, Upgrades and Simulation Models of the UNIFI<br>Autonomous Sail Drone<br>Enrico Boni, Marco Montagni and Luca Pugi                                                                                                                                                                                                                         | 389 |

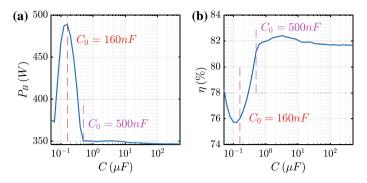

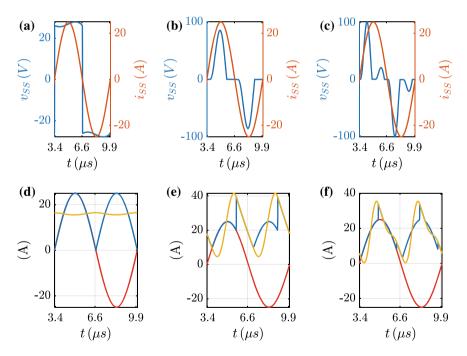

| 46        | <b>DC-Link Capacitor Sizing Method for a Wireless Power Transfer</b><br><b>Circuit to Be Used in Drone Opportunity Charging</b><br>Andrea Carloni, Federico Baronti, Roberto Di Rienzo,<br>Roberto Roncella and Roberto Saletti                                 | 397 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

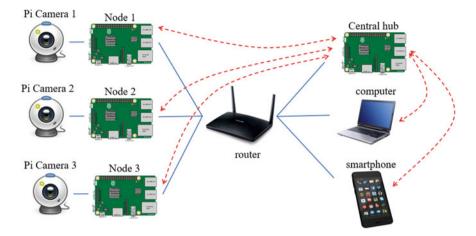

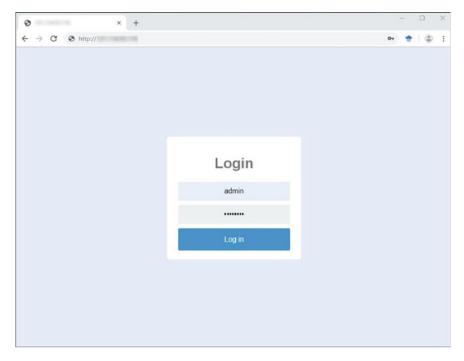

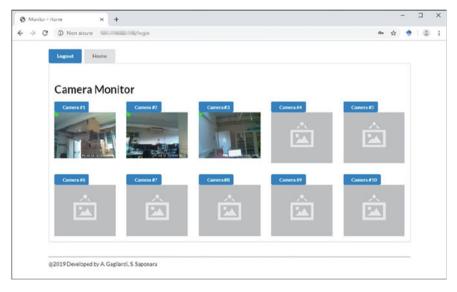

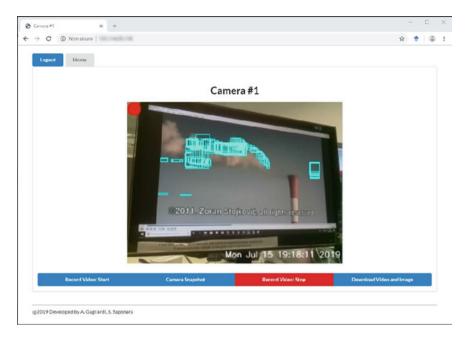

| 47        | Distributed Video Antifire Surveillance System Based on IoT<br>Embedded Computing Nodes                                                                                                                                                                         | 405 |

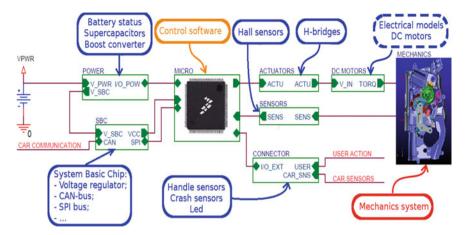

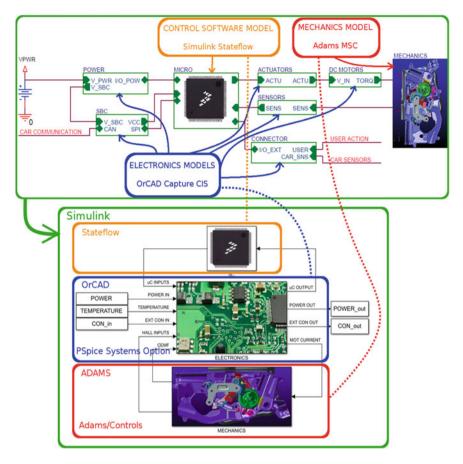

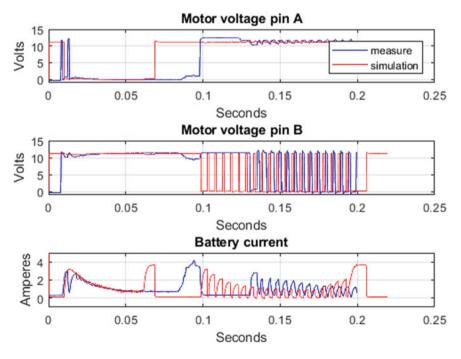

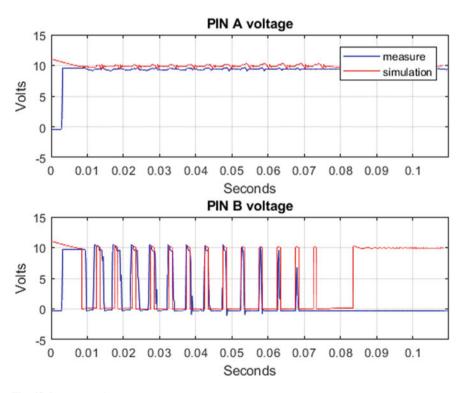

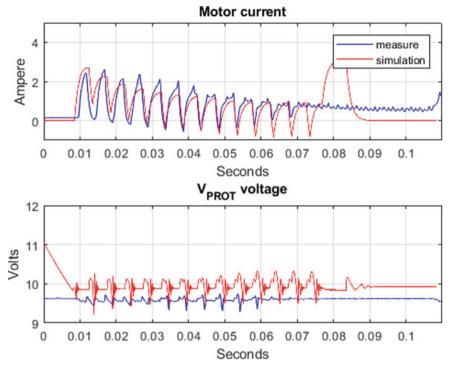

| 48        | Integrated Simulation Environment for Co-design/Verificationof Mechanic, Electronic and Control of Automotive E-Drives:The Smart-Latch Case StudyEmanuele Abbatessa, Davide Dente and Sergio Saponara                                                           | 413 |

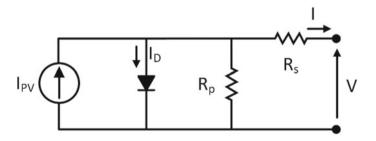

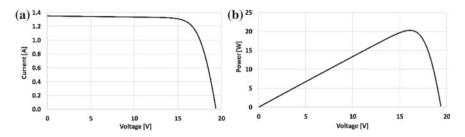

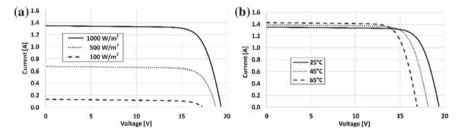

| <b>49</b> | Spice Model of Photovoltaic Panel for Electronic System<br>Design<br>Mirco Muttillo, Tullio de Rubeis, Dario Ambrosini<br>and Giuseppe Ferri                                                                                                                    | 425 |

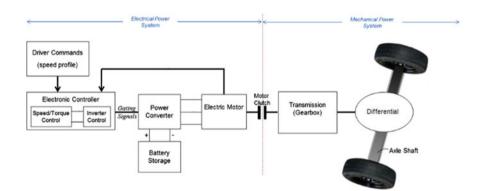

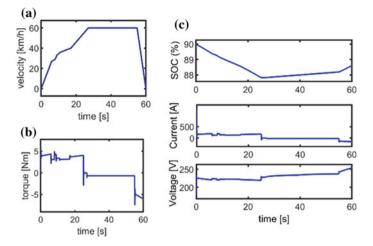

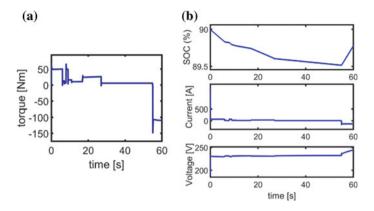

| 50        | Exhaustive Modeling of Electric Vehicle Dynamics, Powertrain<br>and Energy Storage/Conversion for Electrical Component Sizing<br>and DiagnosticGaia Fiore, Lucian Mihet-Popa and Sergio Saponara                                                                | 433 |

| Par       | t X IoT and Integrated Circuits                                                                                                                                                                                                                                 |     |

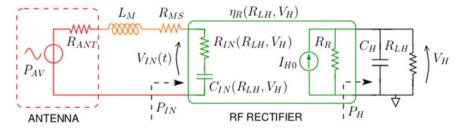

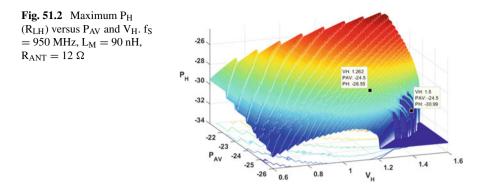

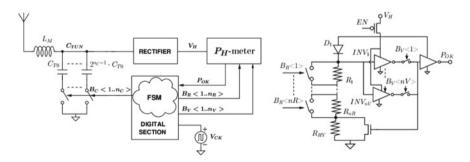

| 51        | Analysis of 3-D MPPT for RF Harvesting<br>Michele Caselli and Andrea Boni                                                                                                                                                                                       | 443 |

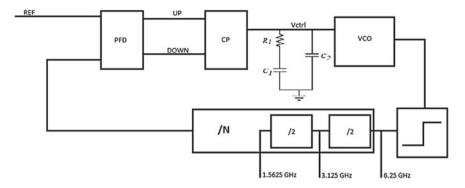

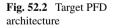

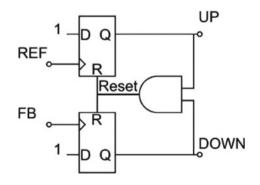

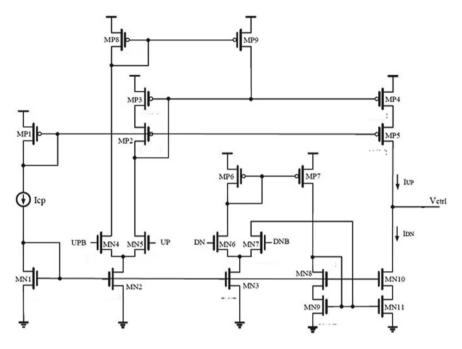

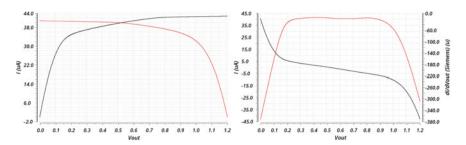

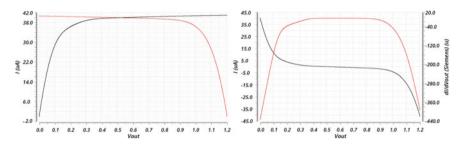

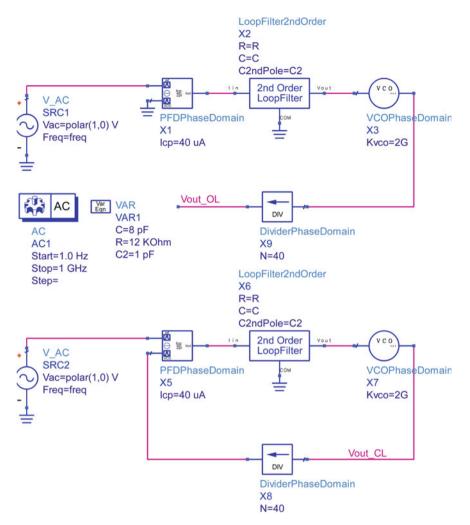

| 52        | Analysis and Simulation of a PLL Architecture Towards a Fully<br>Integrated 65 nm Solution for the New Spacefibre Standard                                                                                                                                      | 451 |

|           | Marco Mestice, Bruno Neri and Sergio Saponara                                                                                                                                                                                                                   | 431 |

| 53        | Marco Mestice, Bruno Neri and Sergio Saponara<br><b>Stability and Startup of Non Linear Loop Circuits</b><br>Francesca Cucchi, Stefano Di Pascoli and Giuseppe Iannaccone                                                                                       | 463 |

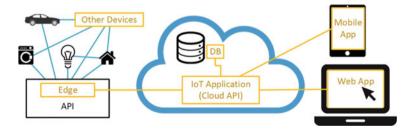

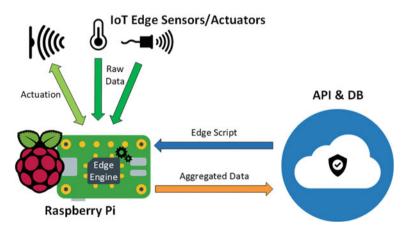

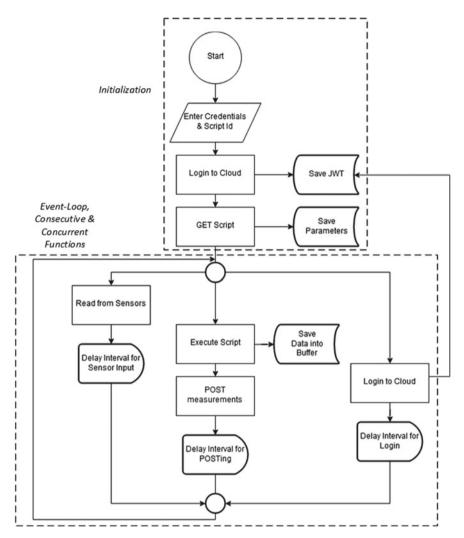

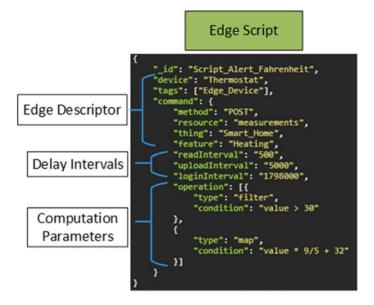

| 53<br>54  | Stability and Startup of Non Linear Loop Circuits                                                                                                                                                                                                               |     |

|           | Stability and Startup of Non Linear Loop Circuits         Francesca Cucchi, Stefano Di Pascoli and Giuseppe Iannaccone         IoT Ubiquitous Edge Engine Implementation         on the Raspberry PI         Ahmad Kobeissi, Riccardo Berta, Francesco Bellotti | 463 |

Antonino Marino and Luca Fanucci

| Contents |

|----------|

|----------|

| 57  | An FPGA Realization for Real-Time Depth Estimation in Image                                                                                                                                                             | 489 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Stefano Marsi, Sergio Carrato, Luca De Bortoli, Paolo Gallina,<br>Francesco Guzzi and Giovanni Ramponi                                                                                                                  | 409 |

| Par | t XI Digital Circuits and Systems                                                                                                                                                                                       |     |

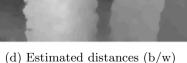

| 58  | Integration of a SpaceFibre IP Core with the LEON3<br>Microprocessor Through an AMBA AHB Bus<br>Gianmarco Dinelli, Gabriele Meoni, Pietro Nannipieri,<br>Luca Dello Sterpaio, Antonino Marino and Luca Fanucci          | 499 |

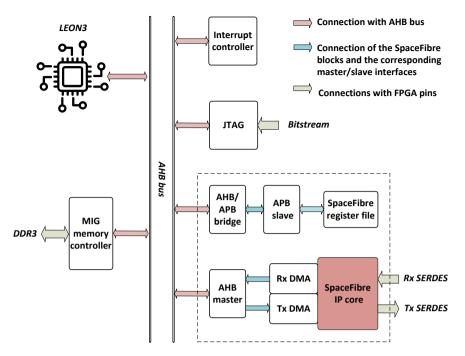

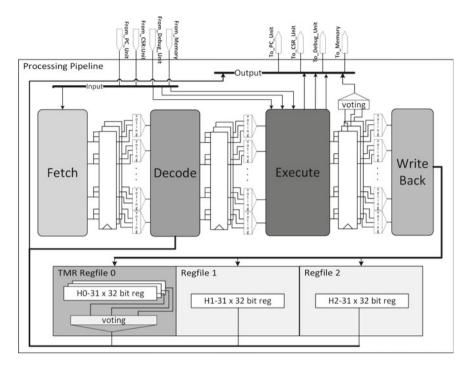

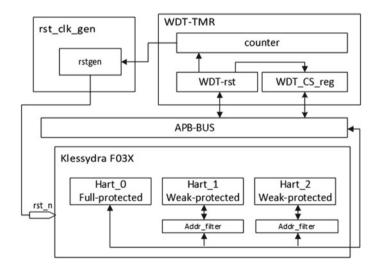

| 59  | A RISC-V Fault-Tolerant Microcontroller Core Architecture<br>Based on a Hardware Thread Full/Partial Protection<br>and a Thread-Controlled Watch-Dog Timer                                                              | 505 |

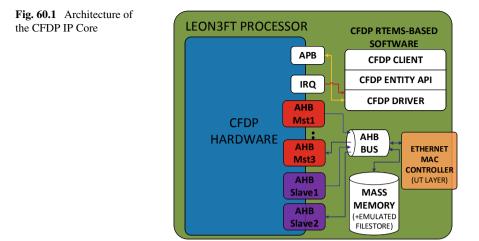

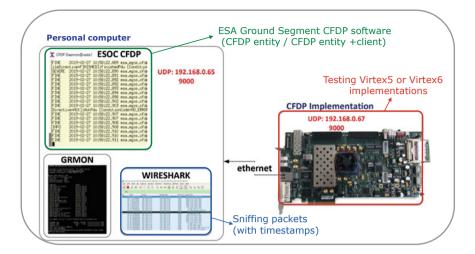

| 60  | Estimating the Downlink Data-Rate of a CCSDS File Delivery<br>Protocol IP Core                                                                                                                                          | 513 |

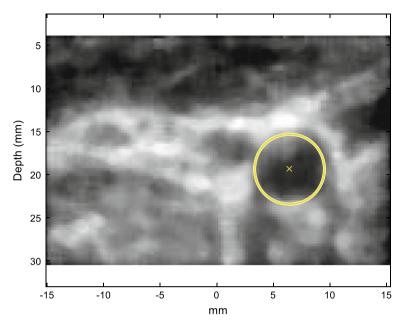

| 61  | Automatic Detection of the Carotid Artery Position for BlindEcho-Doppler Blood Flow InvestigationRiccardo Matera and Stefano Ricci                                                                                      | 521 |

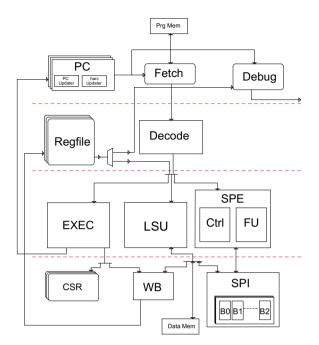

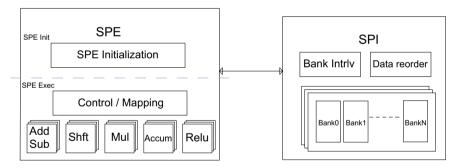

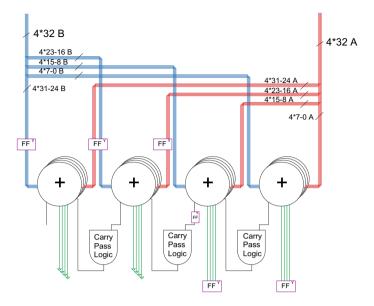

| 62  | Efficient Mathematical Accelerator Design Coupled with<br>an Interleaved Multi-threading RISC-V Microprocessor<br>Abdallah Cheikh, Stefano Sordillo, Antonio Mastrandrea,<br>Francesco Menichelli and Mauro Olivieri    | 529 |

| 63  | AXI4LV: Design and Implementation of a Full-Speed AMBA<br>AXI4-Burst DMA Interface for LabVIEW FPGA<br>Luca Dello Sterpaio, Antonino Marino, Pietro Nannipieri,<br>Gianmarco Dinelli and Luca Fanucci                   | 541 |

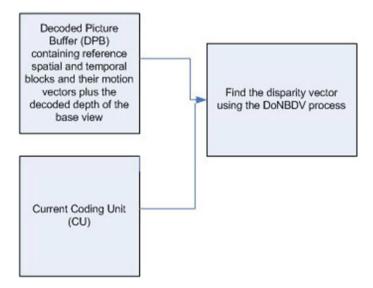

| 64  | <b>3D-HEVC Neighboring Block Based Disparity Vector (NBDV)Derivation Architecture: Complexity and ImplementationAnalysis</b> Waqar Ahmad, Naveed Khan Baloch, Fawad Hussain,<br>Muhammad Asif Khan and Maurizio Martina | 549 |

| Aut | hor Index                                                                                                                                                                                                               | 559 |

# Part I Rad-Hard Electronics

# Chapter 1 Advanced Radiation Sensors VLSI Design in CMOS Technology for High Energy Physics Applications

Tommaso Croci, Arianna Morozzi, Pisana Placidi and Daniele Passeri

**Abstract** In this paper we discuss some issues related to the design, implementation and test of a CMOS Active Pixel Sensor. Two different pixel layout have been proposed based on a standard architecture to investigate the suitability of a 110 nm standard technology for the realization of small pixels, high granularity detectors to be used in High-Energy Physics, medical and space applications, such as particle tracking or beam monitoring.

**Keywords** Active Pixel Sensor  $\cdot$  CMOS  $\cdot$  Radiation sensor  $\cdot$  High energy physics applications

#### 1.1 Introduction

The adoption of standard CMOS technology has been suggested as a viable option for the fabrication of particle detectors, integrating sensitive element and related read-out circuitry on the same substrate. The inherently lower detection efficiency of standard CMOS substrates can be compensated by the simultaneous integration of small capacitance detection nodes and signal conditioning and elaboration of circuitry [1]. This foster the realization of integrated detectors without the need of hybrid solutions, e.g. the very expensive bump-bonding between sensing nodes (pixels) and read-out circuitry or the adoption of dedicated, ad-hoc technology flavours and options (e.g. high-resistivity substrates, with thick epi-layers or multiple wells) [2, 3]. In this paper we discuss some design, implementation and test issues with respect to the development of conventional Active Pixel Sensor (APS) matrices in 110 nm LFoundry technology [4] conceived for CMOS Image Sensor (CIS) fabrication. The aim of this study is to investigate the suitability of such a technology for the realization

© Springer Nature Switzerland AG 2020

S. Saponara and A. De Gloria (eds.), Applications in Electronics Pervading

Industry, Environment and Society, Lecture Notes in Electrical Engineering 627, https://doi.org/10.1007/978-3-030-37277-4\_1

T. Croci (⊠) · A. Morozzi · P. Placidi · D. Passeri INFN-Section of Perugia, Perugia, Italy e-mail: tommaso.croci@pg.infn.it

P. Placidi · D. Passeri Department of Engineering, University of Perugia, Perugia, Italy

of small pixels, high granularity detectors to be used in High-Energy Physics, medical and space applications, such as particle tracking or beam monitoring [5, 6].

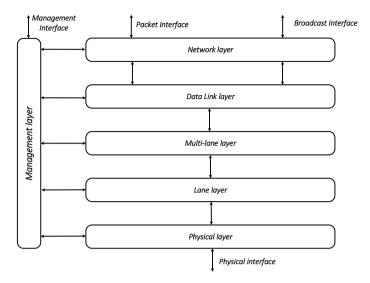

#### 1.2 System Architecture and Active Pixel Sensor

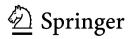

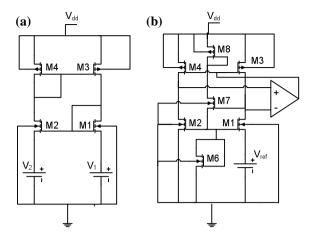

To evaluate the performance of the chosen technology for high energy physics applications, test structures based on single active pixels and on pixel arrays of limited dimensions have been designed. The structures are characterized by the use of the typical three-transistor pixel architecture (Fig. 1.1), with different geometries of the sensitive area. The designed chip houses also the interface circuits required for reading, addressing and interfacing the sensitive component.

The particle detection principle is based on a photodiode, a reverse biased pn junction used to detect the impinging radiation by converting in electrical charge the energy released into the material. In high energy physics the sensor requirements are typically very harsh, such as high efficiency and good spatial localization. A good tolerance to radiation damage is offered by modern submicrometric VLSI processes, guaranteeing the correct functionality of the sensor and a longer operating life.

To collect the maximum amount of charge inside the pixel, the chip substrate or the epitaxial layer, if available, tends to be used as the p-type region of the photodiode, whereas the n-type region is usually made by an n-well or an n+ implantation. In this work we explore the possibility of using a standard CMOS technology, provided that the layout of the sensitive element has been designed according to the technology itself for the specific particle to be detected.

The APS involves the use of a basic electronic signal processing inside the pixel, directly connected to the sensitive element. In this way it is possible to increase the reading speed and to reduce the noise due to the lower impact of the parasitic elements. The price to be paid, however, is the reduction of the fill factor (FF) due to the "blind" area dedicated to electronic circuits. Therefore, during the pixel design,

Fig. 1.1 a APS 3T circuit; b output voltage of the pixel

an effort has been made to limit the area occupancy of the front-end electronics and, at the same time, increasing the segmentation (pixel pitch) for better spatial resolution. The reading is the most critical operation because the photodiode has to be properly biased by connecting the cathode to the power supply through a NMOS (M1 in Fig. 1.1a) fixing its voltage to  $(V_{DD} - V_{th})$ . In Fig. 1.1b an additional voltage drop has been highlighted due to the capacitive coupling between gate and source of M1, when the transistor is turned off. The useful signal is represented by the voltage variation measured at the cathode of the photodiode with respect to this voltage and therefore this configuration limits the useful excursion of the signal. In addition, it should be avoid that the source follower (M2 in Fig. 1.1a) leaves the saturation region, otherwise it would further reduce the voltage swing.

The scaling of CMOS technology introduces significant advantages (for example in the reduction of area occupancy) but from the point of view of the sensitive element requires a greater attention in the design, creating new challenges. In fact the relationship between pixel dimensions and minimum channel length is not straightforward due to the different scaling. Consequently, beyond a certain level of technological integration, pixel scaling is no longer convenient, as the improvement in resolution is no longer sufficient to compensate for a bunch of new disadvantages. Indeed, while the decrease in the supply voltage tends to be proportional to the scaling, the threshold voltages do not decrease following the same trend, reducing the useful signal swing.

#### **1.3 Simulation Results**

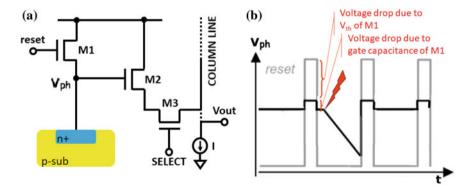

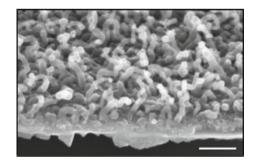

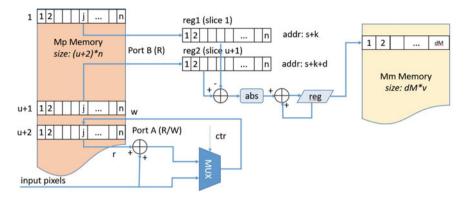

The chip uses two different layout of 3 T pixels, called Small Pixel and Large Pixel (Fig. 1.2). They differ in the sensitive area dimensions, respectively 0.25 and 56  $\mu$ m<sup>2</sup>, while sharing the same square overall occupation, featuring 10  $\mu$ m pixel pitch. Therefore, on a total pixel area of 100  $\mu$ m<sup>2</sup>, the FF of the Small Pixel is around 0.25% while the FF of the Large Pixel is 56%.

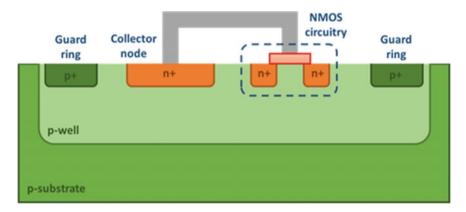

The sensing node (photodiode) is made by a n+ doped implantation, hosted in a deep p-well which is in turn realized on a standard, p-type substrate (Fig. 1.3). The metal interconnections have been shaped aiming at minimizing the antenna effects, at the same time aiming at multiple n+ contacts integration. Within the design flow, several parametric simulations have been carried out, aiming at exploring the different combinations of both reset and source follower transistors and photodiode node geometries and their impact on the pixel performance as a function of an external stimulus compatible with a MIP generation. As a general outcome, the Small Pixel exhibits better performance for low radiation intensity, as illustrated in the following.

In particular, in Table 1.1 the post-layout voltage drops  $(\Delta V)$  on pixel output are reported, as a function of the sensitive node dimensions. A larger sensitive area would in principle collects more charge, with an upper limit corresponding to the Full Well Capacity (FWC). However, a larger area corresponds to a larger (parasitic) capacitance, thus reducing the charge to voltage conversion factor. Following these

Fig. 1.2 a Small pixel and b Large pixel layouts

Fig. 1.3 Simplified cross section of the pixel

indications, we selected the Small Pixel with active area of  $0.5 \times 0.5 \,\mu\text{m}^2$ , while for the Large Pixel we selected the option with the maximum area coverage (Fig. 1.2).

Considering the Small Pixel, Tables 1.2 and 1.3 show that the voltage drop in postlayout simulations tends to decrease at increasing transistor width (W) and length (L). This is due to the contribution of the reset and source follower transistors to the sensing node capacitance. According to this finding, the dimensions and aspect ratio of all the transistors within the pixel has been kept at the minimum value according to the design rules (150/110). Therefore, along the same line, the transistors within the Large Pixel have been kept at the minimum value according to the design rules as well, since the increase of their dimensions does not significantly affect the sensing node capacitance, being dominated by the large diode diffusion capacitance.

Eventually, in Table 1.4 are reported the post-layout voltage drops as a function of the radiative stimulus parameters, namely amplitude and duration of the resulting

| Dimensions (µm <sup>2</sup> ) | $\Delta V (mV)$ |

|-------------------------------|-----------------|

| $0.39 \times 0.39$            | 188.58          |

| $0.5 \times 0.5$              | 190.63          |

| 1 × 1                         | 173.68          |

| $2 \times 2$                  | 98.66           |

| $4 \times 4$                  | 34.68           |

| 6 × 6                         | 16.5            |

| MAX                           | 10.7            |

Table 1.1

Voltage drops as a function of the photodiode sensitive area

Table 1.2 Voltage drops versus width (W) and length (L) of M1 for the Small Pixel

| W (nm)     | $\Delta V (\mathrm{mV})$ |

|------------|--------------------------|

| 150        | 190.63                   |

| 300<br>450 | 134.17                   |

| 450        | 98.35                    |

| L (nm)     | $\Delta V (mV)$          |

| 110        | 190.63                   |

| 220        | 153.75                   |

| 330        | 149.35                   |

Table 1.3 Voltage drops versus width (W) and length (L) of M2 for the Small Pixel

| W (nm) | $\Delta V (\mathrm{mV})$ |  |  |

|--------|--------------------------|--|--|

| 150    | 190.63                   |  |  |

| 300    | 187.18                   |  |  |

| 450    | 179.73                   |  |  |

| L (nm) | $\Delta V (\mathrm{mV})$ |  |  |

| 110    | 190.63                   |  |  |

| 220    | 170.82                   |  |  |

| 330    | 163.82                   |  |  |

current pulse (used as input for circuit level simulation purposes). Data coming from device simulations were exploited to characterize a compact model of the sensing element: a junction diode was supplemented by a current generator describing a radiation-induced current pulse as predicted by device simulations. The quantitative effects of the increase of both pulse amplitude and width are reported in Fig. 1.4.

With reference to noise it should be underlined that the pixel-reset noise ( $N_{reset}$ ) is determined by the thermal noise of the photodiode and is proportional to the inverse of the capacitance seen at the photodiode node. Charge-integration noise ( $N_{integr}$ ) is instead due to dark current and is approximately proportional to the inverse of the

| Amplitude (A) | $\Delta V (\mathrm{mV})$ |  |  |  |

|---------------|--------------------------|--|--|--|

| 600 n         | 10.7                     |  |  |  |

| 1.2 μ         | 14.89                    |  |  |  |

| 1.8 μ         | 19.11                    |  |  |  |

| 2.4 µ         | 23.35                    |  |  |  |

| Duration (ns) | $\Delta V (\mathrm{mV})$ |  |  |  |

| 2             | 23.35                    |  |  |  |

| 4             | 37.36                    |  |  |  |

| 6             | 51.21                    |  |  |  |

|               |                          |  |  |  |

**Table 1.4**Voltage drops as a function of the amplitude and duration of the radiative stimulus forthe Large Pixel

**Fig. 1.4** Voltage drops as a function of the radiative stimulus parameters for the Large Pixel (amplitude on the left, duration on the right)

square of the capacitance [2]. Total pixel noise (obtained from the root mean square of reset and charge-integration noises) is expected to be in the order of a few mV.

#### 1.4 Test Setup

A suitable test environment has been set up, due to the different features that have to be validated, ranging from stand-alone photodiode response to the test of small matrices. This results in a dedicated sequence of test signals to be generated and delivered to the chip which have been devised using a standard Arduino Due board based on a 32-bit ARM core microcontroller. A critical issue concerns the radiation source to be used for testing purposes. To allow for optical test, coverage of sensitive areas with metal layers has been avoided in the chip design. A dedicated PCB has also been designed, accounting for size constraints coming from the optical setup. From the functional point of view, maximum flexibility has again been pursued, accounting for both manual and automatic test procedures. All the control and I/O signals can be generated either through on-board hardware circuitry, by means of routines driving the test board from a PC. Test-board assembly has currently been completed, and actual test is planned to be carried out in the next months.

#### 1.5 Conclusion

This work aimed at the validation of basic performance of sensitive elements integrated in standard 110 nm LFoundry technology conceived for CMOS Image Sensor fabrication for particle detection application. The suitability of such an approach, in particular the adoption of a standard CMOS substrate with optimized pixel layout, has been verified. Results were very encouraging: a significant SNR, expressed in terms of output voltage drop, has been obtained in post-layout simulation. A dedicated PCB has also been designed and fabricated and test on actual chip are on-going.

Acknowledgements This work was supported by the *Department of Engineering* ("Ricerca di Base" 2017 and 2018) and by the *INFN* (SEED and ARCADIA projects).

#### References

- Villani EG et al (2005) Simulation of a novel, radiation-resistant active pixel sensor in a standard 0.25 μm CMOS technology. IEEE Trans Nucl Sci 52(3):752–755

- 2. Passeri D et al (2004) Design, fabrication, and test of CMOS active-pixel radiation sensors. IEEE Trans Nucl Sci 51:1144–1149

- 3. Wang T et al (2017) Development of a depleted monolithic CMOS sensor in a 150 nm CMOS technology for the ATLAS inner tracker upgrade. JINST

- LFOUNDRY TECHNOLOGY 110nm' (Online). http://www.lfoundry.com/en/ technology. Accessed 9 Sept 2019

- Conti E et al (2013) Use of a CMOS image sensor for an active personal dosimeter in interventional radiology. IEEE Trans Instrum Meas 62(5):1065–1072

- 6. Gao W et al (2018) Total-ionization-dose radiation-induced noise modeling and analysis of a  $2k \times 2k$  4T CMOS active pixel sensor for space applications. IEEE Sens J 18(19):8053–8063

# Chapter 2 Design, Operation and BER Test of Multi-Gb/s Radiation-Hard Drivers in 65 nm Technology for Silicon Photonics Optical Modulators

# G. Ciarpi, S. Cammarata, S. Faralli, P. Velha, G. Magazzù, F. Palla and Sergio Saponara

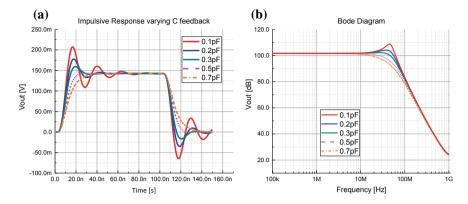

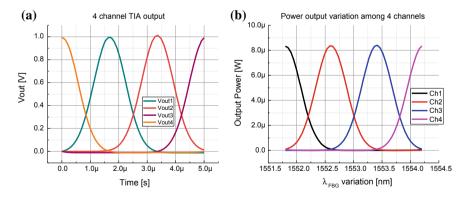

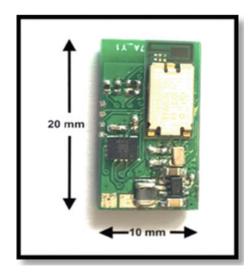

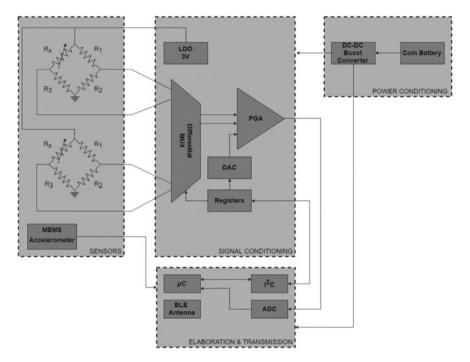

**Abstract** The paper presents the design and the performance characterization, through system-level bit error rate (BER) tests, of a driver for silicon photonics Mach-Zehnder modulator (MZM) devices. Fabricated in TSMC 65 nm technology, the driver exploits a differential topology and a multi-stage current-mode logic architecture. It is designed to withstand radiation levels in compliance with the requirements for the on-detector systems in future particle physics experiments. The driver has been tested up to 800 Mrad showing about 30% degradation in voltage ratings. The BER test made on the stand-alone driver shows a capability of handling 5 Gb/s bit-rates with a quasi-error free BER of  $10^{-11}$ . Electro-optical system-level BER tests carried out with an MZM wire-bonded to the designed driver showed an unexpected degradation in speed performances, which has been mainly attributed to packaging issues. Optimization and re-design activities, still working with 65 nm technology, are currently on-going to meet a data rate of 10 Gb/s for the same radiation hardness.

**Keywords** Silicon photonics · Mach-Zehnder modulator driver · Current-mode logic · Radiation hardness · High energy physics · BER characterization

#### 2.1 Introduction

Silicon Photonics (SiPh) has become a viable technology for reducing the size, weight and energy consumption of optical devices for short-reach optical interconnects. All-

G. Ciarpi · S. Cammarata (🖂) · G. Magazzù · S. Saponara

Dipartimento di Ingegneria dell'Informazione, Università di Pisa, Via G. Caruso 16, Pisa, Italy e-mail: cammarata.simone@yahoo.it

G. Ciarpi · S. Cammarata · S. Faralli · G. Magazzù · F. Palla Istituto Nazionale di Fisica Nucleare – Sezione di Pisa, L. Pontecorvo 3, Pisa, Italy

S. Cammarata · S. Faralli · P. Velha Scuola Superiore Sant'Anna – Istituto TeCIP, Via G. Moruzzi 1, Pisa, Italy

<sup>©</sup> Springer Nature Switzerland AG 2020

S. Saponara and A. De Gloria (eds.), *Applications in Electronics Pervading Industry, Environment and Society*, Lecture Notes in Electrical Engineering 627,

https://doi.org/10.1007/978-3-030-37277-4\_2

silicon modulators are essential components for such communication links and are currently being evaluated at the Europen Organization for Nuclear Physics (CERN) in order to asses their suitability for use in high energy physics (HEP) experiments. Optical and electronic devices installed in the particle detection region have to ensure high reliability to radiation exposure. Custom-made SiPh Mach-Zehnder modulators (MZMs) have already been proved to tolerate radiation levels in line with those expected for future particle physics experiments [1]. In the context of CERN's large hadron collider (LHC) upgrade foreseen for 2026, the beam luminosity boosting will determine a significant increase in data traffic, on the order of dozens of tera-bits per second (Tb/s). The installation of optical transceivers with few Gb/s read-out capabilities will then be required [2]. It represents a data transfer speed roughly one order of magnitude higher than the throughputs currently achievable with state-of-the-art HEP front-end circuits, like those belonging the RD53 project [3].

Photonic devices easily reach operational bandwidths above 10 GHz, but the exploitation of these technologies in compact modules would be possible only after a careful design of the conditioning electronics which allows to encode a data stream onto an optical carrier. The aim of this work is to design a full-custom electronic integrated circuit (EIC) to operate with the MZM presented in [4], withstanding, at the same time, total ionizing doses (TID) up to 1 Grad and 1 MeV equivalent neutron fluences on the order of a few  $10^{16}$  cm<sup>-2</sup> regarding radiation damage from non-ionizing energy losses (NIEL).

Section 2.2 introduces the MZM driver (MZMD) core structure and the main circuital solutions which have been implemented to properly drive a traveling-wave MZM. A purely electrical characterization of the driver performances in terms of bandwidth, output voltage amplitude and bit error rate (BER) is detailedly reported in Sect. 2.3. The following section presents the overall system-level results and describes the electro-optical setup implemented to perform BER measurements of an hybrid transmitting unit made of an MZM driven by the developed MZMD. Conclusions are drawn in Sect. 2.5, mentioning the further activities that are currently ongoing towards the realization of a working prototype suitable for HEP environments.

#### 2.2 Mach-Zehnder Modulator Driver Design

The full-custom MZM driver was designed in the commercial-grade TSMC 65 nm technology because of its recognized radiation hardness, mainly determined by its very thin gate oxide. Ionizing energy losses induce a build-up of positive trapped charges in oxide layers, causing threshold voltage shifts and current leakage in MOS-FET devices. The thinner the oxide the less charges could be trapped and, in turn, the less detrimental will be the radiation effect on the electronic circuit. However, p-MOSFET devices are more sensitive to TID than their n-type counterpart, e.g. a minimum-sized diode-connected p-MOSFET loses the 100% of its on-current after being exposed to a TID of 1 Grad [5]. For this reason, the driver needed to be de-

veloped avoiding p-type MOSFETs [6]. A current-mode logic (CML) architecture, which exploits only n-MOSFETs and passive devices, has thus been adopted.

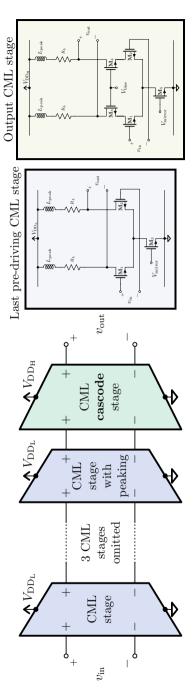

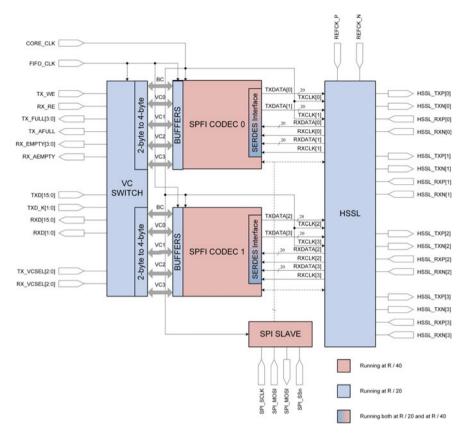

In order to meet speed and wide output swing constraints, the circuit was structured as sketched in Fig. 2.1. Five CML pre-driving stages, supplied at  $V_{DD,L} = 1.2$  V and with gradually increasing sizes, forego an output stage with  $V_{DD,H} = 2.4$  V. The current drained from the  $V_{DD,L}$  power supply (comprising the whole set of pre-driving stages) is around 35 mA while the output stage sinks approximately 60 mA, keeping the MZMD power consumption below 200 mW. Because of the radiation requirements only thin-oxide MOSFETs have been used, therefore the last stage exploits a cascode topology to share the wide voltage drop on two devices. Moreover, a bandwidth increment is obtained using inductive peaking techniques in the last two stages [7, 8].

#### 2.3 Circuit-Level Electrical and Radiation Tolerance Testing

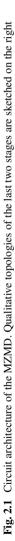

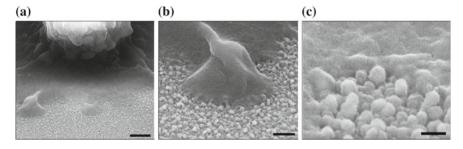

The electrical characterization of the driver was performed in terms of scattering parameters measurements, eye diagram plots and BER tests. S-parameters were carried out gluing the chip on a carrier board and contacting the chip pads with RF and DC probes, as shown in Fig. 2.2.

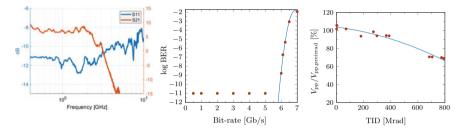

Figure 2.3 shows the  $S_{21}$  and  $S_{11}$  parameters of the driver. The 3-dB  $S_{21}$  bandwidth point is measured around 2.5 GHz, highlighting a potential application of the driver to bit-rates up to 5 Gb/s. The blue line shows that the input matching network of the driver works properly up to 4 GHz, whereupon the  $S_{11}$  parameter exceeds -10 dB.

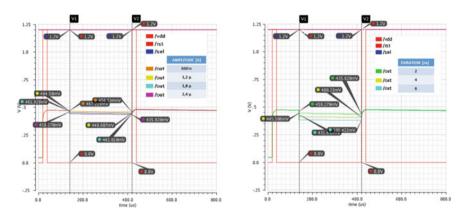

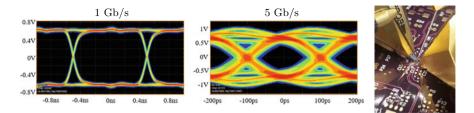

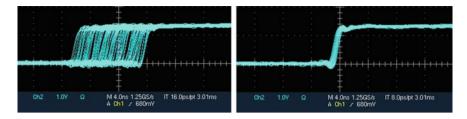

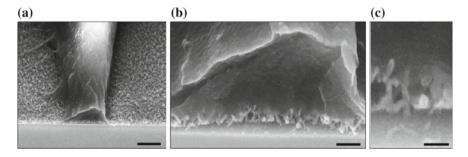

Regarding eye diagrams and BER tests, the EIC was bonded on a custom-made printed circuit board (PCB). Standard SMA coaxial cables were used to connect the board to the instruments, while impedance-matched coplanar transmission lines convey the signals on the PCB. A 12.5 Gb/s pulse pattern generator (PPG) has been used to generate a pseudo random binary sequence (PRBS) following a PRBS-31 pattern, with voltage characteristics in compliance with standard CML levels. The eye diagrams obtained feeding the driver with this signal and measuring the output waveforms with a 23 GHz-bandwidth oscilloscope are shown in Fig. 2.2. The two eye diagrams present nearly the same amplitude, while higher noise and jitter appear at 5 Gb/s.

A BER tester (BERT) was then exploited to understand the impact of jitter-related penalties from a system-level viewpoint. Figure 2.3 reports the BER values for different bit-rates. A plateau at  $10^{-11}$  is shown for data-rates up to 5 Gb/s, indicating that no error have been registered out of 1 Tb of transmitted data. This confirms a *quasi error-free* operation till a bit-rate of 5 Gb/s.

The circuit radiation resistance was investigated exposing the whole EIC to xrays with a dose rate of 4.3 Mrad/h at the INFN-Padova facility. The normalized voltage amplitude degradation of the output signals with increasing dose level is

Fig. 2.2 Left: eye diagrams of driver output voltage at different bit-rates. Right: picture of the on-chip characterization setup

Fig. 2.3 MZMD circuit-level electrical characterization. Input-output S-parameters are reported on the left, while in the middle BER performances are shown. On the right, radiation-induced peak-to-peak voltage  $(V_{pp})$  degradation is documented

reported in Fig. 2.3. At 800 Mrad, which was the highest dose level reached during the test because of limited testing time, the signal amplitude was reduced by 30% with respect to the pre-irradiation value.

#### 2.4 System-Level Electo-Optical BER Testing

The fidelity of a data transmission system is ultimately quantified by the BER. An MZM fabricated in the Imec's isipp25g technology and the custom driver realized within this work have been hybridly integrated on a PCB. The only difference with respect to the testing scenario described in Sect. 2.3 is that the driver output pads are now wire-bonded with the MZM electrodes. The MZM under test is 1.5 mm-long and has no termination impedance. Measurements made on the same MZM with RF probes guarantee that its electro-optical modulation bandwidth remains above 5 GHz also with this load impedance mismatch, thus validating that the bandwidth-bottleneck remains in the electronic domain.

In the framework of fiber optic links, two types of characterization could be performed to carry out BER performances: optical noise loading and receiver sensitivity measurements. The former is an important metric for links which needs to be optically amplified while the latter is more suitable for non-amplified interconnects,

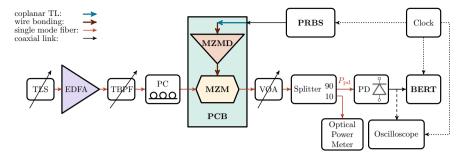

**Fig. 2.4** Electro-optical setup for system-level characterization of an OOK link. Acronyms: TBPF (tunable band-pass filter), PC (polarization controller)

like those used within HEP experiments which cover 200 m at most. Hence, BER performances have been evaluated in function of bit-rate and received power on the photo-detector (PD).

As shown in Fig. 2.4, a standard on-off keying (OOK) transmitting system has been set up. The same PRBS-31 signal is applied at the driver input as before. A tunable laser source (TLS) was used to provide light in the C band near 1550nm. The wavelength tuning allowed to set the MZM at the quadrature point. Light is coupled to the PIC using pigtailed fiber arrays and on-chip grating couplers. The modulated optical signal is attenuated with a variable optical attenuator (VOA) and then captured with a commercial PD, which is directly connected to the BER tester (BERT). Because of some issues encountered in the packaging procedure, which was performed manually, the fiber arrays resulted to be a little misaligned, causing an increase in optical insertion losses compared to similar devices realized in the same technology. Therefore, an erbium-doped fiber amplifier (EDFA) was required to perform BER tests. Even delivering the maximum rated optical power from the TLS the optical intensity at the MZM output was too low that an EDFA placed downstream the DUT failed to amplify the signal for photo-detection. The EDFA was then positioned before the MZM in the optical path, resulting in an injected power in the PIC of about 20 dBm, and an OSNR of 26 dB. Nevertheless, non-linear optical effects have not been captured throughout the measurement routines.

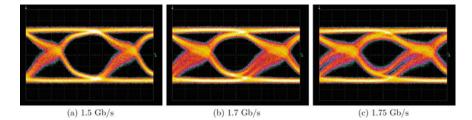

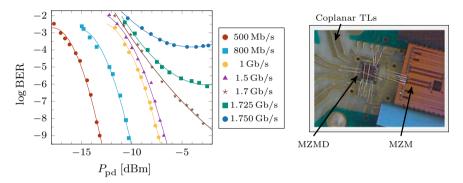

Optical eye diagrams and measured BERs as a function of input power  $P_{pd}$  on the photo-detector are shown for different data rates respectively in Figs. 2.5 and 2.6. The whole system is correctly working up to a bit-rate of 1.5 Gb/s while BER floors start to appear around 1.7 Gb/s, suggesting a systematic failure of the system. The eye diagrams at the PD output indeed report a sharp increase in jitter and intersymbol interference (ISI) as the bit-rate reaches the 1.7 Gb/s level. Even if such poor speed achievements are in contrast with the previously presented BER performances of the stand-alone driver, these unexpected results could also be attributed to the non-optimum arrangement of wire bondings, as can be seen from Fig. 2.6.

**Fig. 2.5** Eye diagrams at the PD output for different data rates: **a** 1.5 Gb/s, **b** 1.7 Gb/s, **c** 1.75 Gb/s. All the plots have the same vertical scale of 20 mV/div

Fig. 2.6 BER performance of the data transmitting unit composed of the designed driver and a MZM bonded together. Acronyms: TL (transmission line)

#### 2.5 Conclusions and Further Work

The design and the experimental characterization of a radiation-hard driver for a traveling-wave MZM have been reported at circuit-level as well as on a communication-link basis. Electrical measurements confirmed that the electronic driver is capable of withstanding data-rates up to 5 Gb/s as required by optical links specification in the HEP framework. A deviation from the expected speed capabilities has shown up during the system-level electro-optical BER test suggesting a leak in the packaging procedure. For this reason, further activities have already started to mitigate package-related parasitic effects and arrive to a working multi-Gb/s transmitter to be deployed in particle physics detectors. Also advanced solutions, such as flip-chip bump-bonding, are under investigation to avoid the usage of wire bondings between EICs and PICs when dealing with radio-frequency large signals as in this case study.

#### References

- Kraxner A, Detraz S, Olantera L, Scarcella C, Sigaud C, Soos C, Troska J, Vasey F (2018) Investigation of the influence of temperature and annealing on the radiation hardness of silicon Mach-Zehnder modulators. IEEE Trans Nucl Sci 65(8):1624–1631

- Colombo T, Amihalachioaei A, Arnaud K, Alessio F et al (2018) The LHCb online system in 2020: trigger-free read-out with (almost exclusively) off-the-shelf hardware. J Phys Conf Ser 1085:032041

- Paternò A, Pacher L, Monteil E, Loddo F, Demaria N, Gaioni L, Canio FD, Traversi G, Re V, Ratti L, Rivetti A, Rolo MDR, Dellacasa G, Mazza G, Marzocca C, Licciulli F, Ciciriello F, Marconi S, Placidi P, Magazzù G, Stabile A, Mattiazzo S, Veri C (2017) A prototype of pixel readout ASIC in 65 nm CMOS technology for extreme hit rate detectors at HL-LHC. J Instrum 12(2):C02043

- Zeiler M, El Nasr-Storey SS, Detraz S, Kraxner A, Olantera L, Scarcella C, Sigaud C, Soos C, Troska J, Vasey F (2017) Radiation damage in silicon photonic mach-zehnder modulators and photodiodes. IEEE Trans Nucl Sci 64(11):2794–2801

- Faccio F, Borghello G, Lerario E, Fleetwood DM, Schrimpf RD, Gong H, Zhang EX, Wang P, Michelis S, Gerardin S, Paccagnella A, Bonaldo S (2018) Influence of ldd spacers and H<sup>+</sup>transport on the total-ionizing-dose response of 65-nm MOSFETs irradiated to ultrahigh doses. IEEE Trans Nucl Sci 65(1):164–174

- 6. Ciarpi G, Saponara S, Magazzù G, Palla F (2019) Radiation hardness by design techniques for 1 grad tid rad-hard systems in 65 nm standard cmos technologies. In: Saponara S, De Gloria A (eds) Applications in electronics pervading industry, environment and society. Springer International Publishing, Cham, pp 269–276

- Palla F, Ciarpi G, Magazzù G, Saponara S (2019) Design of a high radiation-hard driver for Mach–Zehnder modulators based high-speed links for hadron collider applications. Nucl Instrum Methods Phys Res Sect A Accelerators Spectrometers Detectors Assoc Equipment **936**:303–304 (Frontier Detectors for Frontier Physics: 14th Pisa Meeting on Advanced Detectors)

- Ciarpi G, Magazzù G, Palla F, Saponara S (2018) Design of radiation-hard MZM drivers. In: 20th Italian national conference on photonic technologies (Fotonica 2018), May 2018, pp 1–4

# Chapter 3 A Rad-Hard Bandgap Voltage Reference for High Energy Physics Experiments

G. Traversi, L. Gaioni, M. Manghisoni, M. Pezzoli, L. Ratti, V. Re, E. Riceputi and M. Sonzogni

Abstract This work is concerned with the characterization of a bandgap reference circuit, fabricated in a commercial 65 nm CMOS technology, designed for applications to HL-LHC experiments. Measurement results show a temperature coefficient of about 16 ppm/°C over a temperature range of 140 °C (from -40 to 100 °C) and a variation of 1.6% for  $V_{DD}$  from 1.08 to 1.32 V. The mean value of the bandgap output is about 400 mV, with a 5% maximum shift when exposed to a Total Ionizing Dose (TID) around 1 Grad (SiO<sub>2</sub>). The power consumption is 165  $\mu$ W at room temperature, with a core area of 0.02835 mm<sup>2</sup>.

**Keywords** Bandgap voltage reference · Deep submicron · CMOS · Radiation effects · Total ionizing dose (TID)

#### 3.1 Introduction

Voltage references, which provide precise, stable and temperature-insensitive DC voltages, are fundamental building blocks in mixed-mode circuits. The bandgap reference (BGR) is one of the most popular voltage reference that successfully achieves these requirements. It generates a voltage which is obtained from the sum of the voltage across a forward biased pn junction (inversely dependent on the absolute temperature) and a term directly proportional to the absolute temperature (PTAT). Unfortunately, this architecture is not suited for advanced CMOS technology where

M. Pezzoli · L. Ratti

G. Traversi (🖂) · L. Gaioni · M. Manghisoni · V. Re · E. Riceputi · M. Sonzogni

Dipartimento di Ingegneria e Scienze Applicate, Università degli Studi di Bergamo, Via Marconi 5, 24044 Dalmine, BG, Italy

e-mail: gianluca.traversi@unibg.it

Dipartimento di Ingegneria Industriale e dell'Informazione, Università degli Studi di Pavia, Via Ferrata 1, 27100 Pavia, Italy

G. Traversi · L. Gaioni · M. Manghisoni · M. Pezzoli · L. Ratti · V. Re · E. Riceputi · M. Sonzogni Istituto Nazionale di Fisica Nucleare, Sezione di Pavia, Via Bassi 6, 27100 Pavia, Italy

<sup>©</sup> Springer Nature Switzerland AG 2020

S. Saponara and A. De Gloria (eds.), *Applications in Electronics Pervading Industry, Environment and Society*, Lecture Notes in Electrical Engineering 627, https://doi.org/10.1007/978-3-030-37277-4\_3

the supply voltage is 1.2 V or even lower. For this reason, in the last ten years, use of nonstandard devices in place of BJT or diodes has been proposed [1], but at the cost of a poor portability of the design and with the risks associated to the lack of accurate models for nonstandard devices. The resistive subdivision technique has been proposed to implement sub-1V BGR circuits [2], although this technique is not suitable for high-precision references working in a large temperature range. This paper discusses a BGR architecture based on a commercial 65 nm CMOS technology and capable of operating with 1.2 V supply. The proposed IP block has been designed for operation in the harsh radiation environment of the High Luminosity LHC. The 65 nm CMOS technology chosen for this prototype has been tested up to 1 Grad with promising results for CMOS transistors [3]. Nonetheless, other components of the BGR, namely bipolar devices, are affected by bulk damage effects. For this reason, in order to understand their behavior after irradiation, three different BGR versions (the first one based on parasitic PNP bipolar transistors, the second based on pn diodes and the third one based on enclosed-layout MOSFETs biased in weak inversion region) have been designed and submitted for fabrication in a prototype chip. These circuits have been fabricated and characterized before and after irradiation up to 225  $Mrad(SiO_2)$  and the third design (the one based on MOSFETs) demonstrated the best performance in terms of radiation hardness [4]. Based on this work, a voltage reference circuit, designed in a commercial 65 nm CMOS technology and capable of operating in harsh radiation environments up to 1 Grad has been developed and its characterization is shown in this paper.

#### **3.2** Operating Principle and Characterization Results

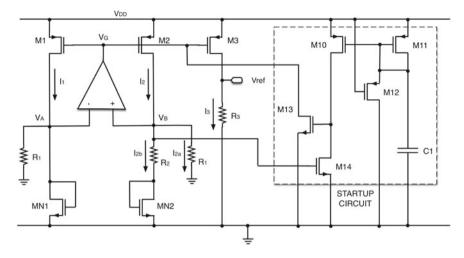

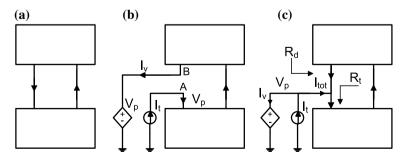

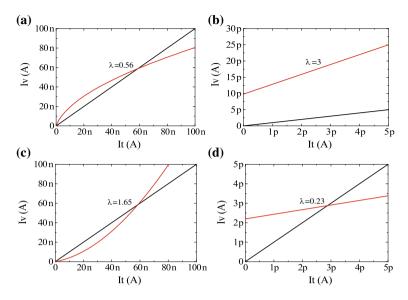

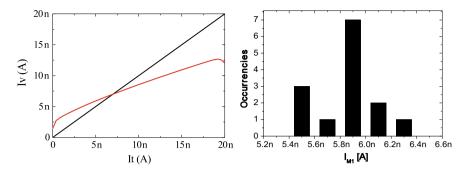

The bandgap circuit described in this paper and shown in Fig. 3.1, is based on a current mode approach [1]. Two currents, one  $(I_{2b})$  proportional to absolute temperature (PTAT) and one  $(I_{2a})$  complementary to absolute temperature (CTAT) are generated and summed in order to obtain a voltage insensitive to temperature. As already mentioned in the Introduction, with the purpose of increasing the radiation hardness of the circuit, only MOSFETs devices have been included in the circuit. In order to obtain a behavior similar to a bipolar transistor, they have been biased in the weak inversion region, where the I-V characteristic of the device is:

$$I_D = \frac{W}{L} I_0 \cdot exp\left(\frac{V_{GS} - V_{th}}{\eta V_T}\right) \cdot \left[1 - exp\left(-\frac{V_{DS}}{V_T}\right)\right]$$

(3.1)

where the  $V_{DS}$  dependence of the drain current can be neglected when  $V_{DS} \ge 4V_T$ . Being M1, M2 and M3 equally sized, the BGR output value is given by:

$$V_{REF} = \frac{R_3}{R_1} \left[ V_{GS1} + \frac{R_1}{R_2} \Delta V_{GS} \right].$$

(3.2)

Fig. 3.1 Schematic of the bandgap reference together with the startup circuit

Since bandgap circuit has two stable operating points, it requires a start-up circuit to prevent operation in the undesired one. Figure 3.1 shows the startup circuit implemented [5]. It is based on a pull down capacitor. During the power on, a current starts to charge the capacitor  $C_1$ , the current is mirrored by  $M_{11}$  and  $M_{12}$  and it charges the gate of  $M_{13}$  thus turning the transistor on.  $M_{13}$  pulls down the gate of the bandgap current mirror injecting current into the bandgap. The power consumption of the startup circuit after power on is zero because, after startup,  $M_{14}$  is turned on and  $M_{13}$  is cutoff. Moreover,  $M_{12}$  discharges  $C_1$  when power supply is switched off.

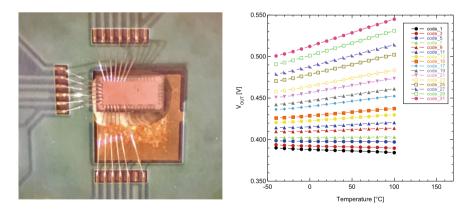

The proposed bandgap reference was fabricated in a commercial 65 nm CMOS technology. The chip microphotograph is presented in Fig. 3.2 (left). Extensive ex-

Fig. 3.2 (Left) Die microphotograph (2 mm  $\times$  1 mm); (right) measured temperature dependence of the bandgap reference voltage as a function of the temperature for different configuration bits of R<sub>2</sub>

perimental measurements were performed in order to characterize the actual behavior of the proposed architecture. For example, the temperature behavior has been measured between -40 and 100 °C while the circuit will operate at -30 °C during the experiment and between about 20 and 40 °C during the operation without cooling. The measurements were performed using Keysight 34461A Digital Multimeter and GENVIRO-030LC Temperature Chamber. In order to be able to compensate for possible process and mismatch effects, the programmability of resistor R<sub>2</sub> (5 bits) has been included. Figure 3.2 (right) shows the measured output voltage as a function of the configuration word, while Table 3.1 summarizes the main characteristics of the bandgap circuits. The comparison shows that the proposed circuit provides the minimum variation of the reference voltage after irradiation. In addition, if needed, the line regulation of this work can be improved by adding a regulated cascode at the

|                                     | This work      | [8]               | [6]               | [9]                               |

|-------------------------------------|----------------|-------------------|-------------------|-----------------------------------|

| Supply voltage (V)                  | 1.2            | 1.2               | 1.2               | 1.2                               |

| Operating voltage range (V)         | 1.08-1.32      | 0.85-1.4          | 1.08-1.32         | 0.85-1.5                          |

| Nominal reference voltage (mV)      | 400            | 405               | 330               | 600                               |

| Line regulation (1.08–1.32 V) (%/V) | 4              | 2.72              | 0.25              | -                                 |

| Temperature coefficient (ppm/°C)    | 16             | 30.5              | 130               | 15                                |

| Temperature range (°C)              | -40 to 100     | 0-80              | -40 to 80         | -40 to 125                        |

| Power consumption @ 25 °C (µW)      | 165            | -                 | 240               | 60                                |

| Radiation induced $\Delta V_{REF}$  | 5% @<br>1 Grad | 0.8% @<br>45 Mrad | 10% @<br>800 Mrad | ± 3% (5<br>samples) @<br>450 Mrad |

| Layout Area (mm <sup>2</sup> )      | 0.028          | 0.064             | 0.018             | 0.056                             |

| Technology                          | CMOS<br>65 nm  | CMOS<br>130 nm    | CMOS<br>65 nm     | CMOS<br>130 nm                    |

Table 3.1 Performance summary of the proposed BGR circuit

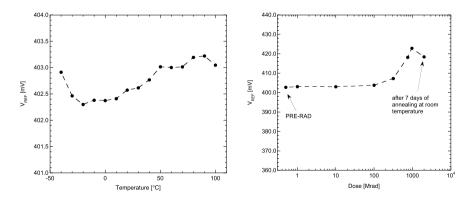

Fig. 3.3 Measured output voltage as a function of the temperature (left); measured output voltage of the bandgap as a function of the absorbed dose of 10 keV X-rays and after annealing (right)

output branch of the circuit, as implemented in [6]. The measured best temperature coefficient (TC) of the bandgap reference is 16 ppm/°C in a range of -40 to 100 °C, as shown in Fig. 3.3 (left).

Irradiation tests were carried out taking into account the unprecedented radiation tolerance requirements of demanding applications such as the HL-LHC [7]. To get an estimate of the performance of the bandgap circuit, we irradiated one device up to about 1 Grad(SiO<sub>2</sub>) total dose of 10-keV X-rays. The irradiation was done at Laboratori Nazionali di Legnaro (Italy) with an X-ray machine at a dose rate of about 1 krad(SiO<sub>2</sub>)/s. During irradiation, the bandgaps were biased as in the real application. Figure 3.3 (right) shows the variation of the output voltage as a function of the TID for the BGR with N-MOSFET. Annealing after one week at room temperature shows minor changes on the reference voltage with respect to the pre-irradiation value.

#### 3.3 Conclusion

In this paper, a new radiation hard bandgap voltage reference circuit has been presented. The circuit has been characterized in a climatic chamber between -40 and +100 °C and irradiated up to 1 Grad(SiO<sub>2</sub>), yielding up to 5% voltage change at the total ionizing dose. The BGR here proposed is able to face very high radiation doses, keeping a reasonable output accuracy, a relatively small area, and a simple architecture.

Acknowledgements The authors wish to thank Serena Mattiazzo and Devis Pantano (University of Padova) for providing the source for X-ray irradiation and for their constant support during the irradiation campaign, and Dr. Francesco De Canio for his contribution to the design and characterization activity. The authors are also in debt with Massimo Rossella (INFN Pavia) who have kindly made the climatic chamber available for the bandgap characterization.

#### References

- Banba H et al (1999) A CMOS bandgap reference circuit with sub-1-V operation. IEEE J Solid State Circ 34:670

- Neuteboom N, Kup BMJ, Janssens J (1997) A DSP-based hearing instrument IC. IEEE J Solid State Circ 32:1790–1806

- 3. Menouni M et al (2015) 1-Grad total dose evaluation of 65 nm CMOS technology for the HL-LHC upgrades. J Instrum 10(5), art. No. C05009

- Traversi G et al (2016) Characterization of bandgap reference circuits designed for high energy physics applications. Nucl Instrum Methods A 824:371–373

- Li W, Yao R, Guo L (2009) A low power CMOS bandgap voltage reference with enhanced power supply rejection. In: Proceedings of the 8th IEEE international conference on ASIC, pp 300–304

- Vergine T, De Matteis M, Michelis S, Traversi G, De Canio F, Baschirotto A (2016) A 65 nm rad-hard bandgap voltage reference for LHC environment. IEEE Trans Nucl Sci 63(3):1762– 1767

- Garcia-Sciveres M, Christainsen J (2013) RD collaboration proposal: development of pixel readout integrated circuits for extreme rate and radiation. CERN-LHCC-2013-008, LHCC-P-006

- Gromov V, Annema AJ, Kluit R, Visschers JL, Timmer P (2007) A radiation hard bandgap reference circuit in a standard 0.13

µm CMOS technology. IEEE Trans Nucl Sci 54(6):2727– 2733

- Cao Y, De Cock W, Steyaert M, Leroux P (2013) A 4.5 MGy TID-tolerant CMOS bandgap reference circuit using a dynamic base leakage compensation technique. IEEE Trans Nucl Sci 60(4):2819–2824

# Chapter 4 Analysis and Comparison of Ring and LC-Tank Oscillators for 65 nm Integration of Rad-Hard VCO for SpaceFibre Applications

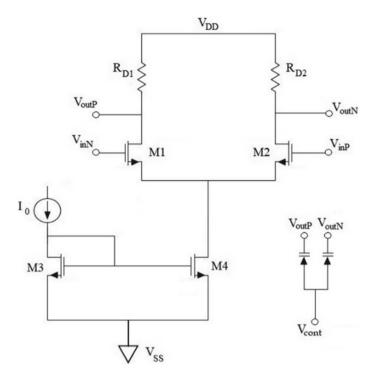

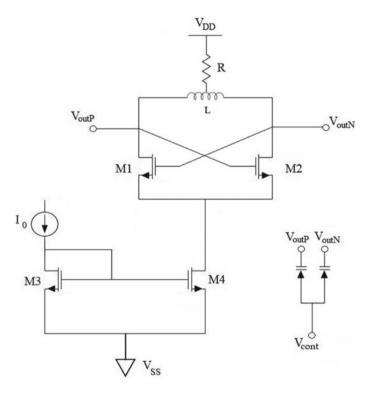

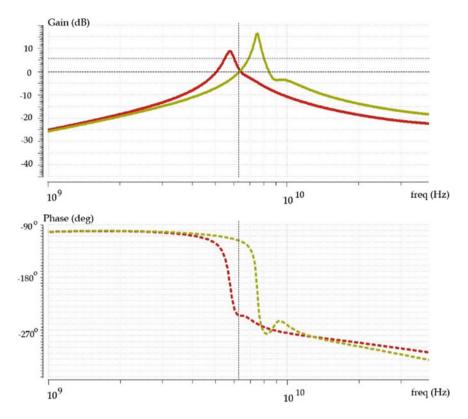

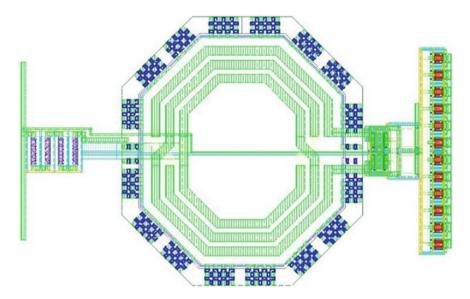

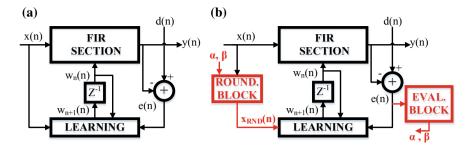

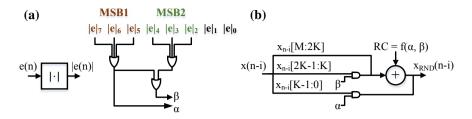

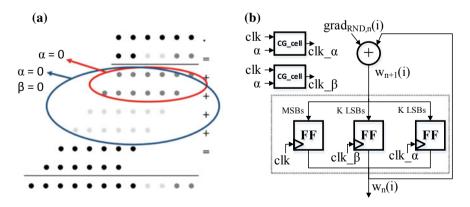

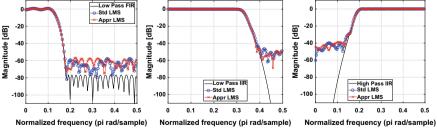

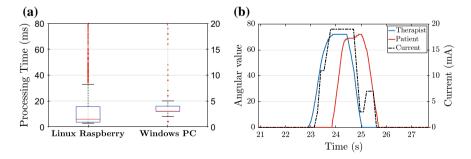

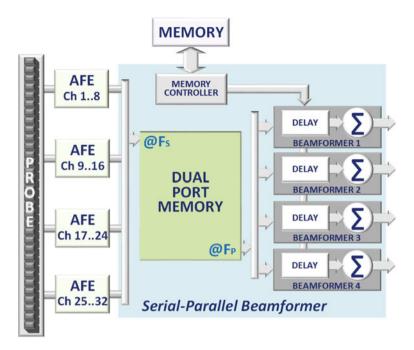

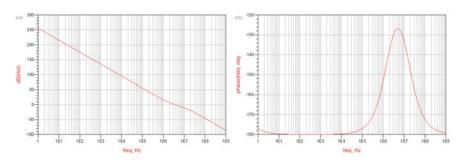

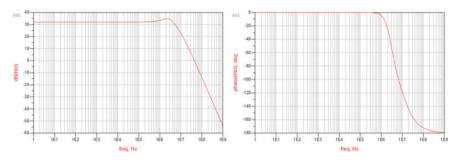

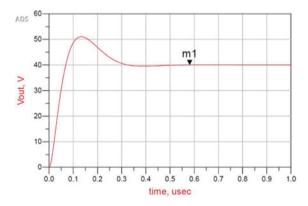

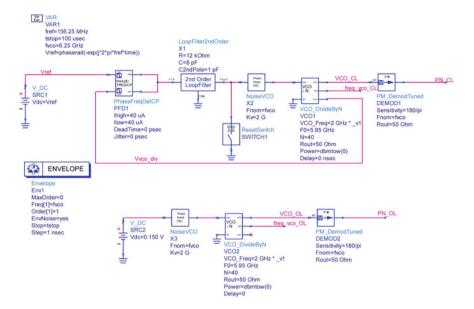

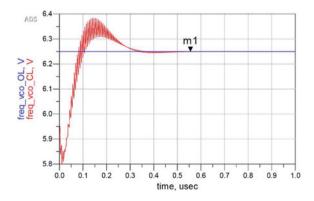

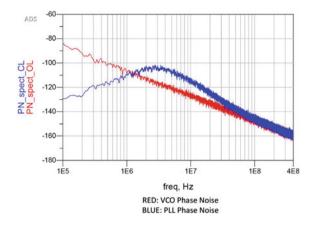

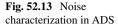

#### D. Monda, G. Ciarpi, G. Mangraviti, L. Berti and Sergio Saponara