#### Ramin Yahyapour (Ed.)

## Euro-Par 2019: Parallel Processing

25th International Conference on Parallel and Distributed Computing Göttingen, Germany, August 26–30, 2019 Proceedings

#### Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board Members

David Hutchison, UK Josef Kittler, UK Friedemann Mattern, Switzerland Moni Naor, Israel Bernhard Steffen, Germany Doug Tygar, USA Takeo Kanade, USA Jon M. Kleinberg, USA John C. Mitchell, USA C. Pandu Rangan, India Demetri Terzopoulos, USA

#### Advanced Research in Computing and Software Science Subline of Lecture Notes in Computer Science

Subline Series Editors

Giorgio Ausiello, University of Rome 'La Sapienza', Italy Vladimiro Sassone, University of Southampton, UK

Subline Advisory Board

Susanne Albers, *TU Munich, Germany* Benjamin C. Pierce, *University of Pennsylvania, USA* Bernhard Steffen, *University of Dortmund, Germany* Deng Xiaotie, *Peking University, Beijing, China* Jeannette M. Wing, *Microsoft Research, Redmond, WA, USA*  More information about this series at http://www.springer.com/series/7407

Ramin Yahyapour (Ed.)

## Euro-Par 2019: Parallel Processing

25th International Conference on Parallel and Distributed Computing Göttingen, Germany, August 26–30, 2019 Proceedings

*Editor* Ramin Yahyapour Gesellschaft für wissenschaftliche Datenverarbeitung mbH Göttingen Georg-August-Universität Göttingen Göttingen, Germany

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-030-29399-4 ISBN 978-3-030-29400-7 (eBook) https://doi.org/10.1007/978-3-030-29400-7

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer Nature Switzerland AG 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### Preface

This volume contains the papers presented at Euro-Par 2019, the 25th International European Conference on Parallel and Distributed Computing, held during August 26–30, 2019, in Göttingen, Germany.

For 25 years, Euro-Par consistently brought together researchers in parallel and distributed computing. Founded by pioneers as a merger of the three thematically related European conference series PARLE and CONPAR-VAPP, Euro-Par started with the aim to create the main annual scientific event on parallel processing in Europe to be the primary choice of such professionals for the presentation of latest results in their fields.

A quarter of a century marks a special occasion to look back and recognize achievements and progress. Since its inception, Euro-Par has been covering all aspects of parallel and distributed computing, ranging from theory to practice, from the smallest to the largest parallel and distributed systems and infrastructures, from fundamental computational problems to full-fledged applications, from architecture, compiler, language, and interface design and implementation to tools, support infrastructures, and application performance. Euro-Par's unique organization into topics, provides an excellent forum for focused technical discussion, as well as interaction with a large, broad, and diverse audience who are researchers in academic institutions, public and private laboratories, or commercial stake-holders.

Euro-Par's topics were always oriented towards novel research issues and the current state of the art. Most topics became constant entries, while new themes emerged and were included in the conference. Euro-Par has a tradition of selecting new organizers and chairs for every edition, leading to fresh ideas and variations while staying true to the tradition. Organizers and chairs of previous editions support their successors. In this sense, Euro-Par also promotes networking across national borders, leading to the unique spirit of Euro-Par.

Previous conferences took place in Stockholm, Lyon, Passau, Southampton, Toulouse, Munich, Manchester, Paderborn, Klagenfurt, Pisa, Lisbon, Dresden, Rennes, Las Palmas, Delft, Ischia, Bordeaux, Rhodes, Aachen, Porto, Vienna, Grenoble, Santiago de Compostela, and Turin.

Thus, Euro-Par in Göttingen followed the well-established format of its predecessors. Euro-Par 2018 successfully added the Chess timer talks and the documentation of artifacts, which were carried over to Euro-Par 2019. The 25th edition of Euro-Par was organized with the support of the Georg-August-Universität Göttingen and GWDG. GWDG serves as the data center of the University and is one of the IT competence centers of the Max Planck Society. Göttingen hosts - jointly with the Konrad-Zuse-Institute in Berlin - the North-German Supercomputer (HLRN), and fosters research in and application of high performance computing. To reflect the applied aspects of parallel computing, new application oriented tracks and workshops were included in the Euro-Par 2019 program.

#### vi Preface

The topics of Euro-Par 2019 were organized into 10 tracks, where topics were merged for organizational reasons or transferred to other event types, namely:

- Support Tools and Environments

- Performance and Power Modeling, Prediction, and Evaluation

- Scheduling and Load Balancing

- Data Management, Analytics, and Deep Learning

- Cluster and Cloud Computing

- Parallel and Distributed Programming, Interfaces, and Languages

- Multicore and Manycore Parallelism

- Theory and Algorithms for Parallel Computation and Networking

- Parallel Numerical Methods and Applications

- Accelerator Computing for Advanced Applications

Overall, 142 papers were submitted from 40 countries. The number of submitted papers, the wide topic coverage, and the aim of obtaining high-quality reviews resulted in a difficult selection process involving a large number of experts. The joint effort of the members of the Scientific Committee and of the 128 external reviewers resulted in 560 reviews: 26 papers received three reviews, 97 received four reviews, and 20 received five or more, that is, on average, 3.94 reviews per paper. The accepted papers were chosen after detailed discussions and finalized during the paper selection meeting, which took place on April 30, 2019. As a result, 36 papers were selected to be presented at the conference and published in these proceedings, resulting in a 25, 3% acceptance rate.

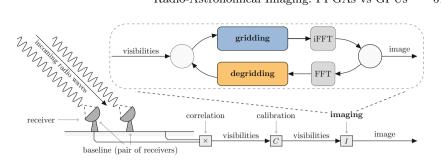

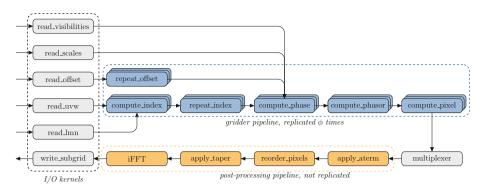

The following two papers were nominated as 'distinguished' and presented in a plenary session: "Radio-Astronomical Imaging: FPGAs vs GPUs" and "Enhancing the Programmability and Performance Portability of GPU Tensor Operations".

In addition to the program, we had the pleasure of hosting three keynotes held by:

- Rosa M. Badia, Barcelona Supercomputing Center, Barcelona, Spain

- Michela Taufer, Tickel College of Engineering and Min H. Kao, Department of Electrical Engineering & Computer Science, Knoxville, Tennessee, USA

- Helmut Grubmüller, Max Planck Institute for Biophysical Chemistry, Theoretical and Computational Biophysics group, Göttingen, Germany

Euro-Par 2019 included a panel discussion and relaunched a poster session, which was specifically aimed at ambitious students.

The conference program started with two days of workshops and a tutorial on specialized topics. Dora Blanco Heras, Christian Boehme, and Ulrich Schwardmann ensured coordination and organization of this pre-conference event as workshop co-chairs. A selection of the papers presented at the workshops will be published in separate proceedings volumes after the conference. The workshop proceedings will also contain the contributions of the poster session.

We would like to thank the authors and chairs for contributing to the success of Euro-Par 2019. Similarly, we would like to extend our appreciation to the Euro-Par 2019 Steering Committee for its support. Last but not least, we would like to express our gratitude to the team at GWDG, whose relentless enthusiasm and effort made this event possible.

August 2019

Ramin Yahyapour Ulrich Schwardmann Christian Boehme

#### Organization

#### **General Chair**

| Ramin Yahyapour | GWDG - Gesellschaft für wissenschaftliche |

|-----------------|-------------------------------------------|

|                 | Datenverarbeitung mbH Göttingen,          |

|                 | University of Göttingen, Germany          |

#### **Steering Committee**

#### **Full Members**

| Luc Bougé                  | ENS Rennes, France                              |

|----------------------------|-------------------------------------------------|

| Fernando Silva             | University of Porto, Portugal                   |

| Marco Aldinucci            | University of Turin, Italy                      |

| Dora Blanco Heras          | CiTIUS, Santiago de Compostela, Spain           |

| Emmanuel Jeannot           | LaBRI-Inria Bordeaux, France                    |

| Christos Kaklamanis        | Computer Technology Institute Patras, Greece    |

| Paul Kelly                 | Imperial College London, UK                     |

| Thomas Ludwig              | University of Hamburg, Germany                  |

| Tomàs Margalef             | University Autonoma of Barcelona, Spain         |

| Wolfgang Nagel             | Technische Universität Dresden, Germany         |

| Francisco Fernández Rivera | CiTIUS, Santiago de Compostela, Spain           |

| Rizos Sakellariou          | The University of Manchester, UK                |

| Henk Sips                  | Delft University of Technology, The Netherlands |

| Domenico Talia             | University of Calabria, Italy                   |

| Jesper Larsson Träff       | Vienna University of Technology, Austria        |

| Denis Trystram             | Grenoble Institute of Technology, France        |

| Felix Wolf                 | Technische Universität Darmstadt, Germany       |

|                            |                                                 |

#### **Honorary Members**

Christian Lengauer Ron Perrott Karl Dieter Reinartz

#### Observers

Krzysztof Rzadca Ramin Yahyapour University of Passau, Germany Oxford e-Research Centre, UK University of Erlangen-Nürnberg, Germany

University of Warsaw, Poland GWDG - Gesellschaft für wissenschaftliche Datenverarbeitung mbH Göttingen, University of Göttingen, Germany

#### Workshops

| Dora Blanco Heras  | University of Santiago de Compostela, Spain                                           |

|--------------------|---------------------------------------------------------------------------------------|

| Christian Boehme   | GWDG - Gesellschaft für wissenschaftliche                                             |

| Ulrich Schwardmann | Datenverarbeitung mbH Göttingen, Germany<br>GWDG - Gesellschaft für wissenschaftliche |

| Unter Serwardmann  | Datenverarbeitung mbH Göttingen, Germany                                              |

| Logistics          |                                                                                       |

| Martina Brücher    | GWDG - Gesellschaft für wissenschaftliche                                             |

|                    | Datenverarbeitung mbH Göttingen, Germany                                              |

| Thomas Otto        | GWDG - Gesellschaft für wissenschaftliche                                             |

|                    | Datenverarbeitung mbH Göttingen, Germany                                              |

#### **Program Committee**

#### **Topic 1: Support Tools and Environments**

#### **Global Chair**

| João M. P. Cardoso                   | University of Porto, Portugal               |

|--------------------------------------|---------------------------------------------|

| <b>Local Chair</b><br>Michael Gerndt | Technical University of Munich, Germany     |

| Chairs                               |                                             |

| Giovanni Agosta                      | Politecnico di Milano, Italy                |

| Mary Hall                            | University of Utah, USA                     |

| Sally McKee                          | Clemson University, USA                     |

| Bernd Mohr                           | Jülich Supercomputing Centre (JSC), Germany |

| Robert Schöne                        | Technische Universität Dresden, Germany     |

| Ana Lucia Varbanescu                 | University of Amsterdam, The Netherlands    |

#### Topic 2: Performance and Power Modeling, Prediction and Evaluation

#### **Global Chair**

| Tan Guangming   | Chinese Academy of Sciences, Institute of Computing<br>Technology, China |

|-----------------|--------------------------------------------------------------------------|

| Local Chair     |                                                                          |

| Andreas Knüpfer | Technische Universität Dresden, Germany                                  |

#### Chairs

| Kaixi Hou    | Virginia Tech, USA                                  |

|--------------|-----------------------------------------------------|

| Jiajia Li    | Pacific Northwest National Laboratory, USA          |

| Eric Liang   | Peking University, China                            |

| Weifeng Liu  | China University of Petroleum, China                |

| Hao Wang     | The Ohio State University, USA                      |

| Junmin Xiao  | Chinese Academy of Sciences, Institute of Computing |

|              | Technology, China                                   |

| Xiaowen Xu   | IAPCM Beijing, China                                |

| Liang Yuan   | Chinese Academy of Sciences, Institute of Computing |

|              | Technology, China                                   |

| Jidong Zhai  | Tsinghua University, China                          |

| Jing Zhang   | Virgina Tech, USA                                   |

| Xiuxia Zhang | Chinese Academy of Sciences, Institute of Computing |

|              | Technology, China                                   |

#### **Topic 3: Scheduling and Load Balancing**

#### **Global Chair**

| Andrei Tchernykh | CICESE Centro de Investigación Científica y de<br>Educación Superior de Ensenada, Mexico |

|------------------|------------------------------------------------------------------------------------------|

|                  | Educación Superior de Enseñada, Mexico                                                   |

#### Local Chair

| Sascha Hunold | Vienna University | of Technology, Austria |

|---------------|-------------------|------------------------|

|               | , renna chirerony | of 1001008,, 1100010   |

#### Chairs

| Zhihui Du             | Tsinghua University, China                         |  |

|-----------------------|----------------------------------------------------|--|

| Fanny Dufossé         | Inria Le Chesnay, France                           |  |

| Matthias Mnich        | Universität Bonn, Germany                          |  |

| Risat Mahmud Pathan   | Chalmers University of Technology, Sweden          |  |

| Krzysztof Rzadca      | University of Warsaw, Poland                       |  |

| Franciszek Seredynski | Cardinal Stefan Wyszyński University in Warsaw,    |  |

| Poland                |                                                    |  |

| Bertrand Simon        | University of Bremen, Germany                      |  |

| Victor V. Toporkov    | National Research University MPEI, Russia          |  |

| Nodari Vakhania       | Universidad Autónoma del Estado de Morelos, Mexico |  |

| Frank Werner          | Otto-von-Guericke-Universität Magdeburg, Germany   |  |

| Prudence W. H. Wong   | University of Liverpool, UK                        |  |

#### **Topic 4: High Performance Architectures and Compilers**

#### **Global Chair**

| Pedro Petersen Moura<br>Trancoso | University of Gothenburg, Sweden        |

|----------------------------------|-----------------------------------------|

| Local Chair                      |                                         |

| Matthias Müller                  | RWTH Aachen, Germany                    |

| Chairs                           |                                         |

| Angelos Arelakis                 | ZeroPoint Technologies AB, Sweden       |

| Alexandra Jimborean              | Uppsala University, Sweden              |

| Nuno Roma                        | Universidade de Lisboa, Portugal        |

| Josef Weidendorfer               | Technical University of Munich, Germany |

|                                  |                                         |

#### Topic 5: Data Management, Analytics and Deep Learning

| Global Chair    |                                                                                     |

|-----------------|-------------------------------------------------------------------------------------|

| Alexandru Iosup | Vrije Universiteit Amsterdam, The Netherlands                                       |

| Local Chair     |                                                                                     |

| Morris Riedel   | Jülich Supercomputing Centre (JSC), Germany<br>and University of Reykjavik, Iceland |

#### Chairs

| Zeynep Akata<br>Jorge Amaya<br>Ira Assent<br>Gabriele Cavallaro<br>Aaron Ding<br>Dmitry Duplyakin<br>Ernir Erlingsson<br>Jens Henrik Goebbert<br>Markus Goetz<br>Jenia Jitsev<br>Volodymyr Kindratenko<br>Kwo-Sen Kuo<br>Bastian Leibe<br>Helmut Neukirchen | University of Amsterdam, The Netherlands<br>Katholieke Universiteit Leuven, Belgium<br>Aarhus University, Denmark<br>Jülich Supercomputing Centre (JSC), Germany<br>Delft University of Technology, The Netherlands<br>University of Utah, USA<br>University of Iceland, Iceland<br>Jülich Supercomputing Centre (JSC), Germany<br>Karlsruhe Institute of Technology (KIT), Germany<br>Jülich Supercomputing Centre (JSC), Germany<br>University of Illinois at Urbana-Champaign, USA<br>Bayesics LLC, USA<br>RWTH Aachen, Germany<br>University of Iceland, Iceland |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rahul Ramachandran                                                                                                                                                                                                                                          | NASA, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Tomas Runarsson                                                                                                                                                                                                                                             | University of Iceland, Iceland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Animesh Trivedi                                                                                                                                                                                                                                             | Vrije Universiteit Amsterdam, The Netherlands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Alexandru Uta                                                                                                                                                                                                                                               | Vrije Universiteit Amsterdam, The Netherlands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ana Lucia Varbanescu                                                                                                                                                                                                                                        | University of Amsterdam, The Netherlands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ~     |     | . •  |  |

|-------|-----|------|--|

| Organ | 172 | tion |  |

| organ | uzu | uon  |  |

| Laurens Versluis | Vrije Universiteit Amsterdam, The Netherlands     |

|------------------|---------------------------------------------------|

| Lin Wang         | Vrije Universiteit Amsterdam, The Netherlands     |

| Xiaoxiang Zhu    | DLR German Aerospace Center, Technical University |

|                  | of Munich, Germany                                |

#### **Topic 6: Cluster and Cloud Computing**

#### **Global Chair**

| Anne-Cećile Orgerie               | CNRS, IRISA Rennes, France |

|-----------------------------------|----------------------------|

| Local Chair<br>Uwe Schwiegelshohn | TU Dortmund, Germany       |

#### Chairs

| Fraunhofer ITWM, Germany                         |

|--------------------------------------------------|

| Äbo Akademi University, Finland                  |

| AGH University of Science and Technology, Poland |

| Universidad Politécnica de Madrid, Spain         |

| The University of Manchester, UK                 |

|                                                  |

#### **Topic 7: Distributed Systems and Algorithms**

| <b>Global Chair</b><br>Dick Epema                                                        | Delft University of Technology, The Netherlands                                                                                                                                                     |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Local Chair</b><br>Franz-Josef Pfreundt                                               | Fraunhofer ITWM, Germany                                                                                                                                                                            |

| <b>Chairs</b><br>Gyorgy Dan<br>Asterios Katsifodimos<br>Stefanie Roos<br>Francois Taiani | KTH Royal Institute of Technology, Sweden<br>Delft University of Technology, The Netherlands<br>Delft University of Technology, The Netherlands<br>University of Rennes, CNRS, Inria, IRISA, France |

#### Topic 8: Parallel and Distributed Programming, Interfaces, and Languages

# Global ChairSato MitsuhisaRIKEN, JapanLocal ChairsChristian SimmendingerT-Systems Stuttgart, GermanyVicen BeltranBarcelona Supercomputing Center (BSC), Spain

xiii

#### Chairs

| Olivier Aumage        | Inria Le Chesnay, France                    |

|-----------------------|---------------------------------------------|

| Marc Gonzalez         | Universitat Politècnica de Catalunya, Spain |

| Changhee Jung         | Virginia Tech, USA                          |

| Karla Morris          | Sandia National Laboratories, USA           |

| Alessandro Pellegrini | Sapienza University of Rome, Italy          |

| Mirko Rahn            | Fraunhofer ITWM, Germany                    |

| Miwako Tsuji          | RIKEN, Japan                                |

| Tom Vander Aa         | Exascience Lab at imec, Belgium             |

| Masahiro Yasugi       | Kyushu Institute of Technology, Japan       |

#### **Topic 9: Multicore and Manycore Parallelism**

#### **Global Chair**

| Barbara Chapman | Stony Brook University, New York, USA |

|-----------------|---------------------------------------|

| Local Chair     |                                       |

Helmholtz-Zentrum Dresden-Rossendorf, Germany

#### Guido Juckeland

#### Juido Juckeland

#### Chairs

| Sridutt Bhalachandra   | Argonne National Laboratory Chicago, USA |

|------------------------|------------------------------------------|

| Sunita Chandrasekaran  | University of Delaware, USA              |

| Rudolf Eigenmann       | University of Delaware, USA              |

| Oscar Hernandez        | Oak Ridge National Laboratory, USA       |

| Konstantinos Krommydas | Intel, USA                               |

| Cheng Wang             | University of Houston, USA               |

| Rengan Xu              | Dell EMC, USA                            |

#### Topic 10: Theory and Algorithms for Parallel Computation and Networking

| Global Chair<br>Frédéric Vivien              | Inria Le Chesnay, France                                                              |

|----------------------------------------------|---------------------------------------------------------------------------------------|

| Local Chair<br>Henning Meyerhenke            | Humboldt-Universität zu Berlin, Germany                                               |

| <b>Chairs</b><br>Kamer Kaya<br>Fanny Pascual | Sabancı University, Turkey<br>Université Pierre et Marie Curie, France                |

| Cynthia Phillips<br>Peter Sanders            | Sandia National Laboratories, USA<br>Karlsruhe Institute of Technology (KIT), Germany |

| <b>Global Chair</b><br>Daniel Kressner | École polytechnique fédérale de Lausanne, Switzerland |

|----------------------------------------|-------------------------------------------------------|

| Local Chair                            | DI D. Common Association Contra Citting on Common     |

| Cornelia Grabe                         | DLR German Aerospace Center Göttingen, Germany        |

| Chair                                  |                                                       |

| Thomas Gerhold                         | DLR German Aerospace Center Göttingen, Germany        |

| Topic 12: Accelerator Comp             | uting                                                 |

| Global Chair                           |                                                       |

| Raphael Y. de Camargo                  | Federal University of ABC, Brazil                     |

| Local Chair                            |                                                       |

| Christian Plessl                       | Paderborn University, Germany                         |

| Chairs                                 |                                                       |

| Pedro Diniz                            | INESC TEC, Portugal                                   |

| Holger Fröning                         | University of Heidelberg, Germany                     |

| Francisco Igual                        | Universidad Complutense de Madrid, Spain              |

| Miriam Leeser                          | Northeastern University, USA                          |

| Andy Nisbet                            | The University of Manchester, UK                      |

| Topic 13: Algorithms and Sy            | stems for Bioinformatics                              |

| Global Chair                           |                                                       |

| Folker Meyer                           | Argonne National Laboratory Chicago, USA              |

| Local Chair                            |                                                       |

| Alexander Sczyrba                      | University of Bielefeld, Germany                      |

| Chairs                                 |                                                       |

| Christophe Blanchet                    | CNRS IFB, France                                      |

| Shane Canon                            | Lawrence Berkeley National Lab, USA                   |

| Rob Finn                               | EMBL-EBI, UK                                          |

| Ananth Grama                           | Purdue University, USA                                |

|                                        |                                                       |

|                                        |                                                       |

#### **Topic 11: Parallel Numerical Methods and Applications**

#### Topic 14: Algorithms and Systems for Digital Humanities

#### **Global Chair**

| Iryna Gurevych                                                              | Technische Universität Darmstadt, Germany                                                                                             |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Local Chair                                                                 |                                                                                                                                       |

| Marco Büchler                                                               | Leibniz Institute of European History Mainz, Germany                                                                                  |

| Chairs                                                                      |                                                                                                                                       |

| Sayeed Choudhury<br>Eckart de Castilho<br>Mark Hedges<br>Andrea Scharnhorst | Johns Hopkins University, USA<br>Technische Universität Darmstadt, Germany<br>King's College London, UK<br>DANS-KNAW, The Netherlands |

#### **Additional Reviewers**

| Tanwir Ahmad             | Tony Curtis            | Sergio Iserte     |

|--------------------------|------------------------|-------------------|

| Artur Andrzejak          | Alberto Antonio Del    | Anshul Jindal     |

| Eugenio Angriman         | Barrio García          | Jophin John       |

| Adnan Ashraf             | Alessandro Di Federico | Vasiliki Kalavri  |

| Nikos Athanasis          | Kostantinos Dogeas     | Sudeep Kanur      |

| Bartosz Balis            | Manuel F. Dolz         | Jeffrey Kelling   |

| Daniel Balouek-Thomert   | Fanny Dufossé          | Marek Klonowski   |

| Md Abdullah Shahneous    | Tim Ehlers             | Oliver Knodel     |

| Bari                     | Pietro Fezzardi        | Dušan Knop        |

| Ayon Basumallik          | Goran Flegar           | Christian Köhler  |

| Sergio Bernabé           | Holger Fröning         | Martin Kong       |

| Anup Bhattacharya        | Tobias Frust           | Jan Kopanski      |

| Akshay Bhosale           | Swapnil Gaikwad        | Daniel Kowalczyk  |

| Marcus Boden             | Jean-François Gibrat   | Roger Kowalewski  |

| Martin Böhm              | Marcos Amarís González | David Kübel       |

| Aurelien Bouteiller      | Alexander Göke         | Thomas Lambert    |

| Lorenz Braun             | Markus Götz            | Sebastian Lamm    |

| Linjin Cai               | Thomas Gruber          | Bo Li             |

| Louis-Claude Canon       | Loic Guegan            | Lingda Li         |

| Paris Carbone            | Amina Guermouche       | Key Liao          |

| Adrián Castelló          | Andrea Gussoni         | Wictor Lund       |

| Márcio Castro            | Peter Györgyi          | Alexander Matz    |

| Imen Chakroun            | Matthias Hauck         | Jan Meizner       |

| Stefano Cherubin         | Byron Hawkins          | Alok Mishra       |

| Franz Christian Heinrich | Roman Iakymchuk        | Clément Mommessin |

| Diego Costa              | Aleksandar Ilic        | Mayuri Morais     |

| Xuewen Cui               | Konstantinos Iordanou  | Grégory Mounié    |

|                          |                        |                   |

xvii

Stefan Mueller Philippe Navaux João Neto Simon Omlor Tim Oosterwijk Marcus Paradies Maciej Pawlik Diego Perdomo Vladimir Podolskiy Laura Promberger Bartlomiej Przybylski Anna Pupykina Issam Raïs Carlos Reaño Mohamad Rezaei Crefeda Rodrigues Javier Rojas Balderrama Paul Saary Amit Sabne Danilo Carastan Santos Günther Schindler Scott Schneider Malte Schwarzkopf Rong Shi Osman Seckin Simsek Sebastian Starke Athanasios Stratikopoulos Lauritz Thamsen Xiaonan Tian Kim-Anh Tran Elena Troubitsyna Denis Trystram Pedro Valero-Lara Alexander van der Grinten Pavel Veselý Roland Vincze Jie Wang Tao Wang Jianwen Wei Minhua Wen Chuan Wu Jeffrey Young Felix Zahn Salah Zrigui Pawel Zuk

### Keynotes

#### Complex Workflows Development in Distributed Computing Infrastructures

Rosa Badia

Workflows and Distributed Computing Group Manager Barcelona Supercomputing Center (BSC) rosa.m.badia@bsc.es

**Abstract.** Distributed computing infrastructures are evolving from traditional models to environments that involve sensors, edge devices, instruments, etc, and, as well, high-end computing systems such as clouds and HPC clusters. A key aspect is how to describe and develop the applications to be executed in such platforms.

Very often these applications are not standalone, but involve a set of sub-applications or steps composing a workflow. The trend in these types of workflows is that the components can be of different nature, combining computationally intensive and data analytics components, for example. The scientists rely on effective environments to describe their workflows and engines and to manage them in complex infrastructures.

COMPSs is a task-based programming model that enables the development of workflows that can be executed in parallel in distributed computing platforms. The workflows that are currently supported may involve different types of tasks, such as parallel simulations (MPI) or analytics (i.e., written in Python thanks to PyCOMPSs, the Python binding for COMPSs). COMPSs, through a storage interface, makes transparent the access to persistent data stored in key-value databases (Hecuba) or object-oriented distributed storage environments (data-Clay).

While COMPSs has been developed from its early times for distributed environments, we have been extending it to deal with more challenging environments, with edge devices and components in the fog, that can appear and disappear. Examples of new features that are considered in these environments are task failure management and input/output data from streams.

The talk will present an overview of the challenges on workflows' development in the mentioned environments and an overview of how it can be tackled with COMPSs.

#### Nanomachines at Work: Atomistic Simulations of Biomolecular Systems

#### Helmut Grubmüller

Director of the Theoretical and Computational Biophysics Group at the Max Planck Institute of Biophysical Chemistry, Göttingen hgrubmu@gwdg.de

**Abstract.** Without highly specialized 'nano machines' - the proteins - no organism would be able to survive. Almost all functions, e.g. photosynthesis for energy production in plants, various forms of movement, signal transmission and information processing, e.g. in the brain, sensor technology, and recognition, are performed by proteins whose perfection was already very advanced two billion years ago and often far exceeds that of our organs, not to mention our current technology.

Atomistic computer simulations of the motion and dynamics of the atoms that make up the proteins, combined with sophisticated experiments, enable a better understanding of the underlying functional mechanisms. We are beginning to realize that, already long ago, evolution 'invented' molecular electric motors, chemical factories, photocells, transformers, accumulators, 'Castor' transporters, and sensors. The lecture gives an overview of the state of the art of atomistic computer simulations, and what we can learn about how proteins are 'manufactured' by ribosomes, how antibiotics interfere with bacterial ribosomes, and how molecular recognition and specific ligand binding works.

We take a more global view on the 'universe' of protein dynamics motion patterns and demonstrate that a systematic coverage of this 'Dynasome' allows one to better predict protein function. Finally, algorithmic challenges concerning GPU implementation and scalability will be discussed.

#### Scientific Applications and Heterogeneous Architectures Data Analytics and the Intersection of HPC and Edge Computing

Michela Taufer and Jack Dongarra

Professor in High Performance Computing Department of Electrical Engineering and Computer Science, The University of Tennessee, Knoxville taufer@utk.edu

Abstract. This talk discusses two emerging trends in computing (i.e., the convergence of data generation and analytics, and the emergence of edge computing) and how these trends can impact heterogeneous applications. Next-generation supercomputers, with their extremely heterogeneous resources and dramatically higher performance than current systems, will generate more data than we need or, even, can handle. At the same time, more and more data is generated at the edge, requiring computing and storage to move closer and closer to data sources. The coordination of data generation and analysis across the spectrum of heterogeneous systems including supercomputers, cloud computing, and edge computing adds additional layers of heterogeneity to applications workflows. More importantly, the coordination can neither rely on manual, centralized approaches as it is predominately done today in HPC nor exclusively be delegated to be just a problem for commercial Clouds. This talk presents case studies of heterogeneous applications in precision medicine and precision farming that expand scientist workflows beyond the supercomputing center and shed our reliance on large-scale simulations exclusively, for the sake of scientific discovery.

#### Contents

#### **Support Tools and Environments**

| Online Fault Classification in HPC Systems Through Machine Learning<br>Alessio Netti, Zeynep Kiziltan, Ozalp Babaoglu, Alina Sîrbu,<br>Andrea Bartolini, and Andrea Borghesi                                   | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Accelerating Data-Dependence Profiling with Static Hints<br>Mohammad Norouzi, Qamar Ilias, Ali Jannesari, and Felix Wolf                                                                                       | 17 |

| Multi-valued Expression Analysis for Collective Checking<br>Pierre Huchant, Emmanuelle Saillard, Denis Barthou,<br>and Patrick Carribault                                                                      | 29 |

| Performance and Power Modeling, Prediction and Evaluation                                                                                                                                                      |    |

| Towards Portable Online Prediction of Network Utilization Using<br>MPI-Level Monitoring<br>Shu-Mei Tseng, Bogdan Nicolae, George Bosilca, Emmanuel Jeannot,<br>Aparna Chandramowlishwaran, and Franck Cappello | 47 |

| A Comparison of Random Task Graph Generation Methods<br>for Scheduling Problems                                                                                                                                | 61 |

| Hardware Counters' Space Reduction for Code Region Characterization<br>Jordi Alcaraz, Anna Sikora, and Eduardo César                                                                                           | 74 |

| Combining Checkpointing and Data Compression to Accelerate<br>Adjoint-Based Optimization Problems<br>Navjot Kukreja, Jan Hückelheim, Mathias Louboutin, Paul Hovland,<br>and Gerard Gorman                     | 87 |

| Scheduling and Load Balancing                                                                                                                                                                                  |    |

| Linear Time Algorithms for Multiple Cluster Scheduling and Multiple                                                                   |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Strip Packing                                                                                                                         | 103 |

| Klaus Jansen and Malin Rau                                                                                                            |     |

| Scheduling on Two Unbounded Resources with Communication Costs<br>Massinissa Ait Aba, Alix Munier Kordon, and Guillaume Pallez (Aupy) | 117 |

| Improving Fairness in a Large Scale HTC System Through Workload         Analysis and Simulation         Frédéric Azevedo, Dalibor Klusáček, and Frédéric Suter                   | 129 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Toggle: Contention-Aware Task Scheduler for Concurrent         Hierarchical Operations         Saurabh Kalikar and Rupesh Nasre                                                  | 142 |

| Load-Balancing for Parallel Delaunay Triangulations<br>Daniel Funke, Peter Sanders, and Vincent Winkler                                                                          | 156 |

| Design-Space Exploration with Multi-Objective Resource-Aware<br>Modulo Scheduling                                                                                                | 170 |

| Implementing YewPar: A Framework for Parallel Tree Search<br>Blair Archibald, Patrick Maier, Robert Stewart, and Phil Trinder                                                    | 184 |

| PLB-HAC: Dynamic Load-Balancing for Heterogeneous<br>Accelerator Clusters<br>Luis Sant'Ana, Daniel Cordeiro, and Raphael Y. de Camargo                                           | 197 |

| Data Management, Analytics and Deep Learning                                                                                                                                     |     |

| Enhancing the Programmability and Performance Portability of GPU<br>Tensor Operations<br>Arya Mazaheri, Johannes Schulte, Matthew W. Moskewicz, Felix Wolf,<br>and Ali Jannesari | 213 |

| Unified and Scalable Incremental Recommenders with Consumed<br>Item Packs                                                                                                        | 227 |

| Declarative Big Data Analysis for High-Energy Physics: TOTEM<br>Use Case                                                                                                         | 241 |

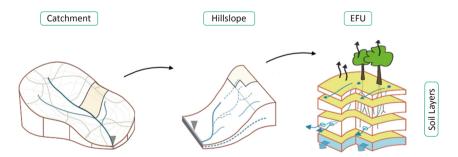

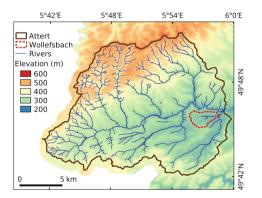

| Clustering as Approximation Method to Optimize<br>Hydrological Simulations<br>Elnaz Azmi, Uwe Ehret, Jörg Meyer, Rik van Pruijssen, Achim Streit,<br>and Marcus Strobl           | 256 |

#### **Cluster and Cloud Computing**

| YOLO: Speeding Up VM and Docker Boot Time by Reducing<br>I/O Operations                                                                                                                                                       |     |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| Parallel and Distributed Programming, Interfaces, and Languages                                                                                                                                                               |     |  |  |  |  |  |

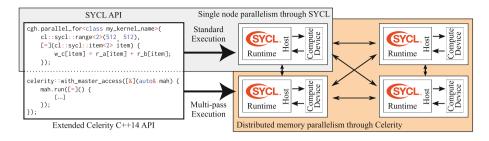

| Celerity: High-Level C++ for Accelerator Clusters<br>Peter Thoman, Philip Salzmann, Biagio Cosenza,<br>and Thomas Fahringer                                                                                                   |     |  |  |  |  |  |

| Dataflow Execution of Hierarchically Tiled Arrays<br>Chih-Chieh Yang, Juan C. Pichel, and David A. Padua                                                                                                                      | 304 |  |  |  |  |  |

| Scalable FIFO Channels for Programming via Communicating<br>Sequential Processes                                                                                                                                              | 317 |  |  |  |  |  |

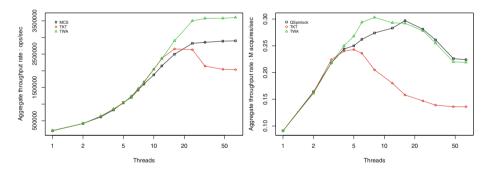

| TWA – Ticket Locks Augmented with a Waiting Array.         Dave Dice and Alex Kogan                                                                                                                                           |     |  |  |  |  |  |

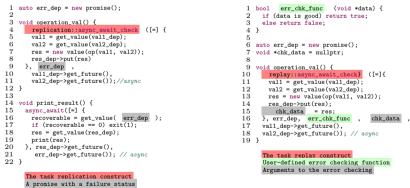

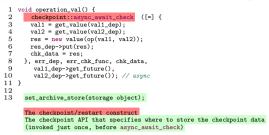

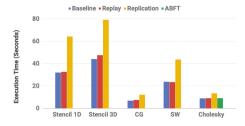

| Enabling Resilience in Asynchronous Many-Task Programming Models<br>Sri Raj Paul, Akihiro Hayashi, Nicole Slattengren, Hemanth Kolla,<br>Matthew Whitlock, Seonmyeong Bak, Keita Teranishi, Jackson Mayo,<br>and Vivek Sarkar | 346 |  |  |  |  |  |

| Multicore and Manycore Parallelism                                                                                                                                                                                            |     |  |  |  |  |  |

| Avoiding Scalability Collapse by Restricting Concurrency<br>Dave Dice and Alex Kogan                                                                                                                                          | 363 |  |  |  |  |  |

| Graph Coloring Using GPUs<br>Meghana Aparna Sistla and V. Krishna Nandivada                                                                                                                                                   | 377 |  |  |  |  |  |

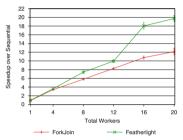

| Featherlight Speculative Task Parallelism                                                                                                                                                                                     | 391 |  |  |  |  |  |

| One Table to Count Them All: Parallel Frequency Estimation<br>on Single-Board Computers<br>Fatih Taşyaran, Kerem Yıldırır, Mustafa Kemal Taş, and Kamer Kaya                                                                  | 405 |  |  |  |  |  |

| Fine-Grained MPI+OpenMP Plasma Simulations: Communication Overlap<br>with Dependent Tasks                                                                                                                                     | 419 |  |  |  |  |  |

xxviii Contents

| Parallel Adaptive Sampling with Almost No Synchronization | 434 |

|-----------------------------------------------------------|-----|

| Alexander van der Grinten, Eugenio Angriman,              |     |

| and Henning Meyerhenke                                    |     |

|                                                           |     |

#### Theory and Algorithms for Parallel Computation and Networking

| Parallel Streaming Random Sampling        |  |  |  |  |

|-------------------------------------------|--|--|--|--|

| Kanat Tangwongsan and Srikanta Tirthapura |  |  |  |  |

#### **Parallel Numerical Methods and Applications**

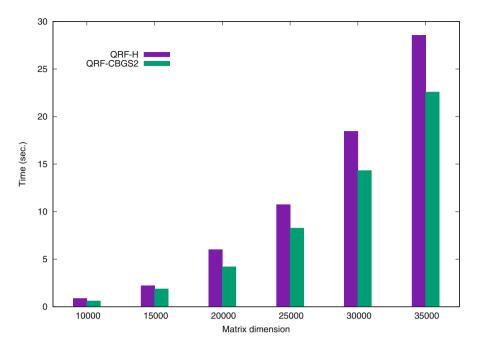

| Cholesky and Gram-Schmidt Orthogonalization for Tall-and-Skinny QR<br>Factorizations on Graphics Processors | 469  |

|-------------------------------------------------------------------------------------------------------------|------|

| Andrés E. Tomás and Enrique S. Quintana-Ortí                                                                |      |

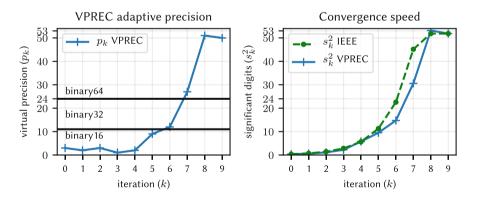

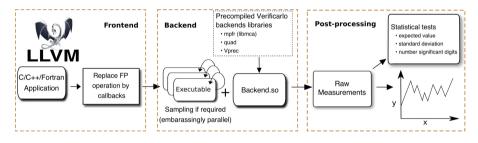

| Automatic Exploration of Reduced Floating-Point Representations                                             | 40.1 |

| in Iterative Methods                                                                                        | 481  |

| Ghislain Lartigue, and David Defour                                                                         |      |

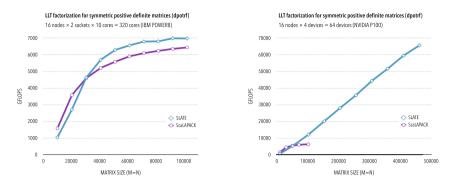

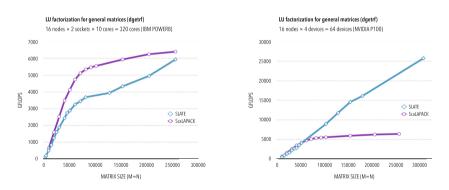

| Linear Systems Solvers for Distributed-Memory Machines                                                      |      |

| with GPU Accelerators                                                                                       | 495  |

| Jakub Kurzak, Mark Gates, Ali Charara, Asim YarKhan,<br>Ichitaro Yamazaki, and Jack Dongarra                |      |

| Accelerator Computing                                                                                       |      |

| Radio-Astronomical Imaging: FPGAs vs GPUs<br>Bram Veenboer and John W. Romein                               | 509  |

| Author Index                                                                                                | 523  |

## **Support Tools and Environments**

#### Online Fault Classification in HPC Systems Through Machine Learning

Alessio Netti<sup>1,2</sup>(⊠), Zeynep Kiziltan<sup>1</sup>, Ozalp Babaoglu<sup>1</sup>, Alina Sîrbu<sup>3</sup>, Andrea Bartolini<sup>4</sup>, and Andrea Borghesi<sup>4</sup>

<sup>1</sup> Department of Computer Science and Engineering, University of Bologna, Bologna, Italy

{alessio.netti,zeynep.kiziltan,ozalp.babaoglu}@unibo.it

<sup>2</sup> Leibniz Supercomputing Centre, Garching bei München, Germany alessio.netti@lrz.de

<sup>3</sup> Department of Computer Science, University of Pisa, Pisa, Italy alina.sirbu@unipi.it

<sup>4</sup> Department of Electrical, Electronic and Information Engineering, University of Bologna, Bologna, Italy

${\tt a.bartolini,andrea.borghesi3} @unibo.it$

Abstract. As *High-Performance Computing* (HPC) systems strive towards the *exascale* goal, studies suggest that they will experience excessive failure rates. For this reason, detecting and classifying faults in HPC systems as they occur and initiating corrective actions before they can transform into failures will be essential for continued operation. In this paper, we propose a fault classification method for HPC systems based on machine learning that has been designed specifically to operate with live streamed data. We cast the problem and its solution within realistic operating constraints of online use. Our results show that almost perfect classification accuracy can be reached for different fault types with low computational overhead and minimal delay. We have based our study on a local dataset, which we make publicly available, that was acquired by injecting faults to an in-house experimental HPC system.

**Keywords:** High-performance computing  $\cdot$  Exascale systems  $\cdot$  Resiliency  $\cdot$  Monitoring  $\cdot$  Fault detection  $\cdot$  Machine learning

#### 1 Introduction

Motivation. Modern scientific discovery is increasingly being driven by computation [18]. As such, HPC systems have become fundamental "instruments" for driving scientific discovery and industrial competitiveness. Exascale  $(10^{18} \text{ oper$  $ations per second})$  is the moonshot for HPC systems and reaching this goal is bound to produce significant advances in science and technology. Future HPC systems will achieve exascale performance through a combination of faster processors and massive parallelism. With Moore's Law reaching its limit, the only

© Springer Nature Switzerland AG 2019

R. Yahyapour (Ed.): Euro-Par 2019, LNCS 11725, pp. 3–16, 2019. https://doi.org/10.1007/978-3-030-29400-7\_1 viable path towards higher performance has to consider switching from increased transistor density towards increased core count, thus leading to increased failure rates [6]. Exascale HPC systems not only will have many more cores, they will also use advanced low-voltage technologies that are more prone to aging effects [4] together with system-level performance and power modulation techniques, all of which tend to increase fault rates [8]. It is estimated that large parallel jobs will encounter a wide range of failures as frequently as once every 30 min on exascale platforms [16]. Consequently, exascale performance, although achieved nominally, cannot be sustained for the duration of applications running for long periods.

In the rest of the paper, we adopt the following terminology. A *fault* is defined as an anomalous behavior at the hardware or software level that can lead to illegal system states (*errors*) and, in the worst case, to service interruptions (*failures*) [10]. Future exascale HPC systems must include automated mechanisms for masking faults, or recovering from them, so that computations can continue with minimal disruptions. This in turn requires detecting and classifying faults as soon as possible since they are the root causes of errors and failures.

*Contributions.* We propose and evaluate a fault classification method based on supervised Machine Learning (ML) suitable for online deployment in HPC systems. Our approach relies on a collection of performance metrics that are readily available in most HPC systems. The experimental results show that our method can classify almost perfectly several types of faults, ranging from hardware malfunctions to software issues and bugs. Furthermore, classification can be achieved with little computational overhead and with minimal delay, thus meeting real time requirements. We characterize the performance of our method in a realistic context similar to online use, where live streamed data is fed to fault classifiers both for training and for detection, dealing with issues such as class imbalance and ambiguous states. Most existing studies, on the contrary, rely on extensive manipulation of data, which is not feasible in online scenarios. Moreover, we reproduce the occurrence of faults basing on real failure traces.

Our evaluation is based on a dataset that we acquired from an experimental HPC system (called Antarex) where we injected faults using FINJ, a tool we previously developed [15]. Making the Antarex dataset publicly available is another contribution of this paper. Acquiring our own dataset for this study was made necessary by the fact that commercial HPC system operators are very reluctant to share trace data containing information about faults in their systems [13].

Related Work. Automated fault detection through system performance metrics and fault injection has been the subject of numerous studies. However, MLbased methods using fine-grained monitored data (i.e., sampling once per second) are more recent. Tuncer et al. [17] propose a framework for the diagnosis of performance anomalies in HPC systems; however, they do not deal with faults that lead to errors and failures, which cause a disruption in the computation, but only with performance anomalies that result in longer runtimes for applications. Moreover, the data used to build the test dataset was not acquired continuously, but rather in small chunks related to single application runs. Thus it is not possible to determine the feasibility of this method when dealing with streamed, continuous data from an online HPC system. A similar work is proposed by Baseman et al. [2], which focuses on identifying faults in HPC systems through temperature sensors. Ferreira et al. [9] analyze the impact of CPU interference on HPC applications by using a kernel-level noise injection framework. Both works deal with specific fault types, and are therefore limited in scope.

Other authors have focused on using coarser-grained data (i.e., sampling once per minute) or on reducing the dimension of collected data, while retaining good detection accuracy. Bodik et al. [5] aggregate monitored data by using fingerprints, which are built from quantiles corresponding to different time epochs. Lan et al. [14] discuss an outlier detection framework based on principal component analysis. Guan et al. [11,12] propose works focused on finding the correlations between performance metrics and fault types through a most relevant principal components method. Wang et al. [19] propose a similar entropy-based outlier detection framework suitable for use in online systems. These frameworks, which are very similar to threshold-based methods, are not suitable for detecting the complex relationships that may exist between different performance metrics under certain faults. One notable work in threshold-based fault detection is the one proposed by Cohen et al. [7], in which probabilistic models are used to estimate threshold values for performance metrics and detect outliers. This approach requires constant human intervention to tune thresholds, and lacks flexibility.

*Organization.* This paper is organized as follows. In Sect. 2, we describe the Antarex dataset, and in Sect. 3, we discuss the features extracted from it. In Sect. 4, we present our experimental results, and we conclude in Sect. 5.

#### 2 The Antarex Dataset

The Antarex dataset contains trace data collected from an HPC system located at ETH Zurich while it was subjected to fault injections. The dataset is publicly available for use by the community and all the details regarding the test environment, as well as the employed applications and faults are extensively documented.<sup>1</sup> Due to space limitations, here we only give a short overview.

#### 2.1 Dataset Overview

In order to acquire data, we executed benchmark applications and at the same time injected faults in a single compute node in the HPC system. The dataset is divided into two parts: the first includes only the CPU and memory-related benchmark applications and fault programs, while the second is strictly hard drive-related. We executed each part in both single-core and multi-core settings, resulting in 4 blocks of nearly 20GB and 32 days of data in total. The dataset's

<sup>&</sup>lt;sup>1</sup> Antarex Dataset: https://zenodo.org/record/2553224.

| Dataset<br>block | Туре       | Parallel | Duration          | Benchmark<br>programs                    | Fault programs                                   |

|------------------|------------|----------|-------------------|------------------------------------------|--------------------------------------------------|

| Block I          | CPU-Mem    | No       | $12\mathrm{days}$ | DGEMM, HPCC,<br>STREAM, HPL <sup>a</sup> | leak, memeater, ddot,<br>dial, cpufreq, pagefail |

| Block III        |            | Yes      |                   |                                          |                                                  |

| Block II         | Hard Drive | No       | 4 days            | IOZone, Bonnie++ <sup>b</sup>            | ioerr, copy                                      |

| Block IV         |            | Yes      |                   |                                          |                                                  |

Table 1. A summary of the structure for the Antarex dataset.

<sup>a</sup>DGEMM: https://lanl.gov/projects/crossroads/, HPCC: https://icl.cs.utk.edu/hpcc/, STREAM: https://www.cs.virginia.edu/stream/, HPL: https://software.intel.com/en-us/articles/intel-mkl-benchmarks-suite

<sup>b</sup>IOZone: https://iozone.org, Bonnie++: https://coker.com.au/bonnie++/

structure is summarized in Table 1. We acquired the data by continuous streaming, thus any study based on it will easily be reproducible on a real HPC system, in an online way.

#### 2.2 Experimental Setup for Data Acquisition

The Antarex compute node used for data acquisition is equipped with two Intel Xeon E5-2630 v3 CPUs, 128 GB of RAM, a Seagate ST1000NM0055-1V4 1TB hard drive and runs the CentOS 7.3 operating system. The node has a default Tier-1 computing system configuration. The FINJ tool [15] was used to execute benchmark applications and to inject faults, in a Python 3.4 environment. To collect performance metrics, we used the Lightweight Distributed Metric Service (LDMS) framework [1]. We configured LDMS to sample a variety of metrics at each second, which come from the meminfo, perfevent, procinterrupts, proceedings, proceedings, proceedings, proceedings, proceedings, and vmstat plugins. This configuration resulted in a total of 2094 metrics collected each second. Some of the metrics are node-level, and describe the status of the node as a whole, others instead are core-specific and describe the status of one of the 16 available CPU cores.

#### 2.3 Features of the Dataset

FINJ orchestrates the execution of benchmark applications and the injection of faults by means of a workload file, which contains a list of benchmark and fault-triggering tasks to be executed at certain times, on certain cores, for certain durations. For this purpose, we used several FINJ-generated workload files, one for each block of the dataset. The details regarding the internal mechanisms driving FINJ are discussed in the associated work by Netti et al. [15].

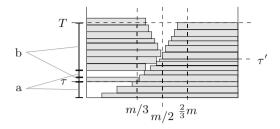

Workload Files. We used two statistical distributions in the FINJ workload generator to create the durations and inter-arrival times of the benchmark and fault-triggering tasks. The benchmark tasks are characterized by duration and inter-arrival times following normal distributions, and 75% of the dataset's duration is spent running benchmarks. Fault-triggering tasks on the other hand are

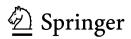

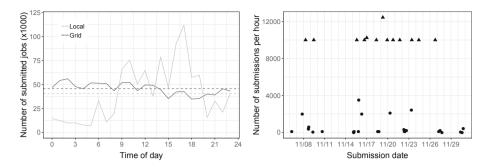

**Fig. 1.** Histograms for fault durations (a) and fault inter-arrival times (b) in the Antarex dataset compared to the PDFs of the Grid5000 data, as fitted on a Johnson SU and Exponentiated Weibull distribution respectively. We define the inter-arrival time as the interval between the start of two consecutive tasks.

modeled using distributions fitted on the Grid5000 host failure trace available on the Failure Trace Archive.<sup>2</sup> In Fig. 1, we show the histograms for the durations (a) and inter-arrival times (b) of the fault tasks in the workload files, together with the original distributions fitted from the Grid5000 data.

FINJ generates each task in the workload by picking randomly the respective application to be executed, from those that are available. This implies that, statistically, all of the benchmark programs we selected will be subject to all of the available fault-triggering programs, given a sufficiently-long workload, with different execution overlaps depending on the starting times and durations of the specific tasks. Such a task distribution greatly mitigates overfitting issues. Finally, we do not allow fault-triggering program executions to overlap.

Benchmark Applications. We used a series of well-known benchmark applications, stressing different parts of the node and providing a diverse environment for fault injection. Since we limit our analysis to a single machine, we use versions of the benchmarks that rely on shared-memory parallelism, for example through the OpenMP library. The benchmark applications are listed in Table 1.

Fault Programs. All the fault programs used to reproduce anomalous conditions on Antarex are available at the FINJ Github repository [15]. As in [17], each program can also operate in a low-intensity mode, thus doubling the number of possible fault conditions. While we do not physically damage hardware, we closely reproduce several reversible hardware issues, such as I/O and memory allocation errors. Some of the fault programs (*ddot* and *dial*) only affect the performance of the CPU core they run on, whereas the other faults affect the entire compute node. The programs and the generated faults are as follows.

<sup>&</sup>lt;sup>2</sup> Failure Trace Archive: http://fta.scem.uws.edu.au/.

- 1. *leak* periodically allocates 16 MB arrays that are never released [17] creating a *memory leak*, causing memory fragmentation and severe system slowdown;

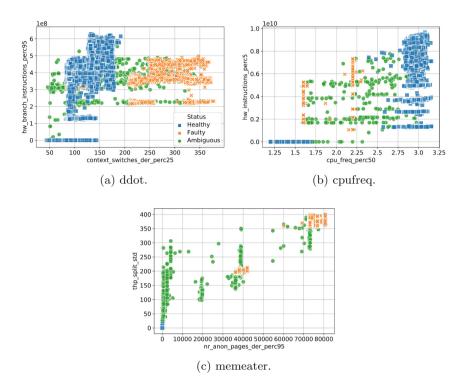

- 2. *memeater* allocates, writes into and expands a 36 MB array [17], decreasing performance through a *memory interference* fault and saturating bandwidth;

- 3. *ddot* repeatedly calculates the dot product between two equal-size matrices. The sizes of the matrices change periodically between 0.9, 5 and 10 times the CPU cache's size [17]. This produces a *CPU and cache interference* fault, resulting in degraded performance of the affected CPU;

- 4. *dial* repeatedly performs floating-point operations over random numbers [17], producing an *ALU interference* fault, resulting in degraded performance for applications running on the same core as the program;

- 5. *cpufreq* decreases the maximum allowed CPU frequency by 50% through the Linux Intel P-State driver.<sup>3</sup> This simulates a *system misconfiguration* or *failing CPU* fault, resulting in degraded performance;

- 6. *pagefail* makes any page allocation request fail with 50% probability.<sup>4</sup> This simulates a *system misconfiguration* or *failing memory* fault, causing performance degradation and stalling of running applications;

- 7. *ioerr* fails one out of 500 hard-drive I/O operations with 20% probability, simulating a *failing hard drive* fault, and causing degraded performance for I/O-bound applications, as well as potential errors;

- 8. copy repeatedly writes and then reads back a 400 MB file from a hard drive. After such a cycle, the program sleeps for 2 s [12]. This simulates an I/O interference or failing hard drive fault by saturating I/O bandwidth, and results in degraded performance for I/O-bound applications.

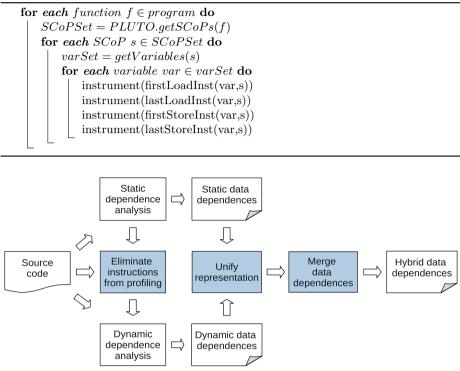

#### 3 Creation of Features

In this section, we explain how a set of features describing the state of the system for classification purposes was obtained from the metrics collected by LDMS.

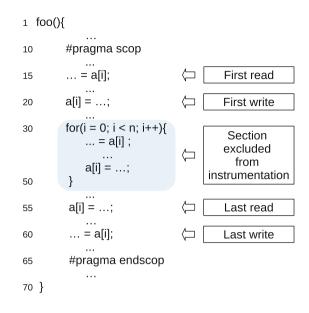

*Post-Processing of Data.* Firstly, we removed all constant metrics (e.g., the amount of total memory in the node), which were redundant, and we replaced the raw monotonic counters captured by the *perfevent* and *procinterrupts* plug-ins with their first-order derivatives. Furthermore, we created an *allocated* metric, both at the CPU core and node level, and integrated it in the original set. This metric has a binary value, and defines whether there is a benchmark allocated on the node or not. Using such a metric is reasonable, since in any HPC system there is always knowledge of which jobs have computational resources currently allocated to them. Lastly, for each metric above, at each time point, we added its first-order derivative to the dataset as proposed by Guan et al. [11].

Feature vectors were then created by aggregating the post-processed LDMS metrics. Each feature vector corresponds to a 60-s aggregation window and is related to a specific CPU core. The step between feature vectors is of 10 s. This

<sup>&</sup>lt;sup>3</sup> Intel P-State Driver: https://kernel.org/doc/Documentation/cpu-freq.

<sup>&</sup>lt;sup>4</sup> Linux Fault Injection: https://kernel.org/doc/Documentation/fault-injection.

allows for high granularity and quick response times to faults. For each metric, we computed several indicators of the distribution of the values measured within the aggregation window [17]. These are the *average*, *standard deviation*, *median*, *minimum*, *maximum*, *skewness*, *kurtosis*, and finally the 5th, 25th, 75th and 95th percentiles. This results in a total of 22 statistical features, including also those related to the first-order derivatives, for each metric in the dataset. The final feature vectors contain thus a total of 3168 elements. This number does not include the metrics collected by the procinterrupts plugin, which were found to be irrelevant after preliminary testing. All the scripts used to process the data are available on the FINJ Github repository [15].

Labeling. In order to train classifiers to distinguish between faulty and normal states, we labeled the feature vectors either according to the fault program (i.e., one of the 8 programs presented in Sect. 2.3) running within the corresponding aggregation window, or "healthy" if no fault was running. The logs produced by the FINJ tool, which are included in the Antarex dataset, detail the fault programs running at each time-stamp. In a generic deployment scenario, if users wish to perform training using data from spontaneous faults in the system, they need to provide the labels explicitly instead of relying on fault injection.

A single aggregation window may capture multiple system states, making labeling not trivial. For example, a feature vector may contain "healthy" time points that are before and after the start of a fault, or even include two different fault types. We define these feature vectors as *ambiguous*. By using a short aggregation window of 60 s, we aim to minimize the impact of such ambiguous system states on fault detection. Since these cannot be completely removed, we experiment with two labelling methods. The first method is *mode*, where all the labels that appear in the time window are considered. Their distribution is examined and the label appearing the most is used for the feature vector. This leads to robust feature vectors, whose label is always representative of the aggregated data. The second method is *recent*, in which the label is given by the state of the system at the most recent time point in the time window. This could correspond to a fault type or could be "healthy". Such an approach may lead to a more responsive fault detection system, where what is detected is the system state at the moment, rather than the state over the last 60 s.

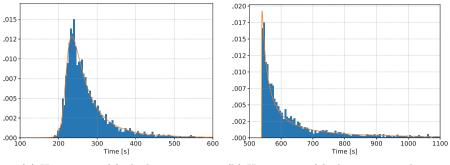

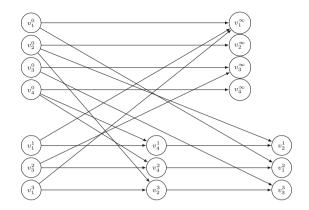

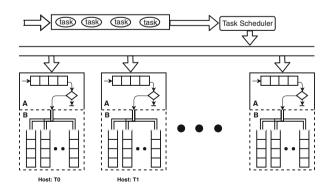

Detection System Architecture. For our fault detection system, we adopted an architecture based on an array of classifiers (Fig. 2). Each classifier corresponds to a specific computing resource type in the node, such as CPU cores, GPUs, MICs, etc. Each classifier is then trained with feature vectors related to all resource units of that type, and is able to perform fault diagnoses for all of them, thus detecting faults both at node level and resource level (e.g., dial and ddot). To achieve this, the feature vectors for each classifier contain all *node-level* metrics for the system, together with *resource-specific* metrics for the resource unit at most, this approach has the benefit of limiting the size of feature vectors, which improves overhead and detection accuracy. This architecture relies on the assumption that resource units of the same type behave in the same way, and

Fig. 2. Architecture of our machine learning-based fault detection system.

that the respective feature vectors can be combined in a coherent set. However, users can also opt to use separate classifiers for each resource unit of the same type, overcoming this limitation, without any alteration to the feature vectors themselves. In our case, the compute node only contains CPU cores. Therefore, we train one classifier with feature vectors that contain both node-level and core-level data, for one core at a time.

The classifiers' training can be performed offline, using labeled data resulting from normal system operation or from fault injection (as in our case). The trained classifiers can then be deployed to detect faults on new, streamed data. Due to this classifier-based architecture, we can only detect one fault at any time. This design assumption is reasonable for us, as the purpose of our study is to distinguish between different fault scenarios automatically. In a real HPC system, although as a rare occurrence, multiple faults may be affecting the same compute node at the same time. In this case, our detection system would only detect the fault whose effects on the system are deemed more relevant by the classifier.

#### 4 Experimental Results

We tested a variety of classifiers, trying to correctly detect which of the 8 faults described in Sect. 2.3 were injected in the HPC node at any point in time of the Antarex dataset. The environment we used was Python 3.4, with the Scikit-learn package. We built the test dataset by picking the feature vector of only one randomly-selected core for each time point. Classifiers were thus trained with data from all cores, and can compute fault diagnoses for any of them.

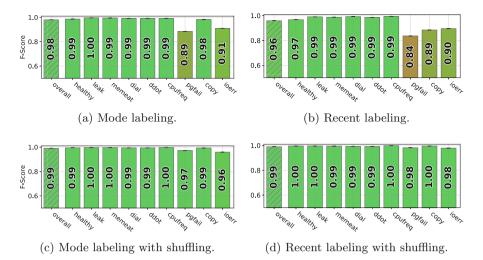

We chose 5-fold cross-validation for evaluation of classifiers, using the average F-score as metric, which corresponds to the harmonic mean between precision and recall. When not specified, feature vectors are read in time-stamp order. In fact, while shuffling is widely used in machine learning as it can improve the quality of training data, such a technique is not well suited to our fault detection framework. Our design is tailored for online systems, where classifiers are trained using only continuous, streamed, and potentially unbalanced data as it is acquired, while ensuring robustness in training so as to detect faults in the

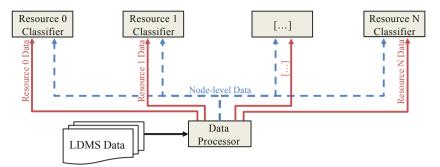

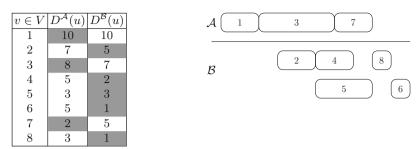

Fig. 3. The classification results on the Antarex dataset, using all feature vectors in time-stamp order, the *mode* labeling method, and different classifiers.