Francky Catthoor · Twan Basten Nikolaos Zompakis · Marc Geilen Per Gunnar Kjeldsberg

# System-Scenariobased Design Principles and Applications

System-Scenario-based Design Principles and Applications

Francky Catthoor • Twan Basten Nikolaos Zompakis • Marc Geilen Per Gunnar Kjeldsberg

# System-Scenario-based Design Principles and Applications

Francky Catthoor IMEC and KU Leuven Leuven, Belgium

Nikolaos Zompakis MicroLab-ECE-NTUA Athens, Greece

Per Gunnar Kjeldsberg Norwegian University of Science and Technology Trondheim, Norway Twan Basten Eindhoven University of Technology and ESI, TNO Eindhoven, The Netherlands

Marc Geilen Eindhoven University of Technology Eindhoven, The Netherlands

### ISBN 978-3-030-20342-9 ISBN 978-3-030-20343-6 (eBook) https://doi.org/10.1007/978-3-030-20343-6

### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG. The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Preface

In the past decades, embedded systems have become much more complex due to the introduction of a substantial amount of conditionally executed functionality in a single application and due to running of several applications or parts of applications concurrently. This substantially increases the dynamic nature of today's applications and systems, and it complicates dealing with their typically tight constraints in terms of, e.g., task deadlines, throughput, and battery lifetime. Also, optimizing for their cost functions like energy consumption and overall fabrication cost is much harder under such dynamic operating conditions. State-of-the-art design methods usually try to cope with these dynamic issues either by taking the corner cases, ending up in the true worst-case design paradigm, or by identifying several most used cases (usecase scenario paradigm) and dealing with them separately. Both of these approaches clearly reduce the complexity introduced by the dynamism, at the cost of adding large margins though.

In contrast, the material in this book encompasses a generic and systematic design-time/run-time methodology for handling the dynamic nature of modern embedded systems without adding such margins. It can be utilized in combination with most existing statically oriented realization methods to effectively deal with dynamism and to drastically increase their performance and efficiency. The presented method is based on the concept of system scenarios, which group system behaviors that are similar from a multidimensional cost perspective, such as resource requirements, delay, and energy consumption. This enables optimization per system scenario. It thus takes a more global cost-oriented system perspective, which is also the main distinction from the abovementioned use-case scenarios. One of the main aims with this book is to disseminate the know-how behind this concept more broadly.

Leuven, Belgium Eindhoven, The Netherlands Athens, Greece Eindhoven, The Netherlands Trondheim, Norway Francky Catthoor Twan Basten Nikolaos Zompakis Marc Geilen Per Gunnar Kjeldsberg

# Contents

| 1 | In                                                  | troduction and Organization of Book Material     | 1                           |    |  |  |

|---|-----------------------------------------------------|--------------------------------------------------|-----------------------------|----|--|--|

|   | Francky Catthoor, Twan Basten, Nikolaos Zompakis,   |                                                  |                             |    |  |  |

|   | Μ                                                   | arc C. W. Geilen, and Per Gunnar Kjeldsberg      |                             |    |  |  |

|   | 1                                                   | Motivation and Context                           | 1                           |    |  |  |

|   | 2                                                   | Contributions of the Book and Target Audience    | 2                           |    |  |  |

|   | 3                                                   | Structure of the Book                            | 3                           |    |  |  |

|   | 4                                                   | Classification                                   | 4                           |    |  |  |

|   | Re                                                  | References                                       |                             |    |  |  |

| 2 | Sy                                                  | stem Scenario Methodology Flow                   | 7                           |    |  |  |

|   | Fr                                                  | Francky Catthoor                                 |                             |    |  |  |

|   | 1                                                   | Introduction and Context                         | 7                           |    |  |  |

|   | 2                                                   | Use-Case Versus System Scenario Concept          | 8                           |    |  |  |

|   | 3                                                   | Motivating Example                               | 10                          |    |  |  |

|   | 4                                                   | Basic Concepts and Terminology                   | 14                          |    |  |  |

|   |                                                     |                                                  | System Scenario Methodology | 20 |  |  |

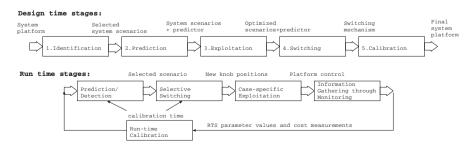

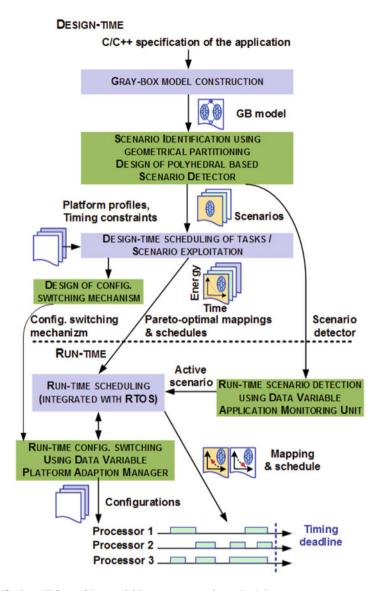

|   |                                                     | 5.1 Methodology Overview                         | 20                          |    |  |  |

|   |                                                     | 5.2 Identification                               | 23                          |    |  |  |

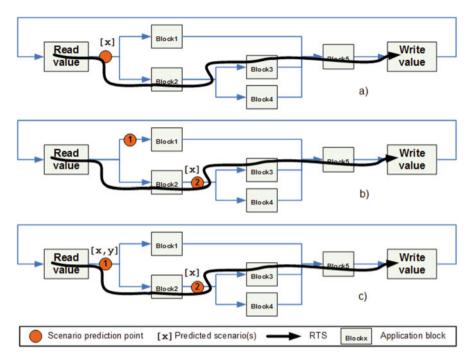

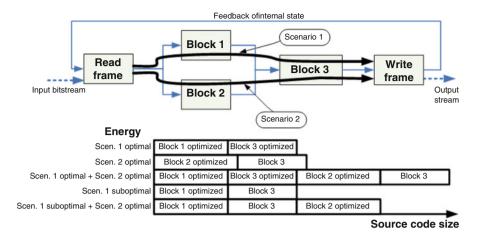

|   |                                                     | 5.3 Prediction                                   | 27                          |    |  |  |

|   |                                                     | 5.4 Exploitation                                 | 31                          |    |  |  |

|   |                                                     | 5.5 Switching                                    | 33                          |    |  |  |

|   |                                                     | 5.6 Calibration                                  | 34                          |    |  |  |

|   | 6                                                   | Case Study Summary                               | 37                          |    |  |  |

|   | 7 Extension to Multi-Tasking and Multi-Threading on |                                                  |                             |    |  |  |

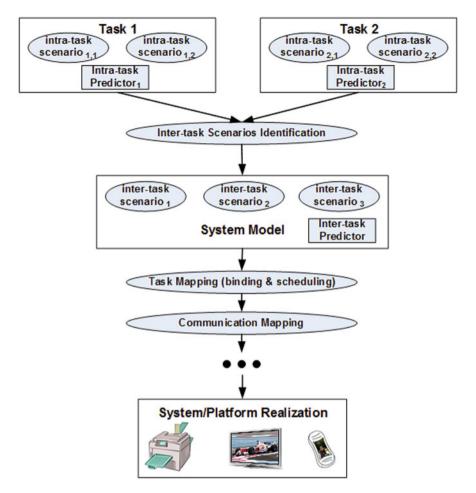

|   |                                                     | Multi-Processor Platforms                        | 42                          |    |  |  |

|   | 8                                                   | Related Work                                     |                             |    |  |  |

|   |                                                     | 8.1 Related Design Approaches                    | 43                          |    |  |  |

|   |                                                     | 8.2 Scenario Exploitation Examples in Literature | 45                          |    |  |  |

|   | 9                                                   | Conclusions                                      | 47                          |    |  |  |

|   | Re                                                  | ferences                                         | 47                          |    |  |  |

|   |                                                     |                                                  |                             |    |  |  |

|   | System-Scenario-based Design Techniques in the Presence |                                                             |  |  |

|---|---------------------------------------------------------|-------------------------------------------------------------|--|--|

|   |                                                         | Variables                                                   |  |  |

|   |                                                         | r, and Per Gunnar Kjeldsberg                                |  |  |

| 1 |                                                         | oduction and Context                                        |  |  |

| 2 |                                                         | nario Identification Through Polyhedral Partitioning        |  |  |

| 2 |                                                         | e Parameter Space                                           |  |  |

|   | 2.1                                                     | Scenario Cost Definition for Use in Polyhedral Partitioning |  |  |

|   | 2.1                                                     | Algorithm for Polyhedral Scenario Identification            |  |  |

|   | 2.2                                                     | Experimental Evaluation of Algorithm for Polyhedral         |  |  |

|   | 2.5                                                     | Scenario Identification                                     |  |  |

| 3 | Scer                                                    | nario Identification Based on Specific Cost Parameters      |  |  |

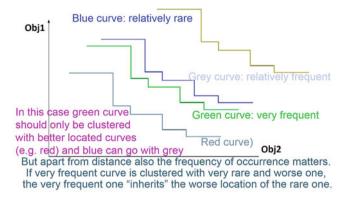

| 5 | 3.1                                                     | RTS Clustering Based on Memory Size and Frequency           |  |  |

|   | 5.1                                                     | of Occurrence                                               |  |  |

|   | 3.2                                                     | Clustering of RTSs Based on Image Size and Set of           |  |  |

|   | 0.2                                                     | Available Platform Configuration Knobs                      |  |  |

| 4 | Scer                                                    | nario Detection                                             |  |  |

|   | 4.1                                                     | Scenario Prediction Using Application Monitoring Unit       |  |  |

|   | 4.2                                                     | Scenario Prediction Through Precomputation                  |  |  |

| 5 | Scer                                                    | nario Switching                                             |  |  |

|   | 5.1                                                     | Scenario Switching Using Platform Adaptation Manager        |  |  |

|   | 5.2                                                     | Switching Gain Evaluation                                   |  |  |

| 6 | Larg                                                    | e-Scale Application Demonstrator                            |  |  |

|   | 6.1                                                     | Application, Platform, and Scenario System Settings         |  |  |

|   | 6.2                                                     | Discussion of Obtained Results                              |  |  |

| 7 | Con                                                     | clusions                                                    |  |  |

| R | eferen                                                  | ces                                                         |  |  |

| р | VFS-c                                                   | oriented Scenario Applications to Processor Architectures   |  |  |

|   |                                                         | s Zombakis, Yahya H. Yassin, Michail Noltsis,               |  |  |

|   |                                                         | os Soudris, Per Gunnar Kjeldsberg, and Francky Catthoor     |  |  |

| 1 |                                                         | ware-Oriented Applications                                  |  |  |

| 2 |                                                         | S-RTH Sleep Mode Extensions                                 |  |  |

|   | 2.1                                                     | Sleep Mode Management.                                      |  |  |

|   | 2.2                                                     | Sleep Mode Experimental Results                             |  |  |

| 3 |                                                         | ability-Sensitive Hardware-Oriented Applications            |  |  |

|   |                                                         | Gas-Pedal Extension                                         |  |  |

|   | 3.1                                                     | Performance Dependability                                   |  |  |

|   | 3.2                                                     | Introducing Gas-Pedal Points                                |  |  |

|   | 3.3                                                     | Choosing the Operating Points                               |  |  |

|   | 3.4                                                     | Case-Study Experiments                                      |  |  |

|   | 3.5                                                     | Hardware-Related Limitations of Our Scheme                  |  |  |

| 4 | Con                                                     | clusions                                                    |  |  |

| R |                                                         | ces                                                         |  |  |

|   |                                                         |                                                             |  |  |

| Contents |

|----------|

|          |

| 5 | DVAFS—Dynamic-Voltage-Accuracy- Frequency-Scaling             |                                                             |     |  |  |

|---|---------------------------------------------------------------|-------------------------------------------------------------|-----|--|--|

|   | Applied to Scalable Convolutional Neural Network acceleration |                                                             |     |  |  |

|   | Bert Moons and Marian Verhelst                                |                                                             |     |  |  |

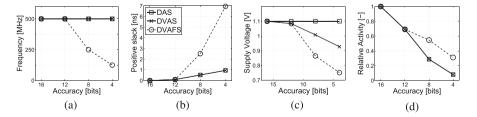

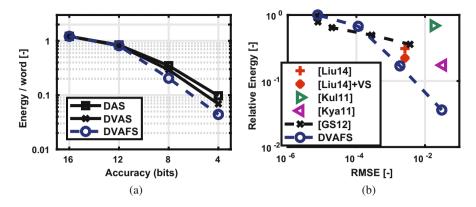

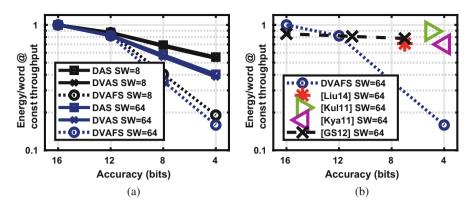

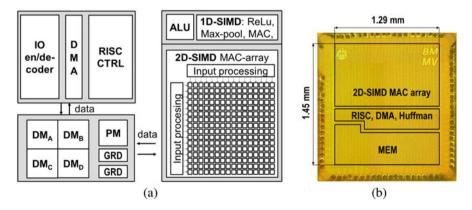

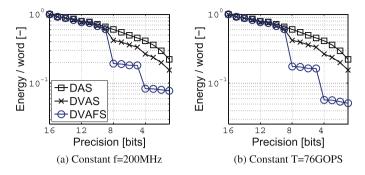

|   | 1                                                             | Exploiting Dynamic Precision Requirements in DVAFS          | 100 |  |  |

|   |                                                               | 1.1 DAS: Dynamic-Accuracy-Scaling                           | 100 |  |  |

|   |                                                               | 1.2 DVAS: Dynamic-Voltage-Accuracy-Scaling                  | 101 |  |  |

|   |                                                               | 1.3 DVAFS: Dynamic-Voltage-Accuracy-Frequency-Scaling       | 102 |  |  |

|   | 2                                                             | DVAFS Performance Analysis                                  | 103 |  |  |

|   |                                                               | 2.1 Performance of a DVAFS Multiplier                       | 103 |  |  |

|   |                                                               | 2.2 Performance of a DVAFS SIMD Processor                   | 104 |  |  |

|   | 3                                                             | A DVAFS Prototype                                           | 106 |  |  |

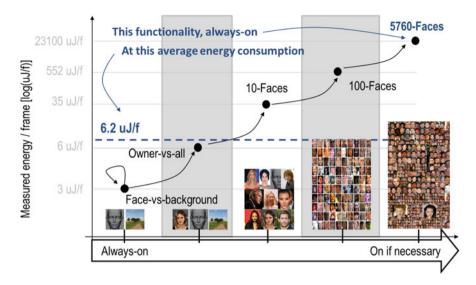

|   |                                                               | 3.1 Envision: A DVAFS-Compatible CNN Processor              | 106 |  |  |

|   |                                                               | 3.2 Envision in a Face Recognition Hierarchy                | 108 |  |  |

|   | 4                                                             | DVAFS Overview                                              | 110 |  |  |

|   | Re                                                            | ferences                                                    | 110 |  |  |

| 6 | P.                                                            | in-Time Exploitation of Application Dynamism                |     |  |  |

| U |                                                               | r Energy-Efficient Exascale Computing                       | 113 |  |  |

|   |                                                               | r Gunnar Kjeldsberg, Robert Schöne, Michael Gerndt, Lubomir | 115 |  |  |

|   |                                                               | ha, Venkatesh Kannan, Kai Diethelm, Marie-Christine Sawley, |     |  |  |

|   |                                                               | n Zapletal, Andreas Gocht, Nico Reissmann, Ondrej Vysocky,  |     |  |  |

|   |                                                               | adhura Kumaraswamy, and Wolfgang E. Nagel                   |     |  |  |

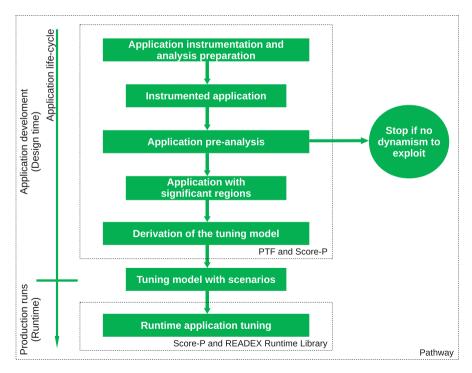

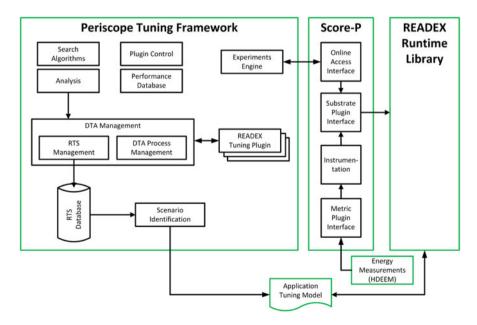

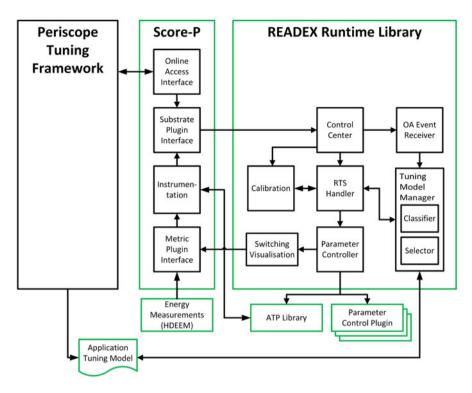

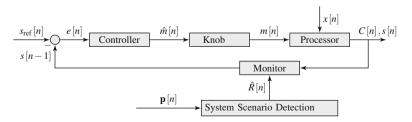

|   | 1                                                             | Introduction and Context                                    | 113 |  |  |

|   | 2                                                             | Auto-tuning of HPC Systems                                  | 115 |  |  |

|   | 3                                                             | The READEX Concept                                          | 117 |  |  |

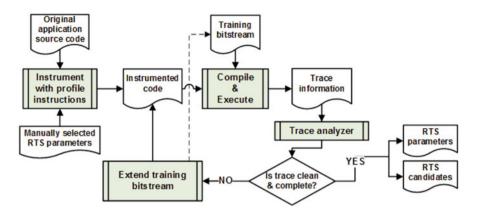

|   | 5                                                             | 3.1 Application Instrumentation and Analysis Preparation    | 117 |  |  |

|   |                                                               | 3.2 Application Pre-analysis                                | 118 |  |  |

|   |                                                               | 3.3 Derivation of the Tuning Model                          | 119 |  |  |

|   |                                                               | 3.4 Run-Time Application Tuning                             | 120 |  |  |

|   | 4                                                             | Experiments                                                 | 120 |  |  |

|   | 5                                                             | Conclusions                                                 | 124 |  |  |

|   | -                                                             | eferences                                                   | 125 |  |  |

|   |                                                               |                                                             |     |  |  |

| 7 |                                                               | stem Scenario Application to Dependable System Design       | 127 |  |  |

|   | Nikolaos Zompakis, Dimitrios Rodopoulos, Michail Noltsis,     |                                                             |     |  |  |

|   | Francky Catthoor, and Dimitrios Soudris                       |                                                             |     |  |  |

|   | 1                                                             | Motivation and Related Work Comparison                      | 127 |  |  |

|   | 2                                                             | A Scenario-Based Performance Dependent Solution             | 129 |  |  |

|   |                                                               | 2.1 Scenario-Based PID Controller                           | 130 |  |  |

|   |                                                               | 2.2 Different Classes of Scenarios                          | 133 |  |  |

|   |                                                               | 2.3 Application of Adaptive System Scenarios                | 134 |  |  |

|   |                                                               | 2.4 Re-clustering Decisions                                 | 136 |  |  |

| Analysis<br>Analysis<br>Alow Modeling and Analysis<br>Maden Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>Jossens | 138<br>139<br>141<br>142<br>143<br>143<br>145 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| esults<br>ade-Offs<br>flow Modeling and Analysis                                                                                            | 141<br>142<br>143<br>143                      |

| ade-Offs<br>flow Modeling and Analysis                                                                                                      | 142<br>143<br>143                             |

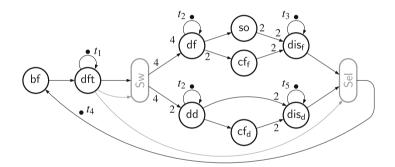

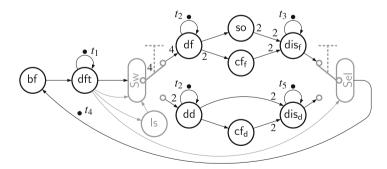

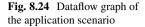

| flow Modeling and Analysis<br>, Mladen Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>ossens                       | 143<br>143                                    |

| flow Modeling and Analysis<br>, Mladen Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>ossens                       | 143                                           |

| flow Modeling and Analysis<br>, Mladen Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>ossens                       | _                                             |

| , Mladen Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>ossens                                                     | 145                                           |

| , Mladen Skelin, J. Reinier van Kampenhout,<br>a, Twan Basten, Sander Stuijk,<br>ossens                                                     |                                               |

| ossens                                                                                                                                      |                                               |

|                                                                                                                                             |                                               |

|                                                                                                                                             |                                               |

|                                                                                                                                             | 145                                           |

|                                                                                                                                             | 149                                           |

| o the Scenario Methodology                                                                                                                  | 149                                           |

| on and Refinement in Timed Dataflow                                                                                                         | 151                                           |

| Analysis of Scenario-Aware Dataflow                                                                                                         | 152                                           |

| ario-Aware Dataflow Model                                                                                                                   | 152                                           |

| ntics of Scenario-Aware Dataflow                                                                                                            | 154                                           |

| nce Analysis of Scenario-Aware Dataflow                                                                                                     | 159                                           |

| Switched Max-Plus Linear Systems                                                                                                            | 163                                           |

|                                                                                                                                             | 166                                           |

| g Model for SADF                                                                                                                            | 170                                           |

|                                                                                                                                             | 170                                           |

| Analysis                                                                                                                                    | 172                                           |

|                                                                                                                                             | 172                                           |

|                                                                                                                                             | 174                                           |

|                                                                                                                                             | 174                                           |

|                                                                                                                                             | 177                                           |

|                                                                                                                                             | 177                                           |

|                                                                                                                                             | 181                                           |

|                                                                                                                                             |                                               |

|                                                                                                                                             |                                               |

|                                                                                                                                             |                                               |

|                                                                                                                                             | 181                                           |

|                                                                                                                                             | 183                                           |

|                                                                                                                                             | 185                                           |

|                                                                                                                                             | 186                                           |

|                                                                                                                                             | 187                                           |

|                                                                                                                                             | 191                                           |

|                                                                                                                                             | 196                                           |

|                                                                                                                                             | 200                                           |

|                                                                                                                                             | 202                                           |

|                                                                                                                                             | 202                                           |

| ut and Makespan Optimization                                                                                                                | 206                                           |

|                                                                                                                                             | ataflow Modeling                              |

### Contents

|       | 5.3    | Code Generation                             | 210 |

|-------|--------|---------------------------------------------|-----|

| 6     | Scer   | nario-Based Data-Intensive Feedback Control | 211 |

|       | 6.1    | Image-Based Control                         | 212 |

|       | 6.2    | Scenario Identification and Exploitation    | 214 |

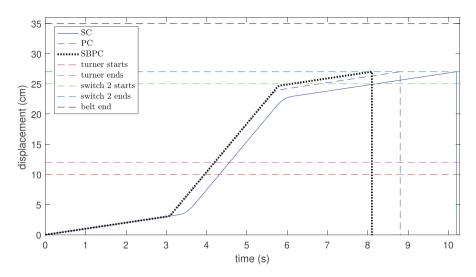

|       | 6.3    | Scenario-Based Pipelined Control (SBPC)     | 218 |

| 7     | Con    | clusions                                    | 221 |

| Re    | eferen | ces                                         | 222 |

|       |        |                                             |     |

| Index |        |                                             | 225 |

# **Chapter 1 Introduction and Organization of Book Material**

Francky Catthoor, Twan Basten, Nikolaos Zompakis, Marc C. W. Geilen, and Per Gunnar Kjeldsberg

# 1 Motivation and Context

In the past decades, embedded systems have become much more complex due to introducing a substantial amount of conditionally executed functionality in a single application, and due to running several applications or parts of applications concurrently. This substantially increases the dynamic nature of today's applications and systems, and it complicates dealing with their typically tight constraints in terms of, e.g., task deadlines, throughput, and battery lifetime. Also optimizing for their cost functions like energy consumption and overall fabrication cost is much harder under such dynamic operating conditions.

T. Basten Eindhoven University of Technology and ESI, TNO, Eindhoven, The Netherlands e-mail: a.a.basten@tue.nl

N. Zompakis MicroLab-ECE-NTUA, Athens, Greece e-mail: nzompakis@microlab.ntua.gr

M. C. W. Geilen Eindhoven University of Technology, Eindhoven, The Netherlands e-mail: m.c.w.geilen@tue.nl

P. G. Kjeldsberg Norwegian University of Science and Technology, NTNU, Trondheim, Norway e-mail: pgk@ntnu.no

© Springer Nature Switzerland AG 2020 F. Catthoor et al. (eds.), *System-Scenario-based Design Principles* and Applications, https://doi.org/10.1007/978-3-030-20343-6\_1

F. Catthoor (🖂)

IMEC and KU Leuven, Leuven, Belgium e-mail: catthoor@imec.be

State-of-the-art design methods usually try to cope with these dynamic issues either by taking the corner cases, ending up in the true worst-case design paradigm; or by identifying several most used cases (use-case scenario paradigm) and dealing with them separately. Both of these approaches clearly reduce the complexity introduced by the dynamism, at the cost of adding large margins though. In contrast, the material in this book encompasses a generic and systematic design-time/runtime methodology for handling the dynamic nature of modern embedded systems without adding such margins. It can be utilized in combination with most existing statically oriented realization methods to effectively deal with dynamism and to drastically increase their performance and efficiency. The presented method is based on the concept of system scenarios, which group system behaviors that are similar from a multi-dimensional cost perspective, such as resource requirements, delay, energy consumption. This enables optimization per system scenario. It thus takes a more global cost-oriented system perspective, which is also the main distinction from the abovementioned use-case scenarios. One of the main aims with this book is to disseminate the know-how behind this concept more broadly.

At design-time, these system scenarios are identified and then individually optimized, typically in a parameterized way. Mechanisms for predicting and detecting the current scenario at run-time and for switching between scenarios at the most appropriate time slots are incorporated. This design trajectory is augmented with a run-time calibration mechanism, which allows the system to learn on-the-fly during its execution, and to adapt itself to the current input stimuli. This happens by extending the scenario set and/or changing the scenario definitions, and it affects both the prediction and switching mechanisms.

To show the generality of the system scenario methodology, we show how it has been effectively applied on many very different real-life design problems in the embedded system context. In all presented case studies substantial cost improvements (e.g., energy reductions) were obtained by exploiting system scenarios. These include several aspects of application to processor architecture mapping, e.g., based on the popular DVFS control knobs, scenario-aware data flow analysis, dependable system design, wireless baseband and protocol system design, biomedical systems like neuroprobes, manufacturing systems, and even dynamic memory management protocols, and photovoltaic system modeling and design.

# 2 Contributions of the Book and Target Audience

As mentioned, state-of-the-art design methods usually try to cope with the dynamic system issues in two basic ways: with worst-case corner cases or through use-case scenarios. Both of these approaches clearly alleviate part of the complexity problem, but they come at the cost of adding large safety margins in the design. In contrast, the system scenario approach discussed in this book avoids this.

The initial system scenario approach methodology was disclosed in [3]. The formalized methodology has been presented in [1] and then generalized further for

the control variable case in [2]. But since then, additional material has been provided and the approach has been extended beyond control variables, and beyond the initial application domains. Hence, we believe this book is a valuable way to provide a systematic and complete view of the approach. For the reader, we offer:

- an effective solution to deal with dynamic system design;

- a broad survey of the state-of-the-art approaches and results in this domain;

- a large set of illustrative industrial-strength case studies covering a broad set of applications, substantiating the effectiveness and wide applicability of the approach.

# **3** Structure of the Book

The rest of this book is organized as follows: First, the overall flow is outlined and the different steps of the approach are summarized, including related work discussion in Chap. 2. The method is illustrated there also using control variable

Fig. 1.1 Dependencies between book chapters

oriented techniques for system design optimization. Next, the extension to data variable oriented techniques is presented in Chap. 3. The following chapters provide case studies and demonstrations of the techniques in different application and system platform contexts. This includes application to processor architecture mapping in Chap. 4; to machine learning in Chap. 5; to HPC server systems in Chap. 6; to dependable system design in Chap. 7; to data flow analysis in Chap. 8; to manufacturing system design in Chap. 9. Remaining case studies are reviewed at the end of Chap. 2.

Figure 1.1 shows the main dependencies between these chapters. The initial chapters are required for a good understanding of the application in different domains. The control variable approach is mainly useful for the application domains mentioned in the left-hand side column of the big box, and the data variable variant is mainly needed in the right-hand side column.

# 4 Classification

**Categories and Subject Descriptors** [Computer Systems Organization]: Special-Purpose and Application-Based Systems|Real-time and embedded systems; [Software Engineering]: Design|Methodologies General Terms: Algorithms, Design, Performance.

Additional Key Words and Phrases Design methodology, dynamic nature, embedded systems, cost and energy reduction, real-time systems, scenario-based design.

Acknowledgements The material in this book is partly based on work in the context of several European and national research projects. In particular we want to acknowledge the support of: the EU Marie Curie project DACMA MEST-CT-2004-504767 and the Artist and HiPEAC Networks of Excellence; the EU FP7 project HARPA with grant number 612069; the EU Horizon 2020 project READEX with grant number 671657; the Flemish FWO (Fonds Wetenschappelijk Onderzoek Vlaanderen); the Netherlands Organisation for Scientific Research (NWO), through the FAME-612.064.101 project and through the Robust Cyber-Physical Systems (RCPS) program, projects 12694 and 12697; the ARTEMIS joint undertaking through the ALMARVI project (621439) and ITEA3 project 14014 ASSUME.

It has been a pleasure for us to work in this research domain and to cooperate with our project partners and our colleagues in the digital processor architecture design and embedded systems communities. Much of this work has been performed in tight cooperation with many university groups, mainly across Europe. In addition to learning many new things about system synthesis/compilation and related issues, we have also developed close connections with excellent people. Moreover, the pan-European aspect of this cooperation has allowed us to come in closer contact with research groups with a different background and "research culture," which has led to very enriching cross-fertilization. This is especially reflected in the many common publications. We want to especially acknowledge the valuable interactions and the excellent cooperation with the colleagues of the TU Eindhoven (The Netherlands); the El. Eng. Dep. of U. Ghent and the K. U. Leuven (Belgium); the ICCS department at the NTUAthens (Greece); the El. Eng. Dep. at the NTNU Trondheim (Norway).

We would like to use this opportunity to thank the many people who have directly helped us in realizing these results and who have provided technical and other contributions in the focus of this book, both at our institutes and at other locations. That includes all the students who helped us during the PhD. and M.S. thesis research.

# References

- S.V. Gheorghita, Dealing with dynamism in embedded system design: application scenarios, Ph.D. thesis, Eindhoven University of Technology, 2007. https://doi.org/10.6100/IR630369

- S.V. Gheorghita, M. Palkovic, J. Hamers, A. Vandecappelle, S. Mamagkakis, T. Basten, L. Eeckhout, H. Corporaal, F. Catthoor, F. Vandeputte, K. De Bosschere, System-scenario-based design of dynamic embedded systems, in *ACM Transactions on Design Automation of Electronic Systems (TODAES)*, vol. 14 (ACM New York, 2009)

- 3. P. Marchal, C. Wong, A. Prayati, N. Cossement, F. Catthoor, R. Lauwereins, D. Verkest, H. De Man, Dynamic memory oriented transformations in the MPEG4 IM1-player on a low power platform, in *Proceedings of the First International Workshop on Power-Aware Computer Systems* (Cambridge MA, 2000), pp. 31–40

# Chapter 2 System Scenario Methodology Flow

**Francky Catthoor**

# 1 Introduction and Context

The main focus of this book is on embedded system realization, even though the extension to high-performance computing (HPC) systems is partly addressed in Chap. 4. Embedded systems usually consist of processors that execute domainspecific applications. These systems are typically very software-intensive [37], having much of their functionality implemented in application and middleware software, which is running on one or multiple/many processors. As a result only the (too) high-performance kernels are left to more custom hardware implementation. Typical examples include cellular phones, wireless access points/gateways, multimedia applications like TV sets or MP3 players, automotive in-car systems, IoT sensor nodes, and body area networks (BANs).

All of these systems have complex workloads and stimuli sequences applied. Thus, these applications are full of dynamism, i.e., their execution costs (e.g., number of processor cycles, memory usage, energy) are strongly environmentdependent (e.g., input data, processor temperature). At the same time, many of these systems are running multimedia and/or communication applications and support multiple standards. And also for emerging domains like BAN systems, standards

F. Catthoor (🖂)

© Springer Nature Switzerland AG 2020

F. Catthoor et al. (eds.), System-Scenario-based Design Principles and Applications, https://doi.org/10.1007/978-3-030-20343-6\_2

Francky Catthoor (editor) based on material provided by Twan Basten, Valentin Gheorghita, Per Gunnar Kjeldsberg, Henk Corporaal, Elena Hammari, Yahya Yassin, Martin Palkovic, Juan Hamers, Arnaut Vandecappelle, Stelios Mamagkakis, Lieven Eeckhout, Frederik Vandeputte, and Koen De Bosschere.

IMEC and KU Leuven, Leuven, Belgium e-mail: catthoor@imec.be

are gradually set up to govern part of the functionality. So still, a large part of their behavior is predefined and it can be characterized quite well at design-time by profiling frameworks.

The rest of this chapter is organized as follows. Section 2 shows the distinction between more conventional use-case versus the system scenario concept which is our focus here. Next, Sect. 3 gives a motivating example for our research objectives, by showing how system scenario exploitation makes an H.264 video decoder significantly more energy efficient. In Sect. 4, the basic concepts and terminology behind the system scenario methodology are described. The overall system scenario methodology for embedded system design is introduced in Sect. 5. The detailed discussion of the main steps follows in Sects. 5.2, 5.3, 5.4, 5.5, and 5.6. In the rest of the book, multiple case studies are incorporated which describe a diversity of applications that fit within this methodology, illustrating its broad application potential. A brief summary of this wide range of applicability is provided in Sect. 6. However, in order to have an illustration of the main steps of the approach also in this chapter, a running case study based on control variable system scenarios is integrated here already in the above sections describing the main steps. The extension to multi-processor platforms and multi-tasking is briefly covered in Sect. 7. The most closely related work is presented in Sect. 8, and the conclusions and our future plans are detailed in Sect. 9.

# 2 Use-Case Versus System Scenario Concept

Scenario-based design [6] has been used for some time already in both hardware [38, 52] and software design [14] of embedded systems. In both of these cases, scenarios concretely describe the use of a future system, in an early phase of the development process. They appear like narrative descriptions of envisioned usage episodes, or unified modeling language (UML) use-case diagrams [23] which enumerate, from a functional and timing point of view, all possible user actions and the system reactions that are required to meet a proposed system function. In this book, this class of scenarios will be called use-case scenarios. They focus on the application functional and timing behaviors and on their interaction with the users and environment. In contrast to the objectives envisioned here, they abstract away or ignore the resources required by a system to meet its specifications and boundary constraints. Hence, these use-case scenarios are mostly usable as an input for design approaches centered around the application context.

In this chapter, we concentrate on a different and complementary type of scenarios, which we call system scenarios. These are derived from the combination of the behavior of the application and its mapping on the system platform. These scenarios are used to reduce the system cost by exploiting information about what can happen at run-time to make better design decisions at design-time, and to exploit the time-varying behavior at run-time. While use-case scenarios classify the application's behavior based on the different ways it can be used, system scenarios

instead classify the behavior based on the multi-dimensional cost trade-offs during the system mapping and implementation trajectory.

By optimizing the system per scenario and by making sure that the actual system scenario can be predicted at run-time, a system setting can be derived per scenario to optimally exploit the system scenario knowledge. To motivate the system scenario usage in embedded system design, we start from the different runtime situations (RTSs) in which a system may run. An RTS is a bounded part of the system execution that can be treated as an integral unit. Each RTS has an associated mapping cost, which usually consists of one or several primary costs, like quality and resource usage (e.g., number of processor cycles, memory size). The system execution is a sequence of RTSs, and the current RTS is known only at the moment it occurs. However, at run-time, using various system parameters, socalled RTS parameters, it can be predicted in advance in which RTS the system will run next for a non-zero future time window. If the information about all possible RTSs in which a system may run is known at design-time, and the RTSs are considered in different steps of the embedded system design, a better optimized (e.g., faster or more energy efficient) system can be built because specific and aggressive design decisions can be made for each RTS. These intermediate per-RTS optimizations lead to a smaller, cheaper, and more energy-efficient system that can deliver the required quality. In general, any combination of N cost dimensions may be targeted. However, the number of cost dimensions and all possible values of the considered RTS parameters may lead to an exponential growth in the number of RTSs.

This will degenerate to a long and overly complicated design process that does not deliver the optimal system at all. Moreover, the run-time overhead of detecting all these different RTSs will be too high compared to the expected gain over their (quite) short time windows. To avoid this situation, in our work, the RTSs are classified and clustered from an *N*-dimensional cost perspective, into system scenarios, such that the cost trade-off combinations within a scenario are always fairly similar, the RTS parameter values allow an accurate prediction, and a system setting can be defined that allows to exploit the scenario knowledge and optimizations. This chapter presents a systematic way of detecting and exploiting both at design-time and run-time the system scenarios of a given system setup. Generic solutions to the various steps in the methodology are provided whenever possible. The method combines design-time analyses and optimizations with information collected at runtime about the environment in which the system is operating and the inputs being received.

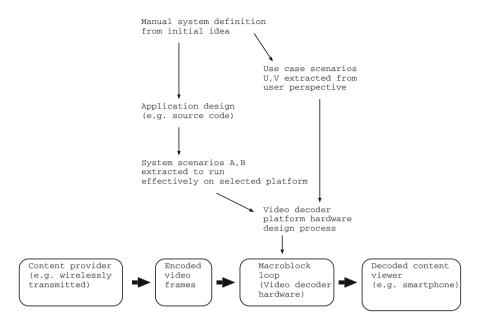

Figure 2.1 depicts a design trajectory using use-case and system scenarios. It starts from a product idea, for which the stake-holders manually define the product's functionality as use-case scenarios. The stakeholders are persons, entities, or organizations who have a direct stake in the final system; they can be owners, regulators, developers, users, or maintainers of the system. These scenarios characterize the system from a user perspective and are used as an input to the design of an embedded system. The latter will typically include both software and platform

Fig. 2.1 Use-case vs system-scenario-based design flows for embedded systems

hardware components. In order to optimize the design of the system, the detection and usage of system scenarios augments this trajectory, as shown in the bottom gray box in the figure. The run-time behavior of the system is classified using the proposed methodology into several system scenarios, with similar cost tradeoffs within each individual scenario. For each specific scenario, more customized and aggressive design decisions can be made than what is feasible for the global functional behavior. The sets of use-case scenarios and system scenarios are not necessarily fully disjoint, and it is possible that one or more use-case scenarios correspond to one system scenario. But still, usually they are not overlapping and it is more likely that a given use-case scenario is split into several system scenarios, or even that many system scenarios intersect several use-case scenarios.

# **3** Motivating Example

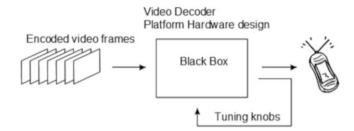

Figure 2.2 shows a typical system to which the system scenario design methodology is applicable. In this system, a content provider sends H.264 encoded sequences of video frames to a mobile device that decodes the content. The video decoder is often implemented as a main loop which is executed repeatedly, reading encoded frames, decoding them, and writing them to an output device (e.g., a screen). The application has to deliver a prespecified throughput (e.g., 25 or 30 frames per second), which imposes a time constraint on each loop iteration. Otherwise, the movie will stutter

Fig. 2.2 Motivating example, no use of scenarios

and the user's experience, i.e., the QoS, will degrade. When this kind of video decoder is implemented in a mobile device that is battery-operated and thus energyconstrained, the goal of using system scenarios during the design is to reduce the energy consumption. That has to happen while retaining an acceptable QoS, including the frame rate. While every frame must be decoded within a fixed period of time, the actual time and energy needed to decode a frame on a processor with a given speed will vary significantly due to the dynamism exhibited by the application. Some frames require all the available decoding time while others demand only a fraction and leave the processor idle for the remaining time. On a small set of video sequences, we already noticed differences up to 450% in the required energy for decoding a single frame.

One well-known approach for reducing energy consumption in this situation (fixed deadline, varying decode time) is the dynamic voltage and frequency scaling (DVFS) technique [39]. When scaling the voltage, the processor's frequency and therefore the execution time scales linearly  $(f_{CLK} - V_{DD})$ , while the energy consumption scales approximately quadratically  $(E - V_{DD}^2)$ . As such, DVFS gives the system an effective configuration knob, namely a choice to work at a certain frequency/voltage. That knob needs to be tuned at run-time. An important issue when applying DVFS in this situation is the need of knowing how many cycles (the cycle budget) are needed for decoding a frame, before actually decoding it. This is necessary to choose the appropriate scaling factor, i.e., to choose in which position to turn the DVFS system knob.

Existing DVFS systems work either fully dynamically based on run-time information or fully statically based on design-time analysis. More information and related work on this will be provided in Chap. 5. In the fully dynamic approach, no information about the decoder is considered except the notion of consecutive frames with different decode times that need to be decoded within a given deadline (Fig. 2.2). Without any information on how the internals of the decoder cause this variation in decode time, it is only possible to predict at run-time the required cycle budget of the current frame based upon the cycle budget needed for previously decoded frames [8, 36]. Another fully static approach considers complete information about the program at design-time and uses static analysis to determine the remaining worst-case cycle budget needed to complete execution at several

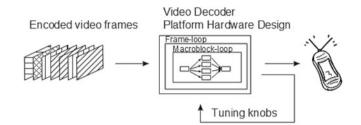

Fig. 2.3 Motivating example, system scenarios

Fig. 2.4 Gray-box model of the H.264/AVC decoder processing a stream object

points in the execution and fixes the DVFS system to the corresponding voltage and frequency [62].

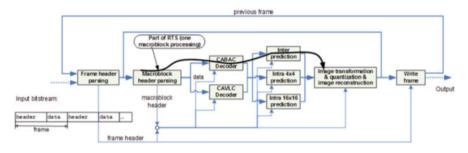

When using our proposed system scenarios (Fig. 2.3), we consider both information about the system at design-time and the occurrence of certain types of input at run-time, which result in particular (groupings of) RTSs. Looking at the general structure of the H.264 decoder (Fig. 2.4), we see that each frame is subdivided into blocks of 16 by 16 pixels, called macro-blocks. The main loop, which is the frame decoding loop, contains a second loop that iterates over the consecutive macroblocks. The read part of this loop takes an encoded macro-block object from the input stream and separates it into a header and the object's data. The write part places the decoded macro-block in the frame. The decoding part consists of several kernels. Each macro-block can be encoded using a different encoding scheme determining which kernels are used. Depending on the exact breakup of how many macro-blocks of each frame belong to each scheme for a given iteration of the main frame loop, each of these kernels is executed for a certain number of times. This forms the runtime situation (RTS) which can be characterized by the current RTS parameters, i.e., the macro-block breakup in this example. These parameters can be used to predict in advance the multi-objective cost dimensions associated with the current RTS.

However, considering each possible breakup of a frame for tuning the system at run-time would cause a too large run-time storage and execution overhead. When decoding CIF images (352 by 288 pixels), consisting of 396 macro-blocks that may belong to 21 different encoding schemes, up to  $6.22 \times 10^{33}$  possible RTSs

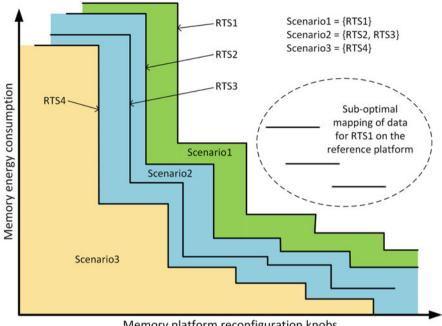

would need to be considered, and for each RTS the receiver has to store the optimal frequency/voltage. This is clearly impossible for any practical system realization. Therefore, it is instead necessary to cluster frames with a similar breakup of macroblock types over the encoding schemes and mapping on the target platform. So frames that need similar cycle budgets can be safely merged into the same system scenario. For each system scenario, we then determine the optimal knob setting of the mapping scheme and the platform. For example, we can determine the frequency/voltage setting of the DVFS scheme by using the cycle budget needed for a single (worst-case) representative frame as the budget needed for all possible frames belonging to this scenario. The above has to be generalized for the multi-objective cost spaces which we typically have to deal with and that is feasible by using Pareto curve trade-off concepts [51].

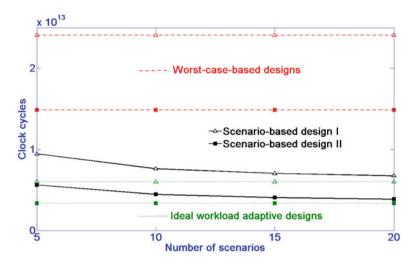

At run-time, whenever a client receives a video stream from a content provider, it predicts for each frame the scenario it belongs to. Then, it scales the voltage and frequency according to the values determined and stored at design-time, thereby reducing the energy consumption while still safely meeting the deadlines. Clearly, the more scenarios are considered, the higher the energy reduction that can be obtained, but also the higher the complexity and overhead of the prediction step. The prediction causes run-time overhead and it will, e.g., add to the energy usage. The cost and gain of extra scenarios have to be traded off carefully to arrive at an optimal system realization.

Another interesting issue is to what extent scenario prediction can be made or needs to be made conservative in order to meet hard parametric constraints, e.g., on timing. For complexity reasons, it will clearly not be possible to consider all possible RTSs in the scenario definition. For the H.264 decoder, for example, there are too many RTSs to take them all into account explicitly. When at run-time a frame arrives with a previously unseen macro-block breakup, it needs to be decided what to do. Hard guarantees on system performance can be given by predicting for these new breakups the backup scenario, which is the scenario that requires the overall worstcase number of cycles to execute. Obviously, if we have to fall back frequently to this backup scenario, this will normally lead to (much) less energy reduction than potentially possible. Fortunately, by definition, this fallback will have to be used very rarely in our approach, making the average loss over the entire execution of the application minimal.

In addition, we can go one step further. In particular, since for video decoding a small percentage of missed frame deadlines is usually acceptable, one can aim for a more aggressive prediction, introducing the risk that a frame may get miss-predicted as belonging to a scenario which has a lower cycle budget than the frame really needs, causing a missed deadline. This leads to a trade-off between overall system quality and QoS in terms of missed deadlines and energy savings. For example, in [31], the application of this additional flexibility has allowed to reduce energy consumption of the H.264 decoder by 46% with less than 0.1% of the deadlines missed, by using only 32 scenarios.

To exemplify the already introduced difference between use-case and system scenarios (see Sect. 2, let us consider a mobile device running an H.264 decoder

that supports two different frame resolutions). From the user perspective, each resolution may be considered as a use-case scenario, because the resolution affects the perceived quality. Due to the different resolution, the two use-case scenarios contain a different number of macro-blocks. Each of the two use-case scenarios can be divided automatically into more system scenarios based on the frame's macro-block mapping breakup, as presented above. This breakup is of no direct interest to the application designer or final product user, because it is a system-internal artifact of the video encoding, but it can clearly be exploited to further reduce energy consumption in the mapping. It may even be possible to integrate certain macro-block breakups of the two different resolutions into a single system scenario.

## 4 Basic Concepts and Terminology

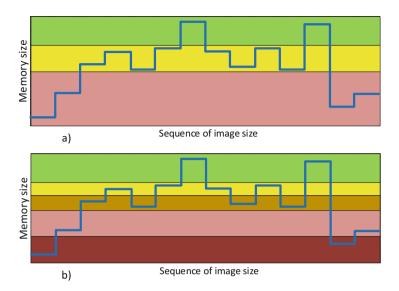

The goal of the system scenario method is, given a system, to exploit at design-time its possible RTSs, without getting into an explosion of detail. If the environment, the inputs, and the hardware architecture status would always be the same, then it would be possible to optimally tune the system to that particular situation. However, since most parameters are typically changing all the time, the system behaves in a dynamic way. This implies that to meet the (at least partly) strict systemlevel requirements which typically apply in our target application domains, it must be designed to handle also the worst-case situation for the hard OoS restriction. Still, it is possible to tune the system at run-time (e.g., change the processor frequency/supply voltage), based on the actual RTS. Unfortunately, if this has to be decided entirely at run-time, the overhead is most likely (way) too large. So, a much better approach is that an optimal configuration for each of the possible situations in the given system is selected up front, at design-time. However, if a different configuration would be stored for every possible RTS, a too huge database is required. Therefore, in our approach the RTSs similar from the resource usage and mapping perspective are clustered together into a single scenario, for which we store a single tuned configuration for the worst case of all RTSs included in that scenario. The latter is the main motivation to keep the RTSs within a given system scenario sufficiently close in the multi-dimensional cost space. For that purpose, a multi-dimensional distance metric has to be defined (see below).

The system scenario methodology deals with two main challenges. First, scenarios introduce various overheads due to switching between scenarios, storing code for a set of scenarios instead of a single application instance, predicting the RTS, etc. The decision of what constitutes a scenario has to take into account all these overheads, which leads to a complicated problem. Therefore, we divide the scenario approach into steps. Second, using a scenario method, the system requires extra functionality: deciding which scenario to switch to (or not to switch), using the scenario to change the system configuration, and updating the scenario set with new information gathered at run-time.

Many system parameters exist that can be tuned at run-time while the system operates, in order to optimize the application behavior on the platform which it is mapped on. We call these parameters system configuration knobs, in short system knobs. A large variety of system knobs is typically available in practical system applications and platforms. Section 3 has given the example of the DVFS knob; entirely different examples of other possible system knobs include the version of the code to run in case of an application that contains multiple versions of its source code; different compiler optimizations being applied to each of them [50]; and the configuration of processing elements (e.g., number and type of function units) in a multi-processor system [60]. Anything that can be changed about the system during operation and that sufficiently affects system cost (directly or indirectly) can be considered a system knob. Note that these changes do not have to occur at the hardware level; they can occur at the software or middleware levels as well. A particular position or tuning of a system knob is called a knob position. If the knob positions are fully fixed at design-time, then the system will always have the same fixed, worst-case cost. By configuring knobs while the system is operating, the system cost can be affected. In the DVFS example, the knob position is the choice of a particular operating voltage, and its change directly affects the processor speed and instantaneous power, and indirectly the total energy consumed to execute the application. However, tuning knob positions at run-time also introduces overhead, which should be taken into account when the net system cost gain is computed.

Instead of choosing a single knob position at design-time, it is possible to design for several different knob positions, combined in a set. At different occurrences during run-time, one of these knob positions is chosen from the available set, depending on the actual RTS. When the RTS starts, the appropriate knob position should be set. Moreover, the knob position is typically not changed during the RTS execution to reduce the overhead. This means the RTS is the integral primitive and hence it also implies the unit time division in our approach. Therefore, it is necessary to determine which RTS is about to start. This prediction is based on RTS parameters, which have to be observable and which are assumed to remain sufficiently constant during the RTS execution. These parameters together with their values in a given RTS form the RTS snapshot. In the H.264 example, the RTS corresponds to the decoding of a frame, and the RTS parameter is the frame breakup into the macro-block types. The number of distinguishable RTSs from a system is exponential in the number of observable parameters. Therefore, to avoid the complexity of handling all of them at run-time, several RTSs are clustered into a single system scenario. A trade-off is present here between optimization quality and run-time overhead of the scenario exploitation, as already illustrated in the motivating example of Sect. 3.

At run-time, the RTS parameters are used to detect the current system scenario rather than the current RTS. In principle, the same knob position is used for all the RTSs in a scenario, so they all have the same cost value, as already indicated: the worst case of all the RTSs in the scenario. Therefore, it is best to cluster RTSs which have nearby cost values in the multi-objective trade-off space. Since at run-time any RTS may be encountered, it is necessary to design not one scenario but rather a scenario set. A scenario set is a partitioning of all possible RTSs, i.e., each RTS must belong to exactly one scenario.

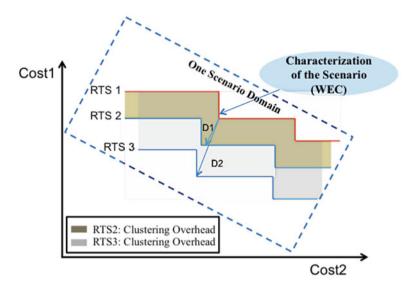

The approach presented above is relatively easy to apply when the cost space is one-dimensional, i.e., when one cost aspect dominates or when all the different cost aspects have been combined in a normalized weighted sum. The latter is not always easy and usually quite suboptimal in practice because comparing apples and oranges in a single dimension usually leads to inconsistencies and suboptimal results. Hence, N-dimensional Pareto sets can and should be used to specify the costs of a system scenario consisting of different RTSs instead of a weighted one-dimensional cost dimension. Such Pareto sets [24, 51] allow to work with a Pareto boundary between all feasible and all non-feasible points in the N-dimensional cost space. The Pareto boundary (the Pareto points) for all the possible RTSs that have been clustered into a scenario (and that can potentially be encountered at run-time) characterizes the scenario. Unfortunately, it becomes less obvious to deal with statements like nearby cost values of RTSs or taking the worst case of all the RTSs in the scenario. So, similarity between costs of different RTSs or in general sets of RTSs (scenarios) has to be substituted by a new element, e.g., by defining the normalized, potentially weighted distance between two N-dimensional Pareto sets as the size of an Ndimensional volume that is present in between these two sets. Based on this distance value, closeness of potential scenario options can be characterized, e.g., to decide whether or not to distinguish scenarios. For more details, the reader is referred to [48, 90, 91].

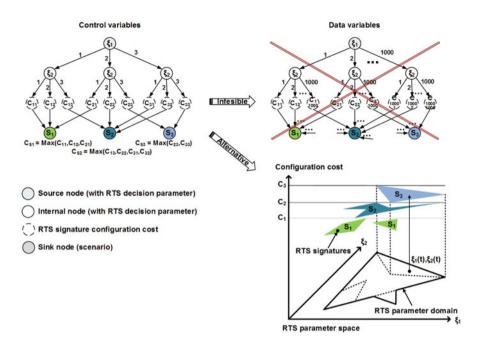

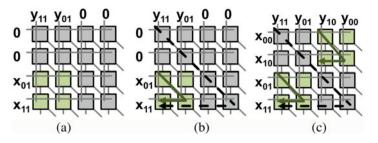

Another crucial characteristic of the system scenario approach lies in the usage for applications dominated by RTS parameters governed by control variables or data variables in the application source code. Initially we have focused our methodology and techniques only on control variables [29]. These techniques assume that the parameters are control variables and/or that they have a limited number (e.g., a few tens up to maximally 100) of possible parameter values for each parameter individually. They can then make use of enumeration and apply a bottom-up approach to cluster these values into system scenarios [26, 28]. This implies some form of conditional CASE statement can be used to represent the options and to select the active case during execution. This is illustrated in Fig. 2.5 on the left. Here 2 different control variable parameters  $\xi_i$  lead to in total 9  $C_{ii}$  run-time situations. The latter have been clustered in 3 system scenarios  $S_i$ . The control diagram represents both the way the detection and the switching can happen at runtime. The discussion in most of this chapter uses this type of systems as a basis. So we will expand in depth the theory for this case. As a main illustration in this chapter, we will also use a running case study based on control variable system scenarios, namely the H.264 decoder.

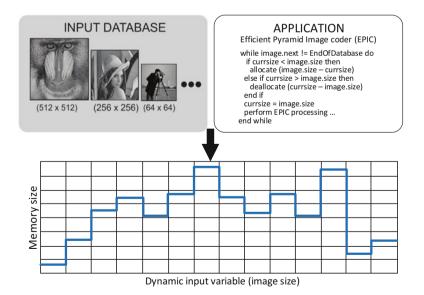

Later, after 2010, we have extended this approach further to data variables [33]. The main theory and illustrations are provided later in this book, in Chap. 3. But here already a brief introduction is included. In particular, this data variable alternative implies that systems have parameters with widely varying data-dependent values coming from data-dependent loops or recursions. When the RTS parameters are data-dependent in this way, they may have thousands or even millions of possible

Fig. 2.5 Control vs data variable-based scenario identification

data values, making bottom-up clustering and enumeration-based prediction/detection totally impractical. That is also shown in Fig. 2.5 at the top right side. The same figure at the bottom right illustrates the theoretical concepts of how to deal with such data variables (see [33]). Let us start from k RTS parameters and N profiled RTS signatures. The latter are defined for each RTS i in Eq. (2.1).

$$r(i) = \xi_1(i), \xi_2(i), \dots, \xi_k(i); c(i)$$

(2.1)

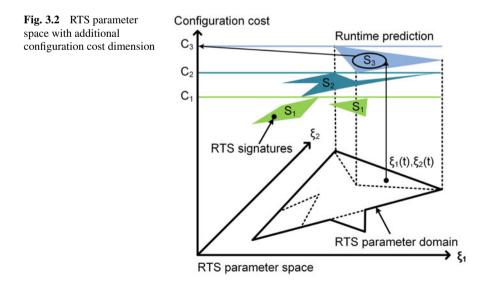

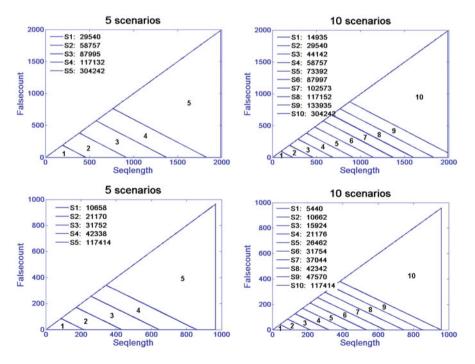

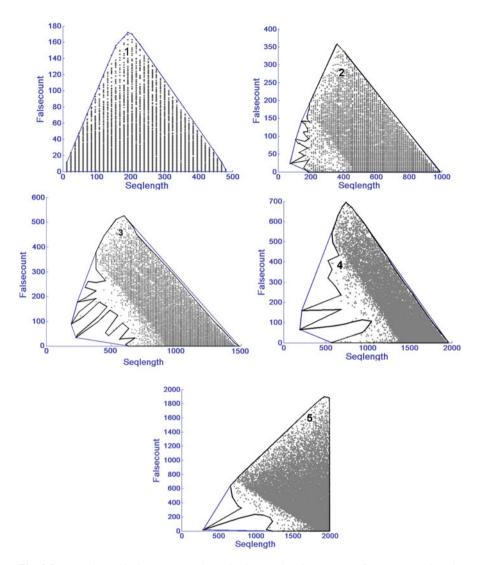

If we assign one dimension to each RTS parameter, the resulting k-dimensional space will define all theoretically possible values for the RTS parameters in the application. We will again call such space an RTS parameter space. When static max and min constraints on the values are added, the space reduces to one or several k-dimensional domain(s). With the representation above, the scenario identification task can be viewed as a distribution of points into S different groups, representing system scenarios, according to which the overall configuration cost is minimized. An RTS point *i* is assigned to scenario *j* whenever its cost c(i) falls into that scenario's cost range  $[C(j)_{\min}, C(j)_{\max}]$ . The scenario cost ranges are determined by a balancing function that tries to achieve that all scenarios have a near-equal probability to occur at run-time. In this way, rare system scenarios are avoided since their storage cost will exceed the gains of adding them. We measure this probability by the number of points, including the repeating ones, that each scenario

contains and call it scenario size. Given a list r of sorted cost RTS signatures (e.g., descending), the scenario cost ranges are then given by the indices corresponding to the integral number of maximum and minimum scenario sizes N/S, as represented in Eq. (2.2).

$$C(j)_{\max} = r((j-1) * N/S + 1); C(j)_{\min} = r((j) * N/S)$$

(2.2)

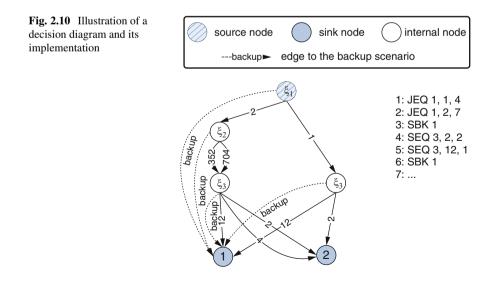

The cost of scenario  $C_j$  is defined as the maximum cost of RTS signatures that it includes:  $C_j = C(j)_{\text{max}}$ . As illustrated in Fig. 2.5, the projection of scenarios onto the RTS parameter space will produce  $M \leq S$  regions that characterize the system scenarios in terms of RTS parameter values. Each region can be described as a polyhedron, and the run-time scenario prediction can be done by checking which polyhedron contains the RTS parameter values of the next RTS. Since we know which scenario the region belongs to, we can foresee that the next running cost will be no more than the cost of that scenario. Checking if a point lies inside a polyhedra is the classical data point location problem from the computational geometry domain, and the advantage of using it for prediction is that it operates on/stores only the vertices of polyhedral regions, not the whole RTS parameter space. This is in contrast to the multi-valued decision diagram (MDD) concept which is used for the control variable option (see Sect. 5.3).

This top-down data variable oriented approach can hence handle arbitrary large domains, provided that the number of convex polyhedral regions stays reasonably low. Otherwise prediction overhead will grow unacceptably. The number of regions depends on the number of system scenarios and the underlying structure of the system, i.e., the relationship between the cost locality of RTS points and the value locality of their RTS parameters.

The desired number of system scenarios is best defined by the user according to the characteristics of the application domain. Typically this is limited to a few dozens because beyond that the potential gains in better following the system dynamics are counterbalanced with the additional cost complexity of detecting and exploiting the (too) large set of possible system scenarios. This can be easily motivated by considering that if the scenario ranges are more or less equally spaced (which is one of the aims anyway) in a one-dimensional cost space, a few dozen scenarios already lead to less than 5% distinction in the associated cost function. For cases where the number of dimensions grows to a large amount, it becomes more complex and the required number of system scenario sets to cover this sufficiently well could potentially grow to a huge amount. But when this would happen, then the extension of so-called subscenarios which we have first introduced in [72] will still provide a way out of this undesired explosion.

Another important extension to keep the number of system scenarios limited is to explicitly allow some remaining parametrization in the position of the Pareto curve in the cost function space. As indicated above, when the system knobs are changing at run-time, we anyway do not want to store a different scenario execution for each of these system knob instances. So we will allow a given "mapping" from the functional system level up to the system implementation level (where the cost functions are defined) to become parametrized in terms of system knob or RTS

parameters. However, that should only be allowed for parameters which maintain the good quality of the chosen mapping for all of the RTS parameter and system knob settings covered by the scenario. This quality will be defined in terms of a multi-dimensional distance function allowing to evaluate how "close" RTS instances are positioned, as explained earlier. We have to be careful then that only parameters are allowed which do not affect the optimal mapping choice and which maintain a simple near-linear relation in defining the related cost function. For instance, when you map a given one-dimensional loop nest of size N with the available control variable options to a data-path or in general a digital SoC platform, the value of N only needs to be fixed inside the control variable scenario when that way of platform mapping is more than negligibly depending on the value of N. But in many applications that is not the case, or at least not for all loop iterators inside a multi-dimensional loop nest. So then the resulting system scenarios can share the same internal mapping for each RTS instance and still have a cost function (defined, e.g., in terms of performance, energy, or sometimes area) which can be expressed as a simple parametrized formula directly depending on the value of N. For instance, performance and energy for the execution of the entire loop can be considered linear in N. Something similar can happen for data variable scenarios when you consider control flow or other parameters that are not related directly to the data variable dimension (which are usually loops or data sizes). This implies that the distance function calculation for the Pareto curves in the cost space defined above should also incorporating N as a parameter. Hence, the closeness of RTS instances that are candidates for the system scenario clustering is evaluated for a given value of N. To allow the easy extrapolation for the closeness for all other values of N, it is now obvious why we strongly preferably want a linear relation of the cost function axes. A clear demonstration of the power and the importance of such parametrized formulas is present in the scenario methodology that has been conceived for dealing with the mapping of dynamic wavelet-based video codecs on L1 data caches (see [16, 17]). There, quite complex but run-time efficient equations have been derived to combine many different Pareto curve working points and positions in compact representations which are tightly characterizing the actual runtime situations. The case of even more strongly dynamic video codecs has been dealt with in [18], with a case study focused on motion compensated temporal filtering (MCTF). In that application, the parameters are so strongly varying at run-time that the combination of the Pareto-curves for the RTSs cannot happen only based on equations. So an alternative has been proposed for such cases based on specializing for the most promising localization schemes.

The following section details the systematic aspects of our methodology of identifying and exploiting system scenarios to create more efficient embedded systems, describing generic solution strategies for the various methodology steps whenever possible.

# 5 System Scenario Methodology

Although the concept of system scenarios has been applied before on top of concrete design techniques both in an ad-hoc way [9, 34, 47, 60] and in a more systematic way [25, 28, 31, 44, 50, 85], it is possible to generalize all those scenario approaches into a common systematic methodology. The first paper where we have described this is [29]. This section summarizes that general and still near-optimal methodology, providing generic solutions whenever possible. But the main instantiation is worked out for control variables, similar to what has been presented earlier in [29]. On top of this, we have further extended the approach to cover data variables, as already introduced in Sect. 4 and later in Chap. 3. The rest of this section is structured as follows. The overall methodology overview is provided in Sect. 5.1. The remaining subsections refine each of the steps of the general methodology. In the subsequent subsections, we always refer to system scenarios also when we use the abbreviated term scenario.

# 5.1 Methodology Overview