# When Fault Injection Collides with Hardware Complexity

Sebanjila Kevin Bukasa<br/>( $^{\boxtimes)},$ Ludovic Claudepierre, Ronan Lashermes, and Jean-Louis Lanet

LHS Inria, Rennes, France {sebanjila.bukasa,ludovic.claudepierre,ronan.lashermes, jean-louis.lanet}@inria.fr

Abstract. Fault Injections (FI) against hardware circuits can make a system inoperable or lead to information security breaches. FI can be used preemptively in order to detect and mitigate weaknesses in a design. FI is an old field of study and therefore numerous techniques and tools can be used for that purpose. Each technique can be used at different levels of circuit design, and has strengths and weaknesses. In this paper, we review these techniques to show their pros and cons and more precisely we highlight their shortcomings with respect to the complexity of modern systems.

# 1 Introduction

In the field of hardware security, Fault Injection (FI) is a technique to alter the correct execution of a program in a chip. The resulting errors can be harnessed in order to weaken the security of the device, by extracting cryptographic keys for example. In the case of hardware security, the distinction between errors (the internal system state is erroneous) and failures (the behaviour does not follow specifications) is blurred. Indeed, the attacker can observe, or deduce, the state of the device though its interaction with the environment; thus it is considered that the attacker can observe errors and exploit them. For example, a timing attack can leak a password during its verification. It is therefore common to use the term *errors* to designate either errors or failures.

A fault may be caused by radiation (laser pulses, electromagnetic pulses, alpha particles, ...), power glitches, clock glitches, abnormal temperatures, etc. Faults are naturally found in hardware, but can also be voluntarily caused by an attacker. In all cases, they can often be exploited for malicious activities. Therefore faults must be mitigated.

FI can be used to infer the faults that can be created in a system, to analyse the errors created as a consequence and whether they make the system vulnerable. The difficulty is in the trade-off between the size of the state space to explore and the speed of the analysis. We will show that the complexity of modern system renders FI tools less precise because they cannot accurately model the erroneous states.

© Springer Nature Switzerland AG 2019

N. Zincir-Heywood et al. (Eds.): FPS 2018, LNCS 11358, pp. 243–256, 2019. https://doi.org/10.1007/978-3-030-18419-3\_16

In this paper, after a context presentation in Sect. 2, we review the techniques and tools to assess the vulnerability of a device to FI in Sect. 3. The shortcomings of actual techniques will be presented in Sect. 4 as well as a discussion on how to improve them. Finally, the conclusion is drawn in Sect. 5.

## 2 Context Safety/Security

FI is an old research discipline [1-4], which originates from the study of fault tolerant systems, mainly from aerospace. FI is defined by Arlat [5] as a validation technique of dependability for fault tolerant systems. It consists in observing system behaviour in presence of faults defined with a fault model. At the beginning, FI was applied on hardware components. Consequently, corresponding fault models were comprised of effects that were deemed representative for failing logic elements, in particular stuck-at logical zero or one. One would be able to inject a fault at transistor level which models an unintended physical effect, such as a signal transition caused by a heavy ion hit and resulting in a communication error at system level for example. While this approach is close to reality, a practical implementation is barely possible.

All FI techniques aim to solve several problems:

- Injection of faults;

- Observation of their effects;

- Intrusiveness of the solution;

- Capacity to explore the entire state space.

The FI techniques have been recognized for a long time necessary to validate the dependability of a system by analysing the behaviour of devices when a fault occurs. More recently, secure devices have to face fault attacks which are similar to failure problems. Efforts have been made to develop techniques for injecting faults into a system prototype or model.

When considering information security, fault injection assumes that the attacker is able to target specific assets in the system. It means that she knows exactly what kind of behaviour she requires to reach her goal. In case of targeting cryptographic algorithms [6,7] or assets (keys, tokens, ...) several solutions have been proposed to protect them against fault injections [8]. Applications can be designed to be resilient against FI, but this resilience mainly focus on software execution of these applications, in some cases this can be a problem, indeed a complete confidence is given to hardware.

## 3 Fault Injection Techniques

Several techniques exist to inject faults, all of them with advantages and disadvantages. Here is an overview of these techniques.

#### 3.1 Hardware-Based FI

Hardware based FI aims at disturbing hardware with physical and environmental parameters (heavy ion radiation, electromagnetic interferences [9], *etc.*), injecting voltage dips on power rails [10, 11] laser fault injection [12] or modifying the value of some pins with circuit editing. The main advantage of this family of techniques over the other solutions is that they evaluate the final device. To achieve this kind of FI it is necessary to possess a final version of the evaluated device.

The effects of physical injections are difficult to control and repeatability of experiment is hard to achieve. To obtain repeatability, instead of injecting physically a fault, injection mechanisms emulate effects of physical perturbations on hardware such as pin-level FI [13].

Fault Injection system for Study of Transient fault effects (FIST) uses heavyion radiation or power disturbance faults to create faults inside a chip when it is exposed to radiation. It can cause single or multiple bit-flips producing transient faults at random locations directly inside a chip, which cannot be done with pin-level injections.

Messaline [5] is a pin-level fault forcing system. It uses both active probes and sockets to conduct pin-level fault injection. It can inject stuck-at, open, bridging and complex logical faults, among others. It can also tune the duration of the fault existence and its frequency. RIFLE [14] is also a pin-level fault injection system for dependability validation. This system can be adapted to a wide range of target systems and faults are mainly injected in processor pins. FI is deterministic and can be reproduced if needed. Different kind of faults can be injected and the fault injector is able to detect whether the injected fault has produced an error or not without specific hardware.

Obviously, hardware-based tools are also hardware dependent. Furthermore, the setup of these hardware-based injectors is rather complex.

#### 3.2 Simulation-Based FI

Simulation based hardware fault injection techniques simulate hardware description of tested circuit using high-level models (mostly Hardware Description Language (HDL) models). It consists in injecting faults into that model to evaluate their impacts. Most of the tools modify the hardware description of tested circuit to include the components necessary to inject faults. These fault injection components can be designed to inject different fault behaviours depending on the fault model. Faults can also be injected using hardware description language simulator commands which allow variables and signals of circuit being modified.

A major disadvantage of simulation based techniques is that they are extremely slow. Simulating the register transfer level (RTL) description of a circuit is multiple orders of magnitude slower than actual circuit operation speed. Hence, even for relatively small processors, simulation based fault injection tools can only evaluate fault propagation for a very short time interval.

VERIFY [15] (VHDL-based Evaluation of Reliability by Injection Faults Efficiently) uses an extension of VHDL for describing faults correlated to a component, enabling hardware manufacturers to express their knowledge of fault behaviour on their components. Multi-threaded fault injection which uses checkpoints and comparison with a golden run is used for faster simulation of faulty runs. Proposed extension to VHDL language unfortunately requires modification on language itself. VERIFY uses an integrated fault model which cannot be extended.

MEFISTO-C [16] conducts fault injection experiments using VHDL simulation models. The tool is an improved version of MEFISTO tool which was developed jointly by LAAS-CNRS and Chalmers. MEFISTO-C uses a VHDL simulator and injects faults via simulator commands in variables and signals defined by a VHDL model. It offers to users a variety of predefined fault models as well as other features to set-up and automatically conduct fault injection campaigns.

FAUMachine [17] is a tool allowing simulation of complete systems, it was the main core for different works in the field of fault injections [18,19]. Its particularity is that it allows to simulate various types of faults and in various devices connected to the system, while making possible the observation of the impacts on the total operation of the system

### 3.3 Emulation-Based FI

System emulation uses hardware prototyping on Field Programmable Gate Arrays (FPGA) based logic emulation systems [20,21]. This technique has been presented as an alternative solution in order to reduce time spent during simulation-based fault injection campaigns.

This technique allows designer to study the actual behaviour of circuits in application environment, taking into account real-time interactions. However, when an emulator is used, initial VHDL description must be complete and fully synthesizable. Modified circuit contains sequences of operations which can flip their output bit based on a control signal value. Such techniques require an additional control mechanism to specify time and location of fault injection in circuit. If such a control mechanism is implemented in circuit, its complexity increases with number of fault injectable memory elements.

Antoni *et al.* [22] proposed a technique to inject a fault on chosen memory elements at run time on a FPGA using runtime reconfiguration. This eliminates the need for having a complex control circuit to determine injection location. However, the time required to reconfigure the circuit could be significant when compared to the total application run time.

Civera *et al.* [20] proposed another solution to provide a more flexible control over runtime fault injection. They used modified flip-flop circuits capable of injecting faults based on a control bit associated with each flip-flop. All these control bits are tied together like a scan-chain and at run time can be programmed to inject fault in any desired flip-flop in the circuit.

## 3.4 Software Implemented FI

The objective of these techniques consists in reproducing at software level errors that would have been produced by faults at hardware level. They are mostly used in order to detect and predict vulnerabilities with respect to hardware fault injection. Software implemented fault injection (SWIFI) tools use a software level abstraction of fault models in order to inject errors in software while it runs or by modifying programs before execution. This approach does not need any hardware modification. SWIFI provides a way to test complete systems including the operating system and the applicative layer. This makes SWIFI techniques quite popular and a large number of such tools exists, Table 1 summarizes some of them and explore their particularities.

| SWIFI technique | Fault model                                      | Fault target                 | Injection point            |

|-----------------|--------------------------------------------------|------------------------------|----------------------------|

| CEU [23]        | Bit flip                                         | Variables                    | Runtime<br>(interruptions) |

| DOCTOR [24]     | Bit flips                                        | Communications,<br>variables | Preruntime                 |

| EFS [25]        | Bit flips, code insertion,<br>data modifications | Control flow, variables      | Runtime (OS<br>service)    |

| FERRARI [26]    | Address, data or flags<br>modifications          | Control flow, variables      | Runtime (parallel process) |

| FIES [27]       | Bit flip, bridging and<br>stuck-at faults        | Control flow, variables      | Runtime                    |

| XCEPTION [28]   | Bit flip, bridging and<br>stuck-at faults        | Variables                    | Runtime<br>(interruptions) |

Table 1. Overview of some SWIFI techniques

The most common fault models are:

- instruction skip (one or several instructions are not executed),

- instruction modification (one or several instructions are modified according to a pattern such as single bit-flip, random change, ...).

Common software mechanisms used for run time FI, such as perturbation functions require a modification of the program. Unfortunately, this extra instrumentation causes execution overhead that will affect the system behaviour (speed, memory consumption, ...). For example, FERRARI [26] and EFS [25] tools require some context switches between its fault injection process and target system process.

A common problem with run time approach is the intrusiveness which refers to the alteration of the original system due to fault injection experiment setup (*e.g.* changes in program flow, additional components, temporal variation, ...). Depending on the actual intention of fault injection, respective tools have to cope with completely different requirements. In contrast to an ideal tool which always provides low intrusiveness, high visibility and high performance, available tools are only specialized on a subset of these requirements.

The major drawback of SWIFI is related to state space problem. The tools often generate much more faults than any other techniques (since the abstraction level has a richer representation, *i.e.* there may be  $2^{32}$  possible instruction values in a 32-bit system and less that  $2^{32}$  wires in the chip). Yet most of the time generated faults do not lead to failures, the error may have been silently suppressed during the execution. The challenge is to either generate only a minimal set of faults (those that can lead to a Silent Data Corruption) or to prune them while they are generated. This leads to several optimization phases during simulation and remains a difficult challenge.

In the context of information security, errors can often be exploited even in the absence of failures. An error can cause copying of a secret in a vulnerable part of memory for example. Since SWIFI tools use a software level abstraction of fault models, they cannot capture such vulnerabilities.

# 4 Techniques Validity

We consider ourselves as evaluators. When it comes to FI, we want to evaluate if a technique is more appropriate in order to evaluate behaviour of a device when a fault occur.

Various injection means exist and several techniques have been using them in different way and targeting several type of devices. Since simulation and emulation based techniques require a white-box model (access to HDL sources, ...) that are most of the time not available to evaluators.

In this section we limit ourselves to hardware-based and software-based injections techniques.

## 4.1 Experiences

In order to test the consistency of SWIFI models, in particular their software level abstraction of fault models with real observations, we conducted different experiments, which we will present here.

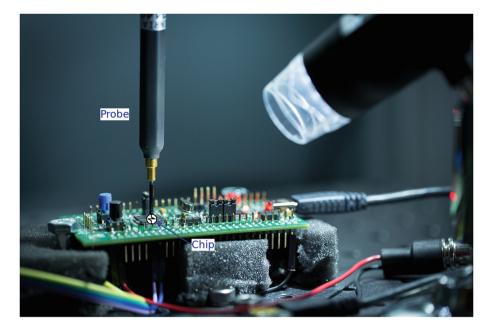

**Faustine Platform.** Our platform, called Faustine Fig. 1, is made of a Keysight 33509B pulse generator, a Keysight 81160A signal generator and a Milmega 80RF1000-175 power amplifier, connected in sequence to generate a signal. This signal then passes through a Langer RF probe RF B 0.3-3 located on the targeted chip to generate an Electromagnetic Fault Injection (EMFI).

In order to launch a fault injection, a synchronization signal (a trigger) is sent by the targeted chip General-Purpose Input/Output (GPIO) (controlled from the code) directly to the 33509B pulse generator. This experimental trick,

Fig. 1. Overview of Faustine platform

possible when the attacker has control of the code (*i.e.* only for vulnerability assessment) is not mandatory. Other synchronization possibilities include sniffing communications with the target or measuring its EM emissions to find a relevant pattern.

The location of the probe on the chip was chosen after a scan that determined the most sensitive area on the chip. The same location was kept for all experiments.

**Microcontroller.** We first analyse a Microcontroller ( $\mu$ C). The targeted board is an STM32VLDISCOVERY board with an STM32F100RB chip, embedding an ARM Cortex-M3 core running at 24 MHz (41.7 ns clock period). As shown in Fig. 2, probe is just on top of the chip.

On this board the tested software is a PIN code checker, the entered PIN code is compared with the internal PIN code if it is false (false=1 in Listing 1.1), the status variable takes the value 0xFFFFFFF, otherwise it takes 0x55555555. Thus in the first case, access will be denied, in the second it will be granted.

```

if(false == 1) {

status = 0xFFFFFFF; }

else {

status = 0x55555555; }

```

Fig. 2. STM32 under probe

| cmp r3, #1              | ; r3 contains *false* |

|-------------------------|-----------------------|

| ite eq                  | ; if then else        |

| moveq.w r4, #4294967295 | ; OxFFFFFFFF          |

| movne.w r4, #1431655765 | ; 0x55555555          |

Listing 1.2. Resulting assembly (thumb2)

As we can see on Listing 1.2, in order to modify the behaviour of the program and thus get access without the PIN code, we can target the *if then else (ite)* instruction. If it is possible to not execute it, then the next two instructions will execute in sequence and, as their result is stored in the same register (r4), only the second assignment will have an impact (overwriting the first one).

In the case of SWIFI, we consider the software level abstraction of fault model by deleting (manual edition of the binary) this instruction which allows us to see that it is indeed the right target, then we target the execution of this instruction with a hardware fault.

In this way, when we inject our fault, we try to synchronize with the code snippet in Listing 1.2 and target the instruction ite eq. In 10% of the cases, the execution is faulty (status = 0x5555555), proving that the SWIFI allows us in this case to find a point of sensitivity and thus to inject our fault effectively.

However, we found that different timings (over a span of 5 instructions) were able to get our faulty behaviour. This can have several plausible explanations, such as the fact that several different skipped instructions can lead to the same impact, or that the *ite eq* instruction can be impacted at different levels of its execution pipeline. **System-on-Chip.** We then analysed a System-on-Chip (SoC). The targeted board is a Raspberry Pi3 board with a BCM2837 chip, which embeds 4 ARM Cortex-A53 cores, running at up to 1.2 GHz (833ps clock period).

```

while(1){

wait(x*desynch_value+x);

turn_on_LED(y);

wait(x*activation_duration+x)

turn_off_LED(y);

}

```

#### Listing 1.3. Targeted C code

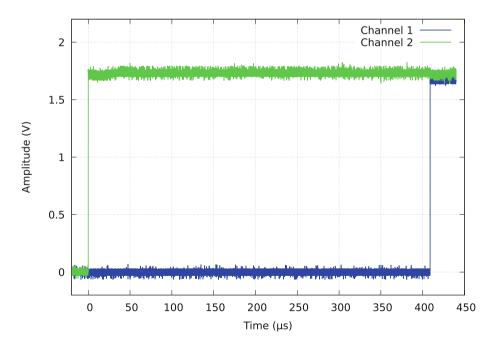

Here we want to evaluate the impact of a fault and compare it to the SWIFI models. The goal is to see if a hardware generated fault can be explained by a software abstraction of the fault model, represented by software modification. Thus we inject faults at different timings during the execution of a loop (Listing 1.3) on 2 of the 4 cores, others being used to communicate with the host, while desynchronizing them (they are not started at the same time). The 2 cores (x) are activating their own signal (y) during a given time in parameter  $(x * activation\_duration + x)$ , this leads to a time span visible in Fig. 3.

**Fig. 3.** Signals are desynchronized. Channel 1 for GPIO signal sent by core 1, channel 2 for GPIO signal sent by core 2. Time span between the two rising edges is due to  $"x * desynch_value + x"$  in Listing 1.3.

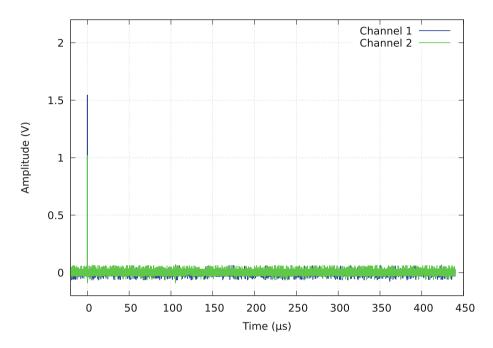

Whatever the timing of the injection, the impact was the same: this had the effect of largely modifying the execution time of the loop on each core, alternately faster or slower in a random way. Another effect is to synchronize the different cores between them (in Fig. 4), but also to break one of the two channels of communication with our host (application channel on one core and debug channel using JTAG).

**Fig. 4.** Signals are shorter and synchronized. First, time span seems to have disappeared, then " $x * activation\_duration + x$ " (in Listing 1.3) seems to have changed to be equal in the 2 cores.

In this case we were not able to find a match with software abstraction of the fault model as usually used in SWIFI techniques. So this lead us to question what makes the difference between a  $\mu$ C and a SoC and thus what prevents us from using SWIFI in the second case.

#### 4.2 System Complexity

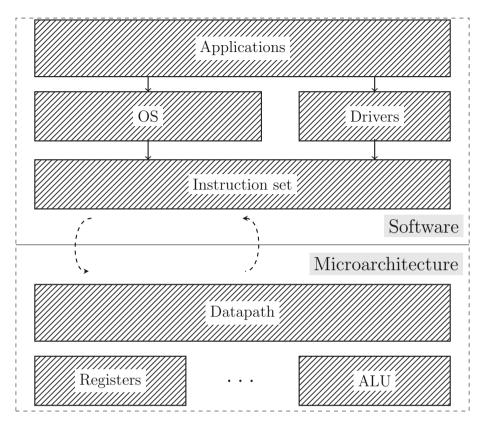

**Abstraction Layers.** A computing system is a complex device. In order to allow humans to build mental models of how such systems work, this complexity is often hidden behind abstraction layers as visible in Fig. 5.

There is a main division between these layers corresponding to the hardware/software interface constituted by the Instruction Set Architecture (ISA). On the upper side, software is constituted of a succession of instructions.

Fig. 5. Abstraction layers

On the lower side, the micro-architecture (hardware) is responsible for upholding this abstract representation.

The micro-architecture is widely different if we consider a  $\mu$ C or a SoC. In the first case, the instruction execution flow is quite simple, with a single core, a simple memory hierarchy, in-order execution, *etc.* In the case of a SoC, the micro-architecture can be quite complex. Several core can share the same memory space, with a complex memory hierarchy (several cache levels, shared or not). Instructions can be executed out-of-order or even speculatively. What happens in hardware differs from the simple model provided by the ISA.

**SWIFI Shortcomings.** The hardware part is mostly fixed, the application designer cannot modify it whereas she controls the software part of the application. In consequences, in order to protect her application, she will act on the software only. This fact remains a main reason that SWIFI techniques are quite popular: they allow the application developer to act upon the results. Therefore SWIFI techniques are preferred by software developers whereas hardware-based fault models are preferred by hardware designers in order to secure the system.

The problem is that the application still executes on a given hardware that may or may not be vulnerable to fault injection. The application developer would like to free herself from this responsibility by considering only software.

Yet SWIFI cannot capture the full extent of hardware fault injection consequences. Indeed they are not able to analyze the range of interactions and components present at the hardware level (the microarchitecture in Fig. 5) by abstracting the behaviour at the software level. Consider a Direct Memory Access (DMA) transfer for example. In this case, a section of memory is copied to another without the Central Processing Unit (CPU) involvement. Instructions are present to describe the desired memory transfer then it is enforced in parallel of the program execution. Therefore, any fault on the DMA transfer cannot be captured by a SWIFI technique.

**Complexity Evolution.** It can be argued that cases that cannot be captured by SWIFI, such as DMA transfers, are special cases not representative of classical applications.

But as we have show in Sect. 4.1, if these asynchronous behaviours are seldom present in simple systems, they are ubiquitous in modern SoCs. In order to squeeze the maximum performance out of modern SoCs, a lot of processing is done in parallel of the instruction flow execution.

The recent trend is in more complex systems, not simpler. As a consequence, SWIFI techniques are less and less able to capture the extent of possible errors in these systems.

# 5 Conclusions

FI tools are quite useful in the context of dependability and information security. They can be used to assess the security of a system with respect to fault attacks. Application developers mostly use SWIFI tools to predict the behaviour of their program in the event of a fault according to a software abstraction of the fault model. However, we have seen that the part targeted by the fault attacks is at the microarchitecture level which is the physical representation of the system, we have seen that in the case of a simple system, such as an  $\mu$ C (also in [29,30]), it was possible to find an abstraction at the software level of behaviour occurring at the hardware level. Nevertheless, through the experiments we conducted it appeared to us that on systems where the microarchitecture is more complex, as in the case of the SoC it became complex to find an abstraction at the software level of the models of faults corresponding to those generally considered by SWIFI methods (bit-flip, stuck-at, skip instruction, etc.). As a consequence, SWIFI is less and less relevant for such systems.

## References

- Hardie, F.H., Suhocki, R.J.: Design and use of fault simulation for saturn computer design. IEEE Trans. Electron. Comput. 4, 412–429 (1967)

- Armstrong, D.: A deductive method for simulating faults in logic circuits. IEEE Trans. Comput. 21, 464–471 (1972)

- Ulrich, E.G., Baker, T., Williams, L.: Fault-test analysis techniques based on logic simulation. In: Proceedings of the 9th Design Automation Workshop, pp. 111–115. ACM (1972)

- Menon, P.R., Chappell, S.G.: Deductive fault simulation with functional blocks. IEEE Trans. Comput. 27(8), 689–695 (1978)

- 5. Arlat, J.: Validation de la sûreté de fonctionnement par injection de fautes, méthode- mise en oeuvre- application. Ph.D. dissertation (1990)

- Joye, M., Tunstall, M.: Fault Analysis in Cryptography, vol. 147. Springer, Heidelberg (2012). https://doi.org/10.1007/978-3-642-29656-7

- Lashermes, R., Fournier, J., Goubin, L.: Inverting the final exponentiation of tate pairings on ordinary elliptic curves using faults. In: Bertoni, G., Coron, J.-S. (eds.) CHES 2013. LNCS, vol. 8086, pp. 365–382. Springer, Heidelberg (2013). https:// doi.org/10.1007/978-3-642-40349-1\_21

- Barenghi, A., Breveglieri, L., Koren, I., Naccache, D.: Fault injection attacks on cryptographic devices: theory, practice, and countermeasures. Proc. IEEE 100(11), 3056–3076 (2012)

- Moro, N., Dehbaoui, A., Heydemann, K., Robisson, B., Encrenaz, E.: Electromagnetic fault injection: towards a fault model on a 32-bit microcontroller. arXiv preprint arXiv:1402.6421 (2014)

- Timmers, N., Spruyt, A., Witteman, M.: Controlling PC on ARM using fault injection. In: 2016 Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC), pp. 25–35. IEEE (2016)

- Tunstall, M., Mukhopadhyay, D., Ali, S.: Differential fault analysis of the advanced encryption standard using a single fault. In: Ardagna, C.A., Zhou, J. (eds.) WISTP 2011. LNCS, vol. 6633, pp. 224–233. Springer, Heidelberg (2011). https://doi.org/ 10.1007/978-3-642-21040-2\_15

- Buchner, S., et al.: Laser simulation of single event upsets. IEEE Trans. Nucl. Sci. 34(6), 1227–1233 (1987)

- Arlat, J., et al.: Fault injection for dependability validation: a methodology and some applications. IEEE Trans. Software Eng. 16(2), 166–182 (1990)

- Madeira, H., Rela, M., Moreira, F., Silva, J.G.: RIFLE: a general purpose pin-level fault injector. In: Echtle, K., Hammer, D., Powell, D. (eds.) EDCC 1994. LNCS, vol. 852, pp. 197–216. Springer, Heidelberg (1994). https://doi.org/10.1007/3-540-58426-9\_132

- Sieh, V., Tschache, O., Balbach, F.: VERIFY: evaluation of reliability using VHDLmodels with embedded fault descriptions. In: Twenty-Seventh Annual International Symposium on Fault-Tolerant Computing, FTCS-27. Digest of Papers, pp. 32–36. IEEE (1997)

- Folkesson, P., Svensson, S., Karlsson, J.: A comparison of simulation based and scan chain implemented fault injection. In: Twenty-Eighth Annual International Symposium on Fault-Tolerant Computing. Digest of Papers, pp. 284–293. IEEE (1998)

- 17. Sieh, V.: Faumachine. http://www3.informatik.uni-erlangen.de/EN/Research/ FAUmachine/description.shtml

- Potyra, S., Sieh, V., Cin, M.D.: Evaluating fault-tolerant system designs using FAUmachine. In: Proceedings of the 2007 Workshop on Engineering Fault Tolerant Systems, p. 9. ACM (2007)

- Sand, M., Potyra, S., Sieh, V.: Deterministic high-speed simulation of complex systems including fault-injection. In: 2009 IEEE/IFIP International Conference on Dependable Systems & Networks, pp. 211–216. IEEE (2009)

- Civera, P., Macchiarulo, L., Rebaudengo, M., Reorda, M.S., Violante, A.: Exploiting FPGA for accelerating fault injection experiments. In: Proceedings of the Seventh International On-Line Testing Workshop, pp. 9–13. IEEE (2001)

- Leveugle, R.: Fault injection in VHDL descriptions and emulation. In: Proceedings-IEEE-International-Symposium-on-Defect-and-Fault-Tolerance-in-VLSI-Systems, pp. 414–419. IEEE Comput. Soc., Los Alamitos (2000)

- Antoni, L., Leveugle, R., Feher, M.: Using run-time reconfiguration for fault injection in hardware prototypes. In: Proceedings of the 17th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, DFT 2002, pp. 245–253. IEEE (2002)

- Velazco, R., Rezgui, S., Ecoffet, R.: Predicting error rate for microprocessor-based digital architectures through C.E.U. (Code Emulating Upsets) injection. IEEE Trans. Nucl. Sci. 47(6), 2405–2411 (2000)

- Han, S., Shin, K.G., Rosenberg, H.A.: Doctor: an integrated software fault injection environment for distributed real-time systems. In: Proceedings of the International Computer Performance and Dependability Symposium, pp. 204–213. IEEE (1995)

- Riviere, L., Bringer, J., Le, T.-H., Chabanne, H.: A novel simulation approach for fault injection resistance evaluation on smart cards. In: 2015 IEEE Eighth International Conference on Software Testing, Verification and Validation Workshops (ICSTW), pp. 1–8. IEEE (2015)

- 26. Kanawati, G.A., Kanawati, N.A., Abraham, J.A.: FERRARI: a flexible softwarebased fault and error injection system. IEEE Trans. Comput. 44(2), 248–260 (1995)

- 27. Höller, A., Rauter, T., Iber, J., Kreiner, C.: Diverse compiling for microprocessor fault detection in temporal redundant systems. In: 2015 IEEE International Conference on Computer and Information Technology; Ubiquitous Computing and Communications; Dependable, Autonomic and Secure Computing; Pervasive Intelligence and Computing, pp. 1928–1935, October 2015

- Carreira, J., Madeira, H., Silva, J.G., et al.: Xception: software fault injection and monitoring in processor functional units. Dependable Comput. Fault Tolerant Syst. 10, 245–266 (1998)

- Yuce, B., Ghalaty, N.F., Schaumont, P.: Improving fault attacks on embedded software using RISC pipeline characterization. In: 2015 Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC), pp. 97–108. IEEE (2015)

- Riviere, L., Najm, Z., Rauzy, P., Danger, J.-L., Bringer, J., Sauvage, L.: High precision fault injections on the instruction cache of ARMv7-M architectures. arXiv preprint arXiv:1510.01537 (2015)